Integrated Silicon Solution, Inc. -- www.issi.com --

1-800-379-4774

1

PRELIMINARY INFORMATION

Rev. 00C

07/22/02

IS71V08F64GS08

IS71V16F64GS08

ISSI

Æ

Copyright © 2002 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time

without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to

obtain the latest version of this device specification before relying on any published information and before placing orders for products.

PRELIMINARY INFORMATION

JULY 2002

3.0 Volt-Only Flash & SRAM COMBO with Stacked Multi-Chip

Package (MCP) -- 64 Mbit Simultaneous Operation Flash

Memory and 8 Mbit Static RAM

MCP FEATURES

∑

Power supply voltage 2.7V to 3.3V

∑

High performance:

Flash: 70 ns maximum access time

SRAM: 70 ns maximum access time

∑

Package: 101-ball BGA & 73-ball BGA

∑

Industrial Temperature: -40C to +85C

FLASH FEATURES

∑

Power Dissipation:

Read Current at 1 Mhz: 7 mA maximum

Read Current at 5 Mhz: 18 mA maximum

Sleep Mode: 5

µ

A maximum

∑

Simultaneous R/W Operations (dual virtual bank):

Zero latency between read and write operations; Data

can be programmed or erased in one bank while data

is simultaneously being read from the other bank

∑

Low-Power Mode:

A period of no activity causes flash to enter a

low-power state

∑

Erase Suspend/Resume:

Suspends of erase activity to allow a read in the

same bank

∑

Sector Erase Architecture:

16 words of 4k size and 126 words of 32K size (32 Mbit)

Any combination of sectors, or the entire flash can

be simultaneously erased

∑

Erase Algorithms:

Automatically preprograms/erases the flash memory

entirely, or by sector

∑

Program Algorithms:

Automatically writes and verifies data at specified

address

∑

Hidden ROM Region:

256 byte with a Factory-serialized secure electronic

serial number (ESN), which is accessible through a

command sequence

∑

Data Polling and Toggle Bit:

Allow for detection of program or erase cycle

completion

∑

Ready-Busy output (RY/

BY

)

Detection of program or erase cycle completion

∑

Over 100,000 write/erase cycles

∑

Low supply voltage (Vccf

2.5V) inhibits writes

∑

WP

/ACC input pin:

If V

IL

, allows partial protection of boot sectors

If V

IH

, allows removal of boot sector protection

If Vacc, program time is improved

SRAM FEATURES (8 Mb density)

∑

Power Dissipation:

Operating: 25 mA maximum

Standby: 15 µA maximum

∑

Chip Selects:

CE1

s, CE2s

∑

Power down feature using

CE1

s, or CE2s,

or

LB

s &

UB

s

∑

Data retention supply voltage: 1.0 to 3.3 volt

∑

Byte data control:

LB

s (DQ0≠DQ7),

UB

s

(DQ8≠DQ15) -- on x16 version

GENERAL DESCRIPTION

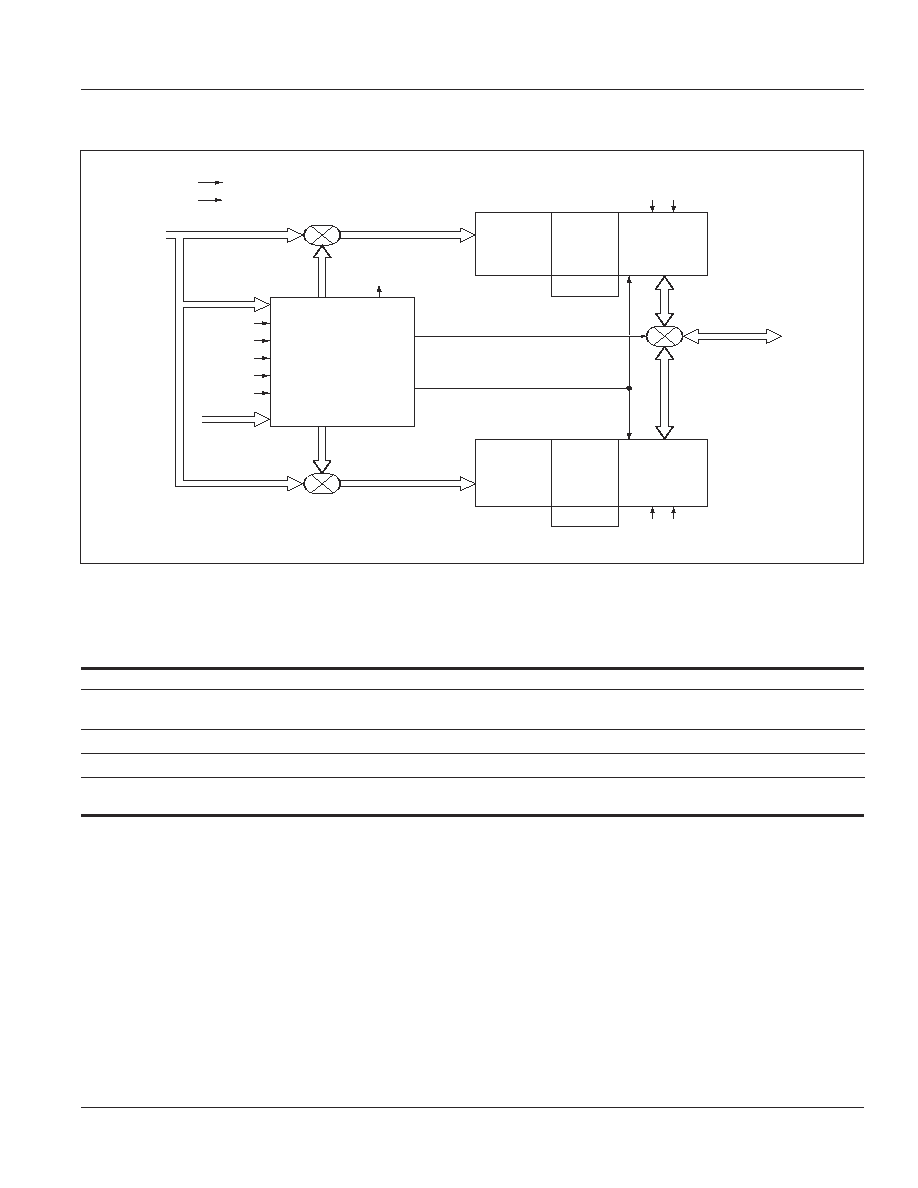

The flash and SRAM MCP is available in 64 Mbit Flash/8

Mbit SRAM, with a data bus of either x8 or x16. The 64 Mbit

flash is composed of 4,194,304 words of 16 bits or 8,388,608

bytes of 8 bits. The 8Mbit SRAM has 524,288 words of 16

bits or 1,048,576 bytes of 8 bits. Data lines DQ0-DQ7

handle the x8 format, while lines DQ0-DQ15 handle the

x16 format.

The package uses a 3.0V power supply for all operations.

No other source is required for program and erase opera-

tions. The flash can be programmed in system using this

3.0V supply, or can be programmed in a standard EPROM

programmer.

The 64 Mbit flash/8 Mbit SRAM is offered in a 73-ball BGA

or 101-ball BGA package. The flash is compatible with the

JEDEC Flash command set standard. The flash access

time is 70 or 85 ns and the SRAM access time is 70 ns.

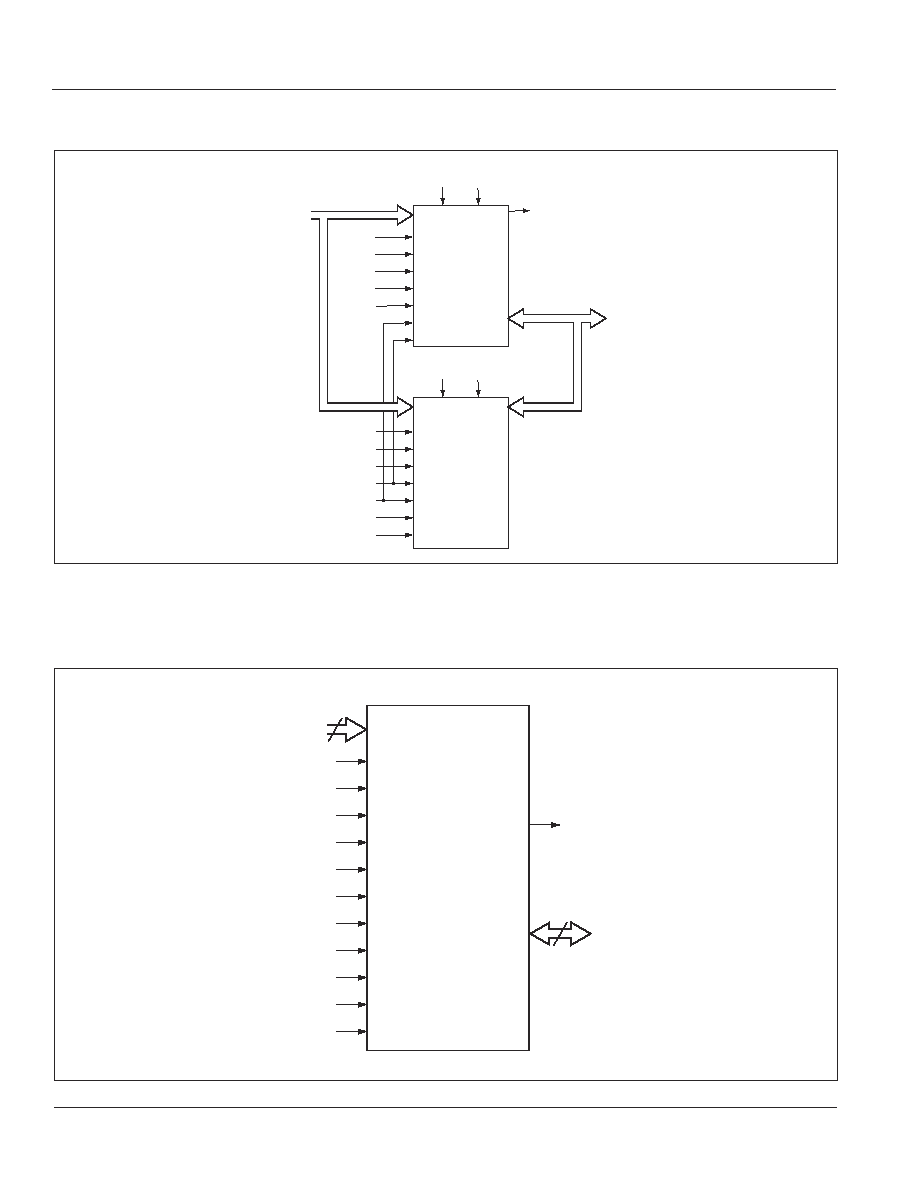

The Flash architecture is composed of two virtual banks

made of a combination of four physical banks, which

allows simultaneous operation on each. Optimized per-

formance can be achieved by first initializing a program or

erase function in one bank, then immediately starting a

read from the other bank. Both operations would then be

operating simultaneously, with zero latency.

4

Integrated Silicon Solution, Inc. -- www.issi.com --

1-800-379-4774

PRELIMINARY INFORMATION

Rev. 00C

07/22/02

IS71V08F64GS08, IS71V16F64GS08

ISSI

Æ

12345678901234

12345678901234

12345678901234

12345678901234

12345678901234

12345678901234

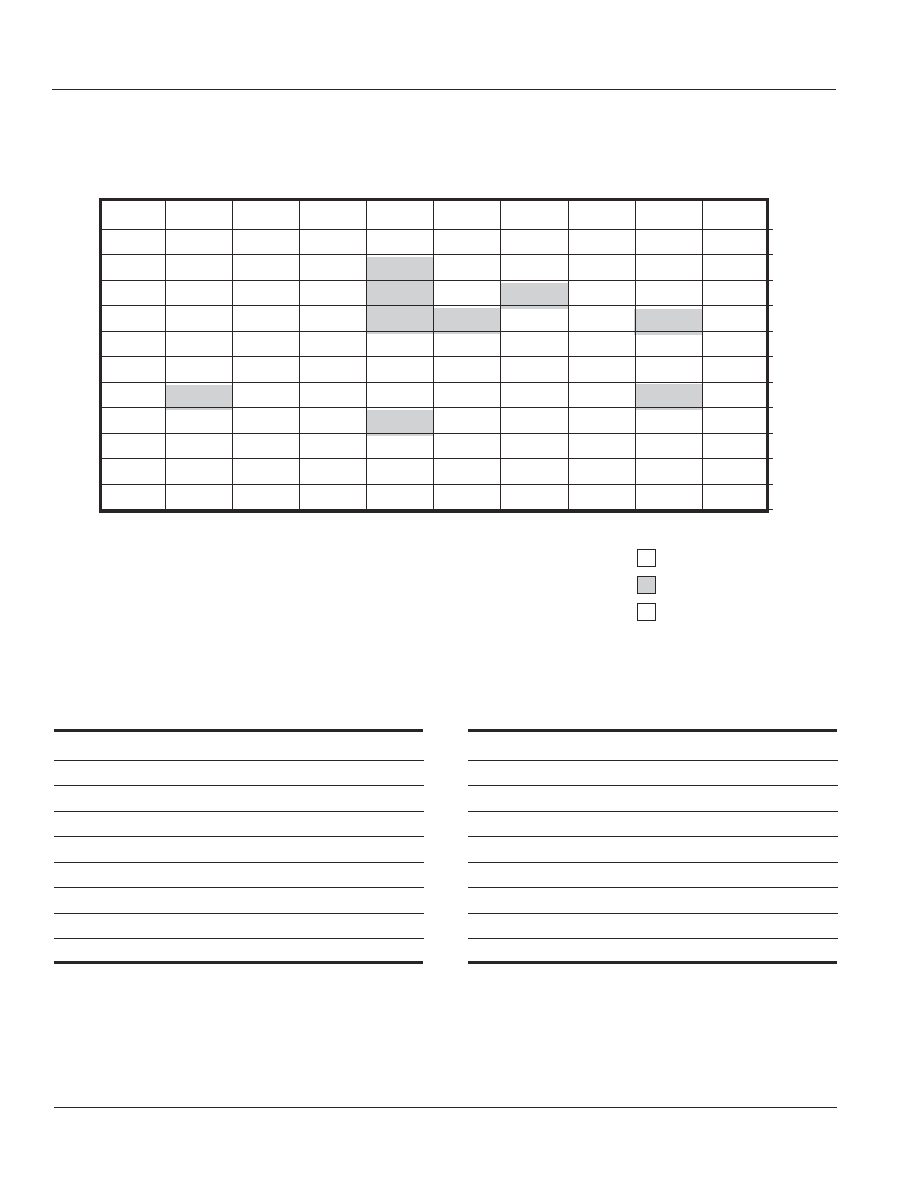

PIN DESCRIPTIONS

A0-A18

Address Inputs, Common

A19-A21, A-1

Address Inputs, Flash

DQ0-DQ15/A-1

Data Inputs/Outputs

RESET

Reset

CE1

s, CE2s

Chip Selects, SRAM

I/Of

I/O Configuration, Flash

CE

f

Chip Enable Input, Flash

OE

Output Enable Input

WE

Write Enable Input

LB

s

Lower-byte Control (DQ0-DQ7), SRAM

UB

s

Upper-byte Control (DQ8-DQ15), SRAM

WP

/ACC

Write Protect/Acceleration Pin, Flash

RY/

BY

Ready/Busy Output

SA

High Order Address Pin, SRAM (x8)

NC

No Connection

Vccf

Power, Flash

Vccs

Power, SRAM

GND

Ground

123456789012345

123456789012345

123456789012345

123456789012345

123456789012345

123456789012345

12345678901234

12345678901234

12345678901234

12345678901234

12345678901234

12345678901234

123456789012345

123456789012345

123456789012345

123456789012345

123456789012345

123456789012345

12345678901234

12345678901234

12345678901234

12345678901234

12345678901234

12345678901234

12345678901234

12345678901234

12345678901234

12345678901234

12345678901234

12345678901234

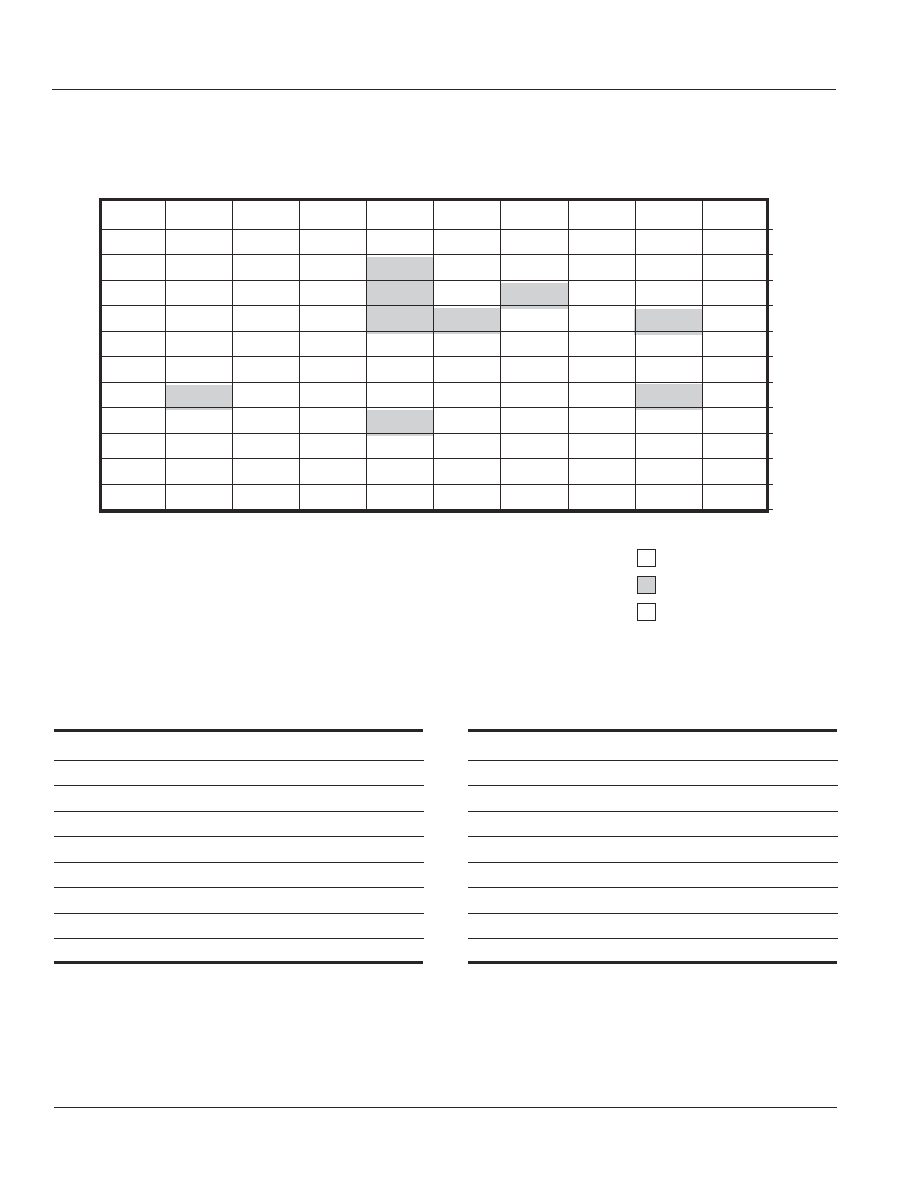

PIN CONFIGURATION (64 Mb Flash and 8 Mb SRAM)

73 BALL FBGA (Top View)

1

2

3

4

5

6

7

8

9

10

A

NC

NC

B

NC

NC

NC

NC

C

NC

A7

LB

WP

/ACC

WE

A8

A11

D

A3

A6

UB

RESET

CE2s

A19

A12

A15

E

A2

A5

A18

RY/

BY

A20

A9

A13

A21

F

NC

A1

A4

A17

A10

A14

NC

NC

G

NC

A0

GND

DQ1

DQ6

SA

A16

NC

H

CE

f

OE

DQ9

DQ3

DQ4

DQ13

DQ15/A-1

I/Of

J

CE1

s

DQ0

DQ10

V

CC

f

V

CC

s

DQ12

DQ7

GND

K

DQ8

DQ2

DQ11

NC

DQ5

DQ14

L

NC

NC

NC

NC

M

NC

NC

1234

1234

1234

1234

Shared

Flash only

SRAM only

Integrated Silicon Solution, Inc. -- www.issi.com --

1-800-379-4774

5

PRELIMINARY INFORMATION

Rev. 00C

07/22/02

IS71V08F64GS08, IS71V16F64GS08

ISSI

Æ

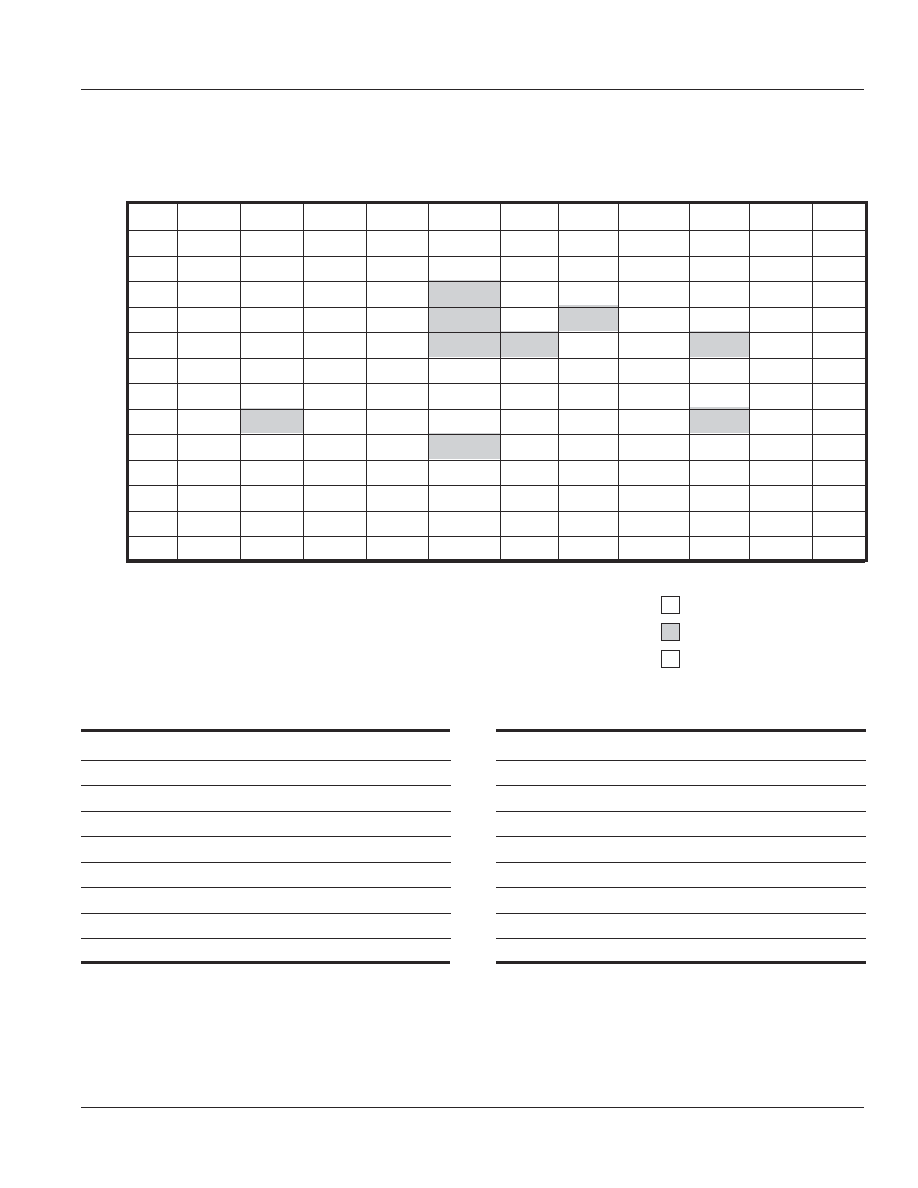

PIN DESCRIPTIONS

A0-A18

Address Inputs, Common

A19-A21, A-1

Address Inputs, Flash

DQ0-DQ15/A-1

Data Inputs/Outputs

RESET

Reset

CE1

s, CE2s

Chip Selects, SRAM

I/Of

I/O Configuration, Flash

CE

f

Chip Enable Input, Flash

OE

Output Enable Input

WE

Write Enable Input

LB

s

Lower-byte Control (DQ0-DQ7), SRAM

UB

s

Upper-byte Control (DQ8-DQ15), SRAM

WP

/ACC

Write Protect/Acceleration Pin, Flash

RY/

BY

Ready/Busy Output, Flash

SA

Address Input Pin, SRAM (x8)

NC

No Connection

Vccf

Power, Flash

Vccs

Power, SRAM

GND

Ground

1234

1234

1234

1234

Shared

Flash only

SRAM only

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

1234567890123

1234567890123

1234567890123

1234567890123

1234567890123

1234567890123

12345678901234

12345678901234

12345678901234

12345678901234

12345678901234

12345678901234

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

12345678901234

12345678901234

12345678901234

12345678901234

12345678901234

12345678901234

123456789012345

123456789012345

123456789012345

123456789012345

123456789012345

123456789012345

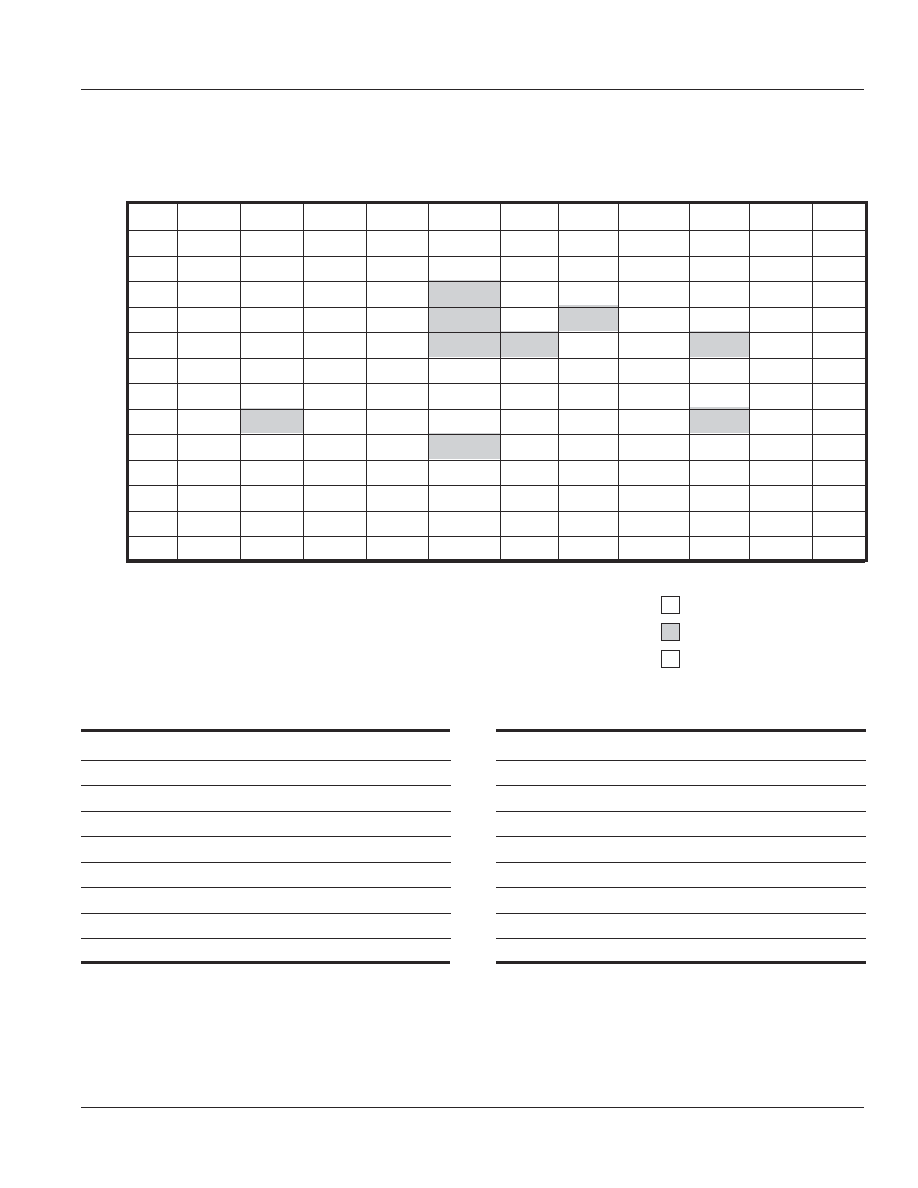

PIN CONFIGURATION (64 Mb Flash and 8 Mb SRAM)

101 BALL FBGA (Top View)

1

2

3

4

5

6

7

8

9

10

11

12

A

NC

NC

NC

NC

NC

NC

B

NC

NC

NC

NC

NC

NC

C

NC

NC

NC

NC

NC

NC

NC

NC

D

NC

A7

LB

s

WP

/ACC

WE

A8

A11

E

A3

A6

UB

s

RESET

CE2s

A19

A12

A15

F

A2

A5

A18

RY/

BY

A20

A9

A13

A21

G

NC

A1

A4

A17

A10

A14

NC

NC

H

NC

A0

GND

DQ1

DQ6

SA

A16

NC

J

CE

f

OE

DQ9

DQ3

DQ4

DQ13

DQ15/A-1

I/Of

K

CE1

s

DQ0

DQ10

V

CC

f

V

CC

s

DQ12

DQ7

GND

L

DQ8

DQ2

DQ11

NC

DQ5

DQ14

M

NC

NC

NC

NC

NC

NC

NC

NC

N

NC

NC

NC

NC

NC

NC

P

NC

NC

NC

NC

NC

NC