Eastman Kodak Company - Microelectronics Technology Division - Rochester, NY 14650-2010

Phone (716) 722-4385 Fax (716) 477-4947

Web:

www.kodak.com/go/ccd

E-mail: ccd@kodak.com

KAI-0372 SERIES

KAI-0372 Series

768(H) x 484(V) Pixel

Interline CCD Image Sensor

Performance Specification

Eastman Kodak Company

Microelectronics Technology Division

Rochester, New York 14650-2010

Revision 2

May 20, 1999

Eastman Kodak Company - Microelectronics Technology Division - Rochester, NY 14650-2010

Phone (716) 722-4385 Fax (716) 477-4947

Web:

www.kodak.com/go/ccd

E-mail: ccd@kodak.com

2

5/20/99

KAI-0372 SERIES

Table of Contents

1.1 Features--------------------------------------------------------------------------------------------4

1.2 Description ----------------------------------------------------------------------------------------5

1.3 Architecture ---------------------------------------------------------------------------------------5

1.4 Image Acquisition--------------------------------------------------------------------------------5

1.5 Charge Transport ---------------------------------------------------------------------------------5

1.6 Output Structure ----------------------------------------------------------------------------------6

1.7 Electronic Shutter --------------------------------------------------------------------------------7

1.8 Color Filter Array --------------------------------------------------------------------------------7

1.9 On-Chip Gate Protection Circuitry -------------------------------------------------------------8

2.1 Packaging Configuration ------------------------------------------------------------------------9

2.2 Pin Description --------------------------------------------------------------------------------- 10

2.3 Absolute Maximum Range-------------------------------------------------------------------- 12

2.4 DC Operating Conditions --------------------------------------------------------------------- 12

2.5 AC Clock Level Conditions------------------------------------------------------------------- 13

2.6 Clock Capacitances ---------------------------------------------------------------------------- 13

2.7 AC Timing Requirements --------------------------------------------------------------------- 14

Frame Timing----------------------------------------------------------------------------------- 15

Line Timing ------------------------------------------------------------------------------------- 16

Pixel Timing ------------------------------------------------------------------------------------ 17

Electronic Shutter Timing --------------------------------------------------------------------- 18

2.8 CCD Clock Waveform Conditions ----------------------------------------------------------- 19

3.1 Image Specifications --------------------------------------------------------------------------- 20

Electro-Optical for KAI-0372M -------------------------------------------------------------- 20

Electro-Optical for KAI-0372CM ------------------------------------------------------------ 21

CCD---------------------------------------------------------------------------------------------- 22

Output Amplifier @ V

DD

= 15V, V

SS

= 0.5V ----------------------------------------------- 22

General ------------------------------------------------------------------------------------------ 23

3.2 Defect Classification --------------------------------------------------------------------------- 24

4.1 Climatic Requirements ------------------------------------------------------------------------ 25

4.2 Quality Assurance and Reliability------------------------------------------------------------ 25

4.3 Ordering Information -------------------------------------------------------------------------- 26

Appendix

Appendix 1 Part Number Availability------------------------------------------------------------- 27

Eastman Kodak Company - Microelectronics Technology Division - Rochester, NY 14650-2010

Phone (716) 722-4385 Fax (716) 477-4947

Web:

www.kodak.com/go/ccd

E-mail: ccd@kodak.com

3

5/20/99

KAI-0372 SERIES

Figures

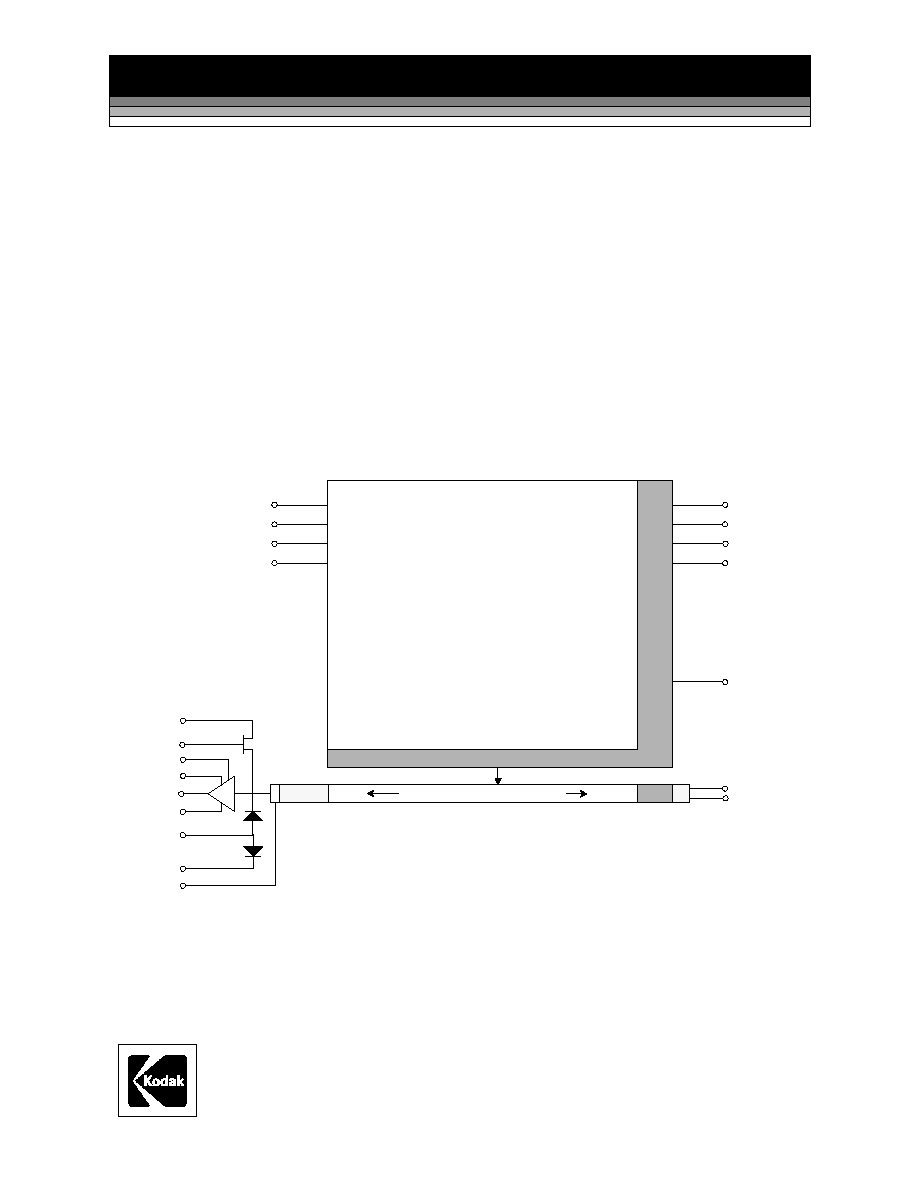

Figure 1

Functional Block Diagram---------------------------------------------------------------4

Figure 2

Output Structure --------------------------------------------------------------------------6

Figure 3

Color Filter Array Pattern ---------------------------------------------------------------7

Figure 4

Internal protection Circuit for

H1 and

H2 ------------------------------------------8

Figure 5

Internal protection Circuit for OG,

R, and VGL-------------------------------------8

Figure 6

Device Drawing---------------------------------------------------------------------------9

Figure 7

Pinout Diagram - Top and Side Views ----------------------------------------------- 11

Figure 8

Frame Timing --------------------------------------------------------------------------- 15

Figure 9

Line Timing ----------------------------------------------------------------------------- 16

Figure 10 Pixel Timing----------------------------------------------------------------------------- 17

Figure 11 Electronic Shutter Timing � Single Register Readout------------------------------ 18

Figure 12 CCD Clock Waveform----------------------------------------------------------------- 19

Figure 13 Nominal KAI-0372M Spectral Response-------------------------------------------- 20

Figure 14 Nominal KAI-0372CM Spectral Response ------------------------------------------ 21

Figure 15 Typical KAI-0372 Series Photoresponse -------------------------------------------- 23

Tables

Table 1 Package Pin Assignments---------------------------------------------------------------- 10

Table 2 Absolute Maximum Ranges ------------------------------------------------------------- 12

Table 3 DC Operating Conditions ---------------------------------------------------------------- 12

Table 4 AC Clock Level Conditions ------------------------------------------------------------- 13

Table 5 Clock Capacitances ----------------------------------------------------------------------- 13

Table 6 AC Timing Requirements---------------------------------------------------------------- 14

Table 7 CCD Clock Waveform Conditions ----------------------------------------------------- 19

Table 8 Electro-Optical Image Specifications KAI-0372M ----------------------------------- 20

Table 9 Electro-Optical Image Specifications KAI-0372CM --------------------------------- 21

Table 10 CCD Image Specifications--------------------------------------------------------------- 22

Table 11 Output Amplifier Image Specifications ------------------------------------------------ 22

Table 12 General Image Specifications ----------------------------------------------------------- 23

Table 13 Defect Classification --------------------------------------------------------------------- 24

Table 14 Climatic Requirements ------------------------------------------------------------------- 25

Table 15 Available Part Numbers � Monochrome, Microlens, Sealed Cover Glass --------- 27

Table 16 Available Part Numbers � Monochrome, Microlens, Taped Cover Glass---------- 27

Table 17 Available Part Numbers � Monochrome, Sealed Cover Glass ---------------------- 27

Table 18 Available Part Numbers � Monochrome, Taped Cover Glass ----------------------- 28

Table 19 Available Part Numbers � Color, Microlens, Sealed Cover Glass ------------------ 28

Eastman Kodak Company - Microelectronics Technology Division - Rochester, NY 14650-2010

Phone (716) 722-4385 Fax (716) 477-4947

Web:

www.kodak.com/go/ccd

E-mail: ccd@kodak.com

4

5/20/99

KAI-0372 SERIES

1.1

Features

�

Front Illuminated Interline Architecture

�

768 (H) x 484 (V) Photosensitive Pixels

�

11.6

�

m(H) x 13.6

�

m(V) Pixel Size

�

8.9 mm(H) x 6.6 mm(V) Photosensitive Area

�

Progressive Scan (Noninterlaced)

�

Electronic Shutter

�

Integral RGB Color Filter Array (optional

)

�

Advanced 2 Phase Buried Channel CCD

Processing

�

On-Chip Dark Reference Pixels

�

Low Dark Current

�

High Output Sensitivity

�

Antiblooming Protection

�

Negligible Lag

�

2/3" Format Compatible

�

Low Smear (0.01% with microlens

)

KAI-0372

Usable Active Image Area

768(H) x 484(V)

11.6

�

m X 13.6

�

m pixels

768 Active Pixels/Line

5 Dark Rows

12 Dark Columns

V1B

V2A

H1

H2

R

Vrd

Vdd

Vss

OG

WELL

Vout

8

768

12

2

= 791 Pixels/Line

V1A

V2B

LTSH

V1B

V2A

V1A

V2B

SUBS

VLG

Figure 1 Functional Block Diagram

Eastman Kodak Company - Microelectronics Technology Division - Rochester, NY 14650-2010

Phone (716) 722-4385 Fax (716) 477-4947

Web:

www.kodak.com/go/ccd

E-mail: ccd@kodak.com

5

5/20/99

KAI-0372 SERIES

1.2

Description

The KAI-0372 series is a high-performance

silicon charge-coupled device (CCD) designed for

video image sensing and electronic still

photography. The device is built using an

advanced true two-phase, double-polysilicon,

NMOS CCD technology. The

p+npn-

photodetector elements eliminate image lag and

reduce image smear while providing antiblooming

protection and electronic-exposure control. The

total chip size is 9.9 (H) mm x 7.7 (V) mm. The

KAI-0372 comes in monochrome and color

versions, both with microlens for sensitivity

improvement

.

Device

Color

Microlens

KAI-0372M

No

Yes

KAI-0372CM

Yes

Yes

1.3

Architecture

The KAI-0372 consists of 371,712 photodiodes,

768 vertical (parallel) CCD shift registers

(VCCDs), one horizontal (serial) CCD shift

register and one output amplifier. The advanced,

progressive-scan architecture of the device allows

the entire image area to be read out in a single

scan. The pixels are arranged in a 768 (H) x 484

(V) array in which an additional 12 columns and 5

rows of light shielded pixels are added as dark

reference.

1.4

Image Acquisition

An electronic representation of an image is

formed when incident photons falling on the

sensor plane create electron-hole pairs within the

individual silicon photodiodes.

These photoelectrons are collected locally by the

formation of potential wells at each photosite.

Below photodiode saturation, the number of

photoelectrons collected at each pixel is linearly

dependent on light level and exposure time and

non-linearly dependent on wavelength. When the

photodiode's charge capacity is reached, excess

electrons are discharged into the substrate to

prevent blooming.

1.5

Charge Transport

The accumulated or integrated charge from each

photodiode is transported to the output by a three

step process. The charge is first transported from

the photodiodes to the VCCDs by applying a large

positive voltage to the phase-one vertical clock

(

V2). This reads out every row, or line, of

photodiodes into the VCCDs.

The charge is then transported from the VCCDs to

the HCCDs line by line. Finally, the HCCDs

transport these rows of charge packets to the

output structures pixel by pixel. On each falling

edge of the horizontal clock,

H2, these charge

packets are dumped over the output gate (OG,

Figure 2) onto the floating diffusion (FDA Figure

2).

Both the horizontal and vertical shift registers use

traditional two-phase complementary clocking for

charge transport. Transfer to the horizontal CDD

begins when

V2 is brought low (and

V1 high)

causing a line of charge to transfer from

V2 to

V1 and subsequently into the horizontal register.

The sequence completes when

V1 is brought low

before the horizontal CCD reads the first line of

charge.