Document Outline

- Table of Contents

- ispLSI 1016EA Data Sheet

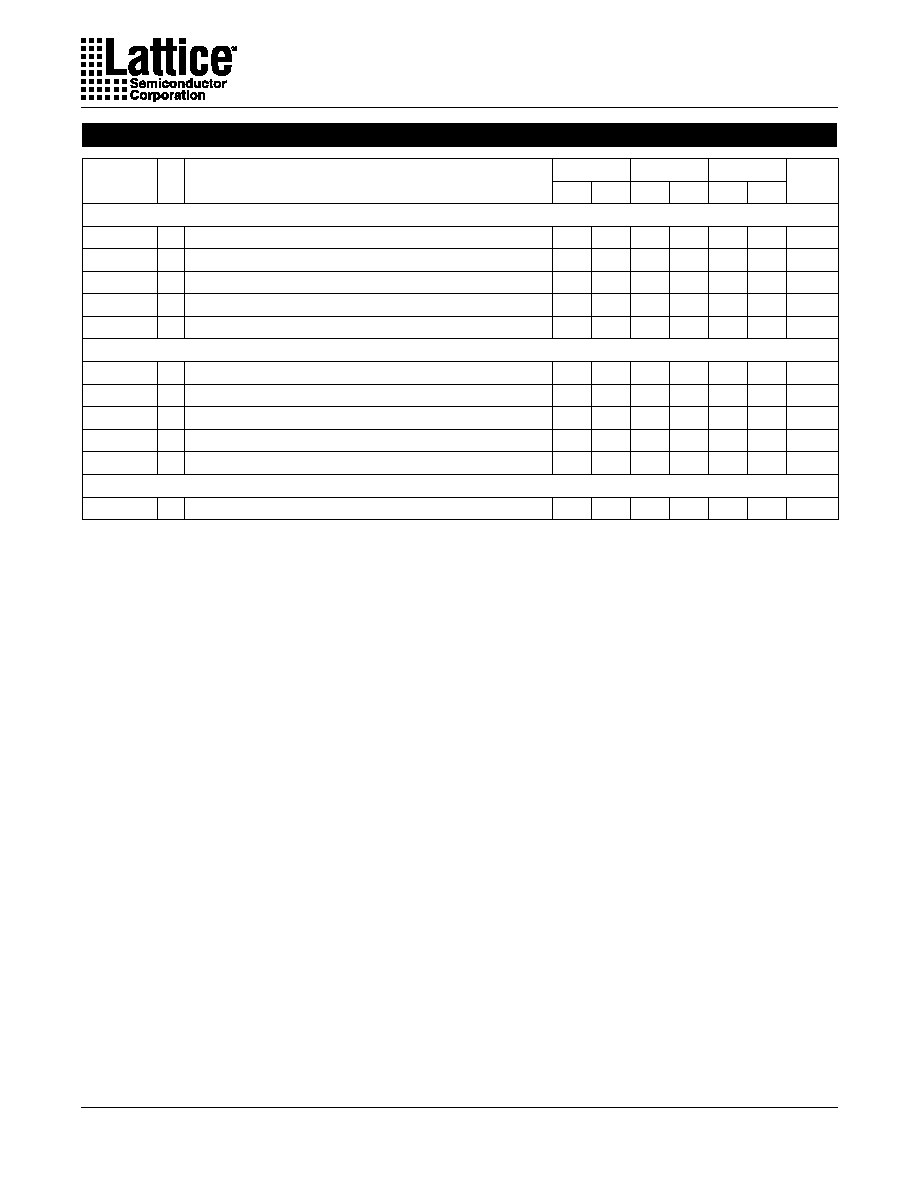

- DC Electrical Characteristics

- AC Characteristics

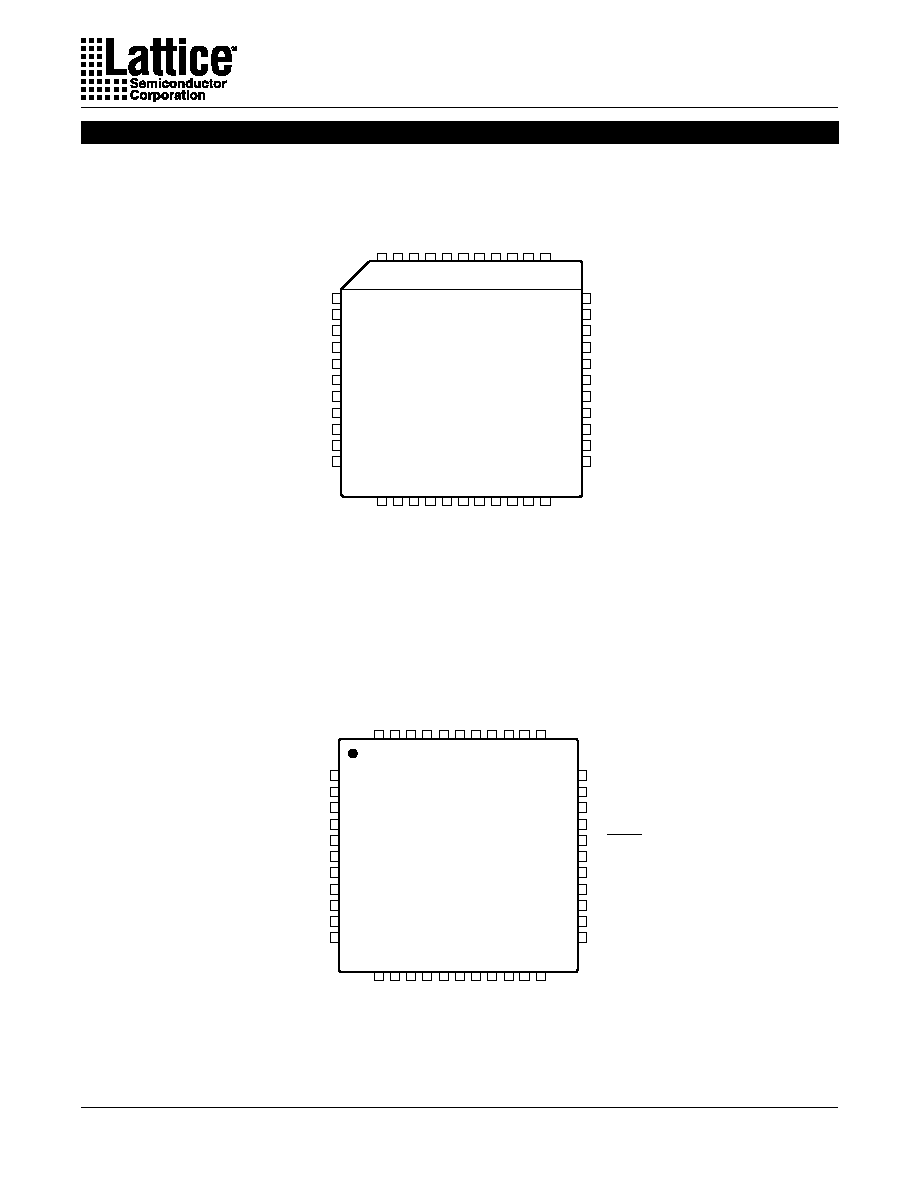

- Pin Configuration: 44 PLCC

- Pin Configuration: 44 TQFP

- Ordering Information

ispLSI

Æ

1016EA

In-System Programmable High Density PLD

1016ea_01

1

Features

∑ HIGH-DENSITY PROGRAMMABLE LOGIC

-- 2000 PLD Gates

-- 32 I/O Pins, One Dedicated Input

-- 96 Registers

-- High-Speed Global Interconnect

-- Wide Input Gating for Fast Counters, State

Machines, Address Decoders, etc.

-- Small Logic Block Size for Random Logic

-- Functionally Compatible with ispLSI 1016E

∑ NEW FEATURES

-- 100% IEEE 1149.1 Boundary Scan Testable

-- ispJTAGTM In-System Programmable via IEEE 1149.1

(JTAG) Test Access Port

-- User-Selectable 3.3V or 5V I/O Supports Mixed-

Voltage Systems (V

CCIO

Pin)

-- Open-Drain Output Option

∑ HIGH-PERFORMANCE E

2

CMOS

Æ

TECHNOLOGY

--

f

max = 200 MHz Maximum Operating Frequency

--

t

pd = 4.5 ns Propagation Delay

-- TTL Compatible Inputs and Outputs

-- Electrically Erasable and Reprogrammable

-- Non-Volatile

-- 100% Tested at Time of Manufacture

-- Unused Product Term Shutdown Saves Power

∑ IN-SYSTEM PROGRAMMABLE

-- Increased Manufacturing Yields, Reduced Time-to-

Market and Improved Product Quality

-- Reprogram Soldered Device for Faster Prototyping

∑ OFFERS THE EASE OF USE AND FAST SYSTEM

SPEED OF PLDs WITH THE DENSITY AND FLEXIBILITY

OF FIELD PROGRAMMABLE GATE ARRAYS

-- Complete Programmable Device Can Combine Glue

Logic and Structured Designs

-- Enhanced Pin Locking Capability

-- Three Dedicated Clock Input Pins

-- Synchronous and Asynchronous Clocks

-- Programmable Output Slew Rate Control to

Minimize Switching Noise

-- Flexible Pin Placement

-- Optimized Global Routing Pool Provides Global

Interconnectivity

∑ ispDesignEXPERTTM ≠ LOGIC COMPILER AND COM-

PLETE ISP DEVICE DESIGN SYSTEMS FROM HDL

SYNTHESIS THROUGH IN-SYSTEM PROGRAMMING

-- Superior Quality of Results

-- Tightly Integrated with Leading CAE Vendor Tools

-- Productivity Enhancing Timing Analyzer, Explore

Tools, Timing Simulator and ispANALYZERTM

-- PC and UNIX Platforms

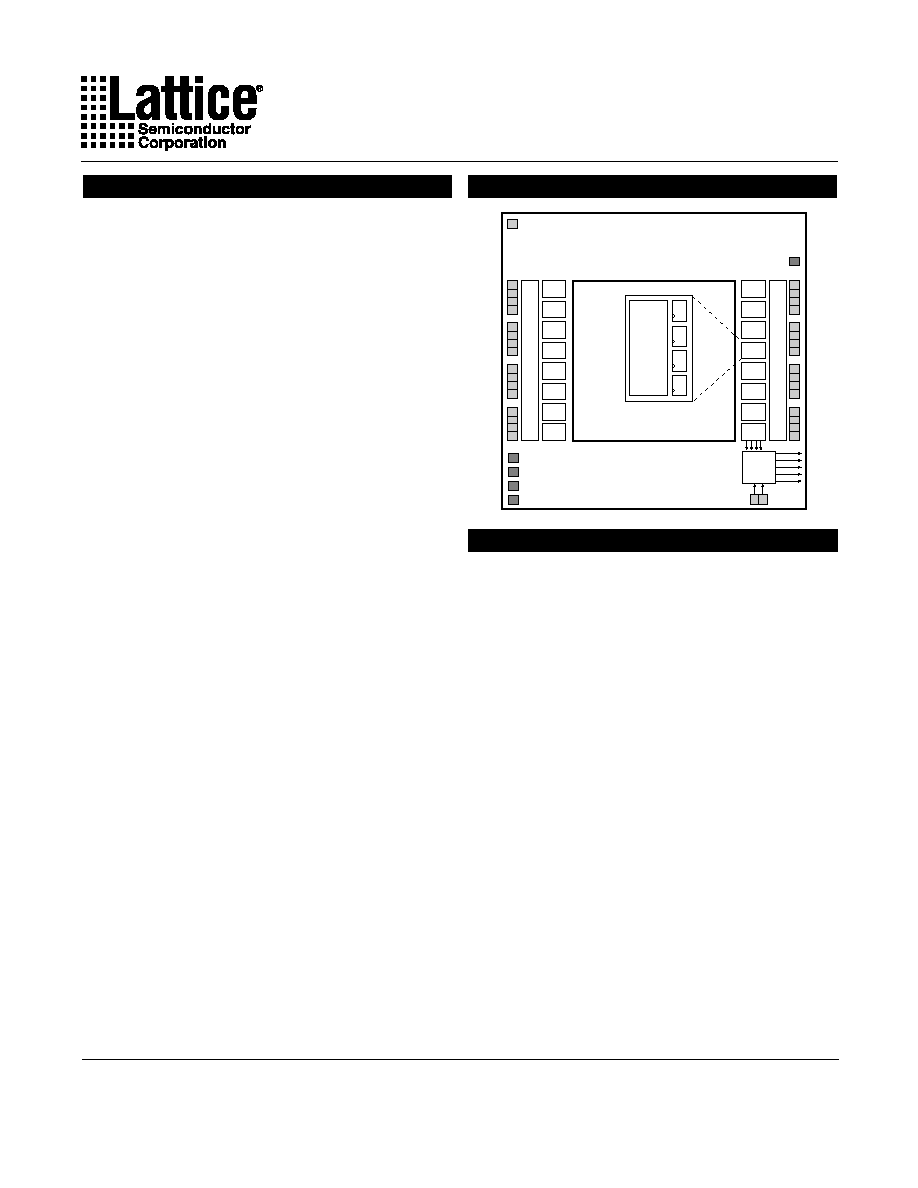

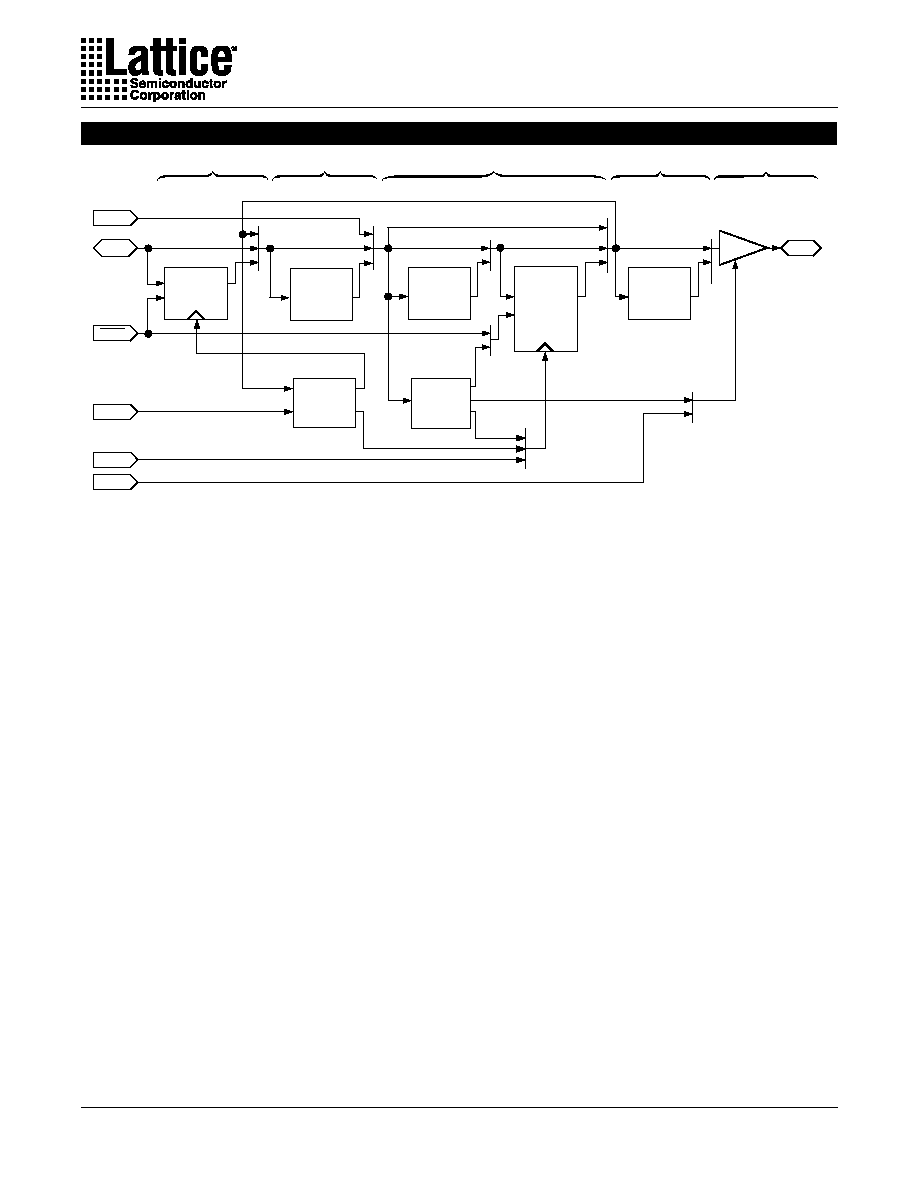

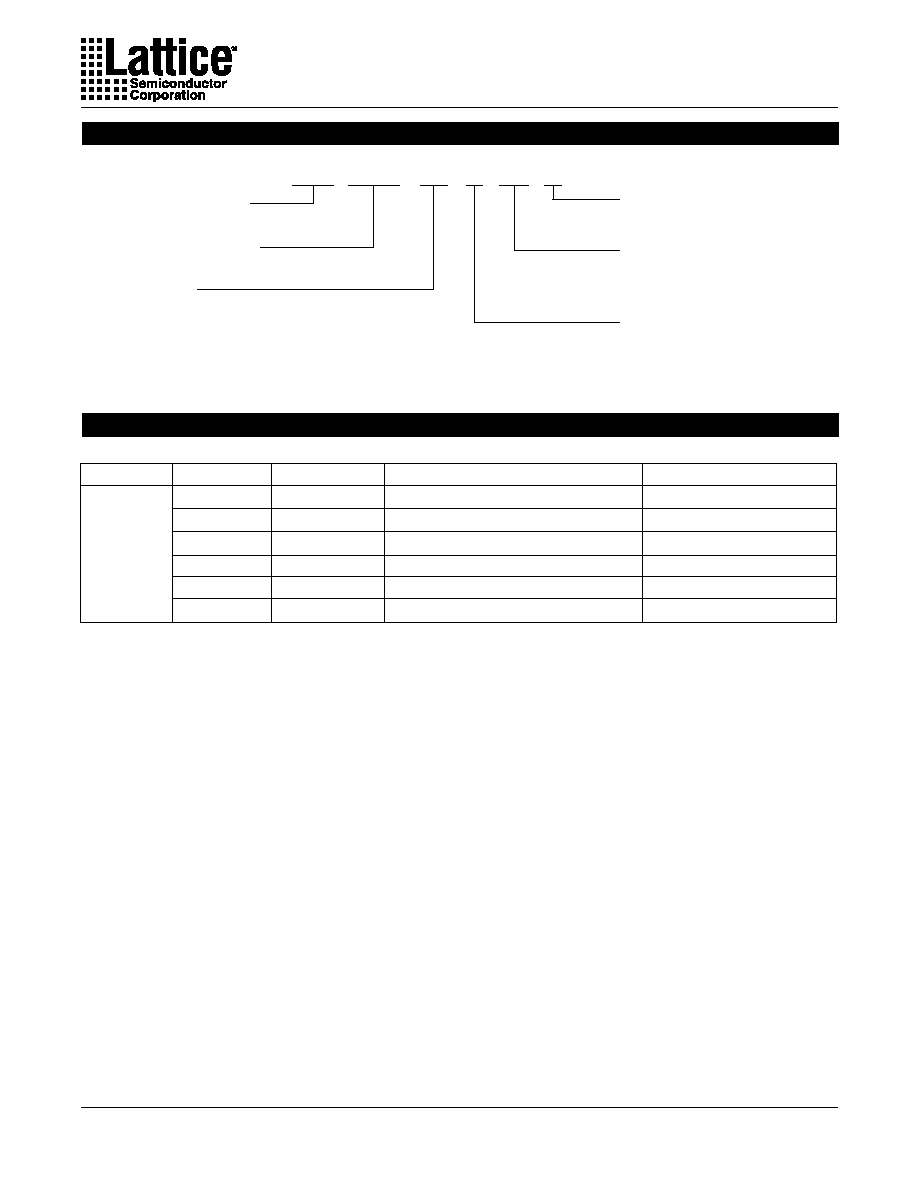

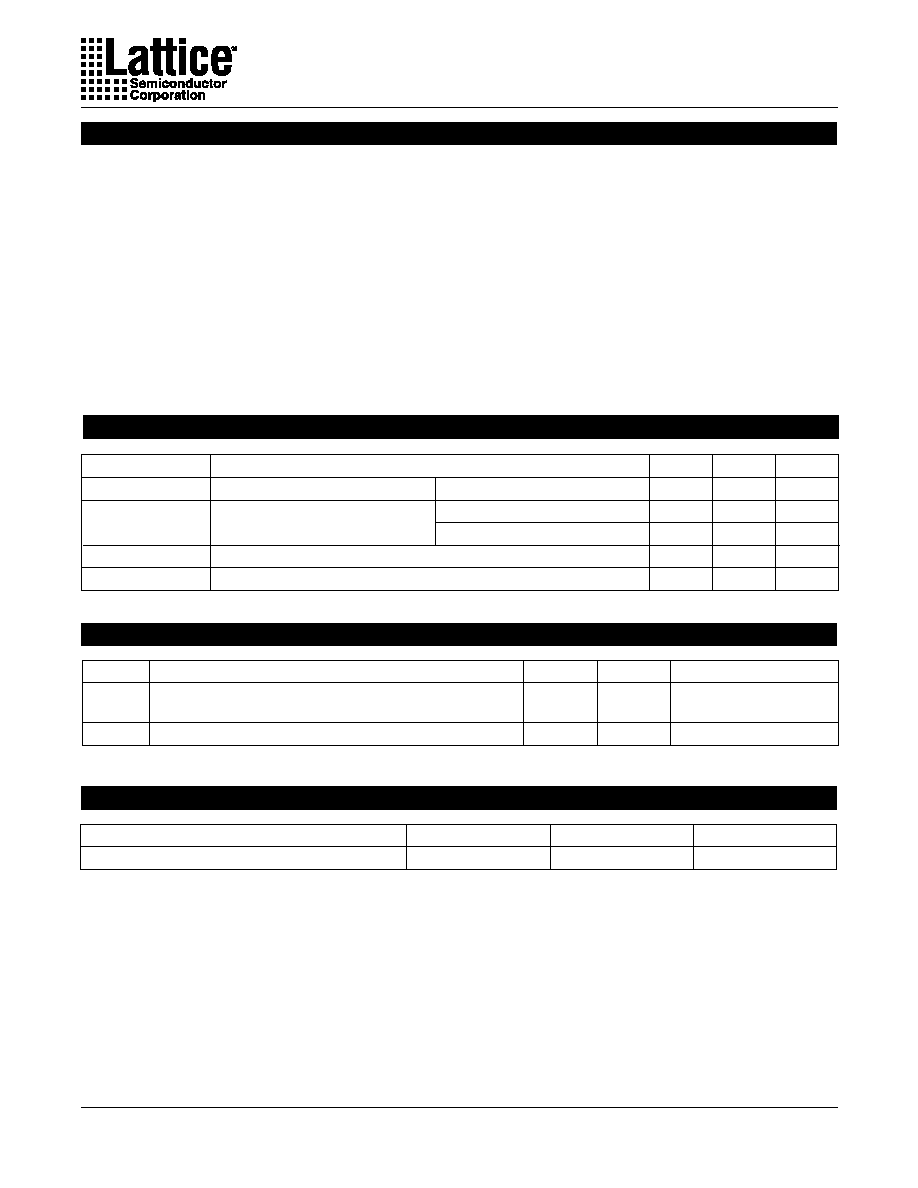

Functional Block Diagram

CLK

A0

A1

A2

A3

A4

A5

A6

A7

B

7

B

6

B

5

B

4

B

3

B

2

B

1

B

0

Output Routing Pool

Output Routing Pool

Global Routing Pool (GRP)

Logic

Array

D Q

D Q

D Q

D Q

GLB

0139C/1016EA

Description

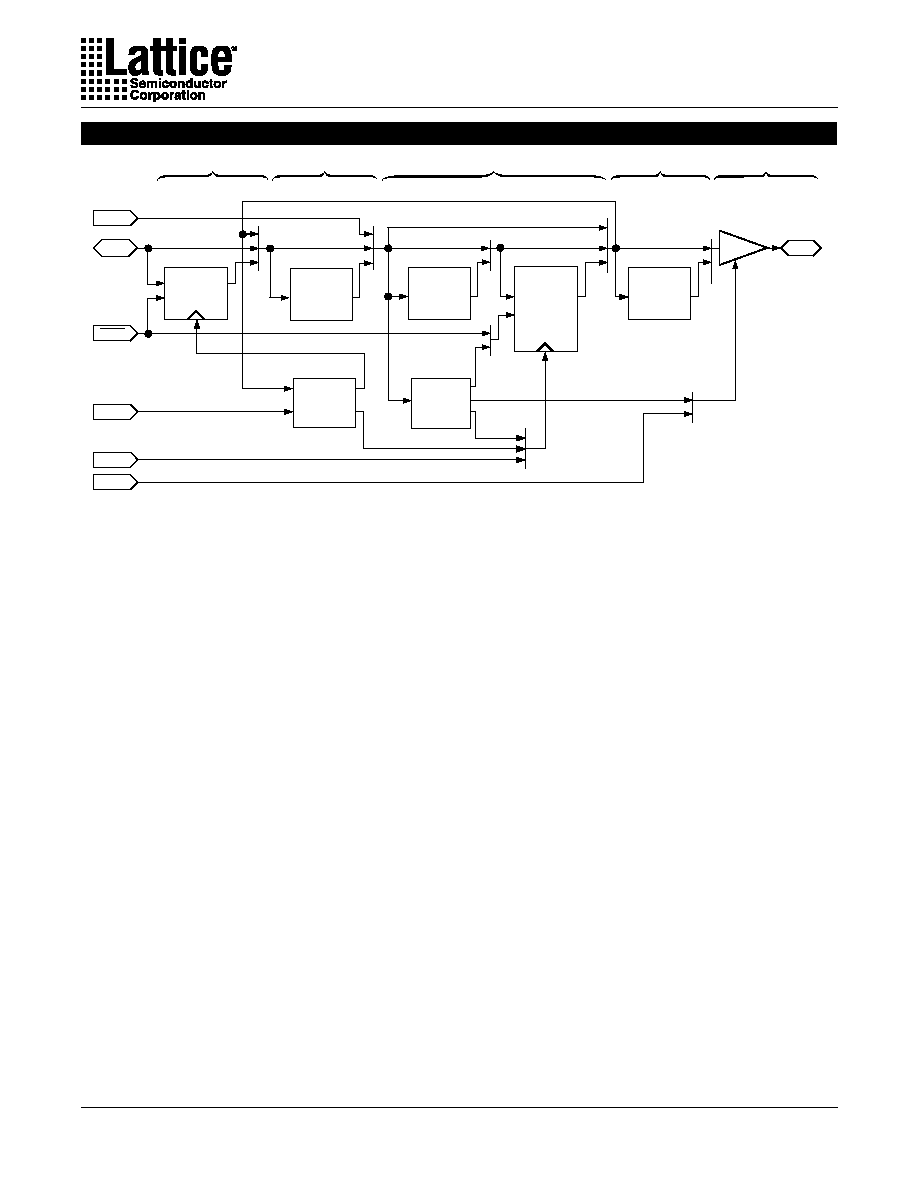

The ispLSI 1016EA is a High Density Programmable

Logic Device containing 96 Registers, 32 Universal I/O

pins, one Dedicated Input pin, two Dedicated Clock Input

pins, one Global OE input pin and a Global Routing Pool

(GRP). The GRP provides complete interconnectivity

between all of these elements. The ispLSI 1016EA fea-

tures 5V in-system programmability (ISPTM) and in-system

diagnostic capabilities via an IEEE 1149.1 Test Access

Port. The ispLSI 1016EA offers non-volatile

reprogrammability of the logic, as well as the intercon-

nect to provide truly reconfigurable systems. A functional

superset of the ispLSI 1016 architecture, the ispLSI

1016EA device adds user-selectable 3.3V or 5V I/O and

open-drain output options.

The basic unit of logic on the ispLSI 1016EA device is the

Generic Logic Block (GLB). The GLBs are labeled A0,

A1...B7 (Figure 1). There are a total of 16 GLBs in the

ispLSI 1016EA device. Each GLB has 18 inputs, a

programmable AND/OR/Exclusive OR array, and four

outputs which can be configured to be either combinato-

rial or registered. Inputs to the GLB come from the GRP

and a dedicated input. All of the GLB outputs are brought

back into the GRP so that they can be connected to the

inputs of any other GLB on the device.

Copyright © 2000 Lattice Semiconductor Corp. All brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject

to change without notice.

LATTICE SEMICONDUCTOR CORP., 5555 Northeast Moore Ct., Hillsboro, Oregon 97124, U.S.A.

Tel. (503) 268-8000; 1-800-LATTICE; FAX (503) 268-8556; http://www.latticesemi.com

June 2000

2

Specifications

ispLSI 1016EA

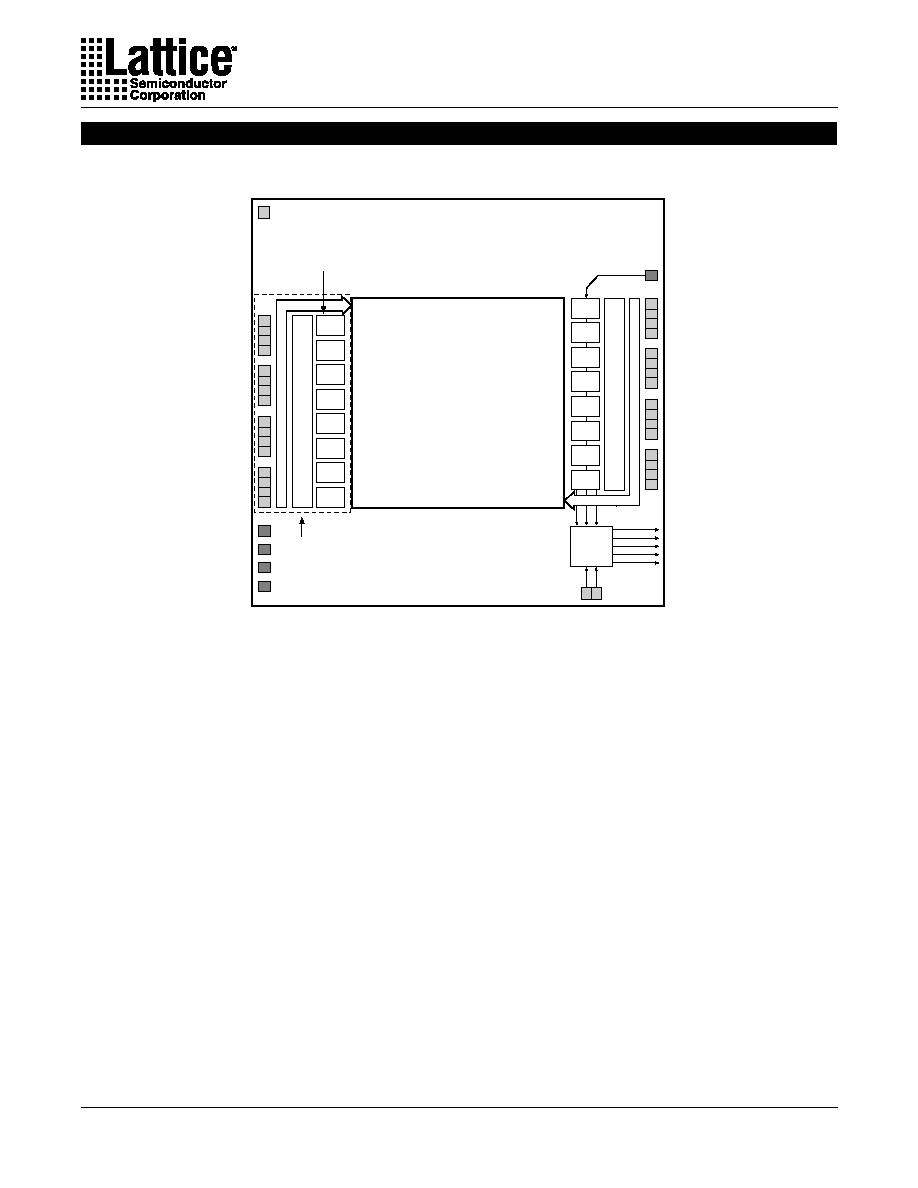

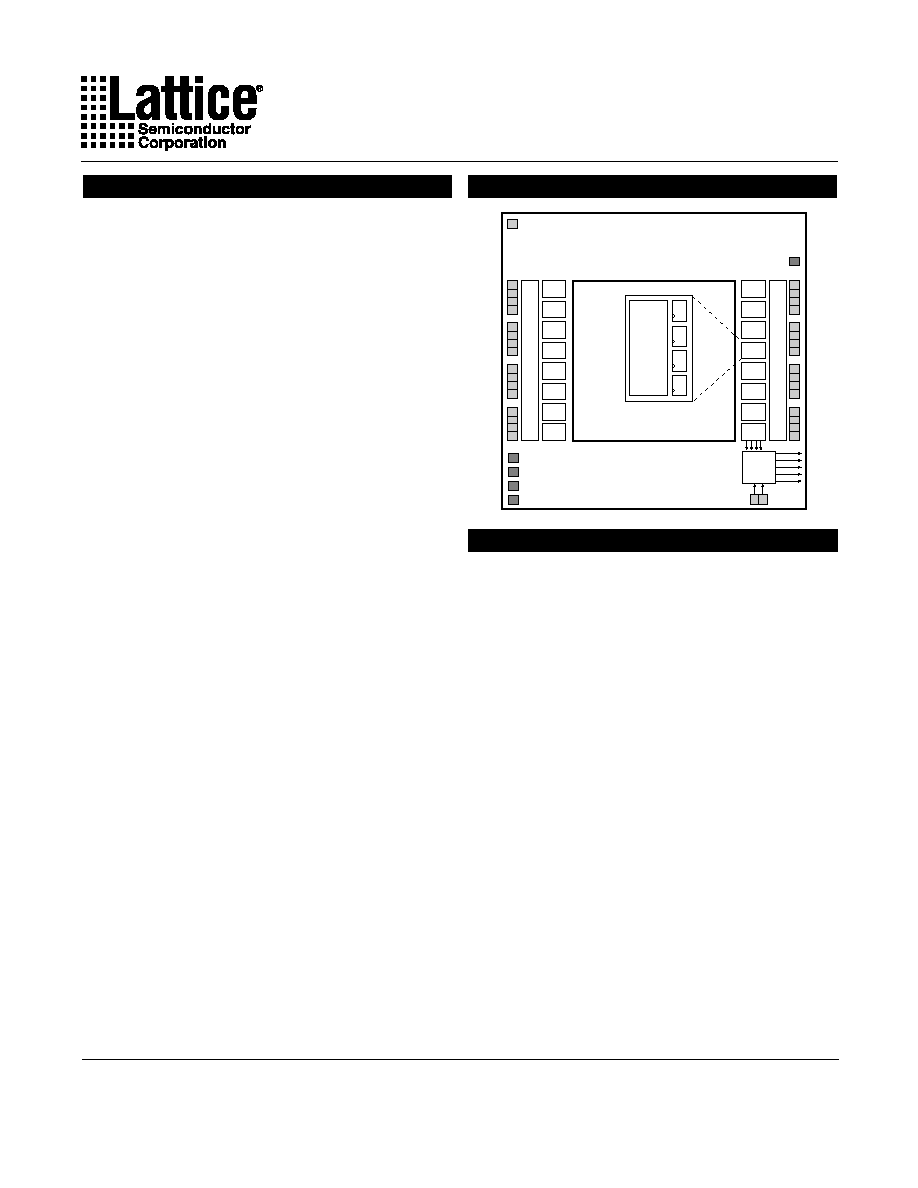

Functional Block Diagram

Figure 1. ispLSI 1016EA Functional Block Diagram

The device also has 32 I/O cells, each of which is directly

connected to an I/O pin. Each I/O cell can be individually

programmed to be a combinatorial input, registered

input, latched input, output or bi-directional

I/O pin with 3-state control. The signal levels are TTL

compatible voltages and the output drivers can source

2 mA or sink 8 mA. Each output can be programmed

independently for fast or slow output slew rate to mini-

mize overall output switching noise. By conneting the

VCCIO pin to a common 5V or 3.3V power supply, I/O

output levels can be matched to 5V or 3.3V-compatible

voltages.

Eight GLBs, 16 I/O cells, a dedicated input (if available)

and one ORP are connected together to make a

Megablock (see Figure 1). The outputs of the eight GLBs

are connected to a set of 16 universal I/O cells by the

ORP. Each ispLSI 1016EA device contains two

Megablocks.

The GRP has, as its inputs, the outputs from all of the

GLBs and all of the inputs from the bi-directional I/O cells.

All of these signals are made available to the inputs of the

GLBs. Delays through the GRP have been equalized to

minimize timing skew.

Clocks in the ispLSI 1016EA device are selected using

the Clock Distribution Network. Two dedicated clock pins

(Y0 and Y1) are brought into the distribution network, and

five clock outputs (CLK 0, CLK 1, CLK 2, IOCLK 0 and

IOCLK 1) are provided to route clocks to the GLBs and

I/O cells. The Clock Distribution Network can also be

driven from a special clock GLB (B0 on the ispLSI

1016EA device). The logic of this GLB allows the user to

create an internal clock from a combination of internal

signals within the device.

Programmable Open-Drain Outputs

In addition to the standard output configuration, the

outputs of the ispLSI 1016EA are individually program-

mable, either as a standard totem-pole output or an

open-drain output. The totem-pole output drives the

specified Voh and Vol levels, whereas the open-drain

output drives only the specified Vol. The Voh level on the

open-drain output depends on the external loading and

pull-up. This output configuration is controlled by a pro-

grammable fuse. The default configuration when the

device is in bulk erased state is totem-pole configuration.

The open-drain/totem-pole option is selectable through

the ispDesignEXPERT software tools.

I/O 0

I/O 1

I/O 2

I/O 3

GOE 0

I/O 6

I/O 7

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

I/O 31

I/O 30

I/O 29

I/O 28

I/O 27

I/O 26

I/O 25

I/O 24

I/O 23

I/O 22

I/O 21

I/O 20

I/O 19

I/O 18

I/O 17

I/O 16

TDI

TDO

TMS

TCK

I/O 4

I/O 5

VCCIO

Global

Routing

Pool

(GRP)

CLK 0

CLK 1

CLK 2

IOCLK 0

IOCLK 1

Clock

Distribution

Network

A0

A1

A2

A3

A4

A5

A6

A7

B7

B6

B5

B4

B3

B2

B1

B0

Output Routing Pool (ORP)

Generic

Logic Blocks

(GLBs)

Megablock

Output Routing Pool (ORP)

Input Bus

lnput Bus

*Note: Y1 and

RESET

are multiplexed on the same pin

Y0

Y1/

RESET

*

0139/1016EA

3

Specifications

ispLSI 1016EA

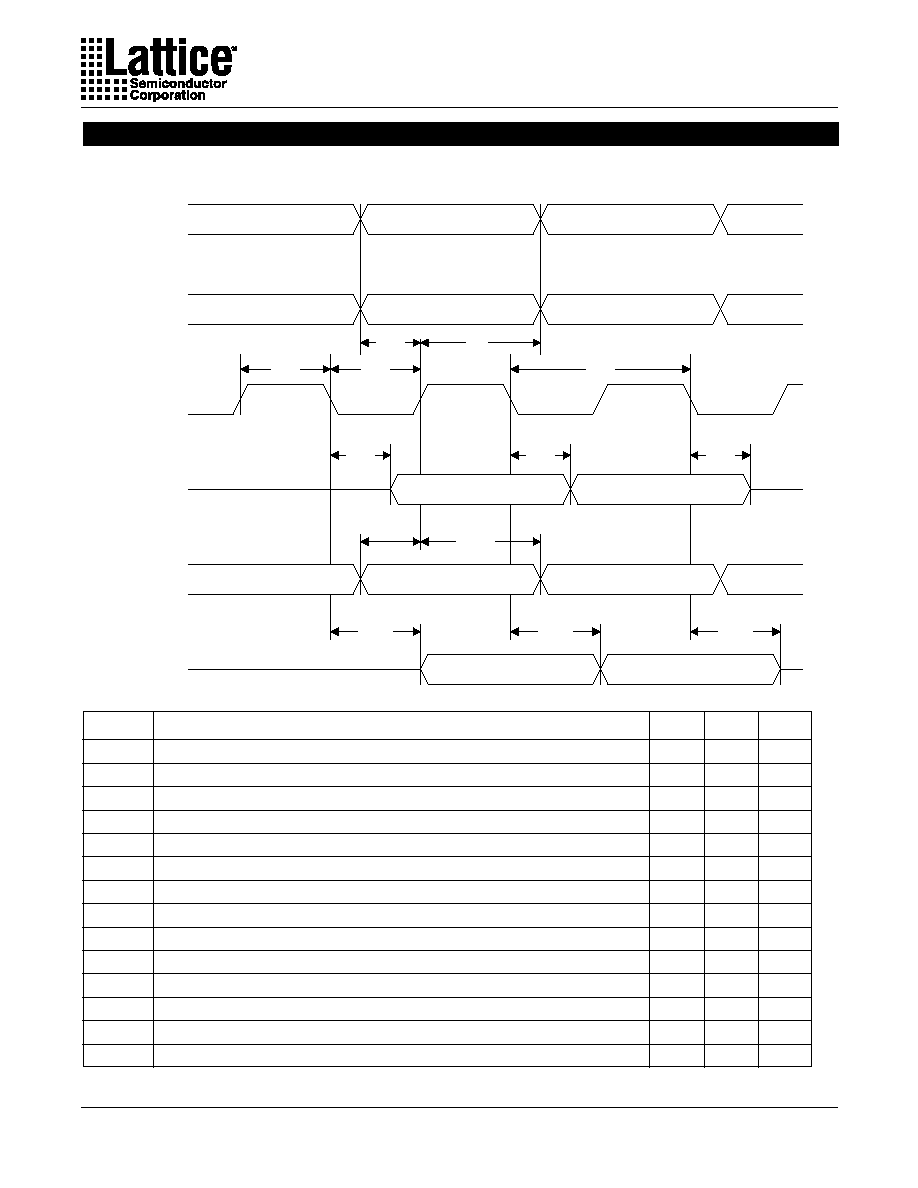

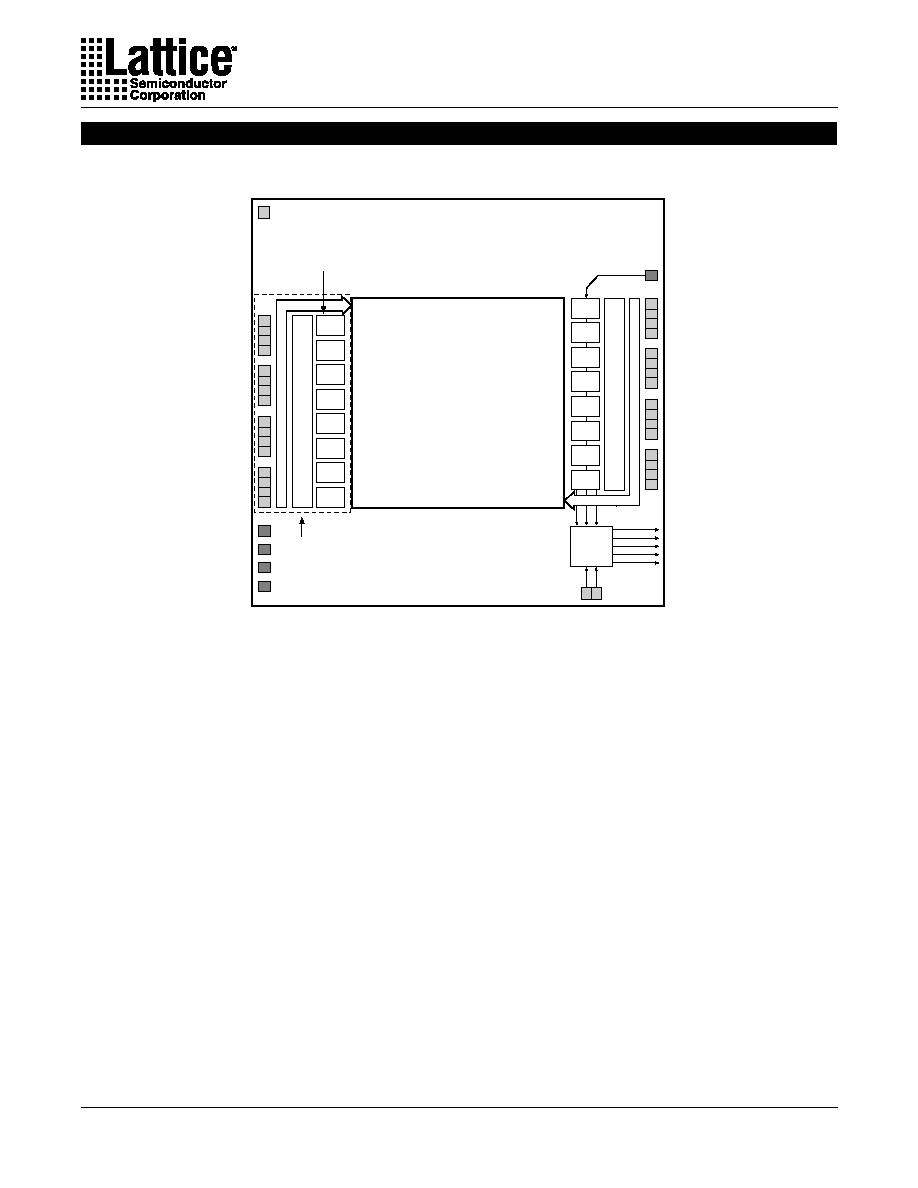

Symbol

Parameter

Min

Max

Units

t

btcp

TCK [BSCAN test] clock pulse width

100

≠

ns

t

btch

TCK [BSCAN test] pulse width high

50

≠

ns

tbtcl

TCK [BSCAN test] pulse width low

50

≠

ns

tbtsu

TCK [BSCAN test] setup time

20

≠

ns

tbth

TCK [BSCAN test] hold time

25

≠

ns

trf

TCK [BSCAN test] rise and fall time

50

≠

mV/ns

tbtco

TAP controller falling edge of clock to valid output

≠

25

ns

tbtoz

TAP controller falling edge of clock to data output disable

≠

25

ns

tbtvo

TAP controller falling edge of clock to data output enable

≠

25

ns

tbtcpsu

BSCAN test Capture register setup time

40

≠

ns

tbtcph

BSCAN test Capture register hold time

25

≠

ns

tbtuco

BSCAN test Update reg, falling edge of clock to valid output

≠

50

ns

tbtuoz

BSCAN test Update reg, falling edge of clock to output disable

≠

50

ns

tbtuov

BSCAN test Update reg, falling edge of clock to output enable

≠

50

ns

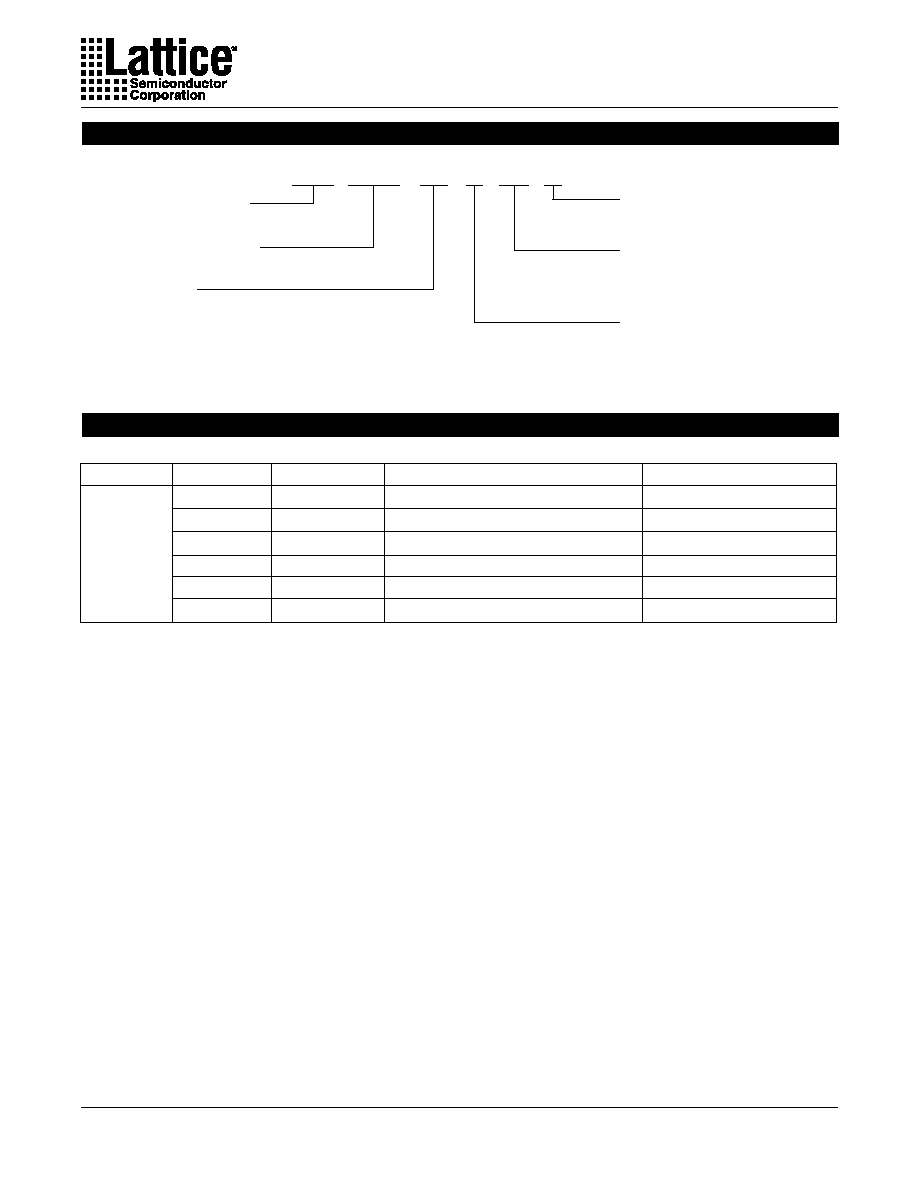

Figure 2. Boundary Scan Waveforms and Timing Specifications

TMS

TDI

TCK

TDO

Data to be

captured

Data to be

driven out

Valid Data

Valid Data

Valid Data

Valid Data

Data Captured

btsu

T

bth

T

btcl

T

btch

T

btcp

T

btvo

T

btco

T

btoz

T

btcpsu

T

btcph

T

btuov

T

btuco

T

btuoz

T

Boundary Scan

4

Specifications

ispLSI 1016EA

Absolute Maximum Ratings

1

Supply Voltage V

CC

................................ -0.5 to +7.0V

Input Voltage Applied ........................ -2.5 to V

CC

+1.0V

Off-State Output Voltage Applied ..... -2.5 to V

CC

+1.0V

Storage Temperature ................................ -65 to 150

∞

C

Case Temp. with Power Applied .............. -55 to 125

∞

C

Max. Junction Temp. (T

J

) with Power Applied ... 150

∞

C

1. Stresses above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional

operation of the device at these or at any other conditions above those indicated in the operational sections of this specification

is not implied (while programming, follow the programming specifications).

DC Recommended Operating Conditions

T

A

= 0

∞

C to + 70

∞

C

SYMBOL

Table 2-0005/1016EA

V

CC

V

CCIO

V

IH

V

IL

PARAMETER

Supply Voltage

Supply Voltage: Output Drivers

Input High Voltage

Input Low Voltage

MIN.

MAX.

UNITS

4.75

4.75

3.0

2.0

0

5.25

5.25

3.6

V

cc

+1

0.8

V

V

V

V

V

Commercial

5V

3.3V

Capacitance (T

A

=25

o

C, f=1.0 MHz)

Erase/Reprogram Specifications

C

SYMBOL

Table 2-0006/1016EA

C

PARAMETER

Y0 Clock Capacitance

10

UNITS

TYPICAL

TEST CONDITIONS

1

2

8

Dedicated Input, I/O, Y1, Y2, Y3, Clock Capacitance

(Commercial)

pf

pf

V = 5.0V, V = 2.0V

V = 5.0V, V = 2.0V

CC

CC

PIN

PIN

Table 2-0008/1016EA

PARAMETER

MINIMUM

MAXIMUM

UNITS

Erase/Reprogram Cycles

10000

--

Cycles

5

Specifications

ispLSI 1016EA

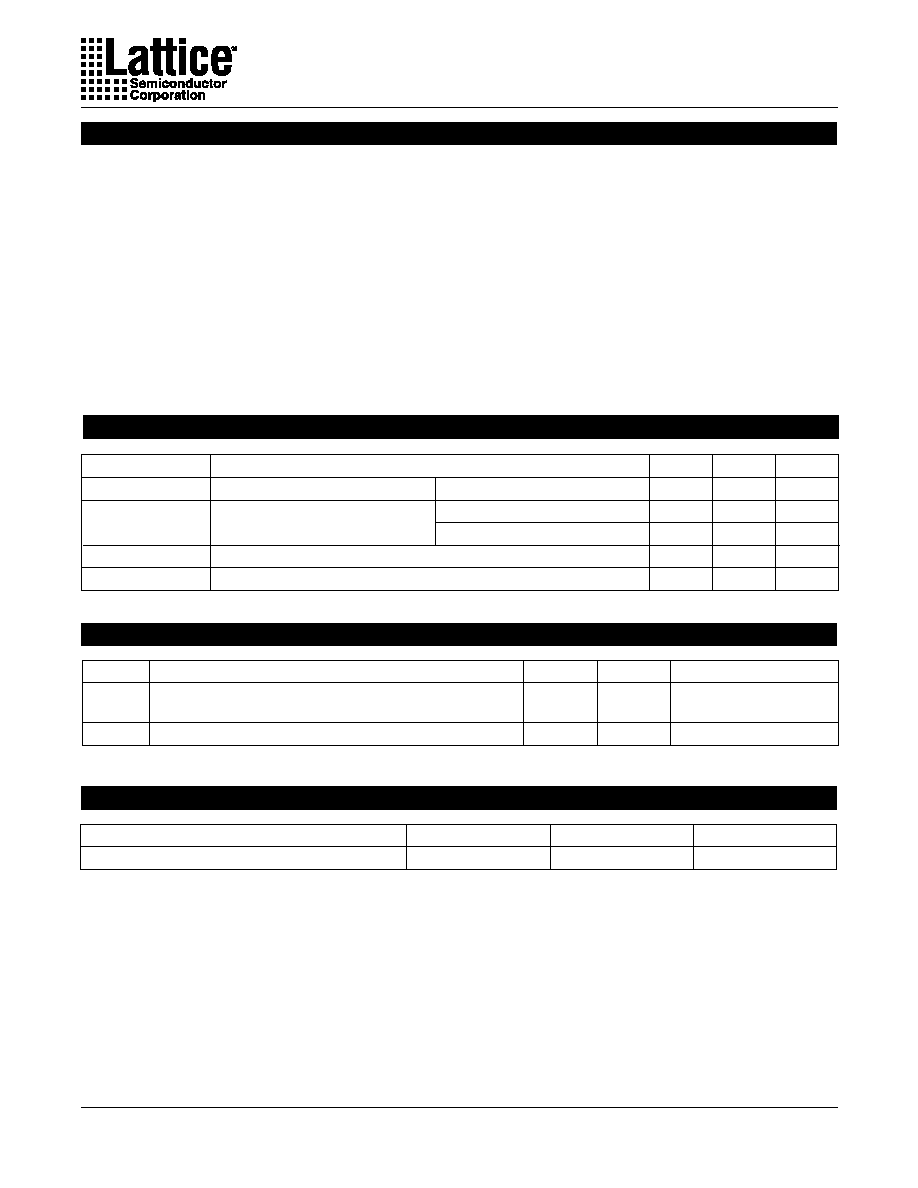

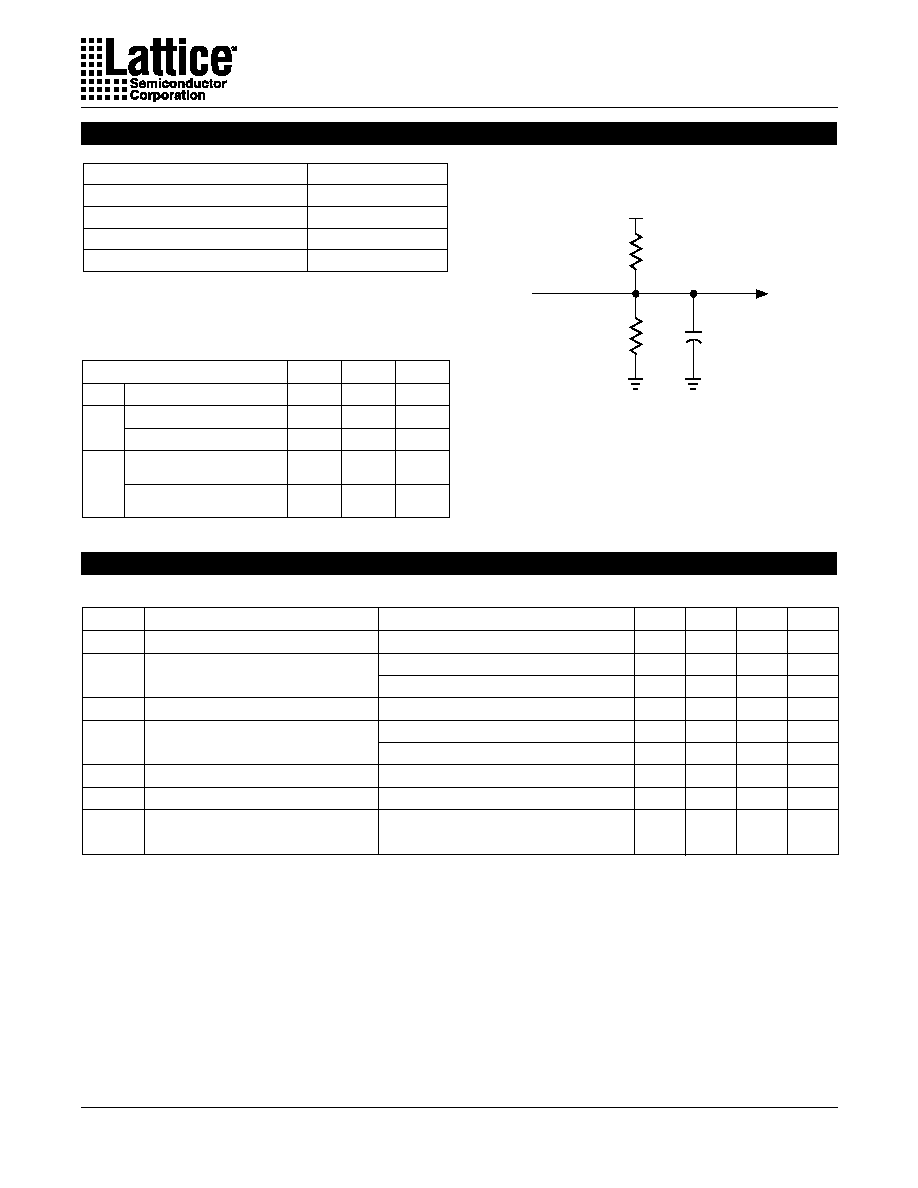

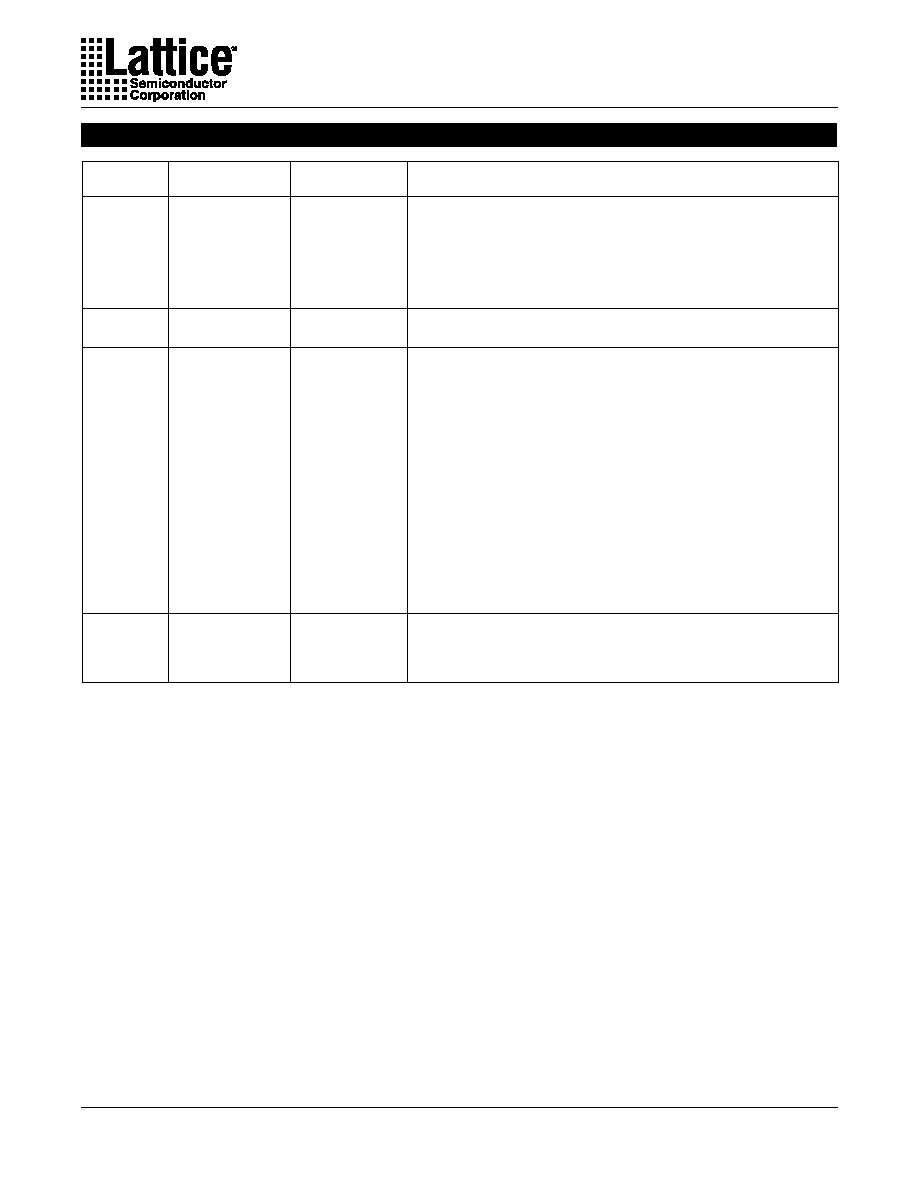

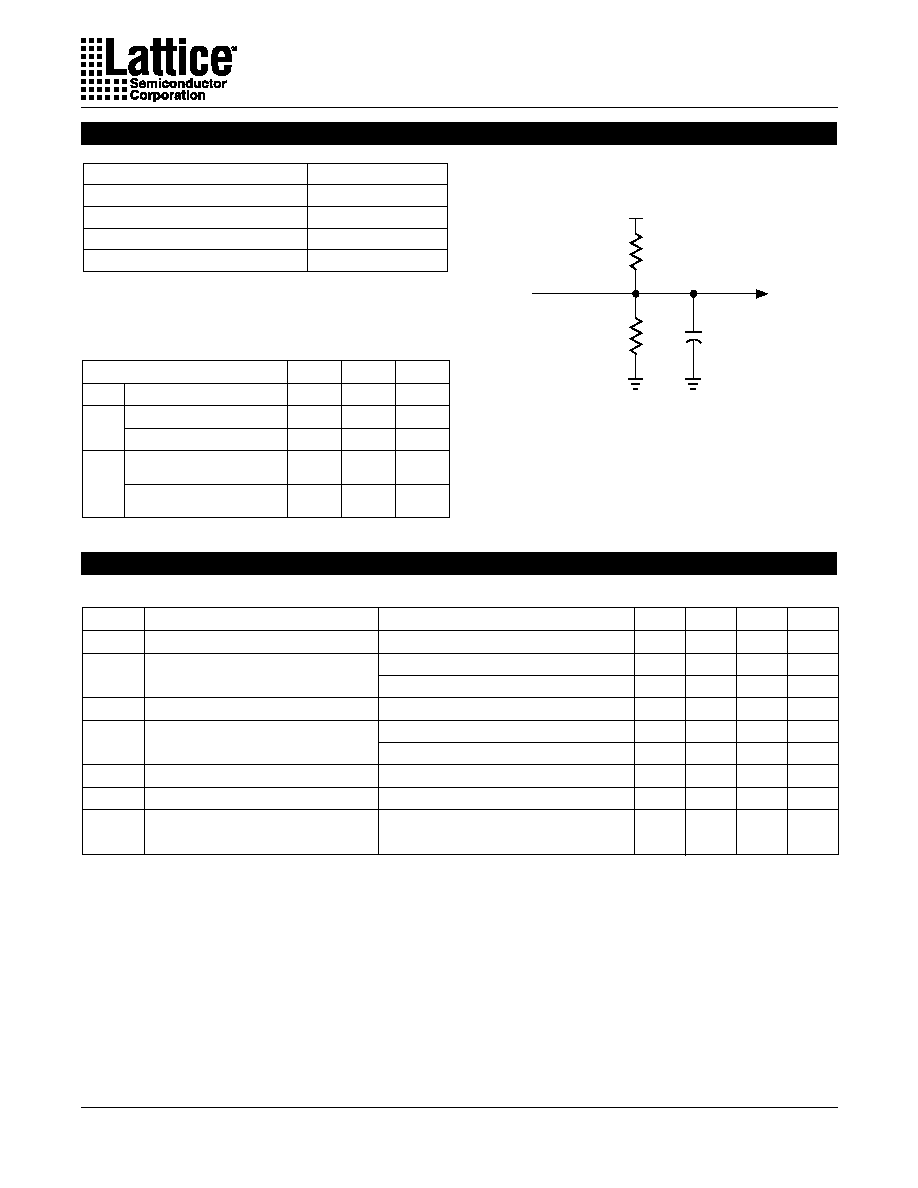

Switching Test Conditions

Figure 3. Test Load

DC Electrical Characteristics

Over Recommended Operating Conditions

Input Pulse Levels

Table 2-0003/1016EA

Input Rise and Fall Time 10% to 90%

Input Timing Reference Levels

Output Timing Reference Levels

Output Load

GND to 3.0V

1.5V

1.5ns

1.5V

See Figure 3

3-state levels are measured 0.5V from

steady-state active level.

Output Load Conditions (see Figure 3)

TEST CONDITION

R1

R2

CL

A

470

390

35pF

B

390

35pF

470

390

35pF

Active High

Active Low

C

470

390

5pF

390

5pF

Active Low to Z

at V +0.5V

OL

Active High to Z

at V -0.5V

OH

Table 2-0004/1016E

+ 5V

R1

R2

CL

*

Device

Output

Test

Point

*

CL includes Test Fixture and Probe Capacitance.

0213a

V

OL

SYMBOL

1. One output at a time for a maximum duration of one second. V

OUT

= 0.5V was selected to avoid test

problems by tester ground degradation. Characterized but not 100% tested.

2. Measured using four 16-bit counters.

3. Typical values are at V

CC

= 5V and T

A

= 25

∞

C.

4. Unused inputs held at 0.0V.

5. Maximum I

CC

varies widely with specific device configuration and operating frequency. Refer to the

Power Consumption section of this data sheet and the Thermal Management section of the Lattice Semiconductor

Data Book CD-ROM to estimate maximum I

CC

.

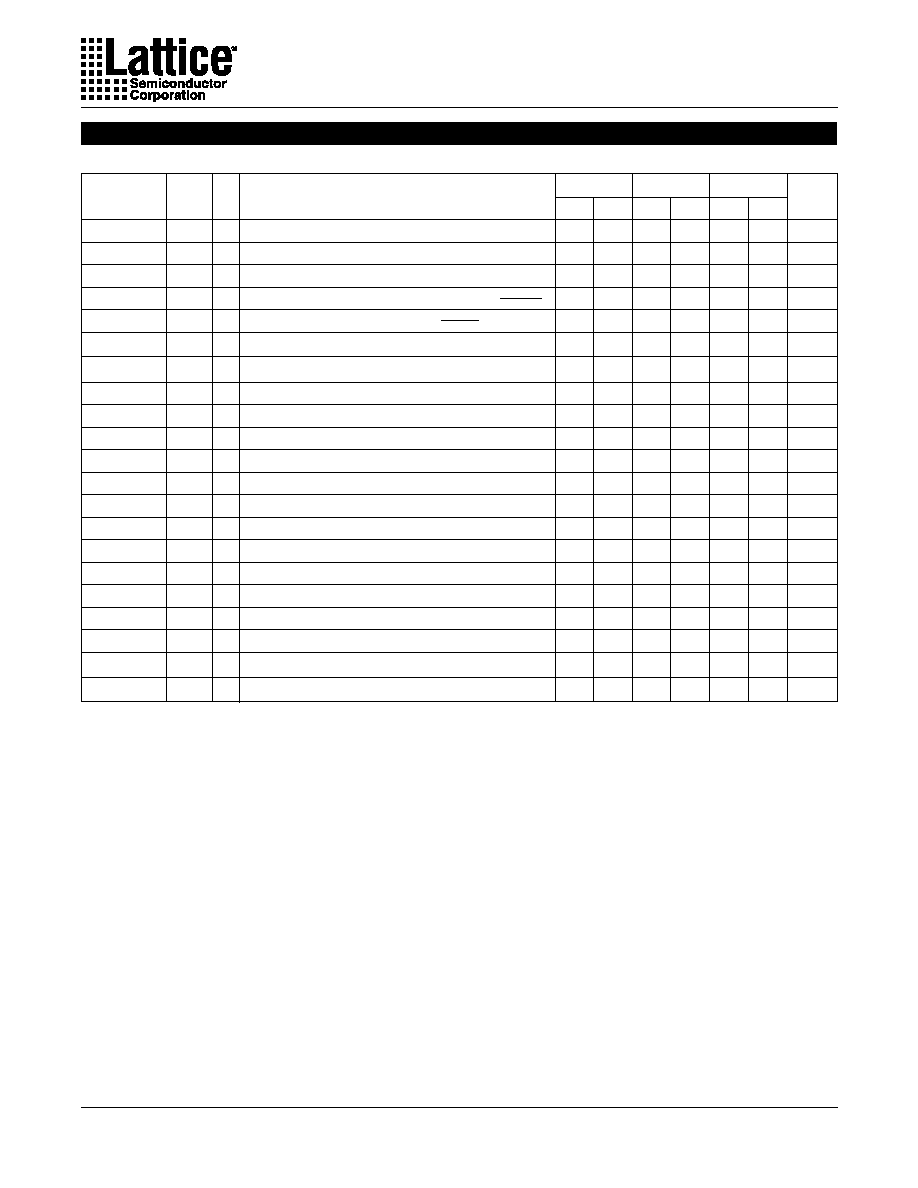

Table 2-0007/1016EA

V

OH

I

IH

I

IL

PARAMETER

I

IL-PU

I

OS

1

I

CC

2, 4, 5

Output Low Voltage

Output High Voltage

Input or I/O Low Leakage Current

Operating Power Supply Current

I

OL

= 8 mA

0V

V

IN

V

IL

(Max.)

V

IL

= 0.0V, V

IH

= 3.0V

CONDITION

MIN.

TYP.

3

MAX. UNITS

--

2.4

--

--

--

--

--

--

--

--

0.4

--

10

-10

10

V

V

2.4

--

--

V

µ

A

Input or I/O High Leakage Current

V

CCIO

V

IN

5.25V

(V

CCIO

- 0.2)V

V

IN

V

CCIO

µ

A

µ

A

I/O Active Pull-Up Current

0V

V

IN

V

IL

--

--

-200

µ

A

Output Short Circuit Current

V

CCIO

= 5.0V or 3.3V, V

OUT

= 0.5V

--

--

-240

mA

--

91

mA

--

f

TOGGLE

= 1 MHz

I

OH

= -2 mA, V

CCIO

= 3.0V

I

OH

= -4 mA, V

CCIO

= 4.75V

6

Specifications

ispLSI 1016EA

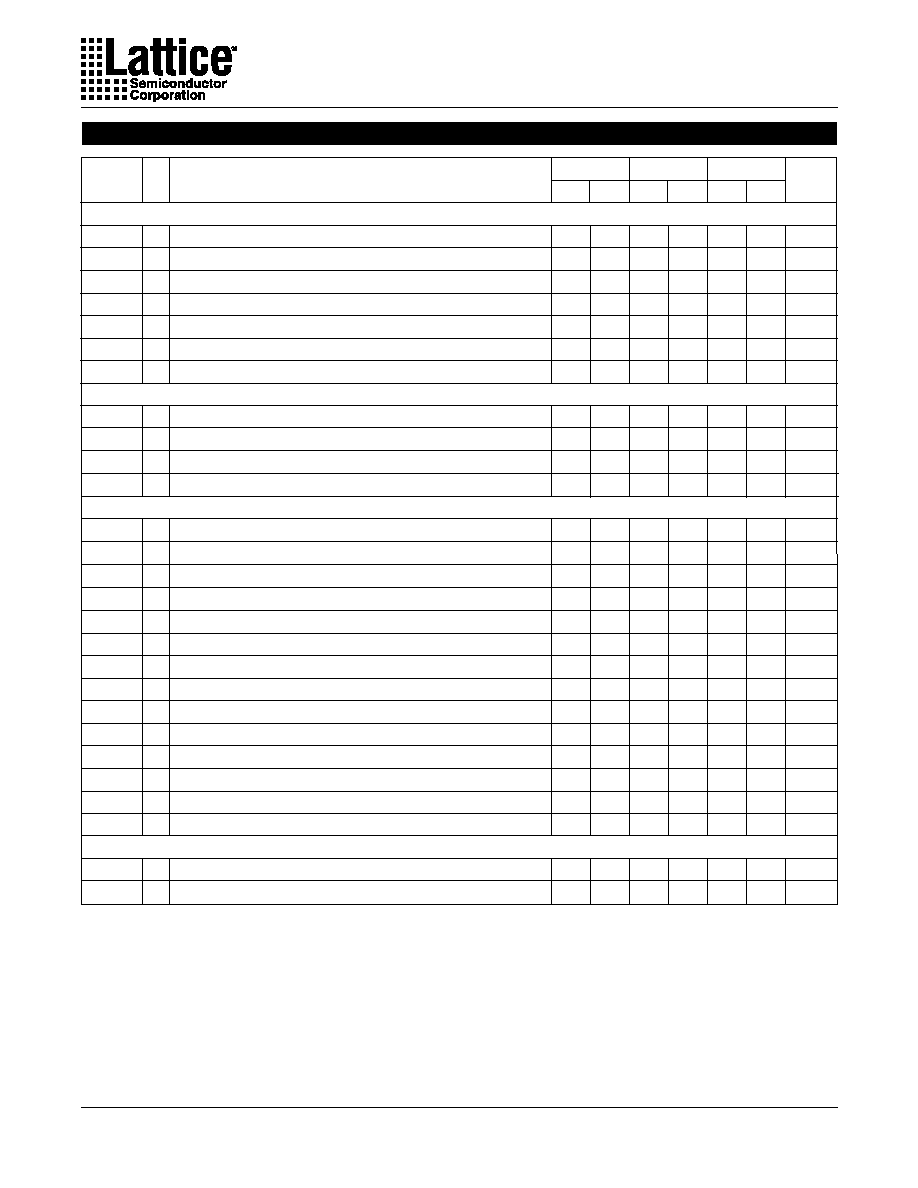

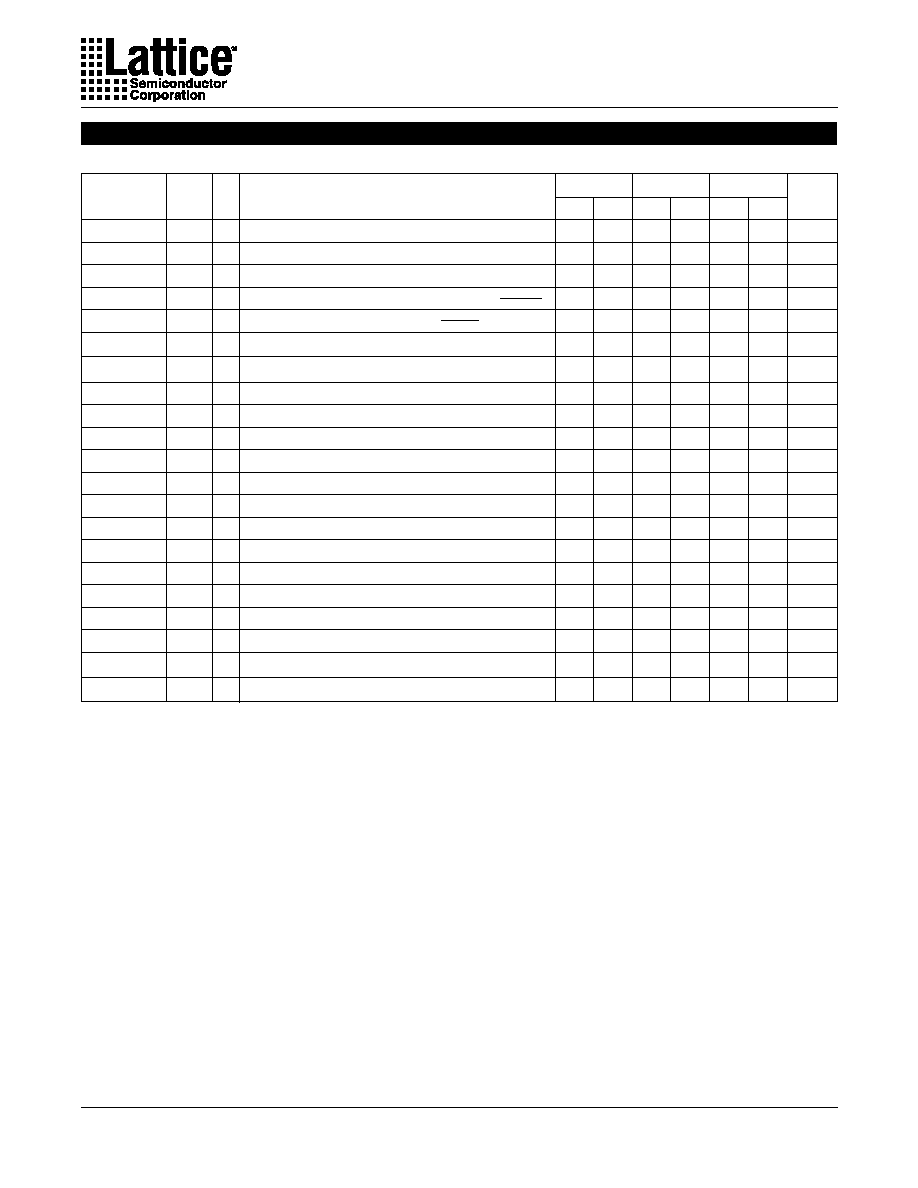

External Timing Parameters

Over Recommended Operating Conditions

t

pd1

UNITS

TEST

COND.

1. Unless noted otherwise, all parameters use a GRP load of four GLBs, 20 PTXOR path, ORP and Y0 clock.

2. Refer to Timing Model

in this data sheet for further details.

3. Standard 16-bit counter using GRP feedback.

4. Reference Switching Test Conditions section.

Table 2-0030A/1016EA

v.2.6

1

4

3

1

tsu2 + tco1

( )

DESCRIPTION

#

2

PARAMETER

A

1

Data Propagation Delay, 4PT Bypass, ORP Bypass

ns

t

pd2

A

2

Data Propagation Delay, Worst Case Path

ns

f

max (Int.)

A

3

Clock Frequency with Internal Feedback

MHz

f

max (Ext.)

--

4

Clock Frequency with External Feedback

MHz

f

max (Tog.)

--

5

Clock Frequency, Max. Toggle

MHz

t

su1

--

6

GLB Reg. Setup Time before Clock,4 PT Bypass

ns

t

co1

A

7

GLB Reg. Clock to Output Delay, ORP Bypass

ns

t

h1

--

8

GLB Reg. Hold Time after Clock, 4 PT Bypass

ns

t

su2

--

9

GLB Reg. Setup Time before Clock

ns

t

co2

--

10

GLB Reg. Clock to Output Delay

ns

t

h2

--

11

GLB Reg. Hold Time after Clock

ns

t

r1

A

12

Ext. Reset Pin to Output Delay

ns

t

rw1

--

13

Ext. Reset Pulse Duration

ns

t

ptoeen

B

14

Input to Output Enable

ns

t

ptoedis

C

15

Input to Output Disable

ns

t

wh

--

18

External Synchronous Clock Pulse Duration, High

ns

t

wl

--

19

External Synchronous Clock Pulse Duration, Low

ns

t

su3

--

20

I/O Reg. Setup Time before Ext. Sync Clock (Y1)

ns

t

h3

--

21

I/O Reg. Hold Time after Ext. Sync. Clock (Y1)

ns

( )

1

twh + twl

t

goeen

B

16

Global OE Output Enable

ns

t

goedis

C

17

Global OE Output Disable

ns

-200

MIN. MAX.

--

4.5

--

200

--

--

--

--

--

--

--

--

--

--

--

--

--

2.0

2.0

--

--

143

250

3.0

0.0

3.5

0.0

3.5

3.0

0.0

6.0

3.5

4.0

5.5

7.0

7.0

--

--

--

4.5

--

4.5

-100

MIN. MAX.

--

10.0

--

100

--

--

--

--

--

--

--

--

--

--

--

--

--

4.0

4.0

--

--

77

125

6.0

0.0

7.0

0.0

6.5

3.5

0.0

12.5

6.0

7.0

13.5

15.0

15.0

--

--

--

9.0

--

9.0

-125

MIN. MAX.

--

7.5

--

125

--

--

--

--

--

--

--

--

--

--

--

--

--

3.0

3.0

--

--

100

167

4.5

0.0

5.5

0.0

5.0

3.0

0.0

10.0

4.5

5.5

10.0

12.0

12.0

--

--

--

7.0

--

7.0

7

Specifications

ispLSI 1016EA

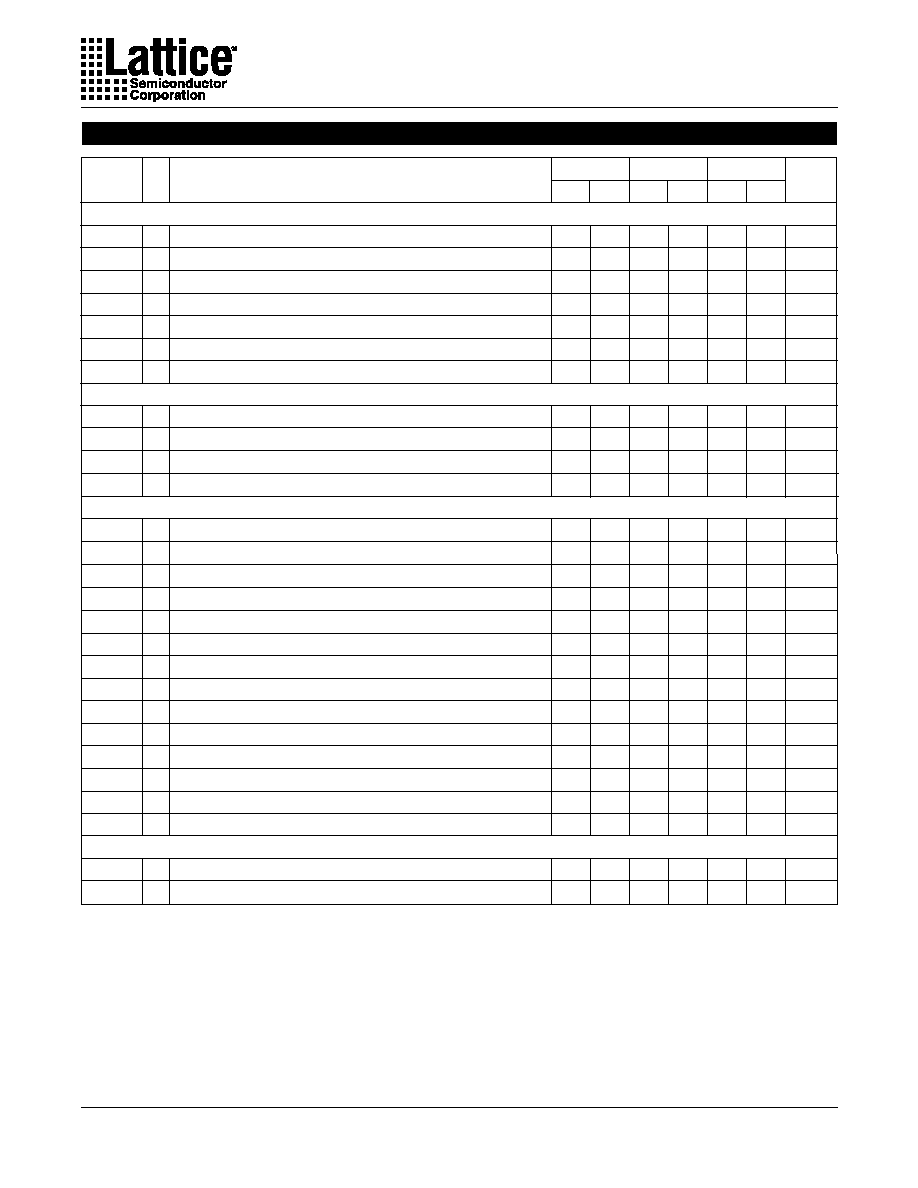

Internal Timing Parameters

1

t

iobp

1. Internal Timing Parameters are not tested and are for reference only.

2. Refer to Timing Model in this data sheet for further details.

3. The XOR adjacent path can only be used by hard macros.

Table 2-0036A/1016EA

v.2.6

Inputs

UNITS

DESCRIPTION

#

2

PARAM.

22 I/O Register Bypass

ns

t

iolat

23 I/O Latch Delay

ns

GLB

t

1ptxor

35 1 ProductTerm/XOR Path Delay

ns

t

20ptxor 36 20 Product Term/XOR Path Delay

ns

t

xoradj

37 XOR Adjacent Path Delay

ns

t

gbp

38 GLB Register Bypass Delay

ns

t

gsu

39 GLB Register Setup Time before Clock

ns

t

gh

40 GLB Register Hold Time after Clock

ns

t

gco

41 GLB Register Clock to Output Delay

ns

3

t

gro

42 GLB Register Reset to Output Delay

ns

t

ptre

43 GLB Product Term Reset to Register Delay

ns

t

ptoe

44 GLB Product Term Output Enable to I/O Cell Delay

ns

t

ptck

45 GLB Product Term Clock Delay

ns

ORP

GRP

t

4ptbpc

33 4 ProductTerm Bypass Path Delay (Combinatorial)

ns

t

4ptbpr

34 4 Product Term Bypass Path Delay (Registered)

ns

t

orp

47 ORP Delay

ns

t

orpbp

48 ORP Bypass Delay

ns

t

iosu

24 I/O Register Setup Time before Clock

ns

t

ioh

25 I/O Register Hold Time after Clock

ns

t

ioco

26 I/O Register Clock to Out Delay

ns

t

ior

27 I/O Register Reset to Out Delay

ns

t

din

28 Dedicated Input Delay

ns

t

grp16

32 GRP Delay, 16 GLB Loads

ns

t

grp8

31 GRP Delay, 8 GLB Loads

ns

t

grp4

30 GRP Delay, 4 GLB Loads

ns

t

grp1

29 GRP Delay, 1 GLB Load

ns

t

gfb

46 GLB Feedback Delay

ns

MIN. MAX.

-200

--

--

--

--

--

--

--

--

--

--

--

--

0.2

1.0

1.5

--

--

3.0

0.0

--

--

--

--

--

--

--

0.3

4.0

1.9

1.9

1.9

0.6

1.4

3.8

2.5

2.1

1.7

1.8

--

--

2.5

0.8

0.1

--

--

4.0

4.0

1.1

2.1

1.7

1.5

1.3

--

0.0

-100

MIN.

MIN.

MAX.

MAX.

-125

--

--

--

--

--

--

--

--

--

--

--

--

0.3

4.0

3.5

--

--

3.4

0.0

--

--

--

--

--

--

--

0.3

4.0

3.6

3.6

3.6

1.2

1.4

4.9

3.8

5.7

3.4

3.1

--

--

3.9

1.3

0.2

--

--

4.6

4.6

1.9

2.5

2.1

1.9

1.7

--

--

--

--

--

--

--

--

--

--

--

--

0.3

3.5

2.8

--

--

3.0

0.0

--

--

--

--

--

--

--

0.4

4.0

4.3

4.3

4.3

2.1

1.7

5.0

4.5

7.2

4.9

4.9

--

--

4.7

--

0.3

--

0.3

1.4

0.4

--

--

5.0

5.0

2.2

2.9

2.5

2.3

2.1

8

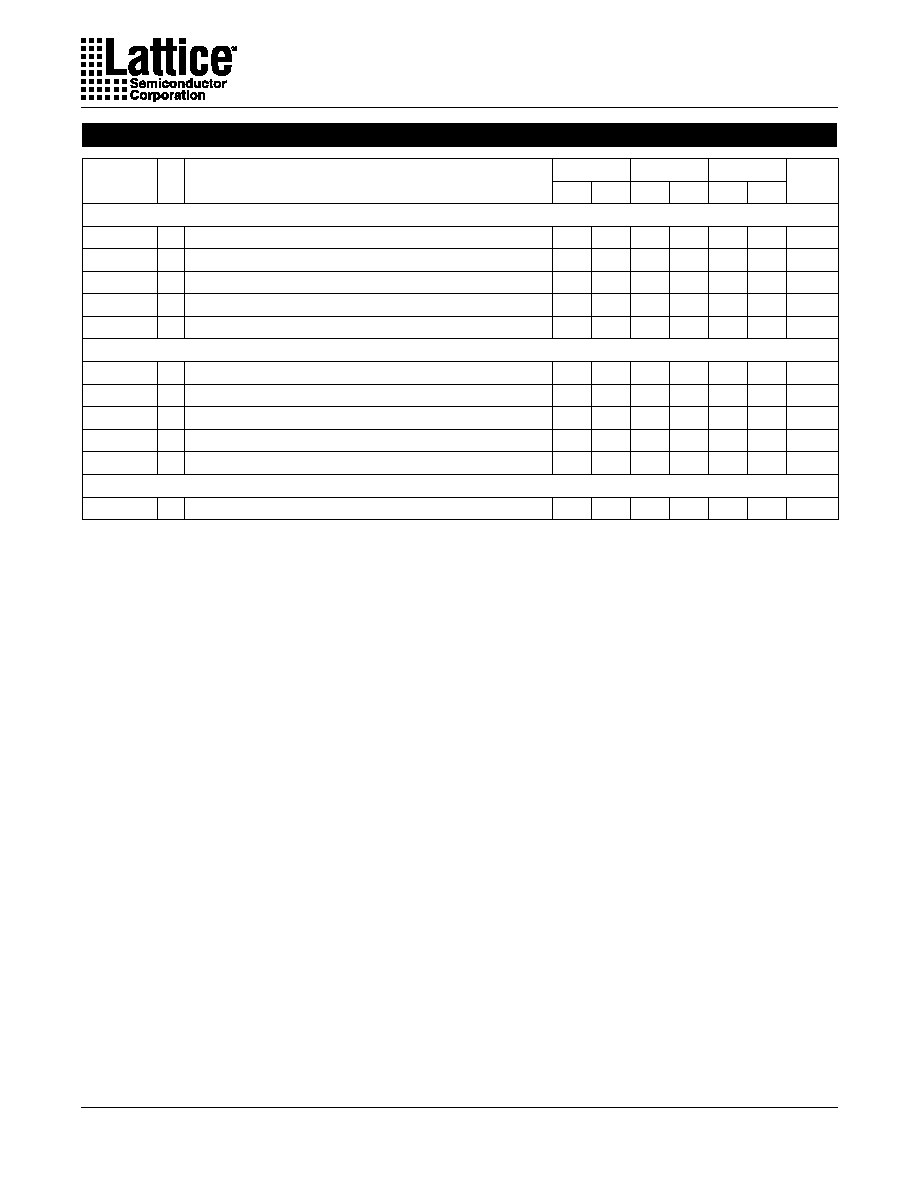

Specifications

ispLSI 1016EA

Internal Timing Parameters

1

t

ob

1. Internal Timing Parameters are not tested and are for reference only.

Table 2-0037A/1016EA

v.2.6

Outputs

UNITS

DESCRIPTION

#

PARAM.

49 Output Buffer Delay

ns

t

oen

51 I/O Cell OE to Output Enabled

ns

t

gy0

54 Clock Delay, Y0 to Global GLB Clock Line (Ref. clk)

ns

Global Reset

Clocks

t

gr

59 Global Reset to GLB and I/O Registers

ns

t

odis

52 I/O Cell OE to Output Disabled

ns

t

gy1

55 Clock Delay, Y1 to Global GLB Clock Line

ns

t

gcp

56 Clock Delay, Clock GLB to Global GLB Clock Line

ns

t

ioy1

57 Clock Delay, Y1 to I/O Cell Global Clock Line

ns

t

iocp

58 Clock Delay, Clock GLB to I/O Cell Global Clock Line

ns

t

goe

53 Global OE

ns

t

sl

50 Output Buffer Delay, Slew Limited Adder

ns

MIN. MAX.

-200

--

--

0.9

--

0.9

0.8

0.0

0.8

--

--

0.9

3.1

0.9

0.0

3.1

0.9

1.8

0.0

1.4

5.0

-100

MIN.

MIN.

MAX.

MAX.

-125

--

--

1.1

--

0.9

0.8

0.0

0.8

--

--

--

--

2.0

5.1

1.9

5.1

1.5

1.8

0.0

2.8

3.9

5.0

5.1

--

--

1.9

--

1.5

0.8

0.0

0.8

--

--

--

1.7

4.0

1.1

4.0

0.9

1.8

0.0

2.8

2.8

3.0

5.0

2.1

9

Specifications

ispLSI 1016EA

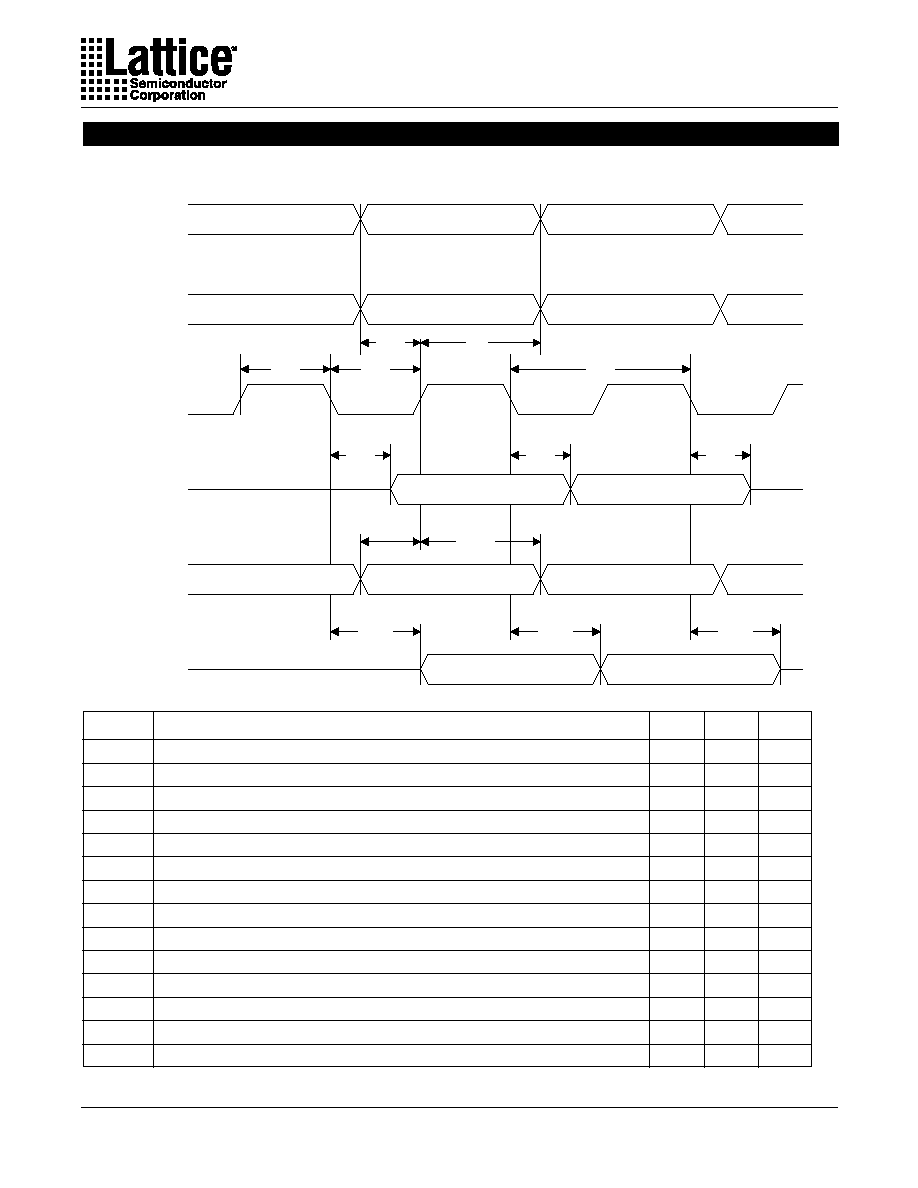

ispLSI 1016EA Timing Model

GLB Reg

Delay

I/O Pin

(Output)

ORP

Delay

0491/1016EA

Feedback

#46

Reg 4 PT Bypass

20 PT

XOR Delays

Control

PTs

Input

Register

Clock

Distribution

I/O Pin

(Input)

Y0

Y1

D

Q

GRP4

GLB Reg Bypass

ORP Bypass

D

Q

RST

RE

OE

CK

I/O Reg Bypass

I/O Cell

ORP

GLB

GRP

I/O Cell

#23 - 27

#30

#34

#33 Comb 4 PT Bypass

#35 - 37

#55 - 58

#43 - 45

#54

#53

#47

#48

Reset

Ded. In

GOE 0

#28

#22

RST

#59

#59

#38

#39 - 42

#51, 52

#49, 50

GRP Loading

Delay

#29, 31 - 32

Derivations of

t

su,

t

h and

t

co from the Product Term Clock

1

=

=

=

=

t

su

Logic + Reg su - Clock (min)

(

t

iobp +

t

grp4 +

t

20ptxor) + (

t

gsu) - (

t

iobp +

t

grp4 +

t

ptck(min))

(#22 + #30 + #36) + (#39) - (#22 + #30 + #45)

(0.3 + 1.5 + 1.9) + (0.2) - (0.3 + 1.5 + 1.2)

0.9

1.6

7.2

1.1

1.4

7.2

=

=

=

=

t

h

Clock (max) + Reg h - Logic

(

t

iobp +

t

grp4 +

t

ptck(max)) + (

t

gh) - (

t

iobp +

t

grp4 +

t

20ptxor)

(#22 + #30 + #45) + (#40) - (#22 + #30 + #36)

(0.3 + 1.5 + 2.5) + (1.0) - (0.3 + 1.5 + 1.9)

=

=

=

=

t

co

Clock (max) + Reg co + Output

(

t

iobp +

t

grp4 +

t

ptck(max)) + (

t

gco) + (

t

orp +

t

ob)

(#22 + #30 + #45) + (#41) + (#47 + #49)

(0.3 + 1.5 + 2.5) + (1.4) + (0.8 + 0.9)

Table 2-0042a/1016EA

v.2.6

Derivations of

t

su,

t

h and

t

co from the Clock GLB

1

=

=

=

=

t

su

Logic + Reg (setup) - Clock (min)

(

t

iobp +

t

grp4 +

t

20ptxor) + (

t

gsu) - (

t

gy0(min) +

t

gco +

t

gcp(min))

(#22 + #30 + #36) + (#39) - (#54 + #41 + #56)

(0.3 + 1.5 + 1.9) + (0.2) - (0.9 + 1.4 + 0.8)

=

=

=

=

t

h

Clock (max) + Reg (hold) - Logic

(

t

gy0(max) +

t

gco +

t

gcp(max)) + (

t

gh) - (

t

iobp +

t

grp4 +

t

20ptxor)

(#54 + #41 + #56) + (#40) - (#22 + #30 + #36)

(0.9 + 1.4 + 1.8) + (1.0) - (0.3 + 1.5 + 1.9)

=

=

=

=

t

co

Clock (max) + Reg (clock-to-out) + Output

(

t

gy0(max) +

t

gco +

t

gcp(max)) + (

t

gco) + (

t

orp +

t

ob)

(#54 + #41 + #56) + (#41) + (#47 + #49)

(0.9 + 1.4 + 1.8) + (1.4) + (0.8 + 0.9)

1. Calculations are based upon timing specifications for the ispLSI 1016EA-200.

10

Specifications

ispLSI 1016EA

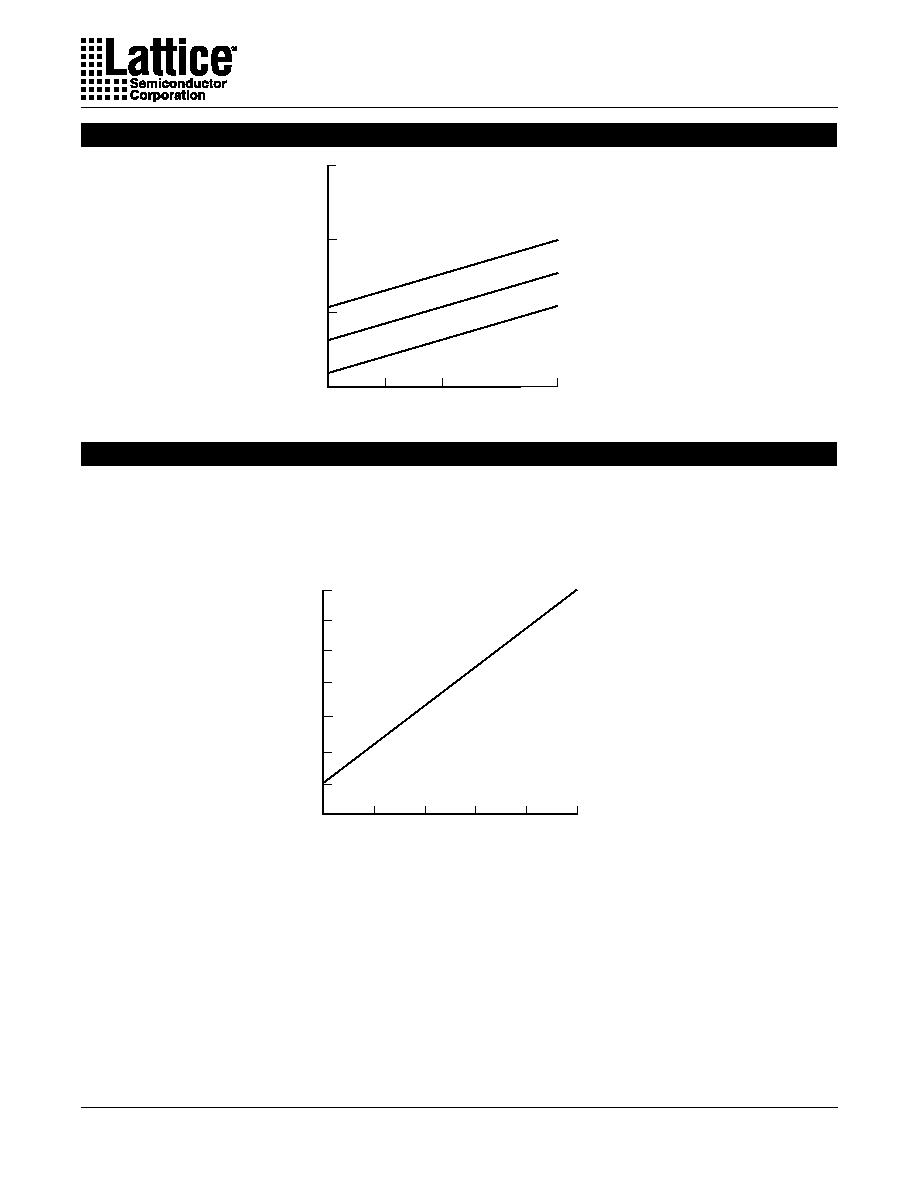

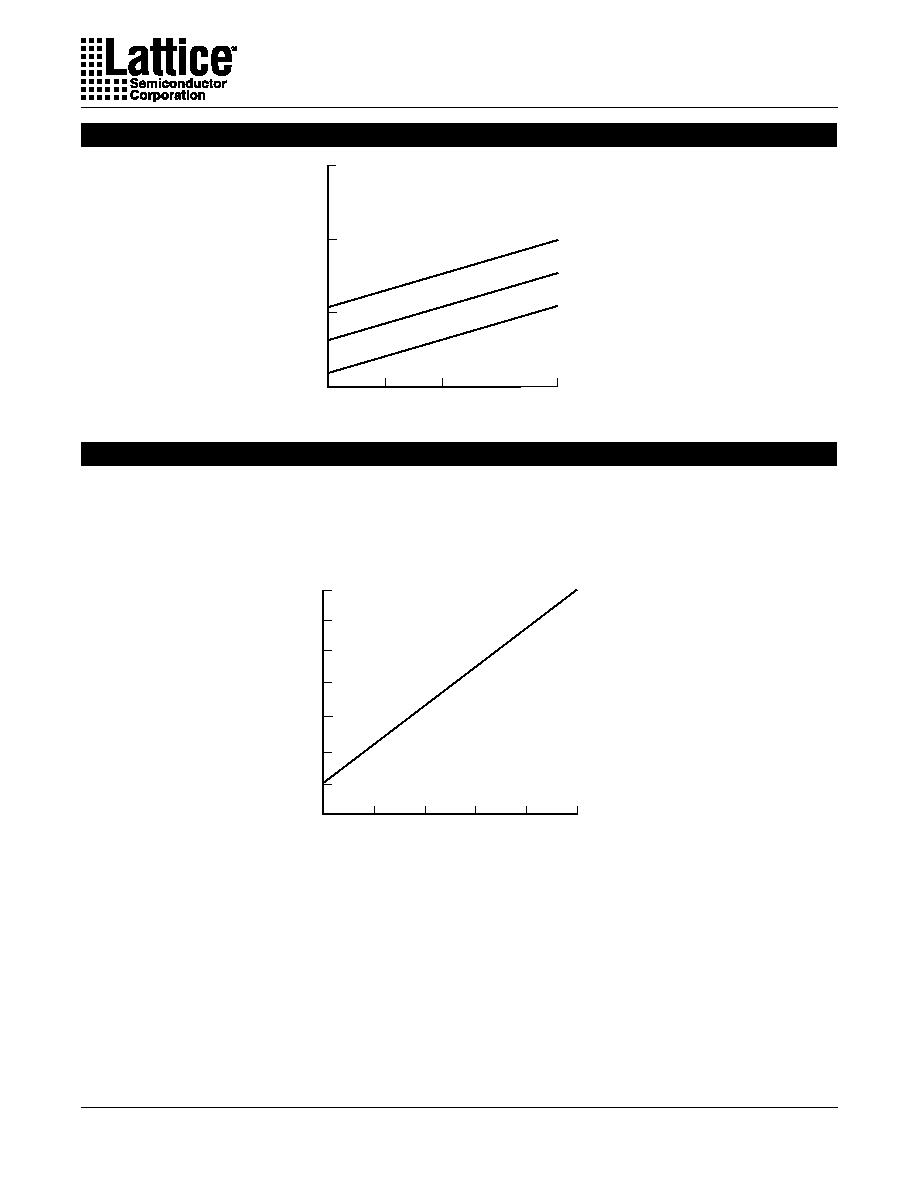

Power Consumption

Power consumption in the ispLSI 1016EA device de-

pends on two primary factors: the speed at which the

device is operating and the number of Product Terms

used. Figure 4 shows the relationship between power

and operating speed.

90

80

120

0

50

100

150

200

250

f

max (MHz)

I

CC (mA)

Notes: Configuration of four 16-bit counters

Typical current at 5V, 25

∞

C

ispLSI 1016EA

110

0127/1016EA

ICC can be estimated for the ispLSI 1016EA using the following equation:

ICC(mA) = 23 + (# of PTs * 0.52) + (# of nets * max freq * 0.004)

Where:

# of PTs = Number of product terms used in design

# of nets = Number of signals used in device

Max freq = Highest clock frequency to the device (in MHz)

The ICC estimate is based on typical conditions (VCC = 5.0V, room temperature) and an assumption of four GLB loads

on average exists and the device is filled with four 16-bit counters. These values are for estimates only. Since the

value of ICC is sensitive to operating conditions and the program in the device, the actual ICC should be verified.

130

140

150

100

Figure 4. Typical Device Power Consumption vs fmax

Maximum GRP Delay vs GLB Loads

GLB Load

ispLSI 1016EA-200

ispLSI 1016EA-125

ispLSI 1016EA-100

3

4

1

8

16

GRP Delay (ns)

4

2

GRP/GLB/1016EA

1

11

Specifications

ispLSI 1016EA

This is a dual function pin. It can be used either as Global Output Enable for

all I/O cells or it can be used as a dedicated input pin.

Input/Output Pins - These are the general purpose I/O pins used by the logic

array.

NAME

Table 2-0002C/1016EA

DESCRIPTION

I/O 0 - I/O 3

I/O 4 - I/O 7

I/O 8 - I/O 11

I/O 12 - I/O 15

I/O 16 - I/O 19

I/O 20 - I/O 23

I/O 24 - I/O 27

I/O 28 - I/O 31

GOE 0/IN 3

1

Y1/

RESET

1

Y0

TDI

TMS

GND

VCC

VCC

Supply voltage for output drivers, 5V or 3.3V.

VCCIO

TDO

TCK

Ground (GND)

PLCC

PIN NUMBERS

15,

19,

25,

29,

37,

41,

3,

7,

16,

20,

26,

30,

38,

42,

4,

8,

17,

21,

27,

31,

39,

43,

5,

9,

18,

22,

28,

32,

40,

44,

6,

10

2

35

11

14

36

1,

12,

13

24

33

23

34

1. Pins have dual function capability which is software selectable.

TQFP

PIN NUMBERS

9,

13,

19,

23,

31,

35,

41,

1,

10,

14,

20,

24,

32,

36,

42,

2,

11,

15,

21,

25,

33,

37,

43,

3,

12,

16,

22,

26,

34,

38,

44,

4

40

29

5

8

30

17,

6,

7

18

27

39

28

Input - Controls the operation of the ISP state machine.

Dedicated Clock input. This clock input is connected to one of the clock inputs

of all of the GLBs on the device.

Input - Functions as an input pin to load programming data into the device and

also used as one of the two control pins for the ispJTAG state machine.

Output - Functions as an output pin to read serial shift register data.

Input - Functions as a clock pin for the Serial Shift Register.

This pin performs two functions:

Dedicated Clock input. This clock input is brought into the clock distribution

network, and can optionally be routed to any GLB on the device.

Active Low (0) Reset pin which resets all of the GLB and I/O registers in the

device.

Pin Description

12

Specifications

ispLSI 1016EA

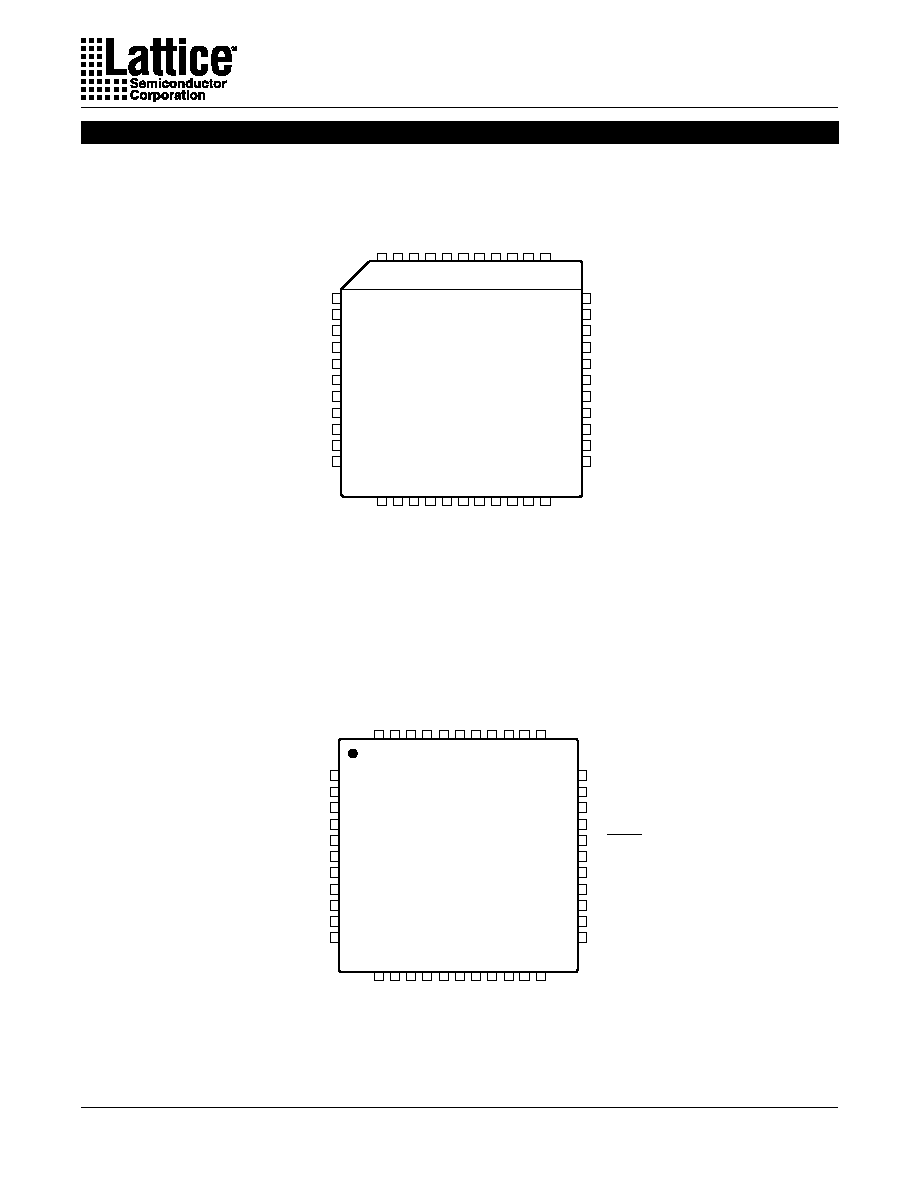

Pin Configurations

ispLSI 1016EA 44-Pin PLCC Pinout Diagram

I/O 18

I/O 17

I/O 16

TMS

Y1/

RESET

1

VCC

TCK

I/O 15

I/O 14

I/O 13

I/O 12

I/O 28

I/O 29

I/O 30

I/O 31

Y0

VCC

VCCIO

TDI

I/O 0

I/O 1

I/O 2

I/O 27

I/O 26

I/O 25

I/O 24

GOE 0/IN 3

1

GND

I/O 23

I/O 22

I/O 21

I/O 20

I/O 19

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

GND

TDO

I/O 8

I/O 9

I/O 10

I/O 11

ispLSI 1016EA

Top View

7

8

9

10

12

11

13

14

15

16

17

39

38

37

36

35

34

33

32

31

30

29

6

18

5

19

4

20

3

21

2

22

1

23

44

24

43

25

42

26

41

27

40

28

0123A-isp1016EA

1. Pins have dual function capability which is software selectable.

ispLSI 1016EA 44-Pin TQFP Pinout Diagram

I/O 18

I/O 17

I/O 16

TMS

Y1/RESET

1

VCC

TCK

I/O 15

I/O 14

I/O 13

I/O 12

I/O 28

I/O 29

I/O 30

I/O 31

Y0

VCC

VCCIO

TDI

I/O 0

I/O 1

I/O 2

I/O 27

I/O 26

I/O 25

I/O 24

GOE 0/IN 3

1

GND

I/O 23

I/O 22

I/O 21

I/O 20

I/O 19

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

GND

TDO

I/O 8

I/O 9

I/O 10

I/O 11

ispLSI 1016EA

Top View

1

2

3

4

6

5

7

8

9

10

11

33

32

31

30

29

28

27

26

25

24

23

44

12

43

13

42

14

41

15

40

16

39

17

38

18

37

19

36

20

35

21

34

22

44 TQFP/1016EA

1. Pins have dual function capability which is software selectable.

13

Specifications

ispLSI 1016EA

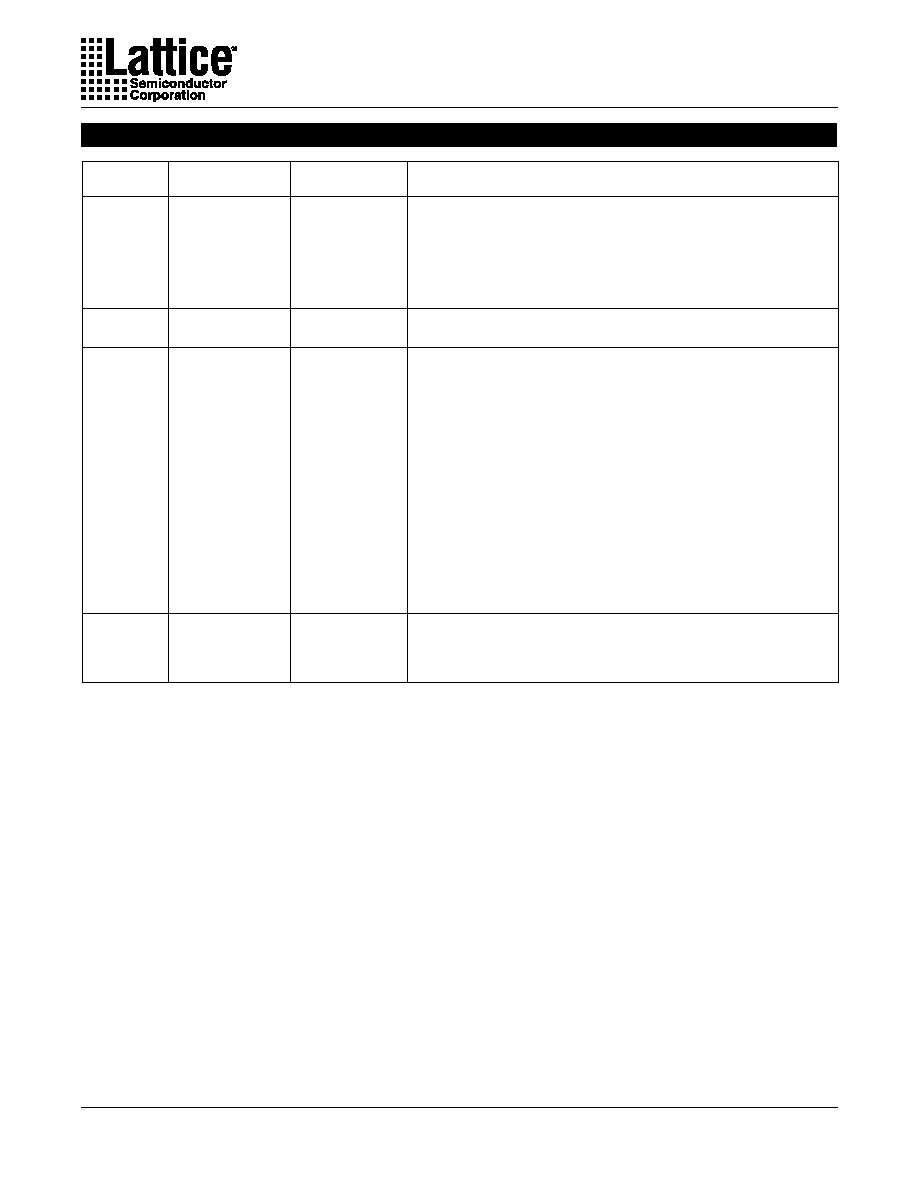

Part Number Description

ispLSI 1016EA Ordering Information

Device Number

Grade

Blank = Commercial

1016EA

XXX

X

XXX

X

Speed

Power

L = Low

Package

J44 = PLCC

T44 = TQFP

--

Device Family

0212/1016EA

ispLSI

200

125

100

=

=

=

200 MHz fmax

125 MHz fmax

100 MHz fmax

125

125

44-Pin PLCC

7.5

7.5

ispLSI 1016EA-125LJ44

44-Pin TQFP

44-Pin PLCC

44-Pin TQFP

ispLSI 1016EA-125LT44

Table 2-0041A/1016EA

FAMILY

fmax (MHz)

200

200

ORDERING NUMBER

PACKAGE

44-Pin PLCC

44-Pin TQFP

tpd (ns)

4.5

4.5

ispLSI

ispLSI 1016EA-200LJ44

ispLSI 1016EA-200LT44

100

100

10

10

ispLSI 1016EA-100LJ44

ispLSI 1016EA-100LT44

COMMERCIAL