1

LTC1329-10/

LTC1329-50/LTC1329A-50

Micropower 8-Bit Current

Output D/A Converter

s

Guaranteed Precision Full-Scale DAC Output

Current at 25

∞

C:

LTC1329A-50

50

µ

A

±

1%

LTC1329-10

10

µ

A

±

3%

LTC1329-50

50

µ

A

±

3%

s

Wide Output Voltage DC Compliance: ≠ 15V to 2.5V

s

Wide Supply Range: 2.7V

V

CC

6.5V

s

Supply Current in Shutdown: 0.2

µ

A

s

Low Supply Current: 75

µ

A for LTC1329-10,

95

µ

A for LTC1329-50/LTC1329A-50

s

Available in 8-Pin SO

s

Triple Mode

TM

Interface Modes

1. Standard 3-Wire Mode

2. Pulse Mode 1-Wire Interface: Increment-Only

3. Pulse Mode 2-Wire Interface: Increment/Decrement

s

Can Read Back the 8-Bit DAC Value in 3-Wire Mode

s

DAC Powers Up at Midrange

s

DAC Contents Are Retained in Shutdown

FEATURES

DESCRIPTIO

N

U

APPLICATIO

N

S

U

s

LCD Contrast Control

s

Backlight Brightness Control

s

Battery Charger Current/Voltage Adjustment

s

Power Supply Voltage Adjustment

s

Trimmer Pot Elimination

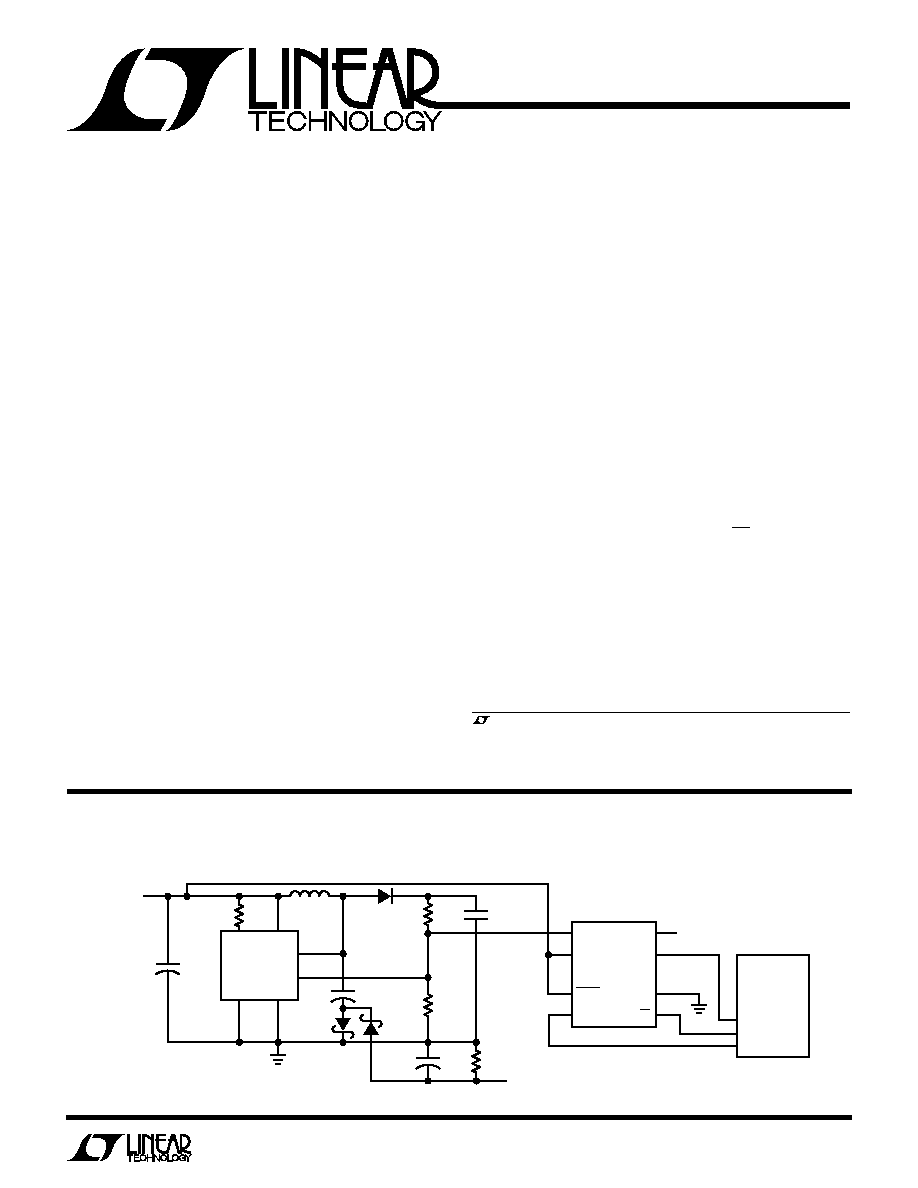

TYPICAL APPLICATIO

N

U

Digitally Controlled LCD Bias Generator

1

2

8

7

D

OUT

D

IN

I

OUT

V

CC

SHDN

CLK

LTC1329-50

GND

CS

47

µ

F

1329 TA01

V

OUT

≠22V at 40mA

V

IN

5V

200k

3

4

6

5

4.7

µ

F

22

µ

F

0.1

µ

F

LT

Æ

1173

1N4148

1N5818

1N5818

L1*

100

µ

H

*GOWANDA GA10-103K OR

COILTRONICS CTX100-4

I

LIM

V

IN

FB

SW2

GND

SW1

220k

47

10.1k

MPU

(e.g., 8051)

P1.2

P1.1

P1.0

+

+

+

The LTC

Æ

1329-10/ LTC1329-50/LTC1329A-50 are

micropower 8-bit current output D/A converters (DACs)

with an output range of 0

µ

A to 10

µ

A for the LTC1329-10

and 0

µ

A to 50

µ

A for the LTC1329-50/LTC1329A-50. The

DAC current output can be biased from ≠ 15V to 2V or

≠ 15V to 2.5V in 3.3V and 5V systems, respectively. Supply

current is only 95

µ

A for the LTC1329-50/LTC1329A-50

and 75

µ

A for LTC1329-10. A shutdown mode drops the

supply current to 0.2

µ

A.

The LTC1329 can communicate with external circuitry by

using one of three interface modes: standard 3-wire serial

mode and two pulse modes. Upon power-up, the internal

counter resets to 1000 0000B, the DAC output assumes

midrange and the chip is configured in 3-wire or pulse

mode depending on the signal level at CS.

In 3-wire mode, the system MPU can serially transfer 8-bit

data to and from the LTC1329. In pulse mode, the upper

six bits of the DAC output can be programmed for incre-

ment-only (1-wire interface) or increment/decrement

(2-wire interface) operation depending on the signal level

at D

IN

.

LTC1329 is available in 8-pin SO packages.

, LTC and LT are registered trademarks of Linear Technology Corporation.

Triple Mode is a trademark of Linear Technology Corporation.

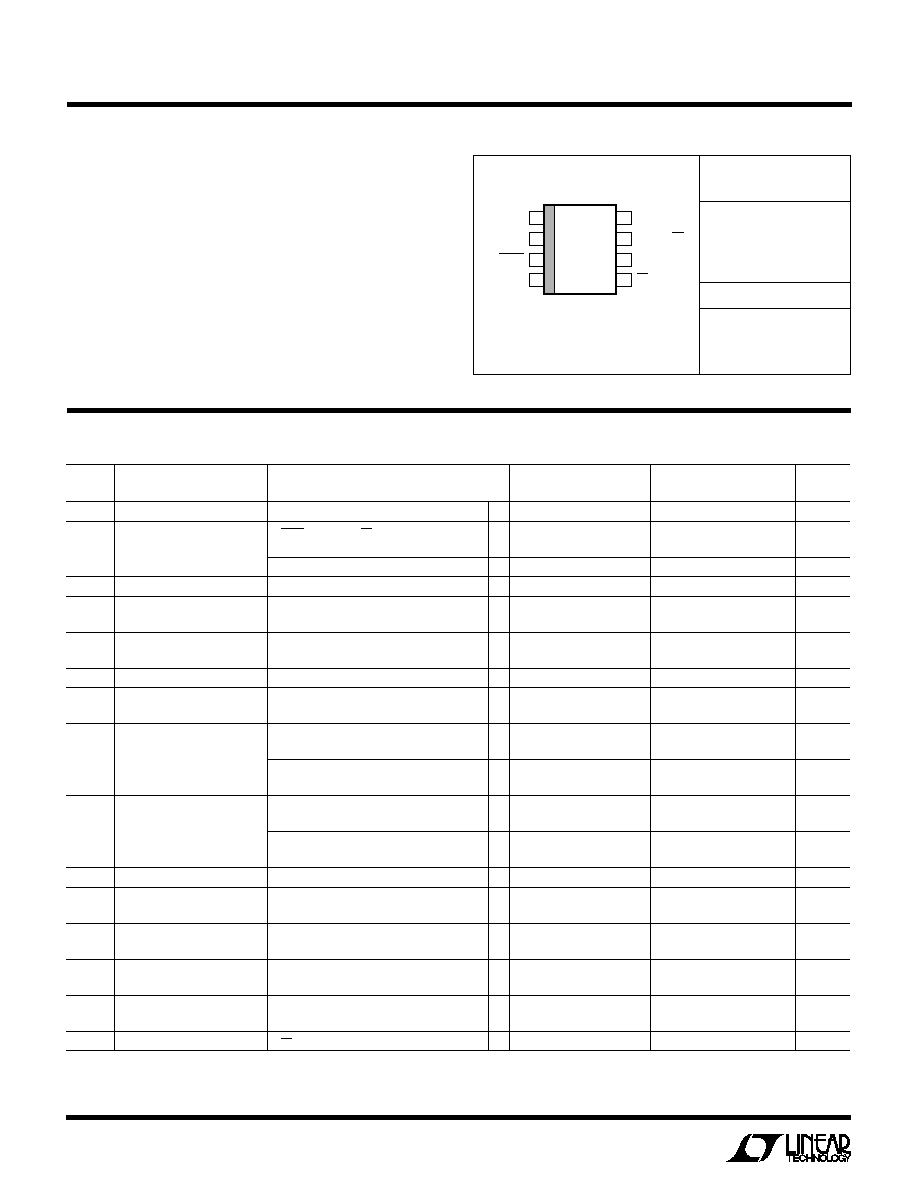

2

LTC1329-10/

LTC1329-50/LTC1329A-50

ABSOLUTE

M

AXI

M

U

M

RATINGS

W

W

W

U

PACKAGE/ORDER I

N

FOR

M

ATIO

N

W

U

U

(Note 1)

Supply Voltage (V

CC

) ................................................ 7V

Input Voltage (All Inputs)............ ≠ 0.3V to (V

CC

+ 0.3V)

Output Voltage

I

OUT

......................................... ≠ 15V to (V

CC

+ 0.3V)

D

OUT

....................................... ≠ 0.3V to (V

CC

+ 0.3V)

Short-Circuit Duration (All Outputs) ............... Indefinite

Operating Temperature Range .................... 0

∞

C to 70

∞

C

Storage Temperature Range ................. ≠ 65

∞

C to 150

∞

C

Lead Temperature (Soldering, 10 sec).................. 300

∞

C

ORDER PART

NUMBER

LTC1329CS8-10

LTC1329CS8-50

LTC1329ACS8-50

T

JMAX

= 125

∞

C,

JA

= 150

∞

C/ W

S8 PART MARKING

1329A5

13291

13295

Consult factory for Industrial and Military grade parts.

V

CC

= 3.3V, T

A

= 25

∞

C, unless otherwise specified.

LTC1329-10

LTC1329-50/LTC1329A-50

SYMBOL PARAMETER

CONDITIONS

MIN

TYP

MAX

MIN

TYP

MAX

UNITS

V

CC

q

2.7

6.5

2.7

6.5

V

I

CC

Supply Current

V

SHDN

= V

DIN

= V

CS

= V

CC

, V

CLK

= 0V,

q

75

130

95

150

µ

A

D

OUT

= NC, I

OUT

= NC

Shutdown

q

0.2

5

0.2

5

µ

A

DAC Resolution

8

8

Bits

DAC Full-Scale Current

Output Voltage at I

OUT

= 0.45V, T

A

= 25

∞

C

9.7

10

10.3

48.5

50

51.5

µ

A

(LTC1329-10, LTC1329-50)

q

9.5

10

10.5

47.5

50

52.5

µ

A

Output Voltage at I

OUT

= 0.45V, T

A

= 25

∞

C

49.5

50

50.5

µ

A

(LTC1329A-50)

q

49.0

50

51.0

µ

A

DAC Zero-Scale Current

Output Voltage at I

OUT

= 0.45V

q

200

200

nA

DAC Differential

Monotonicity Guaranteed

q

±

0.3

±

0.9

±

0.9

LSB

Nonlinearity

Supply Voltage Rejection

V

CC

= 3V to 5.5V, I

OUT

= Full Scale,

q

±

1

±

2

±

1

±

2

LSB

Output Voltage at I

OUT

= 0.45V

V

CC

= 2.7V to 6.5V, Full Scale,

q

±

2.5

±

4

±

2.5

±

4

LSB

Output Voltage at I

OUT

= 0.45V

Output Voltage Rejection

V

CC

= 5V, I

OUT

= Full Scale,

q

±

0.25

±

1

±

0.25

LSB

Output Voltage at I

OUT

= ≠ 15V to 0V

V

CC

= 5V, I

OUT

= Full Scale,

q

±

1.5

±

1.5

LSB

Output Voltage at I

OUT

= 0V to 2.5V

I

IH

, I

IL

Logic Input Current

0V

V

IN

V

CC

q

±

1

±

1

µ

A

V

IH

High Level Input Voltage

V

CC

= 5V

q

2.0

2.0

V

V

CC

= 3.3V

q

1.9

1.9

V

V

IL

Low Level Input Voltage

V

CC

= 5V

q

0.80

0.80

V

V

CC

= 3.3V

q

0.45

0.45

V

V

OH

High Level Output Voltage

V

CC

= 5V, I

O

= 400

µ

A

q

2.4

2.4

V

V

CC

= 3.3V, I

O

= 400

µ

A

q

2.1

2.1

V

V

OL

Low Level Output Voltage

V

CC

= 5V, I

O

= 2mA

q

0.4

0.4

V

V

CC

= 3.3V, I

O

= 1mA

q

0.4

0.4

V

I

OZ

Three-State Output Leakage

V

CS

= V

CC

q

±

5

±

5

µ

A

ELECTRICAL CHARACTERISTICS

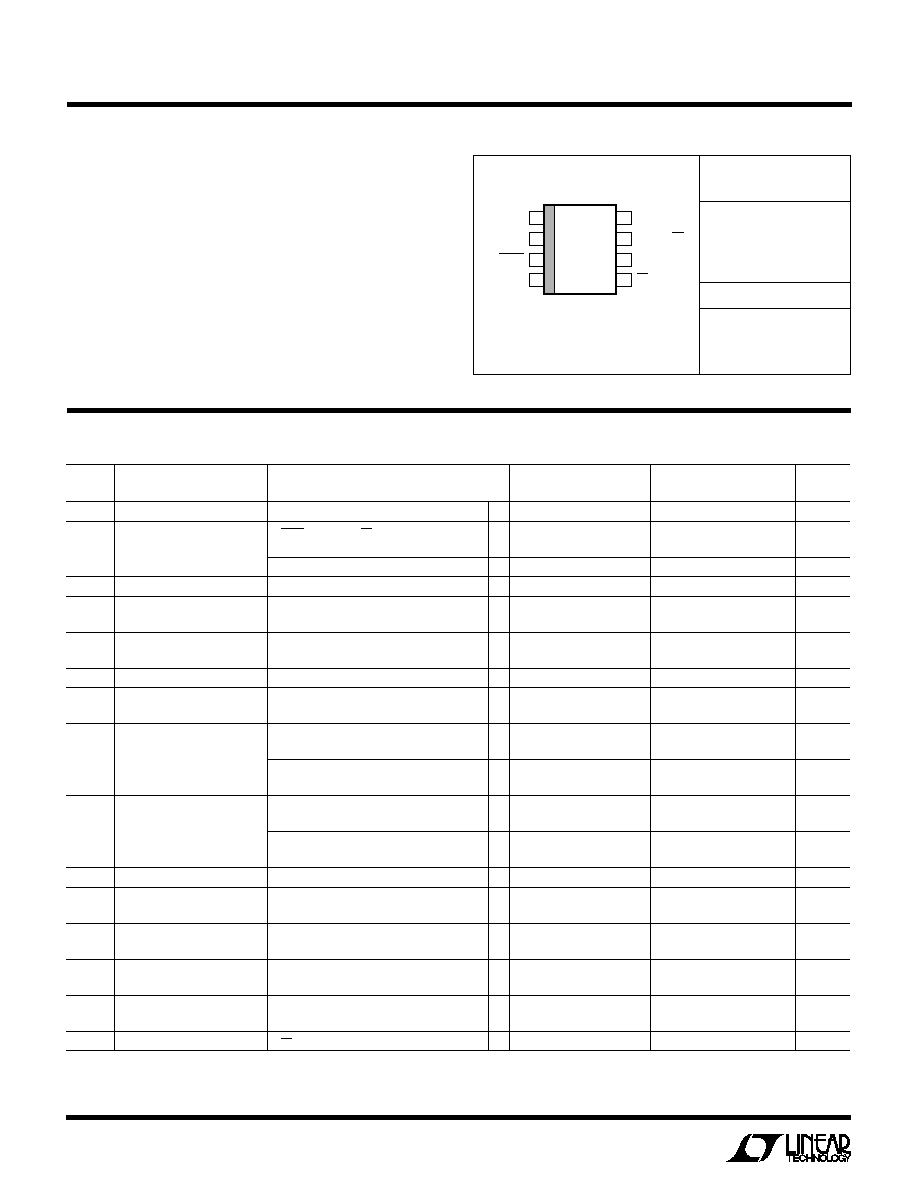

1

2

3

4

8

7

6

5

TOP VIEW

D

OUT

D

IN

(UP/DN)

GND

CS

I

OUT

V

CC

SHDN

CLK

S8 PACKAGE

8-LEAD PLASTIC SO

3

LTC1329-10/

LTC1329-50/LTC1329A-50

V

CC

= 3.3V, unless otherwise specified. (Notes 2, 3)

RECO

E

DED OPERATI

G CO DITIO

S

U

U

U

U

W

W

SYMBOL PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

Serial Interface

f

CLK

Clock Frequency

q

2

MHz

t

CKS

Setup Time, CLK

Before CS

q

150

ns

t

CSS

Setup Time, CS

Before CLK

q

400

ns

t

DV

CS

to D

OUT

Valid

See Test Circuits

q

150

ns

t

DS

D

IN

Setup Time Before CLK

q

150

ns

t

DH

D

IN

Hold Time After CLK

q

150

ns

t

DO

CLK

to D

OUT

Valid

See Test Circuits

q

150

ns

t

CKHI

CLK High Time

q

200

ns

t

CKLO

CLK Low Time

q

250

ns

t

CSH

CLK

Before CS

q

150

ns

t

DZ

CS

to D

OUT

in Hi-Z

See Test Circuits

q

400

ns

t

CKH

CS

Before CLK

q

400

ns

t

CSLO

CS Low Time

f

CLK

= 2MHz (Note 4)

q

4550

ns

V

CLK

= 0V

q

400

ns

t

CSHI

CS High Time

q

400

ns

Note 2: Timing for all input signals is measured at 0.8V for a High-to-Low

transition and at 2V for a Low-to-High transition.

Note 3: Timing specification are guaranteed but not tested.

Note 4: This is the minimum time required for valid data transfer.

The

q

denotes specifications which apply over the full operating

temperature range.

Note 1: Absolute Maximum Ratings are those values beyond which the life

of the device may be impaired.

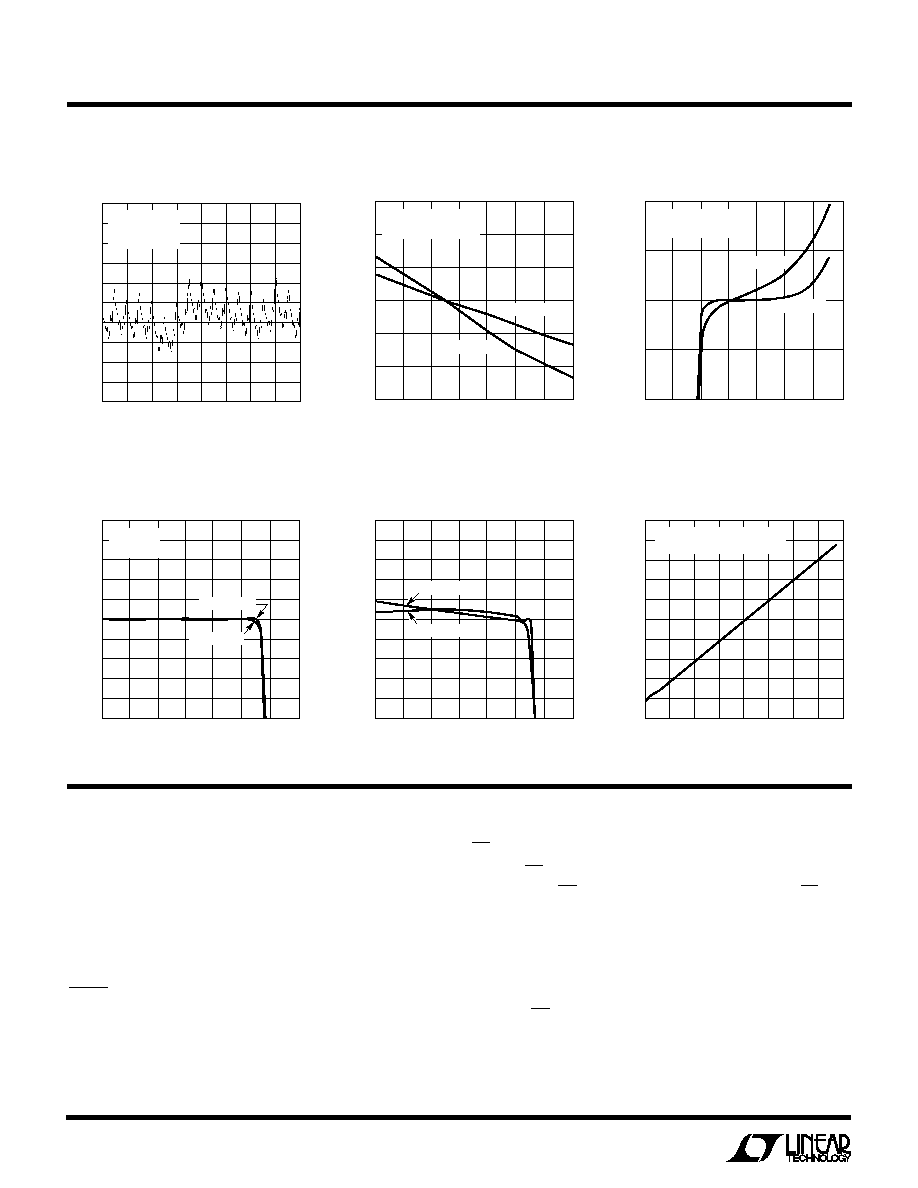

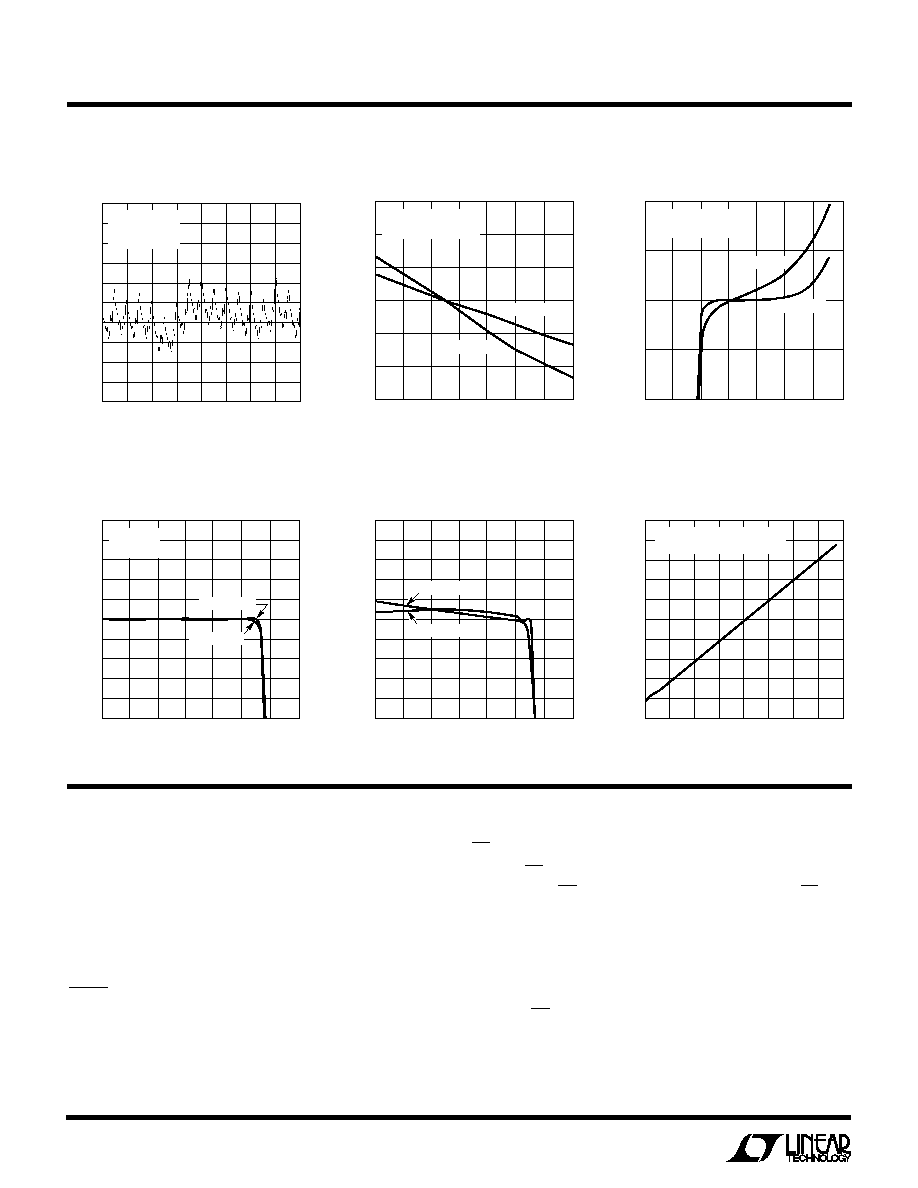

TYPICAL PERFOR

M

A

N

CE CHARACTERISTICS

U

W

CODE

0

DNL (LSB)

1.0

0.8

0.6

0.4

0.2

0

≠0.2

≠0.4

≠0.6

≠0.8

≠1.0

64

128

160

1392 G01

32

96

192 224

256

T

A

= 25

∞

C

V

CC

= 3.3V

V(I

OUT

) = 0.45V

CODE

0

INL (LSB)

1.0

0.8

0.6

0.4

0.2

0

≠0.2

≠0.4

≠0.6

≠0.8

≠1.0

64

128

160

1329 ∑ TPC02

32

96

192 224

256

T

A

= 25

∞

C

V

CC

= 3.3V

V(I

OUT

) = 0.45V

CODE

0

DNL (LSB)

1.0

0.8

0.6

0.4

0.2

0

≠0.2

≠0.4

≠0.6

≠0.8

≠1.0

64

128

160

1392 G03

32

96

192 224

256

T

A

= 25

∞

C

V

CC

= 3.3V

V(I

OUT

) = 0.45V

LTC1329-10 DNL vs Code

LTC1329-10 INL vs Code

LTC1329-50 DNL vs Code

4

LTC1329-10/

LTC1329-50/LTC1329A-50

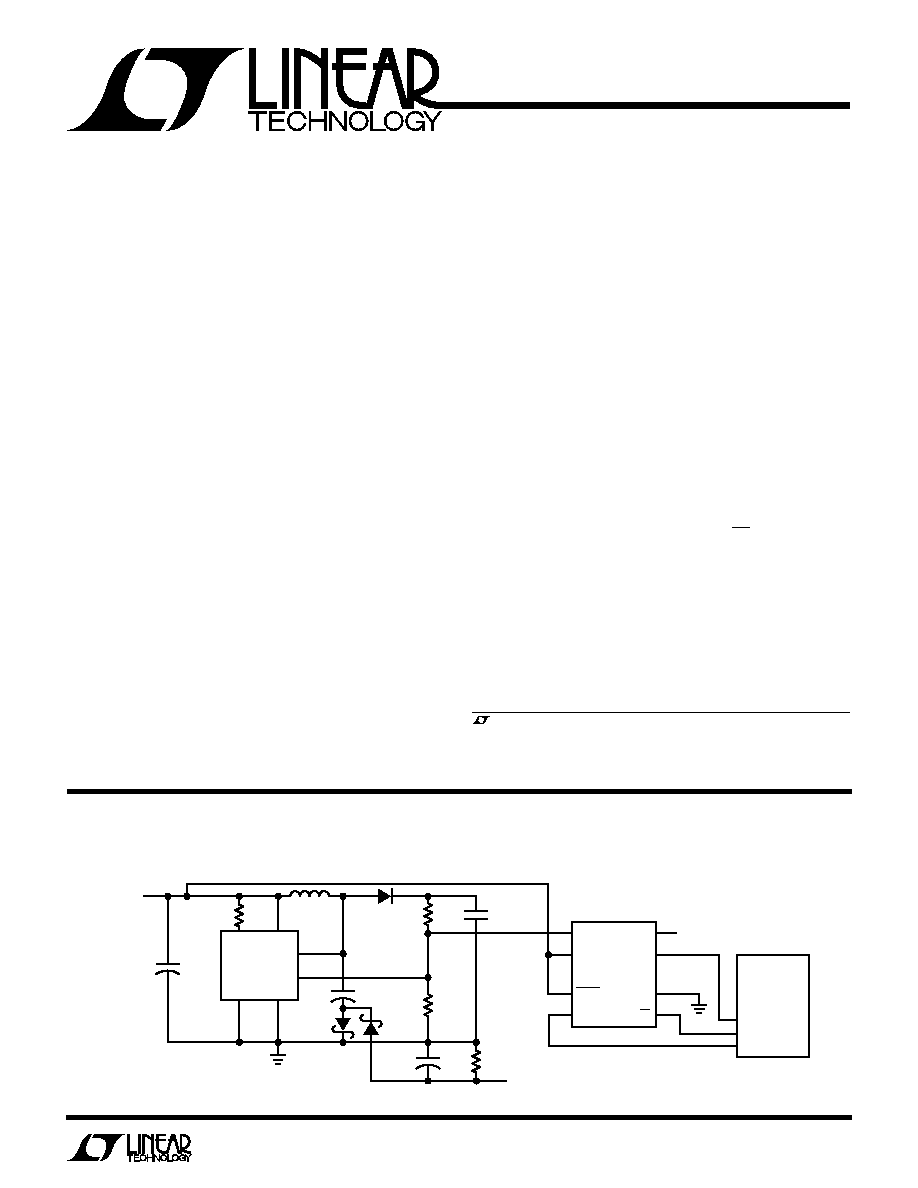

TYPICAL PERFOR

M

A

N

CE CHARACTERISTICS

U

W

TEMPERATURE (

∞

C)

0

FULL-SCALE I

OUT

ERROR (LSB)

3

2

1

0

≠1

≠2

≠3

30

50

1329 G05

10

20

40

60

70

V

CC

= 3.3V

V(I

OUT

) = 0.45V

LTC1329-50

LTC1329-10

CODE

0

INL (LSB)

1.0

0.8

0.6

0.4

0.2

0

≠0.2

≠0.4

≠0.6

≠0.8

≠1.0

64

128

160

1329 ∑ TPC04

32

96

192 224

256

T

A

= 25

∞

C

V

CC

= 3.3V

V(I

OUT

) = 0.45V

LTC1329-10/LTC1329-50 Full-

Scale Current vs Temperature

SUPPLY VOLTAGE (V)

0

FULL-SCALE I

OUT

ERROR (LSB)

2

1

0

≠1

≠2

3

5

1329 G06

1

2

4

6

7

T

A

= 25

∞

C

V(I

OUT

) = 0.45V

LTC1329-50

LTC1329-10

LTC1329-10/LTC1329-50

Supply Voltage Rejection

LTC1329-50 INL vs Code

PI

N

FU

N

CTIO

N

S

U

U

U

I

OUT

(Pin 1): DAC Current Output. In 3.3V or 5V systems,

the DAC current output can be biased from ≠ 15V to 2V or

≠ 15V to 2.5V respectively.

V

CC

(Pin 2): Voltage Supply (2.7V

V

CC

6.5V). This

supply must be kept free from noise and ripple by bypass-

ing directly to the ground plane.

SHDN (Pin 3): Shutdown. A logic low puts the chip

into Shutdown mode. The digital setting for the DAC is

retained.

CLK (Pin 4): Shift Clock. This clock synchronizes the serial

data in 3-wire mode. This pin has a Schmitt trigger input.

CS (Pin 5): Chip Select Input. In 3-wire mode, a logic low

on this CS pin enables the LTC1329. Upon power-up, a

logic high at CS puts the chip into pulse mode. If CS ever

goes low, the chip is configured in 3-wire mode until the

next power is cycled.

GND (Pin 6): Ground. Ground should be tied directly to a

ground plane.

D

IN

(UP/DN)(Pin 7): Data Input. In 3-wire mode, the DAC

data is shifted into D

IN

on the rising edge of CLK. In pulse

mode, upon power-up a logic high at D

IN

puts the counter

into increment-only mode. If D

IN

ever goes low, the

I

OUT

BIAS VOLTAGE (V)

≠15

FULL-SCALE I

OUT

ERROR (LSB)

0.5

0.4

0.3

0.2

0.1

0

≠0.1

≠0.2

≠0.3

≠0.4

≠0.5

≠6

0

1329 G07

≠12

≠9

≠3

3

6

T

A

= 25

∞

C

V

CC

= 3.3V

LTC1329-50

LTC1329-10

LTC1329-10/LTC1329-50

Bias Voltage Rejection

(Full-Scale Current)

I

OUT

BIAS VOLTAGE (V)

≠15

ZERO-SCALE I

OUT

CURRENT (nA)

50

40

30

20

10

0

≠10

≠20

≠30

≠40

≠50

≠6

0

1329 G08

≠12

≠9

≠3

3

6

LTC1329-10

LTC1329-50

LTC1329-10/LTC1329-50

Bias Voltage Rejection

(Zero-Scale Current)

SUPPLY VOLTAGE (V)

2.7

MAXIMUM I

OUT

BIAS VOLTAGE (V)

6.5

6.0

5.5

5.0

4.5

4.0

3.5

3.0

2.5

2.0

1.5

3.7

4.7

5.2

1329 ∑ TPC09

3.2

4.2

5.7

6.2

6.7

T

A

= 25

∞

C

I

OUT

= FULL-SCALE CURRENT

Maximum I

OUT

Bias Voltage

vs Supply Voltage

5

LTC1329-10/

LTC1329-50/LTC1329A-50

PI

N

FU

N

CTIO

N

S

U

U

U

counter is configured in increment/decrement mode until

the power is cycled.

D

OUT

(Pin 8): Data Output. In 3-wire mode, on every

conversion D

OUT

serially outputs the previous 8-bit DAC

data. In pulse mode, D

OUT

is three-stated.

BLOCK DIAGRA

W

LATCH

AND

LOGIC

LATCH

AND

LOGIC

8-BIT

CURRENT

DAC

CLK

SHDN

CLK

1329 BD

D

IN

D

OUT

UP/DN

8-BIT DAC REGISTER/COUNTER

I

OUT

V

CC

D

OUT

8

8

8

9-BIT SHIFT REGISTER

VOLTAGE

REFERENCE

UP ONLY/

UP/DN

MODE SELECT

0 = PULSE

1 = 3-WIRE

POWER-ON

RESET

CONTROL

LOGIC

CLK

D

IN

(UP/DN)

CS

SHDN

SHDN

TEST CIRCUITS

Voltage Waveforms for t

DO

0.8V

0.4V

2.4V

1329 TC03

D

OUT

CLK

t

DO

Voltage Waveforms for t

DZ

, t

DV

1329 TC04

0.8V

CS

D

OUT

SET HIGH

D

OUT

SET LOW

2.4V

2.0V

90%

10%

0.4V

t

DV

t

DZ

HI-Z

HI-Z

HI-Z

HI-Z

3k

100pF

1329 TC01

1.4V

D

OUT

3k

100pF

1329 TC02

5V t

DZ

WAVEFORM 2, t

DV

t

DZ

WAVEFORM 1

D

OUT

Load Circuit for t

DO

Load Circuit for t

DZ,

t

DV