| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: DS21FT44N | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

1 of 117

071702

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device

may be simultaneously available through various sales channels. For information about device errata, click here:

http://www.maxim-ic.com/errata

.

FEATURES

ß 16 or 12 completely independent E1 framers

in one small 27mm x 27mm package

ß Each multichip module (MCM) contains

either four (FF) or three (FT) DS21Q44 die

ß Each quad framer can be concatenated into a

single 8.192MHz backplane data stream

ß IEEE 1149.1 JTAG-Boundary Scan

Architecture

ß DS21FF44 and DS21FT44 are pin

compatible with DS21FF42 and DS21FT42,

respectively, to allow the same footprint to

support T1 and E1 applications

ß 300-pin MCM BGA 1.27mm pitch package

(27mm x 27mm)

ß Low-power 3.3V CMOS with 5V tolerant

input and outputs

APPLICATIONS

ß DSLAMs

ß Multiplexers/Demultiplexers

ß Switches

ß High-Density Line Cards

ORDERING INFORMATION

PART

CHANNEL

PIN-PACKAGE

TEMP. RANGE

DS21FT44

12

300-BGA, 27mm x 27mm

0∞C to +70∞C

DS21FT44N

12

300-BGA, 27mm x 27mm

-40∞C to +85∞C

DS21FF44

16

300-BGA, 27mm x 27mm

0∞C to +70∞C

DS21FF44N

16

300-BGA, 27mm x 27mm

-40∞C to +85∞C

1. DESCRIPTION

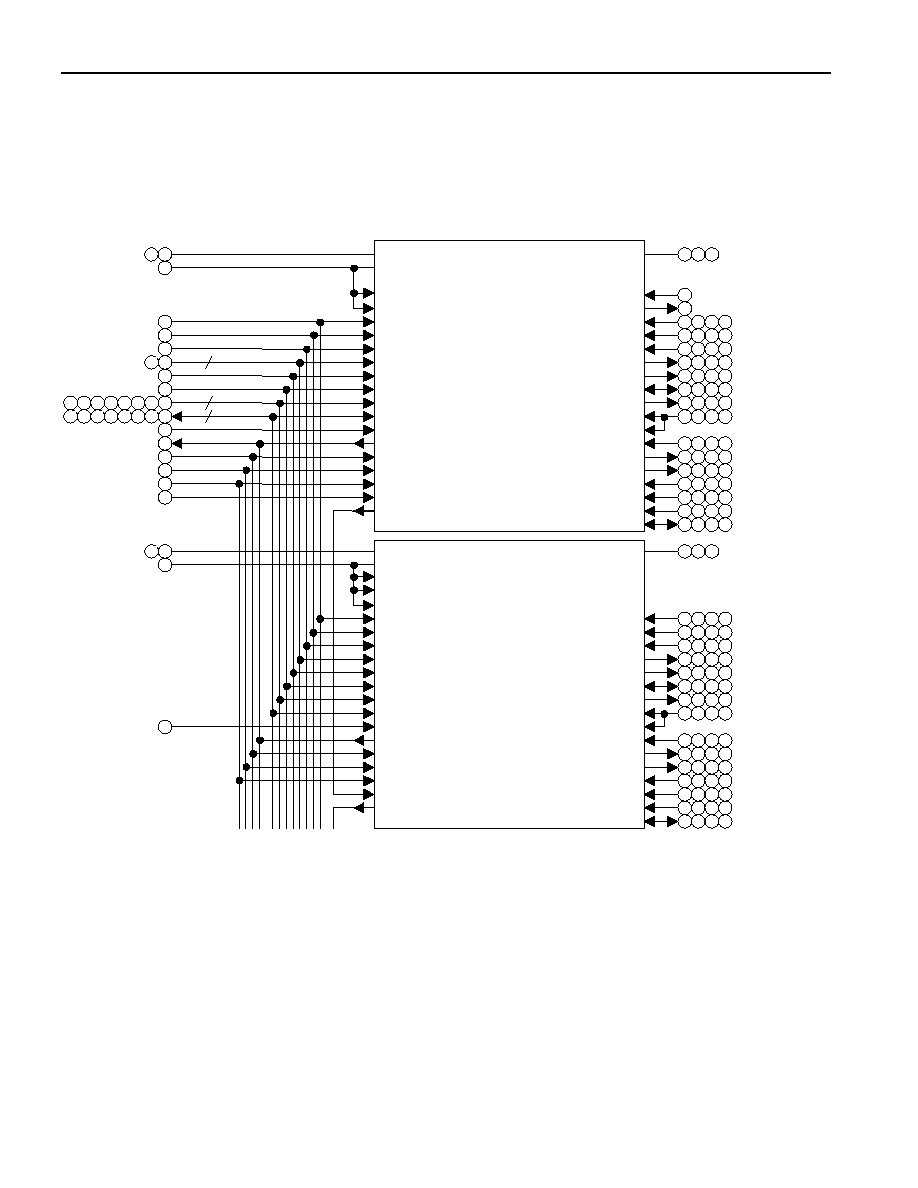

The 4 x 4 and 4 x 3 MCMs offer a high-density packaging arrangement for the DS21Q44 E1 enhanced

quad framer. Either three (DS21FT44) or four (DS21FF44) silicon die of these devices is packaged in a

multichip module (MCM) with the electrical connections as shown in Figure 1-1.

All of the functions available on the DS21Q44 are also available in the MCM packaged version.

However, in order to minimize package size, some signals have been deleted or combined. These

differences are detailed in Table 1-1. In the 4 x 3 (FT) version, the fourth quad framer is not populated

and thus all the signals to and from this fourth framer are absent and should be treated as no connects

(NC). Table 2-1 lists all of the signals on the MCM and it also lists the absent signals for the 4 x 3.

The availability of both a 12-channel and a 16-channel version allow the maximum framer density with

the lowest cost.

www.maxim-ic.com

DS21FT44/DS21FF44

4 x 3 12-Channel E1 Framer

4 x 4 16-Channel E1 Framer

DS21FT44/DS21FF44

2 of 117

Changes from Normal DS21Q44 Configuration

1) TSYSCLK and RSYSCLK are connected together.

2) These signals are not available:

RFSYNC/RLCLK/RLINK/RCHCLK/RMSYNC/RLOS/LOTC/TCHBLK/TLCLK/TLINK/TCHCLK

Figure 1-1. DS21FT44/DS21FF44 SCHEMATIC

8MCLK

CLKSI

RCLK1/2/3/4

RPOS1/2/3/4

RNEG1/2/3/4

RSER1/2/3/4

RSIG1/2/3/4

RSYNC1/2/3/4

RSYSCLK1/2/3/4

TCLK1/2/3/4

TNEG1/2/3/4

TPOS1/2/3/4

TSER1/2/3/4

TSIG1/2/3/4

TSSYNC1/2/3/4

TSYNC1/2/3/4

TSYSCLK1/2/3/4

TLINK0/1/2/3

JTDO

JTDI

JTCLK

JTMS

JTRST

INT*

FMS

D0 to D7

A0 to A7

RD*

WR*

BTS

MUX

CS*

FS0/FS1

TEST

Signals Not Connected &

Left Open Circuited Include:

RLOS/LOTC

RLINK

RLCLK

RCHCLK

RMSYNC

RFSYNC

TLCLK

TCHCLK

TCHBLK

DS21Q44 # 1

RCLK5/6/7/8

RPOS5/6/7/8

RNEG5/6/7/8

RSER5/6/7/8

RSIG5/6/7/8

RSYNC5/6/7/8

RSYSCLK5/6/7/8

TCLK5/6/7/8

TNEG5/6/7/8

TPOS5/6/7/8

TSER5/6/7/8

TSIG5/6/7/8

TSSYNC5/6/7/8

TSYNC5/6/7/8

TSYSCLK5/6/7/8

JTDO

JTDI

JTCLK

JTMS

JTRST

INT*

D0 to D7

A0 to A7

RD*

WR*

BTS

MUX

CS*

FS0/FS1

TEST

Signals Not Connected &

Left Open Circuited Include:

RLOS/LOTC

RLINK

RLCLK

RCHCLK

RMSYNC

RFSYNC

TLCLK

TCHCLK

TCHBLK

8MCLK

DS21Q44 # 2

2

8

8

See Connecting Page

RCHBLK5/6/7/8

RCHBLK1/2/3/4

DVDD

DVSS

DVSS

TLINK0/1/2/3

FMS

CLKSI

DVSS

DVSS

DVDD

DS21FT44/DS21FF44

3 of 117

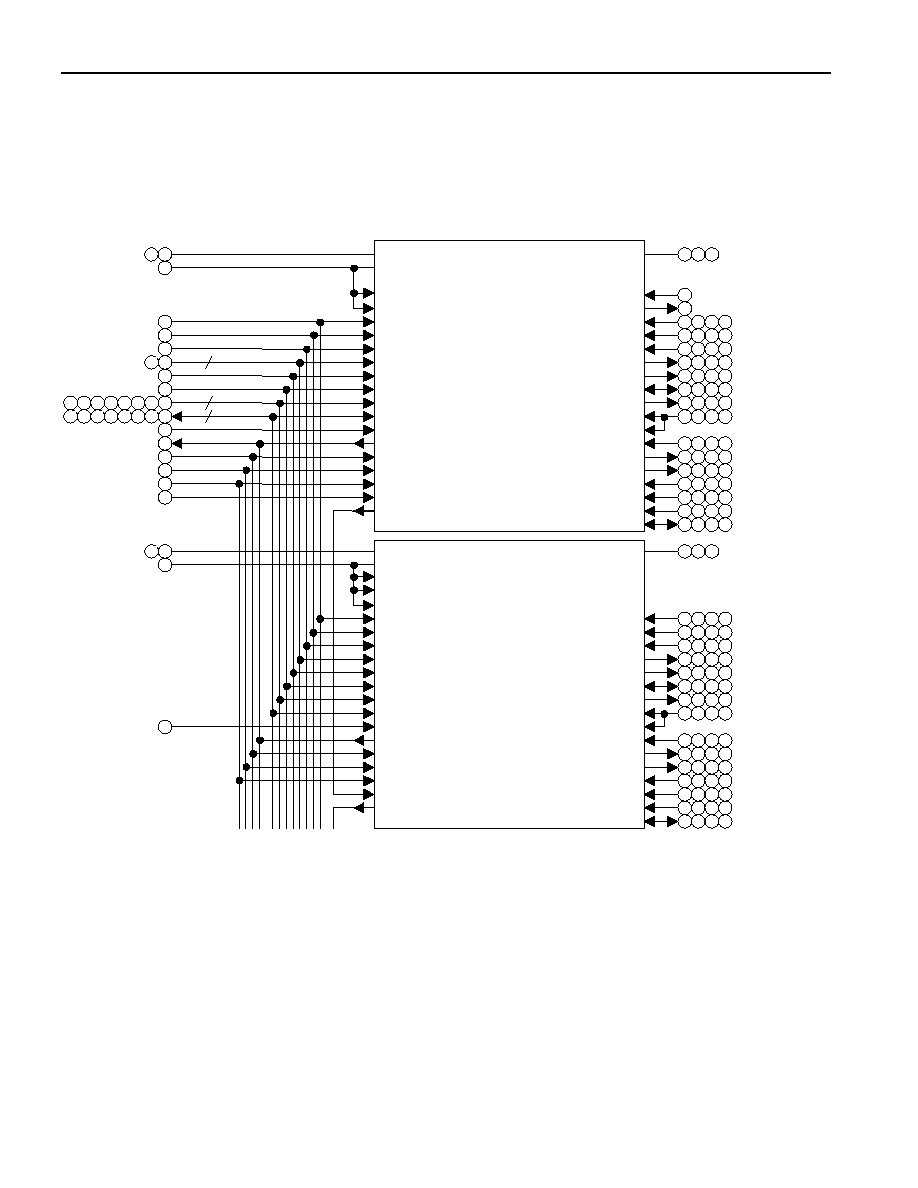

Figure 1-1. DS21FF44/DS21FT44 SCHEMATIC (continued)

CLKSI

RCLK9/10/11/12

RPOS9/10/11/12

RNEG9/10/11/12

RSER9/10/11/12

RSIG9/10/11/12

RSYNC9/10/11/12

RSYSCLK9/10/11/12

TCLK9/10/11/12

TNEG9/10/11/12

TPOS9/10/11/12

TSER9/10/11/12

TSIG9/10/11/12

TSSYNC9/10/11/12

TSYNC9/10/11/12

TSYSCLK9/10/11/12

TLINK0/1/2/3

JTDO

JTDI

JTCLK

JTMS

JTRST

INT*

FMS

D0 to D7

A0 to A7

RD*

WR*

BTS

MUX

CS*

FS0/FS1

TEST

Signals Not Connected &

Left Open Circuited Include:

RLOS/LOTC

RLINK

RLCLK

RCHCLK

RMSYNC

RFSYNC

TLCLK

TCHCLK

TCHBLK

8MCLK

DS21Q44 # 3

RCLK13/14/15/16

RPOS13/14/15/16

RNEG13/14/15/16

RSER13/14/15/16

RSIG13/14/15/16

RSYNC13/14/15/16

RSYSCLK13/14/15/16

TCLK13/14/15/16

TNEG13/14/15/16

TPOS13/14/15/16

TSER13/14/15/16

TSIG13/14/15/16

TSSYNC13/14/15/16

TSYNC13/14/15/16

TSYSCLK13/14/15/16

JTDO

JTDI

JTCLK

JTMS

JTRST

INT*

D0 to D7

A0 to A7

RD*

WR*

BTS

MUX

CS*

FS0/FS1

TEST

Signals Not Connected &

Left Open Circuited Include:

RLOS/LOTC

RLINK

RLCLK

RCHCLK

RMSYNC

RFSYNC

TLCLK

TCHCLK

TCHBLK

8MCLK

DS21Q44 # 4

RCHBLK13/14/15/16

RCHBLK9/10/11/12

DVDD

DVSS

DVSS

TLINK0/1/2/3

FMS

CLKSI

DVSS

DVSS

DVDD

See Connecting Page

jtdot

jtdof

The Fourth Quad Framer

is Not Populated

on the 12 Channel

DS21FT44

DS21FT44/DS21FF44

4 of 117

TABLE OF CONTENTS

1. DESCRIPTION....................................................................................................................................1

2. MCM PIN DESCRIPTION ................................................................................................................7

3. DS21FF44 (4 x 4) PCB LAND PATTERNS ....................................................................................15

4. DS21FT44 (4 x 3) PCB Land Pattern ..............................................................................................16

5. DS21Q42 DIE DESCRIPTION ........................................................................................................17

6. DS21Q44 INTRODUCTION ............................................................................................................18

7. DS21Q44 PIN FUNCTION DESCRIPTION ..................................................................................20

8. DS21Q44 REGISTER MAP .............................................................................................................27

9. PARALLEL PORT ...........................................................................................................................32

10. CONTROL, ID, AND TEST REGISTERS.....................................................................................32

11. STATUS AND INFORMATION REGISTERS .............................................................................42

12. ERROR COUNT REGISTERS........................................................................................................50

13. DS0 MONITORING FUNCTION ...................................................................................................53

14. SIGNALING OPERATION .............................................................................................................56

14.1 PROCESSOR-BASED SIGNALING ...........................................................................................56

14.2 HARDWARE-BASED SIGNALING ...........................................................................................59

15. PER≠CHANNEL CODE GENERATION AND LOOPBACK.....................................................60

15.1 TRANSMIT SIDE CODE GENERATION ..................................................................................60

15.1.1 Simple Idle Code Insertion and Per-Channel Loopback.......................................................60

15.1.2 Per-Channel Code Insertion..................................................................................................62

15.2 RECEIVE SIDE CODE GENERATION......................................................................................62

16. CLOCK BLOCKING REGISTERS................................................................................................63

17. ELASTIC STORES OPERATION..................................................................................................64

17.1 RECEIVE SIDE.............................................................................................................................65

17.2 TRANSMIT SIDE .........................................................................................................................65

DS21FT44/DS21FF44

5 of 117

18. ADDITIONAL (Sa) AND INTERNATIONAL (Si) BIT OPERATION ......................................65

18.1 HARDWARE SCHEME ...............................................................................................................65

18.2 INTERNAL REGISTER SCHEME BASED ON DOUBLE≠FRAME ........................................66

18.3 INTERNAL REGISTER SCHEME BASED ON CRC4 MULTIFRAME...................................68

19. HDLC CONTROLLER FOR THE SA BITS OR DS0 ..................................................................70

19.1 GENERAL OVERVIEW ..............................................................................................................70

19.2 HDLC STATUS REGISTERS ......................................................................................................71

19.3 BASIC OPERATION DETAILS ..................................................................................................72

19.4 HDLC REGISTER DESCRIPTION .............................................................................................73

20. INTERLEAVED PCM BUS OPERATION....................................................................................81

21. JTAG-BOUNDARY SCAN ARCHITECTURE AND TEST ACCESS PORT...........................84

21.1 DESCRIPTION .............................................................................................................................84

21.2 TAP CONTROLLER STATE MACHINE ...................................................................................85

21.3 INSTRUCTION REGISTER AND INSTRUCTIONS .................................................................87

21.4 TEST REGISTERS .......................................................................................................................89

22. TIMING DIAGRAMS.......................................................................................................................93

23. OPERATING PARAMETERS ......................................................................................................103

24. MCM PACKAGE DIMENSIONS .................................................................................................116