General Description

The MAX104/MAX106/MAX108 evaluation kits (EV kits)

are designed to simplify evaluation of the devices' ana-

log-to-digital converters (ADCs). Each EV kit contains

all circuitry necessary to evaluate the dynamic perfor-

mance of these ultra-high-speed converters, including

the power-supply generation for the PECL termination

voltage (PECLV

TT

). Since the design combines high-

speed analog and digital circuitry, the board layout

calls for special precautions and design features.

Connectors for the power supplies (V

CC

A/V

CC

I, V

CC

D,

V

CC

O, V

EE

), SMA connectors for analog and clock

inputs (VIN+, VIN-, CLK+, CLK-), and all digital PECL

outputs simplify connection to the EV kit. The four-layer

board layout (GETekTM material) is optimized for best

dynamic performance of the MAX104 family.

The EV kits come with a MAX104/MAX106/MAX108

installed on the board with a heatsink attached for oper-

ation over the full commercial temperature range.

Features

o

50

Clock and Analog Inputs Through SMA

Coaxial Connectors

o

�250mV Input Signal Range

o

Demultiplexed Differential PECL Outputs

o

On-Board Generation of PECL Termination

Voltage (PECLV

TT

)

o

On-Board Generation of ECL Termination Voltage

(ECLV

TT

)

o

Separate Analog and Digital Power and Ground

Connections with Optimized Four-Layer PCB

o

Square-Pin Headers for Easy Connection of Logic

Analyzer to Digital Outputs

o

Fully Assembled and Tested

Evaluate: MAX104/MAX106/MAX108

MAX104/MAX106/MAX108 Evaluation Kits

________________________________________________________________

Maxim Integrated Products

1

19-1503; Rev 0; 6/99

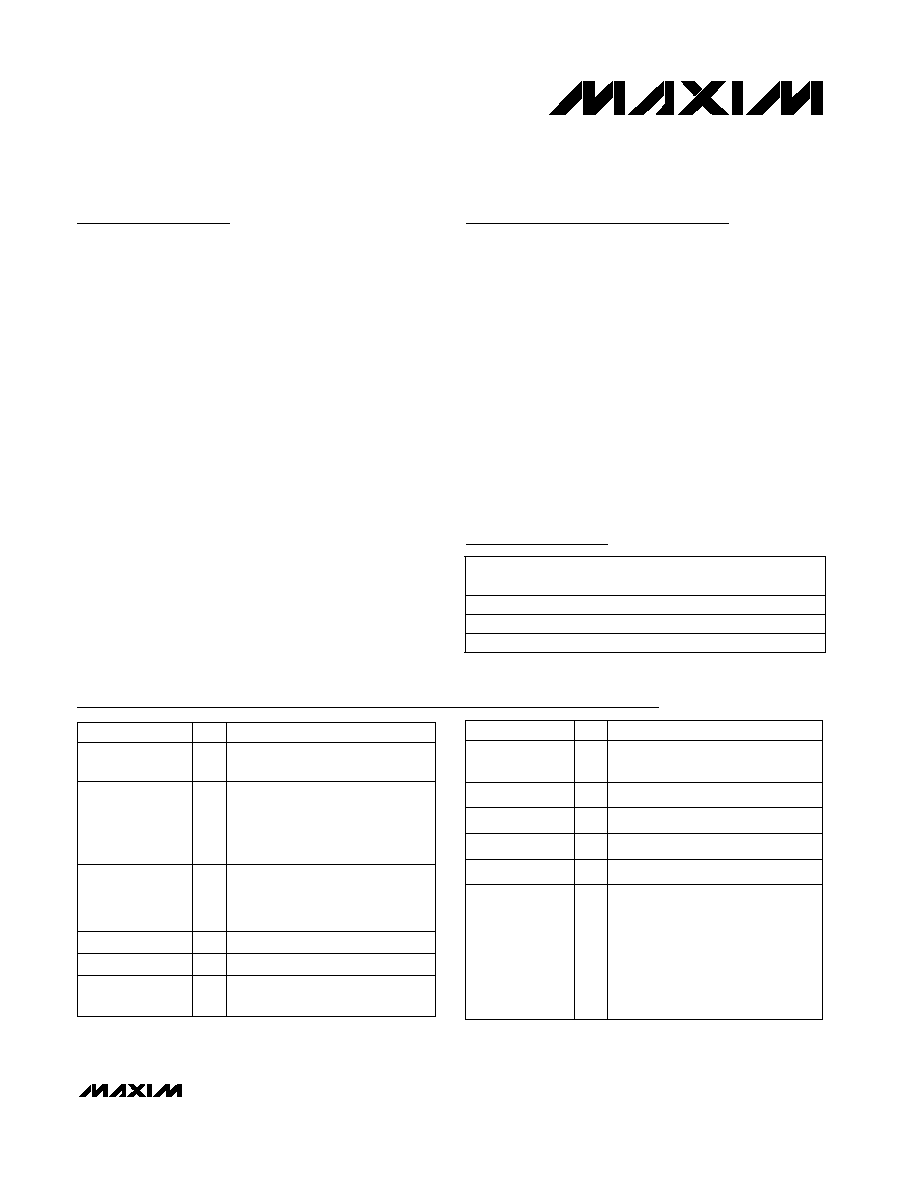

Component List

PART

MAX104

EVKIT

MAX106

EVKIT

0�C to +70�C

0�C to +70�C

TEMP.

RANGE

PIN-

PACKAGE

192 ESBGA

192 ESBGA

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800.

For small orders, phone 1-800-835-8769.

Ordering Information

Not populated; see text for descrip-

tion of reset input operation.

2

R3, R4

DESIGNATION

10k

potentiometer

1

R2

1N5819 Schottky diode

1

D1

47pF �10% ceramic capacitors

(0402)

20

C3�C6, C15, C16,

C22�C25,

C33�C37,

C42�C45, C50

0.01�F �10% ceramic capacitors

(0603)

30

C2, C7�C12, C14,

C17, C18, C19,

C21, C26�C30,

C32, C41, C47,

C49, C51�C59

10�F �10%, 16V tantalum caps

AVX TAJD106D016

7

C1, C13, C20, C31,

C40, C46, C48

DESCRIPTION

QTY

MAX108

EVKIT*

0�C to +70�C

192 ESBGA

SAMPLING

RATE

1Gsps

600Msps

1.5Gsps

GETek is trademark of GE Electromaterials.

49.9

�1% resistors (0603)

38

R5�R38,

R44�R47

DESIGNATION

DESCRIPTION

QTY

2-pin headers

41

JU2, JU4, JU5,

JUA0- to JUA7-,

JUA0+ to JUA7+,

JUP0- to JUP7-,

JUP0+ to JUP7+,

JUOR+, JUOR-,

JUDR-, JUDR+,

JURO-, JURO+

3-pin headers

5

JU3, JU6�JU9

SMA connectors (edge mounted)

10

J1�J10

158

�1% resistors (0603)

2

R52, R54

243

�1% resistors (0603)

2

R51, R53

*

Future product--contact factory for availability.

_________________________Quick Start

The EV kit is delivered fully assembled, tested, and

sealed in an antistatic bag. To ensure proper operation,

open the antistatic bag only at a static-safe work area

and follow the instructions below.

Do not turn on the

power supplies until all power connections to the

EV kit are established.

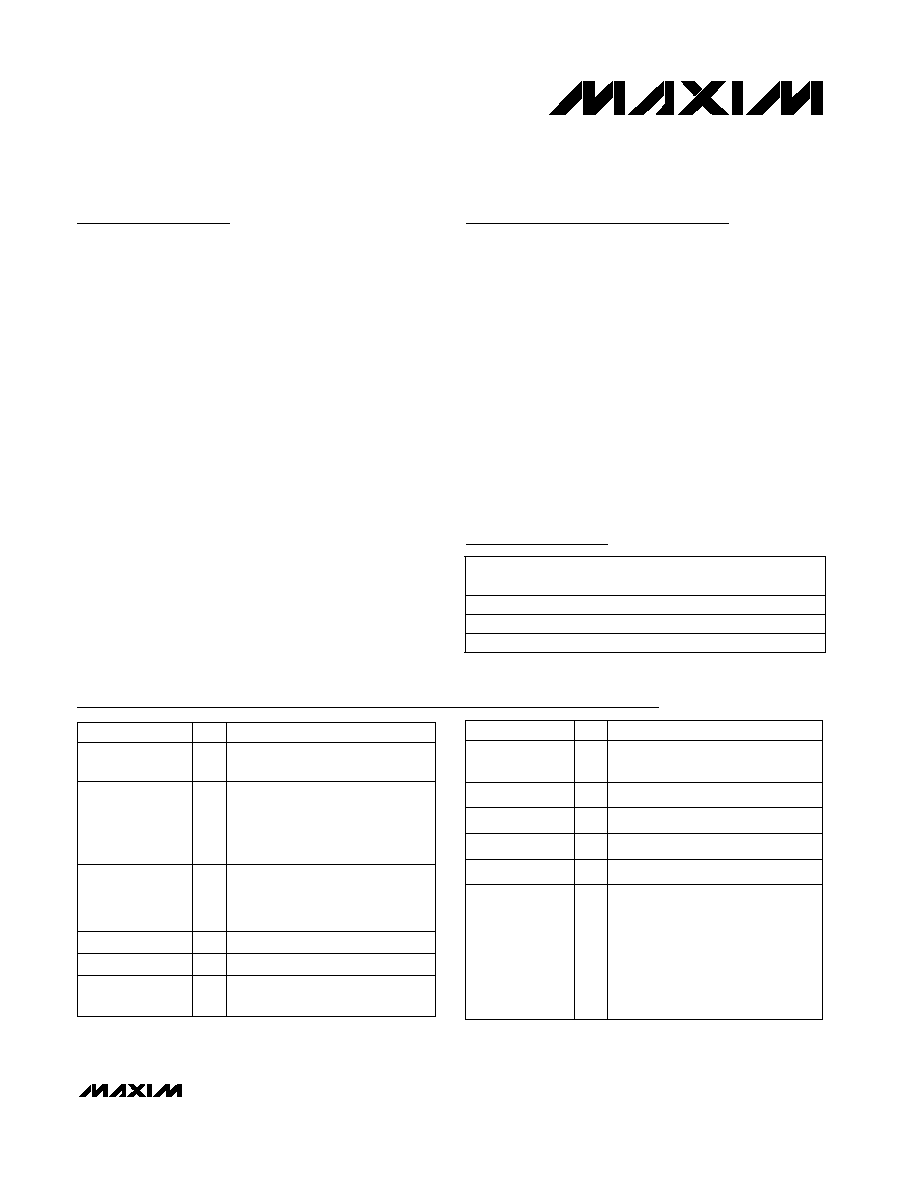

Figure 1 shows a typical evalu-

ation setup with differential analog inputs and single-

ended sine-wave (CLK- is 50

reverse-terminated to

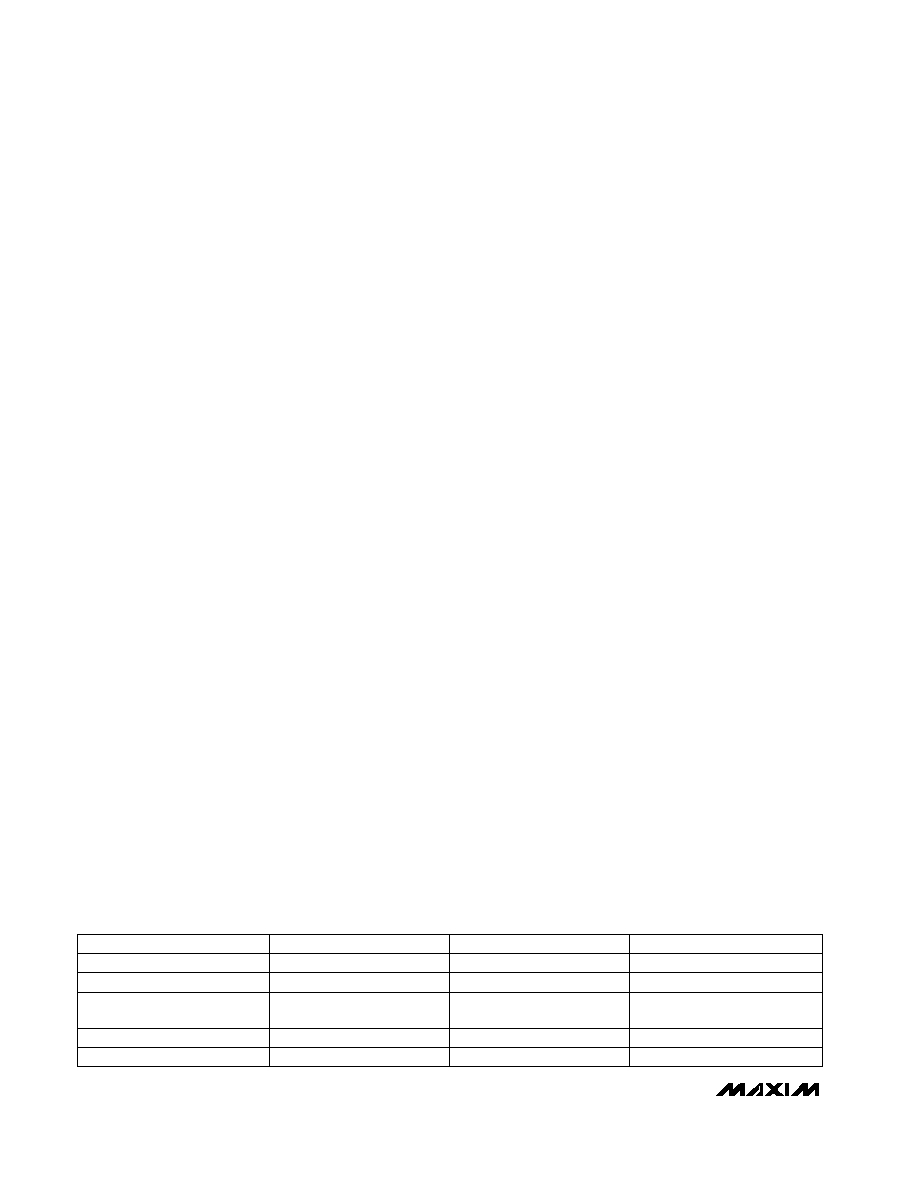

GNDI) clock drive. Figure 2 shows a typical evaluation

setup with single-ended analog inputs (VIN- is 50

reverse-terminated to GNDI) and a single-ended sine-

wave clock drive.

1) Connect a -5V power supply capable of providing

-250mA to the pad marked V

EE

. Connect the sup-

ply's ground to the GNDI pad.

Set the current limit

to 500mA or less.

2) Connect a +5V power supply capable of providing

600mA to the V

CC

I pad. Connect the supply's

ground to the GNDI pad.

3) Connect a +5V power supply capable of providing

250mA to the V

CC

D pad. Connect the supply's

ground to the GNDD pad.

4) Connect a +3.3V or +5V power supply capable of

providing approximately 600mA to the V

CC

O pad.

Connect the supply's ground to the GNDD pad.

5) Connect GNDI to GNDD at the power supplies.

6) Connect an RF source with low phase jitter, such as

an HP8662A (up to 1.28GHz) or an HP8663A (up to

2.56GHz), to clock inputs CLK- and CLK+. For sin-

gle-ended clock inputs, feed a +4dBm (500mV

amplitude) power level from the signal generator

into the CLK+ input and terminate the unused CLK-

input with 50

to GNDI.

7) Connect a �225mV (approximately -1dB below FS)

sine-wave test signal to the analog inputs. Use

VIN+ and VIN- through a balun if the test signal is

differential, or either VIN+ or VIN- if the signal is sin-

gle-ended (see the sections

Single-Ended Analog

Inputs and Differential Analog Inputs in the devices'

data sheets). For best results, use a narrow band-

pass filter designed for the frequency of interest to

reduce the harmonic distortion from the signal gen-

erator.

8) Connect a logic analyzer, such as an HP16500C

with an HP16517A plug-in card for monitoring all 16

output channels (8 channels for primary and 8

channels for auxiliary outputs) of the device.

9) Connect the logic analyzer clock to the DREADY+

output on the EV kit, and set the logic analyzer to

trigger on the falling edge of the acquisition clock.

Set the logic analyzer's threshold voltage to the

V

CC

O supply voltage -1.3V. For example, if V

CC

O =

+3.3V, the threshold voltage should be set to

+2.0V.

10) Turn on the supplies and signal sources. Capture

the digitized outputs from the ADC with the logic

analyzer and transfer the digital record to a PC for

data analysis.

Evaluate: MAX104/MAX106/MAX108

MAX104/MAX106/MAX108 Evaluation Kits

2

_______________________________________________________________________________________

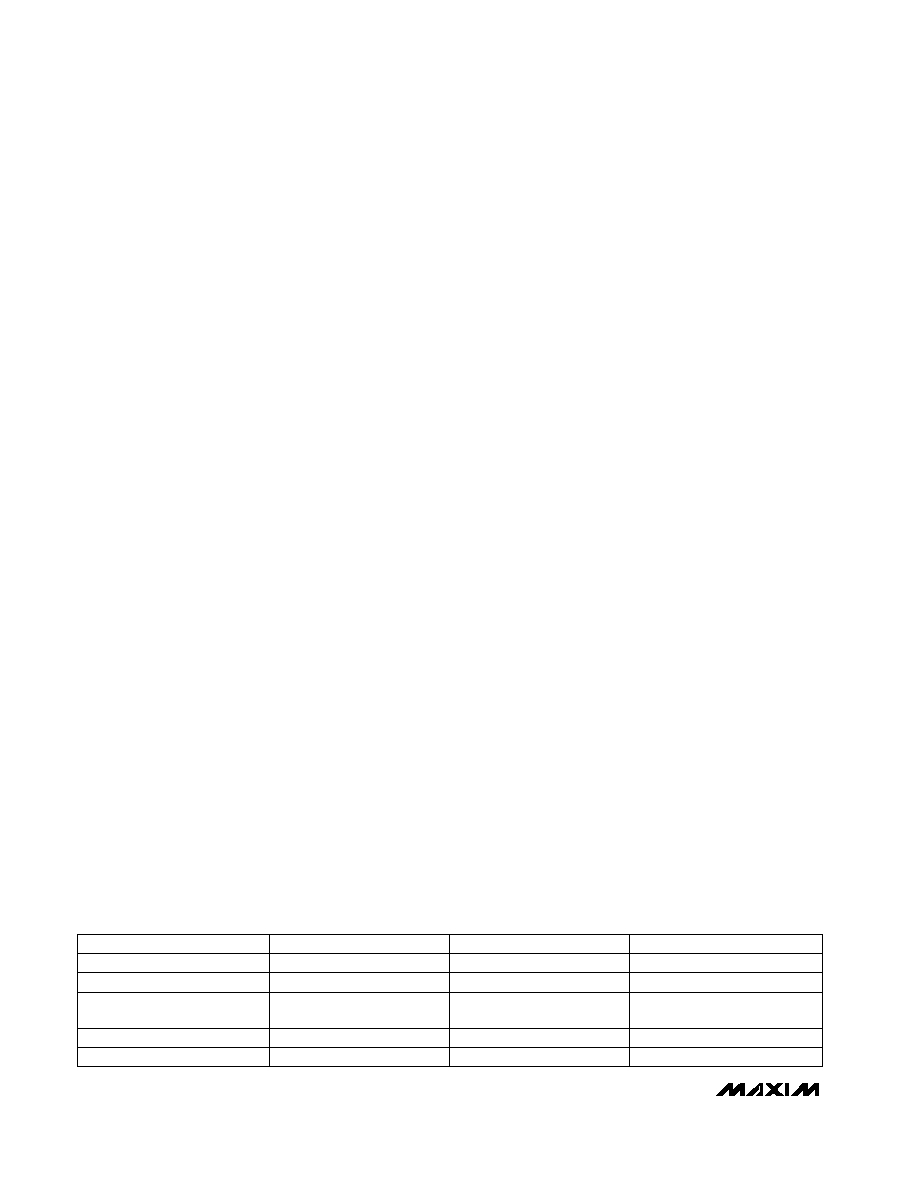

Component List (continued)

Shunts

7

None

Test points

24

V

CC

O, V

CC

D,

GNDD, PECLV

TT

,

GNDA, V

CC

A,

V

CC

I, GNDI, V

EE

,

ECLV

TT

Protective feet

4

None

Heatsink

International Electronic Research

Corp. BDN09-3CB/A01

1

None

MAX104CHC, MAX106CHC, or

MAX108CHC (192-contact ESBGATM)

1

U1

LM2991S, low-dropout adjustable

linear regulator

2

U3, U4

MAX104EVKIT circuit board

1

None

MAX104, MAX106, or MAX108 data

sheet

1

None

DESIGNATION

DESCRIPTION

QTY

ESBGA is a trademark of Amkor/Anam.

Evaluate: MAX104/MAX106/MAX108

MAX104/MAX106/MAX108 Evaluation Kits

_______________________________________________________________________________________

3

MAX104

MAX106

MAX108

EV KIT

BALUN

HP8662/3A

SINE-WAVE SOURCE

PHASE

LOCKED

f

SAMPLE

, + 4dBm

EXTERNAL 50

TERMINATION TO GNDI

HP8662/3A

SINE-WAVE SOURCE

POWER

SUPPLIES

GNDD

+5V ANALOG

VIN+

VIN-

CLK+

CLK-

16 DATA

DREADY+

-5V ANALOG

+5V DIGITAL

+3.3V DIGITAL

GNDI

HP16500C

DATA ANALYSIS

SYSTEM

GPIB

PC

BPF

Figure 1. Typical Evaluation Setup with Differential Analog Inputs and Single-Ended Clock Drive

MAX104

MAX106

MAX108

EV KIT

HP8662/3A

SINE-WAVE SOURCE

PHASE

LOCKED

f

SAMPLE

, + 4dBm

EXTERNAL 50

TERMINATION TO GNDI

EXTERNAL 50

TERMINATION

TO GNDI

HP8662/3A

SINE-WAVE SOURCE

POWER

SUPPLIES

GNDD

+5V ANALOG

VIN+

VIN-

CLK+

CLK-

16 DATA

DREADY+

-5V ANALOG

+5V DIGITAL

+3.3V DIGITAL

GNDI

HP16500C

DATA ANALYSIS

SYSTEM

GPIB

PC

BPF

Figure 2. Typical Evaluation Setup with Single-Ended Analog Inputs and Single-Ended Clock Drive

Evaluate: MAX104/MAX106/MAX108

MAX104/MAX106/MAX108 Evaluation Kits

4

_______________________________________________________________________________________

_______________Detailed Description

Clock Input Requirements

The MAX104/MAX106/MAX108 feature clock inputs

designed for either single-ended or differential opera-

tion with very flexible input drive requirements. Each

clock input is terminated with an on-chip, laser-trimmed

50

resistor to CLKCOM (clock termination return). The

traces from the SMA inputs to the high-speed data con-

verter are 50

microstrip transmission lines.

The CLKCOM termination voltage may be connected

anywhere between ground and -2V for compatibility

with standard ECL drive levels. The side-launched SMA

connectors for the clock signals are located at the

lower left corner of the EV board and are labeled J3

(CLK+) and J4 (CLK-).

An on-board bias generator, located between the ana-

log and clock inputs, creates a -2V termination voltage

(ECLV

TT

) for operation with ECL clock sources. The

voltage is generated by an LM2991 voltage regulator

operated from the board's -5V V

EE

power supply. To

enable this ECLV

TT

bias generator, first remove short-

ing jumper JU2, then move jumper JU3 into its ON

position.

The voltage regulator has a shutdown control that

requires a TTL logic-high level to enter the shutdown

state. This logic level is derived from the +5V analog

supply (V

CC

I). The EV kits are delivered with the

ECLV

TT

bias generator turned off and CLKCOM tied to

GNDI (JU2 installed).

NOTE: If the regulator's shutdown logic level is not

present (V

CC

I on first) before the V

EE

supply is

turned on, the regulator will momentarily turn on

until the V

CC

I supply is energized. If JU2 is installed,

this will momentarily short the regulator's output to

ground. The regulator is short-circuit protected so

no damage will result. The regulator is further pro-

tected by limiting the V

EE

supply current to 500mA.

Single-Ended Clock Inputs

(Sine-Wave Drive)

To obtain the lowest jitter clock drive, AC- or DC-couple

a low-phase-noise sine-wave source into a single clock

input. Clock amplitudes of up to 1V (2Vp-p or +10dBm)

can be accommodated with CLKCOM connected to

GNDI.

The dynamic performance of the data converter is

essentially unaffected by clock-drive power levels from

-10dBm to +10dBm (100mV to 1V clock signal ampli-

tude). The dynamic performance specifications are

measured with a single-ended clock drive of +4dBm

(500mV clock signal amplitude). To avoid saturation of

the input amplifier stage, limit the clock power level to a

maximum of +10dBm.

Differential Clock Inputs (ECL Drive)

The MAX104/MAX106/MAX108 clock inputs may also

be driven with standard ground-referenced ECL logic

levels by using the on-board ECLV

TT

-2V bias genera-

tor as described above. It is also possible to drive the

clock inputs with positive supply referenced (PECL)

levels if the clock inputs are AC-coupled. With AC-cou-

pled clock inputs, the CLKCOM termination voltage

should be grounded. Single-ended DC-coupled ECL

drive is possible as well, if the undriven clock input is

tied to the ECL V

BB

voltage (-1.3V nominal).

Analog Input Requirements

The analog inputs to the ADC on the EV board are pro-

vided by two side-launch SMA connectors located on

the middle left side of the EV kit. They are labeled J1

(VIN+) and J2 (VIN-). The analog inputs are terminated

on-chip with precision laser-trimmed 50

NiCr resistors

to GNDI. Although the analog (and clock) inputs are

ESD protected, good ESD practices should always be

observed. The traces from the SMA inputs to the device

are 50

microstrip transmission lines. The analog

inputs can be driven either single-ended or differential.

Optimal performance is obtained with differential input

drive due to reduction of even-order harmonic distor-

tion. Table 1 represents single-ended input drive, and

Table 2 displays differential input drive.

Table 1. Input Setup and Output Code Results for Single-Ended Analog Inputs

0V

+250mV - 1LSB

0V

+250mV

VIN+

VIN-

0

1

OVERRANGE BIT

11111111

11111111 (full scale)

OUTPUT CODE

0

0V

-250mV + 1LSB

0

00000001

01111111

toggles 10000000

0V

0V

0

0V

-250mV

00000000 (zero scale)

Evaluate: MAX104/MAX106/MAX108

MAX104/MAX106/MAX108 Evaluation Kits

_______________________________________________________________________________________

5

Internal Reference

The MAX104 family features an on-chip +2.5V precision

bandgap reference, which can be used by shorting

jumper JU5 to connect REFOUT with REFIN. If

required, REFOUT can also source up to 2.5mA to sup-

ply other peripheral circuitry.

To use an external reference, remove the shorting

jumper on JU5 and connect the new reference voltage

source to the REFIN side of JU5. Leave the REFOUT

side of JU5 floating. Connect the ground of the external

reference to GNDI on the EV kit. REFIN accepts an

input voltage range of +2.3V to +2.7V.

CAUTION: With an external reference connected,

JU5 must not be installed at any time to avoid dam-

aging the internal reference with the external refer-

ence supply.

Offset Adjust

The devices also provide a control input (VOSADJ) to

eliminate any offset from additional preamplifiers dri-

ving the ADC. The VOSADJ control input is a self-

biased voltage divider from the internal +2.5V precision

reference. Under normal-use conditions, the control

input is left floating.

The EV kits include a 10k

potentiometer that is biased

from the ADC's +2.5V reference. The wiper of the

potentiometer connects to the VOSADJ control input

through JU4. To enable the offset-adjust function, install

a shorting jumper on JU4 and adjust potentiometer R2

while observing the resulting offset in the reconstructed

digital outputs. The offset-adjust potentiometer offers

about �5.5LSB of adjustment range. The EV kits are

shipped from the factory without a shorting jumper

installed on JU4.

Primary and Auxiliary

PECL Outputs

All PECL outputs on the EV kits are powered from the

V

CC

O power supply, which may be operated from any

voltage between +3.0V to +5.0V for flexible interfacing

with either +3.3V or +5V systems. The nominal V

CC

O

supply voltage is +3.3V.

The PECL outputs are standard open-emitter types and

require external 50

termination resistors to the

PECLV

TT

voltage for proper biasing. The termination

resistors are located at the far end of each 50

microstrip transmission line, very close to the square

pin headers for the logic analyzer interface. Every EV

board is delivered with the PECL termination resistors

installed on the back side of the board. Each output

links to a 0.100 inch square 2-pin header to ease the

connection to a high-speed logic analyzer such as

Hewlett Packard's HP16500C.

To capture the digital data from the device in demulti-

plexed 1:2 format, each of the 16 channels from the

logic analyzer is connected to the eight primary (P0 to

P7) and eight auxiliary (A0 to A7) outputs. The ADC

provides differential PECL outputs, but most logic ana-

lyzers (such as the HP16500C) have single-ended

acquisition pods. Connect all single-ended logic ana-

lyzer pods to the same phase (either "+" or "-") of the

PECL outputs.

Data Ready (DREADY) Output

The clock pod from the logic analyzer should be con-

nected to the DREADY+ output at JUDR+ on the EV

kits. Since both the primary and auxiliary outputs

change on the rising edge of DREADY+, set the logic

analyzer to trigger on the falling edge. The DREADY

and data outputs are internally time-aligned, which

places the falling edge of DREADY+ in the approximate

center of the valid data window, resulting in the maxi-

mum setup and hold time for the logic analyzer. Set the

logic analyzer's threshold voltage to V

CC

O - 1.3V. For

example, if V

CC

O is +3.3V, the threshold voltage

should be set to +2.0V. The sample offset (trigger

delay) of the logic analyzer should be set to 0ps under

these conditions.

It is also possible to use the DREADY- output for the

acquisition clock. Under this condition, set the logic

analyzer to trigger on the rising edge of the clock.

Table 3 summarizes the digital outputs and their func-

tions.

Table 2. Input Setup and Output Code Results for Differential Analog Inputs

0

-125mV + 0.5LSB

+125mV - 0.5LSB

1

OVERRANGE BIT

11111111

11111111 (full scale)

-125mV

+125mV

OUTPUT CODE

0

+125mV - 0.5LSB

-125mV + 0.5LSB

0

00000001

01111111

toggles 10000000

0V

0V

0

+125mV

-125mV

00000000 (zero scale)

VIN+

VIN-