General Description

The MAX1277/MAX1279 are low-power, high-speed, seri-

al-output, 12-bit, analog-to-digital converters (ADCs) with

an internal reference that operates at up to 1.5Msps.

These devices feature true-differential inputs, offering bet-

ter noise immunity, distortion improvements, and a wider

dynamic range over single-ended inputs. A standard

SPITM/QSPITM/MICROWIRETM interface provides the clock

necessary for conversion. These devices easily interface

with standard digital signal processor (DSP) synchronous

serial interfaces.

The MAX1277/MAX1279 operate from a single +2.7V to

+3.6V supply voltage. The MAX1277/MAX1279 include a

2.048V internal reference. The MAX1277 has a unipolar

analog input, while the MAX1279 has a bipolar analog

input. These devices feature a partial power-down mode

and a full power-down mode for use between conver-

sions, which lower the supply current to 2mA (typ) and

1µA (max), respectively. Also featured is a separate

power-supply input (V

L

), which allows direct interfacing to

+1.8V to V

DD

digital logic. The fast conversion speed,

low-power dissipation, excellent AC performance, and DC

accuracy (±1 LSB INL) make the MAX1277/MAX1279

ideal for industrial process control, motor control, and

base-station applications.

The MAX1277/MAX1279 come in a 12-pin TQFN pack-

age, and are available in the commercial (0∞C to +70∞C)

and extended (-40∞C to +85∞C) temperature ranges.

Applications

Data Acquisition

Communications

Bill Validation

Portable Instruments

Motor Control

Features

1.5Msps Sampling Rate

Only 22mW (typ) Power Dissipation

Only 1µA (max) Shutdown Current

High-Speed, SPI-Compatible, 3-Wire Serial Interface

68.5dB S/(N + D) at 525kHz Input Frequency

Internal True-Differential Track/Hold (T/H)

Internal 2.048V Reference

No Pipeline Delays

Small 12-Pin TQFN Package

MAX1277/MAX1279

1.5Msps, Single-Supply, Low-Power, True-

Differential, 12-Bit ADCs with Internal Reference

________________________________________________________________ Maxim Integrated Products

1

12

AIN+

11

N.C.

10

SCLK

4

5

N.C.

6

GND

1

2

REF

3

9

8

7

RGND

CNVST

DOUT

V

L

MAX1277

MAX1279

AIN-

V

DD

TQFN

TOP VIEW

PART

TEMP RANGE

PIN-

PACKAGE

INPUT

MAX1277ACTC-T

0

∞C to +70∞C 12 TQFN-12

Unipolar

MAX1277BCTC-T

0

∞C to +70∞C 12 TQFN-12

Unipolar

MAX1277AETC-T

-40

∞C to +85∞C 12 TQFN-12

Unipolar

MAX1277BETC-T

-40

∞C to +85∞C 12 TQFN-12

Unipolar

MAX1279ACTC-T

0

∞C to +70∞C 12 TQFN-12

Bipolar

MAX1279BCTC-T

0

∞C to +70∞C 12 TQFN-12

Bipolar

MAX1279AETC-T

-40

∞C to +85∞C 12 TQFN-12

Bipolar

MAX1279BETC-T

-40

∞C to +85∞C 12 TQFN-12

Bipolar

Pin Configuration

Ordering Information

MAX1277

MAX1279

DOUT

AIN+

4.7

µF

10

µF

10

µF

+2.7V TO +3.6V

0.01

µF

0.01

µF

0.01

µF

+1.8V TO V

DD

AIN-

REF

V

DD

DIFFERENTIAL

INPUT

VOLTAGE

RGND

V

L

GND

CNVST

SCLK

µC/DSP

+

-

Typical Operating Circuit

19-3365; Rev 0; 8/04

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

SPI/QSPI are trademarks of Motorola, Inc.

MICROWIRE is a trademark of National Semiconductor Corp.

MAX1277/MAX1279

1.5Msps, Single-Supply, Low-Power, True-

Differential, 12-Bit ADCs with Internal Reference

2

_______________________________________________________________________________________

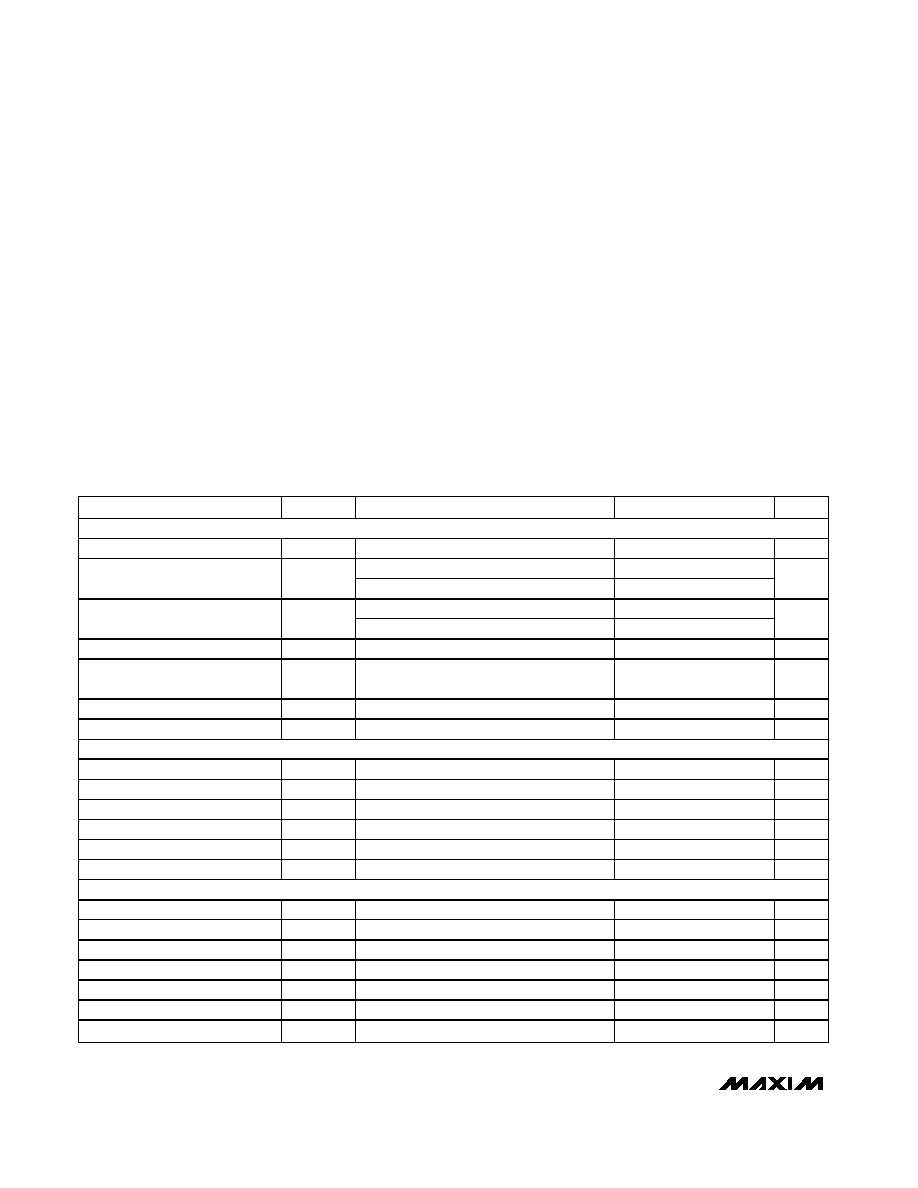

ABSOLUTE MAXIMUM RATINGS

ELECTRICAL CHARACTERISTICS

(V

DD

= +2.7V to +3.6V, V

L

= V

DD

, f

SCLK

= 24MHz, 50% duty cycle, T

A

= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at

T

A

= +25∞C.)

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

V

DD

to GND ..............................................................-0.3V to +6V

V

L

to GND ................-0.3V to the lower of (V

DD

+ 0.3V) and +6V

Digital Inputs

to GND .................-0.3V to the lower of (V

DD

+ 0.3V) and +6V

Digital Output

to GND ....................-0.3V to the lower of (V

L

+ 0.3V) and +6V

Analog Inputs and

REF to GND..........-0.3V to the lower of (V

DD

+ 0.3V) and +6V

RGND to GND .......................................................-0.3V to +0.3V

Maximum Current into Any Pin............................................50mA

Continuous Power Dissipation (T

A

= +70∞C)

12-Pin TQFN (derate 16.9mW/∞C above +70∞C) ......1349mW

Operating Temperature Ranges

MAX127_ _ CTC.................................................0∞C to +70∞C

MAX127_ _ ETC ..............................................-40∞C to +85∞C

Junction Temperature ......................................................+150∞C

Storage Temperature Range .............................-60∞C to +150∞C

Lead Temperature (soldering, 10s) .................................+300∞C

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

DC ACCURACY

Resolution

12

Bits

MAX127_A

-1.0

+1.0

Relative Accuracy (Note 1)

INL

MAX127_B

-1.5

+1.5

LSB

MAX127_A

-1.0

+1.0

Differential Nonlinearity (Note 2)

DNL

MAX127_B

-1.0

+1.5

LSB

Offset Error

±8.0

LSB

Offset-Error Temperature

Coefficient

±1

ppm/∞C

Gain Error

Offset nulled

±6.0

LSB

Gain Temperature Coefficient

±2

ppm/∞C

DYNAMIC SPECIFICATIONS

(f

IN

= 525kHz sine wave, V

IN

= V

REF

, unless otherwise noted.)

Signal-to-Noise Plus Distortion

SINAD

66

68.5

dB

Total Harmonic Distortion

THD

Up to the 5th harmonic

-80

-76

dB

Spurious-Free Dynamic Range

SFDR

-83

-76

dB

Intermodulation Distortion

IMD

f

IN1

= 250kHz, f

IN2

= 300kHz

-78

dB

Full-Power Bandwidth

-3dB point, small-signal method

15

MHz

Full-Linear Bandwidth

S/(N + D) > 68dB, single ended

1.2

MHz

CONVERSION RATE

Minimum Conversion Time

t

CONV

(Note 3)

0.667

µs

Maximum Throughput Rate

1.5

Msps

M i ni m um Thr oug hp ut Rate

( N ote 4)

10

ksps

Track-and-Hold Acquisition Time

t

ACQ

(Note 5)

125

ns

Aperture Delay

5

ns

Aperture Jitter

(Note 6)

30

ps

External Clock Frequency

f

SCLK

(Note 7)

24

MHz

MAX1277/MAX1279

1.5Msps, Single-Supply, Low-Power, True-

Differential, 12-Bit ADCs with Internal Reference

_______________________________________________________________________________________

3

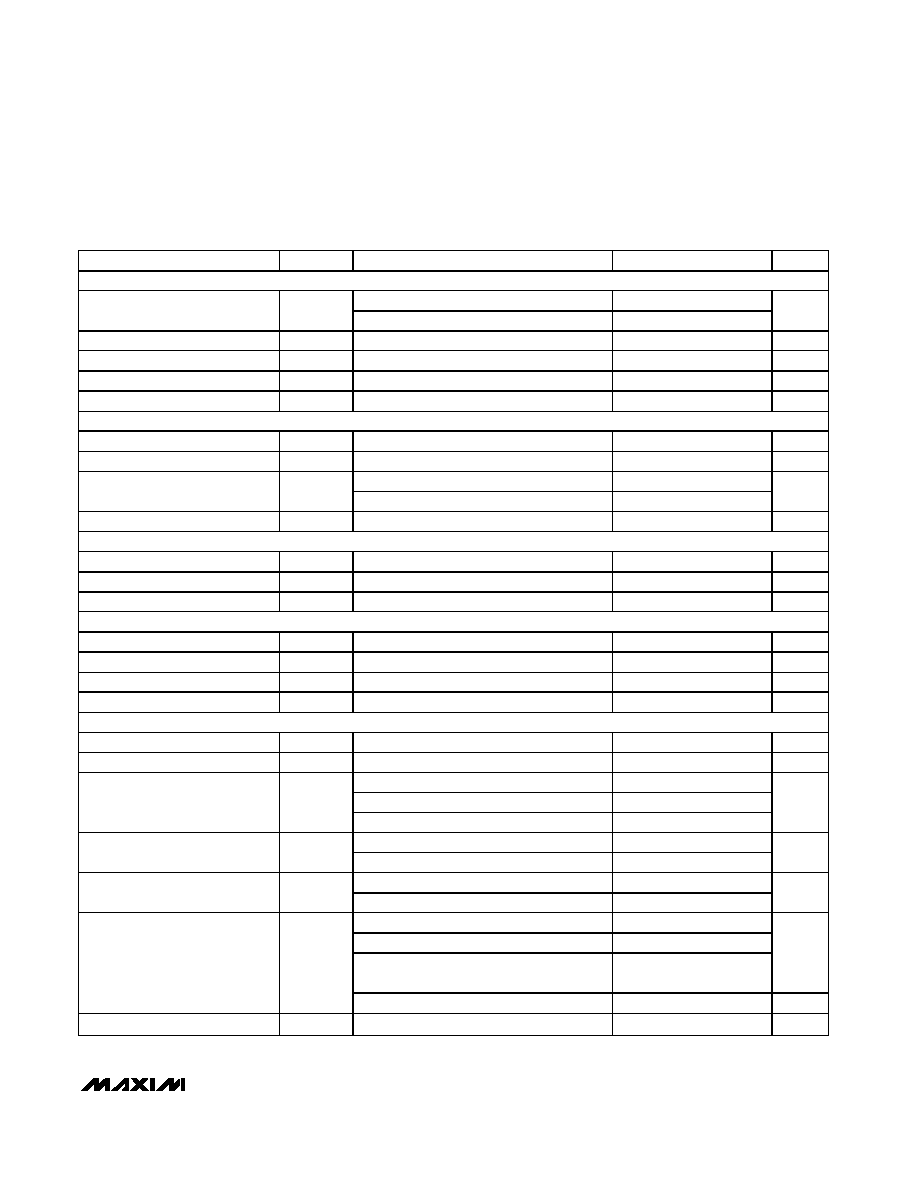

ELECTRICAL CHARACTERISTICS (continued)

(V

DD

= +2.7V to +3.6V, V

L

= V

DD

, f

SCLK

= 24MHz, 50% duty cycle, T

A

= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at

T

A

= +25∞C.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

ANALOG INPUTS (AIN+, AIN-)

AIN+ - AIN-, MAX1277

0

V

REF

Differential Input Voltage Range

V

IN

AIN+ - AIN-, MAX1279

-V

REF

/ 2

+V

REF

/ 2

V

Absolute Input Voltage Range

0

V

DD

V

DC Leakage Current

±1

µA

Input Capacitance

Per input pin

16

pF

Input Current (Average)

Time averaged at maximum throughput rate

75

µA

REFERENCE OUTPUT (REF)

REF Output Voltage Range

Static, T

A

= +25∞C

2.038

2.048

2.058

V

Voltage Temperature Coefficient

±50

ppm/∞C

I

SOURCE

= 0 to 2mA

0.35

Load Regulation

I

SINK

= 0 to 100µA

1.0

mV/mA

Line Regulation

V

DD

= 2.7V to 3.6V, static

0.25

mV/V

DIGITAL INPUTS (SCLK, CNVST)

Input Voltage Low

VIL

0.3 x V

L

V

Input Voltage High

VIH

0.7 x V

L

V

Input Leakage Current

I

IL

0.05

±10

µA

DIGITAL OUTPUT (DOUT)

Output Load Capacitance

C

OUT

For stated timing performance

30

pF

Output Voltage Low

V

OL

I

SINK

= 5mA, V

L

1.8V

0.4

V

Output Voltage High

V

OH

I

SOURCE

= 1mA, V

L

1.8V

V

L

- 0.5V

V

Output Leakage Current

I

OL

Output high impedance

±0.2

±10

µA

POWER REQUIREMENTS

Analog Supply Voltage

V

DD

2.7

3.6

V

Digital Supply Voltage

V

L

1.8

V

DD

V

Static, f

SCLK

= 24MHz

6

8

Static, no SCLK

5

7

Analog Supply Current,

Normal Mode

I

DD

Operational, 1.5Msps

7

9

mA

f

SCLK

= 24MHz

2

Analog Supply Current,

Partial Power-Down Mode

I

DD

No SCLK

2

mA

f

SCLK

= 24MHz

1

Analog Supply Current,

Full Power-Down Mode

I

DD

No SCLK

0.3

1

µA

Operational, full-scale input at 1.5Msps

0.3

1

Static, f

SCLK

= 24MHz

0.15

0.5

Partial/full power-down mode,

f

SCLK

= 24MHz

0.1

0.3

mA

Digital Supply Current (Note 8)

Static, no SCLK, all modes

0.1

1

µA

Positive-Supply Rejection

PSR

V

DD

= 3V +20% -10%, full-scale input

±0.2

±3.0

mV

MAX1277/MAX1279

1.5Msps, Single-Supply, Low-Power, True-

Differential, 12-Bit ADCs with Internal Reference

4

_______________________________________________________________________________________

Note 1:

Relative accuracy is the deviation of the analog value at any code from its theoretical value after the gain error and the offset

error have been nulled.

Note 2:

No missing codes over temperature.

Note 3:

Conversion time is defined as the number of clock cycles (16) multiplied by the clock period.

Note 4:

At sample rates below 10ksps, the input full-linear bandwidth is reduced to 5kHz.

Note 5:

The listed value of three SCLK cycles is given for full-speed continuous conversions. Acquisition time begins on the 14th ris-

ing edge of SCLK and terminates on the next falling edge of CNVST. The IC idles in acquisition mode between conversions.

Note 6:

Undersampling at the maximum signal bandwidth requires the minimum jitter spec for SINAD performance.

Note 7:

1.5Msps operation guaranteed for V

L

> 2.7V. See the Typical Operating Characteristics section for recommended sampling

speeds for V

L

< 2.7V.

Note 8:

Digital supply current is measured with the V

IH

level equal to V

L

, and the V

IL

level equal to GND.

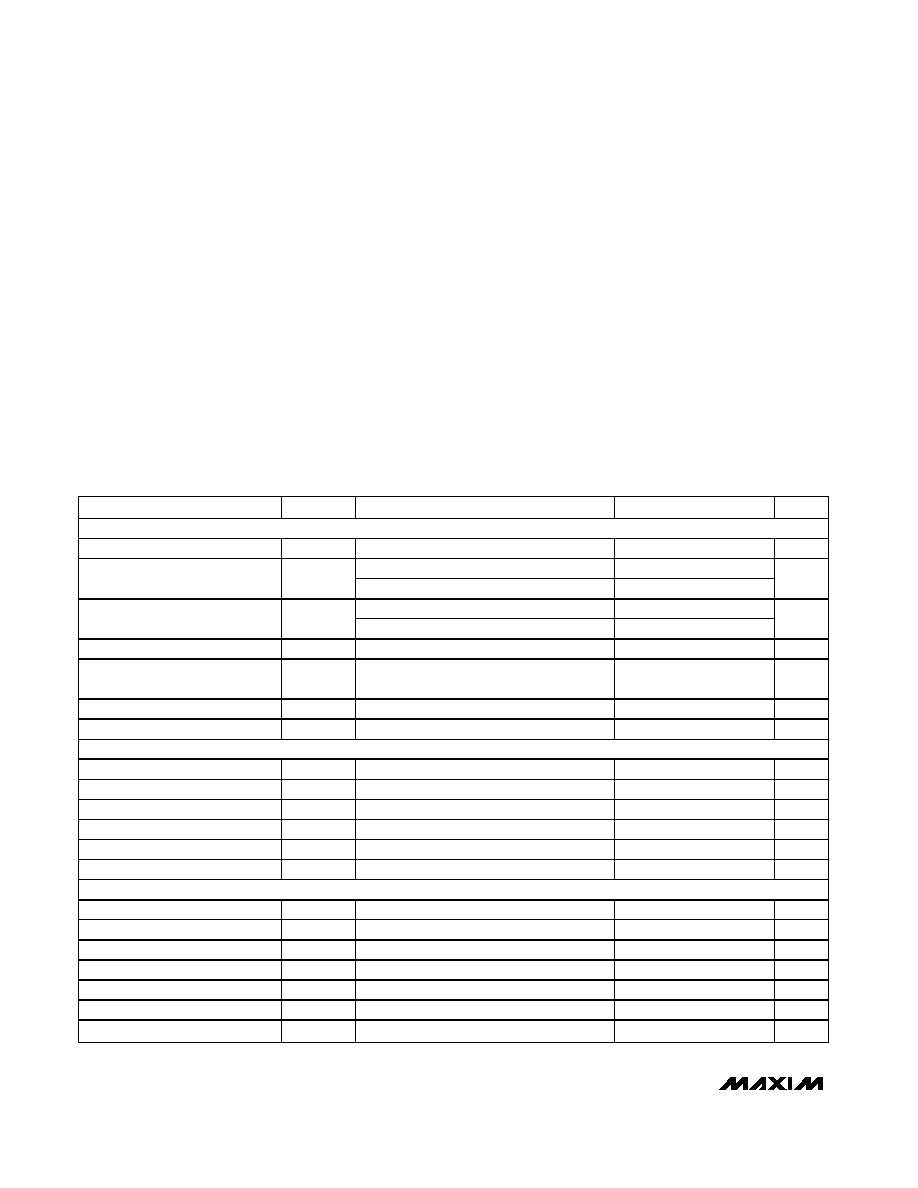

TIMING CHARACTERISTICS

(V

DD

= +2.7V to +3.6V, V

L

= V

DD

, f

SCLK

= 24MHz, 50% duty cycle, T

A

= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at

T

A

= +25∞C.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

V

L

= 2.7V to V

DD

18.7

SCLK Pulse-Width High

t

CH

V

L

= 1.8V to V

DD

, minimum recommended

(Note 7)

22.5

ns

V

L

= 2.7V to V

DD

18.7

SCLK Pulse-Width Low

t

CL

V

L

= 1.8V to V

DD

, minimum recommended

(Note 7)

22.5

ns

C

L

= 30pF, V

L

= 2.7V to V

DD

17

SCLK Rise to DOUT Transition

t

DOUT

C

L

= 30pF, V

L

= 1.8V to V

DD

24

ns

DOUT Remains Valid After SCLK

t

DHOLD

V

L

= 1.8V to V

DD

4

ns

CNVST Fall to SCLK Fall

t

SETUP

V

L

= 1.8V to V

DD

10

ns

CNVST Pulse Width

t

CSW

V

L

= 1.8V to V

DD

20

ns

Power-Up Time; Full Power-Down

t

PWR-UP

2

ms

Restart Time; Partial Power-Down

t

RCV

16

Cycles

CNVST

SCLK

DOUT

t

DHOLD

t

DOUT

t

SETUP

t

CSW

t

CL

t

CH

Figure 1. Detailed Serial-Interface Timing

GND

6k

C

L

DOUT

DOUT

C

L

GND

V

L

a) HIGH-Z TO V

OH

, V

OL

TO V

OH

,

AND V

OH

TO HIGH-Z

b) HIGH-Z TO V

OL

, V

OH

TO V

OL

,

AND V

OL

TO HIGH-Z

6k

Figure 2. Load Circuits for Enable/Disable Times

MAX1277/MAX1279

1.5Msps, Single-Supply, Low-Power, True-

Differential, 12-Bit ADCs with Internal Reference

_______________________________________________________________________________________

5

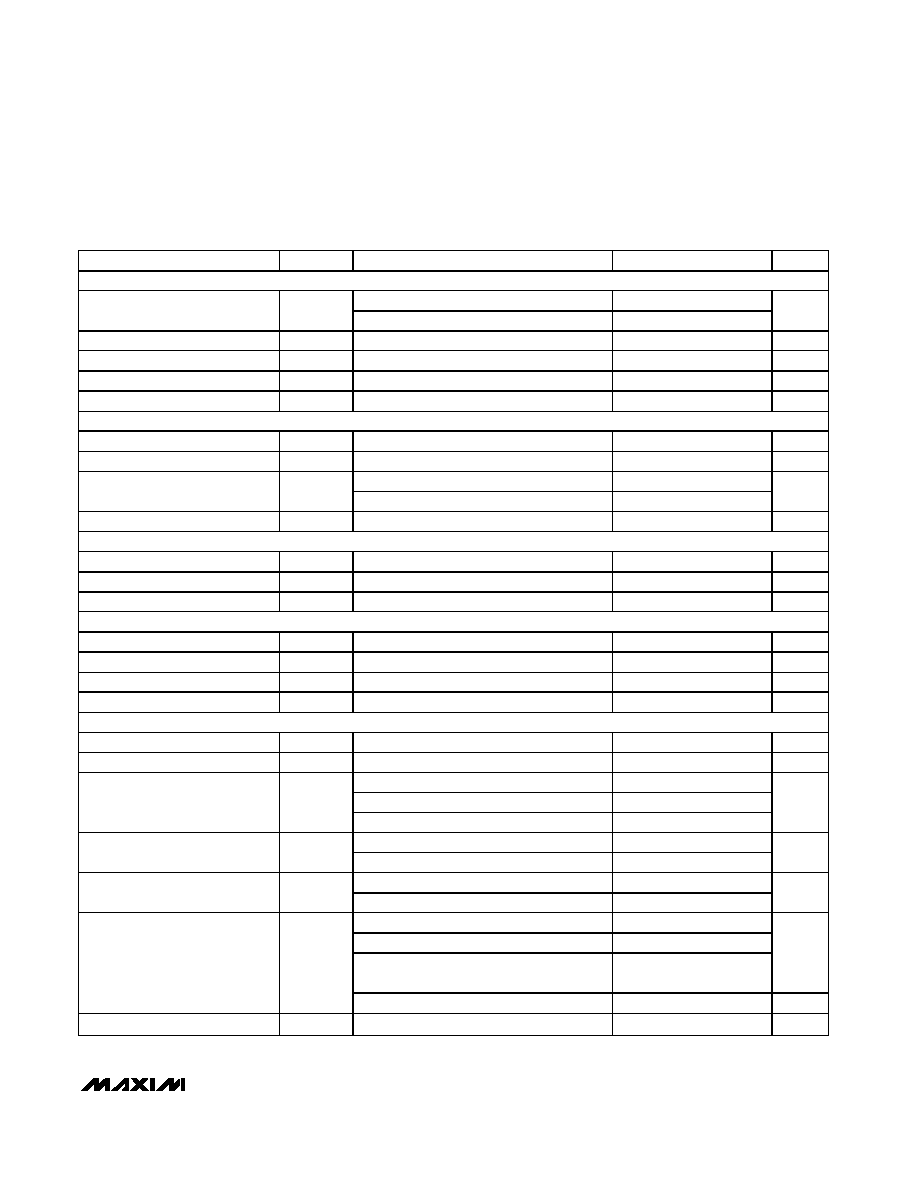

Typical Operating Characteristics

(V

DD

= +3V, V

L

= V

DD

, f

SCLK

= 24MHz, f

SAMPLE

= 1.5Msps, T

A

= T

MIN

to T

MAX

, unless otherwise noted. Typical values are measured

at T

A

= +25∞C.)

MAXIMUM RECOMMENDED f

SCLK

vs. V

L

MAX1277/79 toc01

V

L

(V)

f

SCLK

(MHz)

3.3

3.0

2.7

2.4

2.1

19

21

23

25

17

1.8

3.6

-1.00

-0.75

-0.50

-0.25

0

0.25

0.50

0.75

1.00

0

1024

2048

3072

4096

INTEGRAL NONLINEARITY

vs. DIGITAL OUTPUT CODE (MAX1277)

MAX1277/79 toc02

DIGITAL OUTPUT CODE

INL (LSB)

-1.00

-0.75

-0.50

-0.25

0

0.25

0.50

0.75

1.00

-2048

-1024

0

1024

2048

INTEGRAL NONLINEARITY

vs. DIGITAL OUTPUT CODE (MAX1279)

MAX1277/79 toc03

DIGITAL OUTPUT CODE

INL (LSB)

-1.00

-0.75

-0.50

-0.25

0

0.25

0.50

0.75

1.00

0

1024

2048

3072

4096

DIFFERENTIAL NONLINEARITY

vs. DIGITAL OUTPUT CODE (MAX1277)

MAX1277/79 toc04

DIGITAL OUTPUT CODE

DNL (LSB)

-1.00

-0.75

-0.50

-0.25

0

0.25

0.50

0.75

1.00

-2048

-1024

0

1024

2048

DIFFERENTIAL NONLINEARITY

vs. DIGITAL OUTPUT CODE (MAX1279)

MAX1277/79 toc05

DIGITAL OUTPUT CODE

DNL (LSB)

-6

-4

-5

-2

-3

-1

0

-40

10

-15

35

60

85

OFFSET ERROR

vs. TEMPERATURE (MAX1277)

MAX1277/79 toc06

TEMPERATURE (

∞C)

OFFSET ERROR (LSB)

-6

-4

-5

-2

-3

-1

0

-40

10

-15

35

60

85

OFFSET ERROR

vs. TEMPERATURE (MAX1279)

MAX1277/79 toc07

TEMPERATURE (

∞C)

OFFSET ERROR (LSB)

-2

0

-1

2

1

3

4

-40

10

-15

35

60

85

GAIN ERROR

vs. TEMPERATURE (MAX1277)

MAX1277/79 toc08

TEMPERATURE (

∞C)

GAIN ERROR (LSB)

-4

-2

-3

0

-1

1

2

-40

10

-15

35

60

85

GAIN ERROR

vs. TEMPERATURE (MAX1279)

MAX1277/79 toc09

TEMPERATURE (

∞C)

GAIN ERROR (LSB)