_______________General Description

The MAX9685 is an ultra-fast ECL comparator manufac-

tured with a high-frequency bipolar process (f

T

= 6GHz)

capable of very short propagation delays. This design

maintains the excellent DC matching characteristics nor-

mally found only in slower comparators.

The device is pin-compatible with the AD9685 and

Am6685, but exceeds their AC characteristics.

The MAX9685 has differential inputs and complemen-

tary outputs that are fully compatible with ECL-logic lev-

els. Output current levels are capable of driving 50

terminated transmission lines. The ultra-fast operation

makes signal processing possible at frequencies in

excess of 600MHz.

A latch-enable (LE) function is provided to allow the

comparator to be used in a sample-hold mode. When

LE is ECL high, the comparator functions normally.

When LE is driven ECL low, the outputs are forced to an

unambiguous ECL-logic state, dependent on the input

conditions at the time of the latch input transition. If the

latch-enable function is not used, the LE pin must be

connected to ground.

________________________Applications

High-Speed A/D Converters

High-Speed Line Receivers

Peak Detectors

Threshold Detectors

High-Speed Triggers

____________________________Features

o

1.3ns Propagation Delay

o

0.5ns Latch Setup Time

o

+5V, -5.2V Power Supplies

o

Pin-Compatible with AD9685, Am6685

o

Available in Commercial, Extended-Industrial,

and Military Temperature Ranges

o

Available in Narrow SO Package

______________Ordering Information

* Contact factory for availability of 20-pin PLCC.

** Contact factory for dice specifications.

MAX9685

Ultra-Fast ECL-Output Comparator

with Latch Enable

________________________________________________________________

Maxim Integrated Products

1

TOP VIEW

MAX9685

9

8

7

6

5

4

3

2

V+

GND1

1

IN+

IN-

LE

V-

N.C.

Q OUT

Q OUT

GND2

10

TO-100

DIP/SO

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

GND2

N.C.

N.C.

N.C.

Q OUT

Q OUT

N.C.

N.C.

GND1

V+

IN+

IN-

N.C.

LE

N.C.

V-

__________________________________________________________Pin Configurations

Call toll free 1-800-998-8800 for free samples or literature.

19-2398; Rev 1; 7/93

PART

TEMP. RANGE

PIN-PACKAGE*

MAX9685CPE

0�C to +70�C

16 Plastic DIP

MAX9685CSE

0�C to +70�C

16 Narrow SO

MAX9685CJE

0�C to +70�C

16 CERDIP

MAX9685CTW

0�C to +70�C

10 TO-100

MAX9685C/D

0�C to +70�C

Dice**

MAX9685EPE

-40�C to +85�C

16 Plastic DIP

MAX9685ESE

-40�C to +85�C

16 Narrow SO

MAX9685MJE

-55�C to +125�C

16 CERDIP

MAX9685MTW

-55�C to +125�C

10 TO-100

MAX9685

Ultra-Fast ECL-Output Comparator

with Latch Enable

2

_______________________________________________________________________________________

Supply Voltages.....................................................................�6V

Output Short-Circuit Duration .......................................Indefinite

Input Voltages........................................................................�5V

Differential Input Voltages .....................................................7.0V

Output Current ....................................................................30mA

Continuous Power Dissipation (T

A

= +70�C)

Plastic DIP (derate 10.53mW/�C above +70�C) ..........842mW

Narrow SO (derate 8.70mW/�C above +70�C) ............696mW

CERDIP (derate 10.00mW/�C above +70�C) ...............800mW

TO-100 (derate 6.67mW/�C above +70�C) ..................533mW

Operating Temperature Ranges

MAX9685C_ _ .....................................................0�C to +70�C

MAX9685E_ _ ..................................................-40�C to +85�C

MAX9685M_ _................................................-55�C to +125�C

Storage Temperature Range .............................-55�C to +150�C

Lead Temperature (soldering, 10sec) .............................+300�C

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

PARAMETER

SYMBOL

UNITS

Common-Mode

Rejection Ratio

CMRR

80

dB

Input Voltage Range

V

CM

-2.5

+2.5

V

Input Bias Current

I

B

10

20

�A

Input Offset Current

I

OS

5

�A

Power-Supply

Rejection Ratio

PSRR

60

dB

Input Resistance

R

IN

60

k

C

IN

3

pF

Input Offset Voltage

V

OS

-5

5

mV

Temperature Coefficient

V

OS

/

T

10

�V/�C

CONDITIONS

(Note 1)

T

A

= +25�C

T

A

= +25�C

(Note 1)

R

S

=100

80

-2.5

+2.5

10

20

5

60

60

3

-5

5

15

MAX9685C/E

MIN

TYP

MAX

MAX9685M

MIN

TYP

MAX

T

A

= +25�C

-1.05

-0.87

-1.16

-0.89

-0.89

-0.70

0.88

-0.69

-0.96

-0.81

-0.96

-0.81

-1.14

-0.88

-0.88

-0.70

Logic Output High

Voltage

-0.96

-0.81

-1.89

-1.69

-1.90

-1.65

-1.83

-1.57

-1.82

-1.55

-1.85

-1.65

-1.85

-1.65

-1.90

-1.65

-1.83

-1.57

MAX9685E

-1.85

-1.65

T

A

= +25�C

16

22

16

22

T

A

= T

MIN

to T

MAX

24

25

mA

T

A

= +25�C

20

32

20

32

T

A

= T

MIN

to T

MAX

36

36

mA

-8

8

-7

7

T

A

= T

MIN

to T

MAX

T

A

= T

MIN

to T

MAX

8

12

T

A

= T

MIN

to T

MAX

30

40

Input Capacitance

V

OH

Logic Output Low

Voltage

V

OL

Positive Supply Current

I

CC

Negative Supply

Current

I

EE

T

A

= T

MIN

T

A

= T

MAX

T

A

= +25�C

T

A

= T

MIN

T

A

= T

MAX

T

A

= +25�C

MAX9685C,

MAX9685M

MAX9685E

T

A

= T

MIN

T

A

= T

MAX

T

A

= +25�C

T

A

= T

MIN

T

A

= T

MAX

T

A

= +25�C

MAX9685C,

MAX9685M

V

V

ABSOLUTE MAXIMUM RATINGS

ELECTRICAL CHARACTERISTICS

(V+ = +5V, V- = -5.2V, R

L

= 50

, V

T

= -2V, T

A

= +25�C, unless otherwise noted.)

MAX9685

Ultra-Fast ECL-Output Comparator

with Latch Enable

_______________________________________________________________________________________

3

Note 1:

Not tested, guaranteed by design.

Note 2:

V

IN

= 100mV, V

OD

= 10mV

PARAMETER

SYMBOL

UNITS

1.3

1.8

1.5

2.0

T

A

= 0�C to +70�C

MAX9685M

MIN

TYP

MAX

1.3

1.8

CONDITIONS

T

A

= +25�C

MAX9685C/E

MIN

TYP

MAX

SWITCHING CHARACTERISTICS

(V+ = 5V, V- = -5.2V, R

L

= 50

, V

T

= -2V, T

A

= +25�C, unless otherwise noted.)

__________Applications Information

Layout

Because of the MAX9685's large gain-bandwidth char-

acteristic, special precautions need to be taken if its

high-speed capabilities are to be used. A PC board

with a ground plane is mandatory. Mount all decou-

pling capacitors as close to the power-supply pins as

possible, and process the ECL outputs in microstrip

fashion, consistent with the load termination of 50

to

120

. For low-impedance applications, microstrip lay-

out at the input may also be helpful. Pay close atten-

tion to the bandwidth of the decoupling and terminating

components. Chip components can be used to mini-

mize lead inductance. An unused LE pin must be con-

nected to ground.

Input Slew-Rate Requirements

As with all high-speed comparators, the high gain-

bandwidth product of these devices creates oscillation

problems when the input traverses through the linear

region. For clean switching without oscillation or steps

in the output waveform, the input must meet certain

minimum slew-rate requirements. The tendency of the

part to oscillate is a function of the layout and source

impedance of the circuit employed. Poor layout and

larger source impedance will increase the minimum

slew-rate requirement.

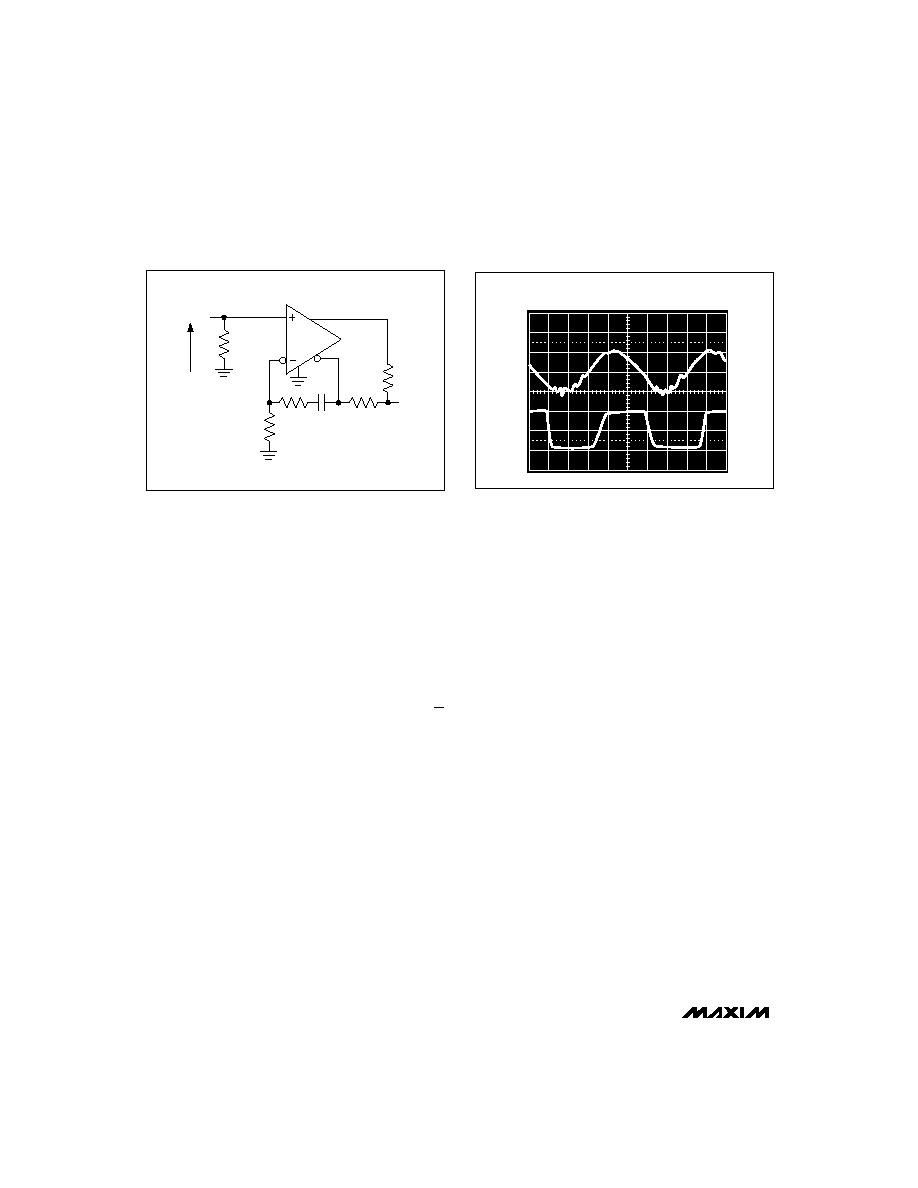

Figure 1 shows a high-speed receiver application with

50

input and output termination. With this configura-

tion, in which a ground plane and microstrip PC board

were used, the minimum slew rate for clean output

switching is 1.6V/�s. Sine-wave inputs imply a mini-

mum signal size of 360mV

RMS

at 500kHz and

90mV

RMS

at 4MHz.

In many applications, the addition of regenerative feed-

back will assist the input signal through the linear

region, which will lower the minimum slew-rate require-

ment considerably. For example, with the addition of

positive feedback components R

f

= 1k

and C

f

=

10pF, the minimum slew-rate requirement can be

reduced by a factor of four.

ERMS =

Slew Rate

2 2nf

Input to Output High

(Notes 1, 2)

t

pd+

T

A

= -55�C to +125�C

1.7

2.4

ns

T

A

= +25�C

1.3

1.8

1.3

1.8

T

A

= 0�C to +70�C

1.5

2.0

Input to Output Low

(Notes 1, 2)

t

pd-

T

A

= -55�C to +125�C

1.7

2.4

ns

T

A

= +25�C

1.2

1.7

1.2

1.7

T

A

= 0�C to +70�C

1.4

2.0

Latch-Enable to Output

High (Notes 1, 2)

t

pd+

(E)

T

A

= -55�C to +125�C

2.0

3.0

ns

T

A

= +25�C

1.2

1.7

1.2

1.7

T

A

= 0�C to +70�C

1.4

2.0

Latch-Enable to Output

High (Notes 1, 2)

t

pd-

(E)

T

A

= -55�C to +125�C

2.0

3.0

ns

Latch-Enable Pulse

Width (Note 2)

t

pw

(E)

3.0

2.0

3.0

2.0

Minimum Setup Time

t

s

0.5

1.0

0.5

1.0

Minimum Hold Time

t

h

0.5

1.0

0.5

1.0

ns

ns

ns

MAX9685

Ultra-Fast ECL-Output Comparator

with Latch Enable

4

_______________________________________________________________________________________

The timing diagram (Figure 3) illustrates the series of

events that complete the compare function, under

worst-case conditions.

The top line of the diagram illustrates two latch-enable

pulses. Each pulse is high for the compare function

and low for the latch function. The first pulse demon-

strates the compare function; part of the input action

takes place during the compare mode. The second

pulse demonstrates a compare-function interval during

which there is no change in the input.

The leading edge of the input signal (illustrated as a

large-amplitude, small-overdrive pulse) switches the

comparator after time interval t

pd

. Output Q and Q

transistors are similar in timing. The input signal must

occur at time t

s

before the latch falling edge, and it

must be maintained for time t

h

after the edge to be

acquired. After t

h

, the output is no longer affected by

the input status until the latch is again strobed. A mini-

mum latch pulse width of t

pw

(E) is needed for the

strobe operation, and the output transitions occur after

a time t

pd

(E).

Definition of Terms

V

OS

Input Offset Voltage--The voltage required

between the input terminals to obtain 0V dif-

ferential at the output.

V

IN

Input Voltage Pulse Amplitude

V

OD

Input Voltage Overdrive

t

pd+

Input to Output High Delay--The propagation

delay measured from the time the input signal

crosses the input offset voltage to the 50%

point of an output low-to-high transition.

t

pd-

Input to Output Low Delay--The propagation

delay measured from the time the input signal

crosses the input offset voltage to the 50%

point of an output high-to-low transition.

t

pd+

(E) Latch-Enable to Output High Delay--The

propagation delay measured from the 50%

point of the latch-enable signal low-to-high

transition to the 50% point of an output low-to-

high transition.

t

pd-

(E)

Latch-Enable to Output Low Delay--The

propagation delay measured from the 50%

point of the latch-enable signal low-to-high

transition to the 50% point of an output high-

to-low transition.

t

pw

(E)

Minimum Latch-Enable Pulse Width--The

minimum time the latch-enable signal must be

high to acquire and hold an input signal.

t

s

Minimum Setup Time--The minimum time

before the negative transition of the latch-

enable pulse that an input signal must be pre-

sent to be acquired and held at the outputs.

t

h

Minimum Hold Time--The minimum time after

the negative transition of the latch-enable signal

that an input signal must remain unchanged to

be acquired and held at the output.

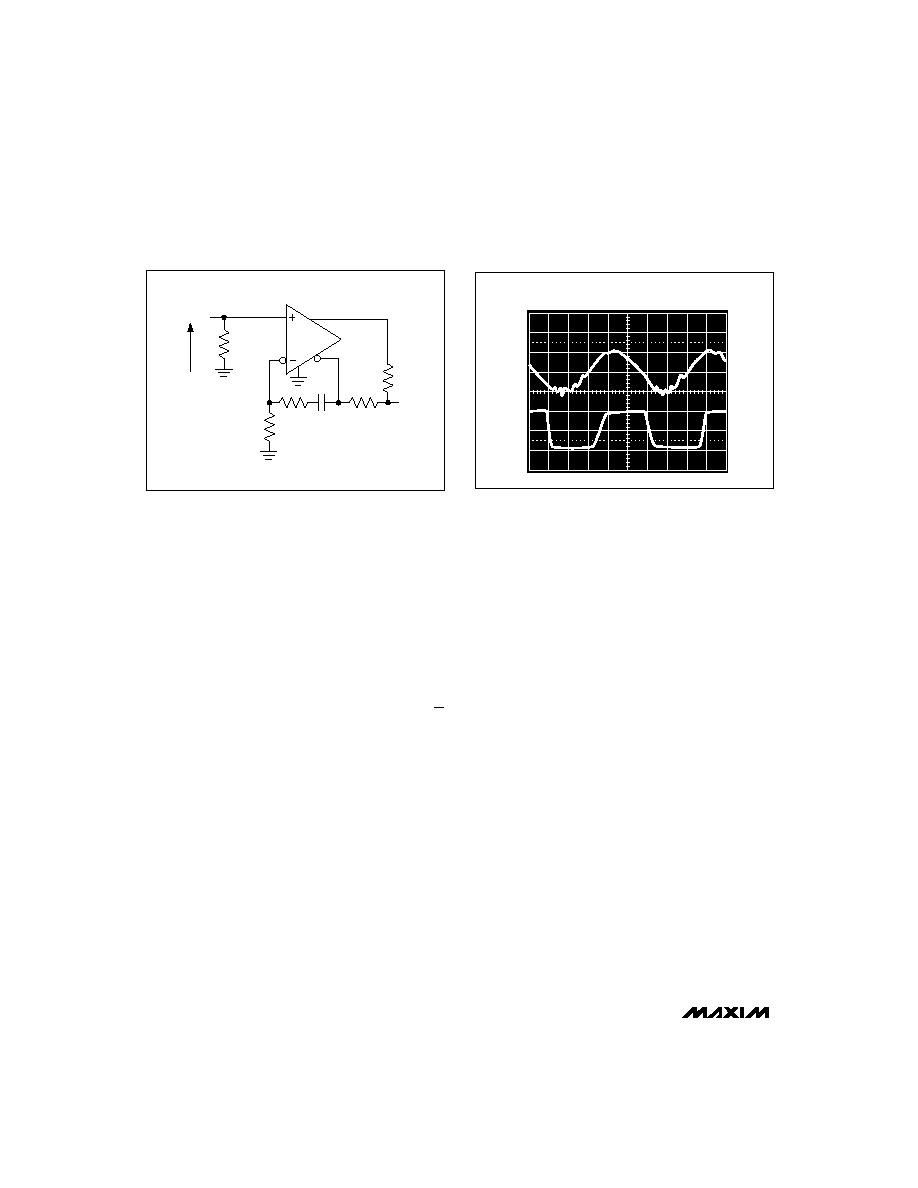

Figure 2. As a high-speed receiver, the MAX9685 is capable

of processing signals in excess of 600MHz. Figure 2 is a

100MHz example with an input signal level of 14mV

RMS

.

-0V

-0.9V

-1.7V

OUTPUT

INPUT

OUTPUT

500mV/div

INPUT

20mV/div

2ns/div

V

IN

-2V

50

C

f

R

f

50

50

50

LE

Figure 1. Regenerative Feedback. High-speed receiver with

50

input and output termination.

MAX9685

Ultra-Fast ECL-Output Comparator

with Latch Enable

_______________________________________________________________________________________

5

LATCH

ENABLE

DIFFERENTIAL

INPUT

VOLTAGE

Q

Q

LATCH

COMPARE

t

s

th

V

OD

V

IN

t

pd

(E)

V

OS

50%

50%

50%

t

pw

(E)

t

pd

Figure 3. Timing Diagram