FEATURES

∑ Bit organization

- 32M x 8 (byte mode)

- 16M x 16 (word mode)

∑ Fast access time

- Random access: 100ns (max.)

- Page access: 30ns (max.)

∑ Page Size

- 8 words per page

PIN CONFIGURATION

70 PIN SSOP

1

P/N:PM0822

REV. 1.3, NOV. 21, 2002

MX23L25611

∑ Current

- Operating: 30mA (max.) @ 5MHz

- Standby: 15uA (max.)

∑ Supply voltage

- 3.0V ~ 3.6V

∑ Package

- 70 pin SSOP

∑ Temperature

- 0~70

∞

C

PIN DESCRIPTION

Symbol

Pin Function

A0~A23

Address Inputs

D0~D14

Data Outputs

D15/A-1

D15 (Word Mode) / LSB Address

(Byte Mode)

CE#

Chip Enable Input

OE#

Output Enable Input

BYTE#

Word/Byte Mode Selection

VCC

Power Supply Pin

VSS

Ground Pin

NC

No Connection

256M-BIT (16M x 16 / 32M x 8) MASK ROM WITH PAGE MODE

(SSOP ONLY)

MODE SELECTION

CE#

OE#

BYTE#

D15/A-1

D0~D7

D8~D15

Mode

Power

H

X

X

X

High Z

High Z

-

Stand-by

L

H

X

X

High Z

High Z

-

Active

L

L

H

Output

D0~D7

D8~D15

Word

Active

L

L

L

Input

D0~D7

High Z

Byte

Active

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

A21

A20

A18

A17

A7

A6

A5

A4

A3

A2

A1

A0

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

CE#

VSS

VSS

OE#

D0

D8

D1

D9

D2

D10

D3

D11

VSS

A19

A8

A9

A10

A11

A12

A13

A14

A15

A16

A23

BYTE#

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

A22

VSS

VSS

D15

D7

D14

D6

D13

D5

D12

D4

VCC

VCC

MX23L25611

3

P/N:PM0822

REV. 1.3, NOV. 21, 2002

MX23L25611

AC CHARACTERISTICS (Ta = 0

∞

C ~ 70

∞

C, VCC = 3.0V ~ 3.6V)

Item

Symbol

23L25611-10

23L25611-12

MIN.

MAX.

MIN.

MAX.

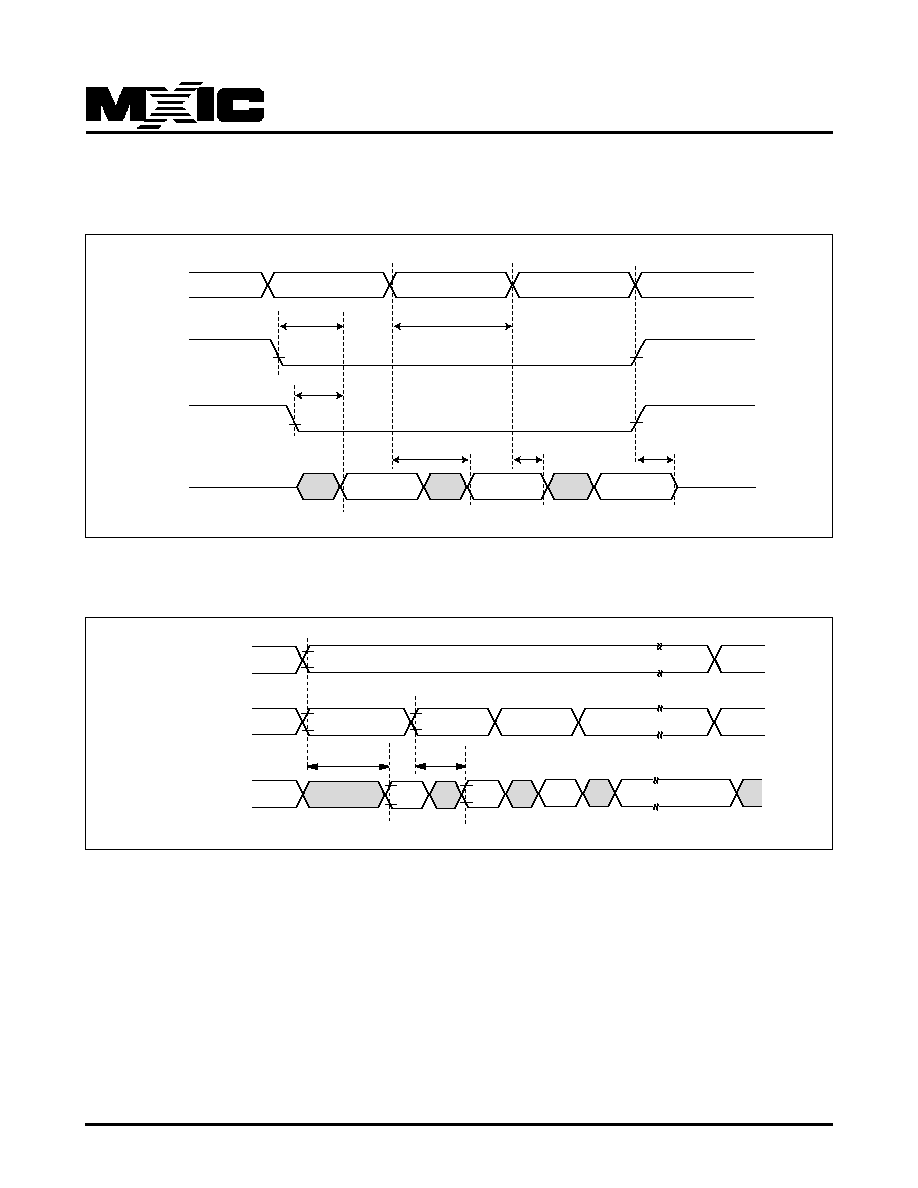

Read Cycle Time

tRC

100ns

-

120ns

-

Address Access Time

tAA

-

100ns

-

120ns

Chip Enable Access Time

tCE

-

100ns

-

120ns

Page Mode Access Time

tPA

-

30ns

-

30ns

Output Enable Time

tOE

-

30ns

0

30ns

Output Hold After Address

tOH

0ns

-

0ns

-

Output High Z Delay

tHZ

-

20ns

-

20ns

AC Test Conditions

Input Pulse Levels

0.4V~ 2.4V

Input Rise and Fall Times

10ns

Input Timing Level

1.5V

Output Timing Level

1.5V

Output Load

See Figure

Note:No output loading is present in tester load board.

Active loading is used and under software programming control.

Output loading capacitance includes load board's and all stray capacitance.

DOUT

C< 100pF

IOL (load)=1.6mA

IOH (load)= -0.4mA

DC CHARACTERISTICS (Ta = 0

∞

C ~ 70

∞

C, VCC = 3.0V ~ 3.6V)

Item

Symbol

MIN.

MAX.

Conditions

Output High Voltage

VOH

2.4V

-

IOH = -0.4mA

Output Low Voltage

VOL

-

0.4V

IOL = 1.6mA

Input High Voltage

VIH

2.2V

VCC+0.3V

Input Low Voltage

VIL

-0.3V

0.2xVCC

Input Leakage Current

ILI

-

10uA

0V, VCC

Output Leakage Current

ILO

-

10uA

0V, VCC

Operating Current

ICC

-

30mA

f=5MHz, all output open

CE#=VIL(Chip Enable)

OE#=VIH(Output Disabled)

Standby Current (TTL)

ISTB1

-

1mA

CE# = VIH

Standby Current (CMOS)

ISTB2

-

15uA

CE# > VCC-0.2V

Input Capacitance

CIN

-

10pF

Ta = 25

∞

C, f = 1MHZ

Output Capacitance

COUT

-

10pF

Ta = 25

∞

C, f = 1MHZ