1

P/N:PM0900

REV. 0.6, AUG. 20, 2003

MX28F640C3T/B

64M-BIT [4M x16] CMOS SINGLE VOLTAGE

3V ONLY FLASH MEMORY

ADVANCED INFORMATION

∑ Automatic Suspend Enhance

- Word write suspend to read

- Sector erase suspend to word write

- Sector erase suspend to read register report

∑ Automatic sector erase, full chip erase, word write and

sector lock/unlock configuration

∑ Status Reply

- Detection of program and erase operation comple-

tion.

- Command User Interface (CUI)

- Status Register (SR)

∑ Data Protection Performance

- Include boot sectors and parameter and main sectors

to be block/unblock

∑ 100,000 minimum erase/program cycles

∑ Common Flash Interface (CFI)

∑ 128-bit Protection Register

- 64-bit Unique Device Identifier

- 64-bit User-Programmable

∑ Latch-up protected to 100mA from -1V to VCC+1V

∑ Package type:

- 48-pin TSOP (12mm x 20mm)

- 48-ball CSP (11mm x 12mm)

FEATURES

∑ Bit Organization: 4,194,304 x 16

∑ Single power supply operation

- 3.0V only operation for read, erase and program

operation

- VCC=VCCQ=2.7~3.6V

- Operating temperature:-40

∞

C~85

∞

C

∑ Fast access time : 90/120ns

∑ Low power consumption

- 9mA maximum active read current, f=5MHz (CMOS

input)

- 21mA program erase current maximum

(VPP=1.65~3.6V)

- 7uA typical standby current under power saving

mode

∑ Sector architecture

- Sector Erase (Sector structure : 4Kword x 2 (boot

sectors), 4Kword x 6 (parameter sectors), 32Kword x

127 (parameter sectors)

- Top/Bottom Boot

∑ Auto Erase (chip & sector) and Auto Program

- Automatically program and verify data at specified

address

GENERAL DESCRIPTION

The MX28F640C3T/B is a 64-mega bit Flash memory

organized as 4M words of 16 bits. The 1M word of data

is arranged in eight 4Kword boot and parameter sectors,

and 127 32Kword main sector which are individually

erasable. MXIC's Flash memories offer the most cost-

effective and reliable read/write non-volatile random ac-

cess memory. The MX28F640C3T/B is packaged in 48-

pin TSOP and 48-ball CSP. It is designed to be repro-

grammed and erased in system or in standard EPROM

programmers.

The standard MX28F640C3T/B offers access time as

fast as 90ns, allowing operation of high-speed micropro-

cessors without wait states.

MXIC's Flash memories augment EPROM functionality

with in-circuit electrical erasure and programming. The

MX28F640C3T/B uses a command register to manage

this functionality. The command register allows for 100%

TTL level control inputs and fixed power supply levels

during erase and programming, while maintaining maxi-

mum EPROM compatibility.

MXIC Flash technology reliably stores memory contents

even after 100,000 erase and program cycles. The MXIC

cell is designed to optimize the erase and programming

2

P/N:PM0900

MX28F640C3T/B

REV. 0.6, AUG. 20, 2003

mechanisms. In addition, the combination of advanced

tunnel oxide processing and low internal electric fields

for erase and program operations produces reliable cy-

cling. The MX28F640C3T/B uses a 2.7V~3.6V VCC sup-

ply to perform the High Reliability Erase and auto Pro-

gram/Erase algorithms.

The highest degree of latch-up protection is achieved

with MXIC's proprietary non-epi process. Latch-up pro-

tection is proved for stresses up to 100 milliamps on

address and data pin from -1V to VCC + 1V.

The dedicated VPP pin gives complete data protection

when VPP< VPPLK.

A Command User Interface (CUI) serves as the inter-

face between the system processor and internal opera-

tion of the device. A valid command sequence written to

the CUI initiates device automation. An internal Write

State Machine (WSM) automatically executes the algo-

rithms and timings necessary for erase, full chip erase,

word write and sector lock/unlock configuration opera-

tions.

A sector erase operation erases one of the device's 32K-

word sectors typically within 1.0s, 4K-word sectors typi-

cally within 0.5s independent of other sectors. Each sec-

tor can be independently erased minimum 100,000 times.

Sector erase suspend mode allows system software to

suspend sector erase to read or write data from any other

sector.

Writing memory data is performed in word increments of

the device's 32K-word sectors typically within 0.8s and

4K-word sectors typically within 0.1s. Word program sus-

pend mode enables the system to read data or execute

code from any other memory array location.

MX28F640C3T/B features with individual sectors lock-

ing by using a combination of bits thirty-nine sector lock-

bits and WP, to lock and unlock sectors.

The status register indicates when the WSM's sector

erase, full chip erase, word program or lock configura-

tion operation is done.

The access time is 90/120ns (tELQV) over the operat-

ing temperature range (-40

∞

C to +80

∞

C) and VCC supply

voltage range of 2.7V~3.6V.

MX28F640C3T/B's power saving mode feature substan-

tially reduces active current when the device is in static

mode (addresses not switching). In this mode, the typi-

cal ICCS current is 7uA (CMOS) at 3.0V VCC.

As CE and RESET are at VCC, ICC CMOS standby

mode is enabled. When RESET is at GND, the reset

mode is enabled which minimize power consumption and

provide data write protection.

A reset time (tPHQV) is required from RESET switching

high until outputs are valid. Similarly, the device has a

wake time (tPHEL) from RESET-high until writes to the

CUI are recognized. With RESET at GND, the WSM is

reset and the status register is cleared.

3

P/N:PM0900

MX28F640C3T/B

REV. 0.6, AUG. 20, 2003

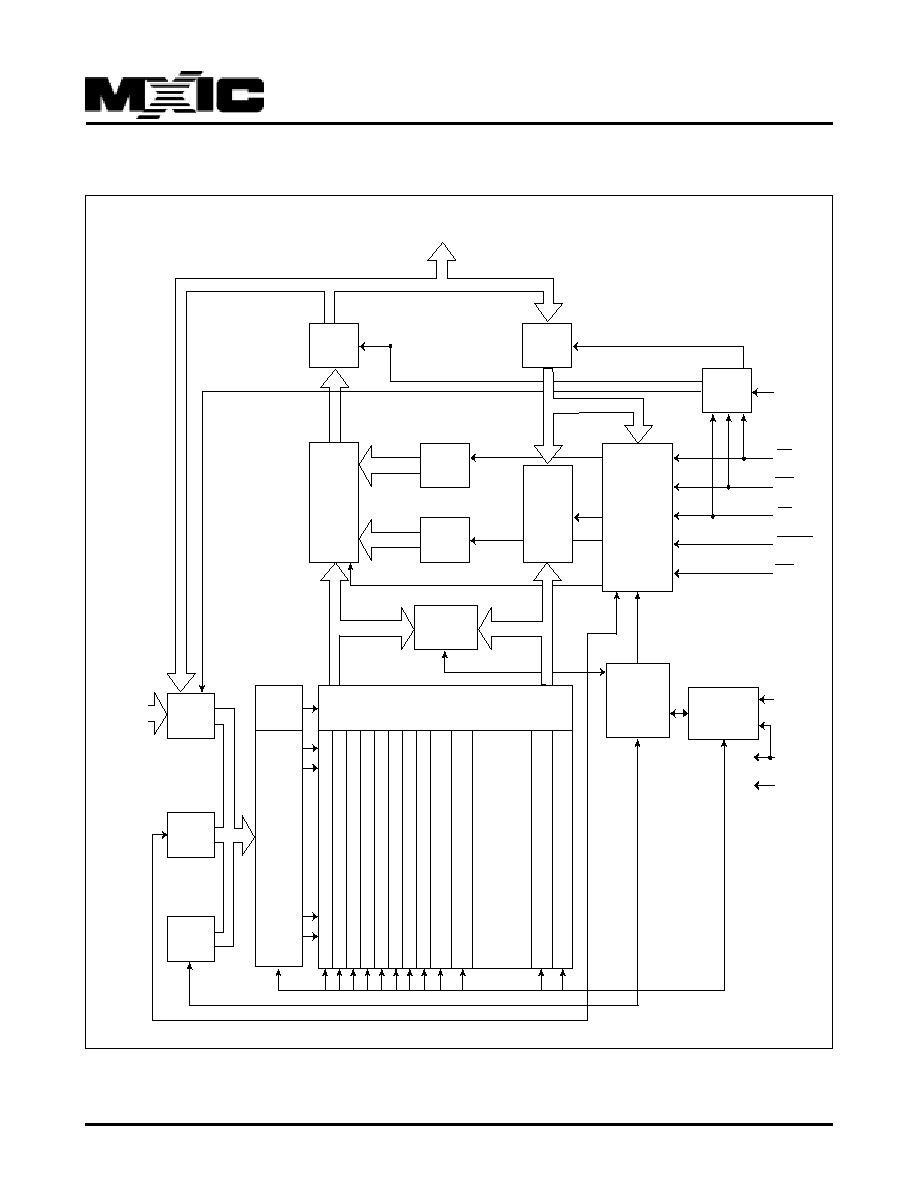

BLOCK DIAGRAM

Output

Buffer

Output

Multiple

x

e

r

Data

Register

Q0~Q7

Identifier

Register

Command

User

Interface

Input

Buffer

Status

Register

Data

Comparator

Y-Gating

32K-Word

Main Sector

x127

.......

.......

Boot Sector 0

Boot Sector 1

P

a

r

ameter Sector 0

P

a

r

ameter Sector 1

P

a

r

ameter Sector 2

P

a

r

ameter Sector 3

P

a

r

ameter Sector 4

P

a

r

ameter Sector 5

Main Sector 0

Main Sector 1

Main Sector 125

Main Sector 126

Write

State

Machine

Program/Erase

Voltage Switch

Y

Decoder

Input

Buffer

A0~A21

Address

Latch

Address

Counter

X

Decoder

I/O

Logic

VCC

CE

WE

OE

RESET

WP

VPP

VCC

GND

4

P/N:PM0900

MX28F640C3T/B

REV. 0.6, AUG. 20, 2003

PIN CONFIGURATIONS

48 TSOP (Standard Type) (12mm x 20mm)

48 Ball CSP

(11 mm x 12 mm) Top View, Ball Down (Ball Pitch=0.75mm, Ball Width=0.35mm)

A15

A14

A13

A12

A11

A10

A9

A8

A21

A20

WE

RESET

VPP

WP

A19

A18

A17

A7

A6

A5

A4

A3

A2

A1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

A16

VCCQ

GND

Q15

Q7

Q14

Q6

Q13

Q5

Q12

Q4

VCC

Q11

Q3

Q10

Q2

Q9

Q1

Q8

Q0

OE

GND

CE

A0

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

MX28F640C3T/B

A1

A13

A2

A11

A3

A8

A4

VPP

A5

WP

A6

A19

B1

A14

B2

A10

B3

WE

B4

RESET

B5

A18

B6

A17

C1

A15

C2

A12

C3

A9

C4

A21

C5

A20

C6

A6

D1

A16

D2

Q14

D3

Q5

D4

Q11

D5

Q2

D6

Q8

E1

VCCQ

E2

Q15

E3

Q6

E4

Q12

E5

Q3

E6

Q9

F1

GND

F2

Q7

F3

Q13

F4

Q4

F5

VCC

F6

Q10

A7

A7

A8

A4

B7

A5

B8

A2

C7

A3

C8

A1

D7

CE

D8

A0

E7

Q0

E8

GND

F7

Q1

F8

OE

11 mm

12 mm

5

P/N:PM0900

MX28F640C3T/B

REV. 0.6, AUG. 20, 2003

Table 1. Pin Description

Symbol

Type

Description and Function

A0-A21

input

Address inputs for memory address. Data pin float to high-impedance when the chip is

deselected or outputs are disable. Addresses are internally latched during a write or

erase cycle.

Q0-Q15

input/output

Data inputs/outputs: Inputs array data on the second CE and WE cycle during a pro-

gram command. Data is internally latched. Outputs array and configuration data. The

data pin float to tri-state when the chip is de-selected.

CE

input

Activates the device's control logic, input buffers, and sense amplifiers. CE high de-

selects the memory device and reduce power consumption to standby level. CE is

active low.

RESET

input

Reset Deep Power Down: when RESET=VIL, the device is in reset/deep power down

mode, which drives the outputs to High Z, resets the WSM and minimizes current level.

When RESET=VIH, the device is normal operation. When RESET transition the device

defaults to the read array mode.

WE

input

Write Enable: to control write to CUI and array sector. WR=VIL becomes active. The

data and address is latched WE on the rising edge of the second WE pulse.

VPP

input/supply

Program/Erase Power Supply:(1.65V~3.6V)

Lower VPP<VPPLK, to protect any contents against Program and Erase Command.

Set VPP=VCC for in-system Read, Program and Erase Operation.

OE

input

Output enable: gates the device's outputs during a real cycle.

WP

input

Write protect: when WP is VIL, the boot sectors cannot be written or erased. When WP

is VIH, locked boot sectors cannot be written or erase. WP is not affected parameter

and main sectors.

VCC

supply

Device power supply: (2.7V~3.6V).

VCCQ

input

I/O Power Supply: supplies for input/output buffers.

[2.7V~3.6V] This input should be tied directly to VCC.

GND

supply

Ground voltage: all the GND pin shall not be connected.