MDT10P10(BE)

This specification are subject to be changed without notice. Any latest information

please preview ttp;//www.mdtic.com.tw

P. 1 2005/6 VER1.3

1. General Description

This EPROM-Based 8-bit micro-controller

uses a fully static CMOS design technology

combines higher speeds and smaller size

with the low power and high noise immunity.

On chip memory system includes 1.0 K

words of ROM, and 32 bytes of static RAM.

2. Features

The followings are some of the features on

the hardware and software :

u

Fully CMOS static design

u

8-bit data bus

u

On chip ROM size : 1K words

u

Internal RAM size : 32 bytes

(25 general purpose registers, 7 special

registers)

u

36 single word instructions

u

14-bit instructions

u

2-level stacks

u

Operating voltage : 2.3V ~ 6.0 V

u

Operating frequency : 0 ~ 20 MHz

u

The most fast execution time is 200 ns

under 20 MHz in all single cycle

instructions except the branch

instructions

u

Addressing modes include direct,

indirect and relative addressing modes

u

Power-on Reset

u

Power edge-detector Reset

u

Sleep Mode for power saving

u

8-bit real time clock/counter(RTCC) with

8-bit programmable prescaler

u

4 types of oscillator can be selected by

programming option (Internal Capacitor

about 10p ):

RC

Low cost RC oscillator

LFXT

Low frequency crystal oscillator

XTAL

Standard crystal oscillator

HFXT

High frequency crystal oscillator

u

4 oscillator start-up time can be

selected by programming option:

150

�

s, 20 ms, 40 ms, 80 ms

u

On-chip RC oscillator based Watchdog

Timer(WDT) can be operated freely

u

12 I/O pins with their own independent

direction control

3. Applications

The application areas of this MDT10P10

range from appliance motor control and

high speed automotive to low power remote

transmitters/receivers, pointing devices,

and telecommunications processors, such

as Remote controller, small instruments,

chargers, toy, automobile and PC

peripheral ... etc.

MDT10P10(BE)

This specification are subject to be changed without notice. Any latest information

please preview ttp;//www.mdtic.com.tw

P. 2 2005/6 VER1.3

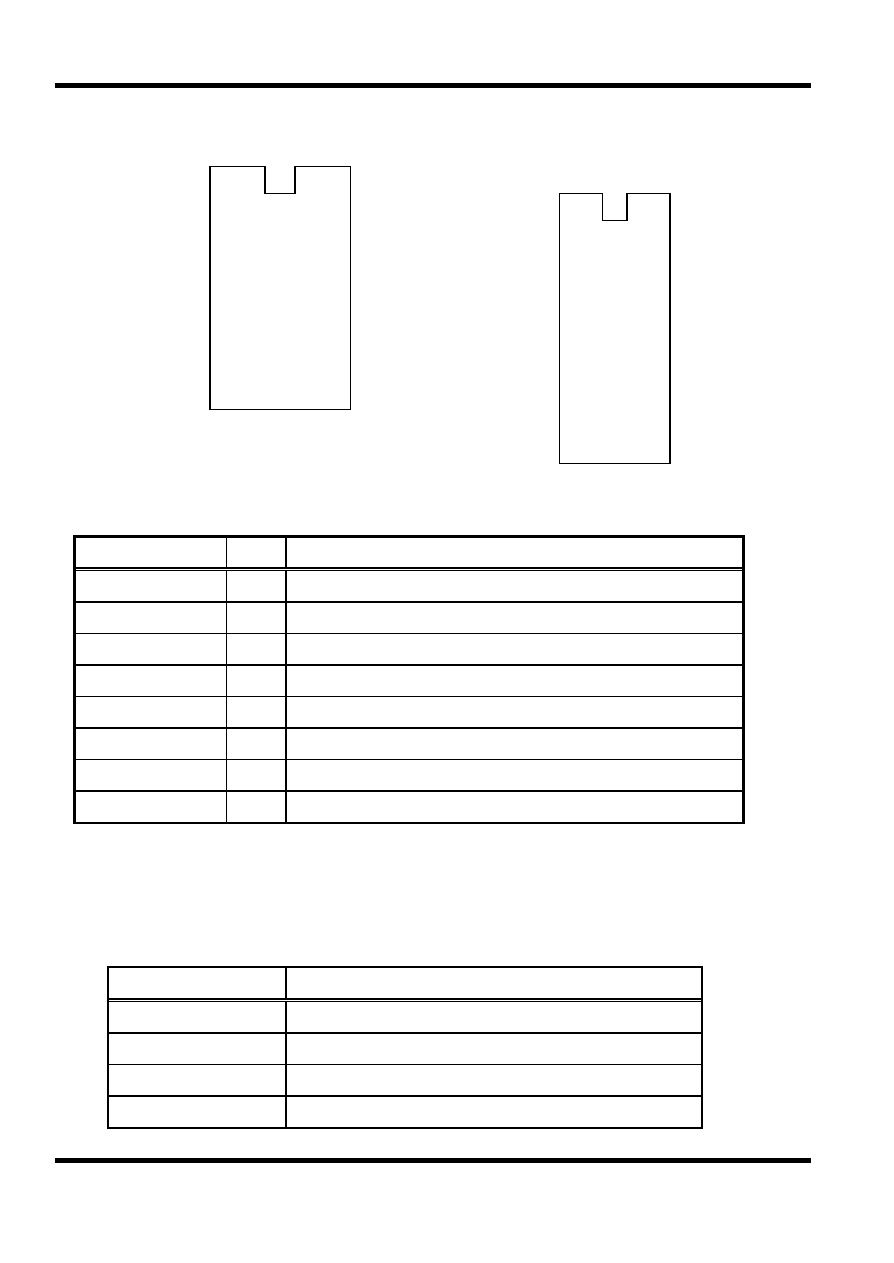

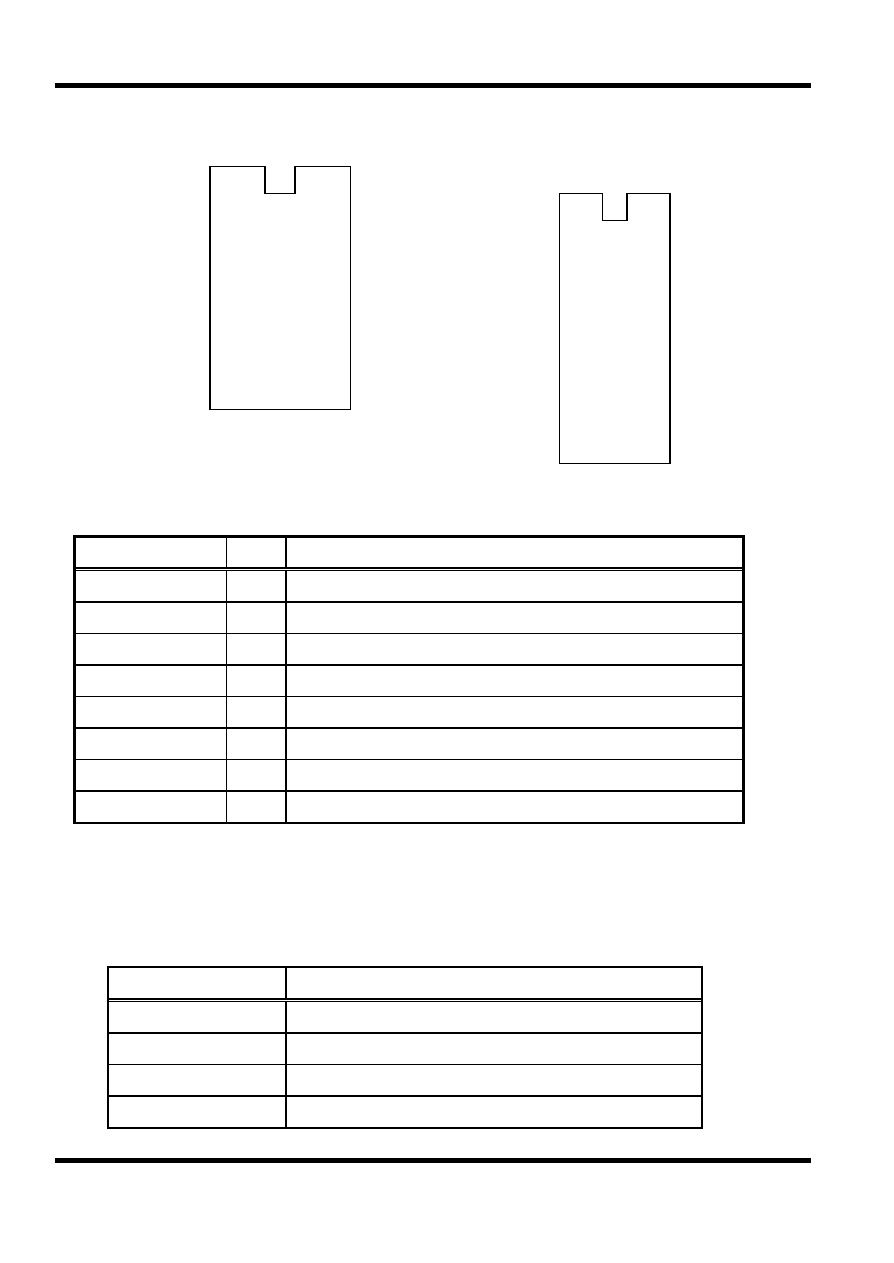

4. Pin Assignment

DIP / SOP

PA2 1

18 PA1

PA3 2

17 PA0

RTCC 3

16 OSC1

/MCLR 4

15 OSC2

V

ss

5

14 V

dd

PB0 6

13 PB7

PB1 7

12 PB6

PB2 8

11 PB5

PB3 9

10 PB4

SSOP

PA2 1

20 PA1

PA3 2

19 PA0

RTCC 3

18 OSC1

/MCLR 4

17 OSC2

VSS 5

16 VDD

VSS 6

15 VDD

PB0 7

14 PB7

PB1 8

13 PB6

PB2 9

12 PB5

PB3 10

11 PB4

5. Pin Function Description

Pin Name

I/O

Function Description

PA0~PA3

I/O

Port A, TTL input level

PB0~PB7

I/O

Port B, TTL input level

RTCC

I

Real Time Clock/Counter, Schmitt Trigger input levels

/MCLR

I

Master Clear, Schmitt Trigger input levels

OSC1

I

Oscillator Input

OSC2

O

Oscillator Output

V

dd

Power supply

V

ss

Ground

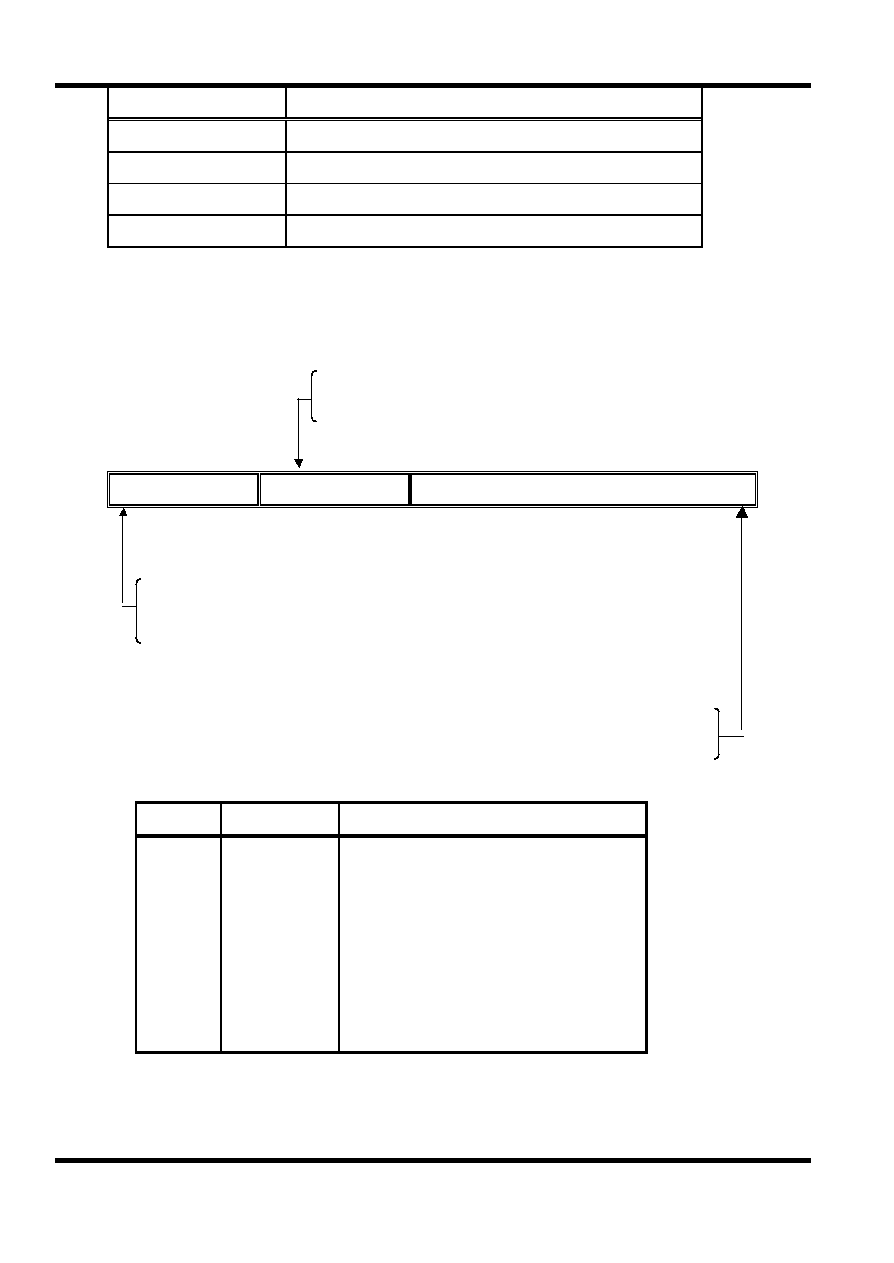

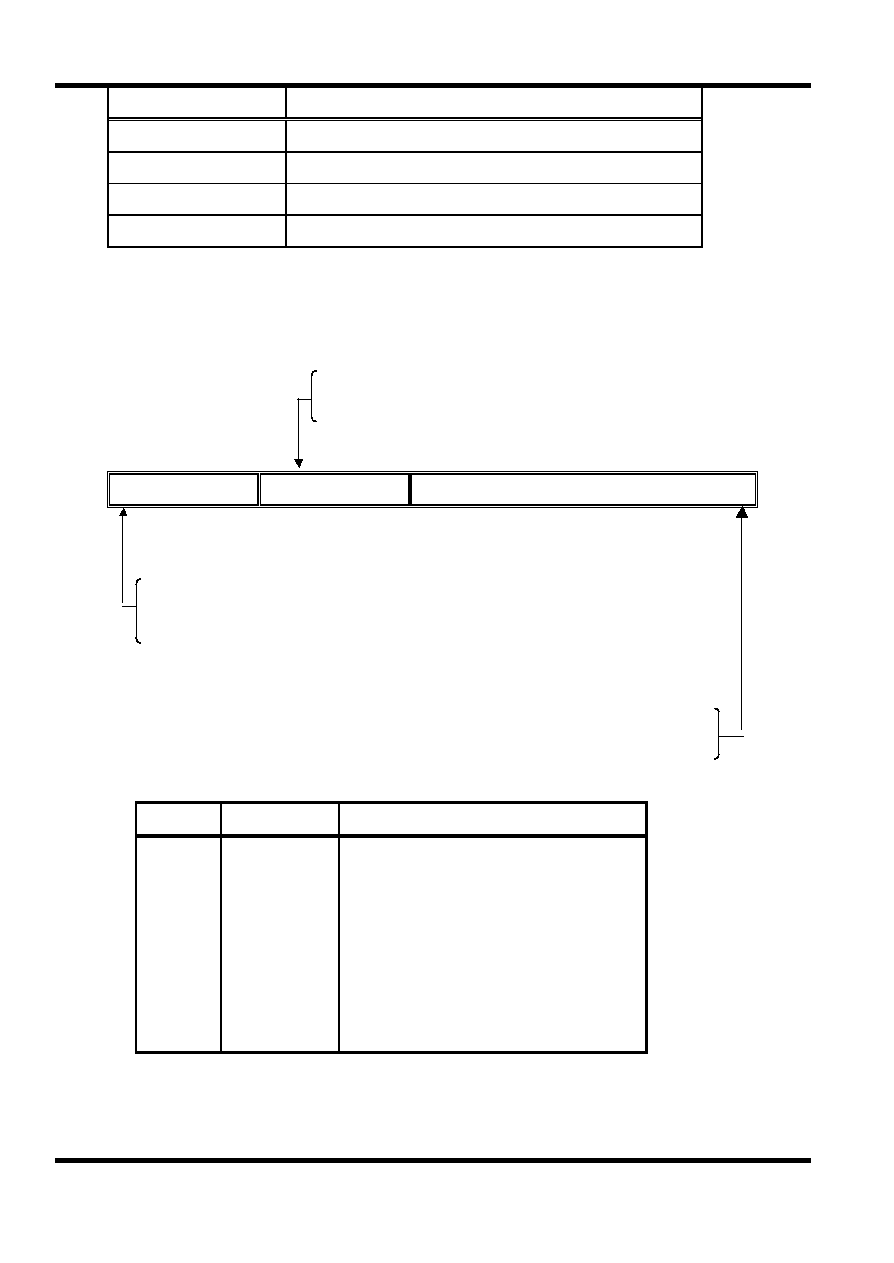

6. Memory Map

(A) Register Map

Address

Description

00

Indirect Addressing Register

01

RTCC

02

PC

03

STATUS

MDT10P10(BE)

This specification are subject to be changed without notice. Any latest information

please preview ttp;//www.mdtic.com.tw

P. 3 2005/6 VER1.3

Address

Description

04

MSR

05

Port A

06

Port B

07~1F

Internal RAM, General Purpose Register

(1) IAR ( Indirect Address Register) : R0

(2) RTCC (Real Time Counter/Counter Register) : R1

(3) PC (Program Counter) : R2

Write PC, CALL --- always 0

LJUMP, JUMP, LCALL --- from instruction word

RTWI, RET --- from STACK

A9

A8

A7~A0

Write PC, JUMP, CALL --- always 0 (ROM 1.0K)

LJUMP, LCALL --- from instruction word

RTWI, RET --- from STACK

Write PC --- from ALU

LJUMP, JUMP, LCALL, CALL --- from instruction word

RTWI, RET --- from STACK

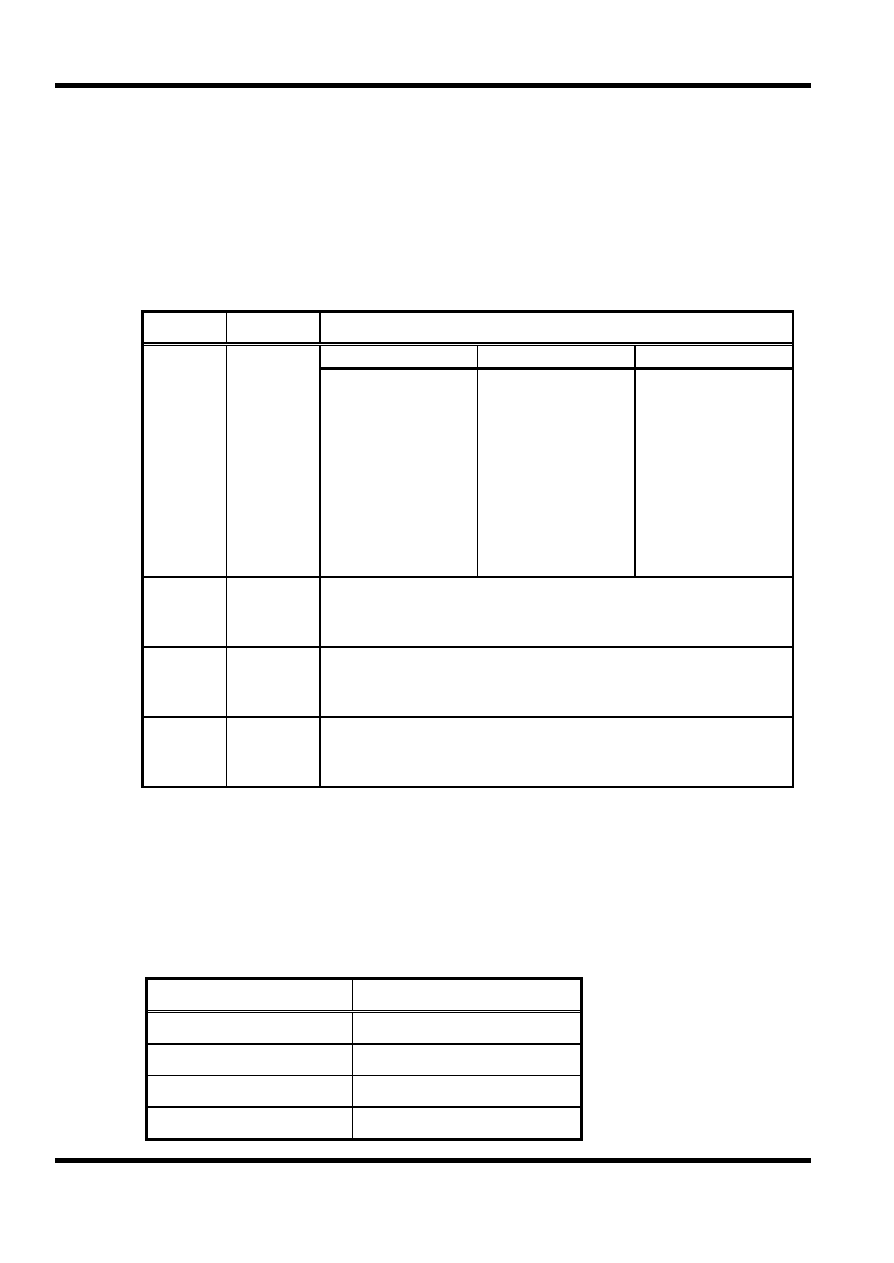

(4) STATUS (Status register) : R3

Bit

Symbol

Function

0

1

2

3

4

5-7

C

HC

Z

PF

TF

----

Carry bit

Half Carry bit

Zero bit

Power loss Flag bit

Time overflow Flag bit

General purpose bit

(5) MSR (Memory Select Register) : R4

MDT10P10(BE)

This specification are subject to be changed without notice. Any latest information

please preview ttp;//www.mdtic.com.tw

P. 4 2005/6 VER1.3

(6) PORT A : R5

PA3~PA0, I/O Register

(7) PORT B : R6

PB7~PB0, I/O Register

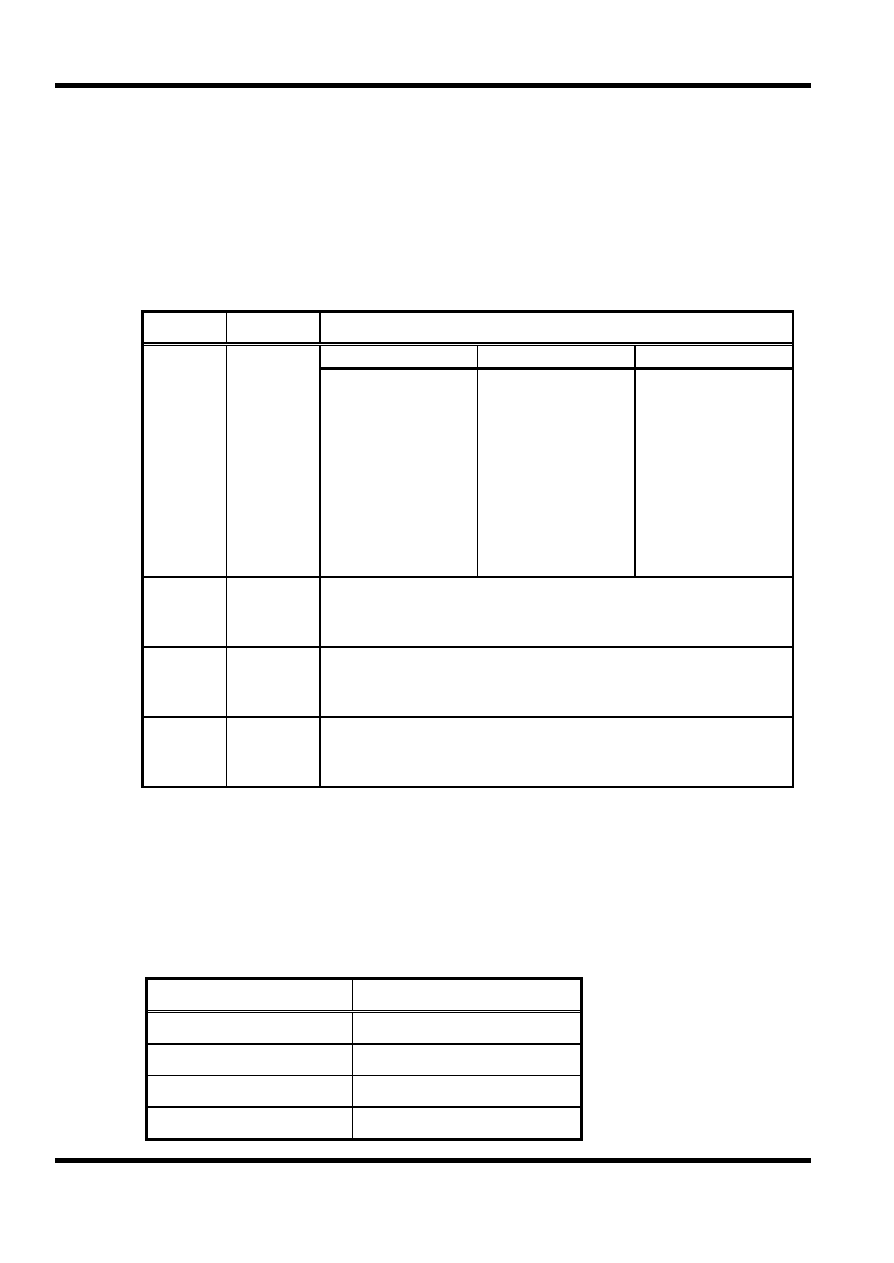

(8) TMR (Time Mode Register)

Bit

Symbol

Function

Prescaler Value

RTCC rate

WDT rate

2

--

0

PS2

--

0

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

1 : 256

1 : 1

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

3

PSC

Prescaler assignment bit :

0

--

RTCC

1

--

Watchdog Timer

4

TCE

RTCC signal Edge :

0

--

Increment on low-to-high transition on RTCC pin

1

--

Increment on high-to-low transition on RTCC pin

5

TCS

RTCC signal set :

0

--

Internal instruction cycle clock

1

--

Transition on RTCC pin

(9) CPIO A, CPIO B (Control Port I/O Mode Register)

The CPIO register is "write-only"

"0", I/O pin in output mode;

"1", I/O pin in input mode.

(10) EPROM Option by writer programming :

Oscillator Type

Oscillator Start-up Time

RC Oscillator

150

�

s,20ms,40ms,80ms

HFXT Oscillator

20 ms,40ms,80ms

XTAL Oscillator

20ms,40 ms,80ms

LFXT Oscillator

40 ms,80 ms

MDT10P10(BE)

This specification are subject to be changed without notice. Any latest information

please preview ttp;//www.mdtic.com.tw

P. 5 2005/6 VER1.3

Watchdog Timer control

Watchdog timer disable all the time

Watchdog timer enable all the time

Power Edge Detect

Security bit

PED Disable

Security Disable

PED Enable

Security Enable

The default EPROM security is disable. Once the IC was set to enable, it can not set to

disable again.

(B) Program Memory

Address

Description

000-1FF

Program memory for MDT10P10

1FF

The starting address of the power on, external reset

or WDT time-out reset for MDT10P10

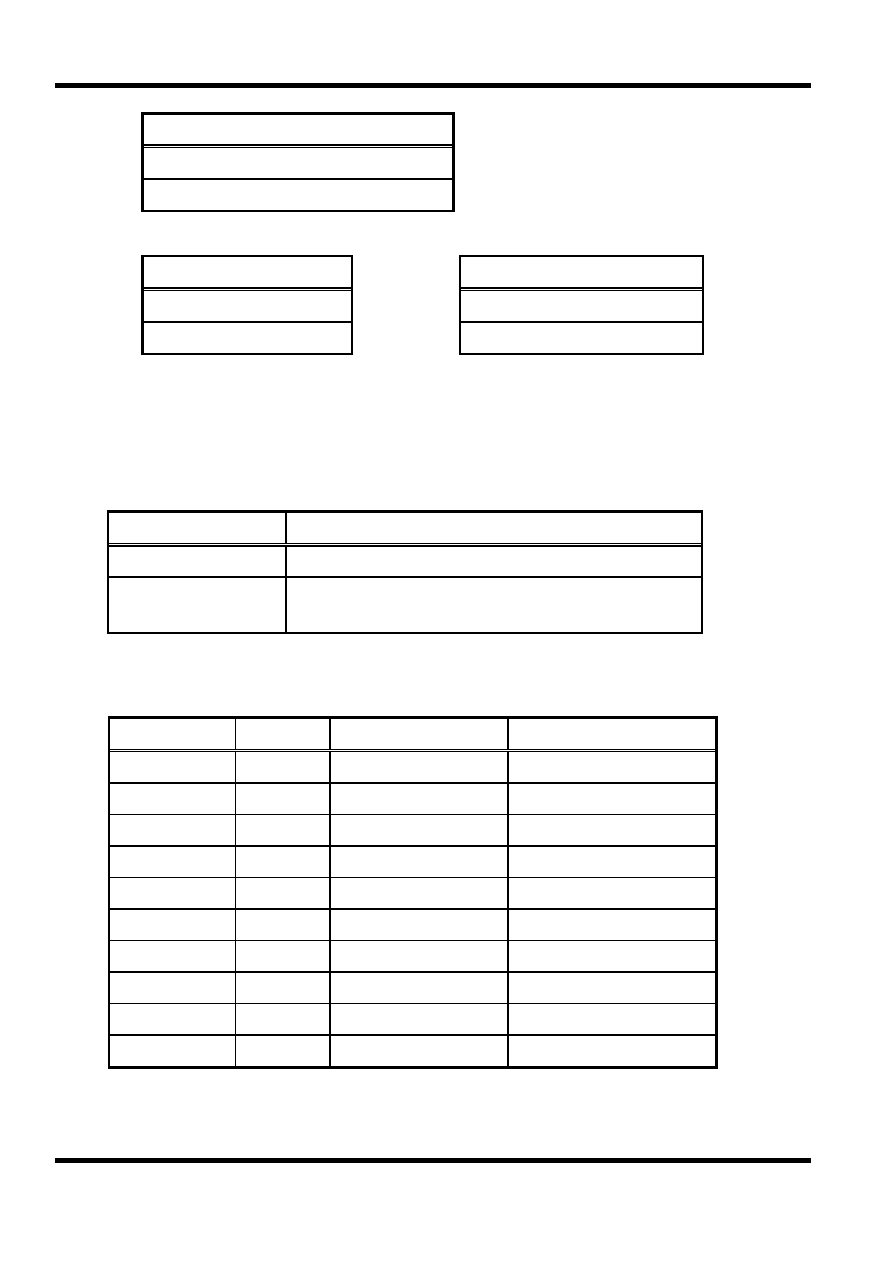

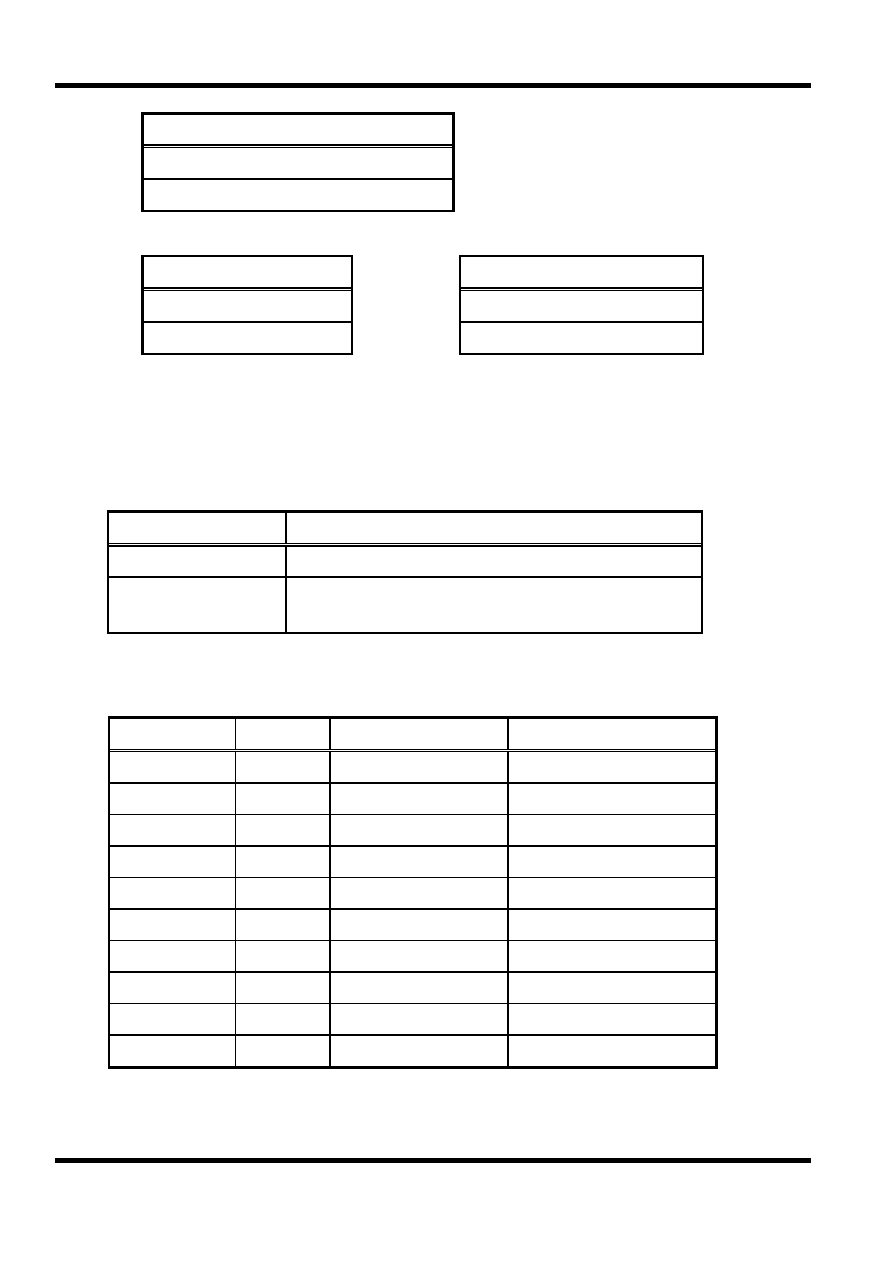

7. Reset Condition for all Registers

Register

Address

Power-On Reset

/MCLR or WDT Reset

CPIO A

1111 1111

1111 1111

CPIO B

1111 1111

1111 1111

TMR

- - 11 1111

- - 11 1111

IAR

00h

xxxx xxxx

uuuu uuuu

RTCC

01h

xxxx xxxx

uuuu uuuu

PC

02h

1111 1111

1111 1111

STATUS

03h

0001 1xxx

000# #uuu

MSR

04h

111x xxxx

111u uuuu

PORT A

05h

- - - - xxxx

- - - - uuuu

PORT B

06h

xxxx xxxx

uuuu uuuu

Note : u

unchanged, x

unknown, -

unimplemented, read as "0"

#

value depends on the condition of the following table