DESCRIPTION

s

3.3V and 5V power supply options

s

Up to 2.5Gbps operation

s

Low noise

s

Chatter-fee signal detect (SD) generation

s

Open collector TTL signal detect (SD) output

s

TTL EN input

s

Differential PECL inputs for data

s

Single power supply

s

Designed for use with Micrel-Synergy laser diode

driver and controller

s

Available in a tiny (3mm) 10-pin MSOP

The SY88943V limiting post amplifier with its high gain

and wide bandwidth is ideal for use as a post amplifier in

fiber-optic receivers with data rates up to 2.5Gbps.

Signals as small as 5mVp-p can be amplified to drive

devices with PECL inputs. The SY88943V generates a

chatter-free Signal Detect (SD) open collector TTL output.

The SY88943V incorporates a programmable level detect

function to identify when the input signal has been lost.

The SD output will change from logic "HIGH" to logic "LOW"

when input signal is smaller than the swing set by SD

LVL

.

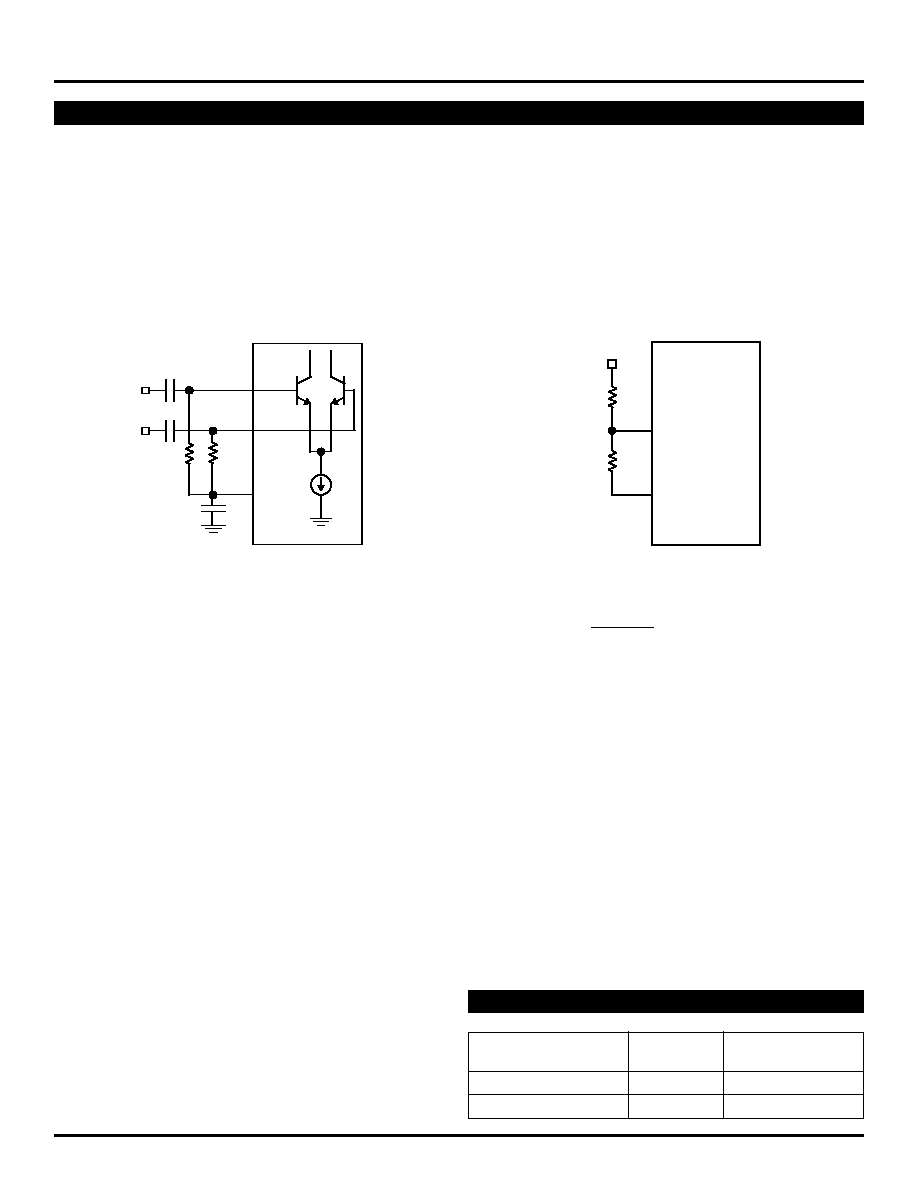

This information can be fed back to the EN input of the

device to maintain stability under loss of signal condition.

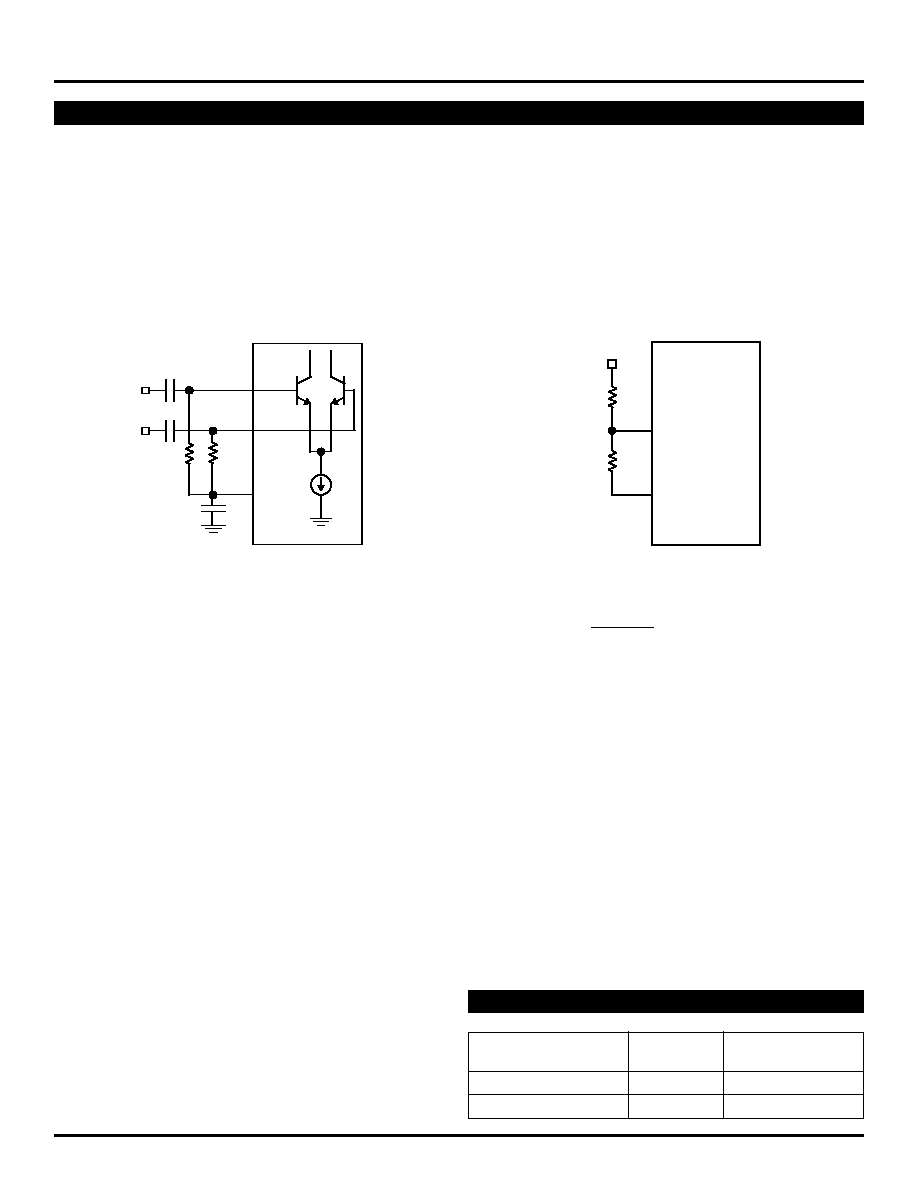

Using SD

LVL

pin, the sensitivity of the level detection can

be adjusted. The SD

LVL

voltage can be set by connecting

a resistor divider between V

CC

and V

REF

as shown in Figure

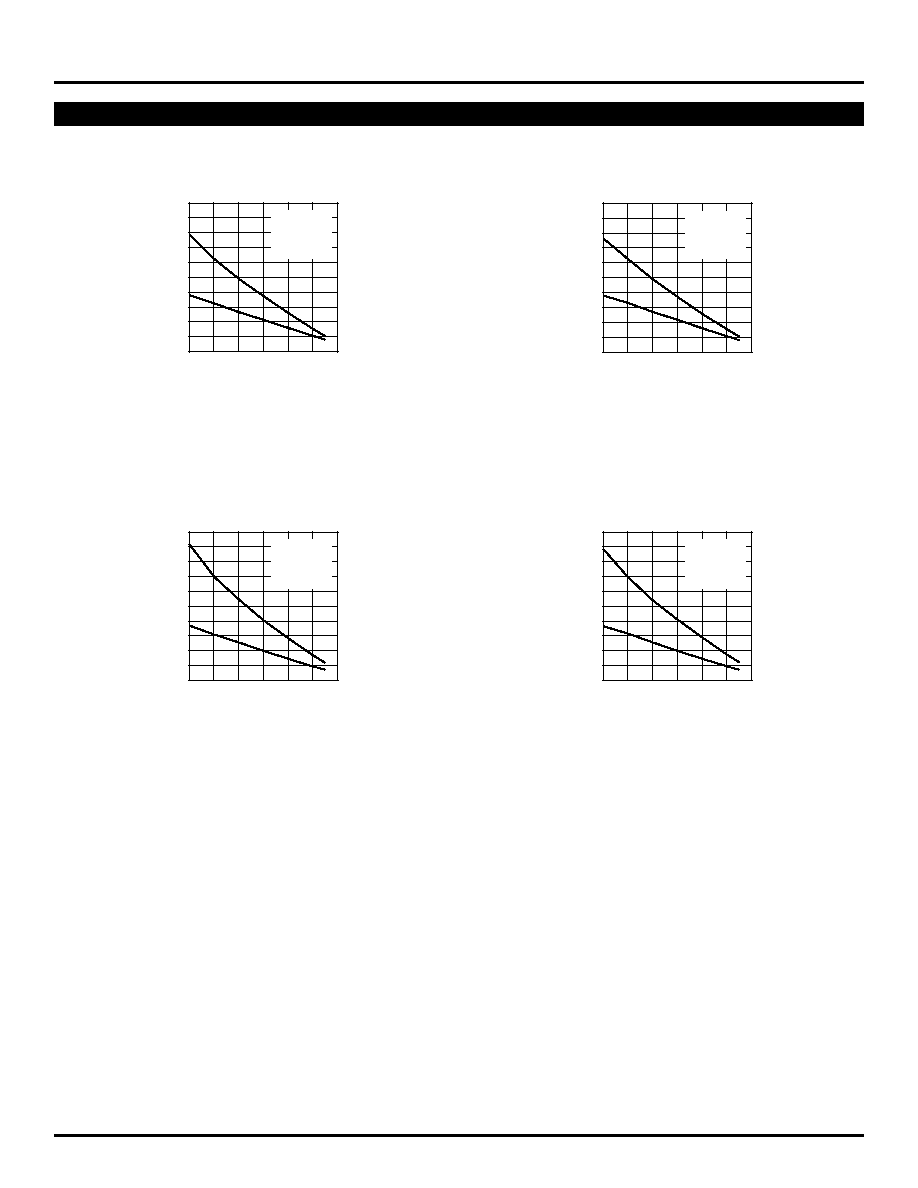

3. Figure 4, 5, 6, and 7 show the relationship between

input level sensitivity and the voltage set on SD

LVL

.

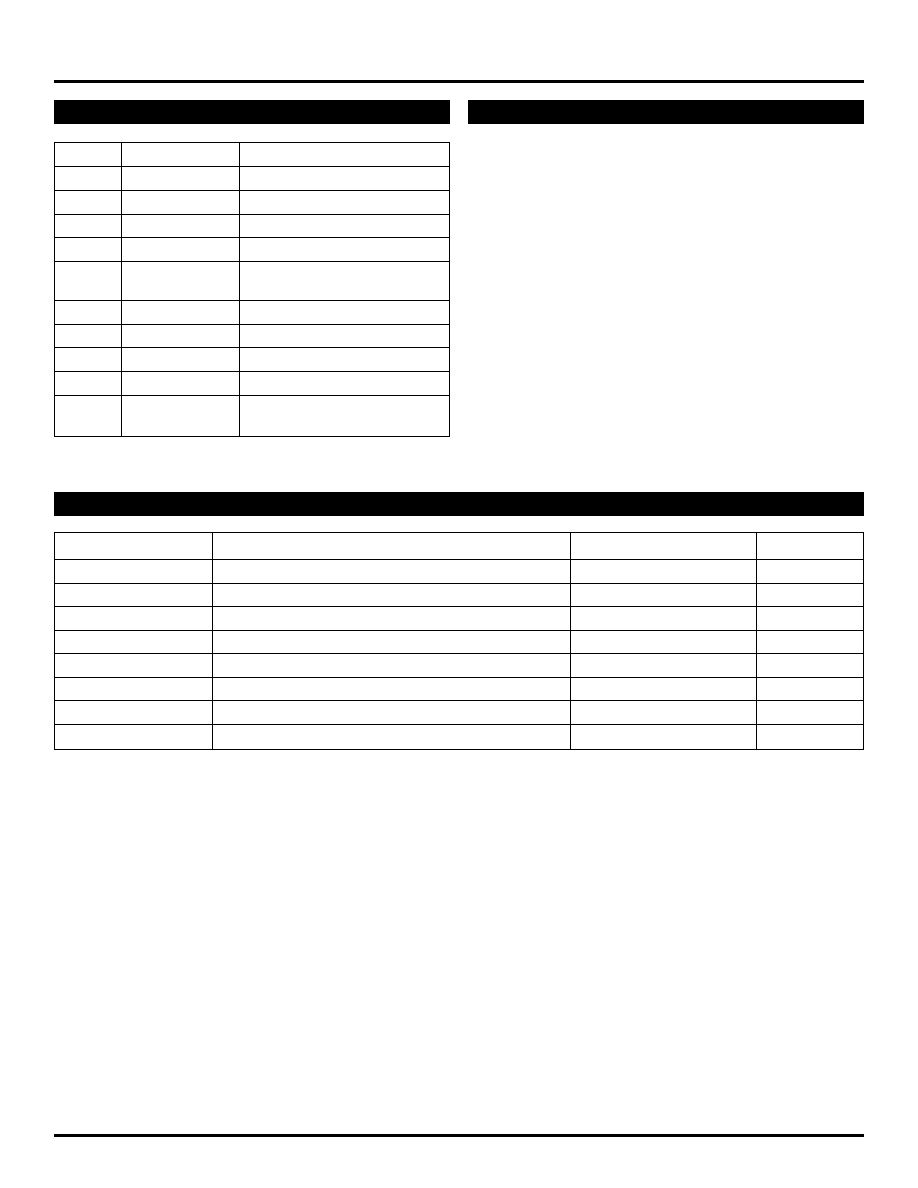

The SD output is a TTL open collector output that

requires a pull-up resistor for proper operation, Figure 1.

SY88943V

SD

4.7k

to 10k

V

CC

Figure 1. SD Output with Desired Rise Time

FEATURES

5V/3.3V 2.5Gbps

LIMITING POST AMPLIFIER

WITH SIGNAL DETECT

SY88943V

APPLICATIONS

s

1.25Gbps and 2.5Gbps ethernet

s

531Mbps, 1062Mbps and 2.12Gbps Fibre Channel

s

622Mbps SONET

s

Gigabit interface converter

s

2.5Gbps SDH/SONET

s

2.5Gbps proprietary links

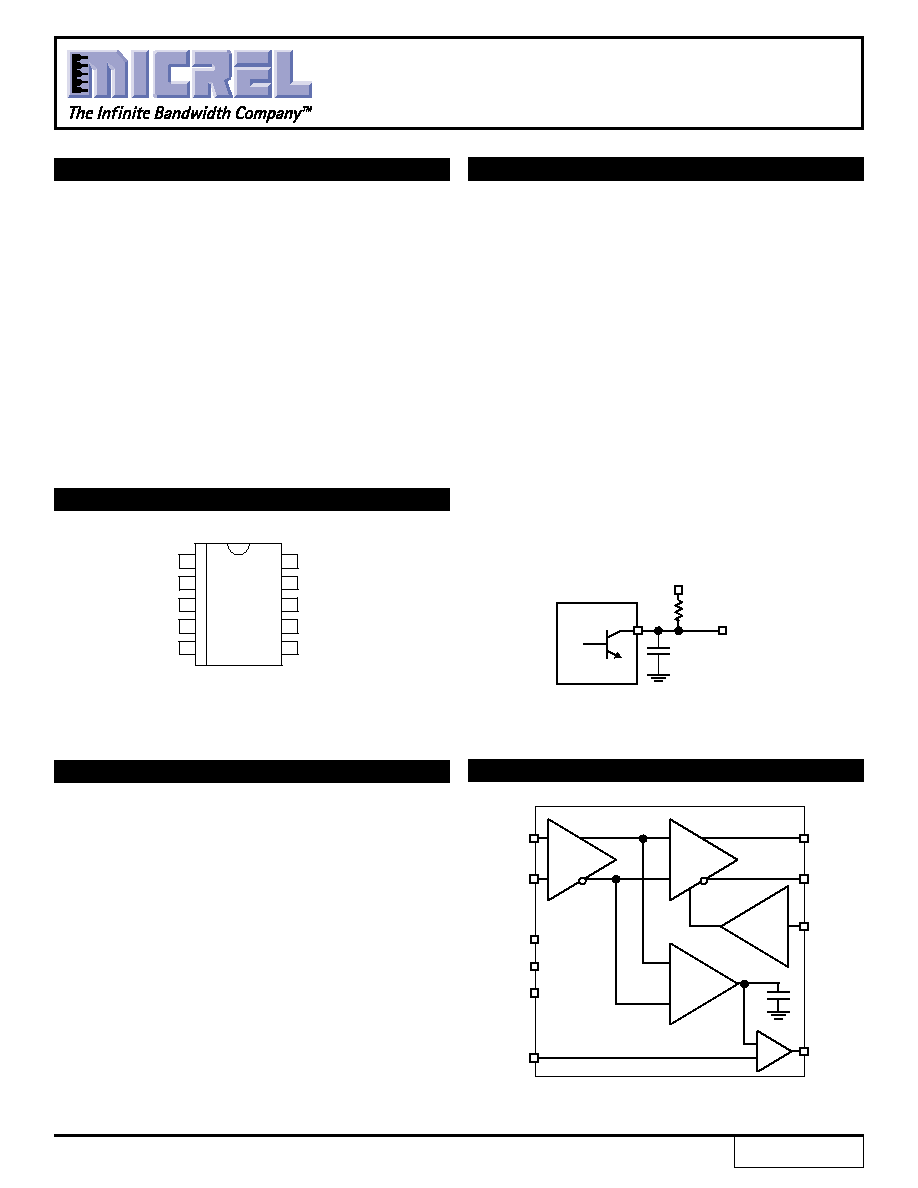

PIN CONFIGURATION

BLOCK DIAGRAM

1

EN

DIN

/DIN

VREF

SDLVL

10 VCC

DOUT

/DOUT

SD

GND

9

8

7

6

2

3

4

5

MSOP

K10-1

Limiting

Amplifer

ECL

Buffer

GND

Enable

Level

Detect

EN

SD

D

OUT

/D

OUT

D

IN

/D

IN

V

REF

V

CC

SD

LVL

1

Rev.: B

Amendment: /0

Issue Date:

August 2000

2

SY88943V

Micrel

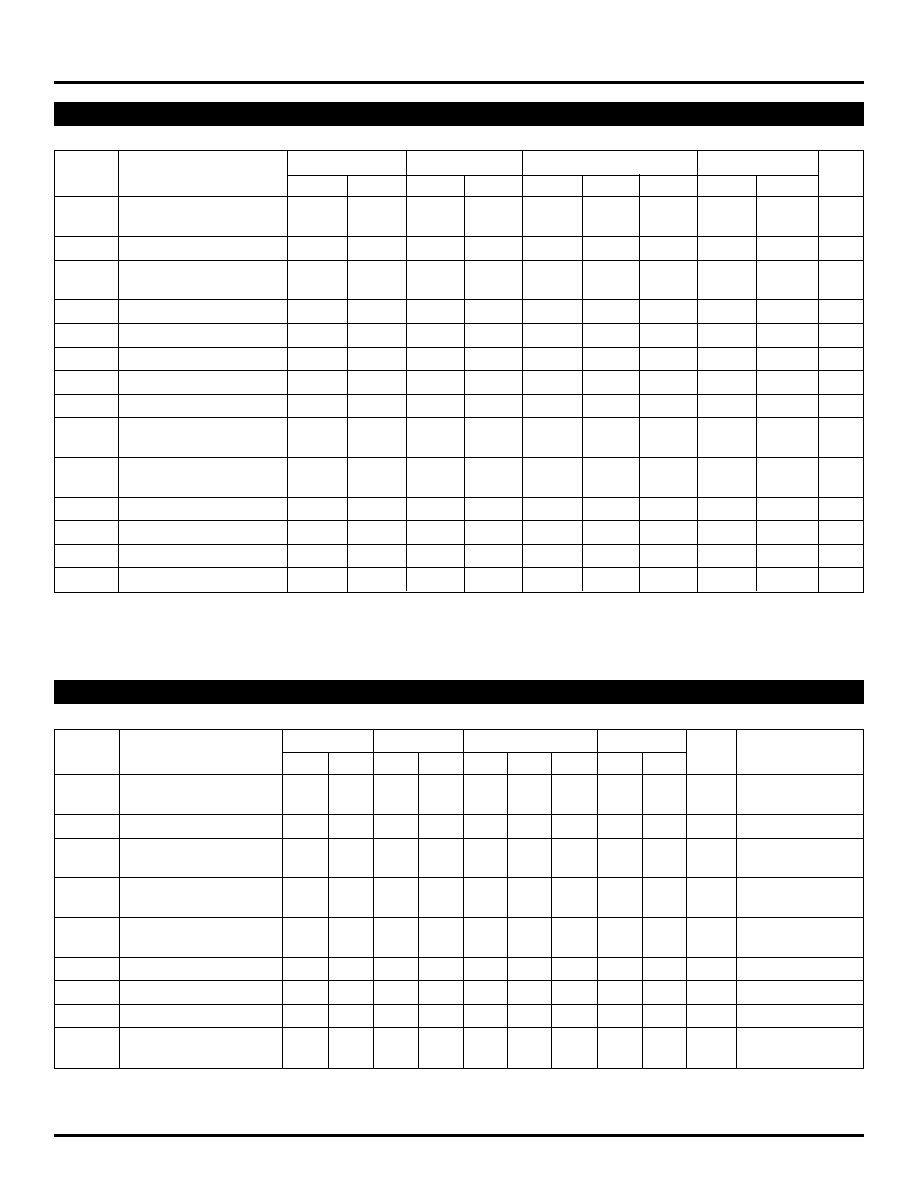

General

The SY88943V is an integrated limiting amplifier intended

for high-frequency fiber-optic applications. The circuit

connects to typical transimpedance amplifiers found within

a fiber-optics link. The linear signal output from a

transimpedance amplifier can contain significant amounts

of noise, and may vary in amplitude over time. The

SY88943V limiting amplifier quantizes the signal and outputs

a voltage-limited waveform.

The EN pin allows the user to disable the output signal

without removing the input signal.

GENERAL DESCRIPTION

Symbol

Rating

Value

Unit

V

CC

Power Supply Voltage

0 to +7.0

V

D

IN

, /D

IN

Input Voltage

0 to V

CC

V

D

OUT

, /D

OUT

Output Voltage (with 50

load)

V

CC

≠2.5 to V

CC

+0.3

V

EN

Input Voltage

0 to V

CC

V

SD

LVL

Input Voltage

0 to V

CC

V

V

REF

Output Voltage

V

CC

≠2.0 to V

CC

V

T

A

Operating Temperature Range

≠40 to +85

∞

C

T

store

Storage Temperature Range

≠55 to +125

∞

C

ABSOLUTE MAXIMUM RATINGS

(1)

NOTE:

1. Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. This is a stress rating only and functional operation is not implied

at conditions other than those detailed in the operational sections of this data sheet. Exposure to ABSOLUTE MAXIMUM RATlNG conditions for extended

periods may affect device reliability.

Pin

Type

Function

D

IN

Data Input

Data Input

/D

IN

Data Input

Inverting Data Input

SD

LVL

Input

SD Level Set

EN

TTL Input

Output Enable (Active High)

SD

TTL Output

Signal Detect

(Open Collector)

GND

Ground

Ground

/D

OUT

PECL Output

Inverting Data Output

D

OUT

PECL Output

Data Output

V

CC

Power Supply

Positive Power Supply

V

REF

Output

Reference Voltage Output for

SD Level Set (see Fig. 3)

PIN NAMES

3

SY88943V

Micrel

T

A

= ≠40

∞

C

T

A

= 0

∞

C

T

A

= +25

∞

C

T

A

= +85

∞

C

Symbol

Parameter

Min.

Max.

Min.

Max.

Min.

Typ.

Max.

Min.

Max.

Unit

I

CC

Power Supply

5V

--

40

--

40

--

33

40

--

45

mA

Current

(1)

3.3V

--

40

--

40

--

28

40

--

45

I

IL

EN Input LOW Current

≠0.3

(6)

--

≠0.3

(6)

--

≠0.3

(6)

--

--

≠0.3

(6)

--

mA

I

IH

EN Input HIGH Current

--

20

(4)

--

20

(4)

--

--

20

(4)

--

20

(4)

µ

A

--

100

(5)

--

100

(5)

--

--

100

(5)

--

100

(5)

V

CMR

Common Mode Range

GND +2.0

V

CC

GND +2.0

V

CC

GND +2.0

--

V

CC

GND +2.0

V

CC

V

V

offset

Differential Output Offset

--

±

100

--

±

100

--

±

17

±

100

--

±

100

mV

SD

LVL

SD

LVL

Level

V

REF

V

CC

V

REF

V

CC

V

REF

--

V

CC

V

REF

V

CC

V

V

OL

SD Output Low Level

(2)

--

0.5

--

0.5

--

--

0.5

--

0.5

V

I

OH

SD Output Leakage

(3)

--

100

--

100

--

--

100

--

100

µ

A

V

OH

D

OUT

and /D

OUT

V

CC

-1085

V

CC

-880 V

CC

-1025 V

CC

-880 V

CC

-1025 V

CC

-955 V

CC

-880 V

CC

-1025

V

CC

-880

mV

HIGH Output

V

OL

D

OUT

and /D

OUT

V

CC

-1830 V

CC

-1555 V

CC

-1810 V

CC

-1620 V

CC

-1810 V

CC

-1705 V

CC

-1620 V

CC

-1810 V

CC

- 1620

mV

LOW Output

V

REF

Reference Supply

V

CC

-1.38 V

CC

-1.26 V

CC

-1.38 V

CC

-1.26 V

CC

-1.38 V

CC

-1.32 V

CC

-1.26

V

CC

-1.38 V

CC

-1.26

V

I

REF

V

REF

Output Current

≠0.8

0.5

≠0.8

0.5

≠0.8

--

0.5

≠0.8

0.5

mA

V

IH

EN Input HIGH Voltage

2.0

--

2.0

--

2.0

--

--

2.0

--

V

V

IL

EN Input LOW Voltage

--

0.8

--

0.8

--

--

0.8

--

0.8

V

NOTES:

1. No output load

2. I

OL

= + 2mA

3. V

OH

= 5.5V

DC ELECTRICAL CHARACTERISTICS

V

CC

= +5V

±

10%, R

LOAD

= 50

to V

CC

≠2V

4. V

IN

= 2.7V

5. V

IN

= V

CC

6. V

IN

= 0.5V

T

A

= ≠40

∞

C

T

A

= 0

∞

C

T

A

= +25

∞

C

T

A

= +85

∞

C

Symbol

Parameter

Min.

Max.

Min.

Max.

Min.

Typ.

Max.

Min.

Max.

Unit

Conditions

PSRR

Power Supply

(1)

--

--

--

--

--

35

--

--

--

dB

Input referred,

Rejection Ratio

55MHz

V

ID

Input Voltage Range

5

1800

5

1800

5

--

1800

5

1800 mVp-p

V

OD

Differential Output

--

--

--

--

--

700

--

--

--

mV

V

ID

= 15mVp-p

Voltage Swing

(2)

--

--

--

--

--

300

--

--

--

mV

V

ID

= 5mVp-p

t

ONL

SD Release Time

(3)

--

0.5

--

0.5

--

0.2

0.5

--

0.5

µ

s

Minimum Input

t

ONH

SD Release Time

(4)

--

0.5

--

0.5

--

0.2

0.5

--

0.5

µ

s

Maximum Input

t

OFFL

SD Assert Time

(3)

--

0.5

--

0.5

--

0.1

0.5

--

0.5

µ

s

V

SR

SD Sensitivity Range

5

50

5

50

5

--

50

5

50

MVp-p

2

23

-1 pattern

HYS

SD Hysteresis

2

8

2

8

2

4.6

8

2

8

dB

2

23

-1 pattern

t

r

, t

f

Output Rise/Fall Time

--

175

--

175

--

150

175

--

175

ps

V

ID

> 100mVp-p

--

--

--

--

--

t

rin

,t

fin

--

--

--

V

ID

< 100mVp-p

AC ELECTRICAL CHARACTERISTICS

V

CC

= +5V

±

10%, R

LOAD

= 50

to V

CC

≠2V

3. Input is a 200MHz square wave, tr < 300ps, 8mVp-p.

4. Input is a 200MHz square wave, tr < 300ps, 1.8Vp-p.

NOTES:

1. Input referred noise = RMS output noise/low frequency gain.

2. Input is a 622MHz square wave.

4

SY88943V

Micrel

PRODUCT ORDERING CODE

Ordering

Package

Operating

Code

Type

Range

SY88943VKC

K10-1

Commercial

SY88943VKCTR

K10-1

Commercial

Output Termination

The SY88943V outputs must be terminated with a 50

load to V

CC

≠2V (or Thevenin equivalent).

Layout and PCB Design

Since the SY88943V is a high-frequency component,

performance can be largely determined by the board layout

and design. A common problem with high-gain amplifiers is

the feedback from the large swing outputs to the input via

the power supply.

DESIGN PROCEDURE

The SY88943V ground pin should be connected to the

circuit board ground. Use multiple PCB vias close to the

part to connect to ground. Avoid long, inductive runs which

can degrade performance.

R2

◊

1.32V

R1 + R2

NOTES:

SD

LVL

= V

CC

-1.32V +

R1 + R2

2.6k

R1

R2

SD

LVL

V

REF

V

CC

Figure 3. SD

LVL

Circuit

D

IN≠

50

50

0.1

µ

F

0.1

µ

F

0.1

µ

F

D

IN+

V

REF

Figure 2. Differential Input Configuration

5

SY88943V

Micrel

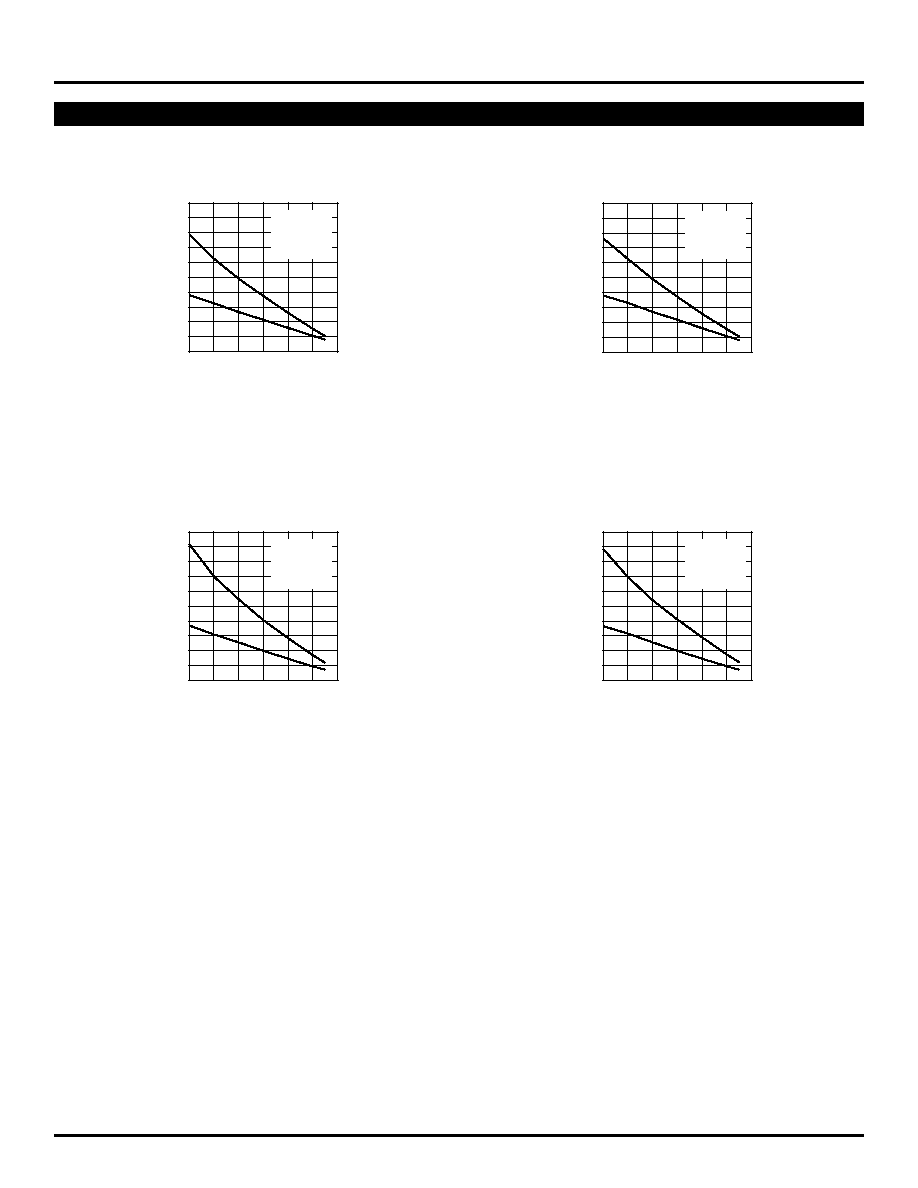

PERFORMANCE CURVE

0

10

20

30

40

50

60

70

80

90

100

0

-0.2 -0.4 -0.6 -0.8 -1.0 -1.2

INPUT LEVEL (mVp-p)

SD

LVL

= V

CC

≠ V (V)

SD Assert and Deassert Levels

vs SD

LVL

3.3V

T

A

= 25

∞

C

2.5Gbps

Pattern 2

23

-1

Figure 4.

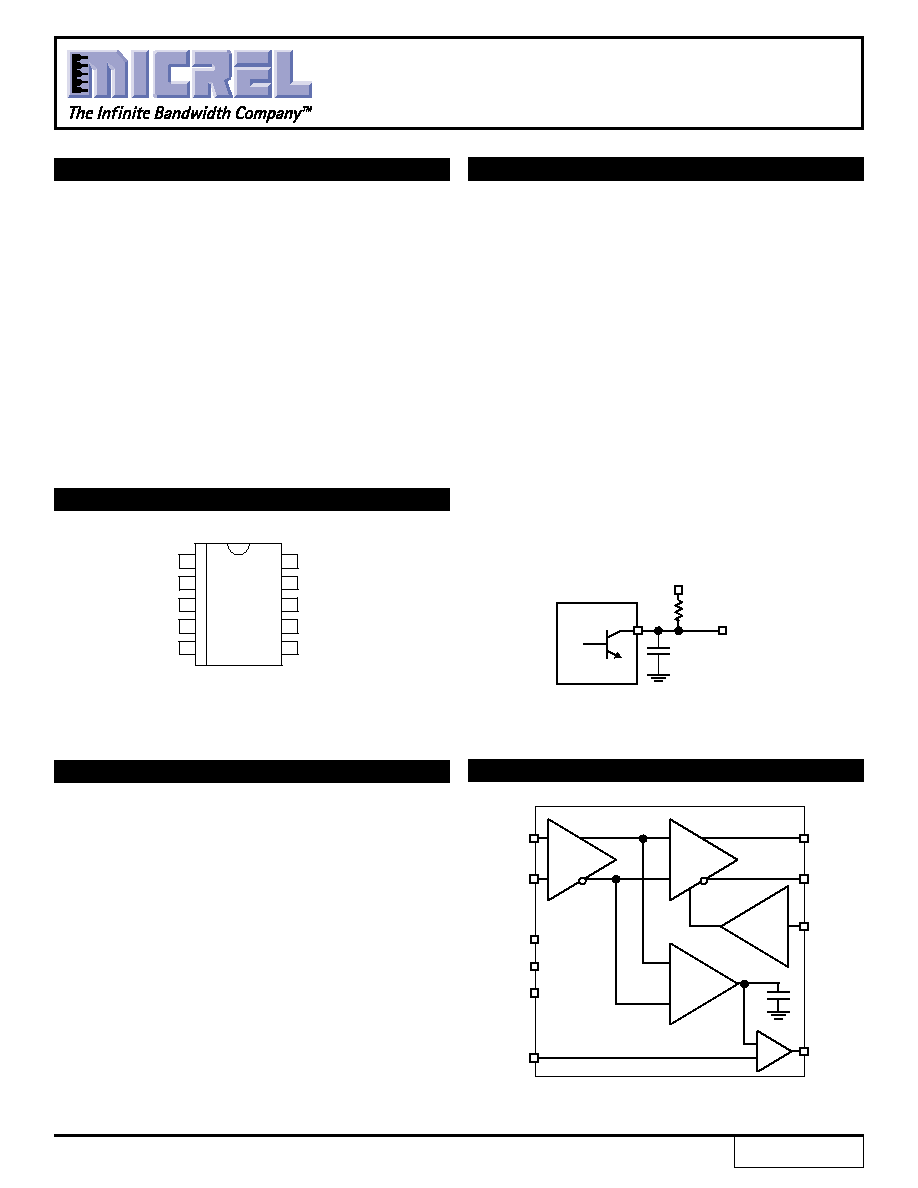

0

10

20

30

40

50

60

70

80

90

100

0

-0.2 -0.4 -0.6 -0.8 -1.0 -1.2

INPUT LEVEL (mVp-p)

SD

LVL

= V

CC

≠ V (V)

SD Assert and Deassert Levels

vs SD

LVL

5.0V

T

A

= 25

∞

C

2.5Gbps

Pattern 2

23

-1

Figure 5.

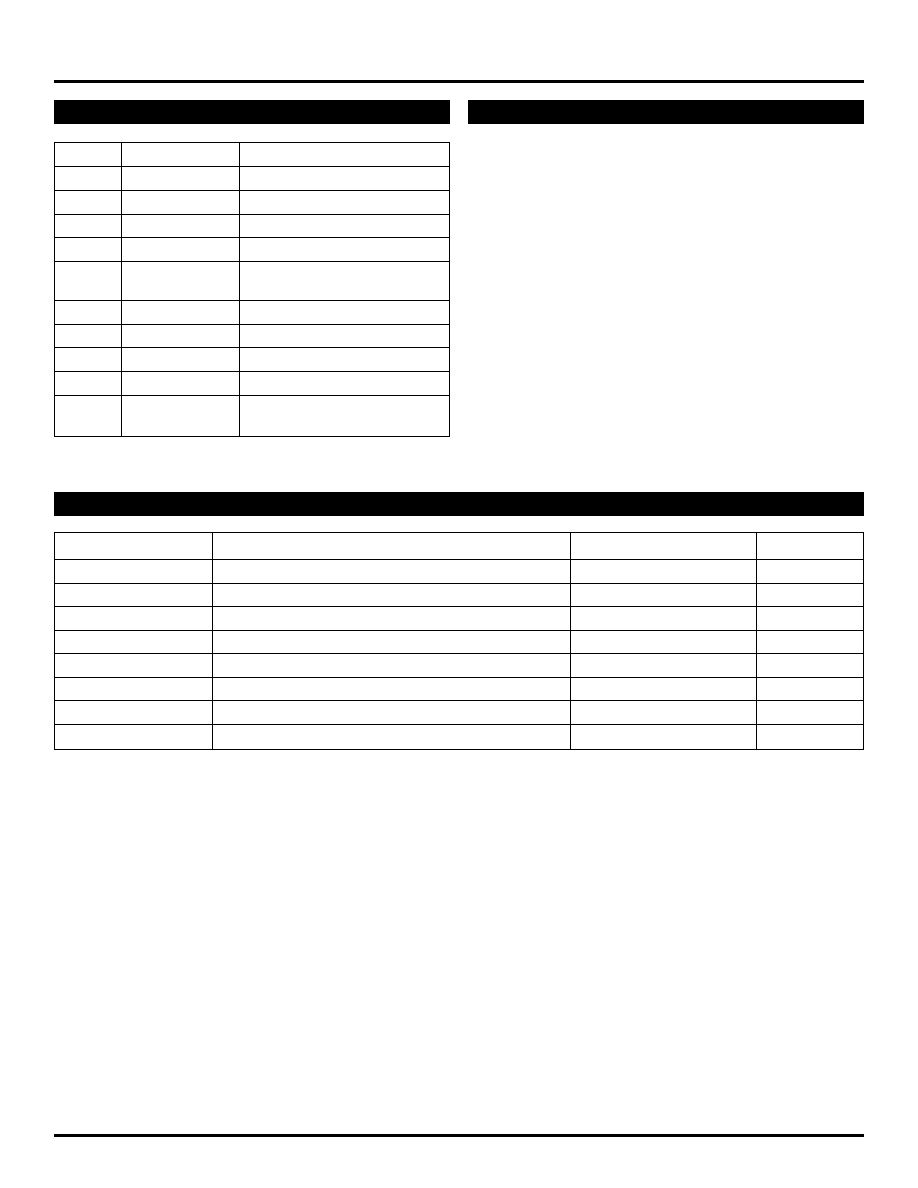

0

10

20

30

40

50

60

70

80

90

100

0

-0.2 -0.4 -0.6 -0.8 -1.0 -1.2

INPUT LEVEL (mVp-p)

SD

LVL

= V

CC

≠ V (V)

SD Assert and Deassert Levels

vs SD

LVL

3.3V

T

A

= 25

∞

C

2.5Gbps

Pattern 2

7

-1

Figure 6.

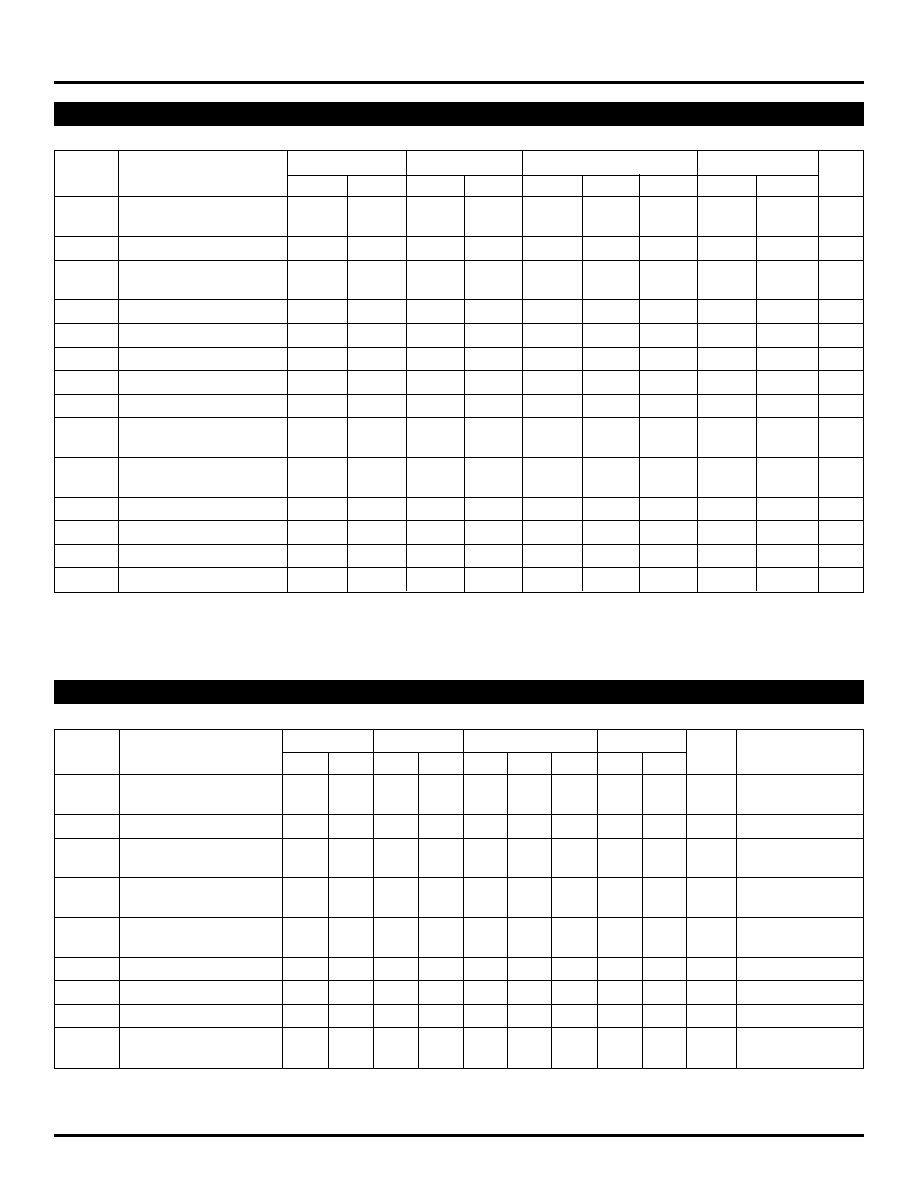

0

10

20

30

40

50

60

70

80

90

100

0

-0.2 -0.4 -0.6 -0.8 -1.0 -1.2

INPUT LEVEL (mVp-p)

SD

LVL

= V

CC

≠ V (V)

SD Assert and Deassert Levels

vs SD

LVL

5.0V

T

A

= 25

∞

C

2.5Gbps

Pattern 2

7

-1

Figure 7.