DESCRIPTION

Selects among four differential inputs

Guaranteed AC performance over temp and voltage:

∑ DC-to > 3.2Gbps data rate throughput

∑ < 600ps In-to-Out T

pd

∑ < 150ps T

r

/T

f

Ultra-low jitter design:

∑ < 1ps

rms

random jitter

∑ < 10ps

p-p

deterministic jitter

∑ < 10ps

p-p

total jitter (clock)

∑ < 0.7ps

rms

crosstalk-induced jitter

Unique input isolation design minimizes crosstalk

Internal input termination

Unique input termination and V

T

pin accepts DC-

coupled and AC-coupled inputs (LVDS, LVPECL,

CML)

350mV LVDS output swing

CMOS/TTL compatible Mux select

Power supply 3.3V +10%

≠40

∞

C to +85

∞

C temperature range

Available in 32-pin (5mm

◊◊

◊◊

◊

5mm) MLFTM package

FEATURES

3.3V, 3.2Gbps DIFFERENTIAL

4:1 LVDS MULTIPLEXER with

INTERNAL INPUT TERMINATION

Precision EdgeTM

SY89545L

APPLICATIONS

SONET/SDH channel select applications

Fiber Channel multi-channel select applications

Gigabit Ethernet multi-channel select

1

Rev.: A

Amendment: /0

Issue Date:

December 2003

The SY89545L is a fast, low jitter 4:1 differential mux

with an LVDS (350mV) compatible output with guaranteed

data rate throughput of 3.2Gbps over temperature and

voltage.

The SY89545L differential inputs include a unique, 3-pin

internal termination that allows access to the termination

network through a V

T

pin. This feature allows the device to

easily interface to different logic standards, both AC- and

DC-coupled without external resistor-bias and termination

networks. The result is a clean, stub-free, low jitter interface

solution.

The SY89545L operates from a single 3.3V supply, and

is guaranteed over the full industrial temperature range

(≠40

∞

C to +85

∞

C). For applications that require a 2.5V supply,

consider the SY89544U. For applications that require two

differential outputs, consider the SY89546U or

SY89545L.The SY89545L is part of a Micrel's Precision

EdgeTM product family. All support documentation can be

found on Micrel's web site at www.micrel.com.

TYPICAL PERFORMANCE

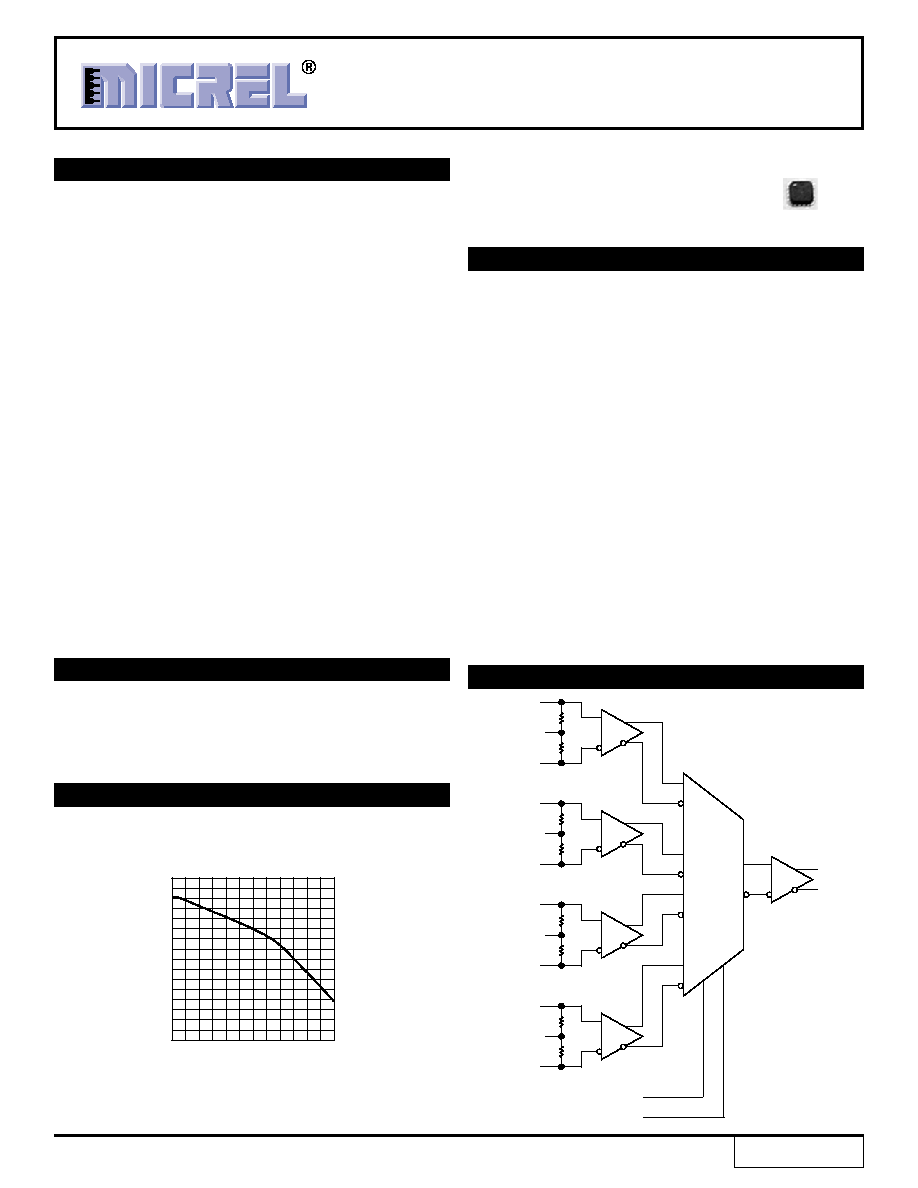

FUNCTIONAL BLOCK DIAGRAM

Precision EdgeTM

IN0

/IN0

V

T0

50

50

IN1

/IN1

V

T1

50

50

Q

/Q

0

1

MUX

4:1 MUX

LVDS

IN2

/IN2

V

T2

50

50

2

IN3

/IN3

V

T3

50

50

3 S0

S1

SEL0

SEL1

Precision Edge is a trademark of Micrel, Inc.

Micro

LeadFrame and MLF are trademarks of Amkor Technology, Inc.

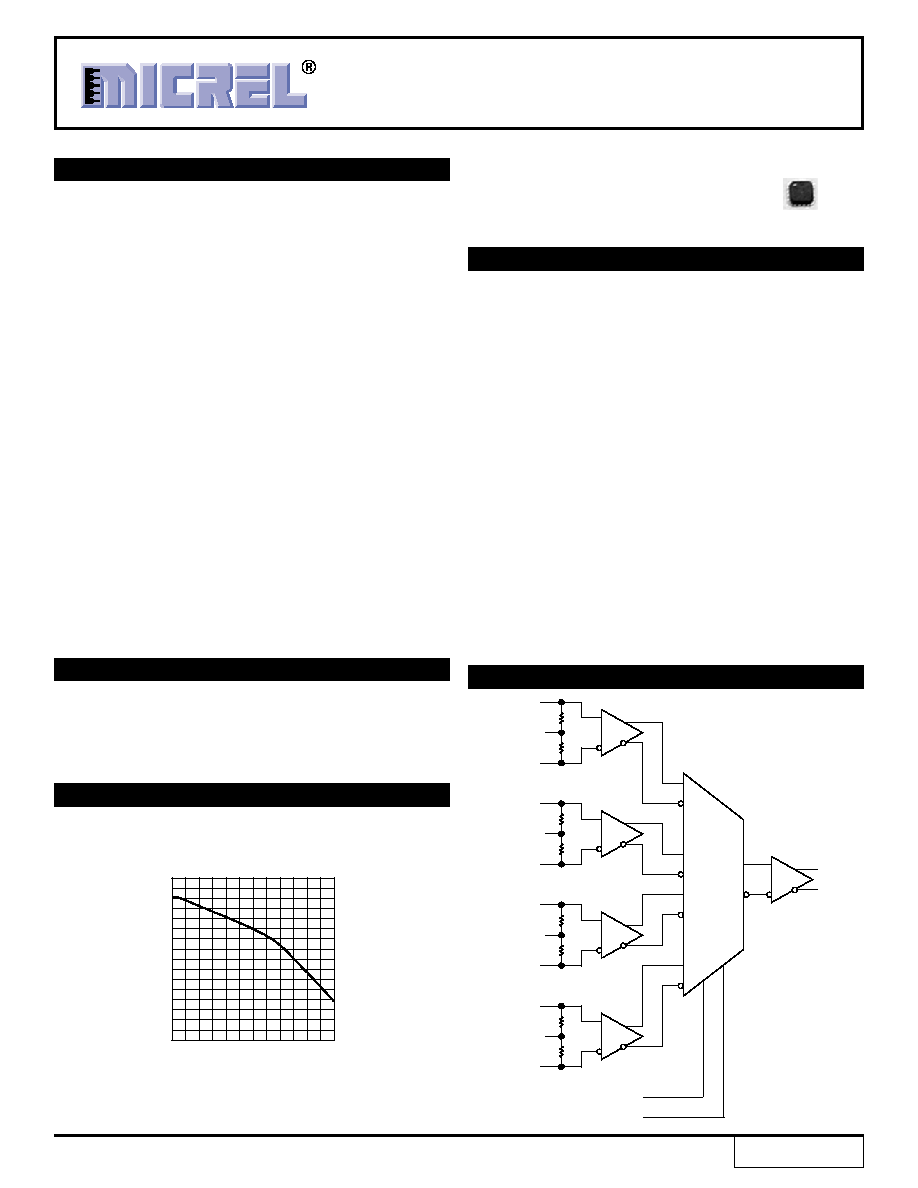

0

50

100

150

200

250

300

350

400

0

1

2

3

4

5

6

OUTPUT AMPLITUDE (mV)

FREQUENCY (GHz)

Output Amplitude

vs. Frequency

M9999-121503

hbwhelp@micrel.com or (408) 955-1690

2

Precision EdgeTM

SY89545L

Micrel

M9999-121503

hbwhelp@micrel.com or (408) 955-1690

PACKAGE/ORDERING INFORMATION

Ordering Information

(1)

Package

Operating

Package

Part Number

Type

Range

Marking

SY89545LMI

MLF-32

Industrial

SY89545L

SY89545LMITR

(2)

MLF-32

Industrial

SY89545L

Notes:

1. Contact factory for die availability. Dice are guaranteed at

T

A

= 25

∞

C, DC Electricals Only.

2. Tape and Reel

Pin Number

Pin Name

Pin Function

4, 2, 32,

IN0, /IN0,

Differential Inputs: These input pairs are the differential signal inputs to the device. Inputs

30, 27, 25, 23, 21

IN1, /IN1,

accept AC- or DC-coupled signals as small as 100mV. Each pin of a pair internally

IN2, /IN2,

terminates to a V

T

pin through 50

. Note that these inputs will default to an indeterminate

IN3, /IN3

state if left open. Unused differential input pairs can be terminated by connecting one input

to V

CC

and the complementary input to GND through a 1k

resistor. The V

T

pin is to be

left open in this configuration. Please refer to the

"Input Interface Applications"

section for

more details.

3, 31, 26, 22

VT0, VT1,

Input Termination Center-Tap: Each side of the differential input pair, terminates to a V

T

VT2, VT3

pin. The V

T0

, V

T1

, V

T2

, V

T3

pins provide a center-tap to a termination network for

maximum interface flexibility. See

"Input Interface Applications"

section for more details.

6, 19

SEL0, SEL1

These single-ended TTL/CMOS compatible inputs select the inputs to the multiplexers.

Note that these inputs are internally connected to a 25k

pull-up resistor and will default

to a logic HIGH state if left open.

1, 5, 8,

VCC

Positive Power Supply: Bypass with 0.1

µ

F

0.01

µ

F low ESR capacitors. The 0.01

µ

F

17, 20, 24, 28, 29

capacitor should be as close to V

CC

pin as possible.

10, 11

Q, /Q

Differential Outputs: This LVDS output pair is the output of the device. It is a

logic function of the IN0, IN1, IN0, IN1 and SEL0 inputs. Please refer to the

"Truth Table'

"

for details.

7, 9, 12, 13, 16, 18

GND,

Ground: Ground pin and exposed pad must be connected to the same ground plane.

Exposed pad

14, 15

NC

No connect. (Unused pins).

PIN DESCRIPTION

1

2

3

4

5

6

7

8

24

23

22

21

20

19

18

17

9 10 11 12 13 14 15 16

32 3130 29 28 27 26 25

VCC

/IN0

VT0

IN0

VCC

SEL0

GND

VCC

VCC

IN3

VT3

/IN3

VCC

SEL1

GND

VCC

VCC

VCC

/IN1

VT1

IN1

IN2

VT2

/IN2

GND

GND

/Q

Q

GND

NC

NC

GND

32-Pin MLFTM

3

Precision EdgeTM

SY89545L

Micrel

M9999-121503

hbwhelp@micrel.com or (408) 955-1690

Absolute Maximum Ratings

(1)

Supply Voltage (V

CC

) ............................... ≠ 0.5V to + 4.0V

Input Voltage (V

IN

) ........................................ ≠0.5V to V

CC

Termination Current

(3)

Source or sink current on V

T .....................................

±

100mA

Input Current

Source or sink current on IN, /IN ..........................

±

50mA

Lead Temperature (soldering, 10 sec.) ................... +220

∞

C

Storage Temperature (TS) ...................... ≠65

∞

C to +150

∞

C

Operating Ratings

(2)

Supply Voltage (V

CC

) ..................................... 3.0V to 3.6V

Ambient Temperature (T

A

) ........................ ≠40

∞

C to +85

∞

C

Package Thermal Resistance

(4)

MLFTM (

JA

)

Still-Air ................................................................ 35

∞

C/W

500lfpm .............................................................. 28

∞

C/W

MLFTM (

JB

)

Junction-to-Board ............................................... 20

∞

C/W

T

A

= ≠40

∞

C to +85

∞

C; Unless otherwise stated.

Symbol

Parameter

Condition

Min

Typ

Max

Units

V

CC

Power Supply

3.0

3.3

3.6

V

I

CC

Power Supply Current

No Load, Max. V

CC

(6)

44

60

mA

R

DIFF_IN

Differential Input Resistance

80

100

120

(IN-to-/IN)

R

IN

Input Resistance

40

50

60

(IN-to-V

T

, /IN-to-V

T

)

V

IH

Input High Voltage

Note 7

V

CC

≠1.6

V

CC

V

(IN, /IN)

V

IL

Input Low Voltage

Note 7

0

V

IH

≠0.1

V

(IN, /IN)

V

IN

Input Voltage Swing

Notes 7, 8

100

V

CC

mV

(IN, /IN)

V

DIFF_IN

Differential Input Voltage Swing

Notes 7, 8

200

2

◊

V

CC

mV

| IN - /IN |

IN-to-V

T

Voltage from Input to V

T

1.8

V

Notes:

1. Permanent device damage may occur if

"Absolute Maximum Ratings"

are exceeded. This is a stress rating only and functional operation is not

implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to

"Absolute Maximum Ratings"

conditions for

extended periods may affect device reliability.

2. The data sheet limits are not guaranteed if the device is operated beyond the operating ratings.

3. Due to the limited drive capability use for input of the same package only.

4. Package thermal resistance assumes exposed pad is soldered (or equivalent) to the device's most negative potential on the PCB.

JB

uses 4-layer

JA

in still air unless otherwise stated.

5. The circuit is designed to meet the DC specifications shown in the above table after thermal equilibrium has been established.

6. Includes current through internal 50

pull-ups.

7. V

IH

(min) not lower than 1.2V.

8. See

"Operating Characteristics"

section for V

IN

and V

DIFF_IN

definition.

DC ELECTRICAL CHARACTERISTICS

(5)

4

Precision EdgeTM

SY89545L

Micrel

M9999-121503

hbwhelp@micrel.com or (408) 955-1690

V

CC

= 3.3V

±

10%; T

A

= ≠40

∞

C to +85

∞

C; R

L

= 100

across Q and /Q, unless otherwise stated.

Symbol

Parameter

Condition

Min

Typ

Max

Units

V

OH

Output HIGH Voltage

See Figure 5a

1.475

V

(Q, /Q)

V

OL

Output LOW Voltage

See Figure 5a

0.925

V

(Q, /Q)

V

OUT

Output Voltage Swing

See Figures 1a, 5a

250

350

mV

(Q, /Q)

V

DIFF-OUT

Differential Output Voltage Swing

See Figure 1b

500

700

mV

| Q - /Q |

V

OCM

Output Common Mode Voltage

See Figure 5b

1.125

1.275

V

(Q, /Q)

V

OCM

Change in Common Mode Voltage

See Figure 5b

≠50

+50

mV

(Q, /Q)

LVDS OUTPUTS DC ELECTRICAL CHARACTERISTICS

(9)

V

CC

= 3.3V

±

10%; T

A

= ≠40

∞

C to +85

∞

C; unless otherwise stated.

Symbol

Parameter

Condition

Min

Typ

Max

Units

V

IH

Input HIGH Voltage

2.0

V

CC

V

V

IL

Input LOW Voltage

0.8

V

I

IH

Input HIGH Current

40

µ

A

I

IL

Input LOW Current

≠300

µ

A

Note:

9. The circuit is designed to meet the DC specifications shown in the above table after thermal equilibrium has been established.

LVTTL/CMOS DC ELECTRICAL CHARACTERISTICS

(9)

5

Precision EdgeTM

SY89545L

Micrel

M9999-121503

hbwhelp@micrel.com or (408) 955-1690

V

CC

= 3.3V

±

10%; T

A

= ≠40

∞

C to +85

∞

C; R

L

= 100

across Q and /Q, unless otherwise stated.

Symbol

Parameter

Condition

Min

Typ

Max

Units

f

MAX

Maximum Operating Frequency

NRZ Data

3.2

Gbps

V

OUT

200mV

Clock

3

GHz

t

pd

Differential Propagation Delay

IN-to-Q

400

500

600

ps

SEL-to-Q

230

500

750

ps

t

SKEW

Input-to-Input Skew

Note 11

25

ps

Part-to-Part Skew

Note 12

200

ps

t

JITTER

Data

Random Jitter (RJ)

Note 13

1

ps

rms

Deterministic Jitter (DJ)

Note 14

10

ps

p-p

Clock

Total Jitter (TJ)

Note 15

10

ps

p-p

Cycle-to-Cycle Jitter

Note 16

1

ps

rms

Crosstalk-Induced Jitter

Note 17

0.7

ps

rms

Adjacent Channel

t

R

, t

F

Output Rise / Fall Time

At full output swing

40

80

150

ps

(20% to 80%)

Notes:

10. Measured with 100mV input swing. See

"Timing Diagrams"

section for definition of parameters. High frequency AC-parameters are guaranteed by

design and characterization.

11. Input-to-input skew is the difference in propagation delay between any two inputs to the output under identical conditions.

12. Part-to-part skew is defined for two parts with identical power supply voltages at the same temperature and with no skew of the edges at the

respective inputs.

13. RJ is measured with a K28.7 comma detect character pattern, measured at 1.25Gbps and 3.2Gbps.

14. DJ is measured at 1.25Gbps and 3.2Gbps, with both K28.5 and 2

23

≠1 PRBS pattern.

15. Total jitter definition: with an ideal clock input of frequency

f

MAX

, no more than one output edge in 10

12

output edges will deviate by more than the

specified peak-to-peak jitter value.

16. Cycle-to-cycle jitter definition: the variation of periods between adjacent cycles, Tn-Tn-1 where T is the time between rising edges of the output

signal.

17. Crosstalk is measured at the output while applying two similar frequencies to adjacent inputs that are asynchronous with respect to each other at the

inputs.

AC ELECTRICAL CHARACTERISTICS

(10)