PRODUCTS AND SPECIFICATIONS DISCUSSED HEREIN ARE FOR EVALUATION AND REFERENCE PURPOSES ONLY AND ARE SUBJECT TO CHANGE BY

MICRON WITHOUT NOTICE. PRODUCTS ARE ONLY WARRANTED BY MICRON TO MEET MICRON'S PRODUCTION DATA SHEET SPECIFICATIONS.

09005aef80ca3ad1

128Mbx16Mobile_Addendum.fm - Rev. A 6/03 EN

1

©2003 Micron Technology, Inc. All rights reserved.

128Mb: x16

Mobile SDRAM Addendum

PRELIMINARY

SYNCHRONOUS

DRAM

MT48LC8M16LFFF ≠ 2 MEG x 16 x 4 BANKS

MT48G8M16LFFF ≠ 2 MEG x 16 x 4 BANKS

MT48V8M16LFFF≠ 2 MEG x 16 x 4 BANKS

This data sheet is an addendum. The complete 128Mb Mobile

SDRAM data sheet is at:

http://www.micron.com/products/

datasheet.jsp?path=/DRAM/Mobile&fileID=581

Features

∑ Temperature Compensated Self Refresh (TCSR)

∑ Fully synchronous; all signals registered on positive

edge of system clock

∑ Internal pipelined operation; column address can

be changed every clock cycle

∑ Internal banks for hiding row access/precharge

∑ Programmable burst lengths: 1, 2, 4, 8, or full page

∑ Auto Precharge, includes CONCURRENT auto

precharge, and Auto Refresh Modes

∑ Self Refresh Mode; standard and low power

∑ 64ms, 4,096-cycle refresh

∑ LVTTL-compatible inputs and outputs

∑ Low voltage power supply

∑ Partial Array Self Refresh power-saving mode

∑ Extended mode register (must be programmed)

NOTE:

1. IT supported only in LX version.

2. Lead-free.

Part Number Example:

MT48G8M16LFFF-8 XT

Figure 1: 54-Ball FBGA Pin Assignment

(Top View)

OPTIONS

MARKING

∑ V

DD

/V

DD

Q

3.3V

LC

3.0V

G

1

2.5V/2.5V-1.8V

V

∑ Configurations

8 Meg x 16 (2 Meg x 16 x 4 banks)

8M16

∑ Self Refresh

Supported

LF

Not Supported

LX

∑ Package/Ball out

Plastic Package

54-ball FBGA (8mm x 9mm)

FF

54-ball FBGA (8mm x 9mm)

BF

2

∑ Timing (Cycle Time)

8ns @ CL = 3 (125 MHz)

-8

10ns @ CL = 3 (100 MHz)

-10

∑ Operating Temperature Range

Mobile (-25∞C to +75∞C)

XT

Industrial(-40∞C to +85∞C)

IT

Table 1:

Address Table

8 MEG x16

Configuration

2 Meg x 16 x 4 banks

Refresh Count

4K

Row Addressing

4K (A0≠A11)

Bank Addressing

4 (BA0, BA1)

Column Addressing

512 (A0≠A8)

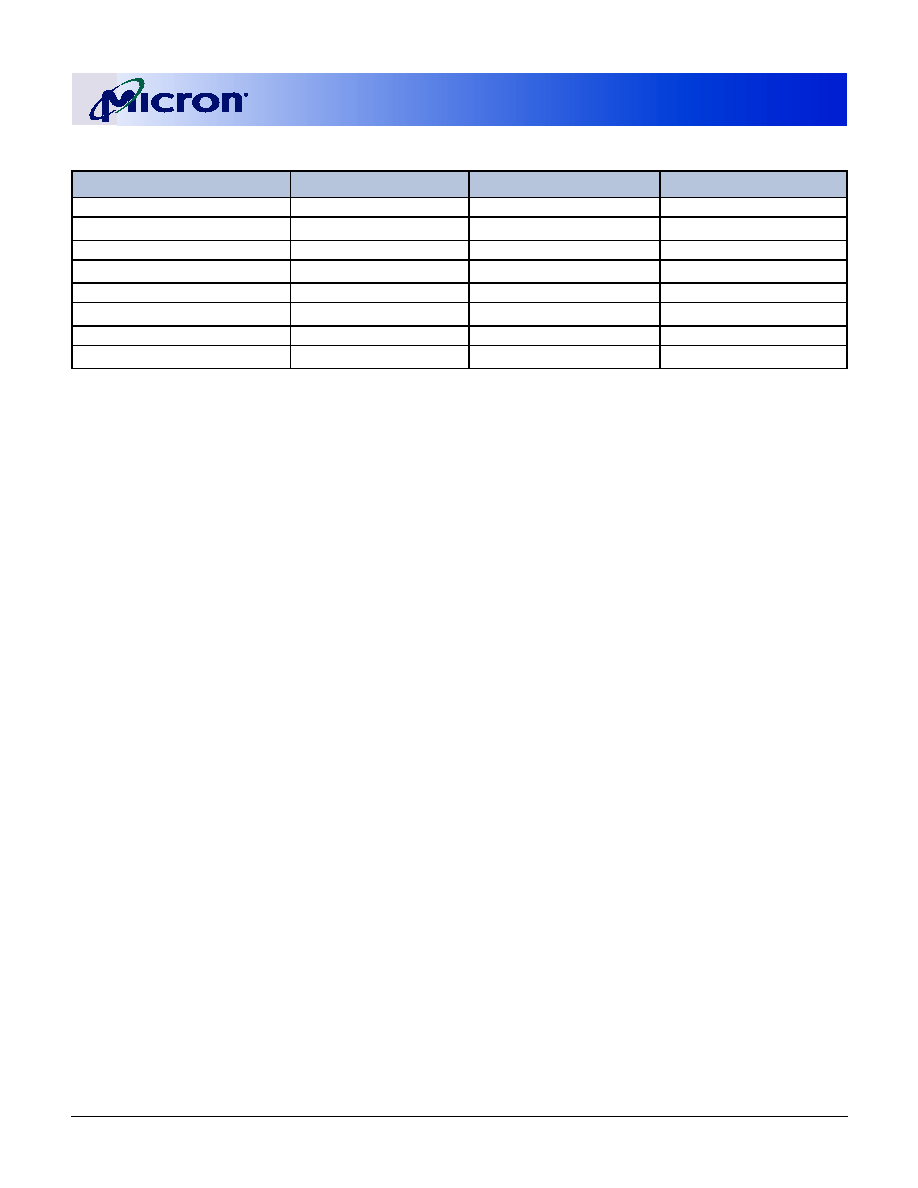

Table 2:

Key Timing Parameters

Maximums, based on

t

CK; CL = CAS (READ) latency

SPEED

GRADE

CLOCK

FREQUENCY

ACCESS TIME

t

RCD

t

RP

CL = 1 CL = 2 CL = 3

-8

125 MHz

≠

≠

6ns

20ns 20ns

-10

100 MHz

≠

≠

6ns

20ns 20ns

-8

100 MHz

≠

7ns

≠

20ns 20ns

-10

83 MHz

≠

7ns

≠

20ns 20ns

-8

50 MHz

18ns

≠

≠

20ns 20ns

-10

40 MHz

18ns

≠

≠

20ns 20ns

A

B

C

D

E

F

G

H

J

1 2 3 4 5 6 7 8

Top View

(Ball Down)

V

SS

DQ14

DQ12

DQ10

DQ8

UDQM

NC/A12

A8

V

SS

DQ15

DQ13

DQ11

DQ9

NC

CLK

A11

A7

A5

V

SS

Q

V

DD

Q

V

SS

Q

V

DD

Q

V

SS

CKE

A9

A6

A4

V

DD

Q

V

SS

Q

V

DD

Q

V

SS

Q

V

DD

CAS#

BA0

A0

A3

DQ0

DQ2

DQ4

DQ6

LDQM

RAS#

BA1

A1

A2

V

DD

DQ1

DQ3

DQ5

DQ7

WE#

CS#

A10

V

DD

9

128Mb: x16

Mobile SDRAM Addendum

PRELIMINARY

09005aef80ca3ad1

Micron Technology, Inc., reserves the right to change products or specifications without notice.

128Mbx16Mobile_Addendum.fm - Rev. A 6/03 EN

2

©2003 Micron Technology, Inc. All rights reserved.

NOTE:

1. Lead-free package.

General Description

The MicronÆ 128Mb SDRAM is a high-speed

CMOS, dynamic random-access memory containing

134,217,728 bits. It is internally configured as a quad-

bank DRAM with a synchronous interface (all signals

are registered on the positive edge of the clock signal,

CLK). Each of the x16's 33,554,432-bit banks is orga-

nized as 4,096 rows by 512 columns by 16 bits.

Read and write accesses to the SDRAM are burst ori-

ented; accesses start at a selected location and con-

tinue for a programmed number of locations in a

programmed sequence. Accesses begin with the regis-

tration of an ACTIVE command, which is then fol-

lowed by a READ or WRITE command. The address

bits registered coincident with the ACTIVE command

are used to select the bank and row to be accessed

(BA0, BA1 select the bank; A0-A11(x16) select the row).

The address bits registered coincident with the READ

or WRITE command are used to select the starting col-

umn location for the burst access.

The SDRAM provides for programmable read or

write burst lengths of 1, 2, 4, or 8 locations, or the full

page, with a burst terminate option. An auto precharge

function may be enabled to provide a self-timed row

precharge that is initiated at the end of the burst

sequence.

The 128Mb SDRAM uses an internal pipelined

architecture to achieve high-speed operation. This

architecture is compatible with the 2n rule of prefetch

architectures, but it also allows the column address to

be changed on every clock cycle to achieve a high-

speed, fully random access. Precharging one bank

while accessing one of the other three banks will hide

the precharge cycles and provide seamless high-speed,

random-access operation.

The 128Mb SDRAM is designed to operate in 3.3V or

3.0V or 2.5V low-power memory systems. An auto

refresh mode is provided, along with a power-saving,

power-down mode. All inputs and outputs are LVTTL-

compatible.

SDRAMs offer substantial advances in DRAM oper-

ating performance, including the ability to synchro-

nously burst data at a high data rate with automatic

column-address generation, the ability to interleave

between internal banks in order to hide precharge

time and the capability to randomly change column

addresses on each clock cycle during a burst access.

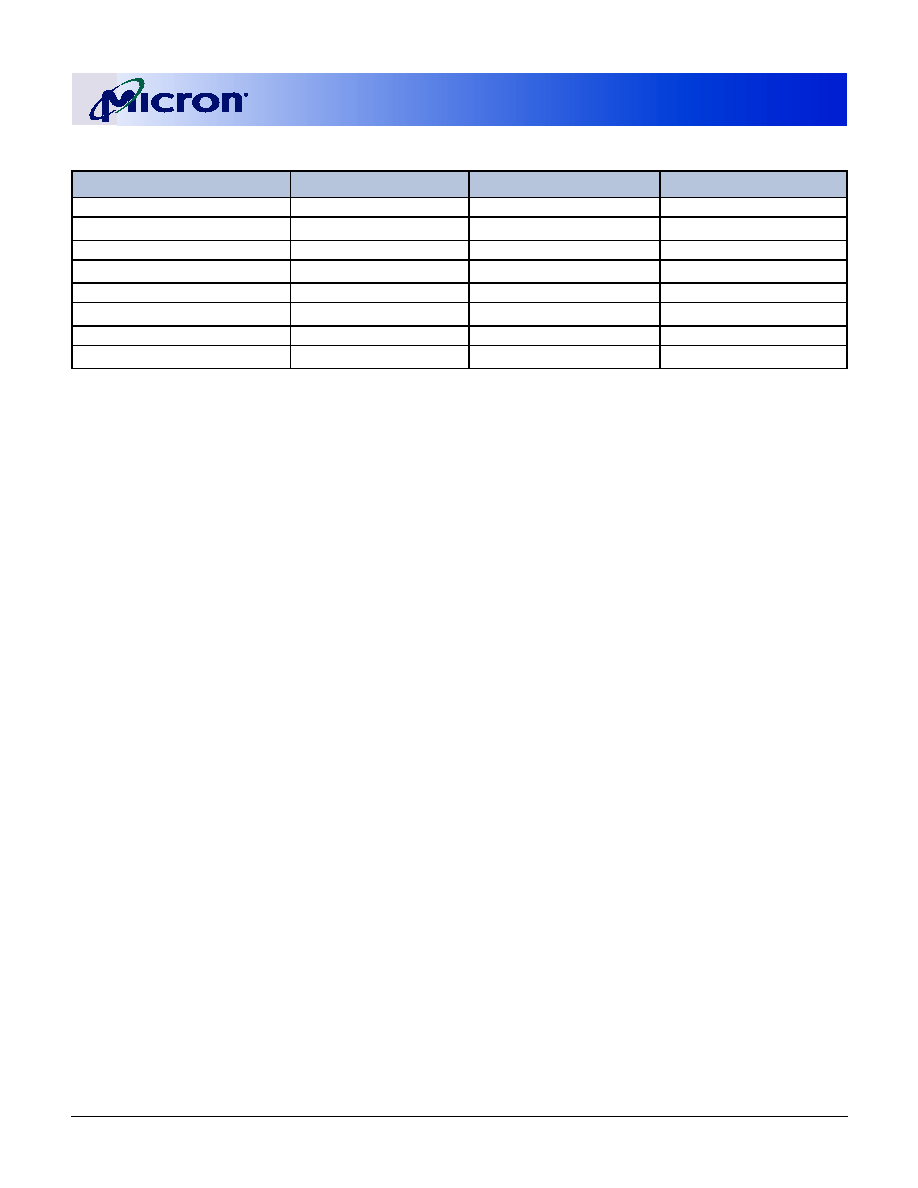

Table 3:

128Mb SDRAM Part Numbers

PART NUMBER

V

DD

/V

DD

Q

ARCHITECTURE

PACKAGE

MT48LC8M16LFFF-xx

3.3V / 3.3V

8 Meg x 16

54-BALL FBGA

MT48LC8M16LFBF-xx

3.3V / 3.3V

8 Meg x 16

54-BALL FBGA

1

MT48G8M16LFFF-xx

3.0V / 3.0V

8 Meg x 16

54-BALL FBGA

MT48G8M16LFBF-xx

3.0V / 3.0V

8 Meg x 16

54-BALL FBGA

1

MT48G8M16LXFF-xx

3.0V / 3.0V

8 Meg x 16

54-BALL FBGA

MT48G8M16LXBF-xx

3.0V / 3.0V

8 Meg x 16

54-BALL FBGA

1

MT48V8M16LFFF-xx

2.5V / 2.5V-1.8V

8 Meg x 16

54-BALL FBGA

MT48V8M16LFBF-xx

2.5V / 2.5V-1.8V

8 Meg x 16

54-BALL FBGA

1

128Mb: x16

Mobile SDRAM Addendum

PRELIMINARY

09005aef80ca3ad1

Micron Technology, Inc., reserves the right to change products or specifications without notice.

128Mbx16Mobile_Addendum.fm - Rev. A 6/03 EN

3

©2003 Micron Technology, Inc. All rights reserved.

Table 4:

Ball Descriptions

54-BALL FBGA

SYMBOL

TYPE

DESCRIPTION

F2

CLK

Input

Clock: CLK is driven by the system clock. All SDRAM input signals are sampled on

the positive edge of CLK. CLK also increments the internal burst counter and

controls the output registers.

F3

CKE

Input

Clock Enable: CKE activates (HIGH) and deactivates (LOW) the CLK signal.

Deactivating the clock provides PRECHARGE POWER-DOWN and SELF REFRESH

operation (all banks idle), ACTIVE POWER-DOWN (row active in any bank) or

CLOCK SUSPEND operation (burst/access in progress). CKE is synchronous except

after the device enters power-down and self refresh modes, where CKE becomes

asynchronous until after exiting the same mode. The input buffers, including

CLK, are disabled during power-down and self refresh modes, providing low

standby power. CKE may be tied HIGH.

G9

CS#

Input

Chip Select: CS# enables (registered LOW) and disables (registered HIGH) the

command decoder. All commands are masked when CS# is registered HIGH. CS#

provides for external bank selection on systems with multiple banks. CS# is

considered part of the command code.

F7, F8, F9

CAS#, RAS#,

WE#

Input

Command Inputs: CAS#, RAS#, and WE# (along with CS#) define the command

being entered.

E8, F1

LDQM,

UDQM

Input

Input/Output Mask: DQM is sampled HIGH and is an input mask signal for write

accesses and an output enable signal for read accesses. Input data is masked

during a WRITE cycle. The output buffers are placed in a High-Z state (two-clock

latency) when during a READ cycle. LDQM corresponds to DQ0≠DQ7, UDQM

corresponds to DQ8≠DQ15. LDQM and UDQM are considered same state when

referenced as DQM.

G7, G8

BA0, BA1

Input

Bank Address Input(s): BA0 and BA1 define to which bank the ACTIVE, READ,

WRITE or PRECHARGE command is being applied. These pins also provide the op-

code during a LOAD MODE REGISTER command

H7, H8, J8, J7,

J3, J2, H3, H2,

H1, G3, H9, G2

A0≠A11

Input

Address Inputs: A0≠A11 are sampled during the ACTIVE command (row- address

A0≠A11) and READ/WRITE command (column-address A0≠A8; with A10 defining

auto precharge) to select one location out of the memory array in the respective

bank. A10 is sampled during a PRECHARGE command to determine if all banks

are to be precharged (A10 HIGH) or bank selected by BA0, BA1 (LOW). The

address inputs also provide the op-code during a LOAD MODE REGISTER

command.

A8, B9, B8, C9,

C8, D9, D8, E9,

E1, D2, D1, C2,

C1, B2, B1, A2

DQ0≠DQ15

I/O

Data Input/Output: Data bus

E2, G1

NC

≠

No Connect: These pins should be left unconnected. G1 is a no connect for this

part but may be used as A12 in future designs.

A7, B3, C7, D3

V

DD

Q

Supply DQ Power: Provide isolated power to DQs for improved noise immunity.

A3, B7, C3, D7,

V

SS

Q

Supply DQ Ground: Provide isolated ground to DQs for improved noise immunity.

A9, E7, J9

V

DD

Supply Power Supply: Voltage dependant on option.

A1, E3, J1

V

SS

Supply Ground.

128Mb: x16

Mobile SDRAM Addendum

PRELIMINARY

09005aef80ca3ad1

Micron Technology, Inc., reserves the right to change products or specifications without notice.

128Mbx16Mobile_Addendum.fm - Rev. A 6/03 EN

4

©2003 Micron Technology, Inc. All rights reserved.

Absolute Maximum Ratings

Stresses greater than those listed may cause perma-

nent damage to the device. This is a stress rating only,

and functional operation of the device at these or any

other conditions above those indicated in the opera-

tional sections of this specification is not implied.

Exposure to absolute maximum rating conditions for

extended periods may affect reliability.

Table 5:

Absolute Maximum Ratings Table

PARAMETER/CONDITION

MIN

MAX

UNITS

Voltage on V

DD

/V

DD

Q Supply

Relative to V

SS

(3.3V)

-1

+4.6

V

Relative to V

SS

(3.0V)

-1

+4.6

V

Relative to V

SS

(2.5V)

-0.5

+3.6

V

Voltage on Inputs, NC or I/O Pins

Relative to V

SS

(3.3V)

-1

+4.6

V

Relative to V

SS

(3.0V)

-1

+4.6

V

Relative to V

SS

(2.5V)

-0.5

+3.6

V

Operating Temperature

T

A

(Mobile; XT parts)

-25

+75

∞C

T

A

(Industrial; IT parts)

-40

+85

∞C

Storage Temperature (plastic)

≠

-55 +150

∞C

Power Dissipation

≠

≠

1

W

Table 6:

DC Electrical Characteristics and Operating Conditions ≠ LC Version

Notes appear on standard 128Mb Mobile SDRAM data sheet; Vdd/VddQ = +3.3V ±0.3V

PARAMETER/CONDITION

SYMBOL

MIN

MAX

UNITS

NOTES

Supply Voltage

V

DD

3

3.6

V

I/O Supply Voltage

V

DD

Q

3

3.6

V

Input High Voltage: Logic 1; All inputs

V

IH

2

V

DD

+ 0.3

V

22

Input Low Voltage: Logic 0; All inputs

V

IL

-0.3

0.8

V

22

Data Output High Voltage: Logic 1; All inputs

V

OH

2.4

≠

V

Data Output LOW Voltage: LOGIC 0; All inputs

V

OL

≠

0.4

V

Input Leakage Current:

Any Input 0V

£ V

IN

£ V

DD

(All other

pins not under test = 0V)

I

I

-5

5

µA

Output Leakage Current: DQs are disabled; 0V

£ V

OUT

£ V

DD

Q

I

OZ

-5

5

µA

Table 7:

DC Electrical Characteristics and Operating Conditions ≠ G Version

Notes appear on standard 128Mb Mobile SDRAM data sheet; V

DD

/V

DDQ

= +3.0V ±0.4V

PARAMETER/CONDITION

SYMBOL

MIN

MAX

UNITS

NOTES

Supply Voltage

V

DD

2.6

3.4

V

I/O Supply Voltage

V

DDQ

2.6

3.4

V

Input High Voltage: Logic 1; All inputs

V

IH

2.0

V

DD

+ 0.3

V

22

Input Low Voltage: Logic 0; All inputs

V

IL

-0.3

0.8

V

22

Data Output High Voltage: Logic 1; All inputs

V

OH

2.4

≠

V

Data Output Low Voltage: LOGIC 0; All inputs

V

OL

≠

0.4

V

Input Leakage Current:

Any input 0V

£ V

IN

£ V

DD

(All other pins

not under test = 0V)

I

I

-5

5

µA

Output Leakage Current: DQs are disabled; 0V

£ V

OUT

£ V

DD

Q

I

OZ

-5

5

µA

128Mb: x16

Mobile SDRAM Addendum

PRELIMINARY

09005aef80ca3ad1

Micron Technology, Inc., reserves the right to change products or specifications without notice.

128Mbx16Mobile_Addendum.fm - Rev. A 6/03 EN

5

©2003 Micron Technology, Inc. All rights reserved.

Table 8:

DC Electrical Characteristics and Operating Conditions ≠ V Version

Notes appear on standard 128Mb Mobile SDRAM data sheet; V

DD

= 2.5 ±0.2V, V

DD

Q = +2.5V ±0.2V or +1.8V ±0.15V

PARAMETER/CONDITION

SYMBOL

MIN

MAX

UNITS

NOTES

Supply Voltage

V

DD

2.3

2.7

V

I/O Supply Voltage

V

DD

Q

1.65

2.7

V

Input High Voltage: Logic 1; All inputs

V

IH

1.25

V

DD

+ 0.3

V

22

Input Low Voltage: Logic 0; All inputs

V

IL

-0.3

+0.55

V

22

Data Output High Voltage: Logic 1; All inputs

V

OH

V

DD

Q - 0.2

≠

V

Data Output Low Voltage: LOGIC 0; All inputs

V

OL

≠

0.2

V

Input Leakage Current:

Any input 0V

£ V

IN

£ V

DD

(All other

pins not under test = 0V)

I

I

-5

5

µA

Output Leakage Current: DQs are disabled; 0V

£ V

OUT

£ V

DD

Q

I

OZ

-5

5

µA

Table 9:

AC Electrical Characteristics and Operating Conditions

V

DD

= +3.3V ±0.3V or +3.0V ±0.4V or +2.5V±0.2V

PARAMETER/CONDITION

SYMBOL

MIN

MAX

UNITS

NOTES

Input High Voltage: Logic 1; All inputs

V

IH

1.4

≠

V

Input Low Voltage: Logic 0; All inputs

V

IL

≠

0.4

V

128Mb: x16

Mobile SDRAM Addendum

PRELIMINARY

09005aef80ca3ad1

Micron Technology, Inc., reserves the right to change products or specifications without notice.

128Mbx16Mobile_Addendum.fm - Rev. A 6/03 EN

6

©2003 Micron Technology, Inc. All rights reserved.

Table 10: ELectrical Characteristics and Recommended AC Operating Conditions

Notes appear on standard 128Mb Mobile SDRAM data sheet

AC CHARACTERISTICS

-8

-10

UNITS NOTES

PARAMETER

SYMBOL

MIN

MAX

MIN

MAX

Access time from CLK (pos.

edge)

CL = 3

t

AC (3)

6

6

ns

27

CL = 2

t

AC (2)

7

7

ns

CL = 1

t

AC (1)

18

18

ns

Address hold time

t

AH

1

1

ns

Address setup time

t

AS

2.5

2.5

ns

CLK high-level width

t

CH

3

3

ns

CLK low-level width

t

CL

3

3

ns

Clock cycle time

CL = 3

t

CK (3)

8

10

ns

23

CL = 2

t

CK (2)

10

12

ns

23

CL = 1

t

CK (1)

20

25

ns

23

CKE hold time

t

CKH

1

1

ns

CKE setup time

t

CKS

2.5

2.5

ns

CS#, RAS#, CAS#, WE#, DQM hold time

t

CMH

1

1

ns

CS#, RAS#, CAS#, WE#, DQM setup time

t

CMS

2.5

2.5

ns

Data-in hold time

t

DH

1

1

ns

Data-in setup time

t

DS

2.5

2.5

ns

Data-out high-impedance time CL = 3

t

HZ (3)

6

6

ns

10

CL = 2

t

HZ (2)

8

8

ns

10

CL = 1

t

HZ (1)

18

18

ns

10

Data-out low-impedance time

t

LZ

1

1

ns

Data-out hold time (load)

t

OH

2.5

2.5

ns

Data-out hold time (no load)

t

OH

N

1.8

1.8

ns

28

ACTIVE to PRECHARGE command

t

RAS

48

120,000

50

120,000

ns

ACTIVE to ACTIVE command period

t

RC

80

100

ns

ACTIVE to READ or WRITE delay

t

RCD

20

20

ns

Refresh period (4,096 rows)

t

REF

64

64

ms

AUTO REFRESH period

t

RFC

80

100

ns

PRECHARGE command period

t

RP

20

20

ns

ACTIVE bank a to ACTIVE bank b command

t

RRD

20

20

ns

Transition time

t

T

0.5

1.2

0.5

1.2

ns

7

WRITE recovery time

Auto precharge mode

t

WR (a)

1 CLK +

7ns

1 CLK +

5ns

≠

24

Manual precharge mode

t

WR (m)

15

15

ns

25

Exit SELF REFRESH to ACTIVE command

t

XSR

80

100

ns

20

128Mb: x16

Mobile SDRAM Addendum

PRELIMINARY

09005aef80ca3ad1

Micron Technology, Inc., reserves the right to change products or specifications without notice.

128Mbx16Mobile_Addendum.fm - Rev. A 6/03 EN

7

©2003 Micron Technology, Inc. All rights reserved.

Table 11: AC Functional Characteristics

Notes appear on standard 128Mb Mobile SDRAM data sheet

PARAMETER

SYMBOL

-8

-10 UNITS

NOTES

READ/WRITE command to READ/WRITE command

t

CCD

1

1

t

CK

17

CKE to clock disable or power-down entry mode

t

CKED

1

1

t

CK

14

CKE to clock enable or power-down exit setup mode

t

PED

1

1

t

CK

14

DQM to input data delay

t

DQD

0

0

t

CK

17

DQM to data mask during WRITEs

t

DQM

0

0

t

CK

17

DQM to data high-impedance during READs

t

DQZ

2

2

t

CK

17

WRITE command to input data delay

t

DWD

0

0

t

CK

17

Data-in to ACTIVE command

t

DAL

5

5

t

CK

15, 21

Data-in to PRECHARGE command

t

DPL

2

2

t

CK

16, 21

Last data-in to burst STOP command

t

BDL

1

1

t

CK

17

Last data-in to new READ/WRITE command

t

CDL

1

1

t

CK

17

Last data-in to PRECHARGE command

t

RDL

2

2

t

CK

16, 21

LOAD MODE REGISTER command to ACTIVE or REFRESH command

t

MRD

2

2

t

CK

26

Data-out to high-impedance from PRECHARGE command

CL = 3

t

ROH(3)

3

3

t

CK

17

CL = 2

t

ROH(2)

2

2

t

CK

17

CL = 1

t

ROH(1)

1

1

t

CK

17

Table 12: I

DD

Specifications and Conditions ≠ x16

Notes appear on standard 128Mb Mobile SDRAM data sheet; V

DD

= +3.3V ±0.3V or +3.0V ±0.4V or +2.5V±0.2V

PARAMETER/CONDITION

SYMBOL

-8

-10

UNITS

NOTES

Operating Current: Active Mode;

Burst = 2; READ or WRITE;

t

RC =

t

RC (MIN)

I

DD

1

130

100

mA

3, 18,

19, 32

Standby Current: Power-Down Mode;

All banks idle; CKE = LOW

I

DD

2

350

350

µA

32

Standby Current: Active Mode;

CKE = HIGH; CS# = HIGH; All banks active after

t

RCD met;

No accesses in progress

I

DD

3

35

30

mA

3, 12,

19, 32

Operating Current: Burst Mode; Continuous burst;

READ or WRITE; All banks active

I

DD

4

100

95

mA

3, 18,

19, 32

Auto Refresh Current

CKE = HIGH; CS# = HIGH

t

RFC =

t

RFC (MIN)

I

DD

5

210

170

mA

3, 12, 18, 19,

32, 33

t

RFC = 15.625µs

I

DD

6

3

3

mA

128Mb: x16

Mobile SDRAM Addendum

PRELIMINARY

09005aef80ca3ad1

Micron Technology, Inc., reserves the right to change products or specifications without notice.

128Mbx16Mobile_Addendum.fm - Rev. A 6/03 EN

8

©2003 Micron Technology, Inc. All rights reserved.

Æ

8000 S. Federal Way, P.O. Box 6, Boise, ID 83707-0006, Tel: 208-368-3900

E-mail: prodmktg@micron.com, Internet: http://www.micron.com, Customer Comment Line: 800-932-4992

Micron, the M logo, and the Micron logo are trademarks and/or service marks of Micron Technology, Inc.

All other trademarks are the property of their respective owners.

Table 13: I

DD

7

≠ Self Refresh Current Options ≠ x16 (IT Only)

Notes appear on standard 128Mb Mobile SDRAM data sheet; V

DD

= +3.3V ±0.3V or +3.0V ±0.4V or +2.5V±0.2V

TEMPERATURE COMPENSATED SELF REFRESH

MAX

TEMPERATURE

-8 AND -10

UNITS

NOTES

PARAMETER/CONDITION

Self Refresh Current:

CKE < 0.2V

85

∞

C

800

µA

4

70

∞

C

500

µA

4

45

∞

C

350

µA

4

15

∞

C

300

µA

4

Table 14: Capacitance

Notes appear on standard 128Mb Mobile SDRAM data sheet

PARAMETER

SYMBOL

MIN

MAX

UNITS

NOTES

Input Capacitance: CLK

C

I

1

2.0

4.0

pF

29

Input Capacitance: All other input-only pins

C

I

2

2.0

5.0

pF

30

Input/Output Capacitance: DQs

C

IO

3.5

6.0

pF

31