1

64Mb: x4, x8, x16 SDRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

64MSDRAM_F.p65 ≠ Rev. F; Pub. 1/03

©2003, Micron Technology, Inc.

64Mb: x4, x8, x16

SDRAM

16 Meg x 4

8 Meg x 8

4 Meg x 16

Configuration

4 Meg x 4 x 4 banks

2 Meg x 8 x 4 banks

1 Meg x 16 x 4 banks

Refresh Count

4K

4K

4K

Row Addressing

4K (A0-A11)

4K (A0-A11)

4K (A0-A11)

Bank Addressing

4 (BA0, BA1)

4 (BA0, BA1)

4 (BA0, BA1)

Column Addressing

1K (A0-A9)

512 (A0-A8)

256 (A0-A7)

SYNCHRONOUS

DRAM

MT48LC16M4A2 ≠ 4 Meg x 4

x 4 banks

MT48LC8M8A2 ≠

2 Meg x 8

x 4 banks

MT48LC4M16A2 ≠ 1 Meg x 16 x 4 banks

For the latest data sheet, please refer to the Micron Web

site:

www.micron.com/dramds

PIN ASSIGNMENT (Top View)

54-Pin TSOP

FEATURES

∑ PC66-, PC100-, and PC133-compliant

∑ Fully synchronous; all signals registered on

positive edge of system clock

∑ Internal pipelined operation; column address can

be changed every clock cycle

∑ Internal banks for hiding row access/precharge

∑ Programmable burst lengths: 1, 2, 4, 8, or full page

∑ Auto Precharge, includes CONCURRENT AUTO

PRECHARGE, and Auto Refresh Modes

∑ Self Refresh Modes: standard and low power

∑ 64ms, 4,096-cycle refresh

∑ LVTTL-compatible inputs and outputs

∑ Single +3.3V ±0.3V power supply

OPTIONS

MARKING

∑ Configurations

16 Meg x 4

(4 Meg x 4

x 4 banks)

16M4

8 Meg x 8

(2 Meg x 8

x 4 banks)

8M8

4 Meg x 16 (1 Meg x 16 x 4 banks)

4M16

∑ WRITE Recovery (

t

WR)

t

WR = "2 CLK"

1

A2

∑ Plastic Package ≠ OCPL

2

54-pin TSOP II (400 mil)

TG

∑ Timing (Cycle Time)

10ns @ CL = 2 (PC100)

-8E

3, 4,5

7.5ns @ CL = 3 (PC133)

-75

7.5ns @ CL = 2 (PC133)

-7E

6ns @ CL = 3 (PC133, x16 Only)

-6

∑ Self Refresh

Standard

None

Low Power

L

∑ Operating Temperature Range

Commercial (0∞C to +70∞C)

None

Industrial (-40∞C to +85∞C)

IT

3

Part Number Example:

MT48LC8M8A2TG-75

NOTE: 1. Refer to Micron Technical Note: TN-48-05.

2. Off-center parting line.

3. Consult Micron for availability.

4. Not recommended for new designs.

5. Shown for PC100 compatibility.

V

DD

DQ0

V

DD

Q

DQ1

DQ2

VssQ

DQ3

DQ4

V

DD

Q

DQ5

DQ6

VssQ

DQ7

V

DD

DQML

WE#

CAS#

RAS#

CS#

BA0

BA1

A10

A0

A1

A2

A3

V

DD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

Vss

DQ15

VssQ

DQ14

DQ13

V

DD

Q

DQ12

DQ11

VssQ

DQ10

DQ9

V

DD

Q

DQ8

Vss

NC

DQMH

CLK

CKE

NC

A11

A9

A8

A7

A6

A5

A4

Vss

x8

x16

x16

x8

x4

x4

-

DQ0

-

NC

DQ1

-

NC

DQ2

-

NC

DQ3

-

NC

-

NC

-

-

-

-

-

-

-

-

-

-

-

-

-

NC

-

NC

DQ0

-

NC

NC

-

NC

DQ1

-

NC

-

NC

-

-

-

-

-

-

-

-

-

-

-

-

-

DQ7

-

NC

DQ6

-

NC

DQ5

-

NC

DQ4

-

NC

-

-

DQM

-

-

-

-

-

-

-

-

-

-

-

-

NC

-

NC

DQ3

-

NC

NC

-

NC

DQ2

-

NC

-

-

DQM

-

-

-

-

-

-

-

-

-

-

-

Note:

The # symbol indicates signal is active LOW. A dash (≠)

indicates x8 and x4 pin function is same as x16 pin function.

KEY TIMING PARAMETERS

SPEED

CLOCK

ACCESS TIME

SETUP

HOLD

GRADE

FREQUENCY

CL = 2* CL = 3*

TIME

TIME

-6

166 MHz

≠

5.5ns

1.5ns

1ns

-7E

143 MHz

≠

5.4ns

1.5ns

0.8ns

-75

133 MHz

≠

5.4ns

1.5ns

0.8ns

-7E

133 MHz

5.4ns

≠

1.5ns

0.8ns

-8E

3, 4, 5

125 MHz

≠

6ns

2ns

1ns

-75

100 MHz

6ns

≠

1.5ns

0.8ns

-8E

3, 4, 5

100 MHz

6ns

≠

2ns

1ns

* CL = CAS (READ) latency

2

64Mb: x4, x8, x16 SDRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

64MSDRAM_F.p65 ≠ Rev. F; Pub. 1/03

©2003, Micron Technology, Inc.

64Mb: x4, x8, x16

SDRAM

dress bits registered coincident with the READ or WRITE

command are used to select the starting column loca-

tion for the burst access.

The SDRAM provides for programmable READ or

WRITE burst lengths of 1, 2, 4, or 8 locations, or the

full page, with a burst terminate option. An auto

precharge function may be enabled to provide a self-

timed row precharge that is initiated at the end of the

burst sequence.

The 64Mb SDRAM uses an internal pipelined

architecture to achieve high-speed operation. This

architecture is compatible with the 2n rule of prefetch

architectures, but it also allows the column address to

be changed on every clock cycle to achieve a high-

speed, fully random access. Precharging one bank

while accessing one of the other three banks will hide

the precharge cycles and provide seamless, high-

speed, random-access operation.

The 64Mb SDRAM is designed to operate in 3.3V

memory systems. An auto refresh mode is provided,

along with a power-saving, power-down mode.

All inputs and outputs are LVTTL-compatible.

SDRAMs offer substantial advances in DRAM oper-

ating performance, including the ability to synchro-

nously burst data at a high data rate with automatic

column-address generation, the ability to interleave

between internal banks in order to hide precharge time

and the capability to randomly change column

addresses on each clock cycle during a burst access.

GENERAL DESCRIPTION

The Micron

Æ

64Mb SDRAM is a high-speed CMOS,

dynamic random-access memory containing

67,108,864 bits. It is internally configured as a quad-

bank DRAM with a synchronous interface (all signals

are registered on the positive edge of the clock signal,

CLK). Each of the x4's 16,777,216-bit banks is orga-

nized as 4,096 rows by 1,024 columns by 4 bits. Each of

the x8's 16,777,216-bit banks is organized as 4,096 rows

by 512 columns by 8 bits. Each of the x16's 16,777,216-

bit banks is organized as 4,096 rows by 256 columns by

16 bits.

Read and write accesses to the SDRAM are burst

oriented; accesses start at a selected location and con-

tinue for a programmed number of locations in a pro-

grammed sequence. Accesses begin with the

registration of an ACTIVE command, which is then fol-

lowed by a READ or WRITE command. The address bits

registered coincident with the ACTIVE command are

used to select the bank and row to be accessed (BA0,

BA1 select the bank; A0-A11 select the row). The ad-

64Mb SDRAM PART NUMBERS

PART NUMBER

ARCHITECTURE

MT48LC16M4A2TG

16 Meg x 4

MT48LC8M8A2TG

8 Meg x 8

MT48LC4M16A2TG

4 Meg x 16

3

64Mb: x4, x8, x16 SDRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

64MSDRAM_F.p65 ≠ Rev. F; Pub. 1/03

©2003, Micron Technology, Inc.

64Mb: x4, x8, x16

SDRAM

TABLE OF CONTENTS

Functional Block Diagram ≠16 Meg x 4 ................

4

Functional Block Diagram ≠ 8 Meg x 8 ................

5

Functional Block Diagram ≠ 4 Meg x 16 ..............

6

Pin Descriptions ........................................................

7

Functional Description ...........................................

8

Initialization .........................................................

8

Register Definition ...............................................

8

Mode Register .................................................

8

Burst Length ..............................................

8

Burst Type ..................................................

9

CAS Latency .............................................. 10

Operating Mode ........................................ 10

Write Burst Mode ...................................... 10

Commands ........................................................... 11

Truth Table 1 (Commands and DQM Operation) .......

11

Command Inhibit .......................................... 12

No Operation (NOP) ...................................... 12

Load Mode Register ........................................ 12

Active ............................................................... 12

Read ................................................................. 12

Write ................................................................ 12

Precharge ......................................................... 12

Auto Precharge ............................................... 12

Burst Terminate .............................................. 12

Auto Refresh ................................................... 13

Self Refresh ...................................................... 13

Operation ............................................................. 14

Bank/Row Activation ..................................... 14

Reads ................................................................ 15

Writes .............................................................. 21

Precharge ......................................................... 23

Power-Down ................................................... 23

Clock Suspend ................................................ 24

Burst Read/Single Write ................................. 24

Concurrent Auto Precharge .......................... 25

Truth Table 2 (CKE) ...................................................

27

Truth Table 3 (Current State, Same Bank) ...................

28

Truth Table 4 (Current State, Different Bank) .............

30

Absolute Maximum Ratings .................................... 32

DC Electrical Characteristics

and Operating Conditions ..................................... 32

I

DD

Specifications and Conditions .......................... 32

Capacitance ............................................................... 33

Electrical Characteristics and Recommended

Operating Conditions (Timing Table) ........... 34

Timing Waveforms

Initialize and Load Mode Register ..................... 36

Power-Down Mode ............................................ 37

Clock Suspend Mode .......................................... 38

Auto Refresh Mode ............................................. 39

Self Refresh Mode ................................................ 40

Reads

Read ≠ Without Auto Precharge .................. 41

Read ≠ With Auto Precharge ........................ 42

Single Read ≠ Without Auto Precharge ....... 43

Single Read ≠ With Auto Precharge ............. 44

Alternating Bank Read Accesses .................... 45

Read ≠ Full-Page Burst ................................... 46

Read ≠ DQM Operation ................................ 47

Writes

Write ≠ Without Auto Precharge ................. 48

Write ≠ With Auto Precharge ....................... 49

Single Write ≠ Without Auto Precharge ...... 50

Single Write ≠ With Auto Precharge ............ 51

Alternating Bank Write Accesses ................... 52

Write ≠ Full-Page Burst .................................. 53

Write ≠ DQM Operation ............................... 54

4

64Mb: x4, x8, x16 SDRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

64MSDRAM_F.p65 ≠ Rev. F; Pub. 1/03

©2003, Micron Technology, Inc.

64Mb: x4, x8, x16

SDRAM

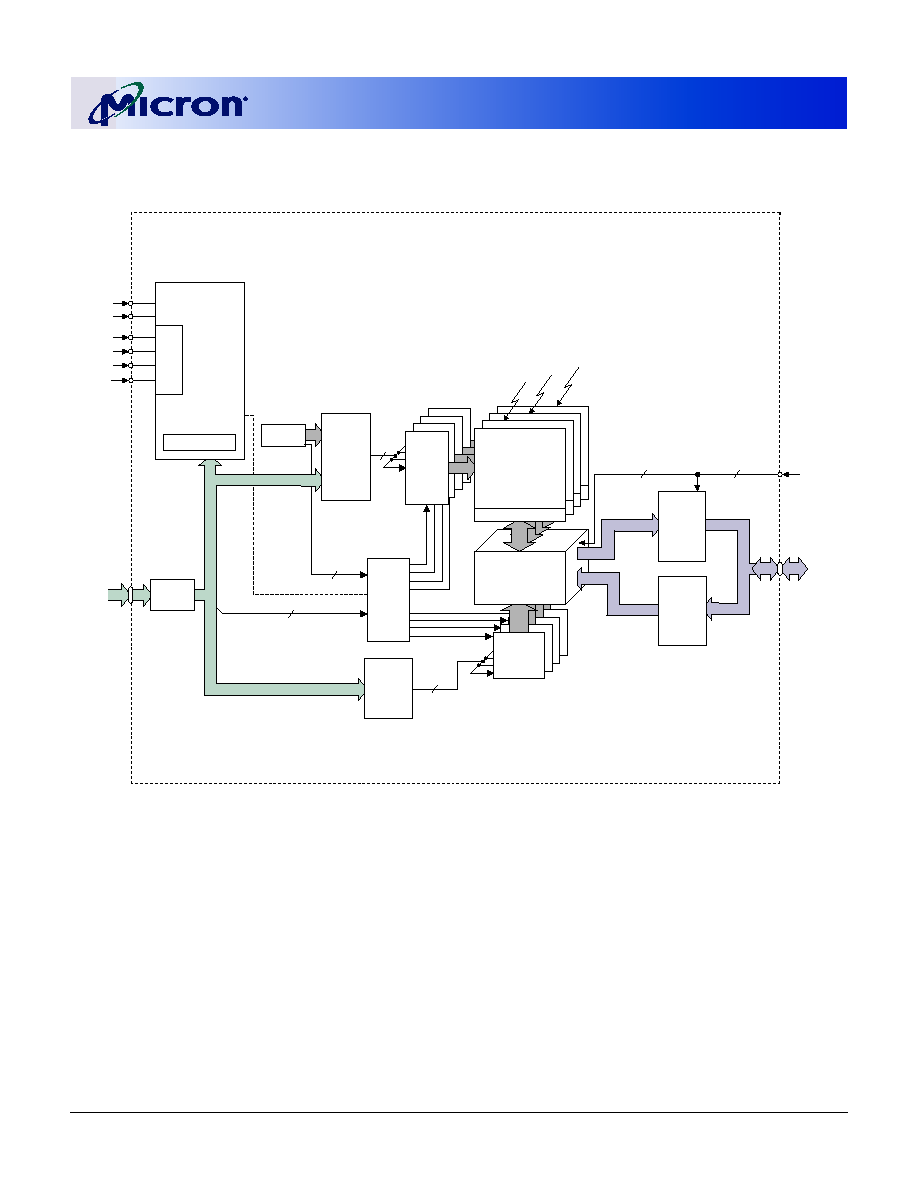

FUNCTIONAL BLOCK DIAGRAM

16 Meg x 4 SDRAM

12

RAS#

CAS#

ROW-

ADDRESS

MUX

CLK

CS#

WE#

CKE

CONTROL

LOGIC

COLUMN-

ADDRESS

COUNTER/

LATCH

MODE REGISTER

10

COMMAND

DECODE

A0-A11,

BA0, BA1

DQM

12

ADDRESS

REGISTER

14

1024

(x4)

4096

I/O GATING

DQM MASK LOGIC

READ DATA LATCH

WRITE DRIVERS

COLUMN

DECODER

BANK0

MEMORY

ARRAY

(4,096 x 1,024 x 4)

BANK0

ROW-

ADDRESS

LATCH

&

DECODER

4096

SENSE AMPLIFIERS

BANK

CONTROL

LOGIC

DQ0-DQ3

4

4

DATA

INPUT

REGISTER

DATA

OUTPUT

REGISTER

4

12

BANK1

BANK2

BANK3

12

10

2

1

1

2

REFRESH

COUNTER

5

64Mb: x4, x8, x16 SDRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

64MSDRAM_F.p65 ≠ Rev. F; Pub. 1/03

©2003, Micron Technology, Inc.

64Mb: x4, x8, x16

SDRAM

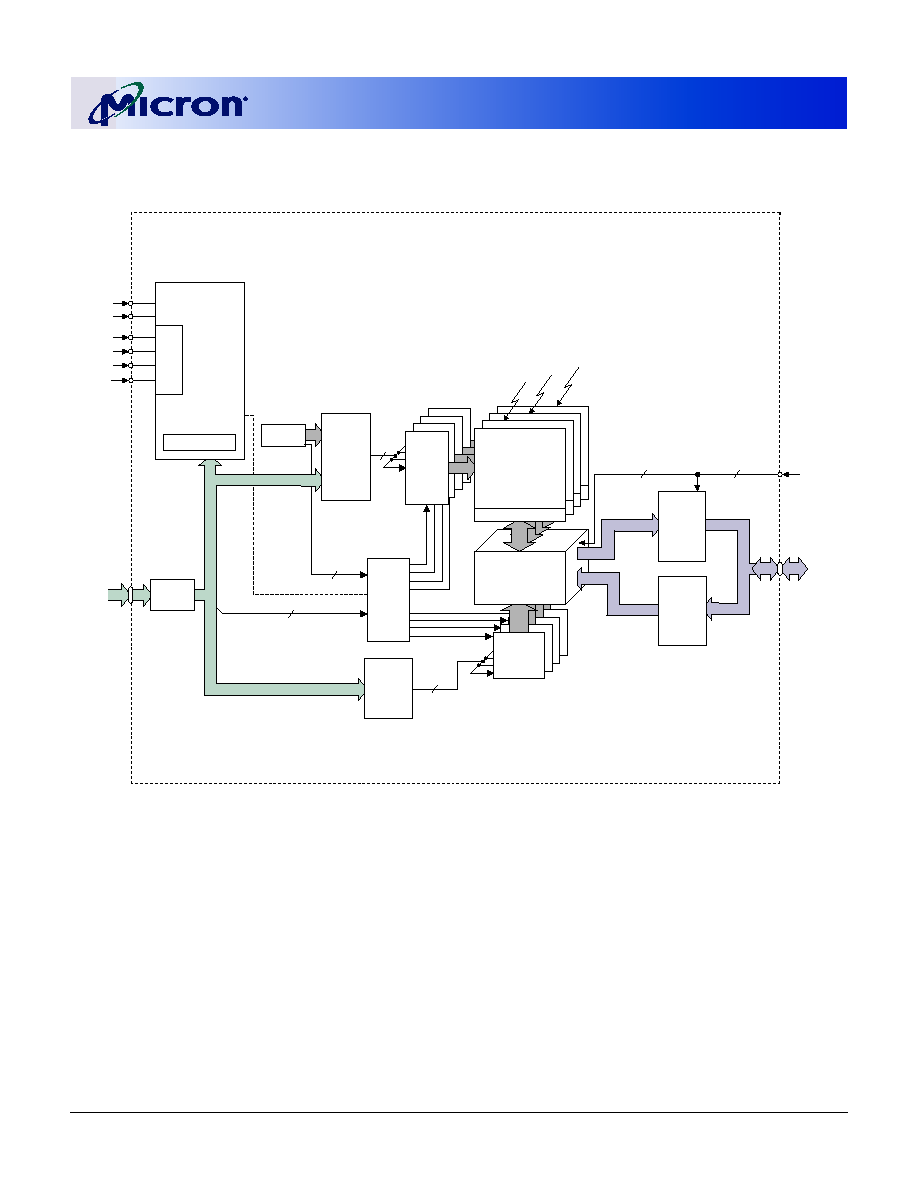

FUNCTIONAL BLOCK DIAGRAM

8 Meg x 8 SDRAM

12

RAS#

CAS#

ROW-

ADDRESS

MUX

CLK

CS#

WE#

CKE

CONTROL

LOGIC

COLUMN-

ADDRESS

COUNTER/

LATCH

MODE REGISTER

9

COMMAND

DECODE

A0-A11,

BA0, BA1

DQM

12

ADDRESS

REGISTER

14

512

(x8)

4096

I/O GATING

DQM MASK LOGIC

READ DATA LATCH

WRITE DRIVERS

COLUMN

DECODER

BANK0

MEMORY

ARRAY

(4,096 x 512 x 8)

BANK0

ROW-

ADDRESS

LATCH

&

DECODER

4096

SENSE AMPLIFIERS

BANK

CONTROL

LOGIC

DQ0-DQ7

8

8

DATA

INPUT

REGISTER

DATA

OUTPUT

REGISTER

8

12

BANK1

BANK2

BANK3

12

9

2

1

1

2

REFRESH

COUNTER