Document Outline

- Features/Options

- Key Timing Parameter

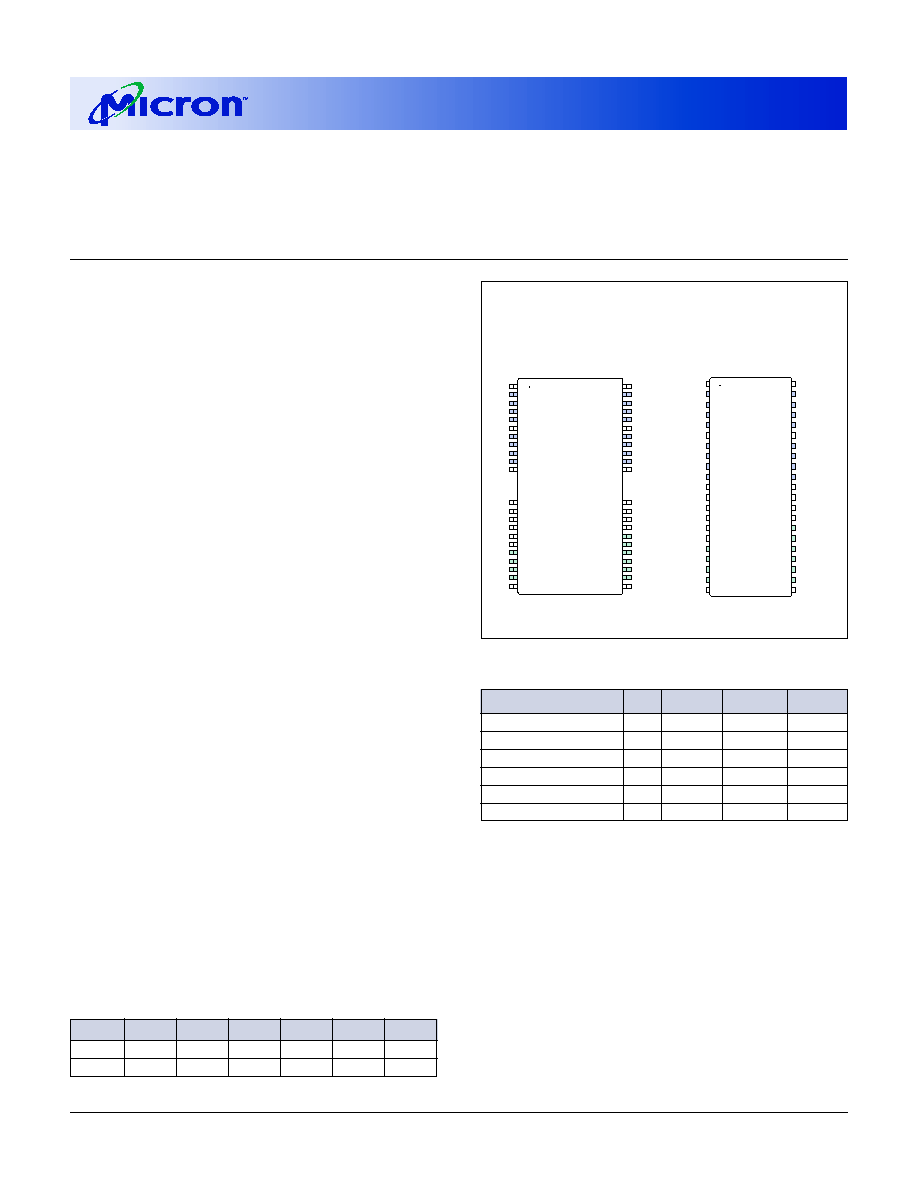

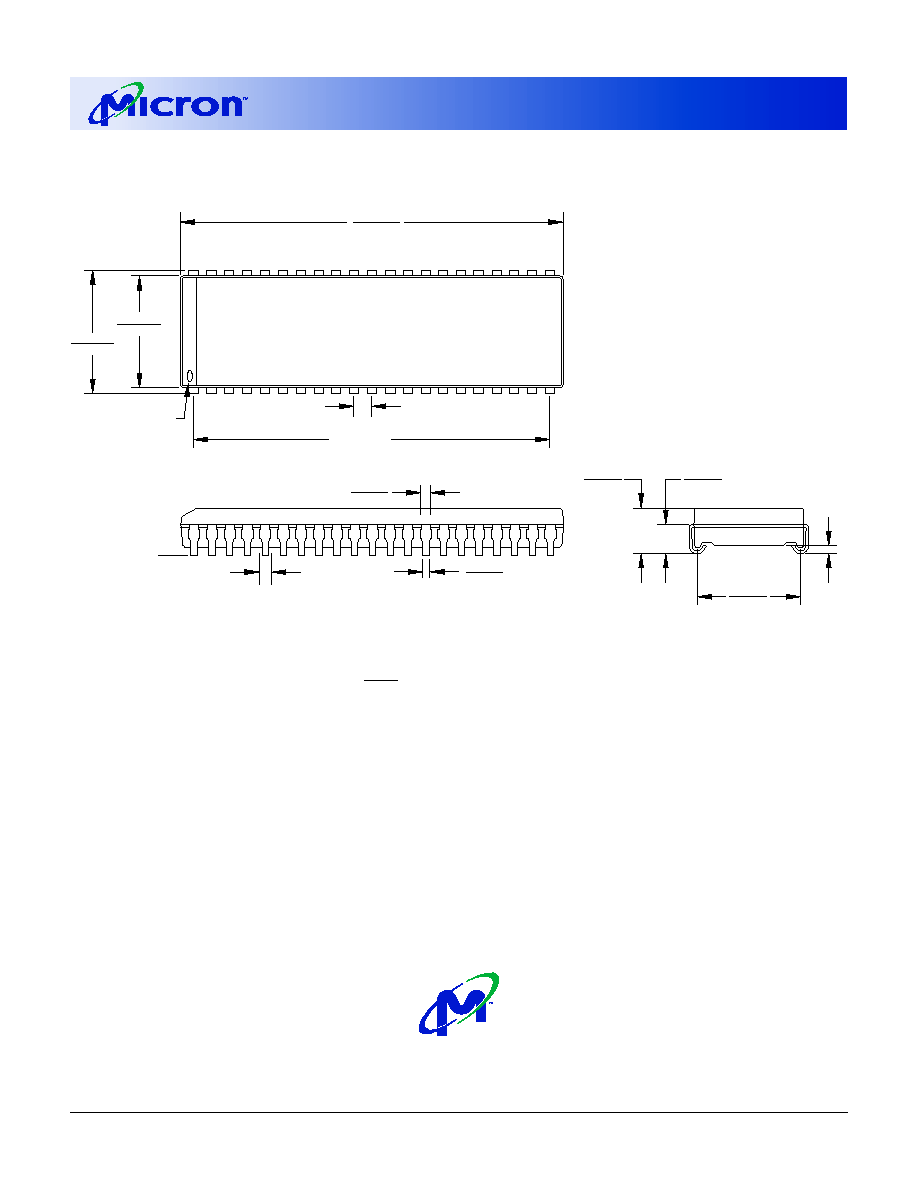

- Pin Assignments; 44/50-Pin TSOP, 42-Pin SOJ

- 1 Meg x 16 EDO DRAM Part Numbers

- General Description

- General Description (continued)

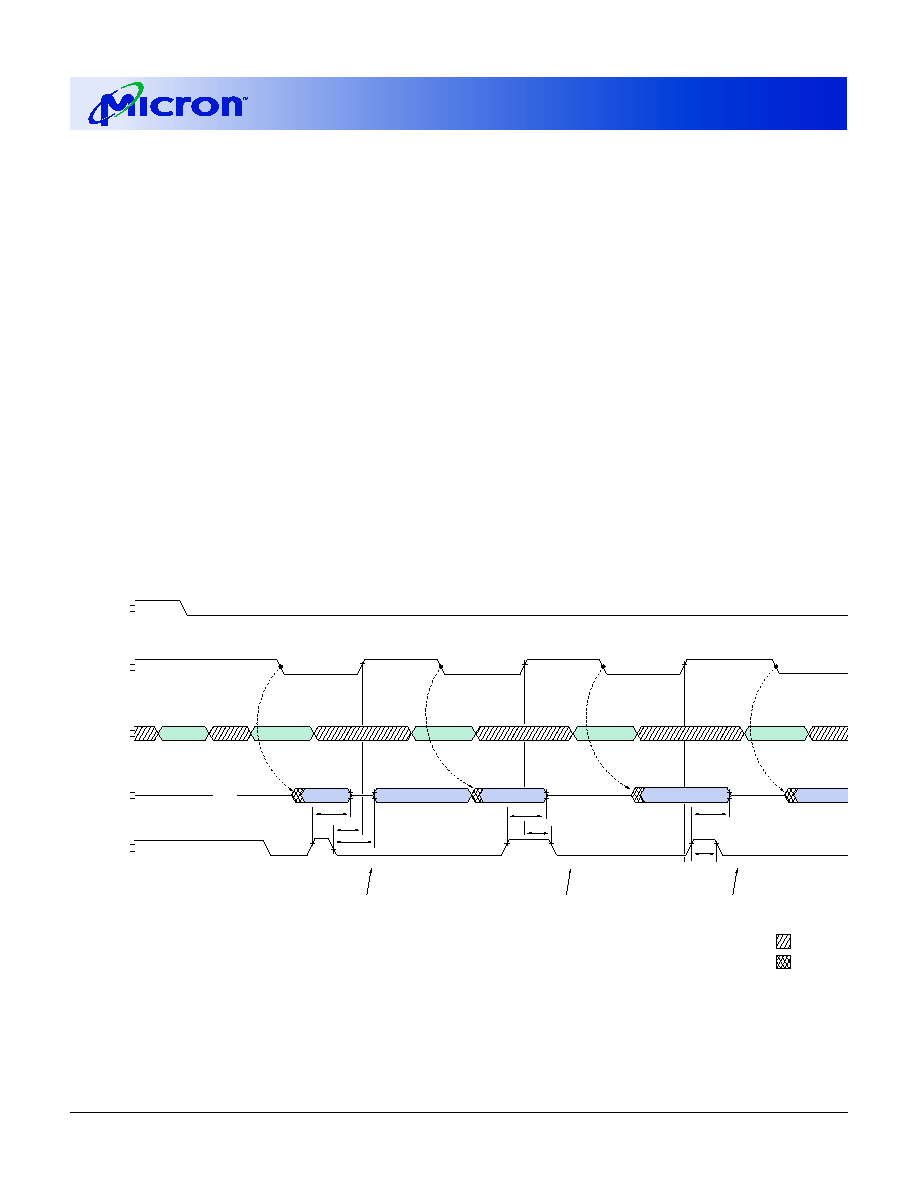

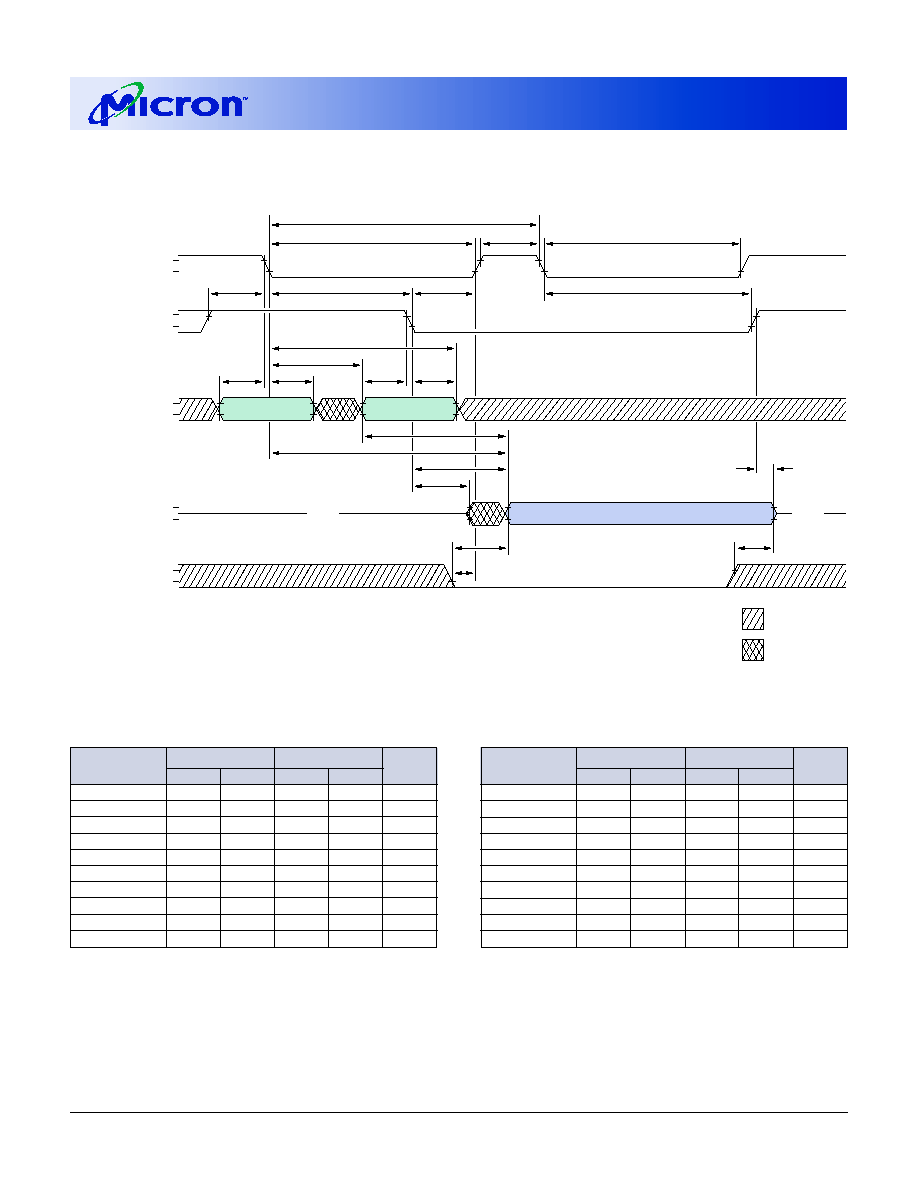

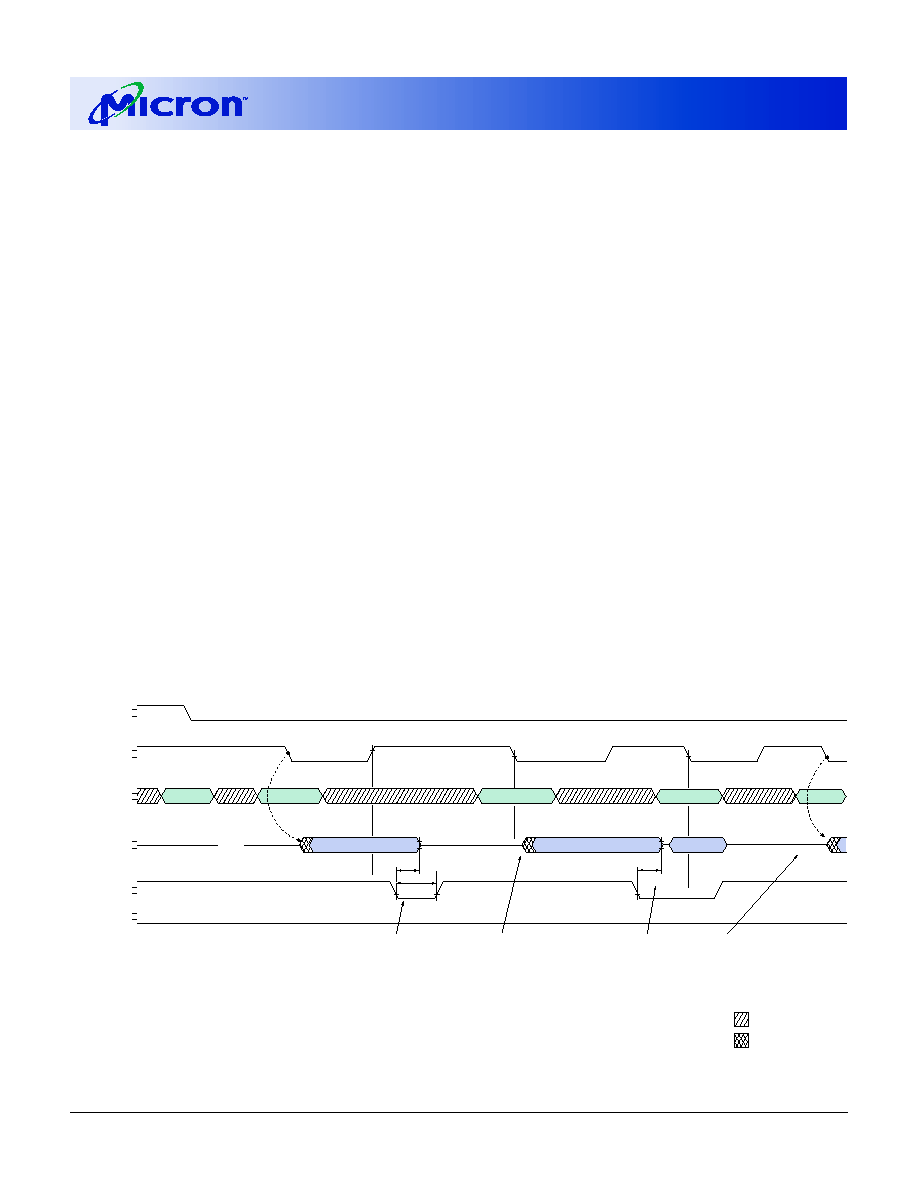

- Figure 1, OE# Control of DQs

- Page Access

- EDO Page Mode

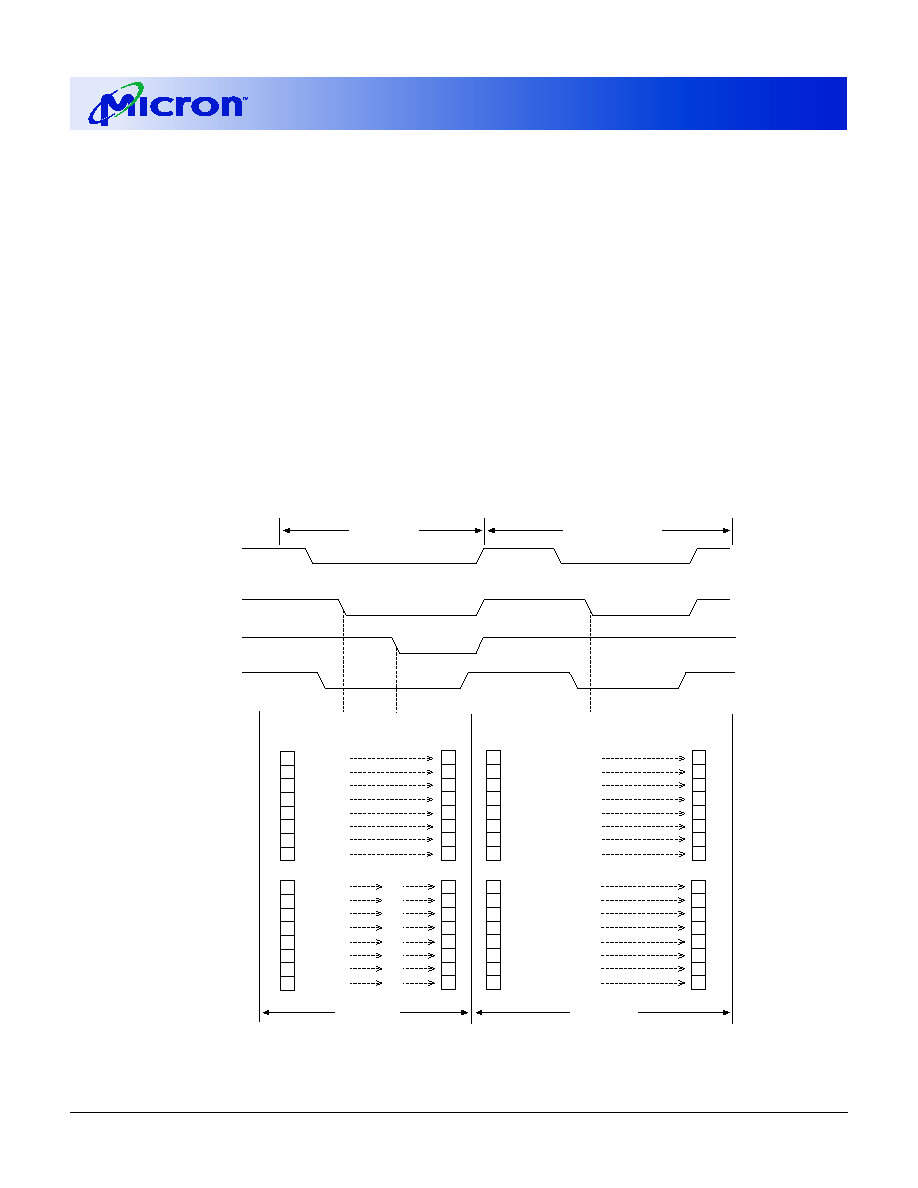

- Byte Access Cycle

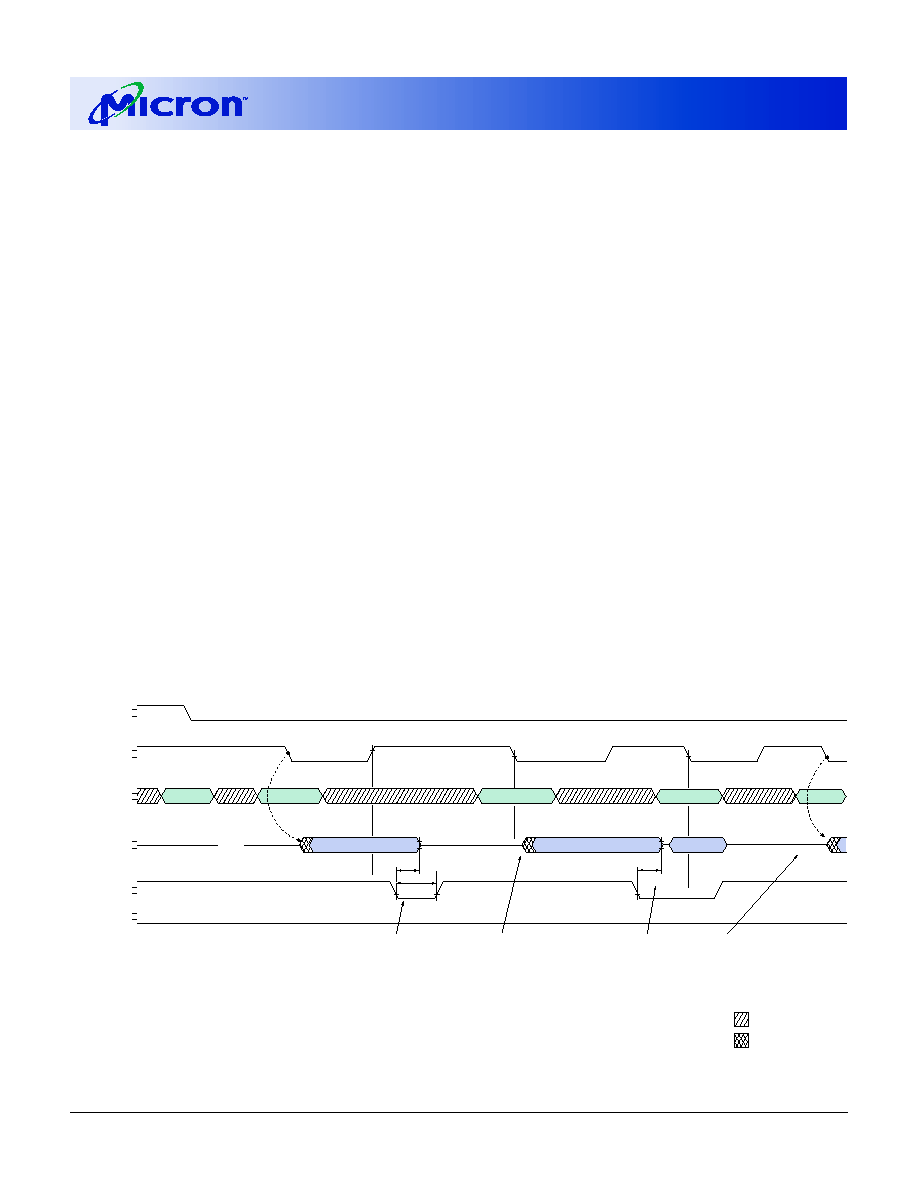

- Figure 2, WE# Control of DQs

- DRAM Refresh

- Standby

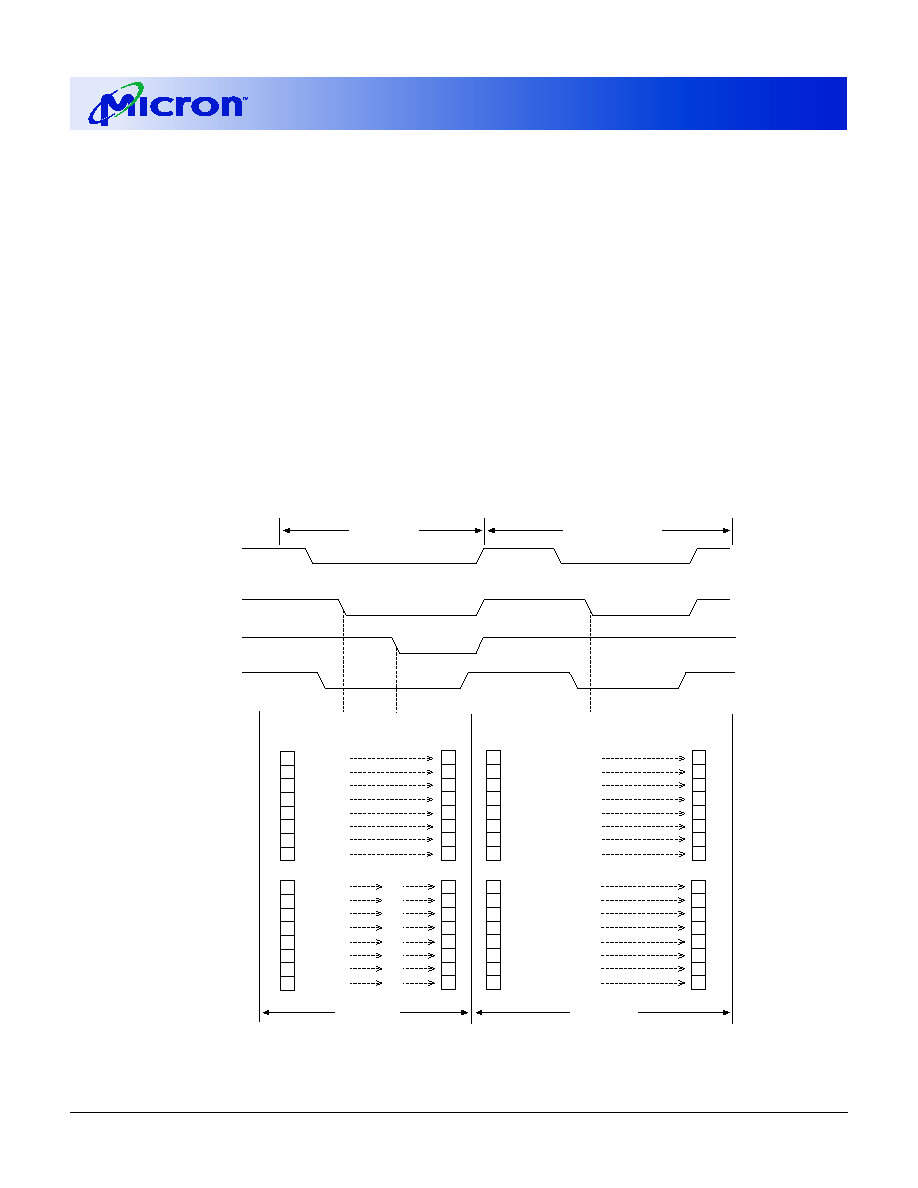

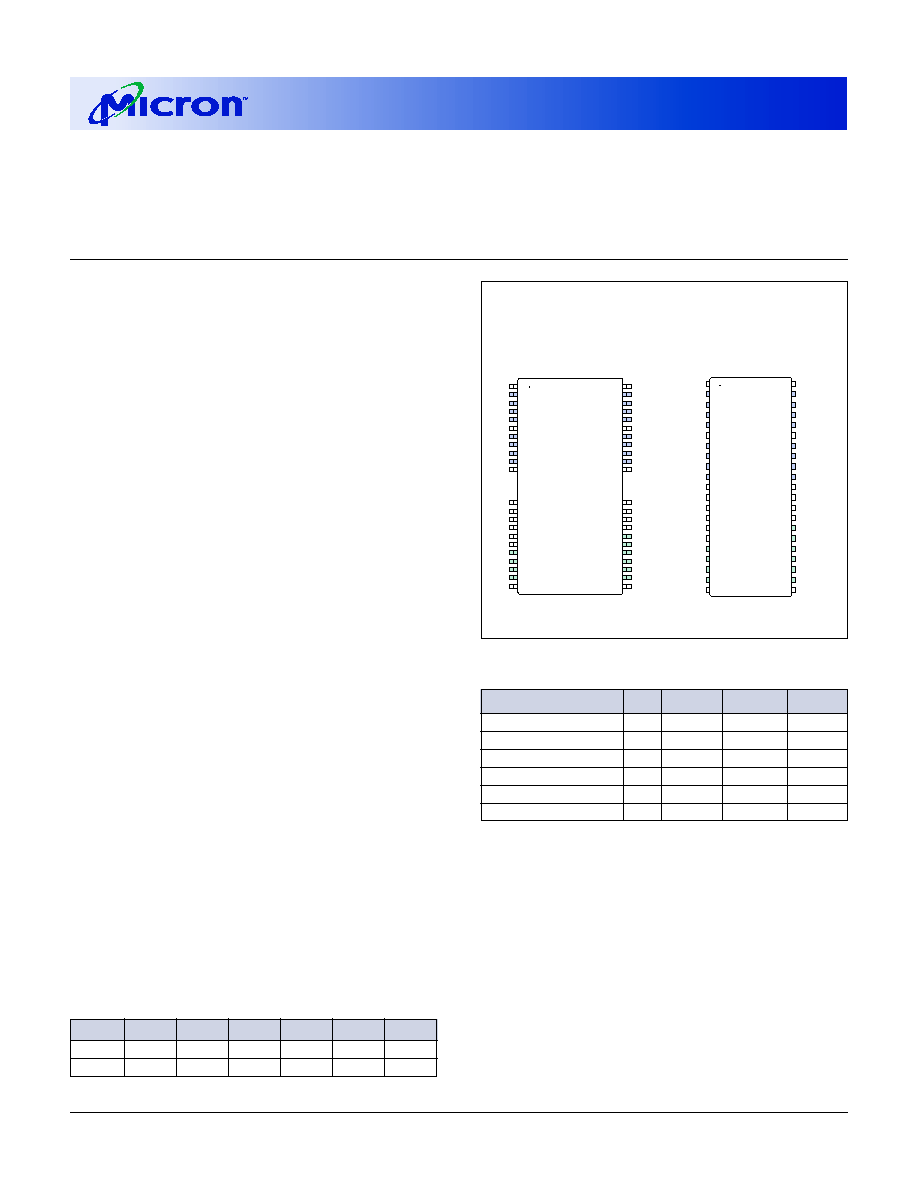

- Figure 3, WORD and BYTE WRITE Example

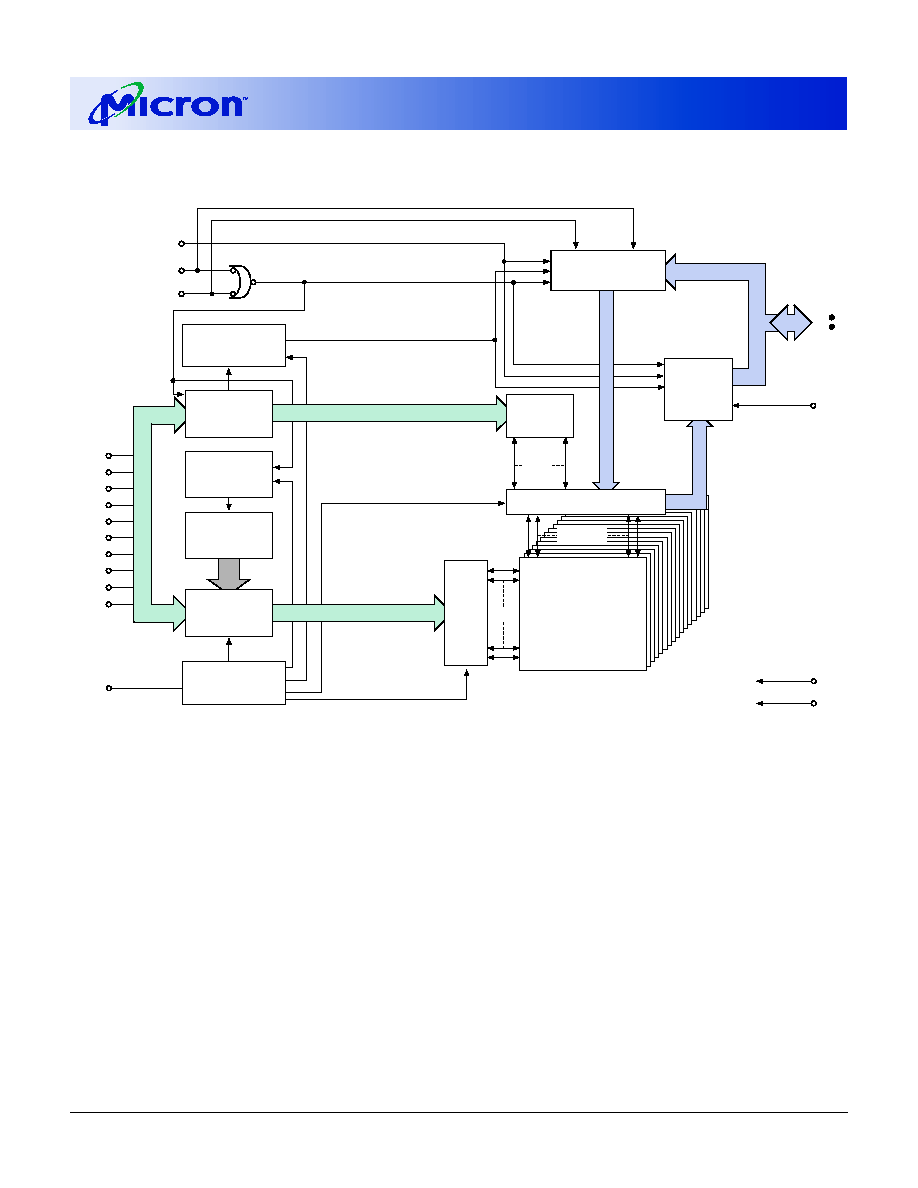

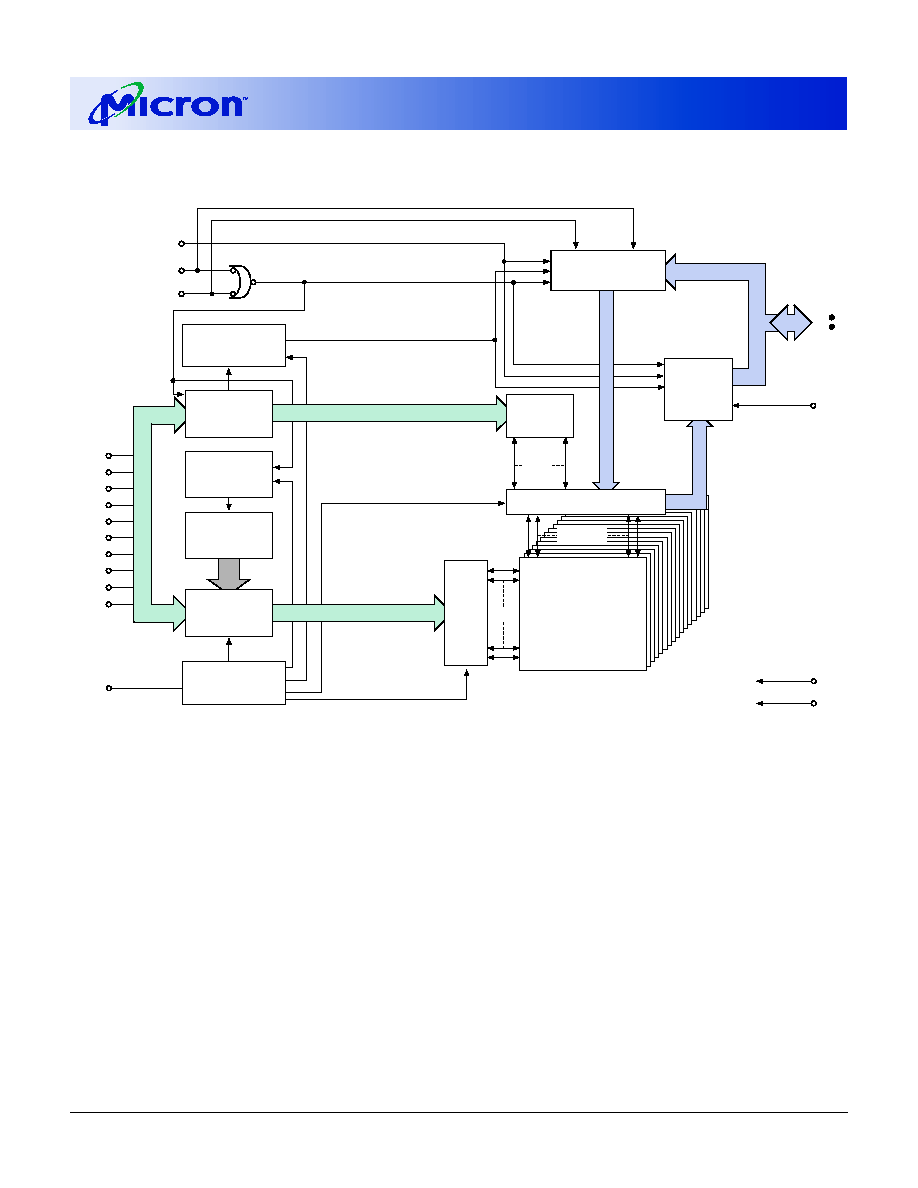

- Functional Block Diagram

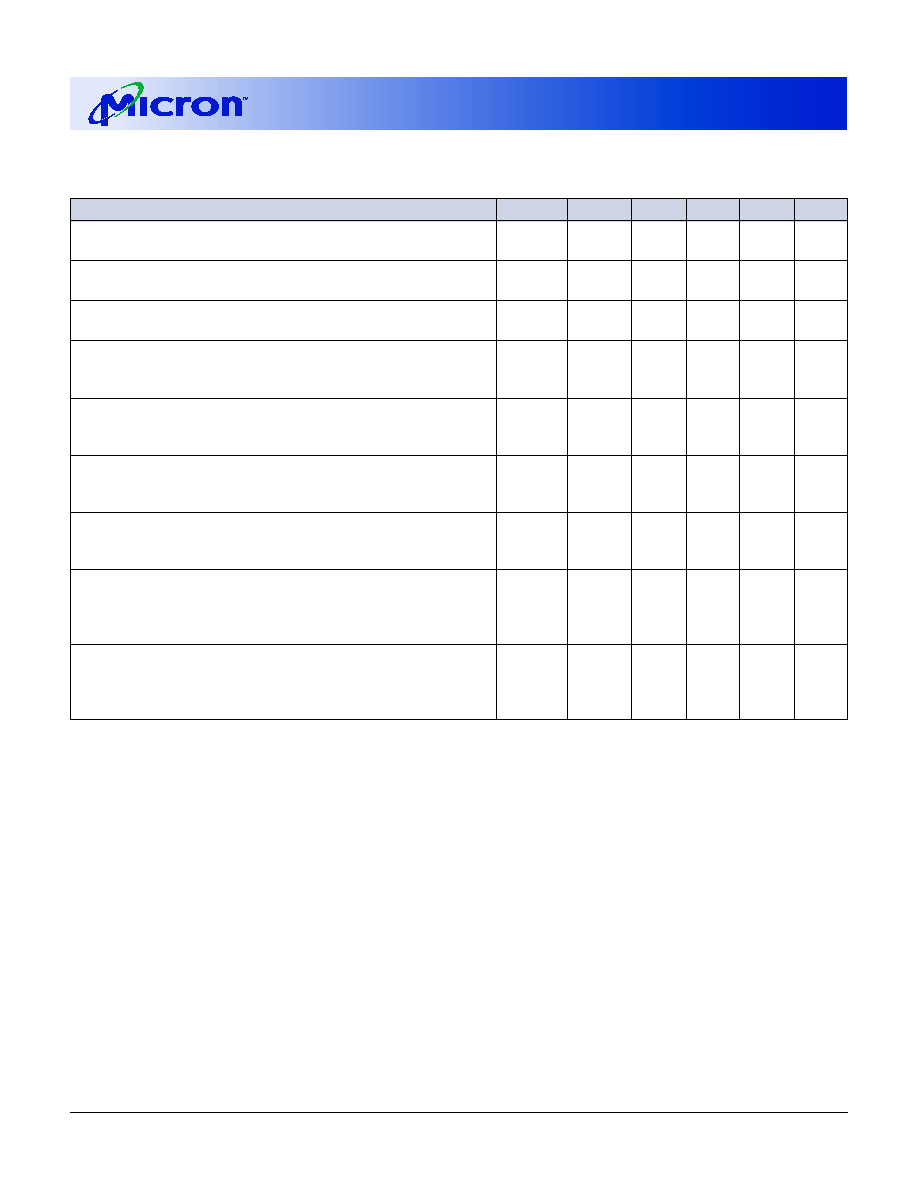

- Absolute Maximum Ratings

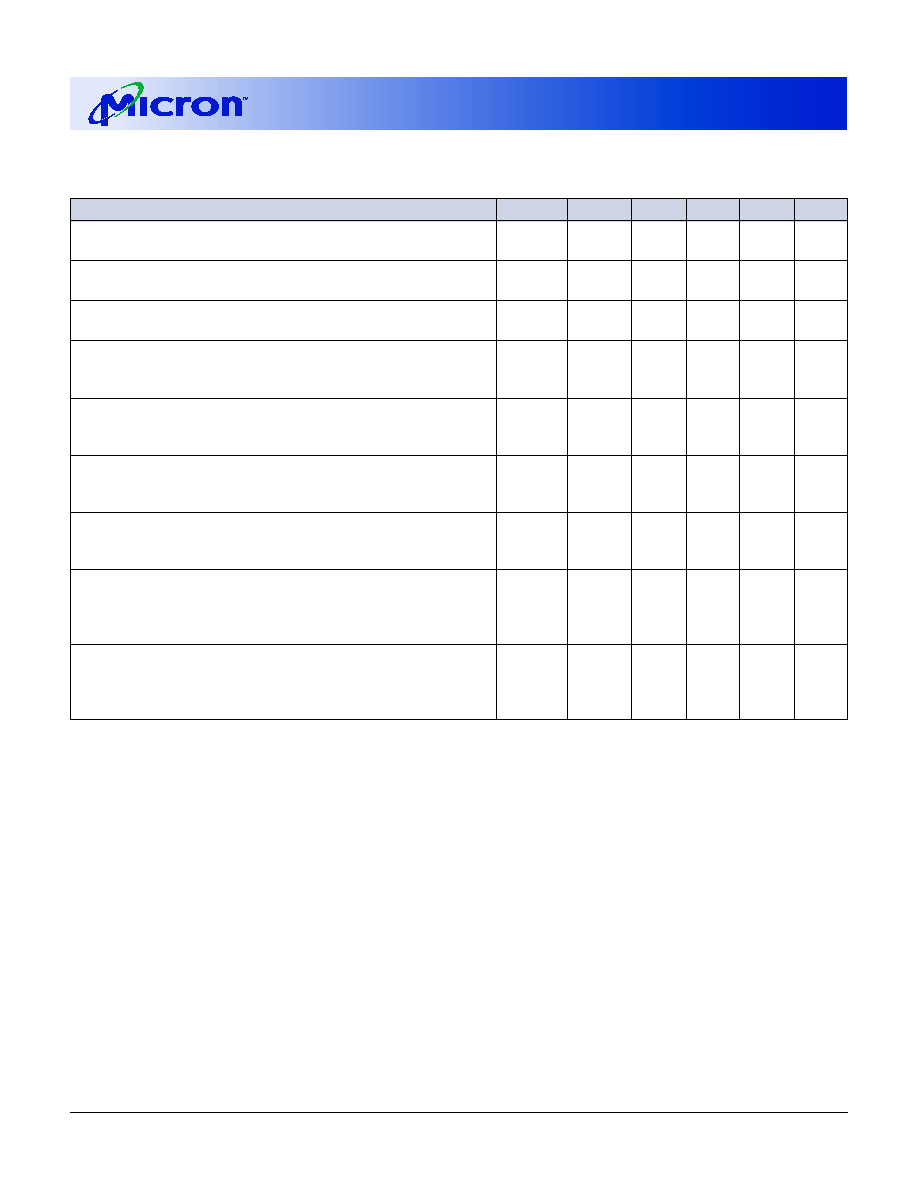

- DC Electrical Characteristics and Operating Conditions

- Icc Operating Conditions and Maximum Limits

- Capacitance

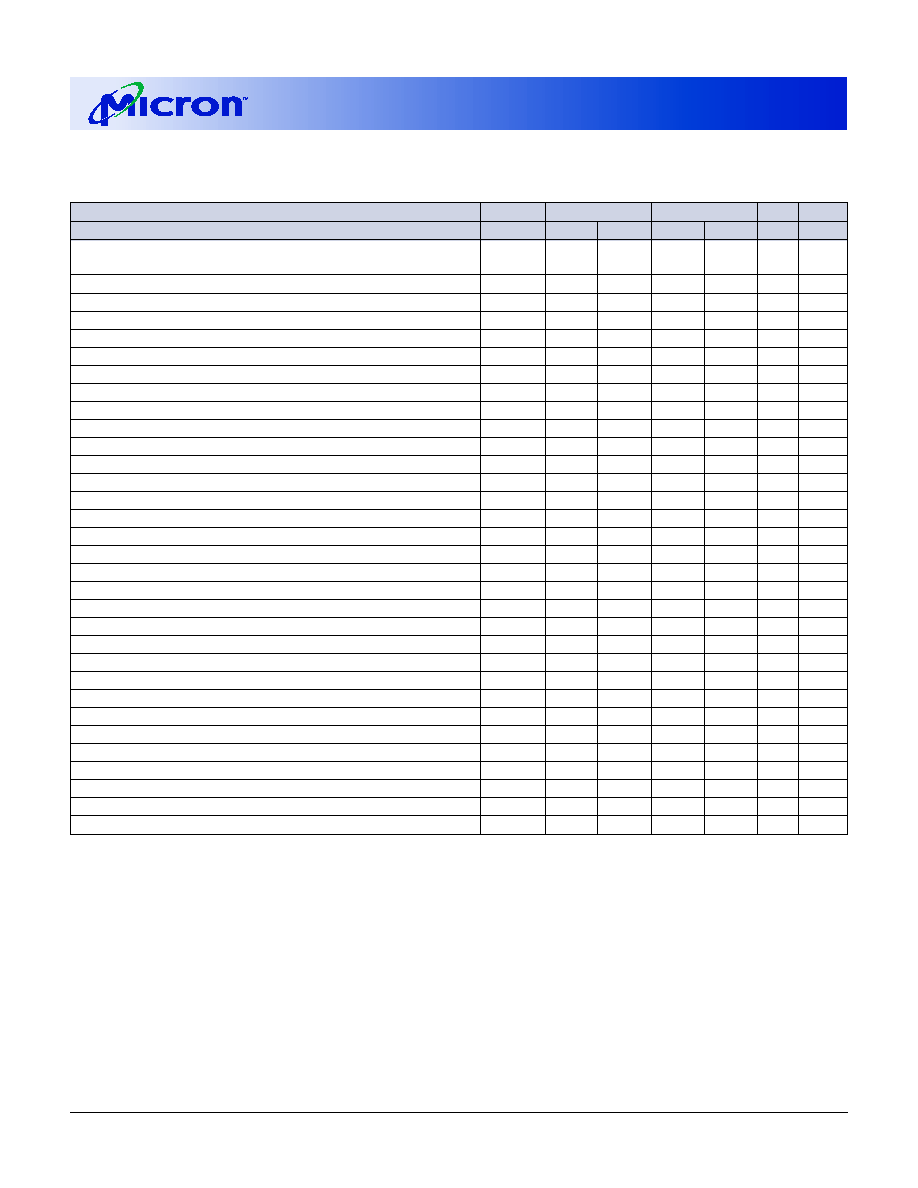

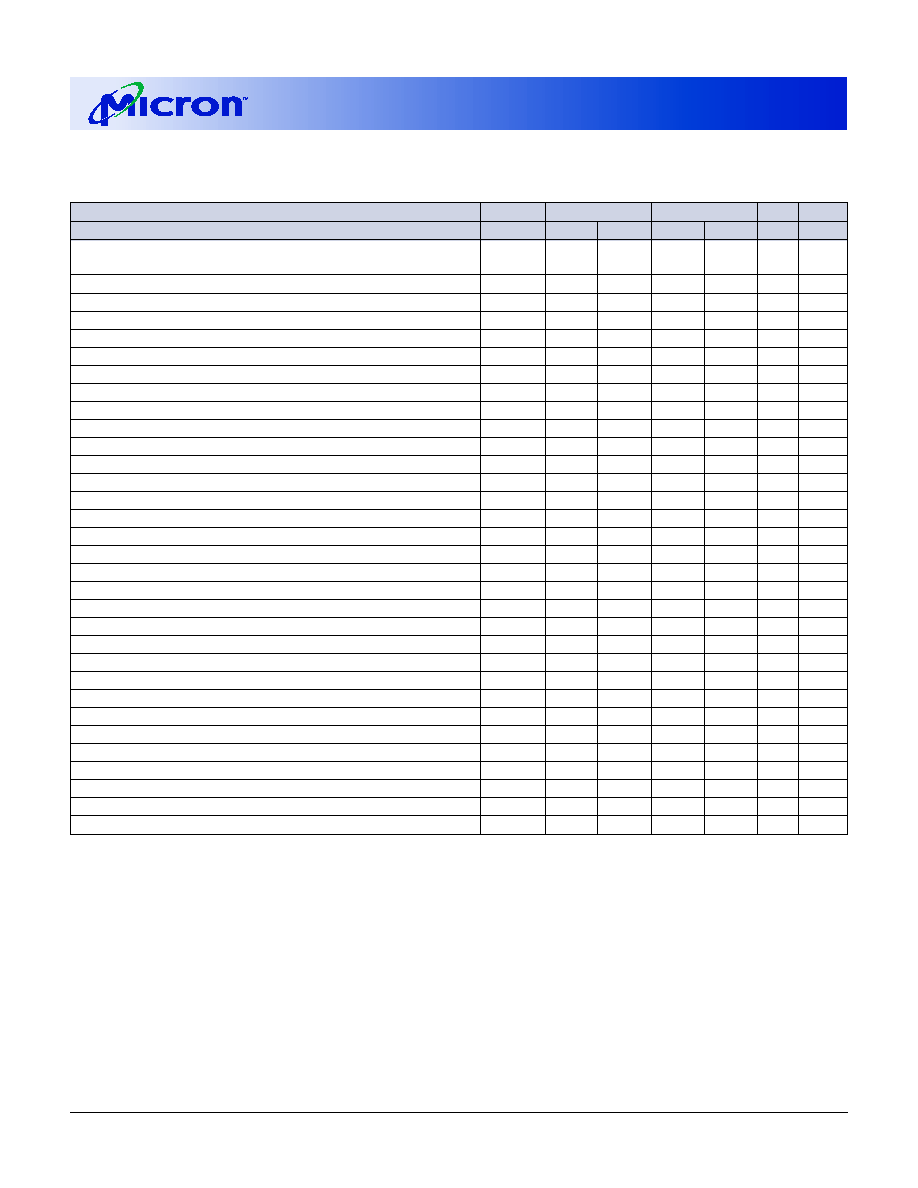

- AC Electrical Characteristics

- AC Electrical Characteristics (continued)

- Notes

- Notes (continued)

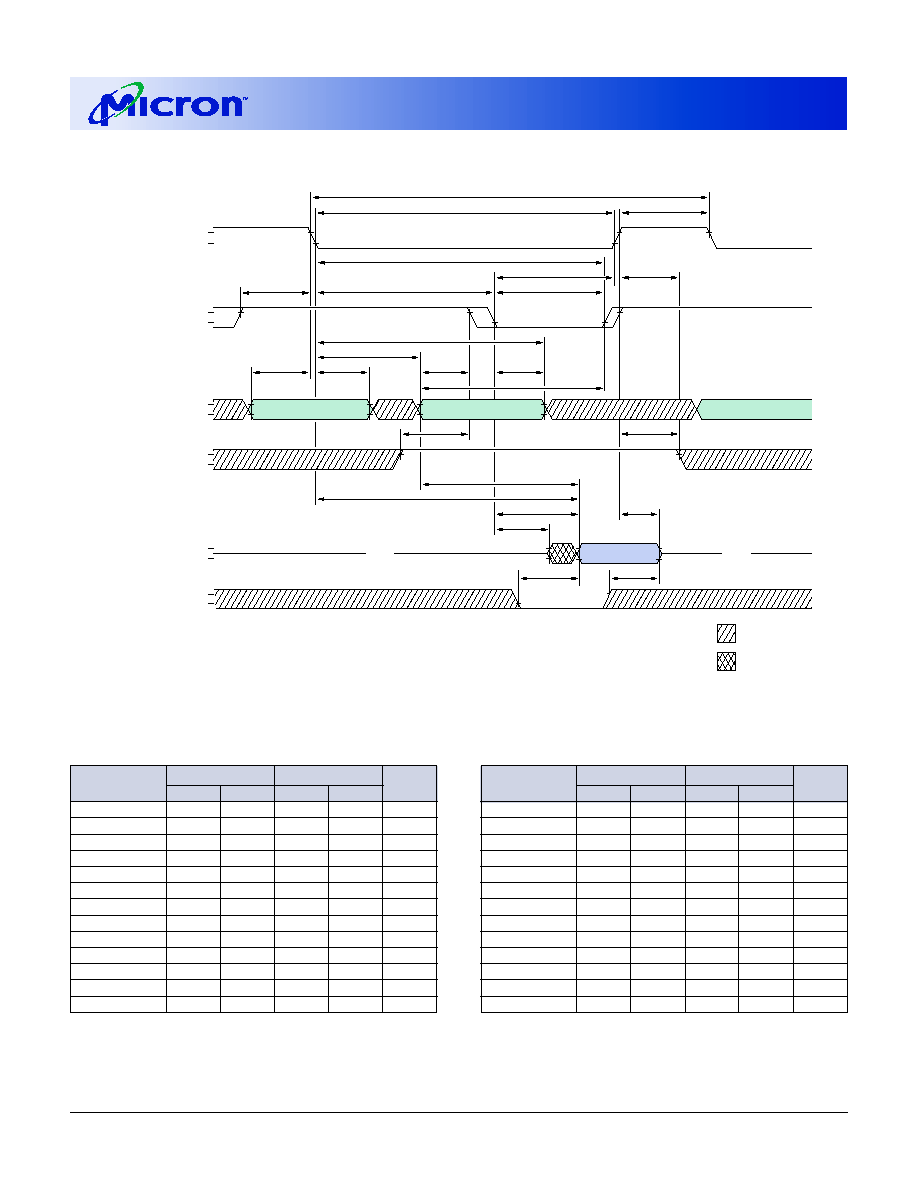

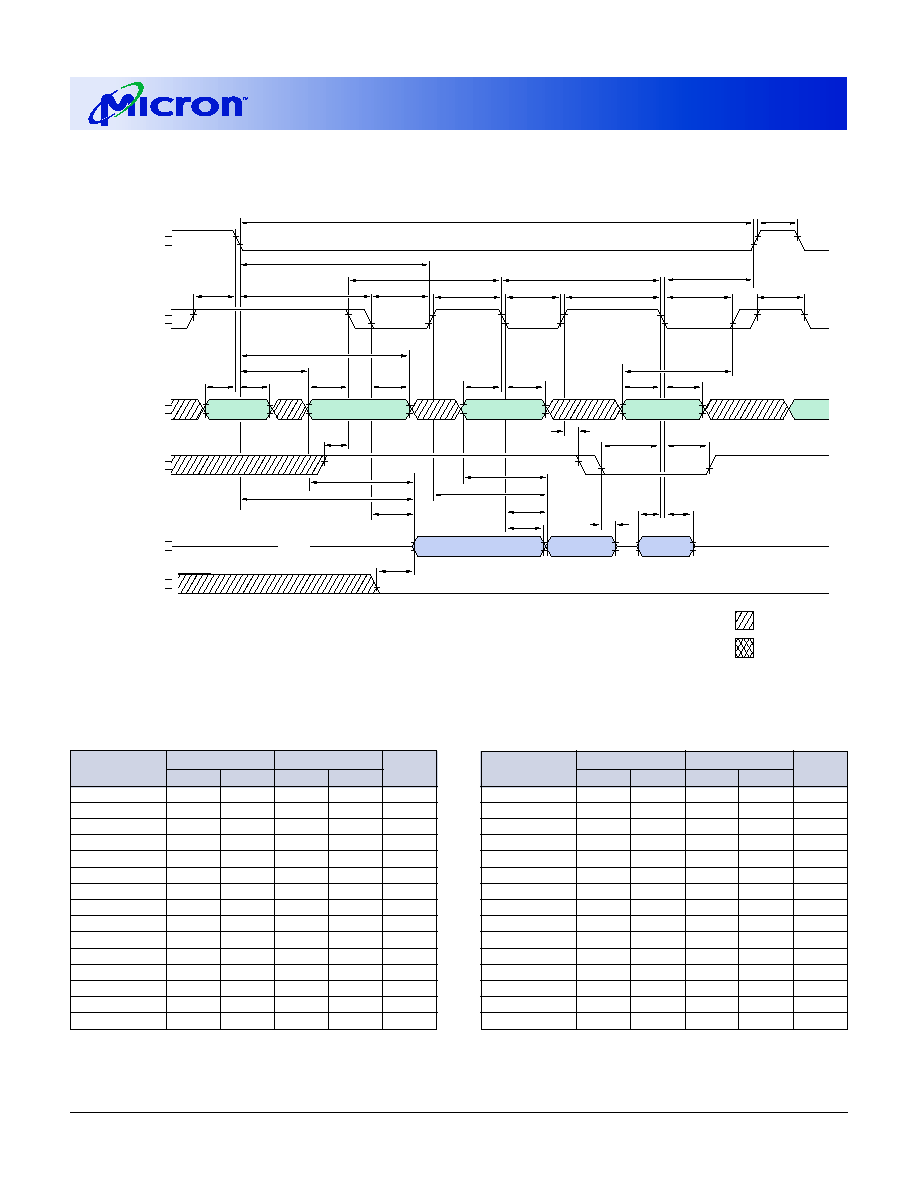

- Timing Diagrams

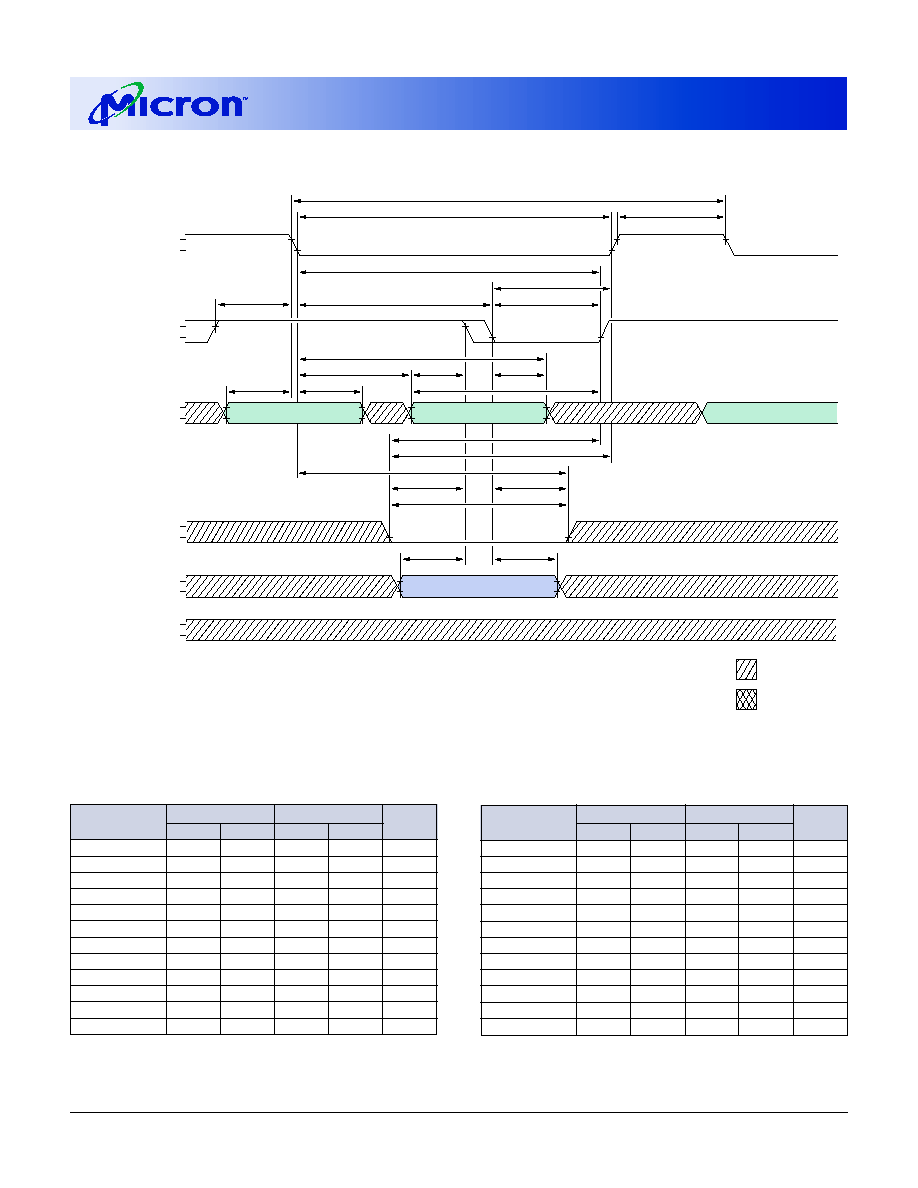

- READ Cycle

- Early WRITE Cycle

- READ-WRITE Cycle

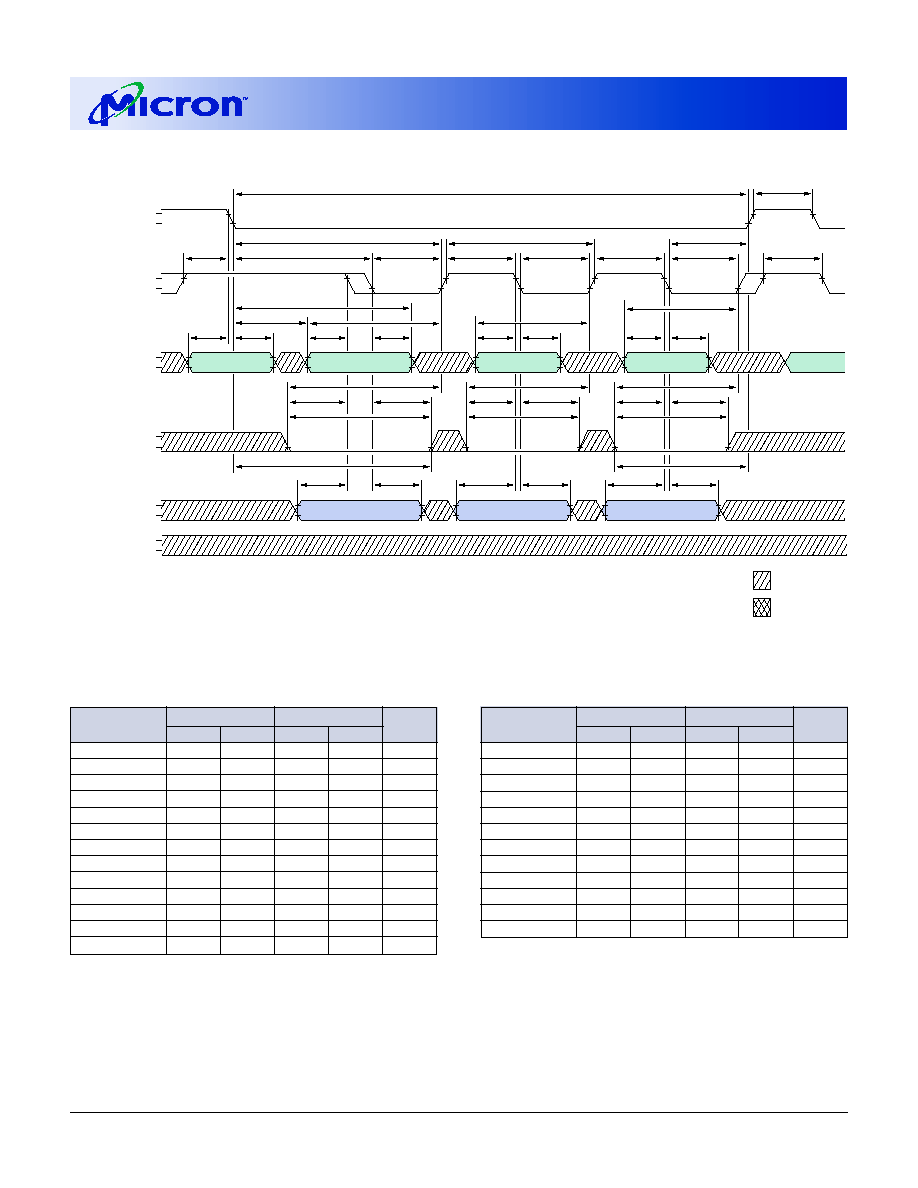

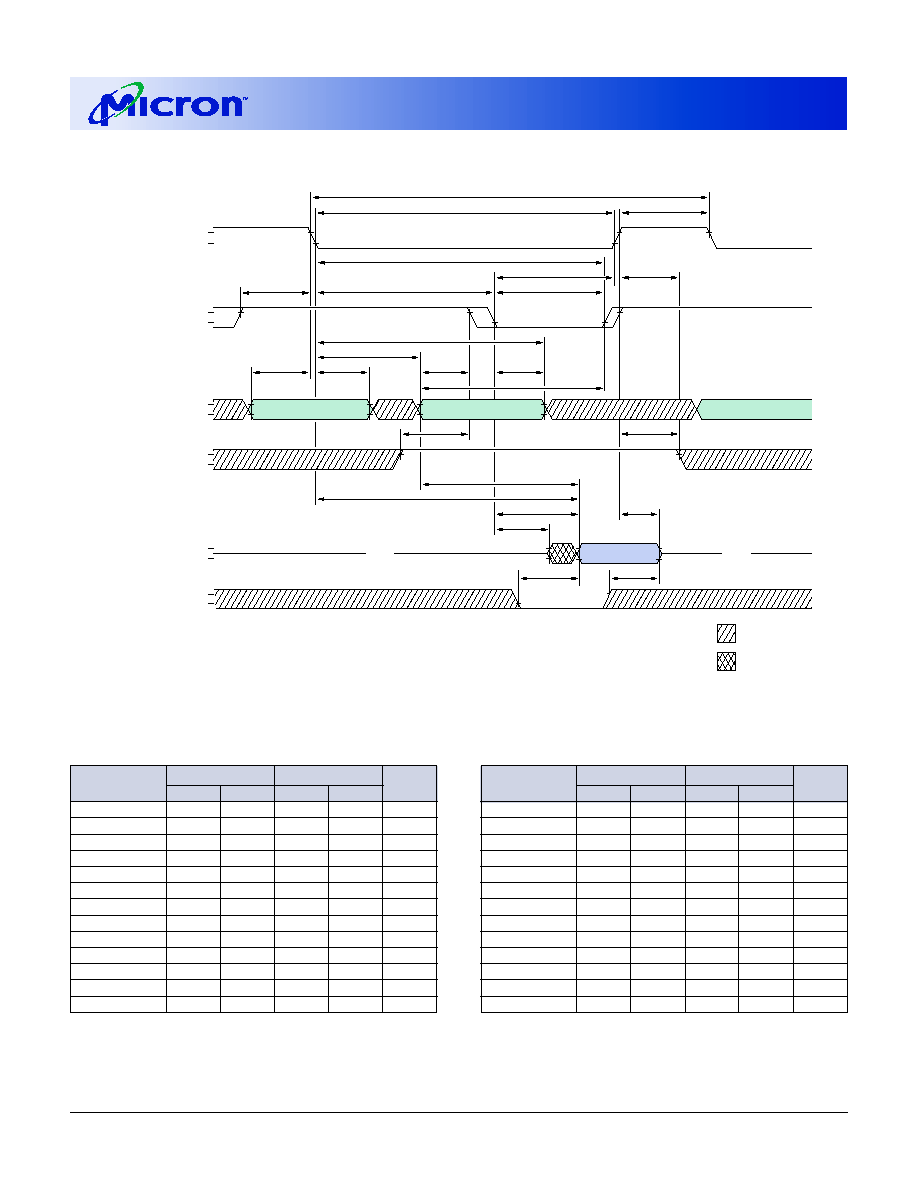

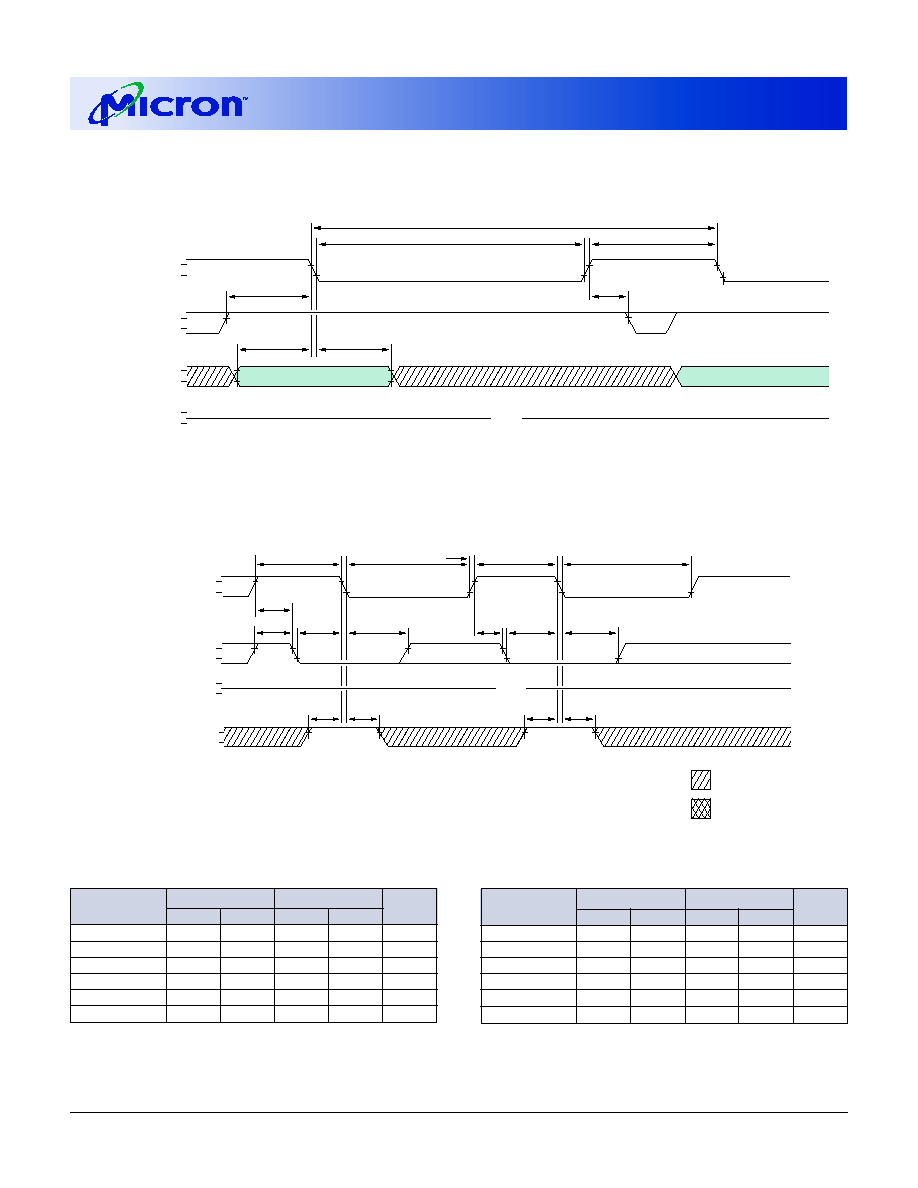

- EDO-Page-Mode READ Cycle

- EDO-Page-Mode EARLY WRITE Cycle

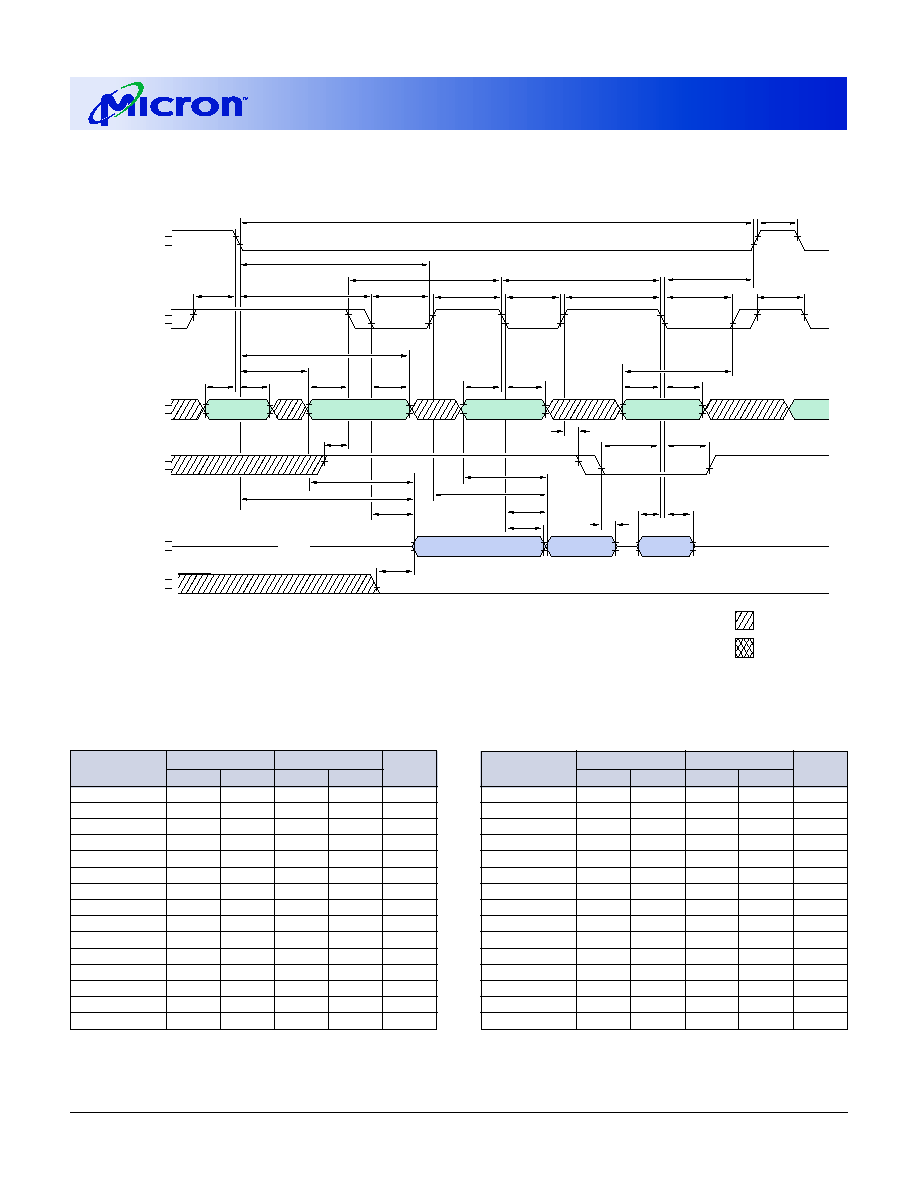

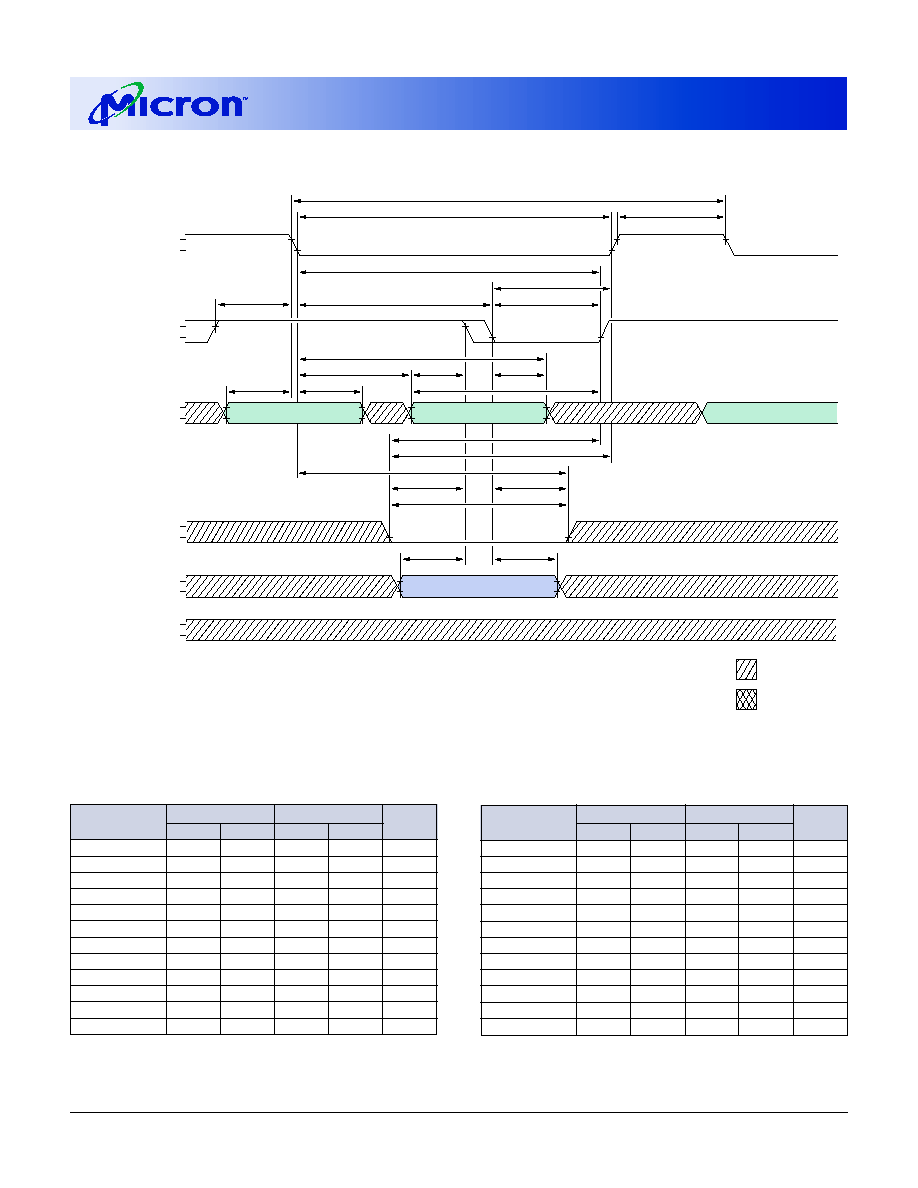

- EDO-Page-Mode READ-WRITE Cycle

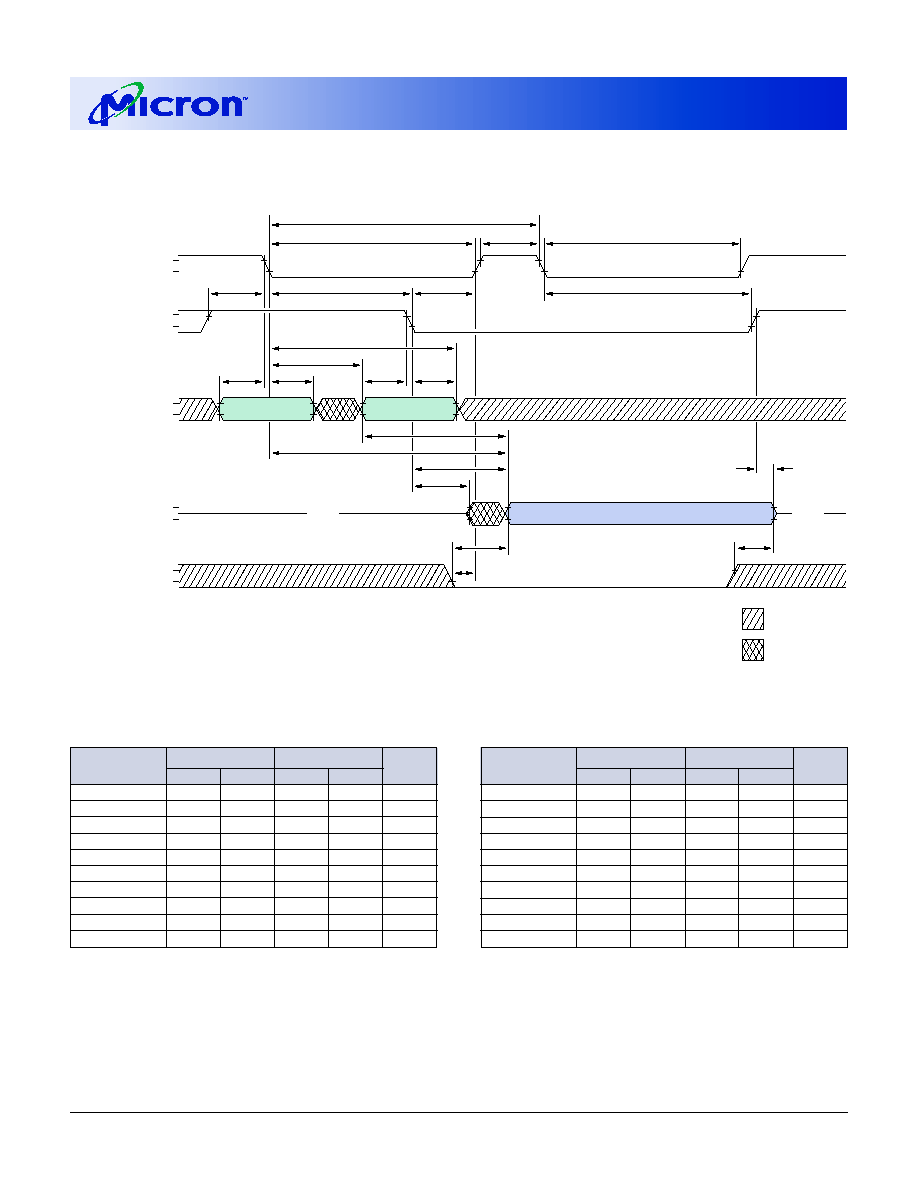

- EDO-Page-Mode READ Early WRITE Cycle

- READ Cycle (with WE#-cintroled disable)

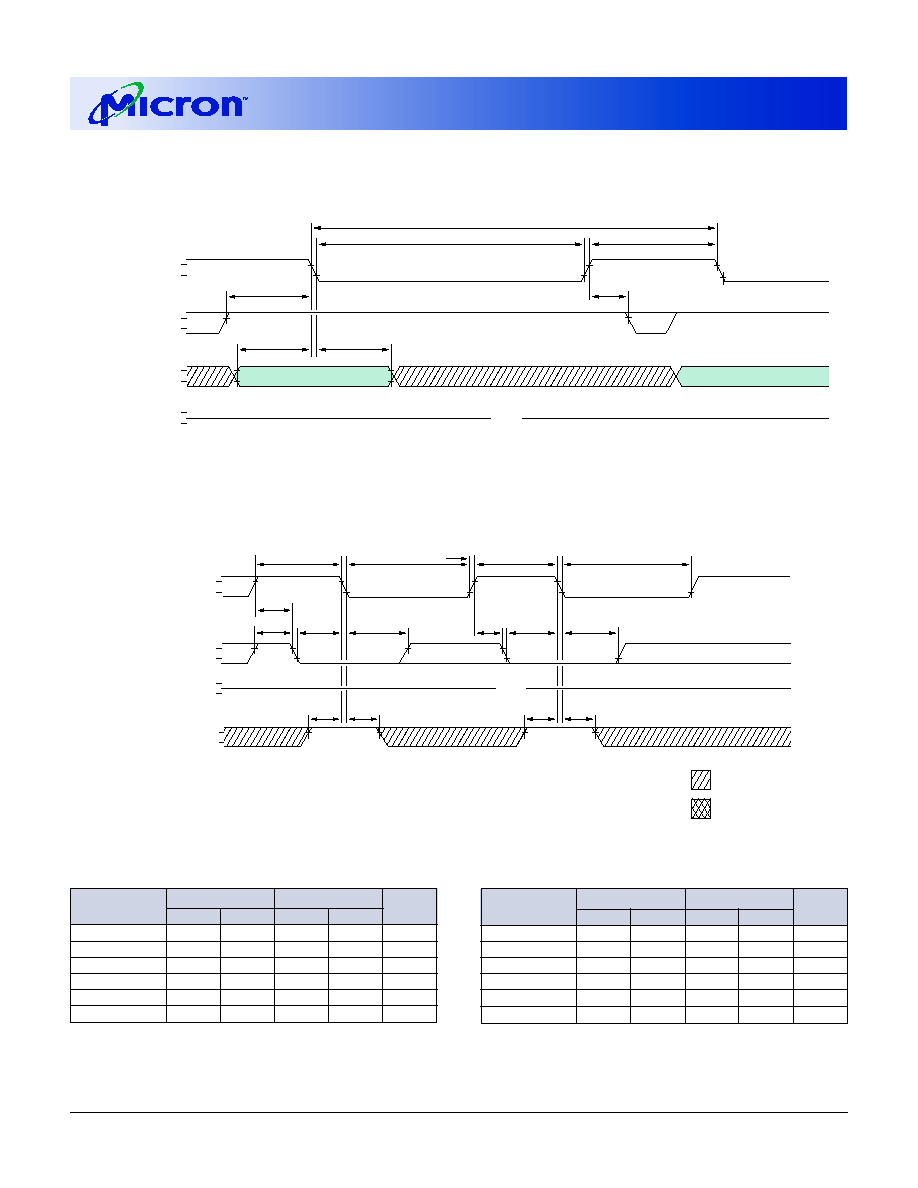

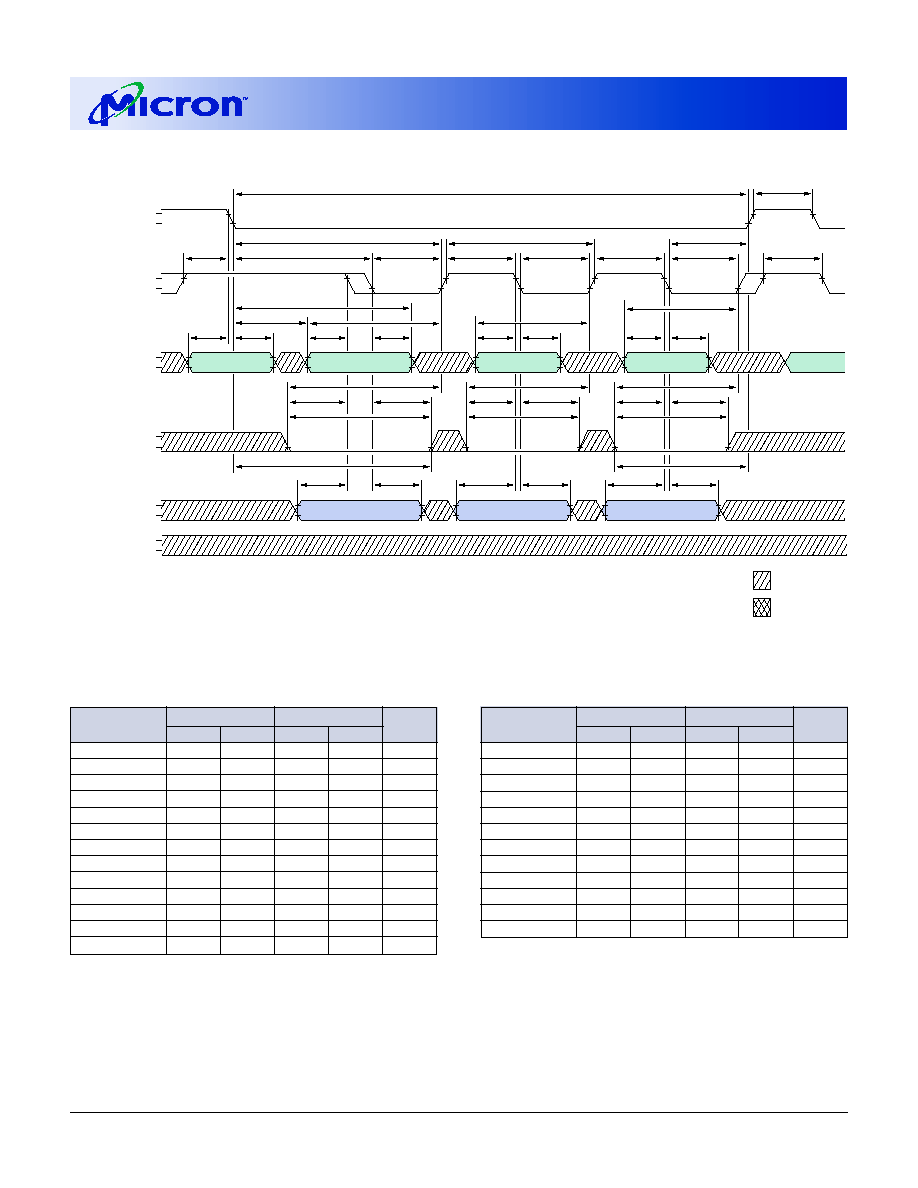

- RAS#-Only Refresh Cycle

- CBR Refresh Cycle

- Hidden Refresh Cycle

- Self Refresh Cycle

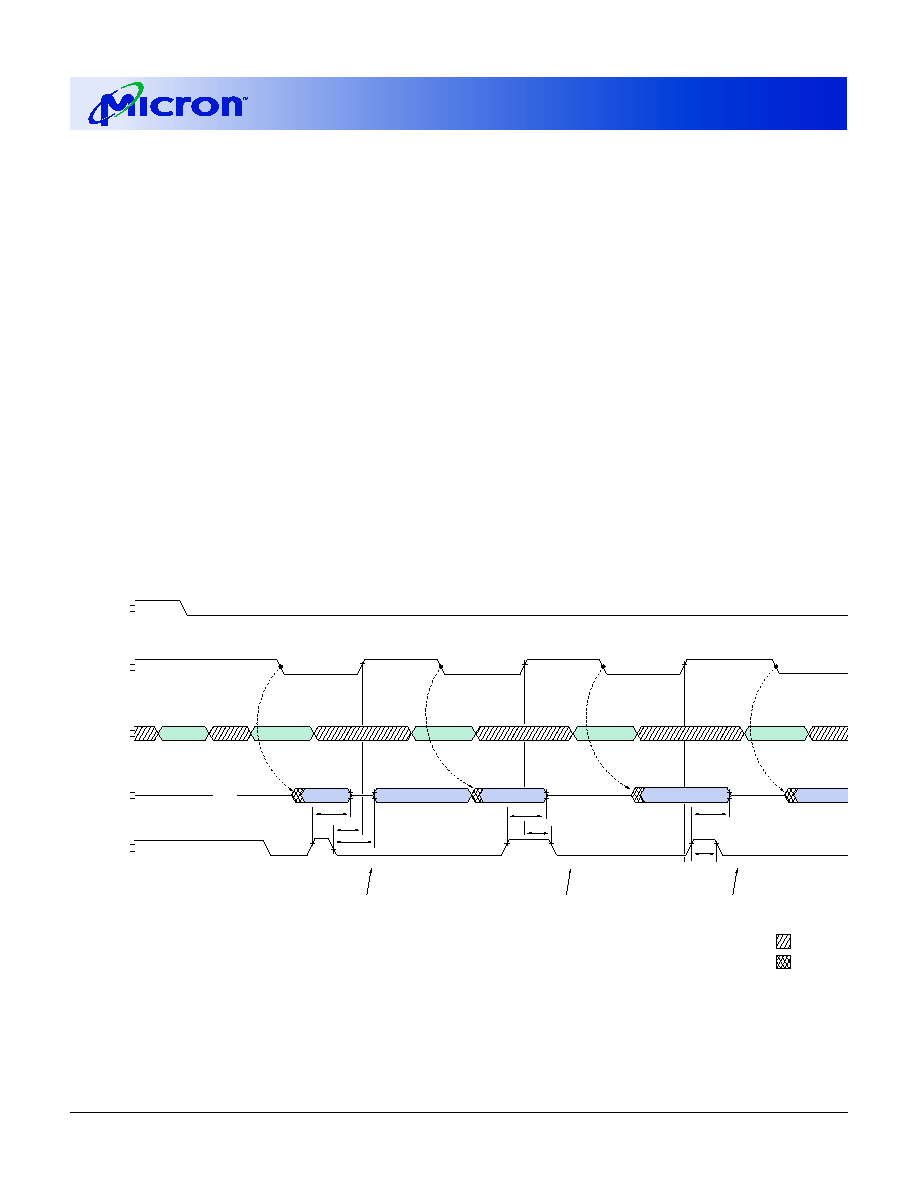

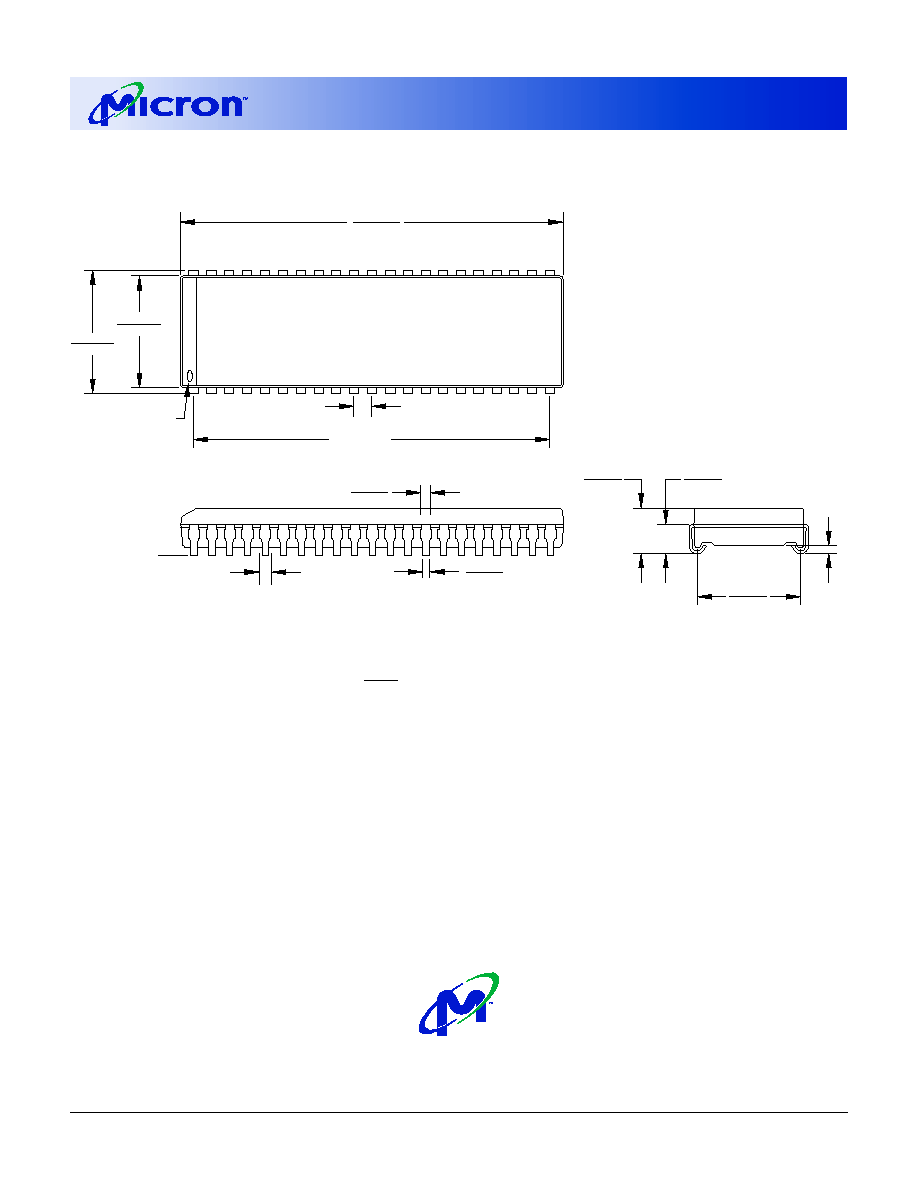

- Package Drawings

- 44/50-Pin Plastic TSOP (400 mil)

- 42-Pin Plastic SOJ (400 mil)

1

1 Meg x 16 EDO DRAM

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

PRODUCTS AND SPECIFICATIONS DISCUSSED HEREIN ARE SUBJECT TO CHANGE BY MICRON WITHOUT NOTICE.

KEY TIMING PARAMETERS

SPEED

t

RC

t

RAC

t

PC

t

AA

t

CAC

t

CAS

-5

84ns

50ns

20ns

25ns

15ns

8ns

-6

104ns

60ns

25ns

30ns

17ns

10ns

FEATURES

∑ JEDEC- and industry-standard x16 timing,

functions, pinouts, and packages

∑ High-performance CMOS silicon-gate process

∑ Single power supply (+3.3V ±0.3V or 5V ±10%)

∑ All inputs, outputs and clocks are TTL-compatible

∑ Refresh modes: RAS#-ONLY, CAS#-BEFORE-RAS#

(CBR), HIDDEN; optional self refresh (S)

∑ BYTE WRITE access cycles

∑ 1,024-cycle refresh (10 row, 10 column addresses)

∑ Extended Data-Out (EDO) PAGE MODE access

∑ 5V-tolerant inputs and I/Os on 3.3V devices

OPTIONS

MARKING

∑ Voltages

1

3.3V

LC

5V

C

∑ Refresh Addressing

1,024 (1K) rows

E5

∑ Packages

Plastic SOJ (400 mil)

DJ

Plastic TSOP (400 mil)

TG

∑ Timing

50ns access

-5

60ns access

-6

∑ Refresh Rates

Standard Refresh (16ms period)

None

Self Refresh (128ms period)

S

2

∑ Operating Temperature Range

Commercial (0

o

C to +70

o

C)

None

Extended (-20

o

C to +80

o

C)

ET

Part Number Example:

MT4LC1M16E5TG-6

NOTE: 1. The third field distinguishes the low voltage offering: LC desig-

nates Vcc = 3.3V and C designates Vcc = 5V.

2. Available only on MT4LC1M16E5 (3.3V)

PIN ASSIGNMENT (Top View)

44/50-Pin TSOP

42-Pin SOJ

1 MEG x 16 EDO DRAM PART NUMBERS

PART NUMBER

Vcc REFRESH PACKAGE REFRESH

MT4LC1M16E5DJ-x

3.3V

1K

400-SOJ

Standard

MT4LC1M16E5DJ-x S

3.3V

1K

400-SOJ

Self

MT4LC1M16E5TG-x

3.3V

1K

400-TSOP

Standard

MT4LC1M16E5TG-x S

3.3V

1K

400-TSOP

Self

MT4C1M16E5DJ-x

5V

1K

400-SOJ

Standard

MT4C1M16E5TG-x

5V

1K

400-TSOP

Standard

NOTE: "-x" indicates speed grade marking under timing

options.

EDO DRAM

MT4C1M16E5 ≠ 1 Meg x 16, 5V

MT4LC1M16E5 ≠ 1 Meg x 16, 3.3V

For the latest data sheet, please refer to the Micron Web

site:

www.micron.com/products/datasheets/sdramds.html

NOTE: The "#" symbol indicates signal is active LOW.

V

CC

DQ0

DQ1

DQ2

DQ3

V

CC

DQ4

DQ5

DQ6

DQ7

NC

NC

NC

WE#

RAS#

NC

NC

A0

A1

A2

A3

V

CC

1

2

3

4

5

6

7

8

9

10

11

15

16

17

18

19

20

21

22

23

24

25

50

49

48

47

46

45

44

43

42

41

40

36

35

34

33

32

31

30

29

28

27

26

V

SS

DQ15

DQ14

DQ13

DQ12

V

SS

DQ11

DQ10

DQ9

DQ8

NC

NC

CASL#

CASH#

OE#

A9

A8

A7

A6

A5

A4

V

SS

V

CC

DQ0

DQ1

DQ2

DQ3

V

CC

DQ4

DQ5

DQ6

DQ7

NC

NC

WE#

RAS#

NC

NC

A0

A1

A2

A3

V

CC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

V

SS

DQ15

DQ14

DQ13

DQ12

V

SS

DQ11

DQ10

DQ9

DQ8

NC

CASL#

CASH#

OE#

A9

A8

A7

A6

A5

A4

V

SS

GENERAL DESCRIPTION

The 1 Meg x 16 is a randomly accessed, solid-state

memory containing 16,777,216 bits organized in a x16

configuration. The 1 Meg x 16 has both BYTE WRITE

and WORD WRITE access cycles via two CAS# pins

(CASL# and CASH#). These function like a single CAS#

found on other DRAMs in that either CASL# or CASH#

will generate an internal CAS#.

The CAS# function and timing are determined by

the first CAS# (CASL# or CASH#) to transition LOW and

the last CAS# to transition back HIGH. Using only one

2

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

Figure 1

OE# Control of DQs

V

V

IH

IL

CASL#/CASH#

V

V

IH

IL

RAS#

V

V

IH

IL

ADDR

ROW

COLUMN (A)

COLUMN (B)

DON'T CARE

UNDEFINED

V

V

IH

IL

OE#

V

V

IOH

IOL

OPEN

DQ

tOD

VALID DATA (B)

VALID DATA (A)

COLUMN (C)

VALID DATA (A)

tOE

VALID DATA (C)

COLUMN (D)

VALID DATA (D)

tOD

tOEHC

tOD

tOEP

tOES

The DQs go back to

Low-Z if

t

OES is met.

The DQs remain High-Z

until the next CAS# cycle

if

t

OEHC is met.

The DQs remain High-Z

until the next CAS# cycle

if

t

OEP is met.

A logic HIGH on WE# dictates read mode, while a

logic LOW on WE# dictates write mode. During a WRITE

cycle, data-in (D) is latched by the falling edge of WE or

CAS# (CASL# or CASH#), whichever occurs last. An

EARLY WRITE occurs when WE is taken LOW prior to

either CAS# falling. A LATE WRITE or READ-MODIFY-

WRITE occurs when WE falls after CAS# (CASL# or

CASH#) was taken LOW. During EARLY WRITE cycles,

the data outputs (Q) will remain High-Z, regardless of

the state of OE#. During LATE WRITE or READ-

MODIFY-WRITE cycles, OE# must be taken HIGH to

disable the data outputs prior to applying input data.

If a LATE WRITE or READ-MODIFY-WRITE is attempted

while keeping OE# LOW, no WRITE will occur, and the

data outputs will drive read data from the accessed

location.

The 16 data inputs and 16 data outputs are routed

through 16 pins using common I/O. Pin direction is

controlled by OE# and WE#.

The 1 Meg x 16 DRAM must be refreshed periodi-

cally in order to retain stored data.

of the two signals results in a BYTE WRITE cycle. CASL#

transitioning LOW selects an access cycle for the lower

byte (DQ0-DQ7), and CASH# transitioning LOW se-

lects an access cycle for the upper byte (DQ8-DQ15).

Each bit is uniquely addressed through the 20 ad-

dress bits during READ or WRITE cycles. These are

entered 10 bits (A0-A9) at a time. RAS# is used to latch

the first 10 bits and CAS#, the latter 10 bits. The CAS#

function also determines whether the cycle will be a

refresh cycle (RAS# ONLY) or an active cycle (READ,

WRITE or READ-WRITE) once RAS# goes LOW.

The CASL# and CASH# inputs internally generate a

CAS# signal that functions like the single CAS# input

on other DRAMs. The key difference is each CAS# input

(CASL# and CASH#) controls its corresponding eight

DQ inputs during WRITE accesses. CASL# controls

DQ0-DQ7, and CASH# controls DQ8-DQ15. The two

CAS# controls give the 1 Meg x 16 both BYTE READ and

BYTE WRITE cycle capabilities.

GENERAL DESCRIPTION (continued)

3

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

V

V

IH

IL

CASL#/CASH#

V

V

IH

IL

RAS#

V

V

IH

IL

ADDR

ROW

COLUMN (A)

DON`T CARE

UNDEFINED

V

V

IH

IL

WE#

V

V

IOH

IOL

OPEN

DQ

tWPZ

The DQs go to High-Z if WE# falls, and if

t

WPZ is met,

will remain High-Z until CAS# goes LOW with

WE# HIGH (i.e., until a READ cycle is initiated).

V

V

IH

IL

OE#

VALID DATA (B)

t

WHZ

WE# may be used to disable the DQs to prepare

for input data in an EARLY WRITE cycle. The DQs

will remain High-Z until CAS# goes LOW with

WE# HIGH (i.e., until a READ cycle is initiated).

t

WHZ

COLUMN (D)

VALID DATA (A)

COLUMN (B)

COLUMN (C)

INPUT DATA (C)

Figure 2

WE# Control of DQs

PAGE ACCESS

Page operations allow faster data operations (READ,

WRITE or READ-MODIFY-WRITE) within a row-

address-defined page boundary. The page cycle is al-

ways initiated with a row address strobed in by RAS#,

followed by a column address strobed in by CAS#. Ad-

ditional columns may be accessed by providing valid

column addresses, strobing CAS# and holding RAS#

LOW, thus executing faster memory cycles. Returning

RAS# HIGH terminates the page mode of operation,

i.e., closes the page.

EDO PAGE MODE

The 1 Meg x 16 provides EDO PAGE MODE, which is

an accelerated FAST-PAGE-MODE cycle. The primary

advantage of EDO is the availability of data-out even

after CAS# returns HIGH. EDO provides for CAS#

precharge time (

t

CP) to occur without the output data

going invalid. This elimination of CAS# output control

provides for pipelined READs.

FAST-PAGE-MODE DRAMs have traditionally

turned the output buffers off (High-Z) with the rising

edge of CAS#. EDO-PAGE-MODE DRAMs operate like

FAST-PAGE-MODE DRAMs, except data will remain

valid or become valid after CAS# goes HIGH during

READs, provided RAS# and OE# are held LOW. If OE# is

pulsed while RAS# and CAS# are LOW, data will toggle

from valid data to High-Z and back to the same valid

data. If OE# is toggled or pulsed after CAS# goes HIGH

while RAS# remains LOW, data will transition to and

remain High-Z (refer to Figure 1). WE# can also perform

the function of disabling the output drivers under cer-

tain conditions, as shown in Figure 2.

During an application, if the DQ outputs are wire

OR'd, OE# must be used to disable idle banks of DRAMs.

Alternatively, pulsing WE# to the idle banks during

CAS# HIGH time will also High-Z the outputs. Inde-

pendent of OE# control, the outputs will disable after

t

OFF, which is referenced from the rising edge of RAS#

or CAS#, whichever occurs last.

BYTE ACCESS CYCLE

The BYTE WRITEs and BYTE READs are determined

by the use of CASL# and CASH#. Enabling CASL# se-

lects a lower BYTE access (DQ0-DQ7). Enabling CASH#

selects an upper BYTE access (DQ8-DQ15). Enabling

both CASL# and CASH# selects a WORD WRITE cycle.

The 1 Meg x 16 may be viewed as two 1 Meg x 8

DRAMs that have common input controls, with the ex-

ception of the CAS# inputs. Figure 3 illustrates the BYTE

WRITE and WORD WRITE cycles.

Additionally, both bytes must always be of the same

mode of operation if both bytes are active. A CAS#

precharge must be satisfied prior to changing modes of

operation between the upper and lower bytes. For ex-

ample, an EARLY WRITE on one byte and a LATE WRITE

on the other byte are not allowed during the same cycle.

4

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

STORED

DATA

1

1

0

1

1

1

1

1

RAS#

CASL#

WE#

X = NOT EFFECTIVE (DON'T CARE)

ADDRESS 1

ADDRESS 0

0

1

0

1

0

0

0

0

WORD WRITE

LOWER BYTE WRITE

CASH#

INPUT

DATA

0

0

1

0

0

0

0

0

1

0

1

0

1

1

1

1

X

X

X

X

X

X

X

X

INPUT

DATA

1

1

0

1

1

1

1

1

INPUT

DATA

STORED

DATA

1

1

0

1

1

1

1

1

INPUT

DATA

STORED

DATA

0

0

1

0

0

0

0

0

1

0

1

0

1

1

1

1

STORED

DATA

0

0

1

0

0

0

0

0

1

0

1

0

1

1

1

1

X

X

X

X

X

X

X

X

1

0

1

0

1

1

1

1

UPPER BYTE

(DQ8-DQ15)

OF WORD

LOWER BYTE

(DQ0-DQ7)

OF WORD

Figure 3

WORD and BYTE WRITE Example

However, an EARLY WRITE on one byte and a LATE

WRITE on the other byte, after a CAS# precharge has

been satisfied, are permissible.

DRAM REFRESH

Preserve correct memory cell data by maintaining

power and executing any RAS# cycle (READ, WRITE) or

RAS# REFRESH cycle (RAS#-ONLY, CBR or HIDDEN)

so that all 1,024 combinations of RAS# addresses are

executed within

t

REF (MAX), regardless of sequence.

The CBR, EXTENDED and SELF REFRESH cycles will

invoke the internal refresh counter for automatic RAS#

addressing.

An optional self refresh mode is available on the "S"

version. The self refresh feature is initiated by per-

forming a CBR REFRESH cycle and holding RAS# LOW

for the specified

t

RASS. The "S" option allows the user

the choice of a fully static, low-power data retention

mode or a dynamic refresh mode at the extended re-

fresh period of 128ms, or 125µs per row, when using a

distributed CBR REFRESH. This refresh rate can be

applied during normal operation, as well as during a

standby or battery backup mode.

The self refresh mode is terminated by driving

RAS# HIGH for a minimum time of

t

RPS. This delay

allows for the completion of any internal refresh cycles

that may be in process at the time of the RAS# LOW-to-

HIGH transition. If the DRAM controller uses a distrib-

uted refresh sequence, a burst refresh is not required

upon exiting self refresh. However, if the DRAM con-

troller utilizes a RAS#-ONLY or burst refresh sequence,

all 1,024 rows must be refreshed within the average

internal refresh rate, prior to the resumption of normal

operation.

STANDBY

Returning RAS# and CAS# HIGH terminates a

memory cycle and decreases chip current to a reduced

standby level. The chip is preconditioned for the next

cycle during the RAS# HIGH time.

5

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

CASL#

CAS#

RAS#

10

10

NO. 2 CLOCK

GENERATOR

REFRESH

CONTROLLER

NO. 1 CLOCK

GENERATOR

1,024 x 1,024 x 16

MEMORY

ARRAY

V

DD

V

SS

10

OE#

DQ0

DQ15

REFRESH

COUNTER

CASH#

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

1,024

1,024 x 16

16

10

10

SENSE AMPLIFIERS

I/O GATING

1,024

DATA-OUT

BUFFER

WE#

16

ROW-

ADDRESS

BUFFERS (10)

ROW

DECODER

COLUMN-

ADDRESS

BUFFER

DATA-IN BUFFER

COLUMN

DECODER

16

FUNCTIONAL BLOCK DIAGRAM

6

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

DC ELECTRICAL CHARACTERISTICS AND OPERATING CONDITIONS

(Notes: 1; notes appear on pages 10-11)

3.3V

5V

PARAMETER/CONDITION

SYMBOL

MIN

MAX

MIN

MAX

UNITS NOTES

SUPPLY VOLTAGE

V

CC

3.0

3.6

4.5

5.5

V

INPUT HIGH VOLTAGE:

Valid Logic 1; All inputs, I/Os and any NC

V

IH

2.0

5.5

2.4

V

CC

+ 1

V

INPUT LOW VOLTAGE:

Valid Logic 0; All inputs, I/Os and any NC

V

IL

-1.0

0.8

-0.5

0.8

V

INPUT LEAKAGE CURRENT:

Any input at V

IN

(0V

£ V

IN

£ V

IH

[MAX]);

I

I

-2

2

-2

2

µA

4

All other pins not under test = 0V

OUTPUT HIGH VOLTAGE:

I

OUT

= -2mA(3.3V), -5mA(5V)

V

OH

2.4

≠

2.4

≠

V

OUTPUT LOW VOLTAGE:

I

OUT

= 2mA(3.3V), 4.2mA(5V)

V

OL

≠

0.4

≠

0.4

V

OUTPUT LEAKAGE CURRENT:

Any output at V

OUT

(0V

£ V

OUT

£ 5.5V);

I

OZ

-5

5

-5

5

µA

DQ is disabled and in High-Z state

ABSOLUTE MAXIMUM RATINGS*

Voltage on V

CC

Pin Relative to V

SS

3.3V ......................................................... -1V to +4.6V

5V ............................................................... -1V to +7V

Voltage on NC, Inputs or I/O Pins Relative to Vss:

3.3V ......................................................... -1V to +5.5V

5V ............................................................... -1V to +7V

Operating Temperature

T

A

(commercial) .................................. 0∫C to +70∫C

T

A

(extended) ................................... -20∫C to +80∫C

Storage Temperature (plastic) ........... -55∫C to +150∫C

Power Dissipation ........................................................ 1W

Short Circuit Output Current ................................ 50mA

*Stresses greater than those listed under "Absolute

Maximum Ratings" may cause permanent damage to

the device. This is a stress rating only, and functional

operation of the device at these or any other conditions

above those indicated in the operational sections of

this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may

affect reliability.

7

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

I

CC

OPERATING CONDITIONS AND MAXIMUM LIMITS

(Notes: 1, 2, 3, 5, 8; notes appear on pages 10-11); (V

CC

[MIN]

£ V

CC

£ V

CC

[MAX])

PARAMETER/CONDITION

SYMBOL SPEED

3.3V

5V

UNITS NOTES

STANDBY CURRENT: TTL

I

CC

1

ALL

1

2

mA

(RAS# = CAS# = V

IH

)

STANDBY CURRENT: CMOS (non-"S" version only)

I

CC

2

ALL

500

500

µA

(RAS# = CAS# = other inputs = V

DD

- 0.2V)

STANDBY CURRENT: CMOS ("S" version only)

I

CC

2

ALL

150

150

µA

(RAS# = CAS# = other inputs = V

DD

- 0.2V)

OPERATING CURRENT: Random READ/WRITE

I

CC

3

-5

180

190

mA

6

Average power supply current

-6

170

180

(RAS#, CAS#, address cycling:

t

RC =

t

RC [MIN])

OPERATING CURRENT: EDO PAGE MODE

I

CC

4

-5

140

150

mA

6

Average power supply current (RAS# = V

IL

, CAS#,

-6

130

140

address cycling:

t

PC =

t

PC [MIN])

REFRESH CURRENT: RAS#-ONLY

I

CC

5

-5

180

190

mA

Average power supply current

-6

170

180

(RAS# cycling, CAS# = V

IH

:

t

RC =

t

RC [MIN])

REFRESH CURRENT: CBR

I

CC

6

-5

180

180

mA

7, 9

Average power supply current

-6

170

170

(RAS#, CAS#, address cycling:

t

RC =

t

RC [MIN])

REFRESH CURRENT: Extended ("S" version only)

I

CC

7

ALL

300

300

µA

7, 9

Average power supply current: CAS# = 0.2V or CBR cycling;

RAS# =

t

RAS (MIN); WE# = V

DD

- 0.2V; A0-A10, OE# and

D

IN

= V

DD

- 0.2V or 0.2V (D

IN

may be left open);

t

RC = 125µs

REFRESH CURRENT: Self ("S" version only)

I

CC

8

ALL

300

300

µA

7, 9

Average power supply current: CBR with RAS#

t

RASS (MIN)

and CAS# held LOW; WE# = V

DD

- 0.2V; A0-A10,

OE# and D

IN

= V

DD

- 0.2V or 0.2V (D

IN

may be left open)

8

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

CAPACITANCE

(Notes: 1, 2, 3, 5, 8; notes appear on pages 10-11)

PARAMETER

SYMBOL MAX UNITS NOTES

Input Capacitance: Addresses

C

I

1

5

p F

Input Capacitance: RAS#, CASL#,CASH#, WE#, OE#

C

I

2

7

p F

Input/Output Capacitance: DQ

C

IO

7

p F

AC ELECTRICAL CHARACTERISTICS

(Notes: 2, 3, 9, 10, 11, 12; notes appear on pages 10-11); (V

CC

[MIN]

£ V

CC

£ V

CC

[MAX])

AC CHARACTERISTICS

-5

-6

PARAMETER

SYMBOL

MIN

MAX

MIN

MAX

UNITS NOTES

Access time from column address

t

AA

25

30

ns

Column-address setup to CAS# precharge

t

ACH

12

15

ns

Column-address hold time (referenced to RAS#)

t

AR

38

45

ns

Column-address setup time

t

ASC

0

0

ns

25

Row-address setup time

t

ASR

0

0

ns

25

Column address to WE# delay time

t

AWD

42

49

ns

13

Access time from CAS#

t

CAC

13

15

ns

14, 25

Column-address hold time

t

CAH

8

10

ns

25

CAS# pulse width

t

CAS

8

10,000

10

10,000

ns

27

CAS# LOW to "Don't Care" during Self Refresh

t

CHD

15

15

ns

CAS# hold time (CBR Refresh)

t

CHR

8

10

ns

7, 26

Last CAS# going LOW to first CAS# to return HIGH

t

CLCH

5

5

ns

28

CAS# to output in Low-Z

t

CLZ

0

0

ns

26

Data output hold after next CAS# LOW

t

COH

3

3

ns

CAS# precharge time

t

CP

8

10

ns

15, 30

Access time from CAS# precharge

t

CPA

28

35

ns

26

CAS# to RAS# precharge time

t

CRP

5

5

ns

26

CAS# hold time

t

CSH

38

45

ns

26

CAS# setup time (CBR Refresh)

t

CSR

5

5

ns

7, 25

CAS# to WE# delay time

t

CWD

28

35

ns

13, 25

WRITE command to CAS# lead time

t

CWL

8

10

ns

26

Data-in hold time

t

DH

8

10

ns

16, 25

Data-in setup time

t

DS

0

0

ns

16, 25

Output disable

t

OD

0

12

0

15

ns

Output enable

t

OE

12

15

ns

17

OE# hold time from WE# during

t

OEH

8

10

ns

18

READ-MODIFY-WRITE cycle

OE# HIGH hold from CAS# HIGH

t

OEHC

5

10

ns

18

OE# HIGH pulse width

t

OEP

5

5

ns

OE# LOW to CAS# HIGH setup time

t

OES

4

5

ns

Output buffer turn-off delay

t

OFF

0

12

0

15

ns

20, 26

9

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

AC ELECTRICAL CHARACTERISTICS (continued)

(Notes: 2, 3, 9, 10, 11, 12; notes appear on pages 10-11); (V

CC

[MIN]

£ V

CC

£ V

CC

[MAX])

AC CHARACTERISTICS

-5

-6

PARAMETER

SYMBOL

MIN

MAX

MIN

MAX

UNITS NOTES

OE# setup prior to RAS#

t

ORD

0

0

ns

during HIDDEN REFRESH cycle

EDO-PAGE-MODE READ or WRITE cycle time

t

PC

20

25

ns

31

EDO-PAGE-MODE READ-WRITE cycle time

t

PRWC

47

56

ns

31

Access time from RAS#

t

RAC

50

60

ns

19

RAS# to column-address delay time

t

RAD

9

12

ns

21

Row address hold time

t

RAH

9

10

ns

RAS# pulse width

t

RAS

50

10,000

60

10,000

ns

RAS# pulse width (EDO PAGE MODE)

t

RASP

50

125,000

60

125,000

ns

RAS# pulse width during Self Refresh

t

RASS

100

100

µs

Random READ or WRITE cycle time

t

RC

84

104

ns

RAS# to CAS# delay time

t

RCD

11

14

ns

22, 25

READ command hold time (referenced to CAS#)

t

RCH

0

0

ns

23, 27

READ command setup time

t

RCS

0

0

ns

25

Refresh period (1,024 cycles)

t

REF

16

16

ms

Refresh period (1,024 cycles) S version

t

REF

128

128

ms

RAS# precharge time

t

RP

30

40

ns

RAS# to CAS# precharge time

t

RPC

5

5

ns

RAS# precharge time exiting Self Refresh

t

RPS

90

105

ns

READ command hold time (referenced to RAS#)

t

RRH

0

0

ns

23

RAS# hold time

t

RSH

13

15

ns

32

READ-WRITE cycle time

t

RWC

116

140

ns

RAS# to WE# delay time

t

RWD

67

79

ns

13

WRITE command to RAS# lead time

t

RWL

13

15

ns

Transition time (rise or fall)

t

T

2

50

2

50

ns

WRITE command hold time

t

WCH

8

10

ns

32

WRITE command hold time (referenced to RAS#)

t

WCR

38

45

ns

WE# command setup time

t

WCS

0

0

ns

13, 25

Output disable delay from WE#

t

WHZ

0

12

0

15

ns

WRITE command pulse width

t

WP

5

5

ns

WE# pulse to disable at CAS# HIGH

t

WPZ

10

10

ns

WE# hold time (CBR Refresh)

t

WRH

8

10

ns

WE# setup time (CBR Refresh)

t

WRP

8

10

ns

10

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

NOTES

1. All voltages referenced to V

SS

.

2. The minimum specifications are used only to

indicate cycle time at which proper operation over

the full temperature range (0∫C

£ T

A

£ 70∫C for

commercial) and (-20∫C

£ T

A

£ 80∫C for extended)

is ensured.

3. An initial pause of 100µs is required after power-

up, followed by eight RAS# refresh cycles (RAS#-

ONLY or CBR with WE# HIGH), before proper

device operation is ensured. The eight RAS# cycle

wake-ups should be repeated any time the

t

REF

refresh requirement is exceeded.

4. NC pins are assumed to be left floating and are

not tested for leakage.

5. I

CC

is dependent on output loading and cycle

rates. Specified values are obtained with mini-

mum cycle time and the outputs open.

6. Column address changed once each cycle.

7. Enables on-chip refresh and address counters.

8. This parameter is sampled. V

DD

= +3.3V; f = 1 MHz.

9. AC characteristics assume

t

T = 2.5ns.

10.V

IH

(MIN) and V

IL

(MAX) are reference levels for

measuring timing of input signals. Transition

times are measured between V

IH

and V

IL

(or

between V

IL

and V

IH

).

11.In addition to meeting the transition rate

specification, all input signals must transit

between V

IH

and V

IL

(or between V

IL

and V

IH

) in a

monotonic manner.

12.Measured with a load equivalent to two TTL gates

and 100pF; and V

OL

= 0.8V and V

OH

= 2V.

13.

t

WCS,

t

RWD,

t

AWD, and

t

CWD are not restrictive

operating parameters.

t

WCS applies to EARLY

WRITE cycles.

t

RWD,

t

AWD and

t

CWD apply to

READ-MODIFY-WRITE cycles. If

t

WCS

t

WCS

(MIN), the cycle is an EARLY WRITE cycle and the

data output will remain an open circuit through-

out the entire cycle. If

t

WCS <

t

WCS (MIN) and

t

RWD

t

RWD (MIN),

t

AWD

t

AWD (MIN) and

t

CWD

t

CWD (MIN), the cycle is a READ-

MODIFY-WRITE and the data output will contain

data read from the selected cell. If neither of the

above conditions is met, the state of data-out is

indeterminate. OE# held HIGH and WE# taken

LOW after CAS# goes LOW results in a LATE

WRITE (OE#-controlled) cycle.

t

WCS,

t

RWD,

t

CWD

and

t

AWD are not applicable in a LATE WRITE

cycle.

14.Assumes that

t

RCD

t

RCD (MAX).

15.If CAS# is LOW at the falling edge of RAS#, Q will

be maintained from the previous cycle. To initiate

a new cycle and clear the data-out buffer, CAS#

must be pulsed HIGH for

t

CP.

16.These parameters are referenced to CAS# leading

edge in EARLY WRITE cycles and WE# leading

edge in LATE WRITE or READ-MODIFY-WRITE

cycles.

17.If OE# is tied permanently LOW, LATE WRITE, or

READ-MODIFY-WRITE operations are not

permissible and should not be attempted.

Additionally, WE# must be pulsed during CAS#

HIGH time in order to place I/O buffers in High-Z.

18.LATE WRITE and READ-MODIFY-WRITE cycles

must have both

t

OD and

t

OEH met (OE# HIGH

during WRITE cycle) in order to ensure that the

output buffers will be open during the WRITE

cycle. The DQs will provide the previously read

data if CAS# remains LOW and OE# is taken back

LOW after

t

OEH is met. If CAS# goes HIGH prior to

OE# going back LOW, the DQs will remain open.

19.Assumes that

t

RCD <

t

RCD (MAX). If

t

RCD is

greater than the maximum recommended value

shown in this table,

t

RAC will increase by the

amount that

t

RCD exceeds the value shown.

20.

t

OFF (MAX) defines the time at which the output

achieves the open circuit condition and is not

referenced to V

OH

or V

OL

. It is referenced from the

rising edge of RAS# or CAS#, whichever occurs last.

21.The

t

RAD (MAX) limit is no longer specified.

t

RAD

(MAX) was specified as a reference point only. If

t

RAD was greater than the specified

t

RAD (MAX)

limit, then access time was controlled exclusively

by

t

AA (

t

RAC and

t

CAC no longer applied). With or

without the

t

RAD (MAX) limit,

t

AA,

t

RAC, and

t

CAC

must always be met.

22.The

t

RCD (MAX) limit is no longer specified.

t

RCD

(MAX) was specified as a reference point only. If

t

RCD was greater than the specified

t

RCD (MAX)

limit, then access time was controlled exclusively

by

t

CAC (

t

RAC [MIN] no longer applied). With or

without the

t

RCD limit,

t

AA and

t

CAC must always

be met.

23.Either

t

RCH or

t

RRH must be satisfied for a READ

cycle.

24.The first CAS#x edge to transition LOW.

25.Output parameter (DQx) is referenced to corre-

sponding CAS# input; DQ0-DQ7 by CASL# and

DQ8-DQ15 by CASH#.

11

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

NOTES (continued)

26.Each CAS#x must meet minimum pulse width.

27.The last CAS#x edge to transition HIGH.

28.Last falling CAS#x edge to first rising CAS#x edge.

29.Last rising CAS#x edge to first falling CAS#x edge.

30.Last rising CAS#x edge to next cycle's last rising

CAS#x edge.

31.Last CAS#x to go LOW.

32.A HIDDEN REFRESH may also be performed after

a WRITE cycle. In this case, WE# is LOW and

OE# is HIGH.

12

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

TIMING PARAMETERS

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

t

AA

25

30

ns

t

ACH

12

15

ns

t

AR

38

45

ns

t

ASC

0

0

ns

t

ASR

0

0

ns

t

CAC

13

15

ns

t

CAH

8

10

ns

t

CAS

8

10,000

10

10,000

ns

t

CLCH

5

5

ns

t

CLZ

0

0

ns

t

CRP

5

5

ns

t

CSH

38

45

ns

t

OD

0

12

0

15

ns

READ CYCLE

NOTE: 1.

t

OFF is referenced from rising edge of RAS# or CAS#, whichever occurs last.

tRRH

tCLZ

tCAC

tRAC

tAA

VALID DATA

OPEN

tOFF

tRCH

ROW

tRCS

tASC

tRAH

tRAD

tAR

tCAH

tRCD

tCAS

tRSH

tCSH

tRP

tRC

tRAS

tCRP

tASR

ROW

OPEN

RAS#

V

V

IH

IL

V

V

IH

IL

ADDR

V

V

IH

IL

DQ

V

V

OH

OL

V

V

IH

IL

tOD

tOE

OE#

V

V

IH

IL

COLUMN

WE#

CASL#/CASH#

tCLCH

NOTE 1

tACH

DON'T CARE

UNDEFINED

t

OE

12

15

ns

t

OFF

0

12

0

15

ns

t

RAC

50

60

ns

t

RAD

9

12

ns

t

RAH

9

10

ns

t

RAS

50

10,000

60

10,000

ns

t

RC

84

104

ns

t

RCD

11

14

ns

t

RCH

0

0

ns

t

RCS

0

0

ns

t

RP

30

40

ns

t

RRH

0

0

ns

t

RSH

13

15

ns

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

13

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

EARLY WRITE CYCLE

DON'T CARE

UNDEFINED

V

V

IH

IL

VALID DATA

ROW

COLUMN

ROW

tDS

tWP

tWCH

tWCS

tWCR

tRWL

tCWL

tCAH

tASC

tRAH

tASR

tRAD

tAR

tCAS

tRSH

tCSH

tRCD

tCRP

tRAS

tRC

tRP

V

V

IH

IL

ADDR

V

V

IH

IL

V

V

IH

IL

DQ

V

V

IOH

IOL

V

V

IH

IL

RAS#

OE#

tDH

tCLCH

WE#

CASL#/CASH#

tACH

TIMING PARAMETERS

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

t

ACH

12

15

ns

t

AR

38

45

ns

t

ASC

0

0

ns

t

ASR

0

0

ns

t

CAH

8

10

ns

t

CAS

8

10,000

10

10,000

ns

t

CLCH

5

5

ns

t

CRP

5

5

ns

t

CSH

38

45

ns

t

CWL

8

10

ns

t

DH

8

10

ns

t

DS

0

0

ns

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

t

RAD

9

12

ns

t

RAH

9

10

ns

t

RAS

50

10,000

60

10,000

ns

t

RC

84

104

ns

t

RCD

11

14

ns

t

RP

30

40

ns

t

RSH

13

15

ns

t

RWL

13

15

ns

t

WCH

8

10

ns

t

WCR

38

45

ns

t

WCS

0

0

ns

t

WP

5

5

ns

14

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

READ-WRITE CYCLE

(LATE WRITE and READ-MODIFY-WRITE cycles)

VALID D

OUT

VALID D

IN

ROW

COLUMN

ROW

V

V

IH

IL

V

V

IH

IL

ADDR

V

V

IH

IL

V

V

IH

IL

DQ

V

V

IOH

IOL

V

V

IH

IL

RAS#

OPEN

OPEN

tOE

tOD

tCAC

tRAC

tAA

tCLZ

tDS

tDH

tAWD

tWP

tRWL

tCWL

tCWD

tRWD

tRCS

tASC

tCAH

tAR

tASR

tRAD

tCRP

tRCD

tCAS, CLCH

tRSH

tCSH

tRAS

tRWC

tRP

tRAH

OE#

tOEH

WE#

tACH

CASL#/CASH#

t

DON'T CARE

UNDEFINED

TIMING PARAMETERS

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

t

AA

25

30

ns

t

ACH

12

15

ns

t

AR

38

45

ns

t

ASC

0

0

ns

t

AWD

42

49

ns

t

ASR

0

0

ns

t

CAC

13

15

ns

t

CAH

8

10

ns

t

CAS

8

10,000

10

10,000

ns

t

CLCH

5

5

ns

t

CLZ

0

0

ns

t

CRP

5

5

ns

t

CSH

38

45

ns

t

CWD

28

35

ns

t

CWL

8

10

ns

t

DH

8

10

ns

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

t

DS

0

0

ns

t

OD

0

12

0

15

ns

t

OE

12

15

ns

t

OEH

8

10

ns

t

RAC

50

60

ns

t

RAD

9

12

ns

t

RAH

9

10

ns

t

RAS

50

10,000

60

10,000

ns

t

RCD

11

14

ns

t

RCS

0

0

ns

t

RP

30

40

ns

t

RSH

13

15

ns

t

RWC

116

140

ns

t

RWD

67

79

ns

t

RWL

13

15

ns

t

WP

5

5

ns

15

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

EDO-PAGE-MODE READ CYCLE

ACH

VALID

DATA

VALID

DATA

VALID

DATA

COLUMN

COLUMN

COLUMN

ROW

ROW

DON'T CARE

UNDEFINED

tOD

tCAH

tASC

tCP

tRSH

tCP

tCP

tCAS, CLCH

tRCD

tCRP

tPC

tCSH

tRASP

tRP

tCAH

tASC

tCAH

tASC

tRAD

t

AR

tRAH

tRAD

tASR

tRCS

tRRH

tRCH

tOFF

tCAC

tCPA

tAA

tCLZ

tCAC

tCPA

tAA

tCAC

tRAC

tAA

tCLZ

tOE

tOD

tOE

tOD

OPEN

OPEN

V

V

IH

IL

V

V

IH

IL

ADDR

V

V

IH

IL

V

V

IH

IL

DQ

V

V

OH

OL

V

V

IH

IL

RAS#

OE#

CASL#/CASH#

WE#

tCOH

tOEP

tOEHC

tOES

tOES

t

tCAS, CLCH

t

tCAS, CLCH

t

t

ACH

t

ACH

t

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

t

OE

12

15

ns

t

OEHC

5

10

ns

t

OEP

5

5

ns

t

OES

4

5

ns

t

OFF

0

12

0

15

ns

t

PC

20

25

ns

t

RAC

50

60

ns

t

RAD

9

12

ns

t

RAH

9

10

1ns

t

RASP

50

125,000

60

125,000

ns

t

RCD

11

14

ns

t

RCH

0

0

ns

t

RCS

0

0

ns

t

RP

30

40

ns

t

RRH

0

0

ns

t

RSH

13

15

ns

TIMING PARAMETERS

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

t

AA

25

30

ns

t

ACH

12

15

ns

t

AR

38

45

ns

t

ASC

0

0

ns

t

ASR

0

0

ns

t

CAC

13

15

ns

t

CAH

8

10

ns

t

CAS

8

10,000

10

10,000

ns

t

CLCH

5

5

ns

t

CLZ

0

0

ns

t

COH

3

3

ns

t

CP

8

10

ns

t

CPA

28

35

ns

t

CRP

5

5

ns

t

CSH

38

45

ns

t

OD

0

12

0

15

ns

16

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

TIMING PARAMETERS

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

t

ACH

12

15

ns

t

AR

38

45

ns

t

ASC

0

0

ns

t

ASR

0

0

ns

t

CAH

8

10

ns

t

CAS

8

10,000

10

10,000

ns

t

CLCH

5

5

ns

t

CP

8

10

ns

t

CRP

5

5

ns

t

CSH

38

45

ns

t

CWL

8

10

ns

t

DH

8

10

ns

t

DS

0

0

ns

EDO-PAGE-MODE EARLY WRITE CYCLE

tDS

tDH

tDS

tDH

tDS

tDH

tWCR

VALID DATA

VALID DATA

VALID DATA

tRWL

tWP

tCWL

tWCH

tWCS

tWP

tCWL

tWCH

tWCS

tWP

tCWL

tWCH

tWCS

tCAH

tASC

tCAH

tASC

tCAH

tASC

tRAH

tASR

tRAD

tAR

COLUMN

COLUMN

COLUMN

ROW

ROW

tCP

tRSH

tCP

tCP

tCAS, CLCH

tRCD

tCRP

tPC

tCSH

tRASP

tRP

V

V

IH

IL

CASL#/CASH#

V

V

IH

IL

ADDR

V

V

IH

IL

WE#

V

V

IH

IL

DQ

V

V

IOH

IOL

RAS#

OE#

V

V

IH

IL

DON'T CARE

UNDEFINED

tACH

tACH

tACH

t

tCAS, CLCH

t

tCAS, CLCH

t

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

t

PC

20

25

ns

t

RAD

9

12

ns

t

RAH

9

10

ns

t

RASP

50

125,000

60

125,000

ns

t

RCD

11

14

ns

t

RP

30

40

ns

t

RSH

13

15

ns

t

RWL

13

15

ns

t

WCH

8

10

ns

t

WCR

38

45

ns

t

WCS

0

0

ns

t

WP

5

5

ns

17

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

EDO-PAGE-MODE READ-WRITE CYCLE

(LATE WRITE and READ-MODIFY-WRITE cycles)

DON'T CARE

UNDEFINED

t

t

OD

tOE

tOD

tOE

tOD

tOE

OPEN

D OUT

VALID

D IN

VALID

D OUT

VALID

D IN

VALID

D OUT

VALID

D IN

VALID

OPEN

tDH

tDS

tAA

tCPA

tCLZ

tCAC

tDH

tDS

tAA

tCPA

tCLZ

tCAC

tDH

tDS

tAA

tCLZ

tCAC

tRAC

tWP

tCWL

tRWL

tCWD

tAWD

tWP

tCWL

tCWD

tAWD

tWP

tCWL

tCWD

tAWD

tRCS

tRWD

tASR

tRAH

tASC

tRAD

tAR

tCAH

tASC

tCAH

tASC

tCAH

tCP

tRSH

tCP

tRP

tRASP

tCP

tRCD

tCSH

tPC

tCRP

ROW

COLUMN

COLUMN

COLUMN

ROW

V

V

IH

IL

V

V

IH

IL

ADDR

V

V

IH

IL

V

V

IH

IL

DQ

V

V

IOH

IOL

V

V

IH

IL

RAS#

OE#

tPRWC

OEH

tCAS, tCLCH

tCAS, tCLCH

tCAS, tCLCH

WE#

CASL#/CASH#

NOTE 1

NOTE: 1.

t

PC is for LATE WRITE cycles only.

TIMING PARAMETERS

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

t

AA

25

30

ns

t

AR

38

45

ns

t

ASC

0

0

ns

t

ASR

0

0

ns

t

AWD

42

49

ns

t

CAC

13

15

ns

t

CAH

8

10

ns

t

CAS

8

10,000

10

10,000

ns

t

CLCH

5

5

ns

t

CLZ

0

0

ns

t

CP

8

10

ns

t

CPA

28

35

ns

t

CRP

5

5

ns

t

CSH

38

45

ns

t

CWD

28

35

ns

t

CWL

8

10

ns

t

DH

8

10

ns

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

t

DS

0

0

ns

t

OD

0

12

0

15

ns

t

OE

12

15

ns

t

OEH

8

10

ns

t

PC

20

25

ns

t

PRWC

47

56

ns

t

RAC

50

60

ns

t

RAD

9

12

ns

t

RAH

9

10

ns

t

RASP

50

125,000

60

125,000

ns

t

RCD

11

14

ns

t

RCS

0

0

ns

t

RP

30

40

ns

t

RSH

13

15

ns

t

RWD

67

79

ns

t

RWL

13

15

ns

t

WP

5

5

ns

18

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

EDO-PAGE-MODE READ EARLY WRITE CYCLE

(Pseudo READ-MODIFY-WRITE)

V

V

IH

IL

V

V

IH

IL

RAS#

V

V

IH

IL

ADDR

V

V

IH

IL

WE#

tRASP

tRP

ROW

COLUMN (A)

COLUMN (N)

ROW

V

V

IH

IL

OE#

V

V

IOH

IOL

tCRP

tCSH

tCAS, tCLCH

tRCD

tASR

tRAH

tRAD

tASC

tAR

tCAH

tASC

tCAH

tASC

tCAH

tCP

tRSH

VALID D

IN

tRCS

tRCH

tWCS

tOE

VALID

D

OUT

VALID D

OUT

tWHZ

tCAC

tCPA

tAA

tCAC

tAA

OPEN

DQ

tPC

RAC

t

tCOH

tWCH

tDS

tDH

tPC

COLUMN (B)

tACH

CASL#/CASH#

tCAS, tCLCH

tCAS, tCLCH

tCP

tCP

DON'T CARE

UNDEFINED

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

TIMING PARAMETERS

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

t

AA

25

30

ns

t

ACH

12

15

ns

t

AR

38

45

ns

t

ASC

0

0

ns

t

ASR

0

0

ns

t

CAC

13

15

ns

t

CAH

8

10

ns

t

CAS

8

10,000

10

10,000

ns

t

CLCH

5

5

ns

t

COH

3

3

ns

t

CP

8

10

ns

t

CPA

28

35

ns

t

CRP

5

5

ns

t

CSH

38

45

ns

t

DH

8

10

ns

t

DS

0

0

ns

t

OE

12

15

ns

t

PC

20

25

ns

t

RAC

50

60

ns

t

RAD

9

12

ns

t

RAH

9

10

ns

t

RASP

50

125,000

60

125,000

ns

t

RCD

11

14

ns

t

RCH

0

0

ns

t

RCS

0

0

ns

t

RP

30

40

ns

t

RSH

13

15

ns

t

WCH

8

10

ns

t

WCS

0

0

ns

t

WHZ

0

12

0

15

ns

19

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

tCLZ

tCAC

tRAC

tAA

VALID DATA

OPEN

tRCH

tRCS

tASC

tRAH

tRAD

tAR

tCAH

tRCD

tCAS, CLCH

tCSH

tCRP

tASR

ROW

OPEN

RAS#

V

V

IH

IL

V

V

IH

IL

ADDR

V

V

IH

IL

DQ

V

V

OH

OL

V

V

IH

IL

tOD

tOE

OE#

V

V

IH

IL

COLUMN

WE#

tWHZ

tWPZ

tCP

tASC

tRCS

COLUMN

tCLZ

CASL#/CASH#

t

DON'T CARE

UNDEFINED

READ CYCLE

(with WE#-controlled disable)

TIMING PARAMETERS

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

t

AA

25

30

ns

t

AR

38

45

ns

t

ASC

0

0

ns

t

ASR

0

0

ns

t

CAC

13

15

ns

t

CAH

8

10

ns

t

CAS

8

10,000

10

10,000

ns

t

CLCH

5

5

ns

t

CLZ

0

0

ns

t

CP

8

10

ns

t

CRP

5

5

ns

t

CSH

38

45

ns

t

OD

0

12

0

15

ns

t

OE

12

15

ns

t

RAC

50

60

ns

t

RAD

9

12

ns

t

RAH

9

10

ns

t

RCD

11

14

ns

t

RCH

0

0

ns

t

RCS

0

0

ns

t

WHZ

0

12

0

15

ns

t

WPZ

10

10

ns

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

20

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

RAS#-ONLY REFRESH CYCLE

(OE# and WE# = DON'T CARE)

ROW

V

V

IH

IL

V

V

IH

IL

ADDR

V

V

IH

IL

RAS#

tRC

tRAS

tRP

tCRP

tASR

tRAH

ROW

OPEN

Q

V

V

OH

OL

tRPC

CASL#/CASH#

CBR REFRESH CYCLE

(Addresses and OE# = DON'T CARE)

tRP

V

V

IH

IL

RAS#

tRAS

OPEN

tCHR

tCSR

V

V

IH

IL

CASL#/CASH#

DQ

tRP

tRAS

tRPC

tCSR

tRPC

tCHR

tCP

V

V

IH

IL

tWRP

tWRH

tWRP

tWRH

WE#

DON'T CARE

UNDEFINED

V

V

OH

OL

NOTE 1

TIMING PARAMETERS

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

t

ASR

0

0

ns

t

CHR

8

10

ns

t

CP

8

10

ns

t

CRP

5

5

ns

t

CSR

5

5

ns

t

RAH

9

10

ns

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

t

RAS

50

10,000

60

10,000

ns

t

RC

84

104

ns

t

RP

30

40

ns

t

RPC

5

5

ns

t

WRH

8

10

ns

t

WRP

8

10

ns

NOTE: 1. End of first CBR REFRESH cycle.

21

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

t

OE

12

15

ns

t

OFF

0

12

0

15

ns

t

ORD

0

0

ns

t

RAC

50

60

ns

t

RAD

9

12

ns

t

RAH

9

10

ns

t

RAS

50

10,000

60

10,000

ns

t

RCD

11

14

ns

t

RP

30

40

ns

t

RSH

13

15

ns

DON'T CARE

UNDEFINED

tCLZ

tOFF

OPEN

VALID DATA

OPEN

COLUMN

ROW

tCAC

tRAC

tAA

tCAH

tASC

tRAH

tASR

tRAD

tAR

tCRP

tRCD

tRSH

tRAS

tRC

tRP

tCHR

tRAS

DQx

V

V

IOH

IOL

V

V

IH

IL

ADDR

V

V

IH

IL

V

V

IH

IL

RAS#

V

V

IH

IL

tOE

tOD

OE#

tORD

CASL#/CASH#

HIDDEN REFRESH CYCLE

(WE# = HIGH; OE# = LOW)

TIMING PARAMETERS

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

t

AA

25

30

ns

t

AR

38

45

ns

t

ASC

0

0

ns

t

ASR

0

0

ns

t

CAC

13

15

ns

t

CAH

8

10

ns

t

CHR

8

10

ns

t

CLZ

0

0

ns

t

CRP

5

5

ns

t

OD

0

12

0

15

ns

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

22

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

SELF REFRESH CYCLE

(Addresses and OE# = DON'T CARE)

V

V

IH

IL

RAS#

tRASS

OPEN

V

V

IH

IL

V

V

OH

OL

DQ

tRPC

tCHD

tRPS

tRPC

tRP

tCP

CASL#/

CASH#

tWRH

tWRP

WE#

V

V

IH

IL

tWRH

tWRP

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

NOTE 1

tCSR

DON'T CARE

UNDEFINED

tCP

NOTE 2

(

)

(

)

(

)

(

)

TIMING PARAMETERS

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

t

CHD

15

15

ns

t

CLCH

5

5

ns

t

CP

8

10

ns

t

CSR

5

5

ns

t

RASS

100

100

µs

-5

-6

SYMBOL

MIN

MAX

MIN

MAX

UNITS

t

RP

30

40

ns

t

RPC

5

5

ns

t

RPS

90

105

ns

t

WRH

8

10

ns

t

WRP

8

10

ns

NOTE: 1. Once

t

RASS (MIN) is met and RAS# remains LOW, the DRAM will enter self refresh mode.

2. Once

t

RPS is satisfied, a complete burst of all rows should be executed.

23

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

44/50-PIN PLASTIC TSOP (400 mil)

NOTE: 1. All dimensions in inches (millimeters)

MAX or typical where noted.

MIN

2. Package width and length do not include mold protrusion; allowable mold protrusion is .01" per side.

SEE DETAIL A

.024 (0.60)

.016 (0.40)

.008 (0.20)

.002 (0.05)

DETAIL A

.010 (0.25)

.032 (0.80)

TYP

.007 (0.18)

.005 (0.13)

.047 (1.20)

MAX

.004 (0.10)

.031 (0.80)

TYP

1

50

25

.018 (0.45)

.012 (0.30)

.828 (21.04)

.822 (20.88)

.467 (11.86)

.459 (11.66)

.402 (10.21)

.398 (10.11)

PIN #1 INDEX

SEATING PLANE

.029 (0.75) TYP

24

1 Meg x 16 EDO DRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

D52_B.p65 ≠ Rev. B; Pub. 3/01

©2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

42-PIN PLASTIC SOJ (400 mil)

.148 (3.76)

.138 (3.51)

1.000 (25.40)

1.079 (27.41)

1.073 (27.25)

SEATING PLANE

.380 (9.65)

.360 (9.14)

.030 (0.76)

MIN

PIN #1 INDEX

.050 (1.27) TYP

.445 (11.30)

.435 (11.05)

.405 (10.29)

.399 (10.13)

.095 (2.40)

.080 (2.02)

.020 (0.51)

.015 (0.38)

.037 (0.94) MAX

DAMBAR PROTRUSION

.026 (0.66)

.032 (0.81)

NOTE: 1. All dimensions in inches (millimeters)

MAX or typical where noted.

MIN

2. Package width and length do not include mold protrusion; allowable mold protrusion is .01" per side.

8000 S. Federal Way, P.O. Box 6, Boise, ID 83707-0006, Tel: 208-368-3900

E-mail: prodmktg@micron.com, Internet: http://www.micron.com, Customer Comment Line: 800-932-4992

Micron is a registered trademark and the Micron logo and the M logos are trademarks of Micron Technology, Inc.