32, 64, 128MB x 64 SDRAM DIMM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

SD5C4_8_16X72AG_B.fm - Rev. B 9/02

1

©2002, Micron Technology Inc.

32MB / 64MB / 128MB (x72)

168-PIN SDRAM DIMMs

SYNCHRONOUS DRAM

MODULE

MT5LSDT472A -32MB

MT5LSDT872A(I) - 64MB

MT5LSDT1672A(I) - 128MB

For the latest data sheet, please refer to the Micron Web

site:

www.micron.com/moduleds

Features

∑ PC100- and PC133-compliant

∑ JEDEC-standard, 168-pin, dual in-line memory

module (DIMM)

∑ Unbuffered

∑ 32MB (4 Meg x 72), 64MB (8 Meg x 72), 128MB (16

Meg x 72)

∑ ECC-Optimized Pinout

∑ Single +3.3V ±0.3V power supply

∑ Fully synchronous; all signals registered on positive

edge of system clock

∑ Internal pipelined operation; column address can

be changed every clock cycle

∑ Internal SDRAM banks for hiding row access/precharge

∑ Programmable burst lengths: 1, 2, 4, 8, or full page

∑ Auto Precharge, including CONCURRENT AUTO

PRECHARGE, and Auto Refresh Modes

∑ Self Refresh Mode

∑ 32/64MB: 64ms, 4,096-cycle refresh; 128MB: 64ms,

8,192-cycle refresh

∑ LVTTL-compatible inputs and outputs

∑ Serial Presence-Detect (SPD)

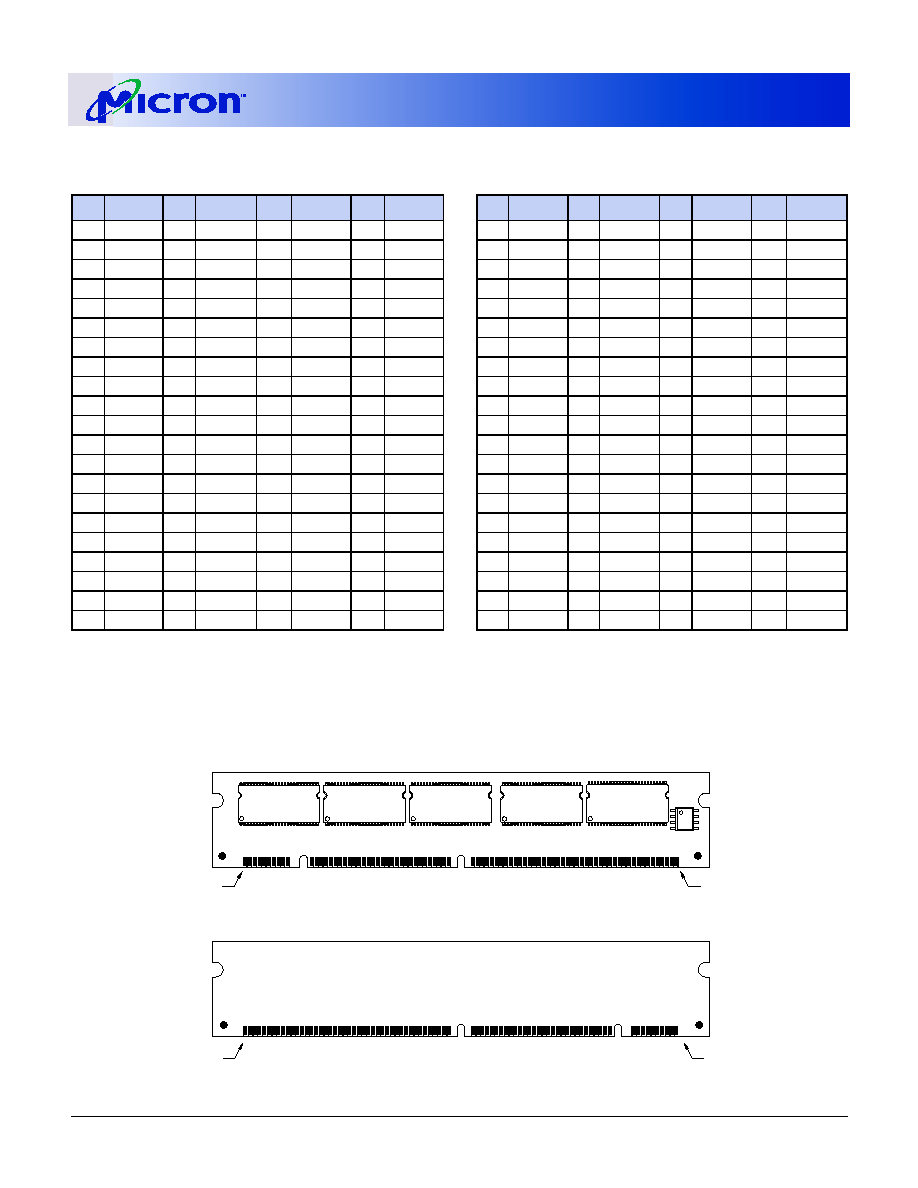

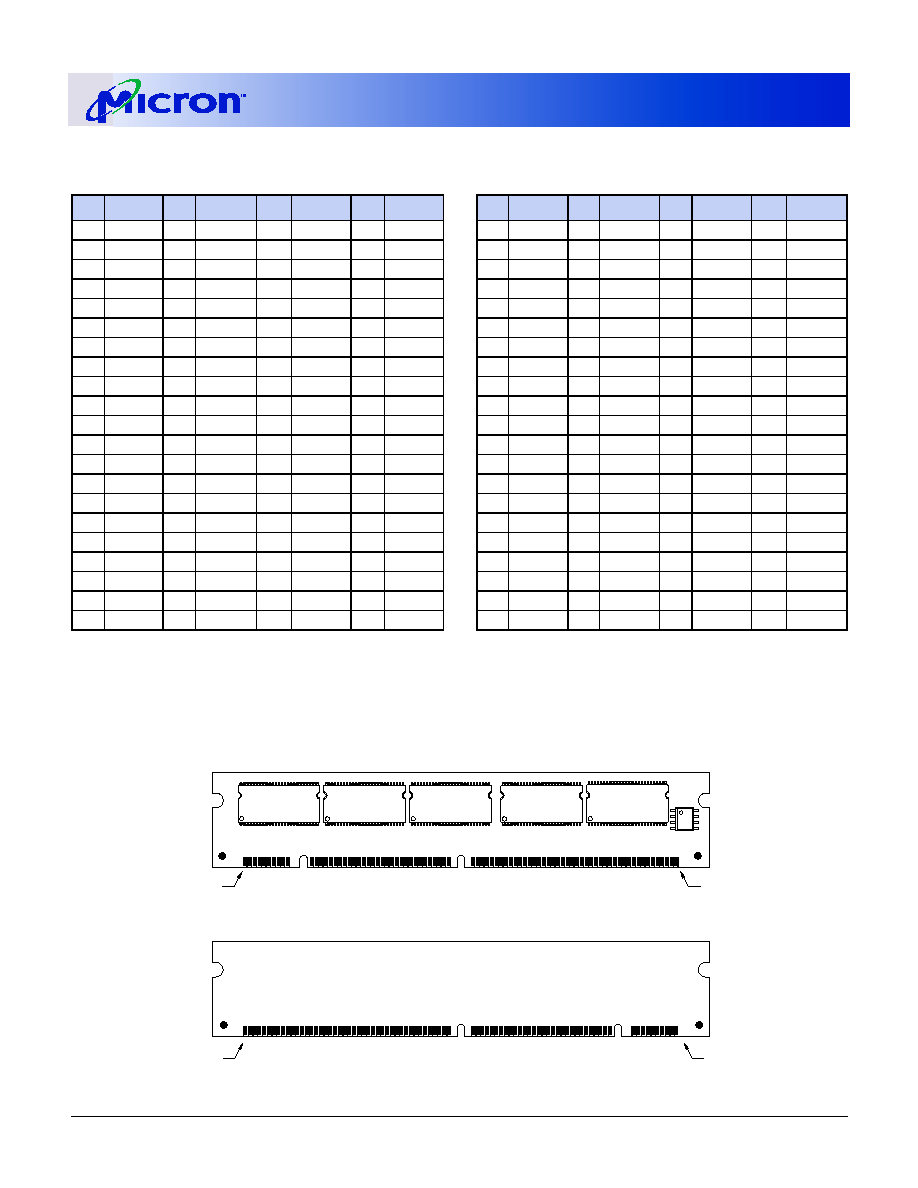

Figure 1: 168-Pin DIMM ≠ MO-161

OPTIONS

MARKING

∑ Package

168-pin DIMM (gold)

G

∑ Operating Temperature Range

Commercial (0∞C to +70∞C)

None

Industrial (-40∞C to +85∞C)

1

NOTE:

1. Consult Micron for availability; Industrial Temperature

option available in -133 speed only.

I

∑ Frequency / CAS Latency

7.5ns (133 MHz) / CL = 2

-13E

7.5ns (133 MHz) / CL = 3

-133

8ns (100 MHz) / CL = 2

-10E

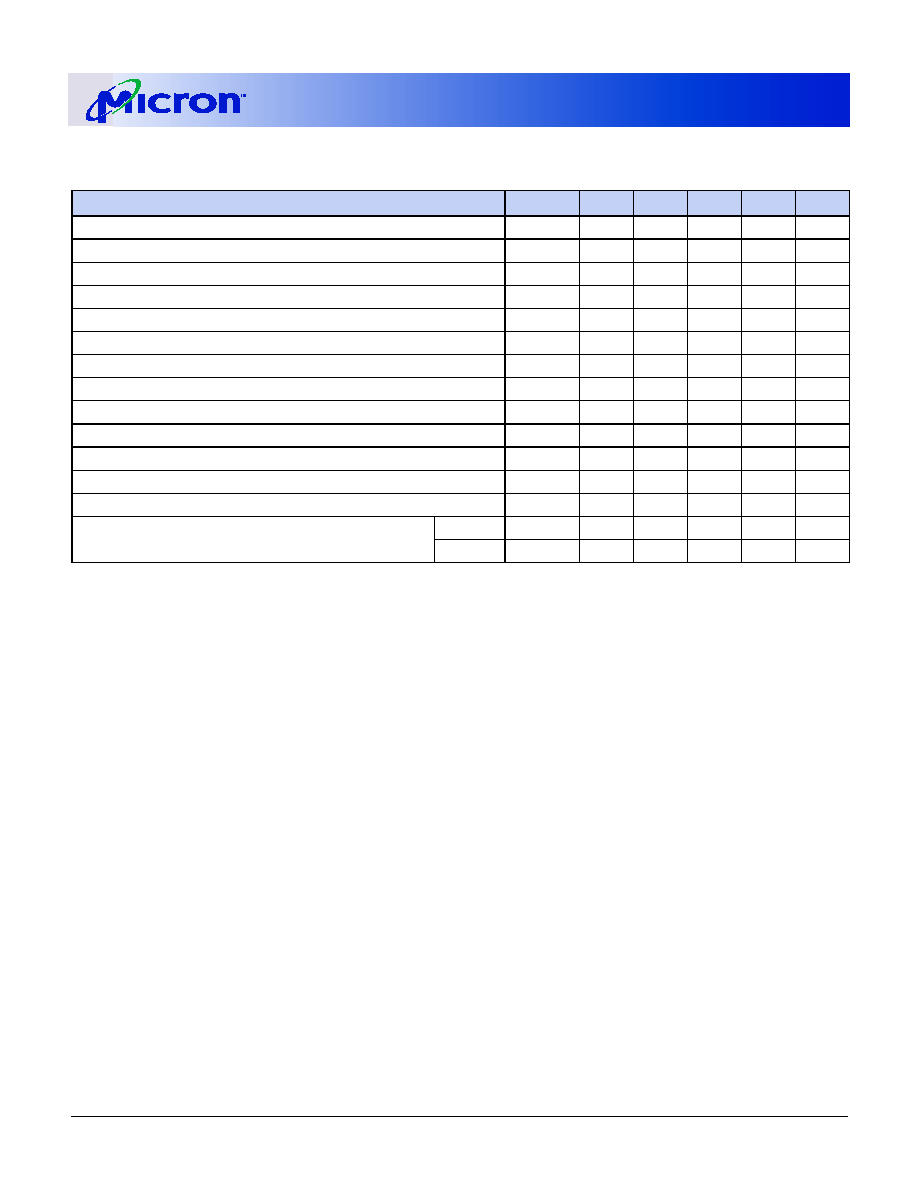

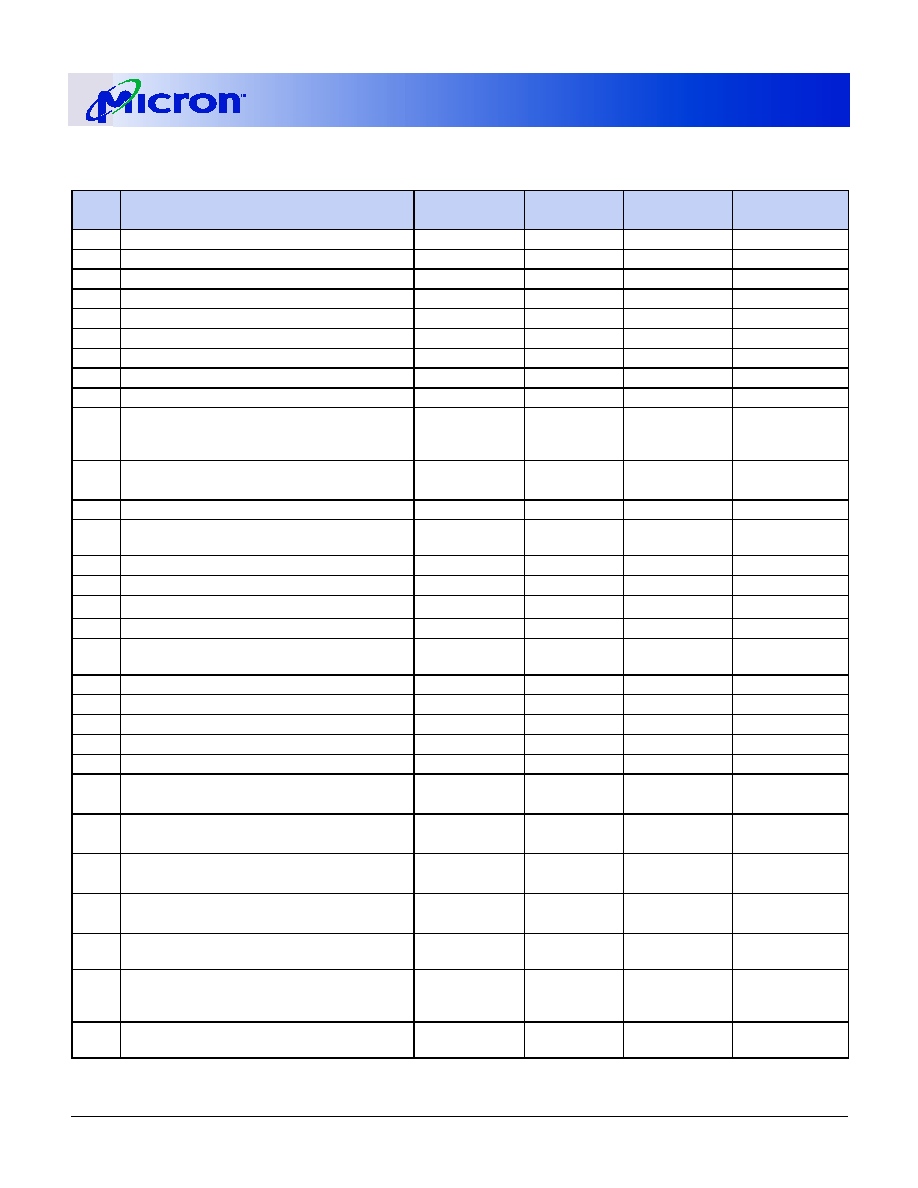

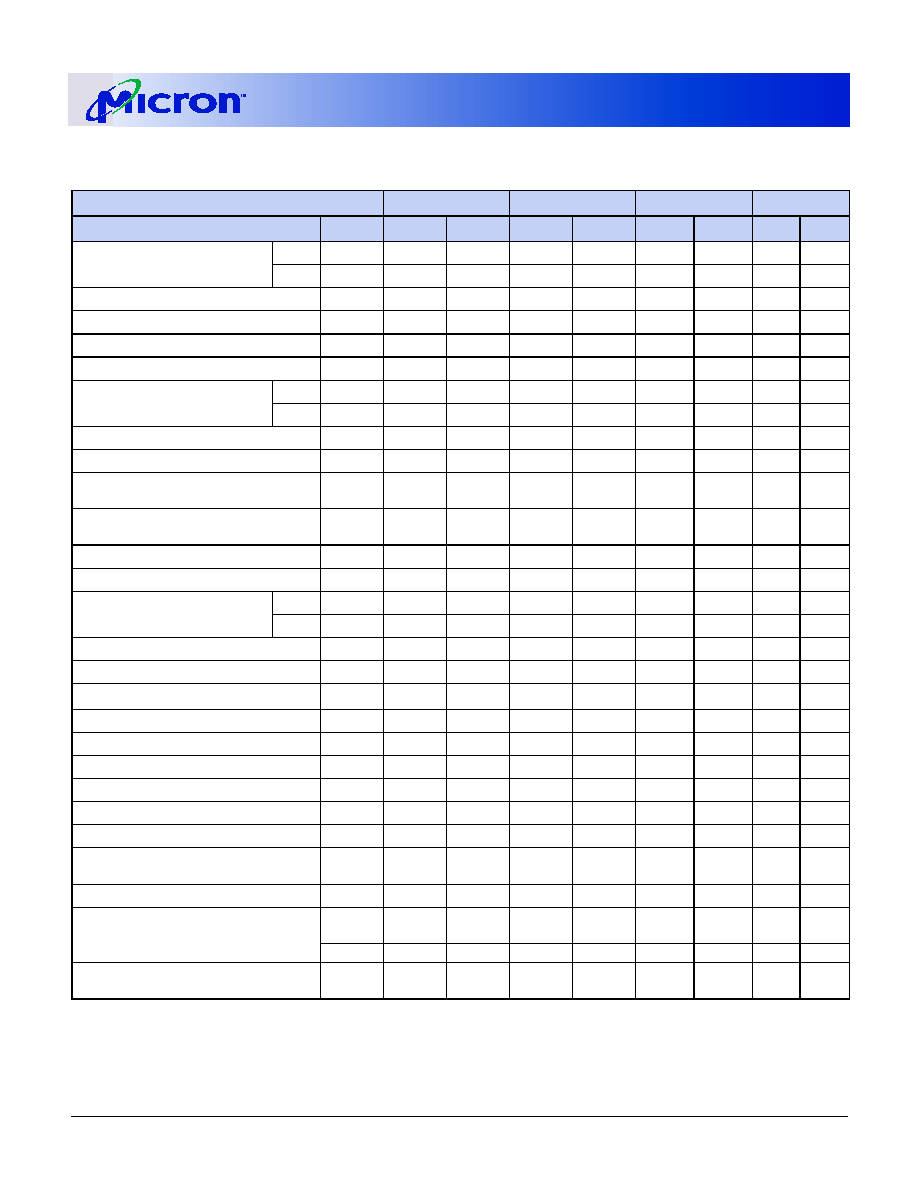

Table 1:

Address Table

32MB

MODULE

64MB

MODULE

128MB

MODULE

Refresh Count

4K

4K

8K

Device Banks

4 (BA0, BA1)

4 (BA0, BA1)

4 (BA0, BA1)

Device Conf.

4 Meg x 16

8 Meg x 16 16 Meg x 16

Row Addressing 4K (A0-A11) 4K (A0-A11) 8K (A0-A12)

Column Addr.

256 (A0-A7) 512 (A0-A8) 512 (A0-A8)

Module Banks

1 (S0, S2)

1 (S0, S2)

1 (S0, S2)

Table 2:

Timing Parameters

MODULE

MARKING

PC100

(CL -

t

RCD -

t

RP)

PC133

(CL -

t

RCD -

t

RP)

-13E

2 - 2 - 2

2 - 2 - 2

-133

2 - 2 - 2

3 - 3 - 3

-10E

2 - 2 - 2

n/a

Table 3:

Part Numbers

PART NUMBER

CONFIGURATION

SYSTEM

BUS SPEED

MT5LSDT472AG-13E_

4 Meg x 72

133 MHz

MT5LSDT472AG-133_

4 Meg x 72

133 MHz

MT5LSDT472AG-10E_

4 Meg x 72

100 MHz

MT5LSDT872AG-13E_

8 Meg x 72

133 MHz

MT5LSDT872A(I)G-133_

8Meg x 72

133 MHz

MT5LSDT872AG-10E_

8 Meg x 72

100 MHz

MT5LSDT1672AG-13E_

16 Meg x 72

133 MHz

MT5LSDT1672A(I)G-133_

16 Meg x 72

133 MHz

MT5LSDT1672AG-10E_

16 Meg x 72

100 MHz

NOTE:

The designators for component and PCB revision are the last

two characters of each part number. Consult factory for cur-

rent revision codes. Example: MT5LSDT1672AG-133B1.

32MB / 64MB / 128MB (x72)

168-PIN SDRAM DIMMs

32, 64, 128MB x 64 SDRAM DIMM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

SD5C4_8_16X72AG_B.fm - Rev. B 9/02

2

©2002, Micron Technology Inc.

NOTE:

Pin 126 is NC for 32MB and 64MB modules, or A12 for the 128MB module.

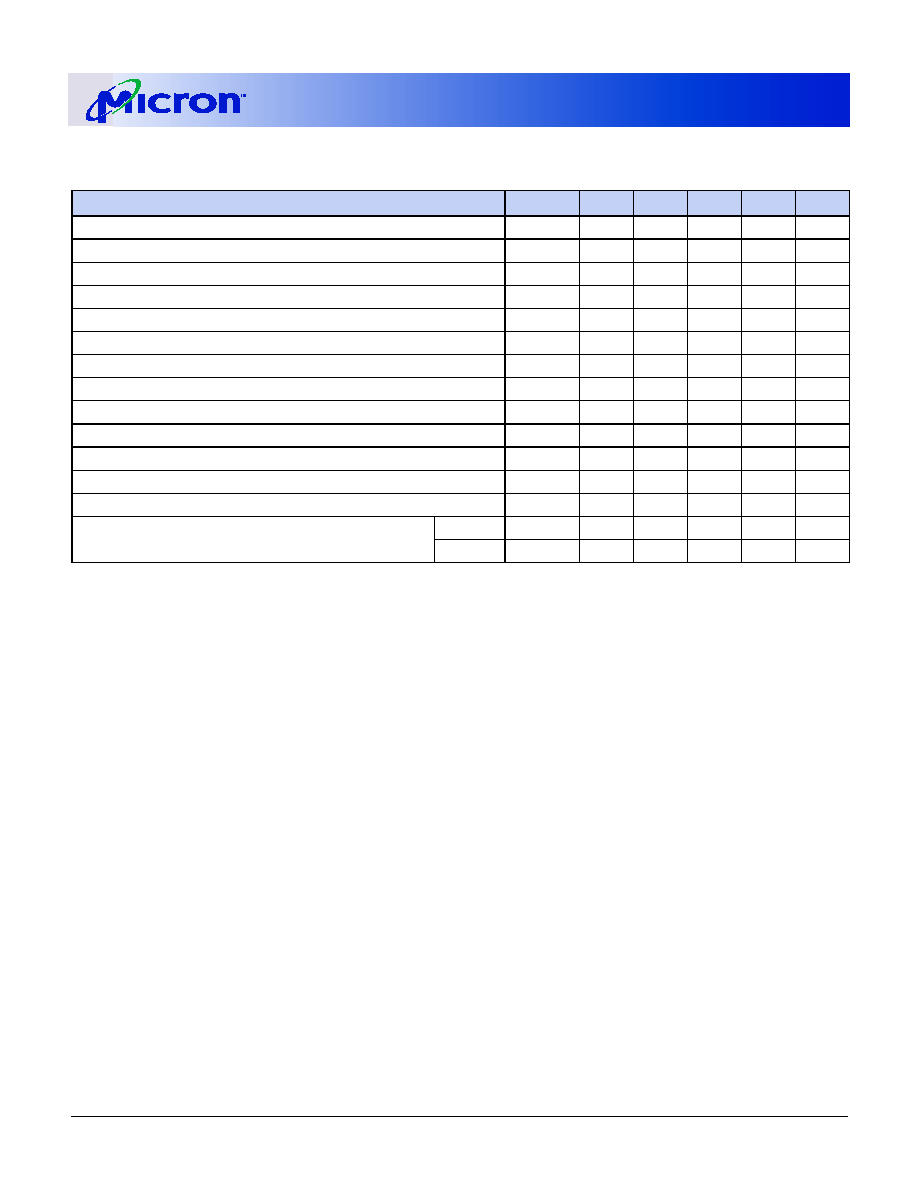

Figure 2: Pin Locations (168-Pin DIMM)

Table 4:

Pin Assignment

(168-Pin DIMM Front)

PIN SYMBOL PIN

SYMBOL

PIN

SYMBOL

PIN

SYMBOL

1

V

SS

22

CB1

43

V

SS

64

V

SS

2

DQ0

23

V

SS

44

NC

65

DQ21

3

DQ1

24

NC

45

S2#

66

DQ22

4

DQ2

25

NC

46

DQM2

67

DQ23

5

DQ3

26

V

DD

47

DQM3

68

V

SS

6

V

DD

27

WE#

48

NC

69

DQ24

7

DQ4

28

DQM0

49

V

DD

70

DQ25

8

DQ5

29

DQM1

50

NC

71

DQ26

9

DQ6

30

S0#

51

NC

72

DQ27

10

DQ7

31

NC

52

CB2

73

V

DD

11

DQ8

32

V

SS

53

CB3

74

DQ28

12

V

SS

33

A0

54

V

SS

75

DQ29

13

DQ9

34

A2

55

DQ16

76

DQ30

14

DQ10

35

A4

56

DQ17

77

DQ31

15

DQ11

36

A6

57

DQ18

78

V

SS

16

DQ12

37

A8

58

DQ19

79

CK2

17

DQ13

38

A10

59

V

DD

80

NC

18

V

DD

39

BA1

60

DQ20

81

WP

19

DQ14

40

V

DD

61

NC

82

SDA

20

DQ15

41

V

DD

62

NC

83

SCL

21

CB0

42

CKO

63

CKE1

84

V

DD

Table 5:

Pin Assignment

(168-Pin DIMM Back)

PIN SYMBOL PIN SYMBOL PIN SYMBOL PIN

SYMBOL

85

V

SS

106

CB5

127

V

SS

148

V

SS

86

DQ32

107

V

SS

128

CKE0

149

DQ53

87

DQ33

108

NC

129

DNU

150

DQ54

88

DQ34

109

NC

130

DQM6

151

DQ55

89

DQ35

110

V

DD

131

DQM7

152

V

SS

90

V

DD

111

CAS#

132

DNU

153

DQ56

91

DQ36

112

DQM4

133

V

DD

154

DQ57

92

DQ37

113

DQM5

134

NC

155

DQ58

93

DQ38

114

DNU

135

NC

156

DQ59

94

DQ39

115

RAS#

136

CB6

157

V

DD

95

DQ40

116

V

SS

137

CB7

158

DQ60

96

V

SS

117

A1

138

V

SS

159

DQ61

97

DQ41

118

A3

139

DQ48

160

DQ62

98

DQ42

119

A5

140

DQ49

161

DQ63

99

DQ43

120

A7

141

DQ50

162

V

SS

100

DQ44

121

A9

142

DQ51

163

DNU

101

DQ45

122

BA0

143

V

DD

164

NC

102

V

DD

123

A11

144

DQ52

165

SA0

103

DQ46

124

V

DD

145

NC

166

SA1

104

DQ47

125

DNU

146

NC

167

SA2

105

CB4

126 NC/A12*

147

NC

168

V

DD

U1

U2

U4

U5

Back View

PIN 1

PIN 84

PIN 85

PIN 168

U3

No Components on This Side of Module

Front View

U6

32MB / 64MB / 128MB (x72)

168-PIN SDRAM DIMMs

32, 64, 128MB x 64 SDRAM DIMM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

SD5C4_8_16X72AG_B.fm - Rev. B 9/02

3

©2002, Micron Technology Inc.

Table 6:

PIN Descriptions

Pins are listed in module pinout order and do not necessarily correlate with symbols.

PIN NUMBERS

SYMBOL

TYPE

DESCRIPTION

27, 111, 115

RAS#, CAS#,

WE#,

Input

Command Inputs: RAS#, CAS#, and WE# (along with S0#, S2#)

define the command being entered.

42, 79

CK0, CK2

Input

Clock: CK is driven by the system clock. All SDRAM input

signals are sampled on the positive edge of CK. CK also

increments the internal burst counter and controls the output

registers.

128

CKE0

Input

Clock Enable: CKE activates (HIGH) and deactivates (LOW) the

CK signal. Deactivating the clock provides PRECHARGE

POWER-DOWN and SELF REFRESH operation (all device banks

idle) or CLOCK SUSPEND OPERATION (burst access in

progress). CKE is synchronous except after the device enters

power-down and self refresh modes, where CKE becomes

asynchronous until after exiting the same mode. The input

buffers, including CK, are disabled during power-down and

self refresh modes, providing low standby power.

30, 45

S0#, S2#

Input

Chip Select: S# enables (registered LOW) and disables

(registered HIGH) the command decoder. All commands are

masked when S# is registered HIGH. S# is considered part of

the command code.

28, 29, 46, 47, 112, 113,

130, 131

DQM0-DQM7

Input

Input/Output Mask: DQMB is an input mask signal for write

accesses and an output enable signal for read accesses. Input

data is masked when DQMB is sampled HIGH during a WRITE

cycle. The output buffers are placed in a High-Z state (two-

clock latency) when DQMB is sampled HIGH during a READ

cycle.

39, 122

BA0, BA1

Input

Bank Address: BA0 and BA1 define to which device bank the

ACTIVE, READ, WRITE, or PRECHARGE command is being

applied.

33-38, 117-121, 123,

126

(128MB)*

A0-A11

(32MB/64MB)

A0-A12

(128MB)

Input

Address Inputs: Provide the row address for ACTIVE

commands, and the column address and auto prcharge bit

(A10) for READ/WRITE commands, to select one location out

of the memory arrary in the respective device bank. A10

sampled during a PRECHARGE command determines whether

the PRECHARGE applies to one device bank (A10 LOW ≠

device bank selected by BA0, BA1) or all device banks (A10

HIGH). The address inputs also provide the op-code during a

MODE REGISTER SET command.

81

WP

Input

Write Protect: Serial presence-detect hardware write protect.

83

SCL

Input

Serial Clock for Presence-Detect: SCL is used to synchronize

the presence-detect data transfer to and from the module.

165-167

SA0-SA2

Input

Presence-Detect Address Inputs: These pins are used to

configure the presence-detect device.

82

SDA

Input/Output

Serial Presence-Detect Data: SDA is a bidirectional pin used to

transfer addresses and data into and out of the presence-

detect portion of the module.

2-5, 7-11, 13-17, 19-20,

55-58, 60, 65-67, 69-72,

74-77, 86-89, 91-95, 97-

101, 103-104, 139-142,

144, 149-151, 153-156,

158-161*

DQ0-DQ63

Input/Output

Data I/Os: Data bus.

32MB / 64MB / 128MB (x72)

168-PIN SDRAM DIMMs

32, 64, 128MB x 64 SDRAM DIMM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

SD5C4_8_16X72AG_B.fm - Rev. B 9/02

4

©2002, Micron Technology Inc.

21, 22, 52, 53, 105, 106,

136, 137

CB0-CB7

Input/Output

ECC check bits.

6, 18, 26, 40, 41, 49, 59,

73, 84, 90, 102, 110, 124,

133, 143, 157, 168

V

DD

Supply

Power Supply: +3.3V ±0.3V.

1, 12, 23, 32, 43, 54, 64,

68, 78, 85, 96, 107, 116,

127, 138, 148, 152, 162

V

SS

Supply

Ground.

114, 125, 129, 132, 163

DNU

≠

Do Not Use: These pins are not used on these modules, but

are assigned pins on other modules in this product family.

24, 25, 31, 44, 48, 50, 51,

61, 62, 80, 108, 109, 126

(32MB/64MB), 134, 135,

145-147, 164

NC

≠

Not Connected: These pins are not connected on these

modules.

Table 6:

PIN Descriptions

Pins are listed in module pinout order and do not necessarily correlate with symbols.

PIN NUMBERS

SYMBOL

TYPE

DESCRIPTION

32MB / 64MB / 128MB (x72)

168-PIN SDRAM DIMMs

32, 64, 128MB x 64 SDRAM DIMM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

SD5C4_8_16X72AG_B.fm - Rev. B 9/02

5

©2002, Micron Technology Inc.

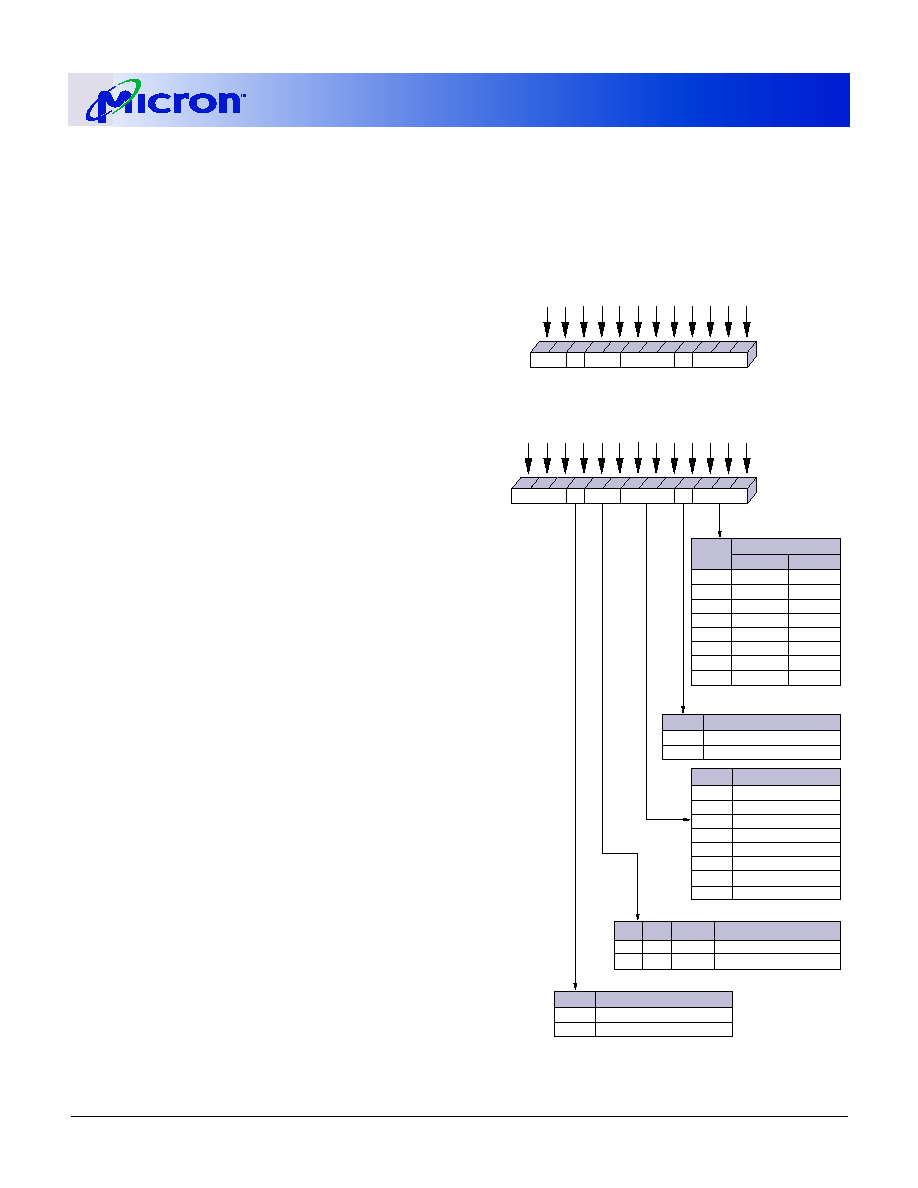

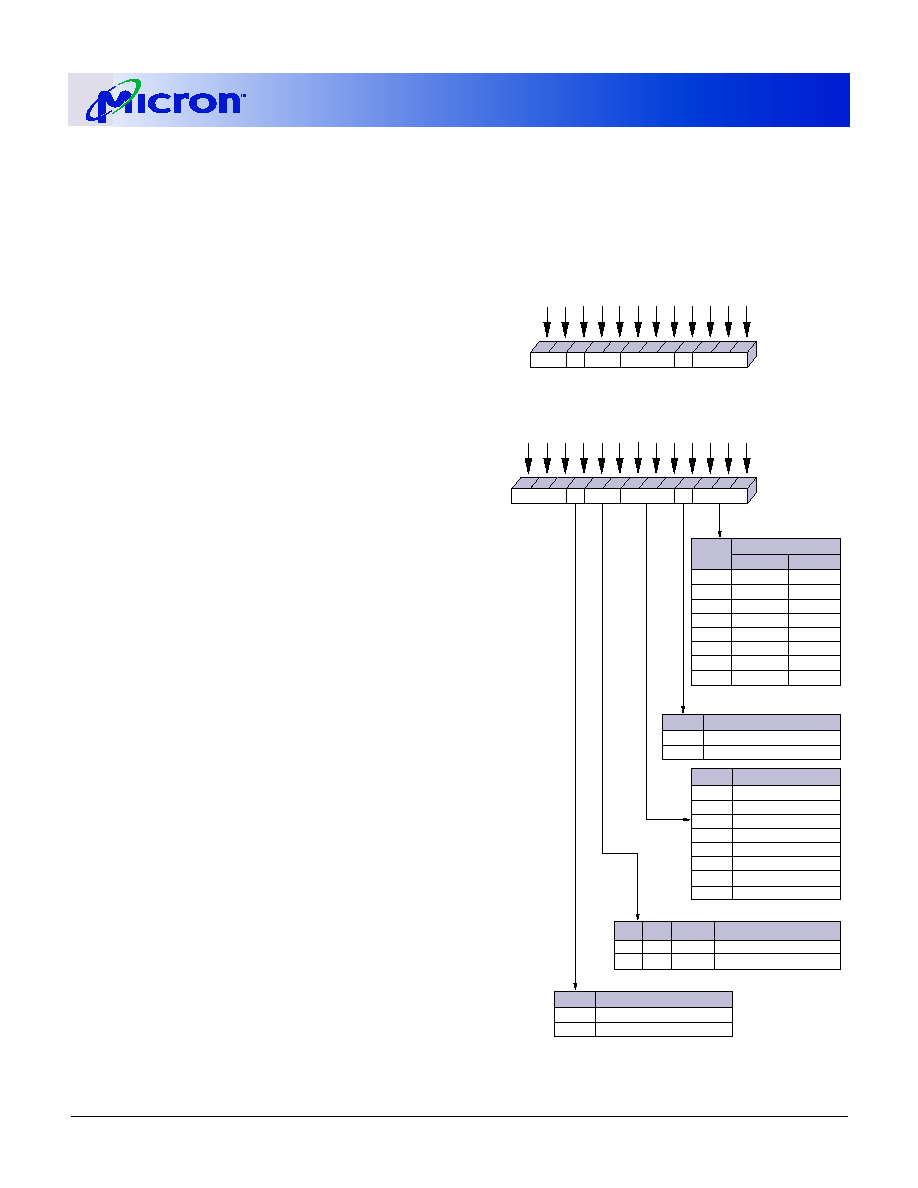

Figure 3: Functional Block Diagram

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQMH

U1

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQM4

S2#

RAS#

CAS#

CKE0

WE#

RAS#: SDRAMs

CAS#: SDRAMs

CKE: SDRAMs

WE#: SDRAMs

A0-A11: SDRAMs

A0-A12: SDRAMs

BA0-1: SDRAMs

A0-A11(32MB/64MB)

A0-A12(128MB)

BA0-1

V

DD

V

SS

SDRAMs U1-U5

SDRAMs U1-U5

DQML CS#

DQM0

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQMH

U2

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQM5

DQM1

DQML CS#

DQM1

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQMH

U4

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQM6

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQML CS#

DQM2

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DQMH

U5

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQM7

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQML CS#

DQM3

S0#

10pF

CK1, CK3

CK0

6.6pF

A0

SA0

SPD

U6

SDA

A1

SA1

A2

SA2

WP

SCL

U1

U2

U3

CK2

13.6pF

U4

U5

DQMH

U3

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

DQML CS#

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

Note:

1. All resistor values are 10

W unless otherwise specified.

2. Per industry standard, Micron modules use various component speed grades as referenced in the module part numbering guide at

www.micron.com/numberguide

.

U1-U5 = MT48LC4M16A2TG SDRAMs for 32MB Comm. Temp.

U1-U5 = MT48LC8M16A2TG SDRAMs for 64MB Comm. Temp.

U1-U5 = MT48LC16M16A2TG SDRAMs for 128MB Comm. Temp.

U1-U5 = MT48LC8M16A2TG-75 IT SDRAMs for 64MB Ind. Temp.

U1-U5 = MT48LC16M16A2TG-75 IT SDRAMs for 128MB Ind. Temp.

32MB / 64MB / 128MB (x72)

168-PIN SDRAM DIMMs

32, 64, 128MB x 64 SDRAM DIMM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

SD5C4_8_16X72AG_B.fm - Rev. B 9/02

6

©2002, Micron Technology Inc.

General Description

The Micron

Æ

MT5LSDT472A, MT5LSDT872A(I), and

MT5LSDT1672A(I) are a high-speed CMOS, dynamic

random-access, 32MB, 64MB, and 128MB memory

modules organized in a x72, ECC configuration. ECC

functions to detect and correct one-bit memory errors.

These module use SDRAM devices which are internally

configured as quad-bank DRAMs with a synchronous

interface (all signals are registered on the positive edge

of the clock signals CK0, CK2). The four banks of the

x16 configured devices used for these modules are

configured as 4,096 bit-rows by 256 bit-columns, by 16

input/output bits for the 32MB module; 4,096 bit-rows

by 512 bit-columns, by 16 input/output bits for the

64MB; module and 8,192 bit-rows by 512 bit-columns,

by 16 input/output bits for the 128MB module.

Read and write accesses to the SDRAM module are

burst oriented; accesses start at a selected location and

continue for a programmed number of locations in a

programmed sequence. Accesses begin with the regis-

tration of an ACTIVE command, which is then fol-

lowed by a READ or WRITE command. The address

bits registered coincident with the ACTIVE command

are used to select the device bank and row to be

accessed (BA0, BA1 select the device bank, A0-A11 for

32MB/64MB; A0-A12 for 128MB select the device row).

The address bits registered coincident with the READ

or WRITE command(A0-A7 32MB; A0-A8 64/128MB)

are used to select the starting device column location

for the burst access.

These modules provide for programmable READ or

WRITE burst lengths of 1, 2, 4, or 8 locations, or the full

page, with a burst terminate option. An auto precharge

function may be enabled to provide a self-timed row

precharge that is initiated at the end of the burst

sequence. These modules use an internal pipelined

architecture to achieve high-speed operation. This

architecture is compatible with the 2n rule of prefetch

architectures, but it also allows the column address to

be changed on every clock cycle to achieve a high-

speed, fully random access. Precharging one device

bank while accessing one of the other three device

banks will hide the PRECHARGE cycles and provide

seamless, high-speed, random access operation.

These modules are designed to operate in 3.3V, low-

power memory systems. An auto refresh mode is pro-

vided, along with a power-saving, power-down mode.

All inputs, outputs, and clocks are LVTTL-compatible.

SDRAM modules offer substantial advances in

DRAM operating performance, including the ability to

synchronously burst data at a high data rate with auto-

matic column-address generation, the ability to inter-

leave between internal banks in order to hide

precharge time, and the capability to randomly change

column addresses on each clock cycle during a burst

access. For more information regarding SDRAM opera-

tion, refer to the 64Mb, 128Mb, or 256Mb SDRAM

component data sheets.

Serial Presence-Detect Operation

These modules incorporate serial presence-detect

(SPD). The SPD function is implemented using a

2,048-bit EEPROM. This nonvolatile storage device

contains 256 bytes. The first 128 bytes can be pro-

grammed by Micron to identify the module type and

various SDRAM organizations and timing parameters.

The remaining 128 bytes of storage are available for

use by the customer. System READ/WRITE operations

between the master (system logic) and the slave

EEPROM device (DIMM) occur via a standard IIC bus

using the DIMM's SCL (clock) and SDA (data) signals.

Initialization

SDRAMs must be powered up and initialized in a

predefined manner. Operational procedures other

than those specified may result in undefined opera-

tion. Once power is applied to V

DD

and V

DD

Q (simulta-

neously) and the clock is stable (stable clock is defined

as a signal cycling within timing constraints specified

for the clock pin), the SDRAM requires a 100µs delay

prior to issuing any command other than a COM-

MAND INHIBIT or NOP. Starting at some point during

this 100µs period and continuing at least through the

end of this period, COMMAND INHIBIT or NOP com-

mands should be applied.

Once the 100µs delay has been satisfied with at least

one COMMAND INHIBIT or NOP command having

been applied, a PRECHARGE command should be

applied. All device banks must then be precharged,

thereby placing the device in the all banks idle state.

Once in the idle state, two AUTO REFRESH cycles

must be performed. After the AUTO REFRESH cycles

are complete, the SDRAM is ready for mode register

programming. Because the mode register will power

up in an unknown state, it should be loaded prior to

applying any operational command.

Mode Register Definition

The mode register is used to define the specific

mode of operation of the SDRAM. This definition

includes the selection of a burst length, a burst type, a

CAS latency, an operating mode, and a write burst

mode, as shown in the Mode Register Definition Dia-

gram. The mode register is programmed via the LOAD

32MB / 64MB / 128MB (x72)

168-PIN SDRAM DIMMs

32, 64, 128MB x 64 SDRAM DIMM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

SD5C4_8_16X72AG_B.fm - Rev. B 9/02

7

©2002, Micron Technology Inc.

MODE REGISTER command and will retain the stored

information until it is programmed again or the device

loses power.

Mode register bits M0≠M2 specify the burst length,

M3 specifies the type of burst (sequential or inter-

leaved), M4≠M6 specify the CAS latency, M7 and M8

specify the operating mode, M9 specifies the write

burst mode, and M10 and M11 are reserved for future

use. For the 128MB module, Address A12 (M12) is

undefined but should be driven LOW during loading of

the mode register.

The mode register must be loaded when all device

banks are idle, and the controller must wait the speci-

fied time before initiating the subsequent operation.

Violating either of these requirements will result in

unspecified operation.

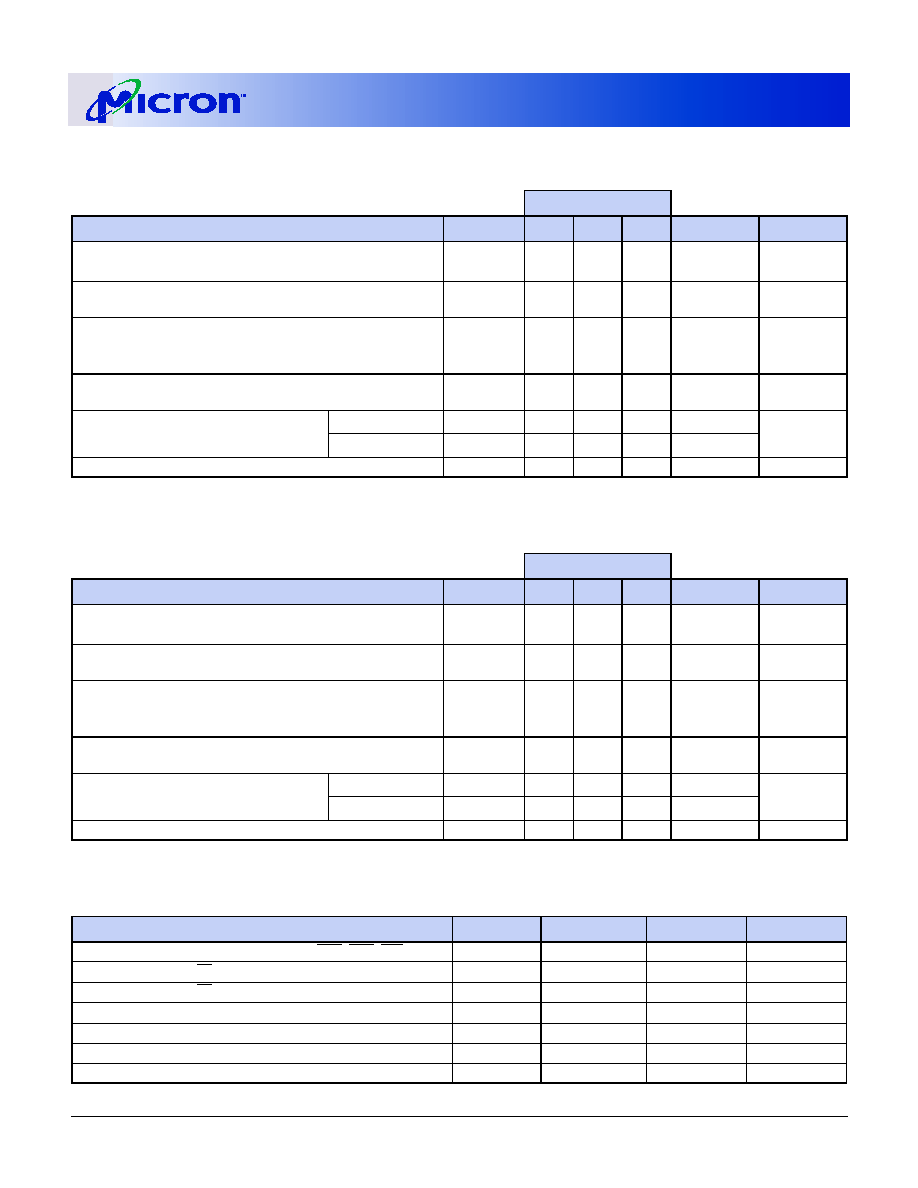

Burst Length

Read and write accesses to the SDRAM are burst ori-

ented, with the burst length being programmable, as

shown in Figure 4, Mode Register Definition Diagram.

The burst length determines the maximum number of

column locations that can be accessed for a given

READ or WRITE command. Burst lengths of 1, 2, 4, or 8

locations are available for both the sequential and the

interleaved burst types, and a full-page burst is avail-

able for the sequential type. The full-page burst is used

in conjunction with the BURST TERMINATE com-

mand to generate arbitrary burst lengths.

Reserved states should not be used, as unknown

operation or incompatibility with future versions may

result.

When a READ or WRITE command is issued, a block

of columns equal to the burst length is effectively

selected. All accesses for that burst take place within

this block, meaning that the burst will wrap within the

block if a boundary is reached, as shown in the Burst

Definition Table. The block is uniquely selected by A1≠

A7 (32MB) or A1-A8 (64MB/128MB) when the burst

length is set to two; by A2≠A7 or A2-A8 when the burst

length is set to four; and by A3≠A7 or A3-A8 when the

burst length is set to eight. The remaining (least signif-

icant) address bit(s) is (are) used to select the starting

location within the block. Full-page bursts wrap within

the page if the boundary is reached, as shown in

Table 7, Burst Definition Table, on page 8.

Burst Type

Accesses within a given burst may be programmed

to be either sequential or interleaved; this is referred to

as the burst type and is selected via bit M3.

The ordering of accesses within a burst is deter-

mined by the burst length, the burst type and the start-

ing column address, as shown in Table 7, Burst

Definition Table, on page 8.

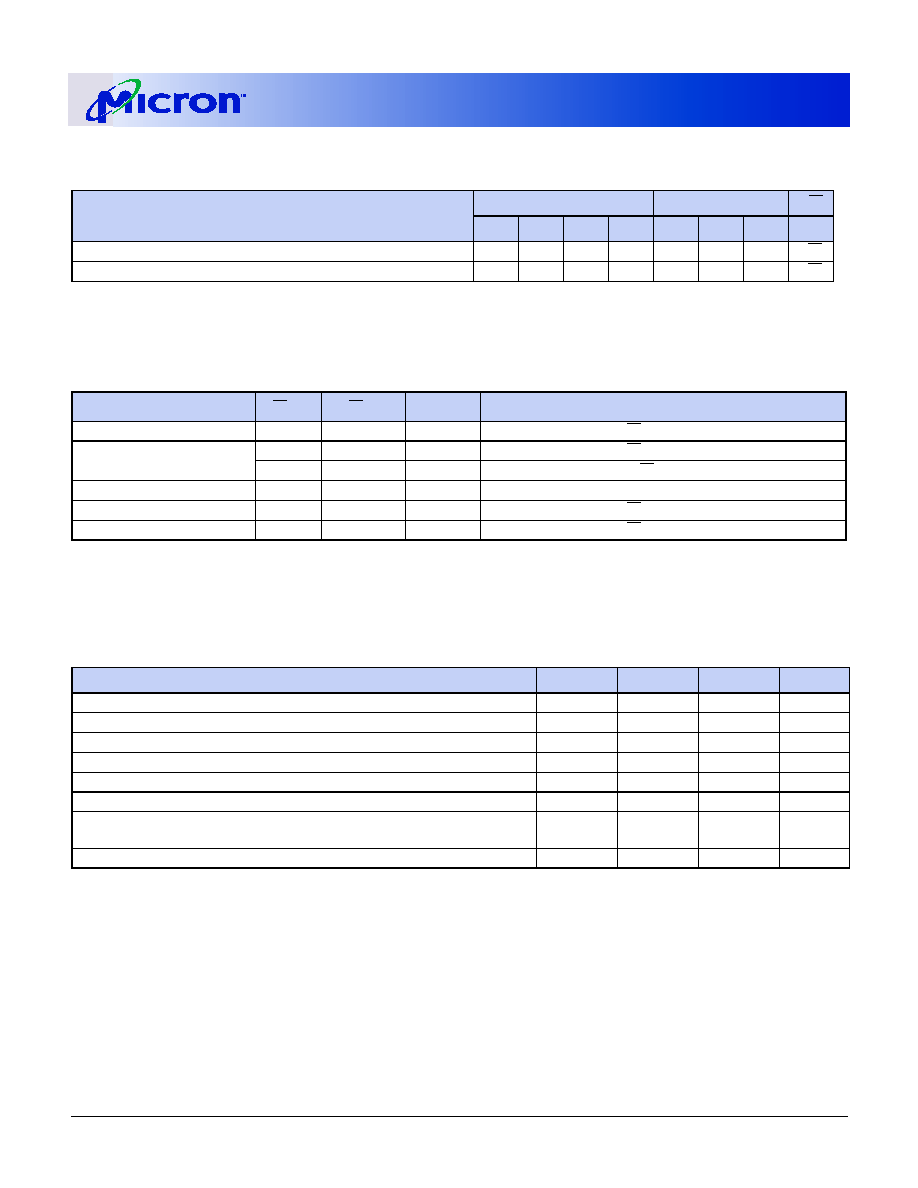

Figure 4: Mode Register Definition

Diagram

M3 = 0

1

2

4

8

Reserved

Reserved

Reserved

Full Page

M3 = 1

1

2

4

8

Reserved

Reserved

Reserved

Reserved

Operating Mode

Standard Operation

All other states reserved

0

-

0

-

Defined

-

0

1

Burst Type

Sequential

Interleaved

CAS Latency

Reserved

Reserved

2

3

Reserved

Reserved

Reserved

Reserved

Burst Length

128MB Module

32MB Module, 64MB Module

M0

0

1

0

1

0

1

0

1

Burst Length

CAS Latency

BT

A9

A7

A6

A5

A4

A3

A8

A2

A1

A0

Mode Register (Mx)

Address Bus

9

7

6

5

4

3

8

2

1

0

M1

0

0

1

1

0

0

1

1

M2

0

0

0

0

1

1

1

1

M3

M4

0

1

0

1

0

1

0

1

M5

0

0

1

1

0

0

1

1

M6

0

0

0

0

1

1

1

1

M6-M0

M8

M7

Op Mode

A10

A11

10

11

Reserved*

WB

0

1

Write Burst Mode

Programmed Burst Length

Single Location Access

M9

*Should program

M12, M11, M10 = "0, 0, 0"

to ensure compatibility

with future devices.

*Should program

M11 and M10 = "0, 0, 0"

to ensure compatibility

with future devices.

A12

12

Burst Length

CAS Latency

BT

A9

A7

A6

A5

A4

A3

A8

A2

A1

A0

Mode Register (Mx)

Address Bus

9

7

6

5

4

3

8

2

1

0

Op Mode

A10

A11

10

11

Reserved* WB

32MB / 64MB / 128MB (x72)

168-PIN SDRAM DIMMs

32, 64, 128MB x 64 SDRAM DIMM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

SD5C4_8_16X72AG_B.fm - Rev. B 9/02

8

©2002, Micron Technology Inc.

NOTE:

1. For full-page accesses: y = 256 (32MB); y = 512 (64MB/

128MB).

2. For a burst length of two, A1-Ai select the block-of-two

burst; A0 selects the starting column within the block.

3. For a burst length of four, A2-Ai select the block-of-four

burst; A0-A1 select the starting column within the block.

4. For a burst length of eight, A3-Ai select the block-of-eight

burst; A0-A2 select the starting column within the block.

5. For a full-page burst, the full row is selected and

A0-Ai select the starting column.

6. Whenever a boundary of the block is reached within a

given sequence above, the following access wraps within

the block.

7. For a burst length of one, A0-Ai select the unique column

to be accessed, and mode register bit M3 is ignored.

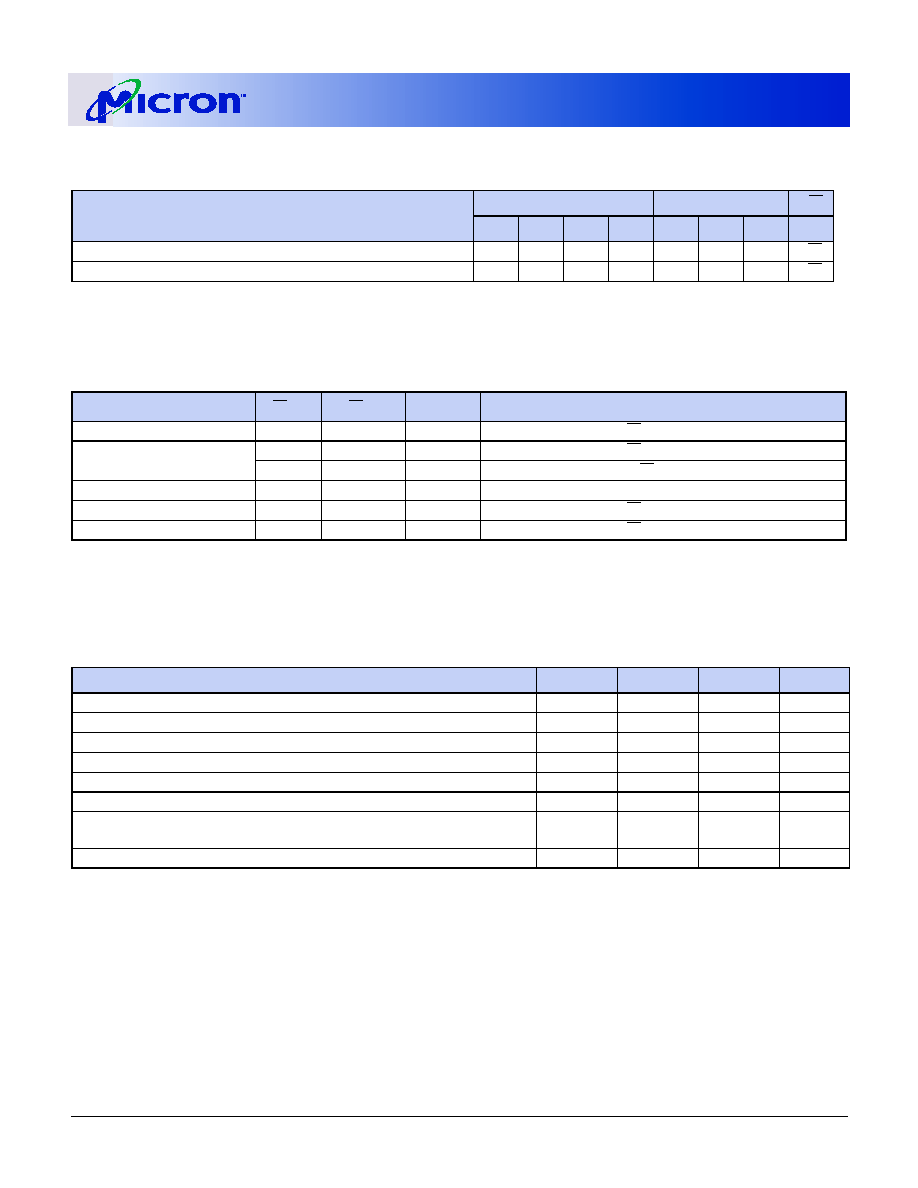

CAS Latency

The CAS latency is the delay, in clock cycles,

between the registration of a READ command and the

availability of the first piece of output data. The latency

can be set to two or three clocks.

If a READ command is registered at clock edge n,

and the latency is m clocks, the data will be available

by clock edge n + m. The DQs will start driving as a

result of the clock edge one cycle earlier (n + m - 1),

and provided that the relevant access times are met,

the data will be valid by clock edge n + m. For example,

assuming that the clock cycle time is such that all rele-

vant access times are met, if a READ command is regis-

tered at T0 and the latency is programmed to two

clocks, the DQs will start driving after T1 and the data

will be valid by T2, as shown in Figure 5, CAS Latency

Diagram. The CAS Latency Table indicates the operat-

ing frequencies at which each CAS latency setting can

be used.

Reserved states should not be used as unknown

operation or incompatibility with future versions may

result.

Figure 5: CAS Latency Diagram

Operating Mode

The normal operating mode is selected by setting

M7 and M8 to zero; the other combinations of values

for M7 and M8 are reserved for future use and/or test

modes. The programmed burst length applies to both

READ and WRITE bursts.

Table 7:

Burst Definition Table

BURST

LENGTH

STARTING

COLUMN

ADDRESS

ORDER OF ACCESSES WTHIN A

BURST

TYPE =

SEQUENTIAL

TYPE =

INTERLEAVED

2

A0

0

0-1

0-1

1

1-0

1-0

4

A1 A0

0

0

0-1-2-3

0-1-2-3

0

1

1-2-3-0

1-0-3-2

1

0

2-3-0-1

2-3-0-1

1

1

3-0-1-2

3-2-1-0

8

A2 A1 A0

0

0

0

0-1-2-3-4-5-6-7

0-1-2-3-4-5-6-7

0

0

1

1-2-3-4-5-6-7-0

1-0-3-2-5-4-7-6

0

1

0

2-3-4-5-6-7-0-1

2-3-0-1-6-7-4-5

0

1

1

3-4-5-6-7-0-1-2

3-4-5-6-7-0-1-2-

1

0

0

4-5-6-7-0-1-2-3

4-5-6-7-0-1-2-3

1

0

1

5-6-7-0-1-2-3-4

5-4-7-6-1-0-3-2

1

1

0

6-7-0-1-2-3-4-5

6-7-4-5-2-3-0-1

1

1

1

7-0-1-2-3-4-5-6

7-6-5-4-3-2-1-0

Full

Page (y)

n = A0-Ai*

(location

0-y)

Cn, Cn + 1,

Cn + 2, Cn + 3,

Cn + 4. . . Cn - 1,

Cn . . .

Not supported

* i = 7 for 32MB module

i = 8 for 64MB and 128MB modules

CLK

DQ

T2

T1

T3

T0

CAS Latency = 3

LZ

D

OUT

tOH

t

COMMAND

NOP

READ

tAC

NOP

T4

NOP

DON'T CARE

UNDEFINED

CLK

DQ

T2

T1

T3

T0

CAS Latency = 2

LZ

D

OUT

tOH

t

COMMAND

NOP

READ

tAC

NOP

32MB / 64MB / 128MB (x72)

168-PIN SDRAM DIMMs

32, 64, 128MB x 64 SDRAM DIMM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

SD5C4_8_16X72AG_B.fm - Rev. B 9/02

9

©2002, Micron Technology Inc.

Test modes and reserved states should not be used

because unknown operation or incompatibility with

future versions may result.

Write Burst Mode

When M9 = 0, the burst length programmed via M0-

M2 applies to both READ and WRITE bursts; when M9

= 1, the programmed burst length applies to READ

bursts, but write accesses are single-location (non-

burst) accesses.

Table 8:

CAS Latency Table

SPEED

ALLOWABLE OPERATING CLOCK

FREQUENCY (MHz)

CAS LATENCY = 2

CAS LATENCY = 3

-13E

£ 133

£ 143

-133

£ 100

£ 133

-10E

£ 100

N/A

32MB / 64MB / 128MB (x72)

168-PIN SDRAM DIMMs

32, 64, 128MB x 64 SDRAM DIMM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

SD5C4_8_16X72AG_B.fm - Rev. B 9/02

10

©2002, Micron Technology Inc.

Commands

This Truth Table provides a general reference of

available commands. For a more detailed description

of commands and operations, refer to the 64Mb,

128Mb, or 256Mb SDRAM component data sheet.

NOTE:

1. CKE is HIGH for all commands shown except SELF REFRESH.

2. A0-A11 define the op-code written to the mode register, and for the 128MB module, A12 should be driven LOW.

3. A0-A11 (32MB/64MB) or A0-A12 (128MB) provide device row address, and BA0, BA1 determine which device bank is made active.

4. A0-A7 (32MB) or A0-A8 (64MB/128MB) provide device column address; A10 HIGH enables the auto precharge feature (nonpersis-

tent), while A10 LOW disables the auto precharge feature; BA0, BA1 determine which device bank is being read from or written to.

5. A10 LOW: BA0, BA1 determine the device bank being precharged. A10 HIGH: All device banks precharged and BA0, BA1 are "Don't

Care."

6. This command is AUTO REFRESH if CKE is HIGH, SELF REFRESH if CKE is LOW.

7. Internal refresh counter controls device row addressing; all inputs and I/Os are "Don't Care" except for CKE.

8. Activates or deactivates the DQs during WRITEs (zero-clock delay) and READs (two-clock delay).

Table 9:

Truth Table ≠ Commands and DQMB Operation

Note: 1

NAME (FUNCTION)

CS#

RAS# CAS# WE#

DQMB

ADDR

DQS

NOTES

COMMAND INHIBIT (NOP)

H

X

X

X

X

X

X

NO OPERATION (NOP)

L

H

H

H

X

X

X

ACTIVE (Select bank and activate row)

L

L

H

H

X

Bank/Row

X

3

READ (Select bank and column, and start READ

burst)

L

H

L

H

L/H

8

Bank/Col

X

4

WRITE (Select bank and column, and start WRITE

burst)

L

H

L

L

L/H

8

Bank/Col

Valid

4

BURST TERMINATE

L

H

H

L

X

X

Active

PRECHARGE (Deactivate row in bank or banks)

L

L

H

L

X

Code

X

5

AUTO REFRESH or SELF REFRESH

(Enter self refresh mode)

L

L

L

H

X

X

X

6, 7

LOAD MODE REGISTER

L

L

L

L

X

Op-Code

X

2

Write Enable/Output enable

≠

≠

≠

≠

L

≠

Active

8

Write Inhibit/Output High-Z

≠

≠

≠

≠

H

≠

High-Z

8

32MB / 64MB / 128MB (x72)

168-PIN SDRAM DIMMs

32, 64, 128MB x 64 SDRAM DIMM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

SD5C4_8_16X72AG_B.fm - Rev. B 9/02

11

©2002, Micron Technology Inc.

Absolute Maximum Ratings*

Voltage on V

DD

, V

DD

Q Supply

Relative to V

SS

. . . . . . . . . . . . . . . . . . . . -1V to +4.6V

Voltage on Inputs, NC or I/O Pins

Relative to V

SS

. . . . . . . . . . . . . . . . . . . . -1V to +4.6V

Operating Temperature

T

A

(Commercial) . . . . . . . . . . . . . . . . . .0∞C to +70∞C

T

A

(Industrial). . . . . . . . . . . . . . . . . . .-40∞C to +85∞C

Storage Temperature (plastic) . . . . . .-55∞C to +150∞C

Power Dissipation. . . . . . . . . . . . . . . . . . . . . . . . . . . . 5W

*Stresses greater than those listed under "Absolute

Maximum Ratings" may cause permanent damage to

the device. This is a stress rating only, and functional

operation of the device at these or any other condi-

tions above those indicated in the operational sections

of this specification is not implied. Exposure to abso-

lute maximum rating conditions for extended periods

may affect reliability.

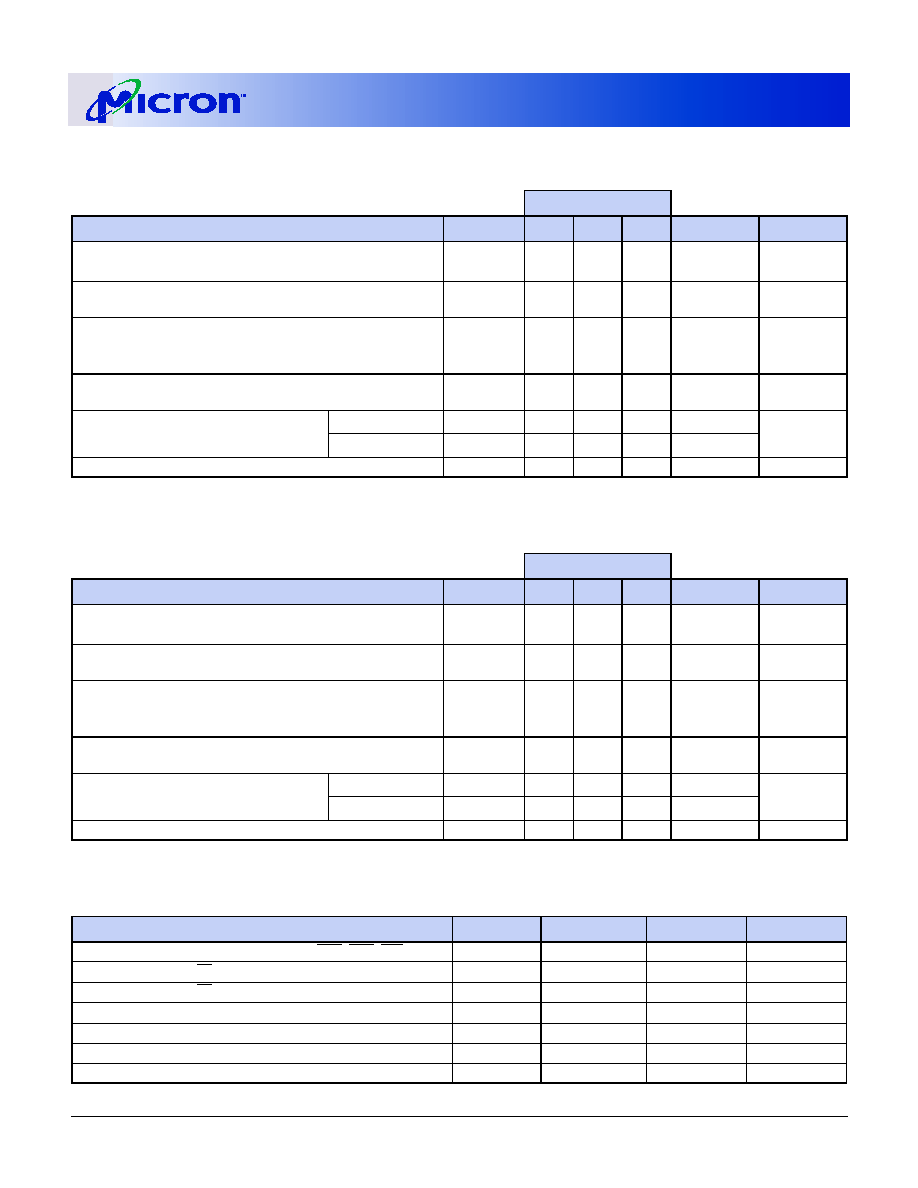

Table 10: DC Electrical Characteristics and Operating Conditions

Notes: 1, 5, 6; notes appear following the parameter tables; V

DD

, V

DD

Q = +3.3V ±0.3V

PARAMETER/CONDITION

SYMBOL

MIN

MAX

UNITS

NOTES

SUPPLY VOLTAGE

V

DD

,

V

DD

Q

3

3.6

V

INPUT HIGH VOLTAGE: Logic 1; All inputs

V

IH

2

V

DD

+ 0.3

V

22

INPUT LOW VOLTAGE: Logic 0; All inputs

V

IL

-0.3

0.8

V

22

INPUT LEAKAGE CURRENT: Any input 0V

£ V

IN

£ V

DD

(All other pins not under

test = 0V)

Command/

Address, CKE0

I

I

-25

25

µA

33

CK0, S0

-15

15

CK2, S2

-10

10

DQ, DQM

-5

5

OUTPUT LEAKAGE CURRENT: DQs are disabled;

0V

£ V

OUT

£ V

DD

Q

I

OZ

-5

5

µA

33

OUTPUT LEVELS: Output High Voltage

(I

OUT

= -4mA)

V

OH

2.4

≠

V

Output Low Voltage (I

OUT

= 4mA)

V

OL

≠

0.4

V

Table 11: I

DD

Specifications and Conditions ≠ 32MB Module

Notes: 1, 5, 6, 11, 13; notes appear following the parameter tables; V

DD

, V

DD

Q = +3.3V ±0.3V; DRAM components only

MAX

PARAMETER/CONDITION

SYMBOL

-13E

-133

-10E

UNITS

NOTES

OPERATING CURRENT: Active Mode; Burst = 2; READ or

WRITE;

t

RC =

t

RC (MIN)

I

DD

1

625

575

475

mA

3, 18, 19, 29

STANDBY CURRENT: Power-Down Mode; All device banks

idle; CKE = LOW

I

DD

2

10

10

10

mA

29

STANDBY CURRENT: Active Mode; CKE = HIGH; CS# =

HIGH; All device banks active after

t

RCD met; No accesses

in progress

I

DD

3

225

225

175

mA

3, 12, 19, 29

OPERATING CURRENT: Burst Mode; Continuous burst;

READ or WRITE; All device banks active

I

DD

4

750

700

600

mA

3, 18, 19, 29

AUTO REFRESH CURRENT

CS# = HIGH; CKE = HIGH

t

RFC =

t

RFC (MIN)

I

DD

5

1,150

1,050

950

mA

3, 12, 18, 19,

29, 30

t

RFC = 15.62µs

I

DD

6

15

15

15

mA

SELF REFRESH CURRENT: CKE

£ 0.2V

I

DD

7

5

5

5

mA

4

32MB / 64MB / 128MB (x72)

168-PIN SDRAM DIMMs

32, 64, 128MB x 64 SDRAM DIMM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

SD5C4_8_16X72AG_B.fm - Rev. B 9/02

12

©2002, Micron Technology Inc.

Table 12: I

DD

Specifications and Conditions ≠ 64MB Module

Notes: 1, 5, 6, 11, 13; notes appear following the parameter tables; V

DD

, V

DD

Q = +3.3V ±0.3V; DRAM components only

MAX

PARAMETER/CONDITION

SYMBOL

-13E

-133

-10E

UNITS

NOTES

OPERATING CURRENT: Active Mode; Burst = 2; READ or

WRITE;

t

RC =

t

RC (MIN)

I

DD

1

800

750

700

mA

3, 18, 19, 29

STANDBY CURRENT: Power-Down Mode; All device banks

idle; CKE = LOW

I

DD

2

10

10

10

mA

29

STANDBY CURRENT: Active Mode; CKE = HIGH; CS# =

HIGH; All device banks active after

t

RCD met; No accesses

in progress

I

DD

3

250

250

200

mA

3, 12, 19, 29

OPERATING CURRENT: Burst Mode; Continuous burst;

READ or WRITE; All device banks active

I

DD

4

825

750

700

mA

3, 18, 19, 29

AUTO REFRESH CURRENT

CS# = HIGH; CKE = HIGH

t

RFC =

t

RFC (MIN)

I

DD

5

1,650

1,550

1,350

mA

3, 12, 18, 19,

29, 30

t

RFC = 15.62µs

I

DD

6

15

15

15

mA

SELF REFRESH CURRENT: CKE

£ 0.2V

I

DD

7

10

10

10

mA

4

Table 13: I

DD

Specifications and Conditions ≠ 128MB Module

Notes: 1, 5, 6, 11, 13; notes appear following the parameter tables; V

DD

, V

DD

Q = +3.3V ±0.3V; DRAM components only

MAX

PARAMETER/CONDITION

SYMBOL

-13E

-133

-10E

UNITS

NOTES

OPERATING CURRENT: Active Mode; Burst = 2; READ or

WRITE;

t

RC =

t

RC (MIN)

I

DD

1

625

625

625

mA

3, 18, 19, 29

STANDBY CURRENT: Power-Down Mode; All device banks

idle; CKE = LOW

I

DD

2

10

10

10

mA

29

STANDBY CURRENT: Active Mode; CKE = HIGH; CS# =

HIGH; All device banks active after

t

RCD met; No accesses

in progress

I

DD

3

200

200

200

mA

3, 12, 19, 29

OPERATING CURRENT: Burst Mode; Continuous burst;

READ or WRITE; All device banks active

I

DD

4

675

675

675

mA

3, 18, 19, 29

AUTO REFRESH CURRENT

CS# = HIGH; CKE = HIGH

t

RFC =

t

RFC (MIN)

I

DD

5

1,425

1,350

1,350

mA

3, 12, 18, 19,

29, 30

t

RFC = 7.81µs

I

DD

6

17.5

17.5

17.5

mA

SELF REFRESH CURRENT: CKE

£ 0.2V

I

DD

7

12.5

12.5

12.5

mA

4

Table 14: Capacitance

Notes 1, 2; notes appear following parameter table

PARAMETER

SYMBOL

MIN

MAX

UNITS

Input Capacitance: A0-A12, BA0, BA1, RAS, CAS, WE, CKE0

C

I1

12.5

19

pF

Input Capacitance: S0

C

I2

a

7.5

11.4

pF

Input Capacitance: S2

C

I2

b

5

7.6

pF

Input Capacitance: CK0

C

I3

a

14.1

17.1

pF

Input Capacitance: CK2

C

I3

b

18.6

20.6

pF

Input Capacitance: DQMB0-DQMB7

C

I4

2.5

3.8

pF

Inuput/Output Capacitance: DQ0-DQ63

C

IO

4

6

pF

32MB / 64MB / 128MB (x72)

168-PIN SDRAM DIMMs

32, 64, 128MB x 64 SDRAM DIMM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

SD5C4_8_16X72AG_B.fm - Rev. B 9/02

13

©2002, Micron Technology Inc.

Table 15: Electrical Characteristics and Recommended AC Operating Conditions

Notes: 5, 6, 8, 9, 11, 31; notes appear following the parameter tables; V

DD

, V

DD

Q = +3.3V ±0.3V

AC CHARACTERISTICS

-13E

-133

-10E

PARAMETER

SYMBOL

MIN

MAX

MIN

MAX

MIN

MAX

UNITS NOTES

Access time from CLK

(pos. edge)

CL = 3

t

AC(3)

5.4

5.4

6

ns

27

CL = 2

t

AC(2)

5.4

6

6

ns

Address hold time

t

AH

0.8

0.8

1

ns

Address setup time

t

AS

1.5

1.5

2

ns

CLK high-level width

t

CH

2.5

2.5

3

ns

CLK low-level width

t

CL

2.5

2.5

3

ns

Clock cycle time

CL = 3

t

CK(3)

7

7.5

8

ns

23

CL = 2

t

CK(2)

7.5

10

10

ns

23

CKE hold time

t

CKH

0.8

0.8

1

ns

CKE setup time

t

CKS

1.5

1.5

2

ns

CS#, RAS#, CAS#, WE#, DQM hold

time

t

CMH

0.8

0.8

1

ns

CS#, RAS#, CAS#, WE#, DQM setup

time

t

CMS

1.5

1.5

2

ns

Data-in hold time

t

DH

0.8

0.8

1

ns

Data-in setup time

t

DS

1.5

1.5

2

ns

Data-out high-impedance

time

CL = 3

t

HZ(3)

5.4

5.4

6

ns

10

CL = 2

t

HZ(2)

5.4

6

6

ns

10

Data-out low-impedance time

t

LZ

1

1

1

ns

Data-out hold time (load)

t

OH

3

3

3

ns

Data-out hold time (no load)

t

OH

N

1.8

1.8

1.8

ns

28

ACTIVE to PRECHARGEcommand

t

RAS

37

120,000

44

120,000

50

120,000

ns

32

ACTIVE to ACTIVE command period

t

RC

60

66

70

ns

ACTIVE to READ or WRITE delay

t

RCD

15

20

20

ns

Refresh period (8,192 rows)

t

REF

64

64

64

ms

AUTO REFRESH period

t

RFC

66

66

70

ns

PRECHARGE command period

t

RP

15

20

20

ns

ACTIVE bank a to ACTIVE bank b

command

t

RRD

14

15

20

ns

Transition time

t

T

0.3

1.2

0.3

1.2

0.3

1.2

ns

7

WRITE recovery time

t

WR

1 CLK +

7ns

1 CLK +

7.5ns

1 CLK +

7ns

ns

24

14

15

15

ns

25

Exit SELF REFRESH to ACTIVE

command

t

XSR

67

75

80

ns

20

32MB / 64MB / 128MB (x72)

168-PIN SDRAM DIMMs

32, 64, 128MB x 64 SDRAM DIMM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

SD5C4_8_16X72AG_B.fm - Rev. B 9/02

14

©2002, Micron Technology Inc.

Table 16: AC Functional Characteristics

Notes: 5, 6, 8, 9, 11, 31; notes appear following the parameter tables

PARAMETER

SYMBOL

-13E

-133

-10E

UNITS NOTES

READ/WRITE command to READ/WRITE command

t

CCD

1

1

1

t

CK

17

CKE to clock disable or power-down entry mode

t

CKED

1

1

1

t

CK

14

CKE to clock enable or power-down exit setup mode

t

PED

1

1

1

t

CK

14

DQM to input data delay

t

DQD

0

0

0

t

CK

17

DQM to data mask during WRITEs

t

DQM

0

0

0

t

CK

17

DQM to data high-impedance during READs

t

DQZ

2

2

2

t

CK

17

WRITE command to input data delay

t

DWD

0

0

0

t

CK

17

Data-in to ACTIVE command

t

DAL

4

5

4

t

CK

15, 21

Data-into PRECHARGE command

t

DPL

2

2

2

t

CK

16, 21

Last data-in to burst STOP command

t

BDL

1

1

1

t

CK

17

Last data-in to new READ/WRITE command

t

CDL

1

1

1

t

CK

17

Last data-in to PRECHARGE command

t

RDL

2

2

2

t

CK

16, 21

LOAD MODE REGISTER command to ACTIVE or REFRESH command

t

MRD

2

2

2

t

CK

26

Data-out to high-impedance from PRECHARGE

command

CL =3

t

ROH(3)

3

3

3

t

CK

17

CL = 2

t

ROH(2)

2

2

2

t

CK

17

32MB / 64MB / 128MB (x72)

168-PIN SDRAM DIMMs

32, 64, 128MB x 64 SDRAM DIMM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

SD5C4_8_16X72AG_B.fm - Rev. B 9/02

15

©2002, Micron Technology Inc.

Notes

1. All voltages referenced to V

SS

.

2. This parameter is sampled. V

DD

, V

DD

Q = +3.3V;

f = 1 MHz; T

A

= 25∞C; pin under test biased at 1.4V.

3. I

DD

is dependent on output loading and cycle

rates. Specified values are obtained with mini-

mum cycle time and the outputs open.

4. Enables on-chip refresh and address counters.

5. The minimum specifications are used only to

indicate cycle time at which proper operation

over the full temperature range is ensured (0∞C

£

T

A

£ +70∞C for Commercial, -40∞C £ T

A

£ +85∞C for

Industrial).

6. An initial pause of 100µs is required after power-

up, followed by two AUTO REFRESH commands,

before proper device operation is ensured. (V

DD

and V

DD

Q must be powered up simultaneously.

V

SS

and V

SS

Q must be at same potential.) The two

AUTO REFRESH command wake-ups should be

repeated any time the

t

REF refresh requirement is

exceeded.

7. AC characteristics assume

t

T = 1ns.

8. In addition to meeting the transition rate specifi-

cation, the clock and CKE must transit between

V

IH

and V

IL

(or between V

IL

and V

IH

) in a mono-

tonic manner.

9. Outputs measured at 1.5V with equivalent load:

10.

t

HZ defines the time at which the output achieves

the open circuit condition; it is not a reference to

V

OH

or V

OL

. The last valid data element will meet

t

OH before going High-Z.

11. AC timing and I

DD

tests have V

IL

= 0V and V

IH

= 3V,

with timing referenced to 1.5V crossover point. If the

input transition time is longer than 1ns, then the

timing is referenced at V

IL

(MAX) and V

IH

(MIN) and

no longer at the ISV crossover point.

12. Other input signals are allowed to transition no

more than once every two clocks and are other-

wise at valid V

IH

or V

IL

levels.

13. I

DD

specifications are tested after the device is

properly initialized.

14. Timing actually specified by

t

CKS; clock(s) speci-

fied as a reference only at minimum cycle rate.

15. Timing actually specified by

t

WR plus

t

RP; clock(s)

specified as a reference only at minimum cycle

rate.

16. Timing actually specified by

t

WR.

17. Required clocks are specified by JEDEC function-

ality and are not dependent on any timing param-

eter.

18. The I

DD

current will increase or decrease propor-

tionally according to the amount of frequency

alteration for the test condition.

19. Address transitions average one transition every

two clocks.

20. CLK must be toggled a minimum of two times

during this period.

21. Based on

t

CK = 10ns for -10E;

t

CK = 7.5ns for -133

and -13E.

22. V

IH

overshoot: V

IH

(MAX) = V

DD

Q + 2V for a pulse

width

£ 3ns, and the pulse width cannot be

greater than one-third of the cycle rate. V

IL

under-

shoot: V

IL

(MIN) = -2V for a pulse width

£ 3ns.

23. The clock frequency must remain constant (stable

clock is defined as a signal cycling within timing

constraints specified for the clock pin) during

access or precharge states (READ, WRITE, includ-

ing

t

WR and PRECHARGE commands). CKE may

be used to reduce the data rate.

24. Auto precharge mode only. The precharge timing

budget (

t

RP) begins 7ns for -13E; 7.5ns for -133;

and 7ns for -10E after the first clock delay, after

the last WRITE is executed. May not exceed limit

set for precharge mode.

25. Precharge mode only.

26. JEDEC and PC100 specify three clocks.

27.

t

AC for -133/-13E at CL = 3 with no load is 4.6ns

and is guaranteed by design.

28. Parameter guaranteed by design.

29. For -13E, CL = 2 and

t

CK = 7.5ns; for -133, CL = 3

and

t

CK = 7.5ns; for -10E, CL=2 and

t

CK = 10ns.

30. CKE is HIGH during refresh command period

t

RFC (MIN), else CKE is LOW. The I

DD

6 limit is

actually a nominal value and does not result in a

fail value.

31. Refer to device data sheet for timing waveforms.

32. The value of

t

RAS used in -13E speed grade mod-

ules is calculated from

t

RC -

t

RP.

33. Leakage number reflects the worst-case leakage

possible through the module pin, not what each

memory device contributes.

Q

50pF

32MB / 64MB / 128MB (x72)

168-PIN SDRAM DIMMs

32, 64, 128MB x 64 SDRAM DIMM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

SD5C4_8_16X72AG_B.fm - Rev. B 9/02

16

©2002, Micron Technology Inc.

SPD Clock and Data Conventions

Data states on the SDA line can change only during

SCL LOW. SDA state changes during SCL HIGH are

reserved for indicating start and stop conditions, as

indicated in Figure 6, Data Validity, and Figure 7, Defi-

nition of Start and Stop.

SPD Start Condition

All commands are preceded by the start condition,

which is a HIGH-to-LOW transition of SDA when SCL

is HIGH. The SPD device continuously monitors the

SDA and SCL lines for the start condition and will not

respond to any command until this condition has been

met.

SPD Stop Condition

All communications are terminated by a stop condi-

tion, which is a LOW-to-HIGH transition of SDA when

SCL is HIGH. The stop condition is also used to place

the SPD device into standby power mode.

SPD Acknowledge

Acknowledge is a software convention used to indi-

cate successful data transfers. The transmitting device,

either master or slave, will release the bus after trans-

mitting eight bits. During the ninth clock cycle, the

receiver will pull the SDA line LOW to acknowledge

that it received the eight bits of data as indicated in

Figure Figure 8, Acknowledge Response from Receiver.

The SPD device will always respond with an

acknowledge after recognition of a start condition and

its slave address. If both the device and a WRITE oper-

ation have been selected, the SPD device will respond

with an acknowledge after the receipt of each subse-

quent eight-bit word. In the read mode, the SPD device

will transmit eight bits of data, release the SDA line,

and monitor the line for an acknowledge. If an

acknowledge is detected and no stop condition is gen-

erated by the master, the slave will continue to trans-

mit data. If an acknowledge is not detected, the slave

will terminate further data transmissions and await

the stop condition to return to standby power mode.

Figure 6: Data Validity

Figure 7: Definition of Start and Stop

Figure 8: Acknowledge Response from Receiver

SCL

SDA

DATA STABLE

DATA STABLE

DATA

CHANGE

SCL

SDA

START

BIT

STOP

BIT

SCL from Master

Data Output

from Transmitter

Data Output

from Receiver

9

8

Acknowledge

32MB / 64MB / 128MB (x72)

168-PIN SDRAM DIMMs

32, 64, 128MB x 64 SDRAM DIMM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

SD5C4_8_16X72AG_B.fm - Rev. B 9/02

17

©2002, Micron Technology Inc.

Table 17: EEPROM Device Select Code

The most significant bit (b7) is sent first

DEVICE TYPE IDENTIFIER

CHIP ENABLE

RW

b7

b6

b5

b4

b3

b2

b1

b0

Memory Area Select Code (two arrays)

1

0

1

0

SA2

SA1

SA0

RW

Protection Register Select Code

0

1

1

0

SA2

SA1

SA0

RW

Table 18: EEPROM Operating Modes

MODE

RW BIT

WC

1

BYTES

INITIAL SEQUENCE

Current Address Read

1

V

IH

or V

IL

1

START, Device Select, RW = `1'

Random Address Read

0

V

IH

or V

IL

1

START, Device Select, RW = `0', Address

1

V

IH

or V

IL

1

reSTART, Device Select, RW = `1'

Sequential Read

1

V

IH

or V

IL

≥ 1

Similar to Current or Random Address Read

Byte Write

0

V

IL

1

START, Device Select, RW = `0'

Page Write

0

V

IL

£ 16

START, Device Select, RW = `0'

Table 19: Serial Presence-Detect EEPROM DC Operating Conditions

V

DD

= +3.3V ±0.3V; all voltages referenced to V

SS

PARAMETER/CONDITION

SYMBOL

MIN

MAX

UNITS

SUPPLY VOLTAGE

V

DD

3

3.6

V

INPUT HIGH VOLTAGE: Logic 1; All inputs

V

IH

V

DD

x 0.7

V

DD

+ 0.5

V

INPUT LOW VOLTAGE: Logic 0; All inputs

V

IL

-1

V

DD

x 0.3

V

OUTPUT LOW VOLTAGE: I

OUTL

= 3mA

V

OL

≠

0.4

V

INPUT LEAKAGE CURRENT: V

IN

= GND to V

DD

I

LI

≠

10

µA

OUTPUT LEAKAGE CURRENT: V

OUT

= GND to V

DD

I

LO

≠

10

µA

STANDBY CURRENT: SCL = SDA = V

DD

- 0.3V;

All other inputs = GND or 3.3V ±10%

I

SB

≠

30

µA

POWER SUPPLY CURRENT: SCL clock frequency = 100 KHz

I

DD

≠

2

mA

32MB / 64MB / 128MB (x72)

168-PIN SDRAM DIMMs

32, 64, 128MB x 64 SDRAM DIMM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

SD5C4_8_16X72AG_B.fm - Rev. B 9/02

18

©2002, Micron Technology Inc.

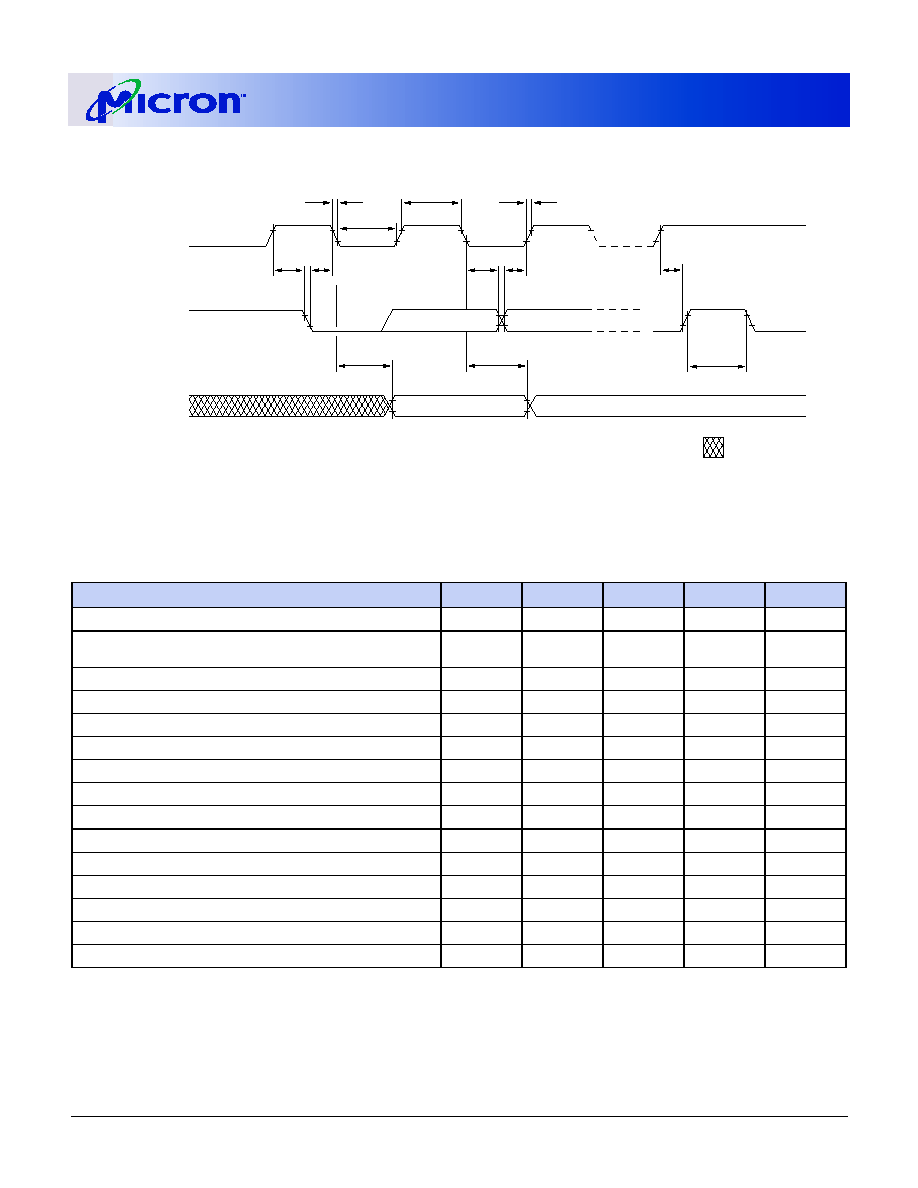

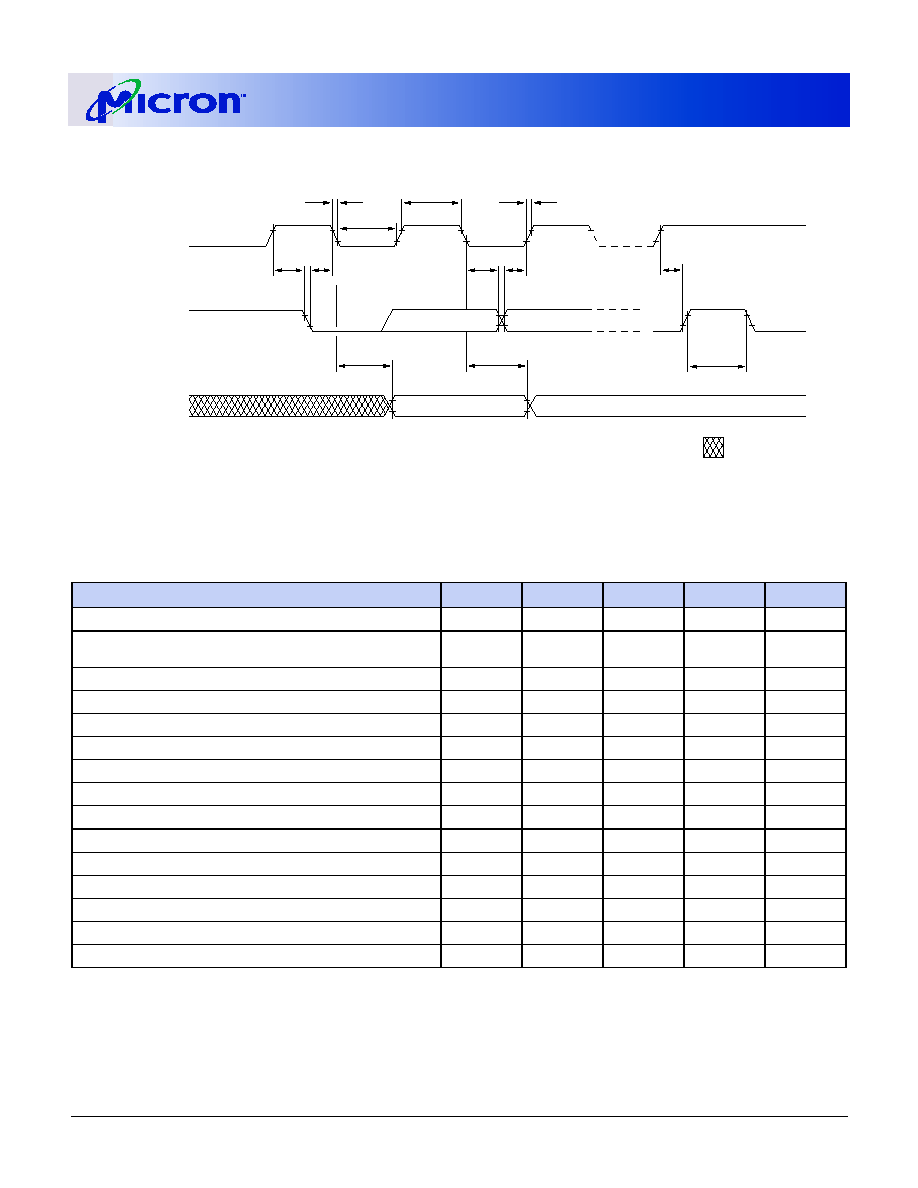

Figure 9: SPD EEPROM Timing Diagram

NOTE:

1. Timing actually specified ty

t

WR.

SCL

SDA IN

SDA OUT

tLOW

tSU:STA

tHD:STA

tF

tHIGH

tR

tBUF

tDH

tAA

tSU:STO

tSU:DAT

tHD:DAT

UNDEFINED

Table 20: Serial Presence-Detect EEPROM AC Operating Conditions

V

DD

= +3.3V ±0.3V; all voltages referenced to V

SS

PARAMETER/CONDITION

SYMBOL

MIN

MAX

UNITS

NOTES

SCL LOW to SDA data-out valid

t

AA

0.3

3.5

µs

Time the bus must be free before a new transition can

start

t

BUF

4.7

µs

Data-out hold time

t

DH

300

ns

SDA and SCL fall time

t

F

300

ns

Data-in hold time

t

HD:DAT

0

µs

Start condition hold time

t

HD:STA

4

µs

Clock HIGH period

t

HIGH

4

µs

Noise suppression time constant at SCL, SDA inputs

t

I

100

ns

Clock LOW period

t

LOW

4.7

µs

SDA and SCL rise time

t

R

1

µs

SCL clock frequency

t

SCL

100

KHz

Data-in setup time

t

SU:DAT

250

ns

Start condition setup time

t

SU:STA

4.7

µs

Stop condition setup time

t

SU:STO

4.7

µs

WRITE cycle time

t

WRC

10

ms

1

32MB / 64MB / 128MB (x72)

168-PIN SDRAM DIMMs

32, 64, 128MB x 64 SDRAM DIMM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

SD5C4_8_16X72AG_B.fm - Rev. B 9/02

19

©2002, Micron Technology Inc.

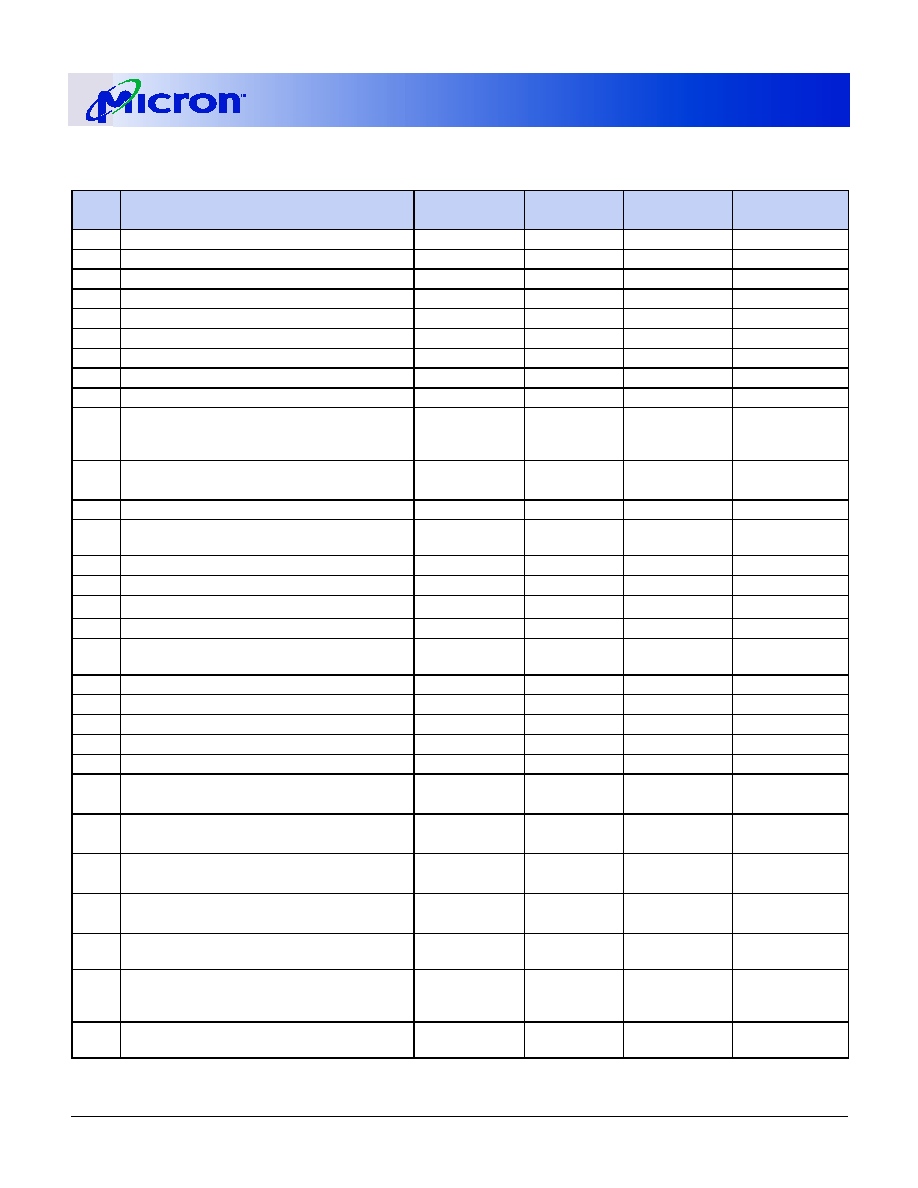

Table 21: Serial Presence-Detect Matrix

"1"/"0": Serial Data, "driven to HIGH"/"driven to LOW."

BYTE

DESCRIPTION

ENTRY

(VERSION)

MT5LSDT472A MT5LSDT872A(I) MT5LSDT1672A(I)

0

NUMBER OF BYTES USED BY MICRON

128

80

80

80

1

TOTAL NUMBER OF SPD MEMORY BYTES

256

08

08

08

2

MEMORY TYPE

SDRAM

04

04

04

3

NUMBER OF ROW ADDRESSES

12 or 13

0C

0C

0D

4

NUMBER OF COLUMN ADDRESSES

8 or 9

08

09

09

5

NUMBER OF BANKS

1

01

01

01

6

MODULE DATA WIDTH

72

48

48

48

7

MODULE DATA WIDTH (continued)

0

00

00

00

8

MODULE VOLTAGE INTERFACE LEVELS

LVTTL

01

01

01

9

SDRAM CYCLE TIME,

t

CK

(CAS LATENCY = 3)

7ns (-13E)

7.5ns (-133)

8ns (-10E)

70

75

80

70

75

80

70

75

80

10

SDRAM ACCESS FROM CLOCK,

t

AC

(CAS LATENCY = 3)

5.4ns (-13E/-133)

6ns (-10E)

54

60

54

60

54

60

11

MODULE CONFIGURATION TYPE

ECC

02

02

02

12

REFRESH RATE/TYPE

(80) 15.6µs/SELF

(82) 7.81µs/SELF

80

80

82

13

SDRAM WIDTH (PRIMARY SDRAM)

16

10

10

10

14

ERROR-CHECKING SDRAM DATA WIDTH

16

10

10

10

15

MINIMUM CLOCK DELAY,

t

CCD

1

01

01

01

16

BURST LENGTHS SUPPORTED

1, 2, 4, 8, PAGE

8F

8F

8F

17

NUMBER OF INTERNAL BANKS

ON SDRAM DEVICE

4

04

04

04

18

CAS LATENCIES SUPPORTED

2, 3

06

06

06

19

CS LATENCY

0

01

01

01

20

WE LATENCY

0

01

01

01

21

SDRAM MODULE ATTRIBUTES

UNBUFFERED

00

00

00

22

SDRAM DEVICE ATTRIBUTES: GENERAL

0E

0E

0E

0E

23

SDRAM CYCLE TIME,

t

CK

(CAS LATENCY = 2)

7.5ns (-13E)

10ns (-133/-10E)

75

A0

75

A0

75

A0

24

SDRAM ACCESS FROM CK,

t

AC

(CAS LATENCY = 2)

5.4ns (-13E)

6ns (-133/-10E)

54

60

54

60

54

60

25

SDRAM CYCLE TIME,

t

CK

(CAS LATENCY = 1)

≠

00

00

00

26

SDRAM ACCESS FROM CK,

t

AC

(CAS LATENCY = 1)

≠

00

00

00

27

MINIMUM ROW PRECHARGE TIME,

t

RP

15ns (-13E)

20ns (-133/-10E)

0F

14

0F

14

0F

14

28

MINIMUM ROW ACTIVE TO ROW ACTIVE,

t

RRD

14ns (-13E)

15ns (-133)

20ns (-10E)

0E

0F

14

0E

0F

14

0E

0F

14

29

MINIMUM RAS# TO CAS# DELAY,

t

RCD

15ns (-13E)

20ns (-133/-10E)

0F

14

0F

14

0F

14

32MB / 64MB / 128MB (x72)

168-PIN SDRAM DIMMs

32, 64, 128MB x 64 SDRAM DIMM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

SD5C4_8_16X72AG_B.fm - Rev. B 9/02

20

©2002, Micron Technology Inc.

NOTE:

1. The value of

t

RAS used for the -13E part is calculated from

t

RC -

t

RP. Actual device specification value is 37ns.

30

MINIMUM RAS# PULSE WIDTH,

t

RAS

(Note 1)

45ns (-13E)

44ns (-133)

50ns (-10E)

2D

2C

32

2D

2C

32

2D

2C

32

31

MODULE BANK DENSITY

32MB, 64MB, or

128MB

08

10

20

32

COMMAND AND ADDRESS SETUP TIME

1.5ns (-13E/-133)

2ns (-10E)

15

20

15

20

15

20

33

COMMAND AND ADDRESS HOLD TIME

0.8ns (-13E/-133)

1ns (-10E)

08

10

08

10

08

10

34

DATA SIGNAL INPUT SETUP TIME

1.5ns (-13E/-133)

2ns (-10E)

15

20

15

20

15

20

35

DATA SIGNAL INPUT HOLD TIME

0.8ns (-13E/-133)

1ns (-10E)

08

10

08

10

08

10

36-61 RESERVED

00

00

00

62

SPD REVISION

1.2

12

12

12

63

CHECKSUM FOR BYTES 0-62

-13E

-133

-10E

70

B6

FE

79

BF

07

8C

D2

1A

64

MANUFACTURER'S JEDEC ID CODE

MICRON

2C

2C

2C

65-71 MANUFACTURER'S JEDEC ID CODE

(continued)

FF

FF

FF

72

MANUFACTURING LOCATION

1-11

01-0B

01-0B

01-0B

73-90 MODULE PART NUMBER (ASCII)

Variable Data

Variable Data

Variable Data

91

PCB IDENTIFICATION CODE

1-9

01-09

01-09

01-09

92

IDENTIFICATION CODE (continued)

0

00

00

00

93

YEAR OF MANUFACTURE IN BCD

Variable Data

Variable Data

Variable Data

94

WEEK OF MANUFACTURE IN BCD

Variable Data

Variable Data

Variable Data

95-98 MODULE SERIAL NUMBER

Variable Data

Variable Data

Variable Data

99-125 MANUFACTURER-SPECIFIC DATA (RSVD)

Variable Data

Variable Data

Variable Data

126

SYSTEM FREQUENCY

100/133 MHz

64

64

64

127

SDRAM COMPONENT AND CLOCK DETAIL

AF

AF

AF

Table 21: Serial Presence-Detect Matrix

"1"/"0": Serial Data, "driven to HIGH"/"driven to LOW."

BYTE

DESCRIPTION

ENTRY

(VERSION)

MT5LSDT472A MT5LSDT872A(I) MT5LSDT1672A(I)

Æ

8000 S. Federal Way, P.O. Box 6, Boise, ID 83707-0006, Tel: 208-368-3900

E-mail: prodmktg@micron.com, Internet: http://www.micron.com, Customer Comment Line: 800-932-4992

Micron and the M logo are registered trademarks and the Micron logo is a trademark of Micron Technology, Inc.

32MB / 64MB / 128MB (x72)

168-PIN SDRAM DIMMs

32, 64, 128MB x 64 SDRAM DIMM

©2002, Micron Technology Inc.

SD5C4_8_16X72AG_B.fm - Rev. B 9/02

21

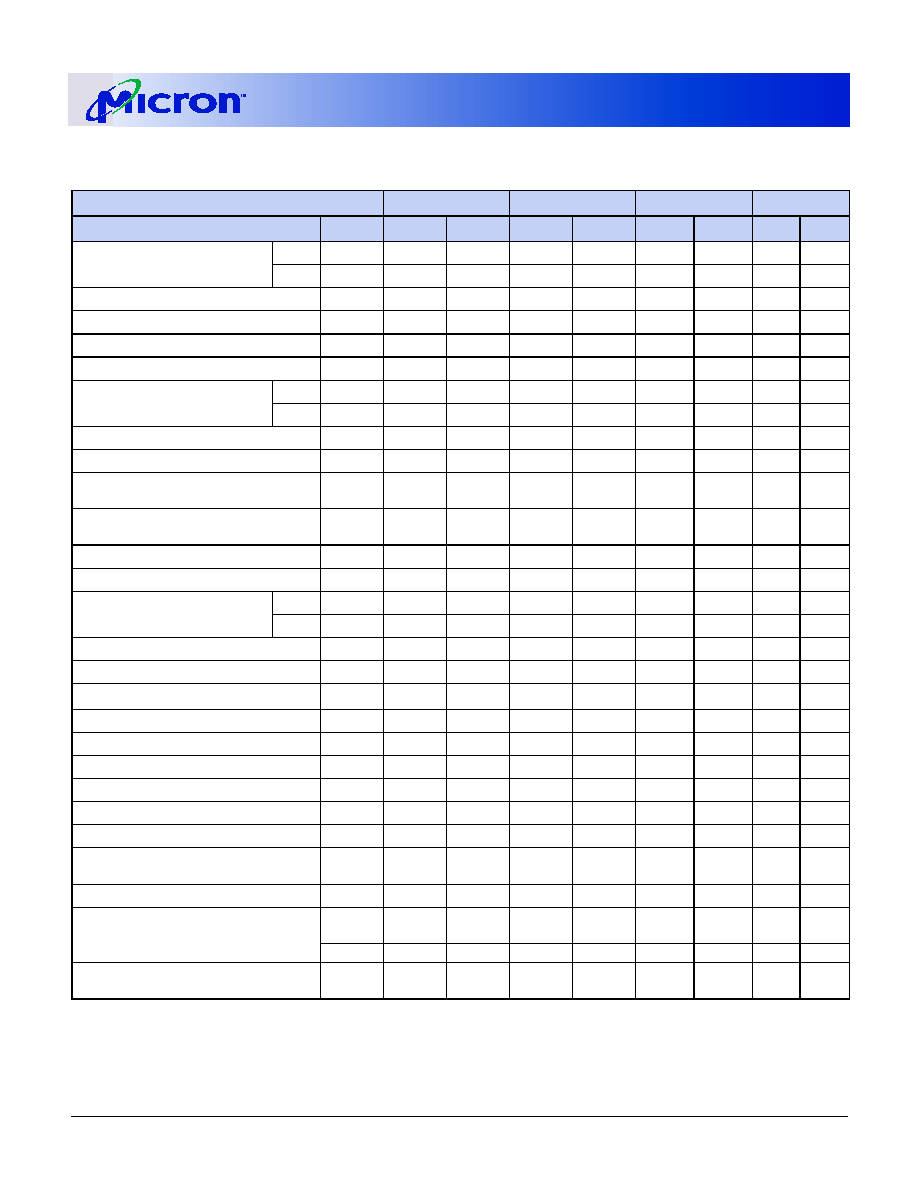

Figure 10: 168-Pin DIMM

NOTE:

All dimensions in inches (millimeters)

or typical where noted.

PIN 1 (PIN 85 ON BACKSIDE)

.700 (17.78)

TYP

.118 (3.00)

(2X)

.118 (3.00) TYP

4.550 (115.57)

.050 (1.27)

TYP

.118 (3.00)

TYP

.039 (1.00)

TYP

.079 (2.00) R

(2X)

.039 (1.00)R (2X)

FRONT VIEW

.128 (3.25)

.118 (3.00)

PIN 84 (PIN 168 ON BACKSIDE)

(2X)

.250 (6.35) TYP

1.661 (42.18)

2.625 (66.68)

1.005 (25.53)

0.995 (25.27)

5.256 (133.50)

5.244 (133.20)

.125 (3.18)

MAX

.054 (1.37)

.046 (1.17)

U1

U2

U4

U5

U3

U6

MAX

MIN