VCT 38xxA

Video/Controller/Teletext

IC Family

Edition Oct. 17, 2000

6251-518-1AI

ADVANCE INFORMATION

MICRONAS

MICRONAS

VCT 38xxA

ADVANCE INFORMATION

2

Micronas

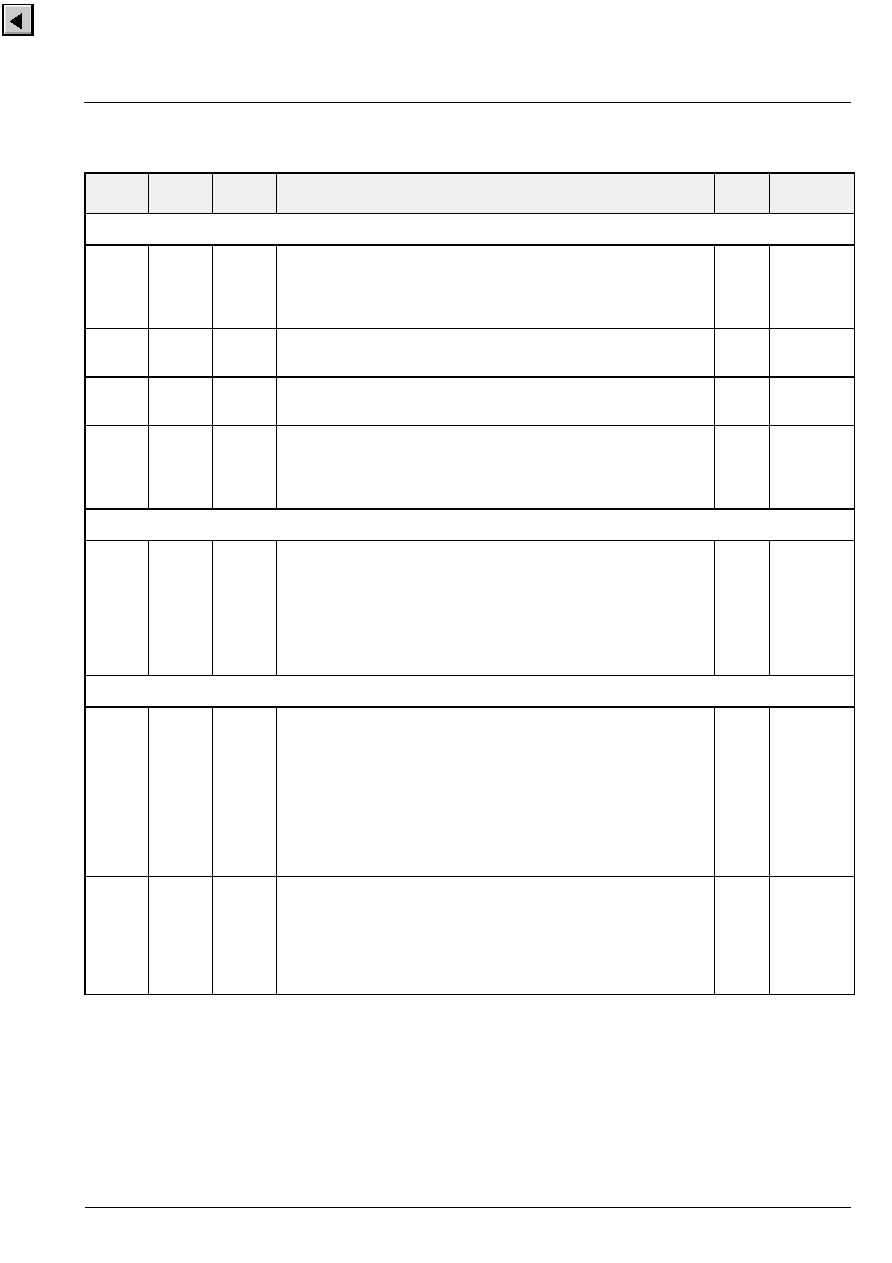

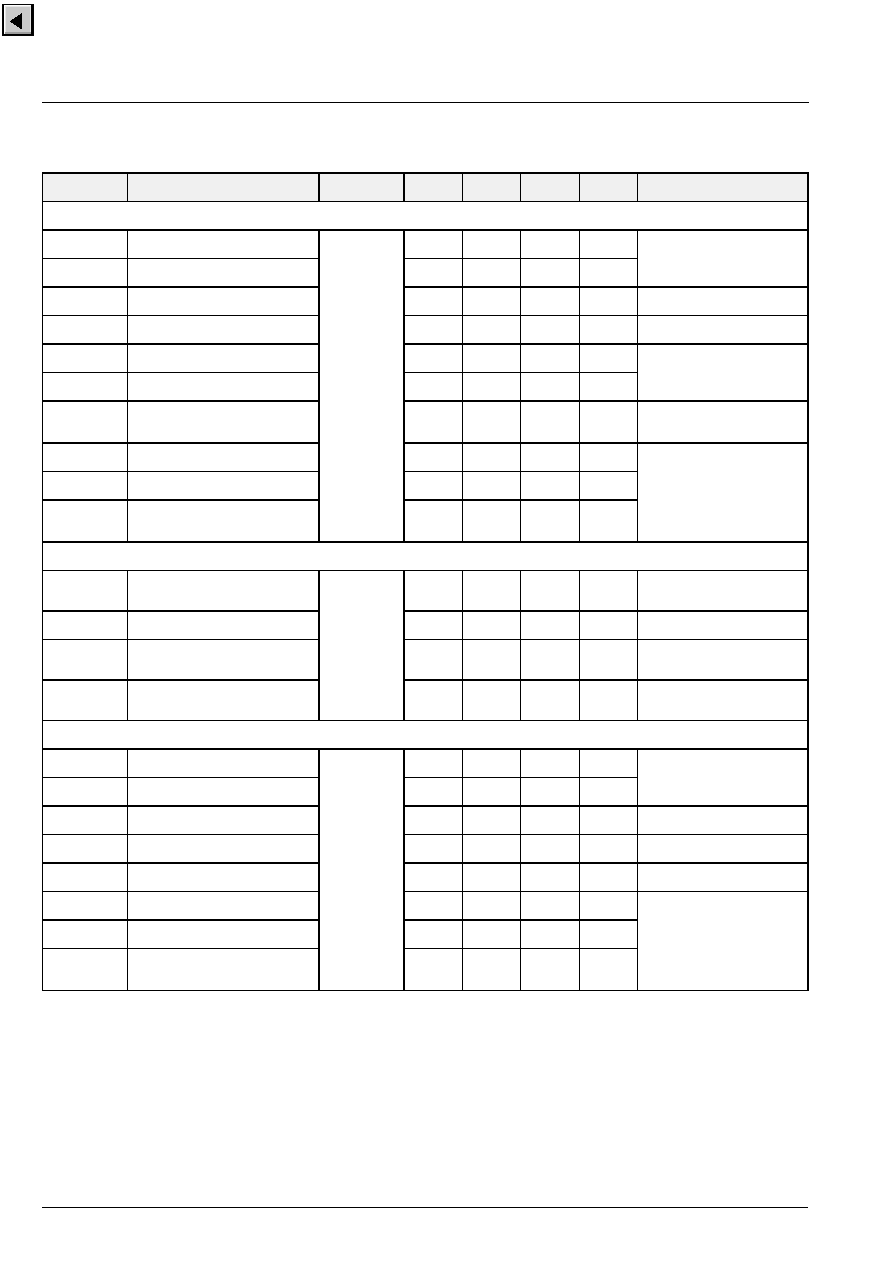

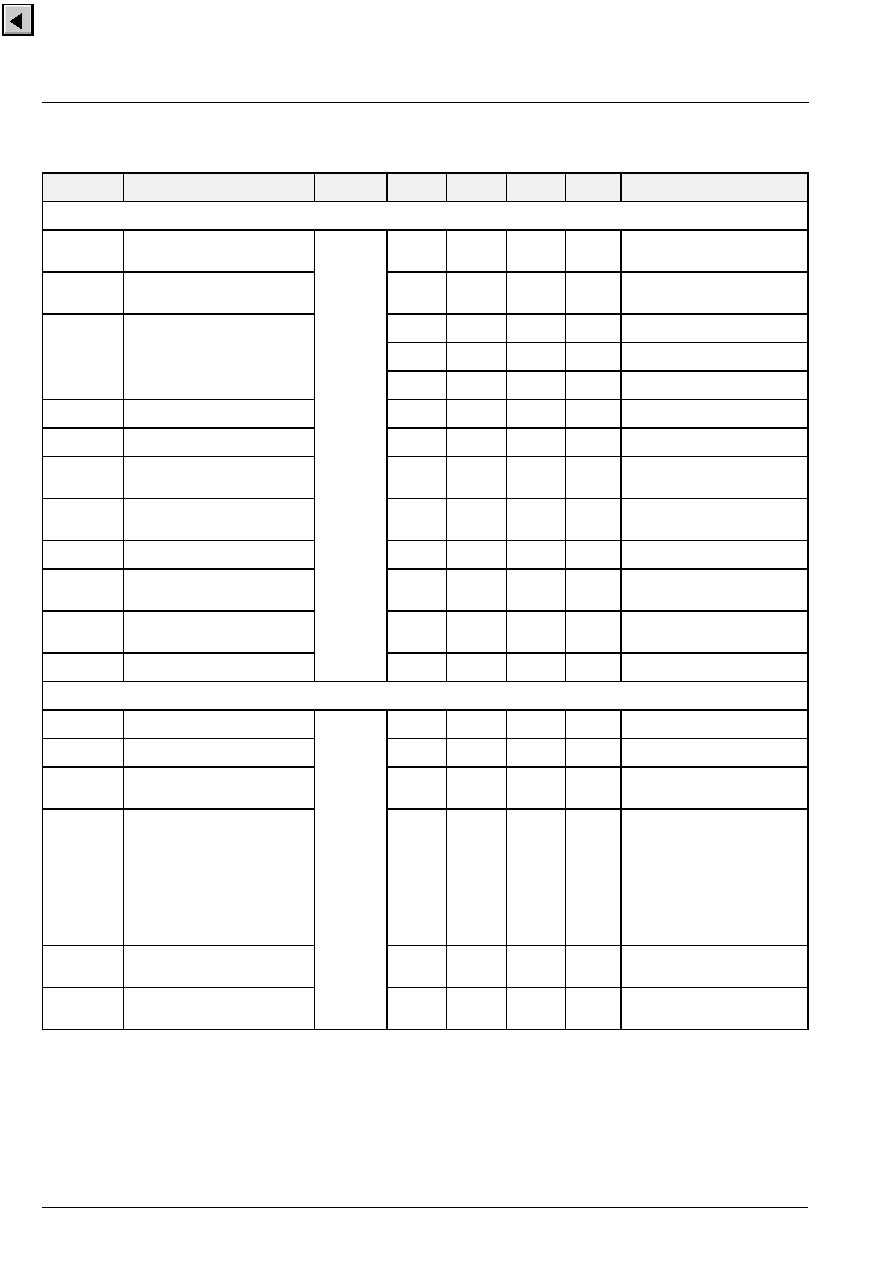

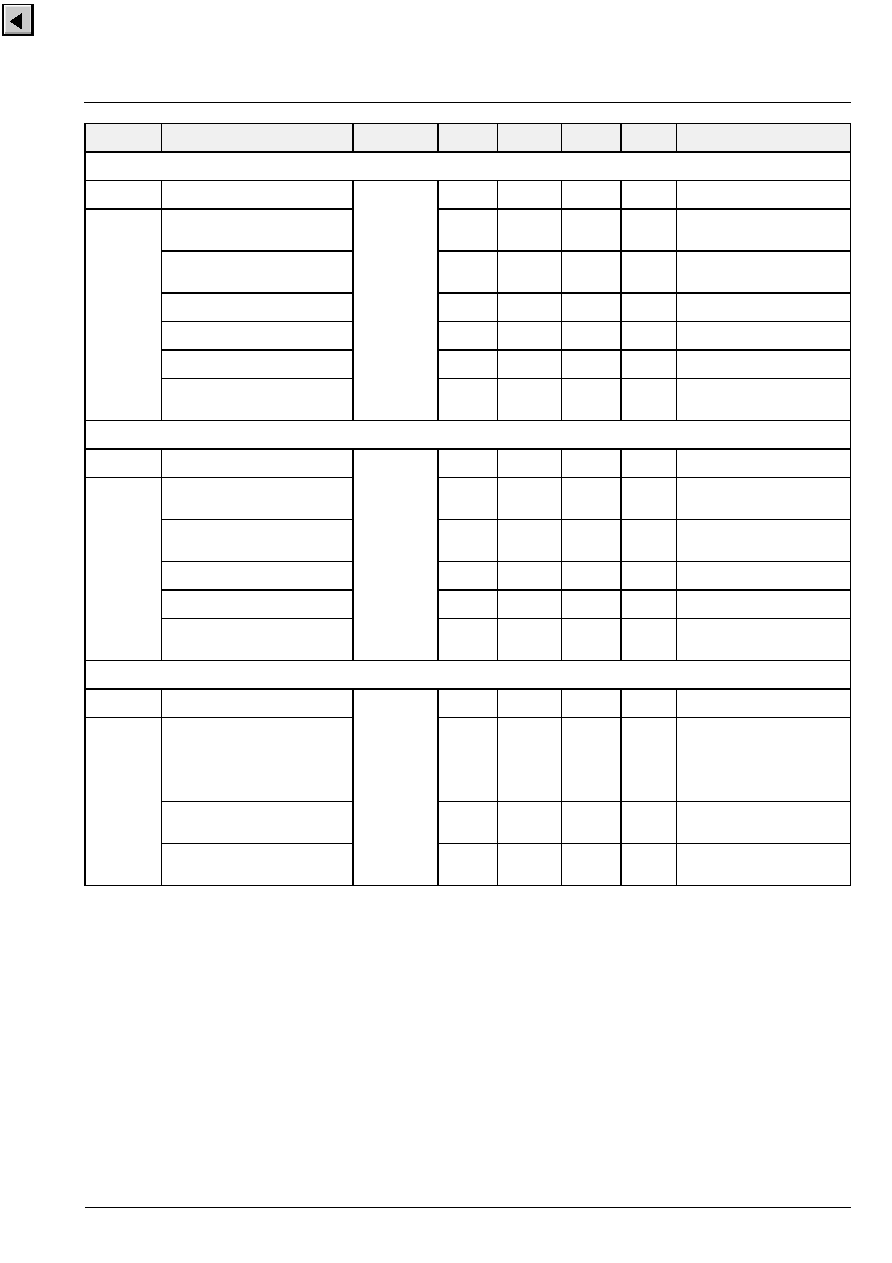

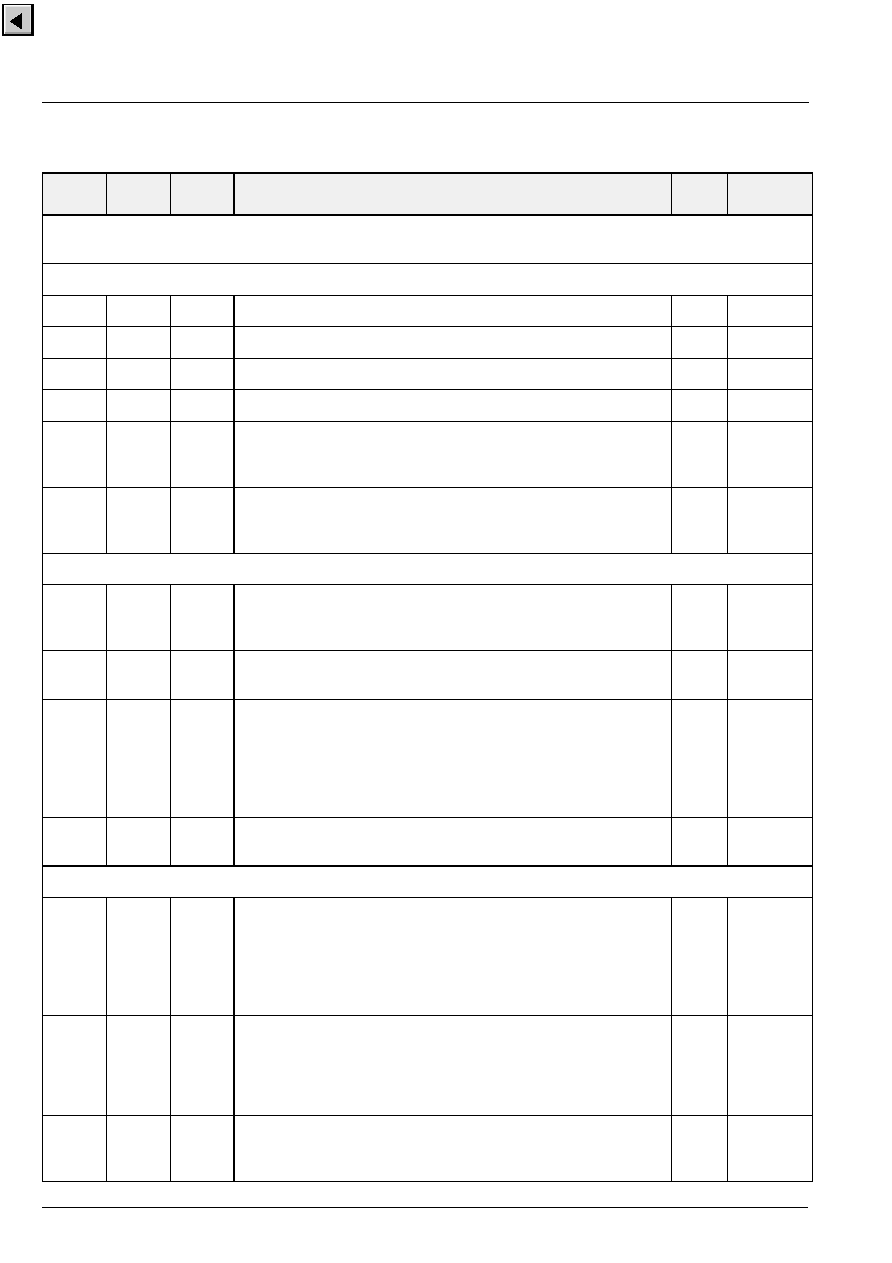

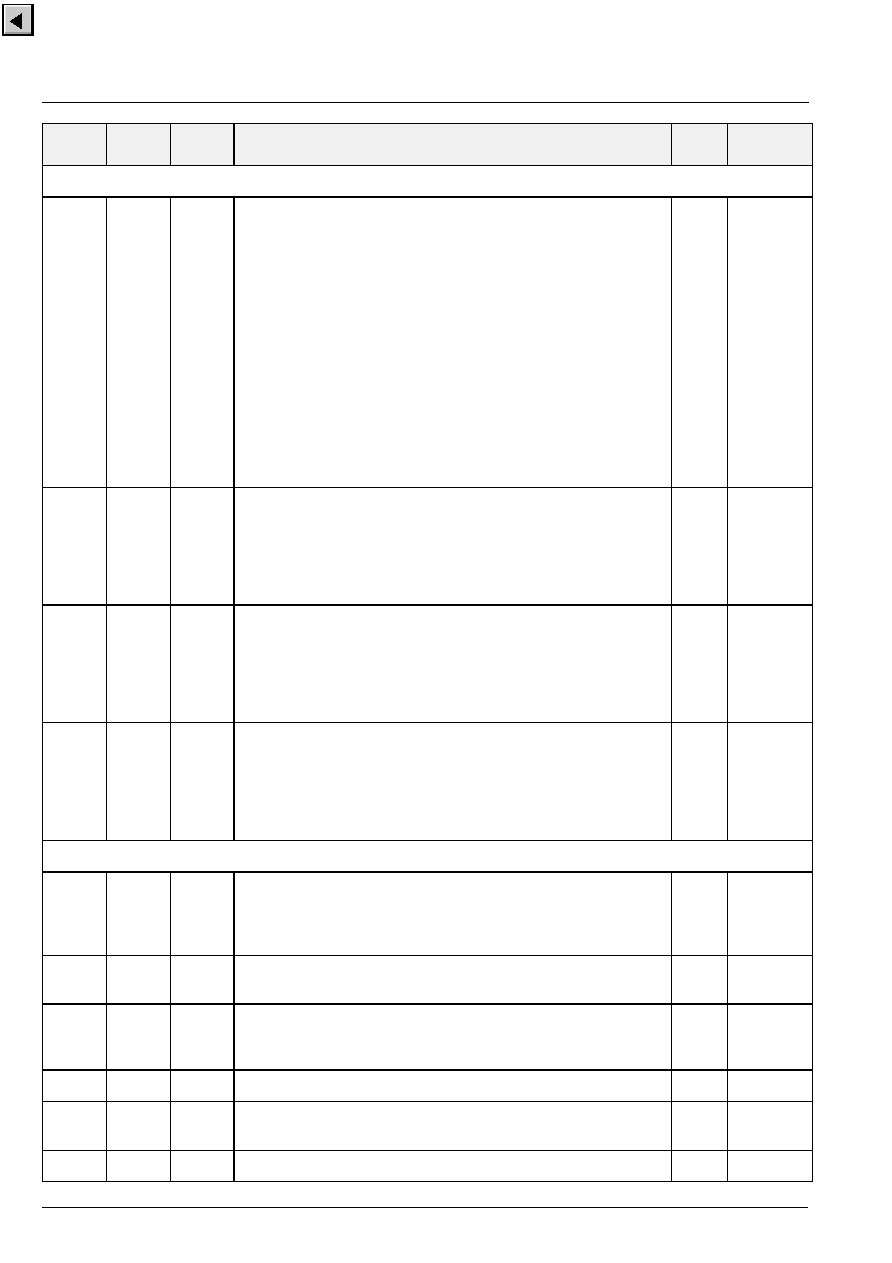

Contents

Page

Section

Title

7

1.

Introduction

8

1.1.

Features

8

1.1.1.

Video Features

8

1.1.2.

Microcontroller Features

8

1.1.3.

OSD Features

8

1.1.4.

Teletext Features

8

1.1.5.

Audio Features

8

1.1.6.

General Features

9

1.2.

Chip Architecture

10

1.3.

System Application

11

2.

Video Processing

11

2.1.

Introduction

11

2.2.

Video Front-end

11

2.2.1.

Input Selector

11

2.2.2.

Clamping

11

2.2.3.

Automatic Gain Control

11

2.2.4.

Analog-to-Digital Converters

12

2.2.5.

Digitally Controlled Clock Oscillator

12

2.2.6.

Analog Video Output

12

2.3.

Adaptive Comb Filter

13

2.4.

Color Decoder

13

2.4.1.

IF-Compensation

14

2.4.2.

Demodulator

14

2.4.3.

Chrominance Filter

14

2.4.4.

Frequency Demodulator

14

2.4.5.

Burst Detection / Saturation Control

14

2.4.6.

Color Killer Operation

15

2.4.7.

Automatic Standard Recognition

15

2.4.8.

PAL Compensation/ 1-H Comb Filter

16

2.4.9.

Luminance Notch Filter

16

2.4.10.

Skew Filtering

16

2.5.

Horizontal Scaler

16

2.6.

Black-line Detector

17

2.7.

Test Pattern Generator

17

2.8.

Video Sync Processing

18

2.9.

Macrovision Detection

18

2.10.

Display Processing

18

2.10.1.

Luma Contrast Adjustment

18

2.10.2.

Black-Level Expander

19

2.10.3.

Dynamic Peaking

21

2.10.4.

Digital Brightness Adjustment

21

2.10.5.

Soft Limiter

21

2.10.6.

Chroma Interpolation

21

2.10.7.

Chroma Transient Improvement

22

2.10.8.

Inverse Matrix

22

2.10.9.

RGB Processing

22

2.10.10.

OSD Color Look-up Table

22

2.10.11.

Picture Frame Generator

23

2.10.12.

Priority Decoder

23

2.10.13.

Scan Velocity Modulation

23

2.10.14.

Display Phase Shifter

Contents, continued

Page

Section

Title

ADVANCE INFORMATION

VCT 38xxA

Micronas

3

25

2.11.

Video Back-end

25

2.11.1.

CRT Measurement and Control

26

2.11.2.

SCART Output Signal

27

2.11.3.

Average Beam Current Limiter

27

2.11.4.

Analog RGB Insertion

27

2.11.5.

Fast-Blank Monitor

29

2.12.

Synchronization and Deflection

29

2.12.1.

Deflection Processing

29

2.12.2.

Angle and Bow Correction

29

2.12.3.

Horizontal Phase Adjustment

30

2.12.4.

Vertical and East/West Deflection

30

2.12.5.

EHT Compensation

31

2.12.6.

Protection Circuitry

31

2.13.

Reset Function

31

2.14.

Standby and Power-On

32

2.15.

I

2

C Bus Slave Interface

32

2.15.1.

Control and Status Registers

44

2.15.1.1.

Scaler Adjustment

46

2.15.1.2.

Calculation of Vertical and East-West Deflection Coefficients

47

3.

Text and OSD Processing

47

3.1.

Introduction

47

3.2.

SRAM Interface

47

3.3.

Text Controller

49

3.4.

Teletext Acquisition

49

3.5.

Teletext Page Management

49

3.5.1.

Memory Manager

50

3.5.2.

Memory Organization

50

3.5.3.

Page Table

52

3.5.4.

Ghost Row Organization

52

3.5.5.

Subpage Manager

53

3.6.

WST Display Controller

55

3.7.

Display Memory

57

3.8.

Character Generator

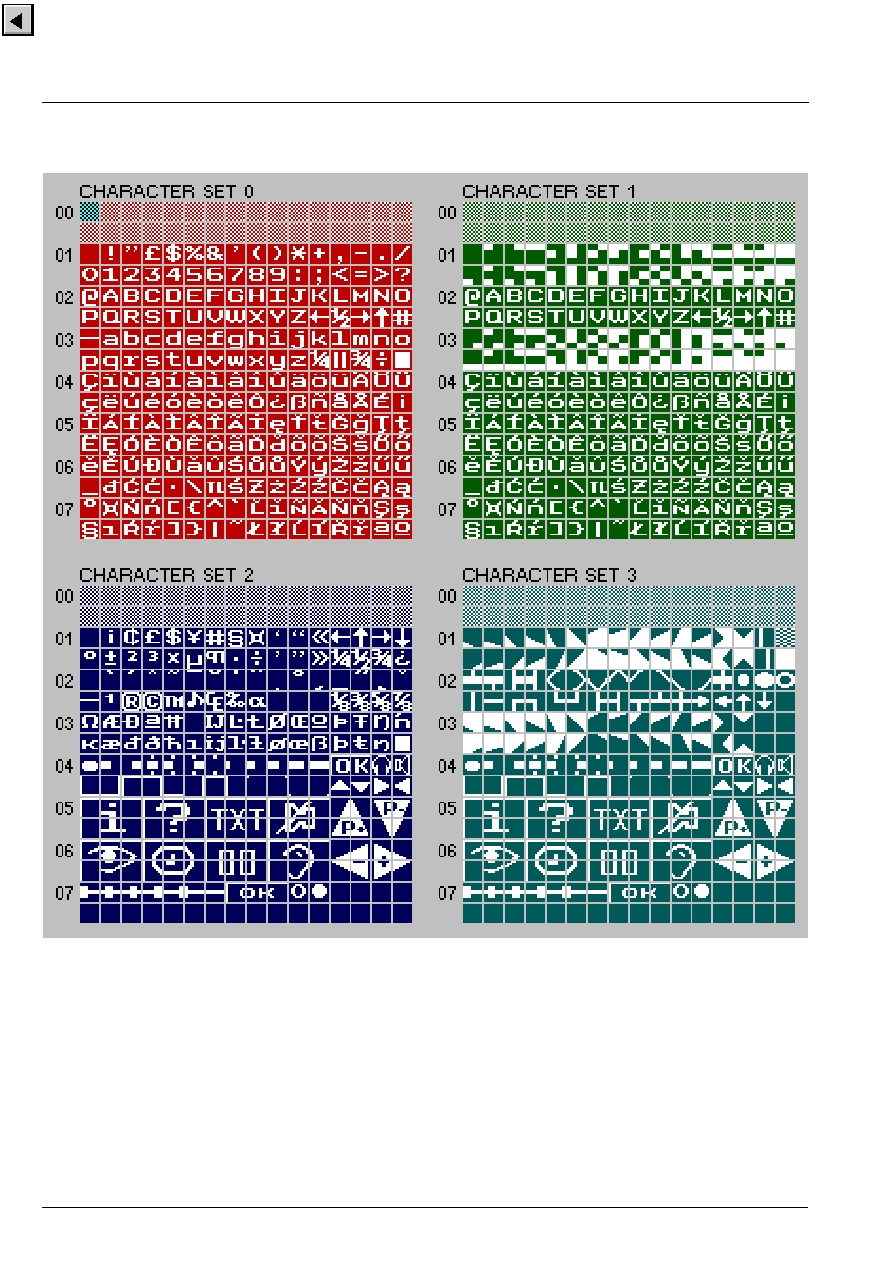

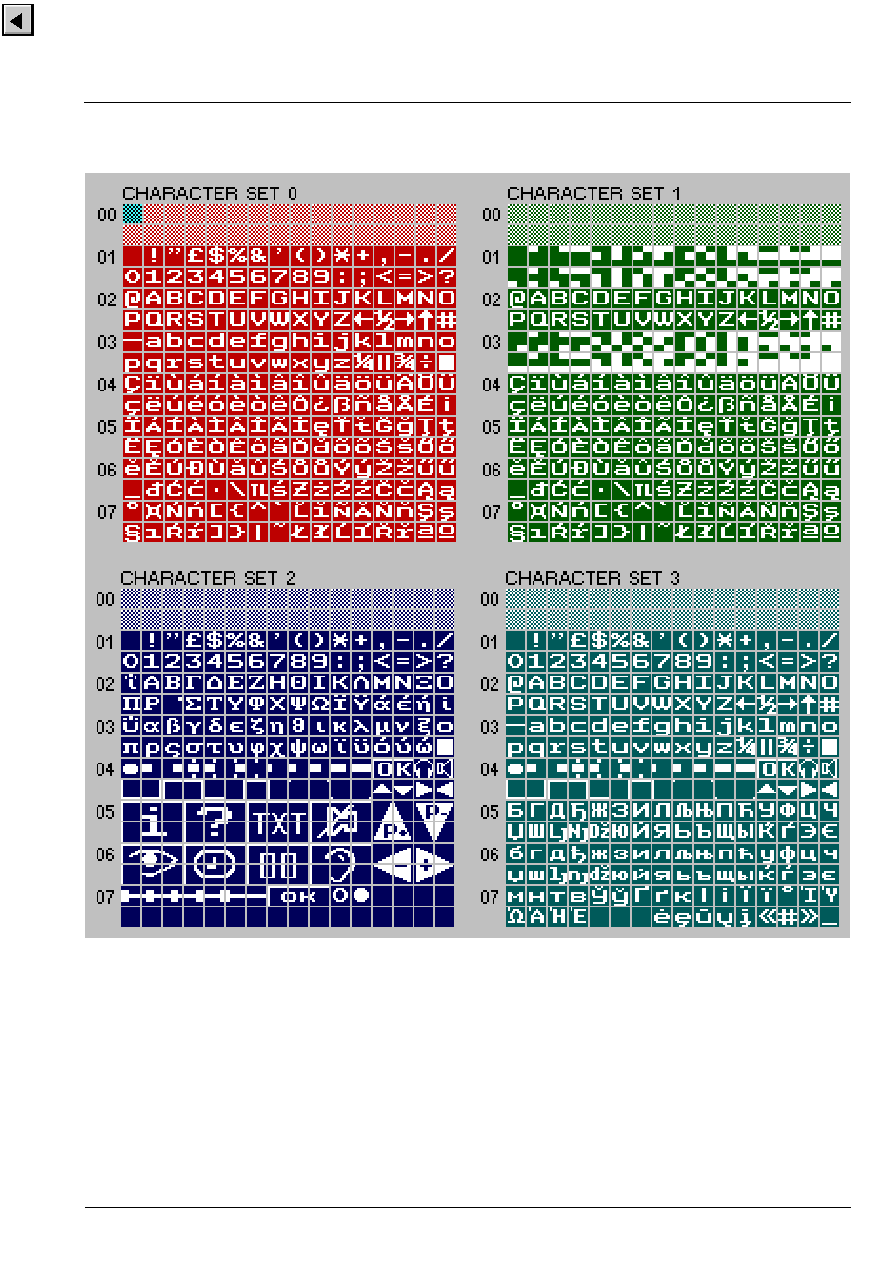

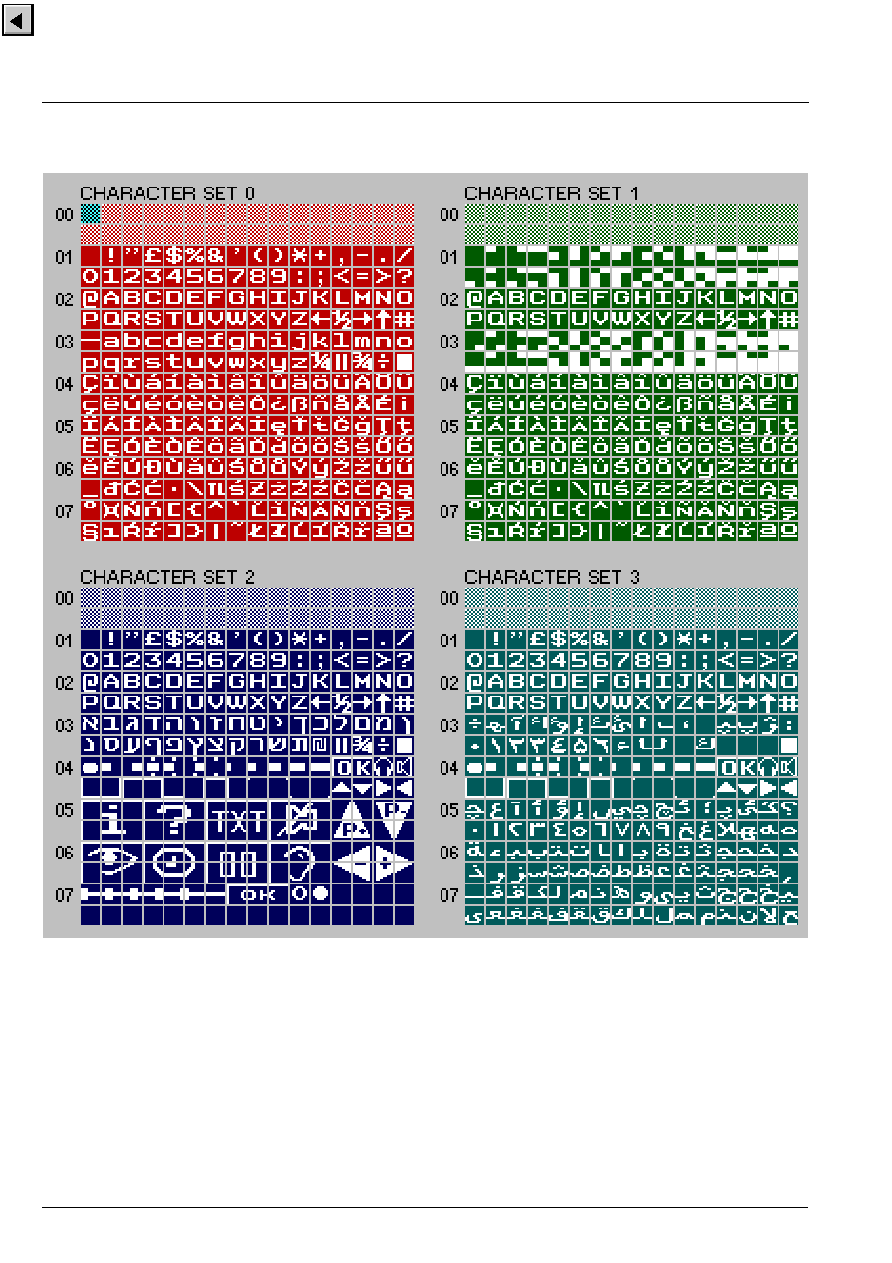

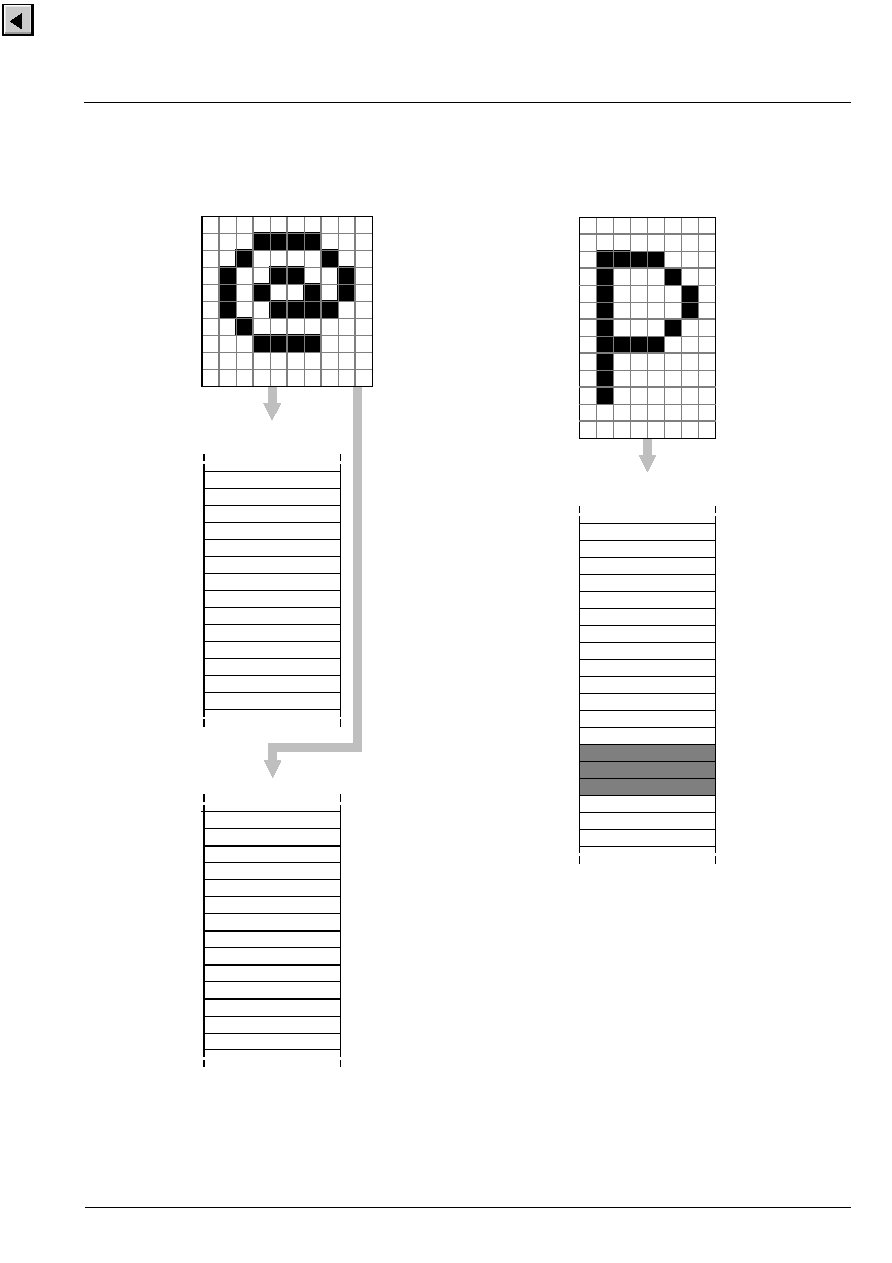

58

3.8.1.

Character Code Mapping

59

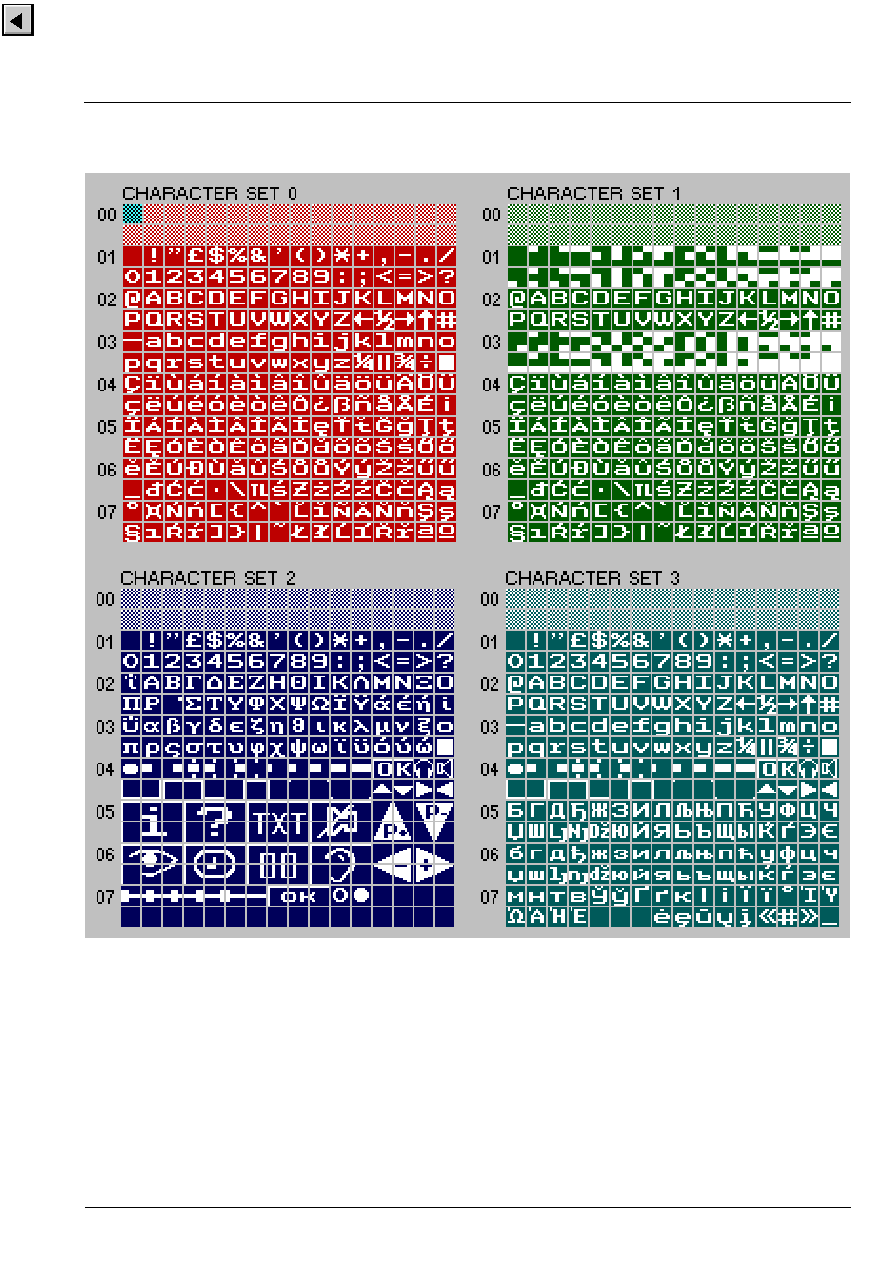

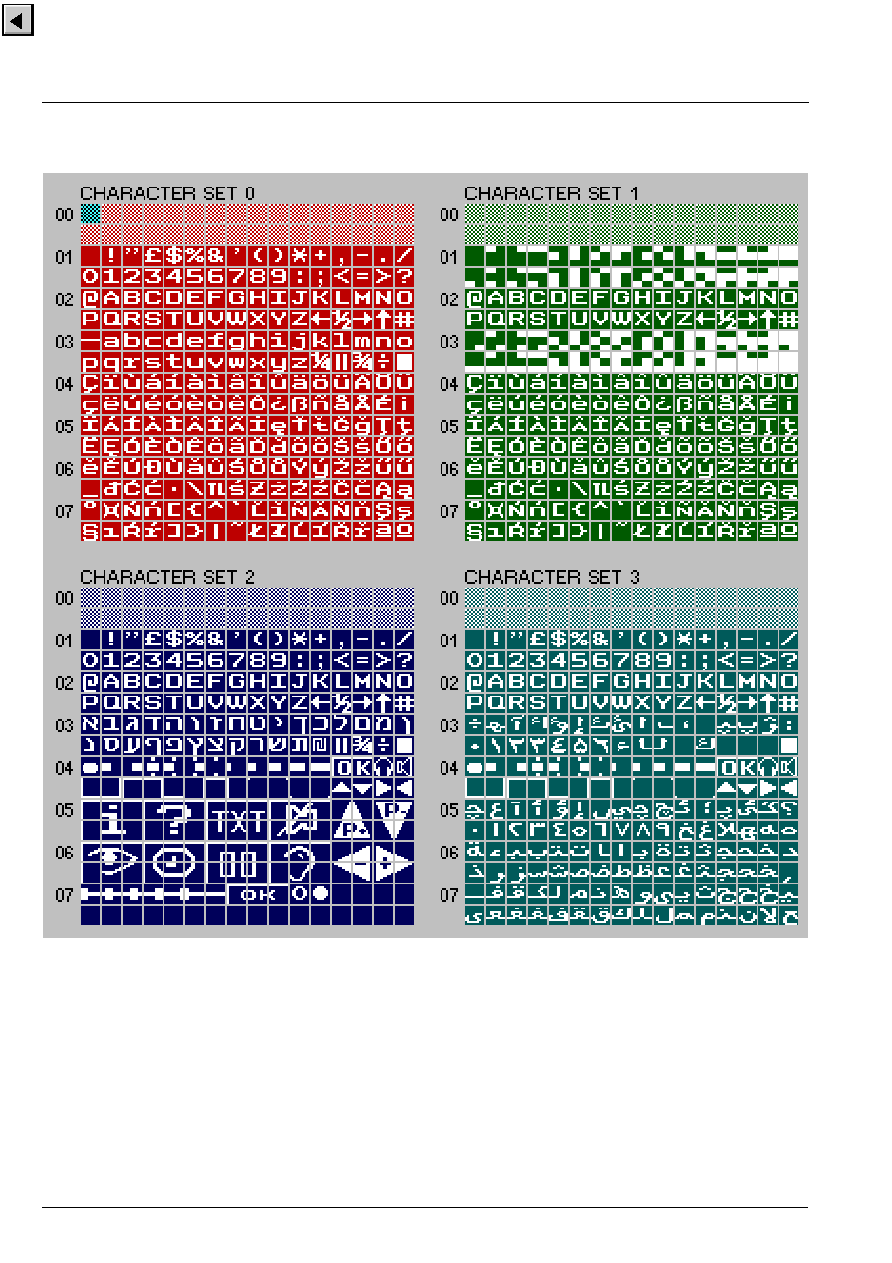

3.8.2.

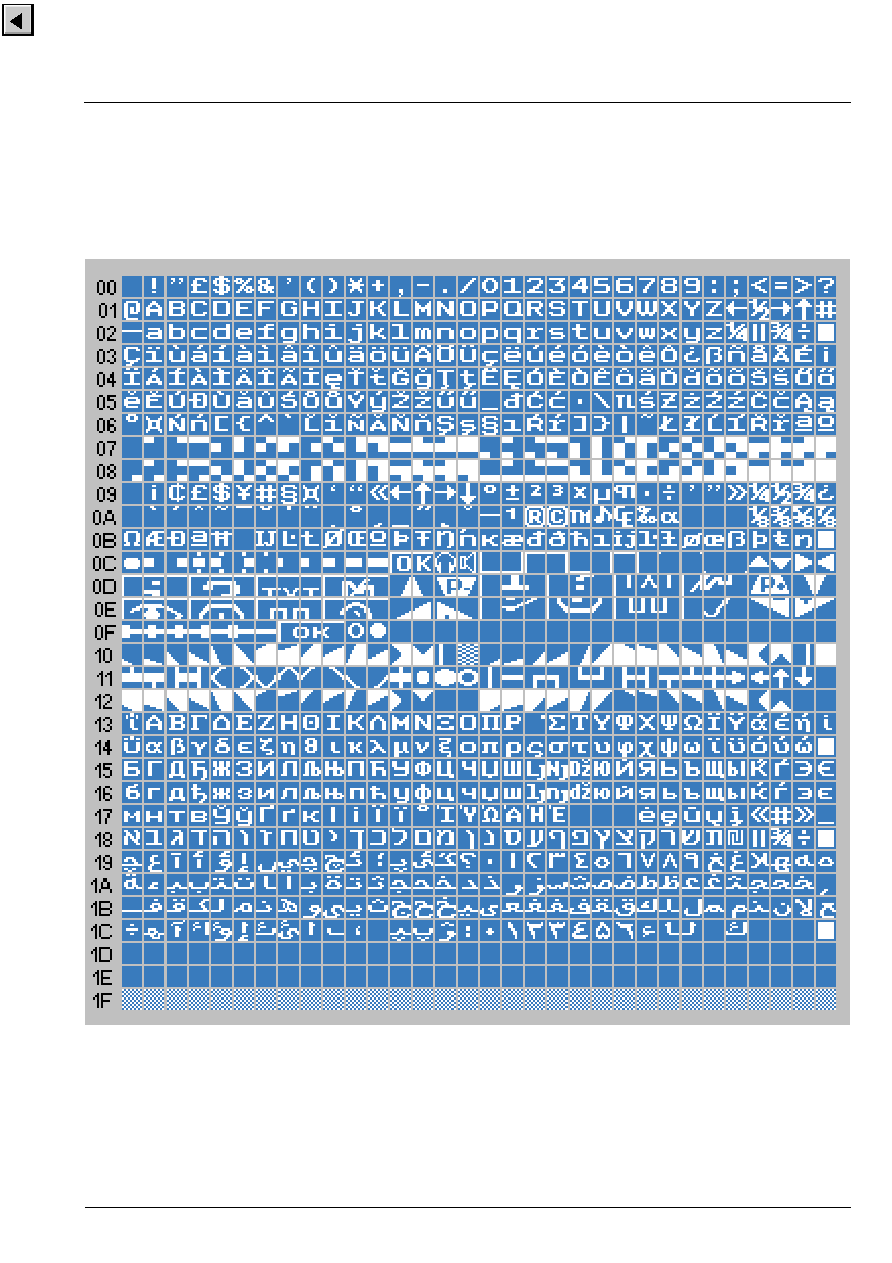

Character Font ROM

60

3.8.3.

Latin Font Mapping

61

3.8.4.

Cyrillic Font Mapping

62

3.8.5.

Arabic Font Mapping

63

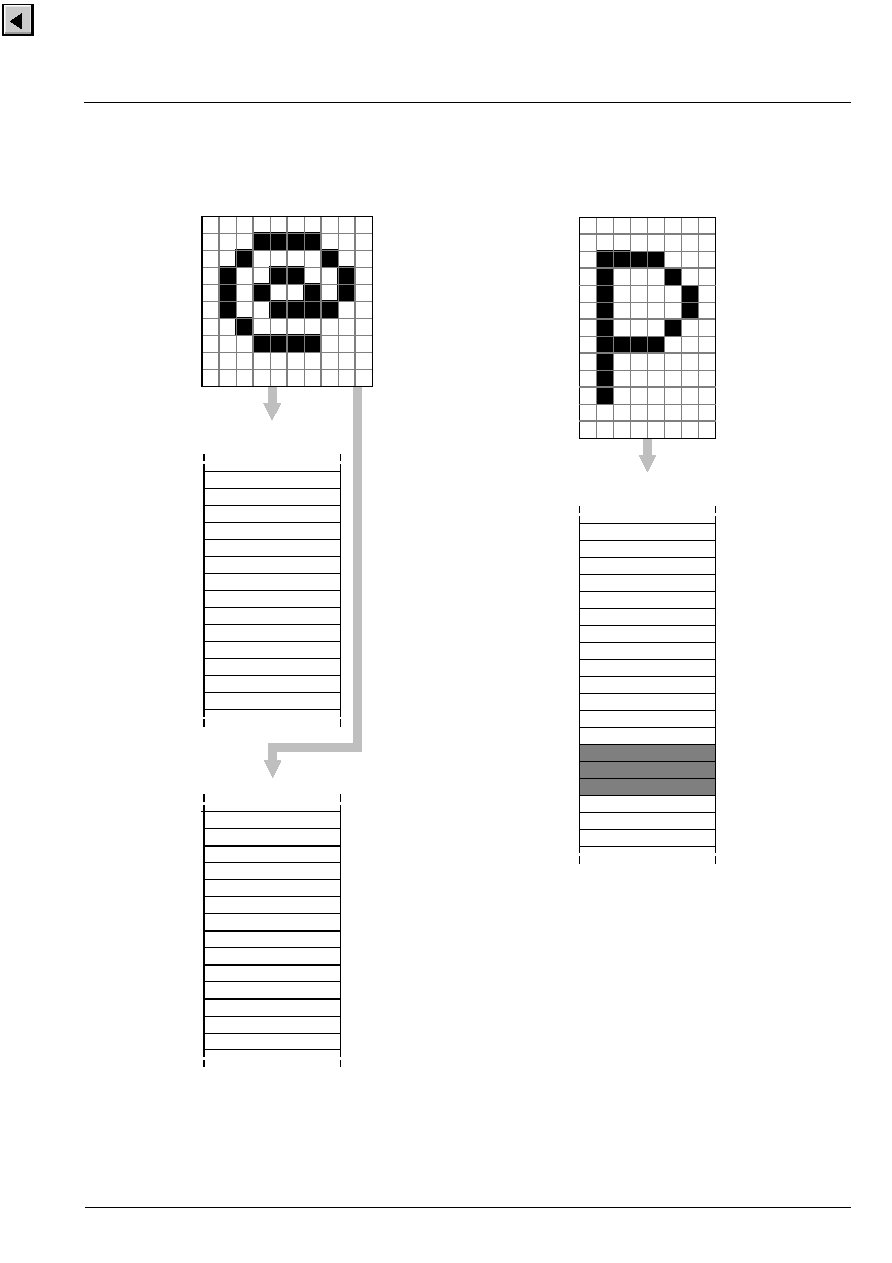

3.8.6.

Character Font Structure

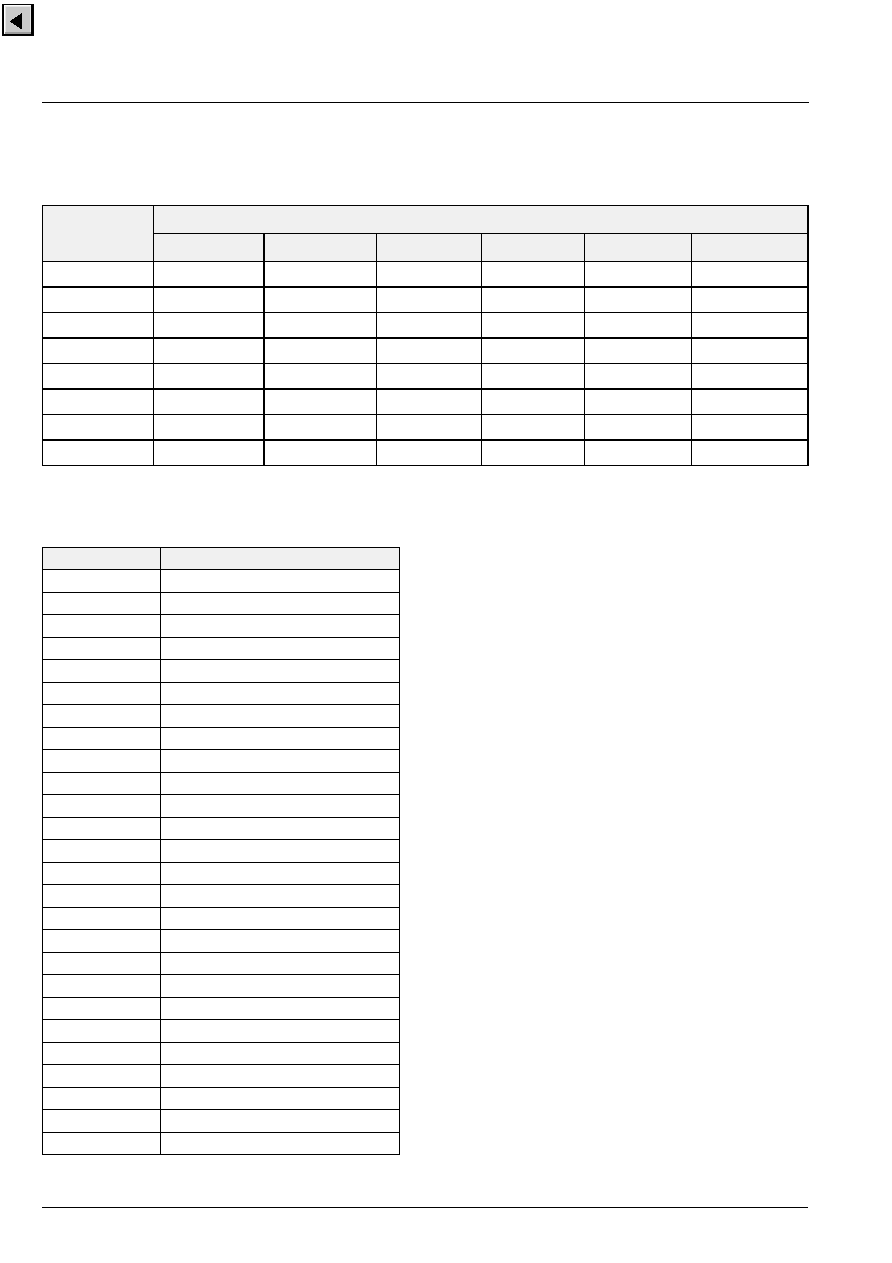

64

3.9.

National Character Mapping

66

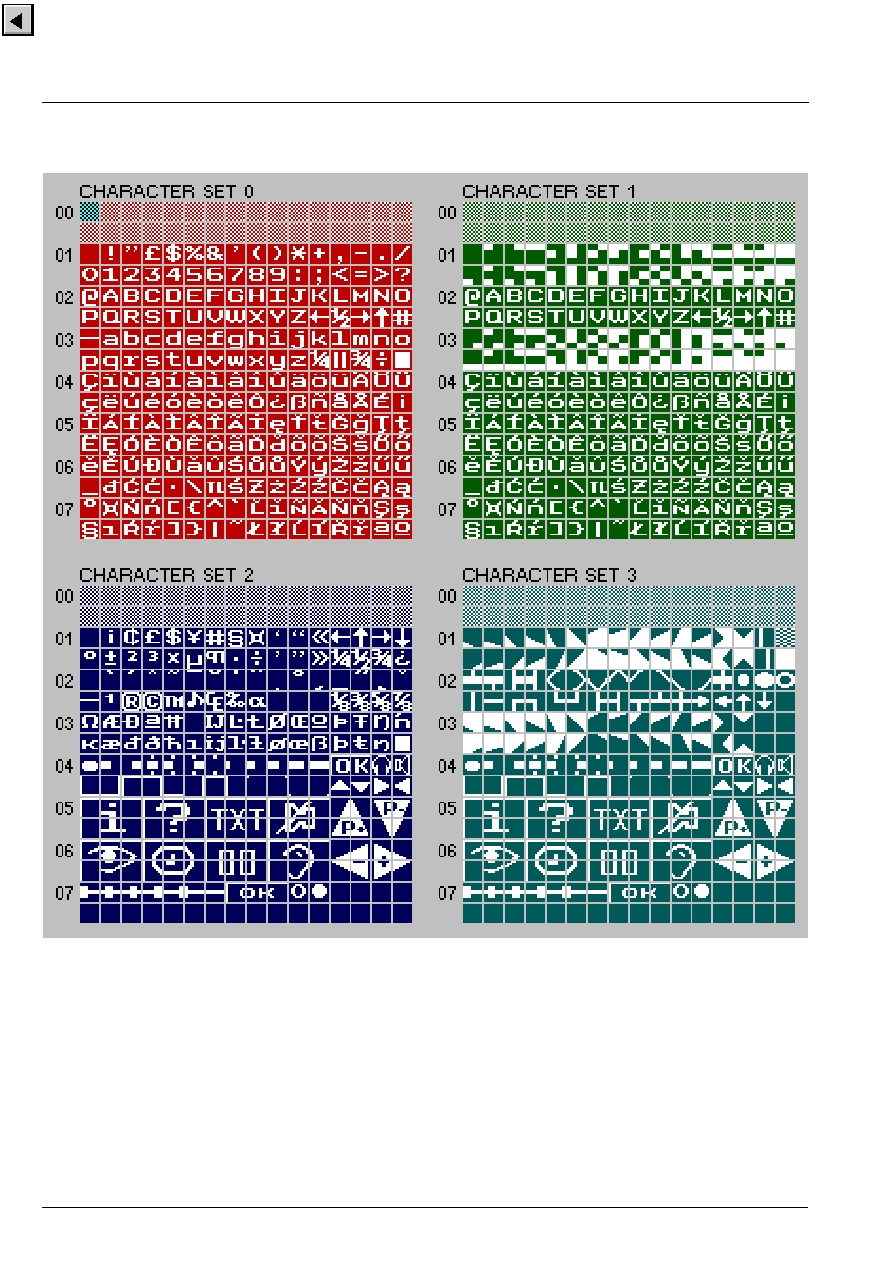

3.10.

Four-Color Mode

67

3.11.

OSD Layer

68

3.12.

Command Language

76

3.13.

I/O Register

82

3.14.

I

2

C-Bus Slave Interface

82

3.14.1.

Subaddressing

82

3.14.1.1.

CPU Subaddressing

83

3.14.1.2.

DRAM Subaddressing

83

3.14.1.3.

Command Subaddressing

83

3.14.1.4.

Data Subaddressing

84

3.14.1.5.

Hardware Identification

VCT 38xxA

ADVANCE INFORMATION

4

Micronas

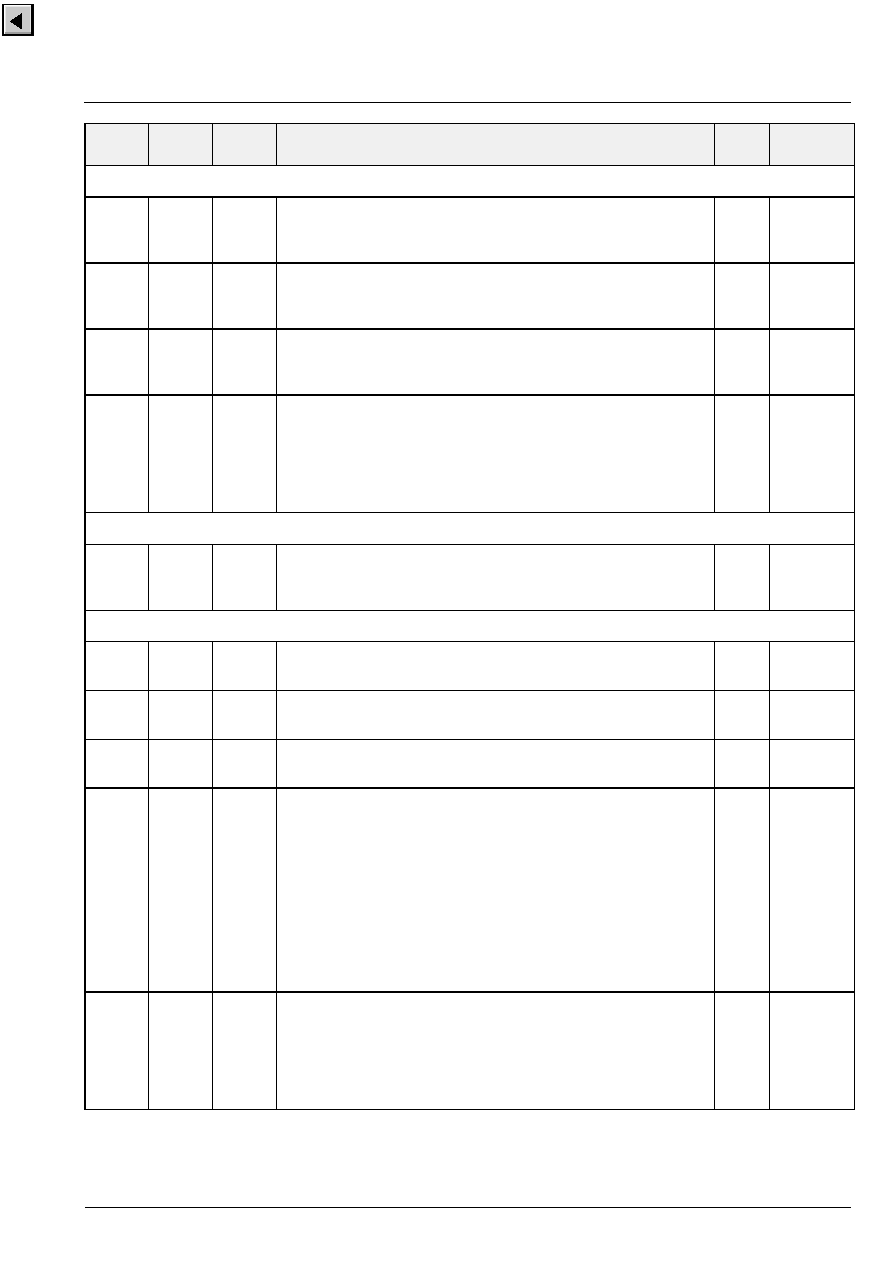

Contents, continued

Page

Section

Title

85

4.

Audio Processing

85

4.1.

Introduction

85

4.2.

Input Select

85

4.3.

Volume Control

85

4.4.

I

2

C-Bus Slave Interface

86

5.

TV Controller

86

5.1.

Introduction

86

5.2.

CPU

86

5.2.1.

CPU Slow Mode

87

5.3.

RAM and ROM

87

5.3.1.

Address Map

87

5.3.2.

Bootloader

87

5.4.

Control Register

89

5.5.

Standby Registers

90

5.6.

Test Registers

90

5.7.

Reset Logic

90

5.7.1.

Alarm Function

90

5.7.2.

Software Reset

91

5.7.2.1.

From Standby into Normal Mode

91

5.7.2.2.

From Normal into Standby Mode

91

5.7.3.

Internal Reset Sources

92

5.7.3.1.

Supply Supervision

92

5.7.3.2.

Clock Supervision

93

5.7.3.3.

Watchdog

94

5.7.4.

External Reset Sources

94

5.7.5.

Summary of Module Reset States

94

5.7.6.

Reset Registers

95

5.8.

Memory Banking

95

5.8.1.

Banking Register

96

5.9.

DMA Interface

98

5.9.1.

DMA Registers

99

5.10.

Interrupt Controller

99

5.10.1.

Features

99

5.10.2.

General

99

5.10.3.

Initialization

99

5.10.4.

Operation

99

5.10.5.

Inactivation

101

5.10.6.

Precautions

101

5.10.7.

Interrupt Registers

103

5.10.8.

Interrupt Assignment

103

5.10.8.1.

Interrupt Multiplexer

104

5.10.9.

Port Interrupt Module

106

5.10.10.

Interrupt Timing

107

5.11.

Memory Patch Module

107

5.11.1.

Features

107

5.11.2.

General

107

5.11.3.

Initialization

108

5.11.4.

Patch Operation

108

5.11.5.

Patch Registers

109

5.12.

I

2

C-Bus Master Interface

111

5.12.1.

I2C Bus Master Interface Registers

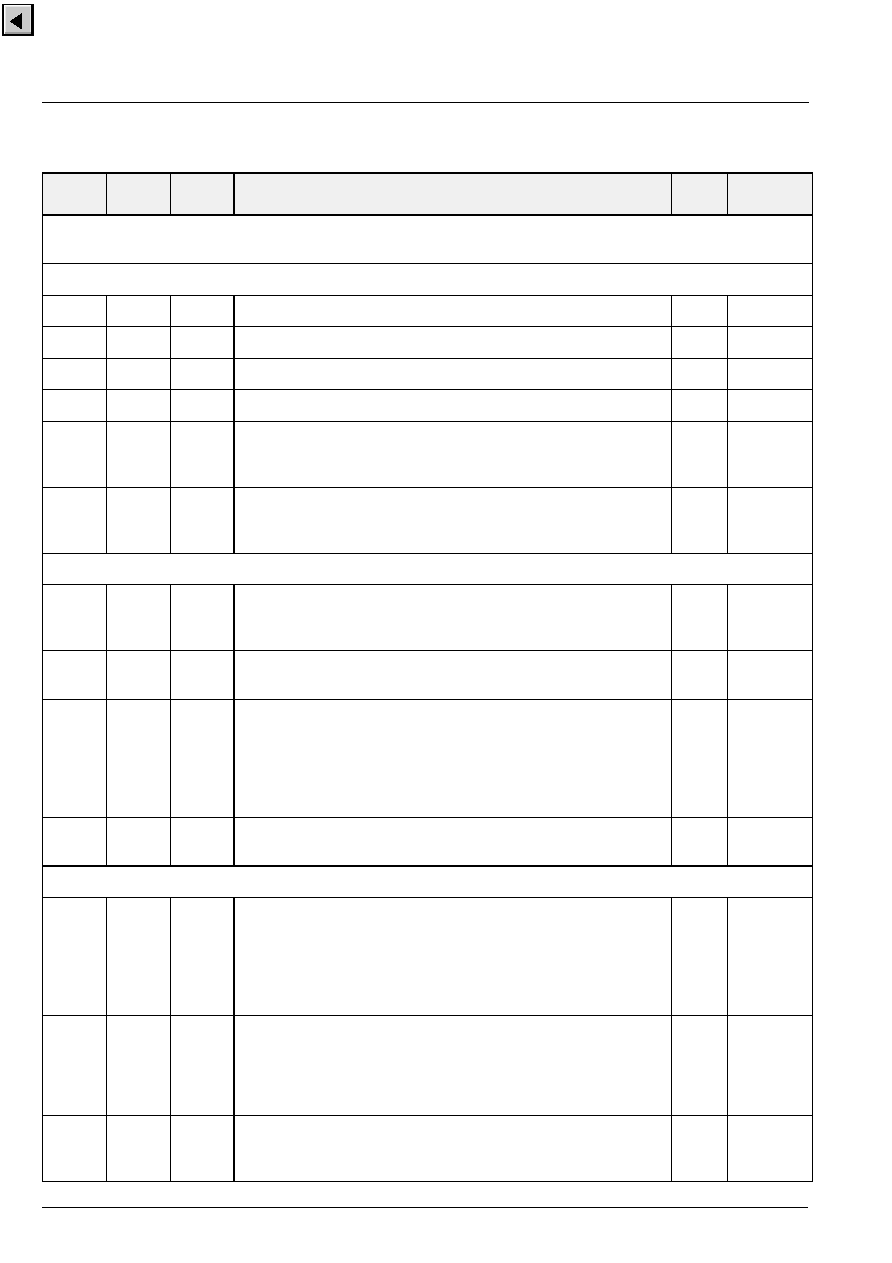

Contents, continued

Page

Section

Title

ADVANCE INFORMATION

VCT 38xxA

Micronas

5

113

5.13.

Timer T0 and T1

113

5.13.1.

Features

113

5.13.2.

Operation

114

5.13.3.

Timer Registers

115

5.14.

Capture Compare Module (CAPCOM)

115

5.14.1.

Features

116

5.14.2.

Initialization

116

5.14.3.

Operation of CCC

116

5.14.3.1.

Operation of Subunit

117

5.14.4.

Inactivation

118

5.14.5.

CAPCOM Registers

120

5.15.

Pulse Width Modulator

120

5.15.1.

Features

120

5.15.2.

General

120

5.15.3.

Initialization

120

5.15.4.

Operation

120

5.15.5.

PWM Registers

121

5.16.

Tuning Voltage Pulse Width Modulator

121

5.16.1.

Features

121

5.16.2.

General

122

5.16.3.

Initialization

122

5.16.4.

Operation

122

5.16.5.

TVPWM Registers

123

5.17.

A/D Converter (ADC)

123

5.17.1.

Features

123

5.17.2.

Operation

124

5.17.3.

Measurement Errors

124

5.17.4.

Comparator

125

5.17.5.

ADC Registers

126

5.18.

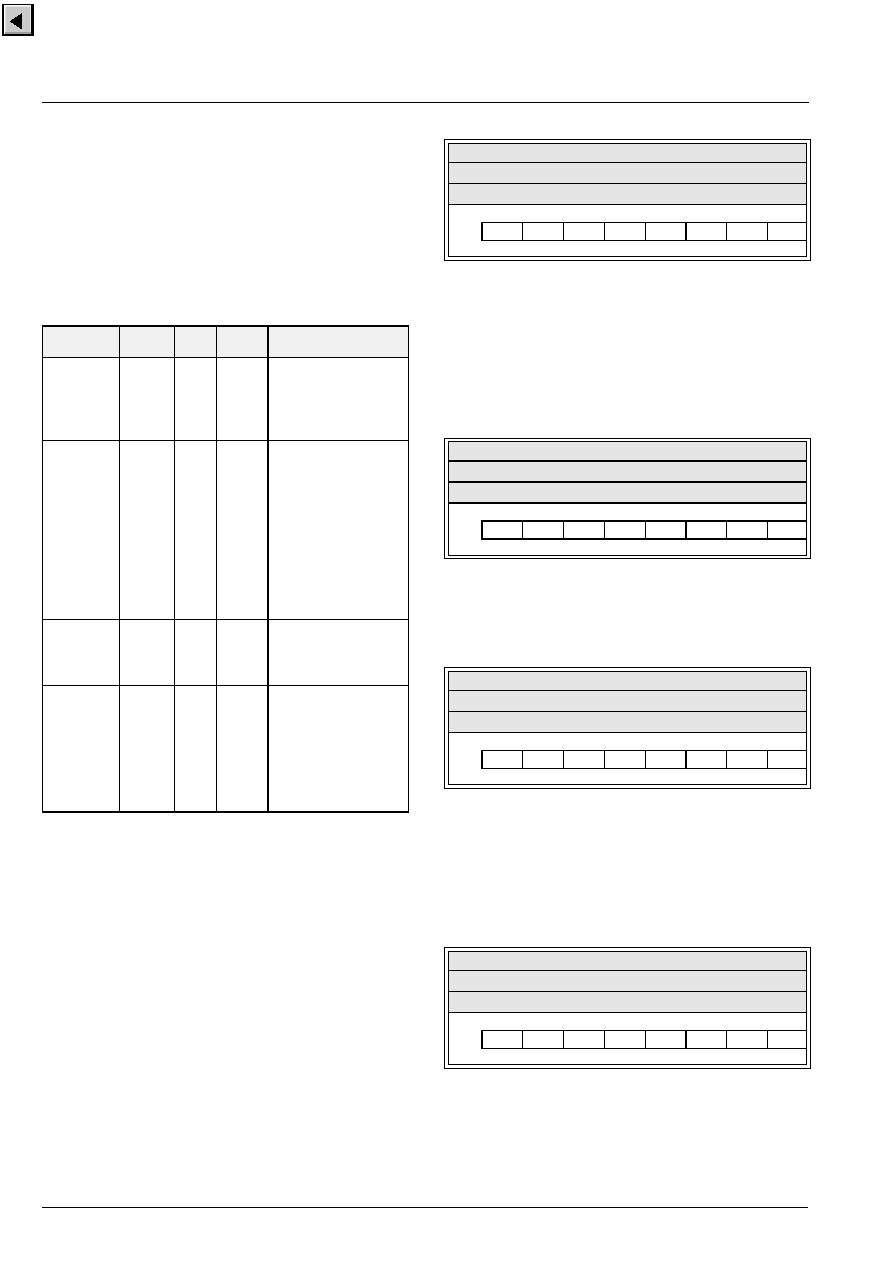

Ports

126

5.18.1.

Port Assignment

127

5.18.2.

Universal Ports P1 to P3

127

5.18.2.1.

Features

128

5.18.2.2.

Universal Port Mode

128

5.18.3.

Universal Port Registers

129

5.18.4.

I

2

C Ports P40 and P41

129

5.18.4.1.

Features

130

5.18.5.

Audio Ports P42 to P46

130

5.18.5.1.

Features

131

5.18.6.

CLK20 Output Port

131

5.18.6.1.

Features

132

5.19.

I/O Register Cross Reference

VCT 38xxA

ADVANCE INFORMATION

6

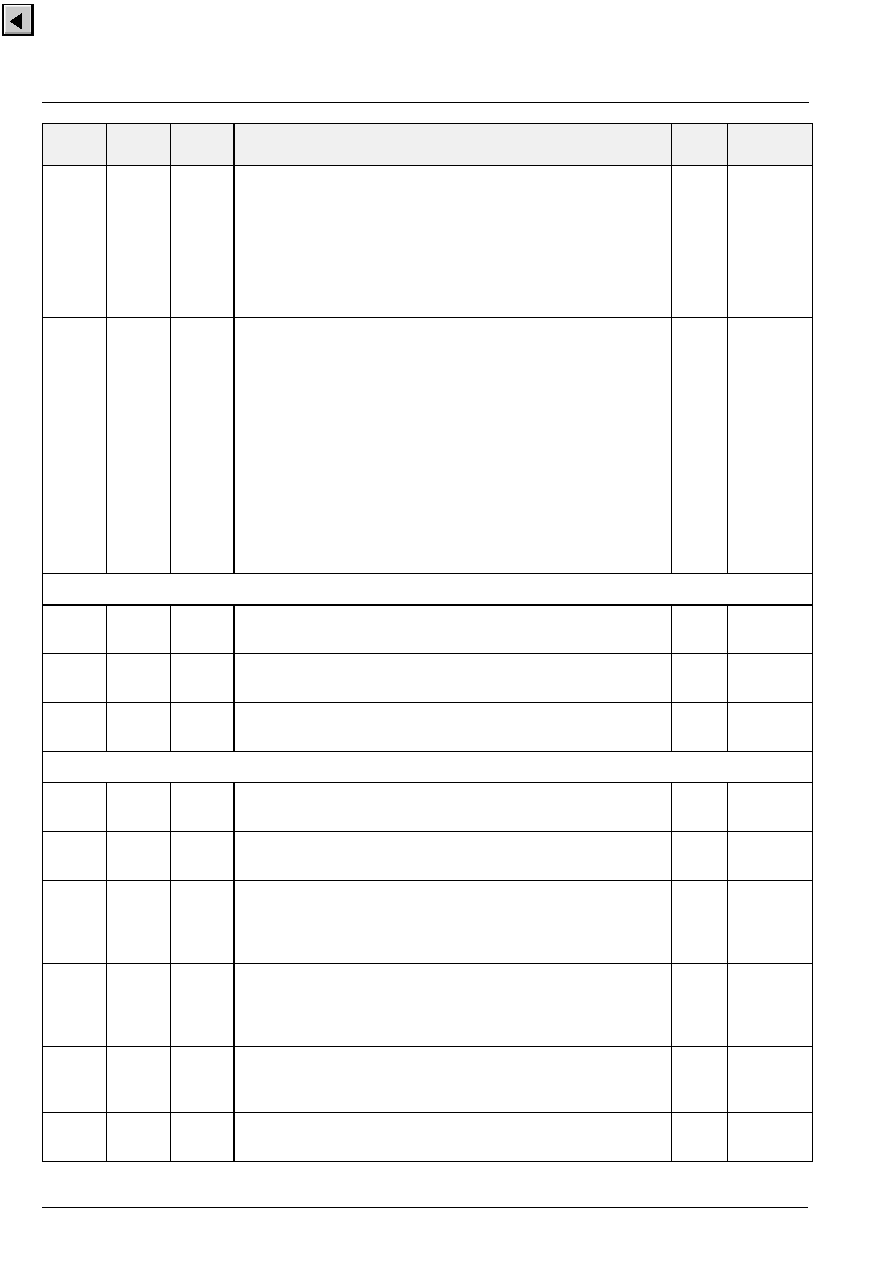

Micronas

Contents, continued

Page

Section

Title

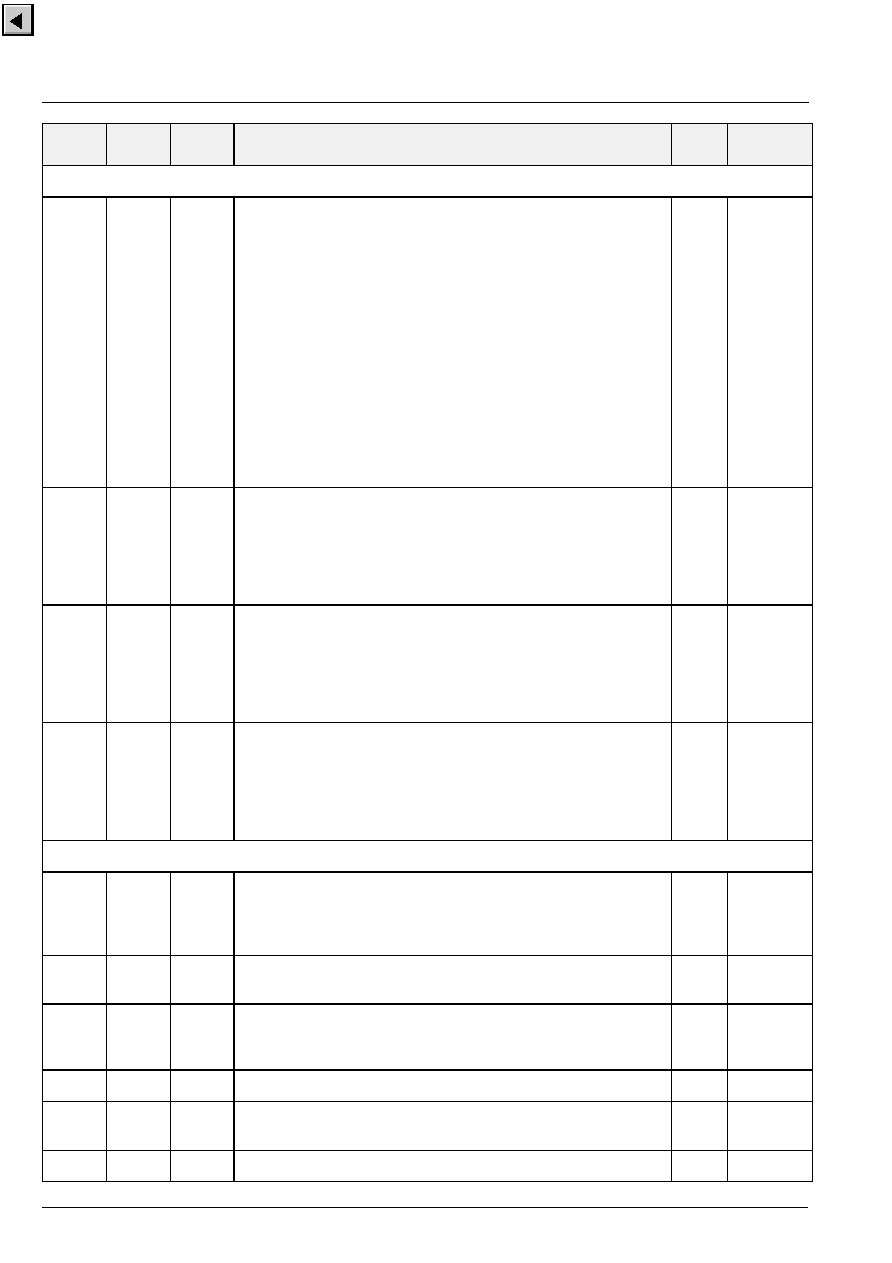

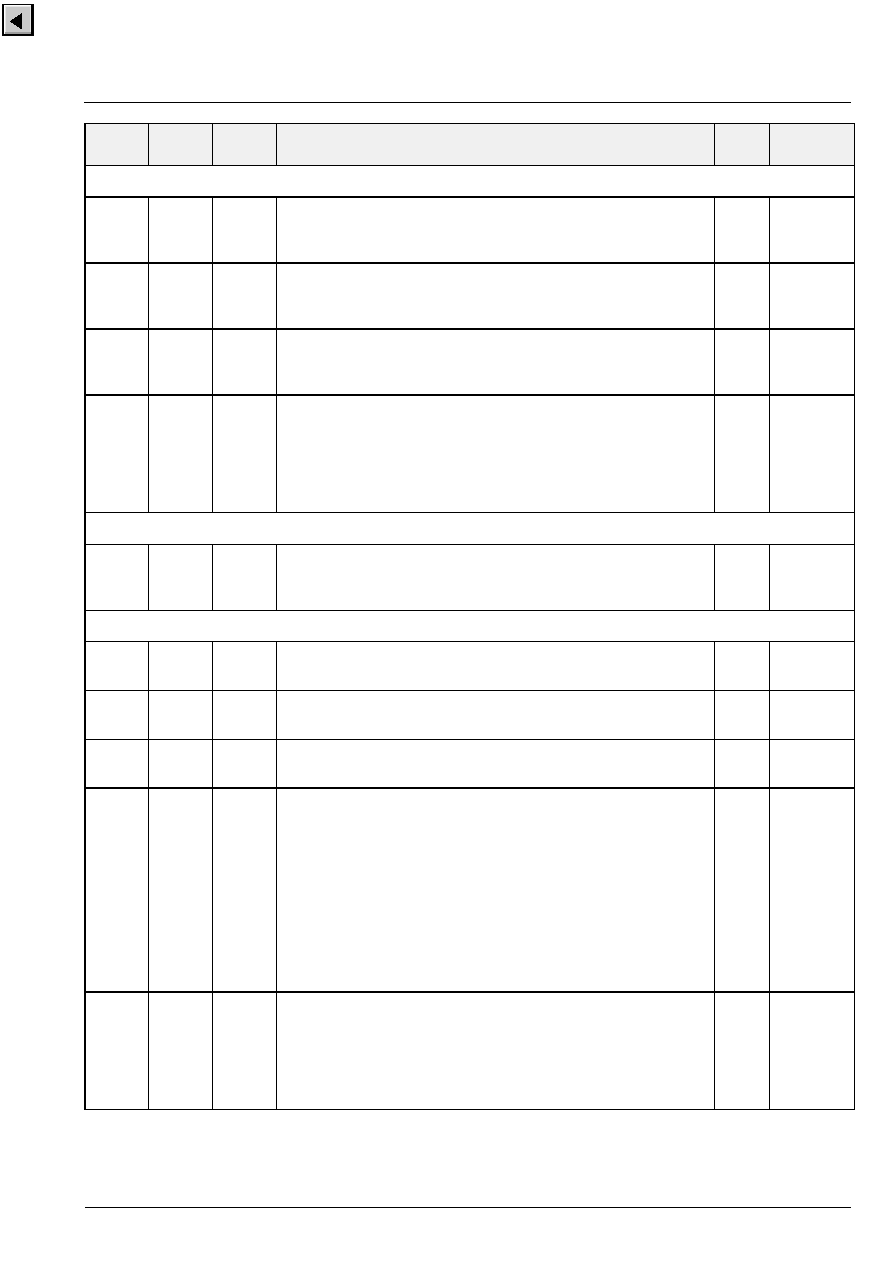

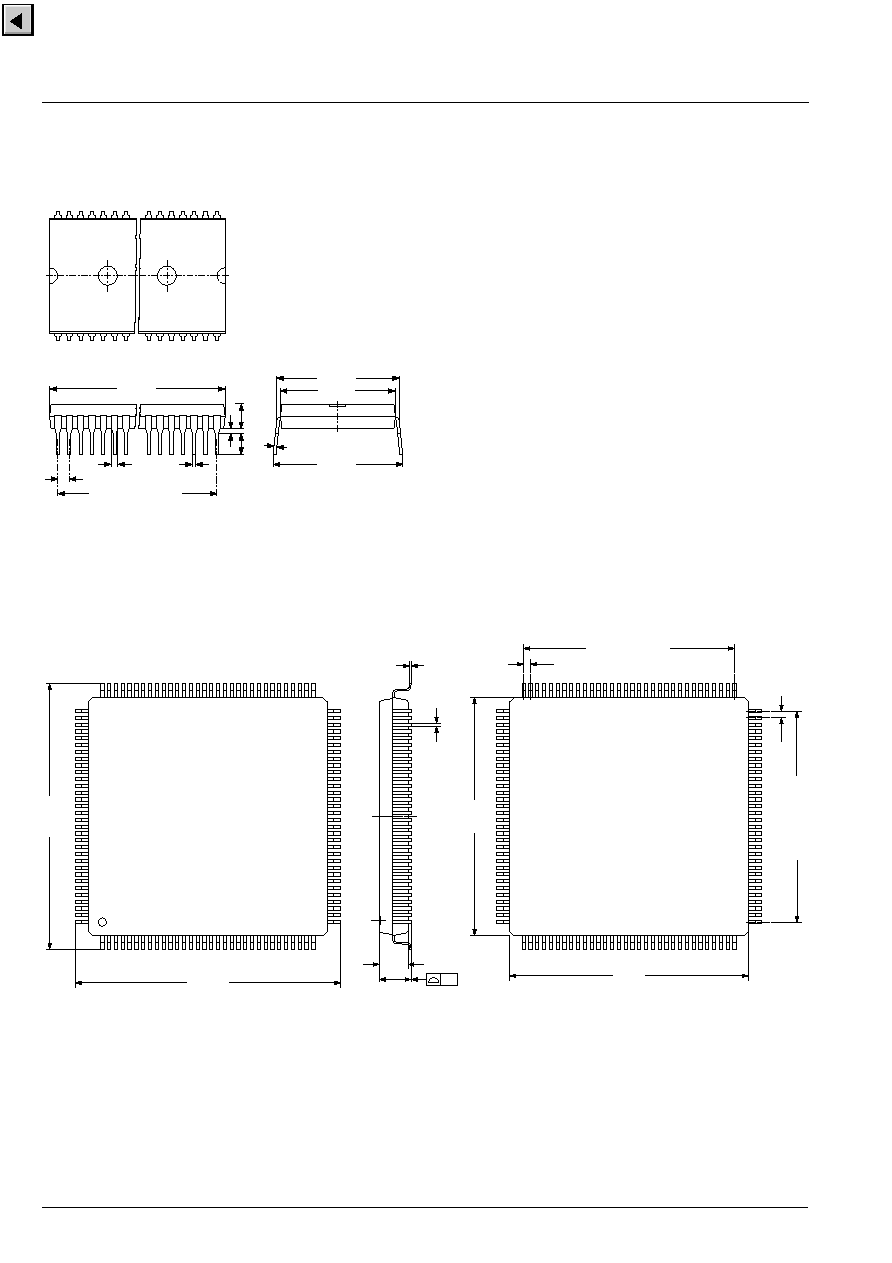

136

6.

Specifications

136

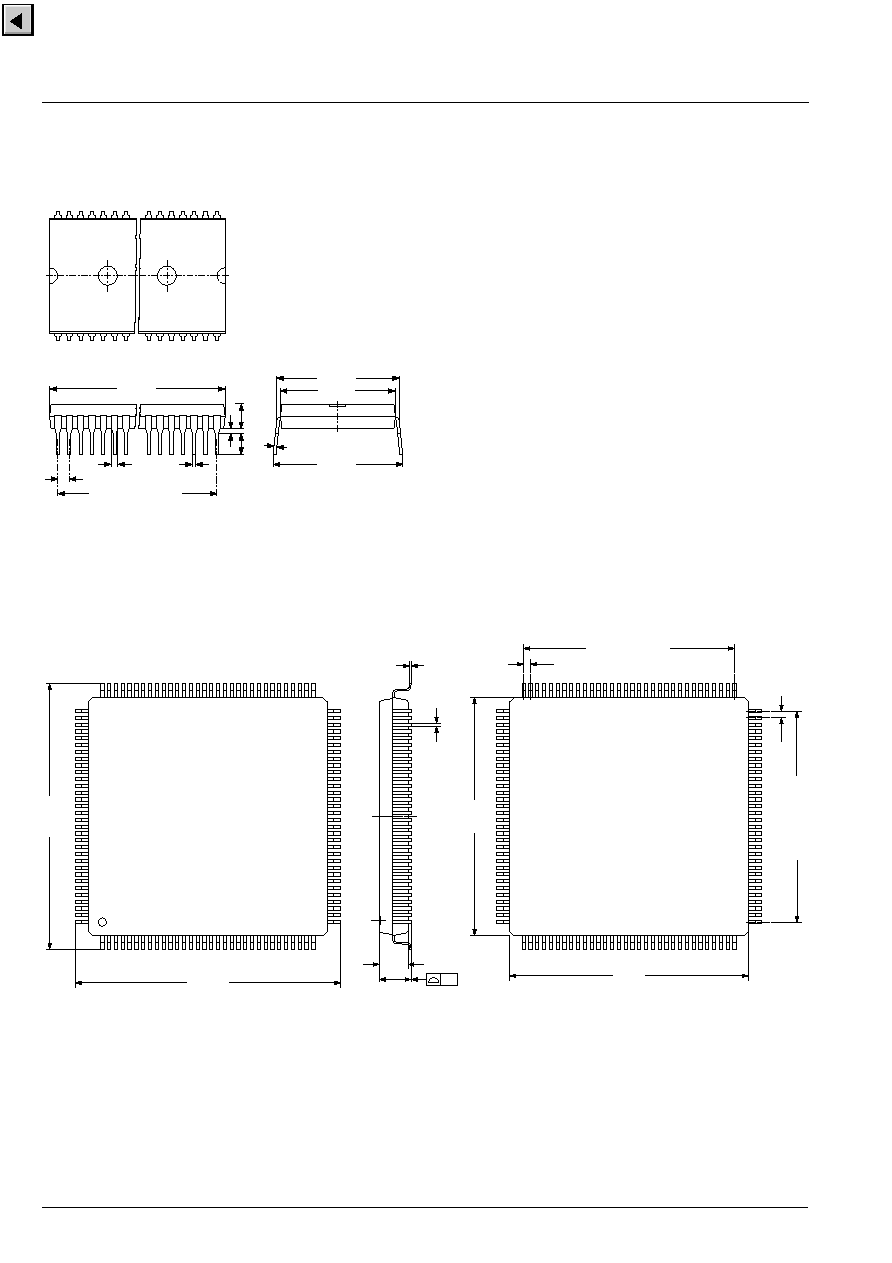

6.1.

Outline Dimensions

138

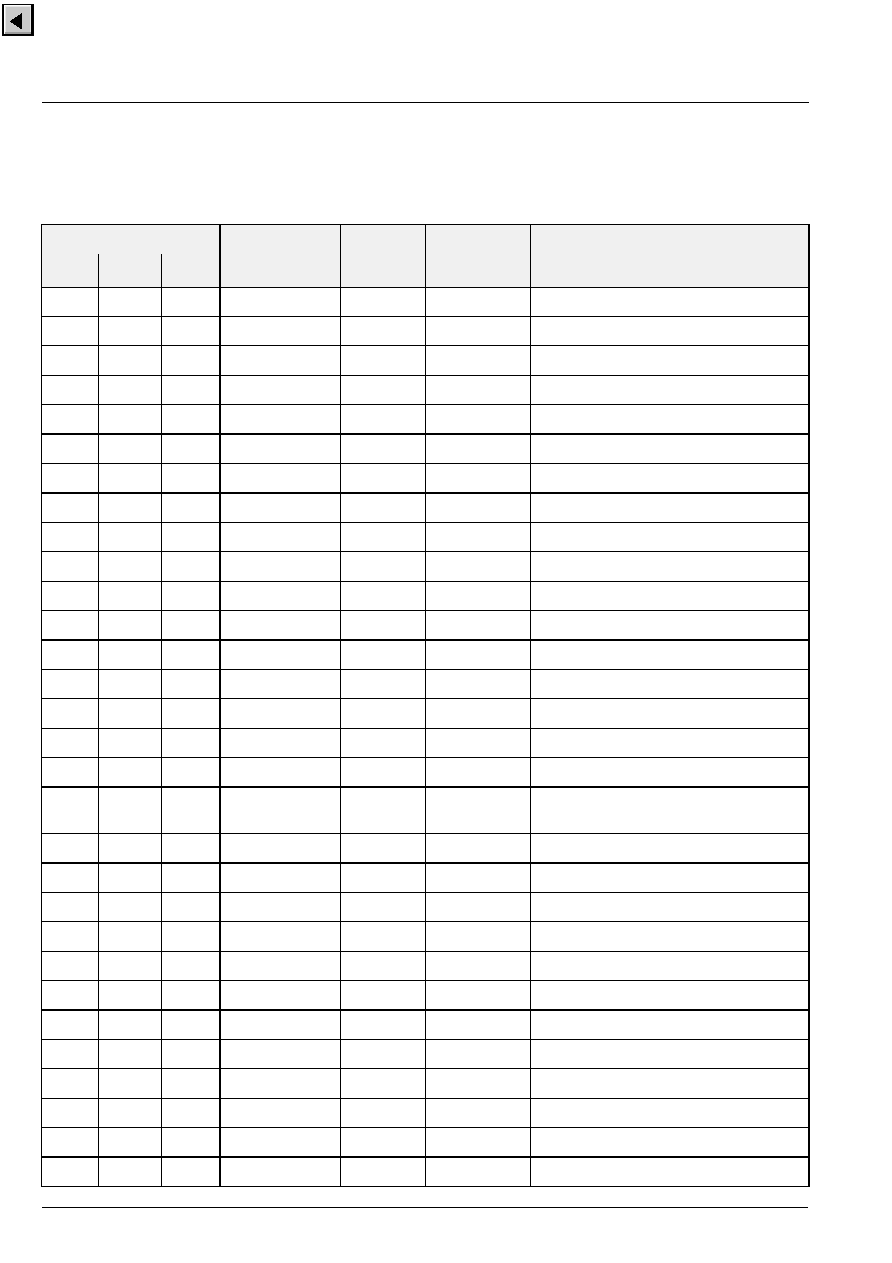

6.2.

Pin Connections and Short Descriptions

142

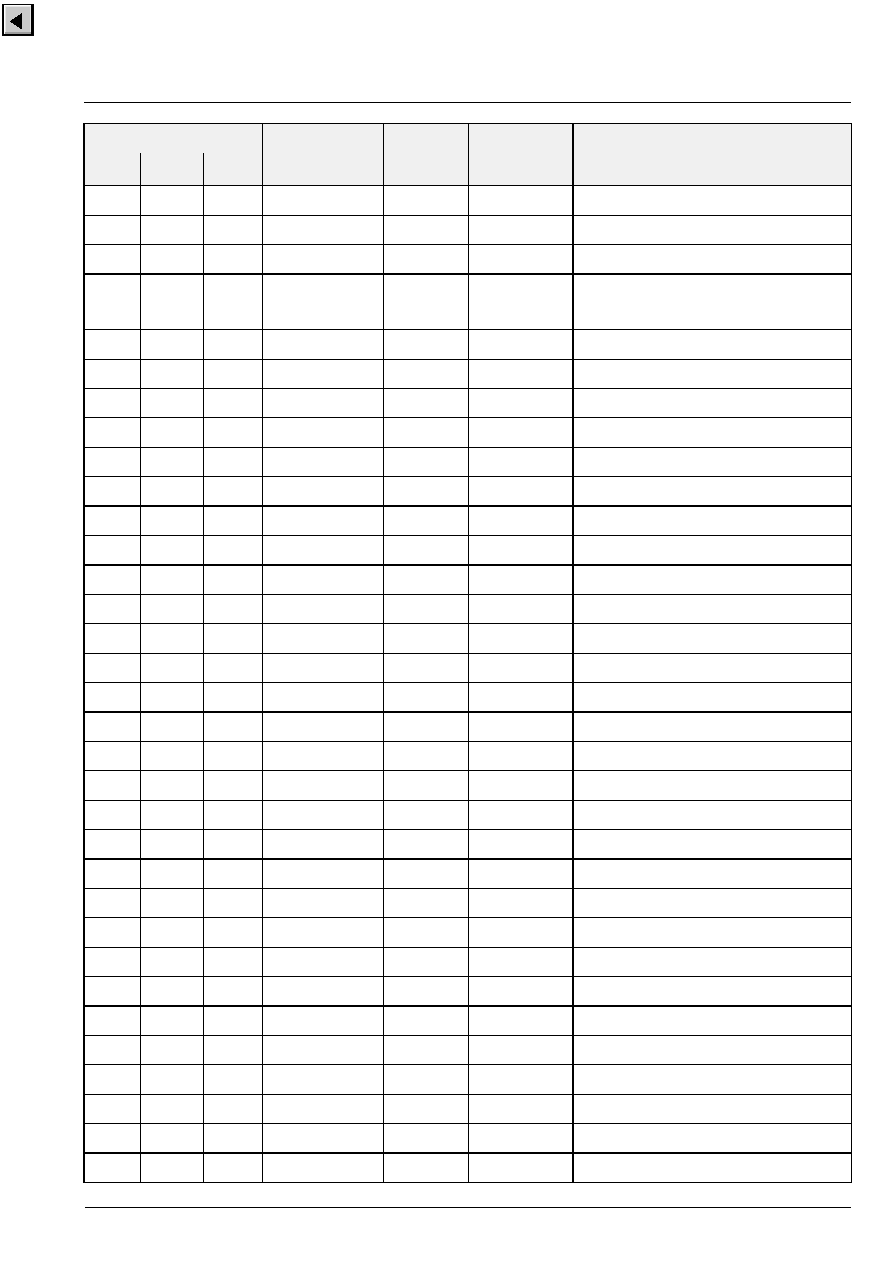

6.3.

Pin Descriptions for PSDIP64 package

144

6.4.

Pin Descriptions for PMQFP128 package

145

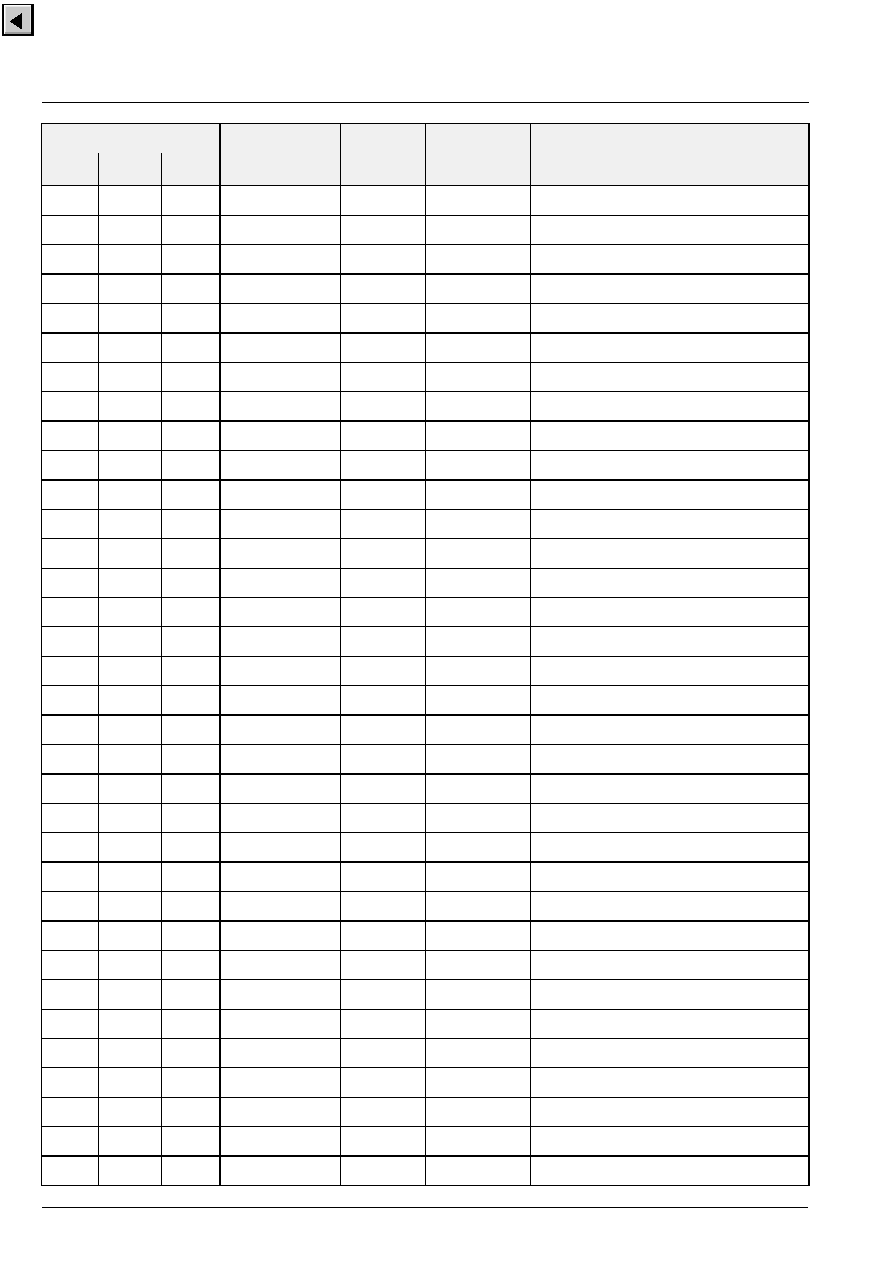

6.5.

Pin Configuration

147

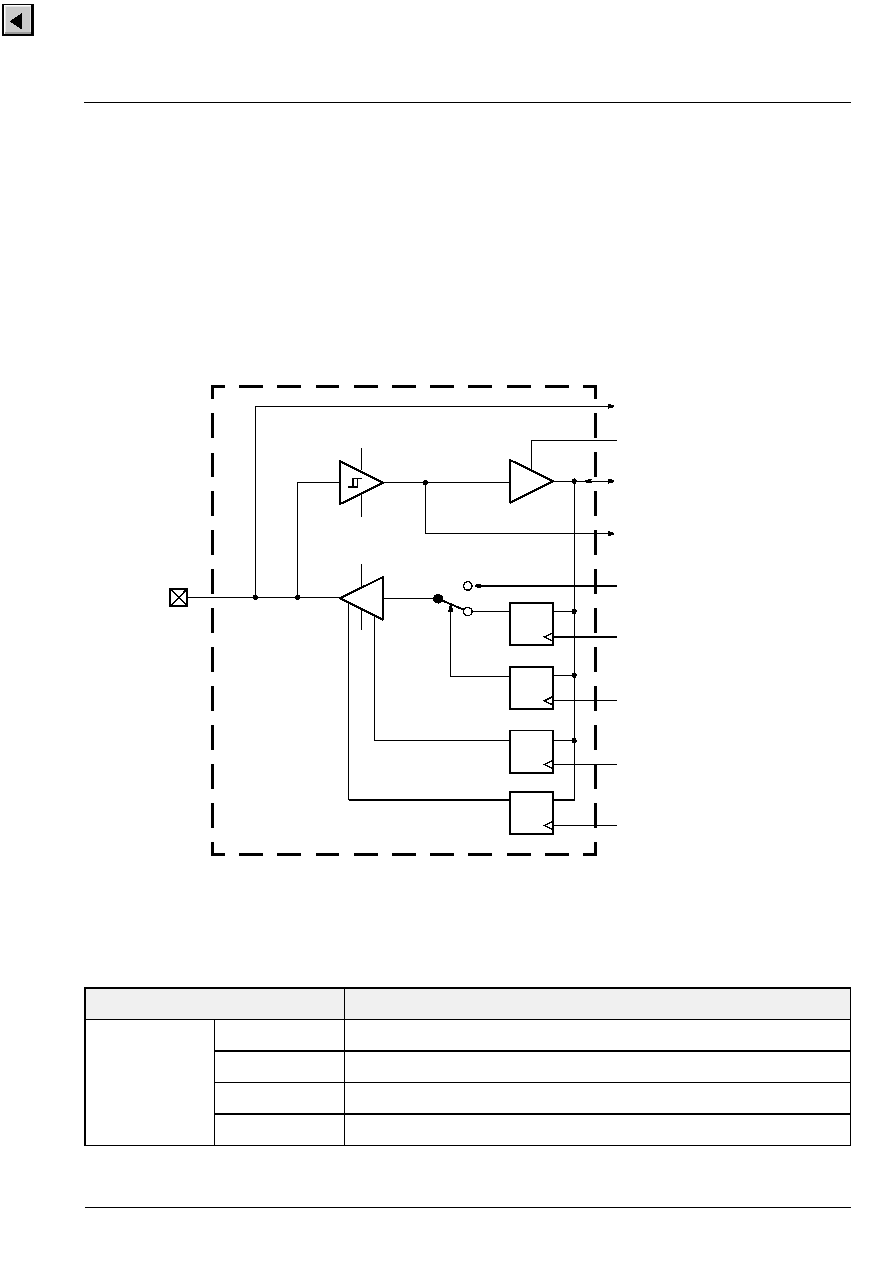

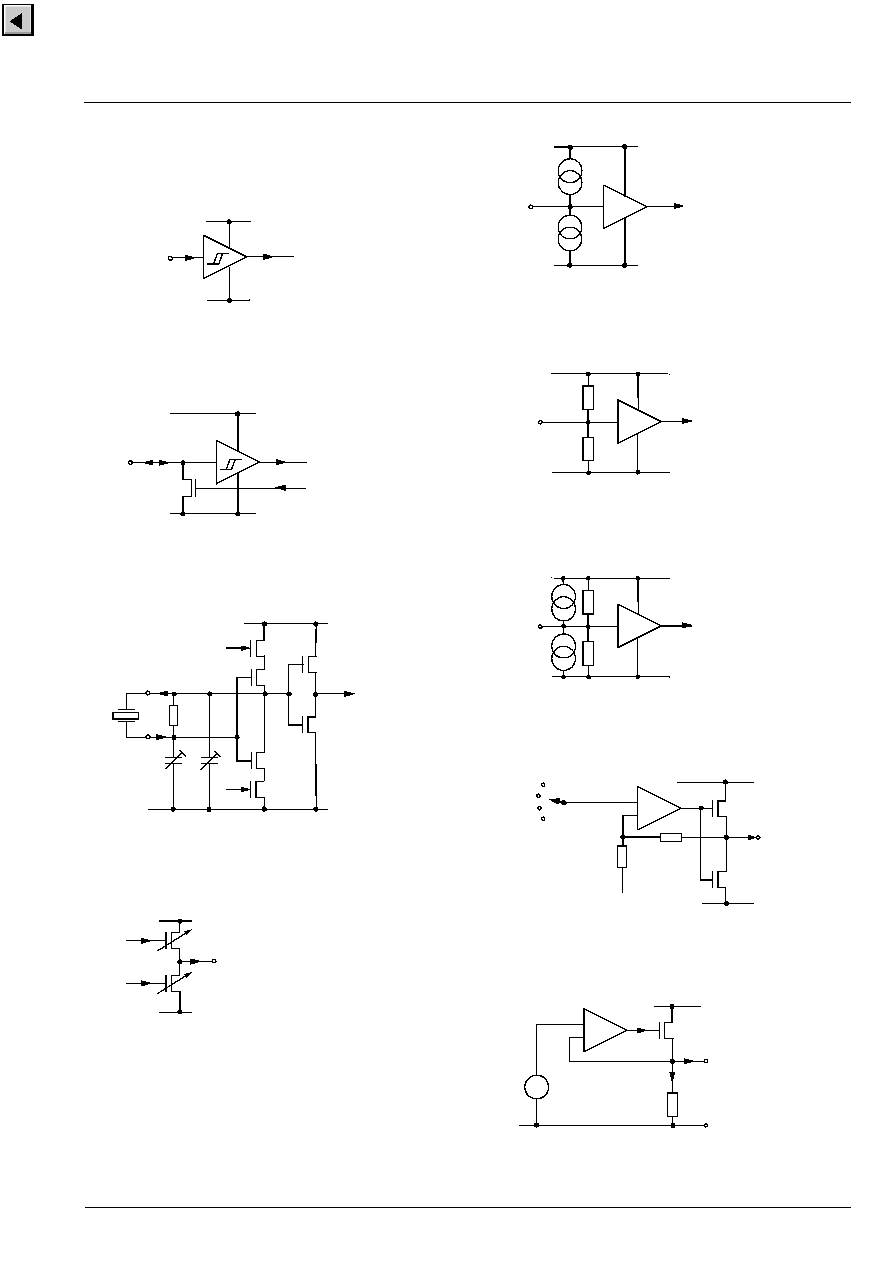

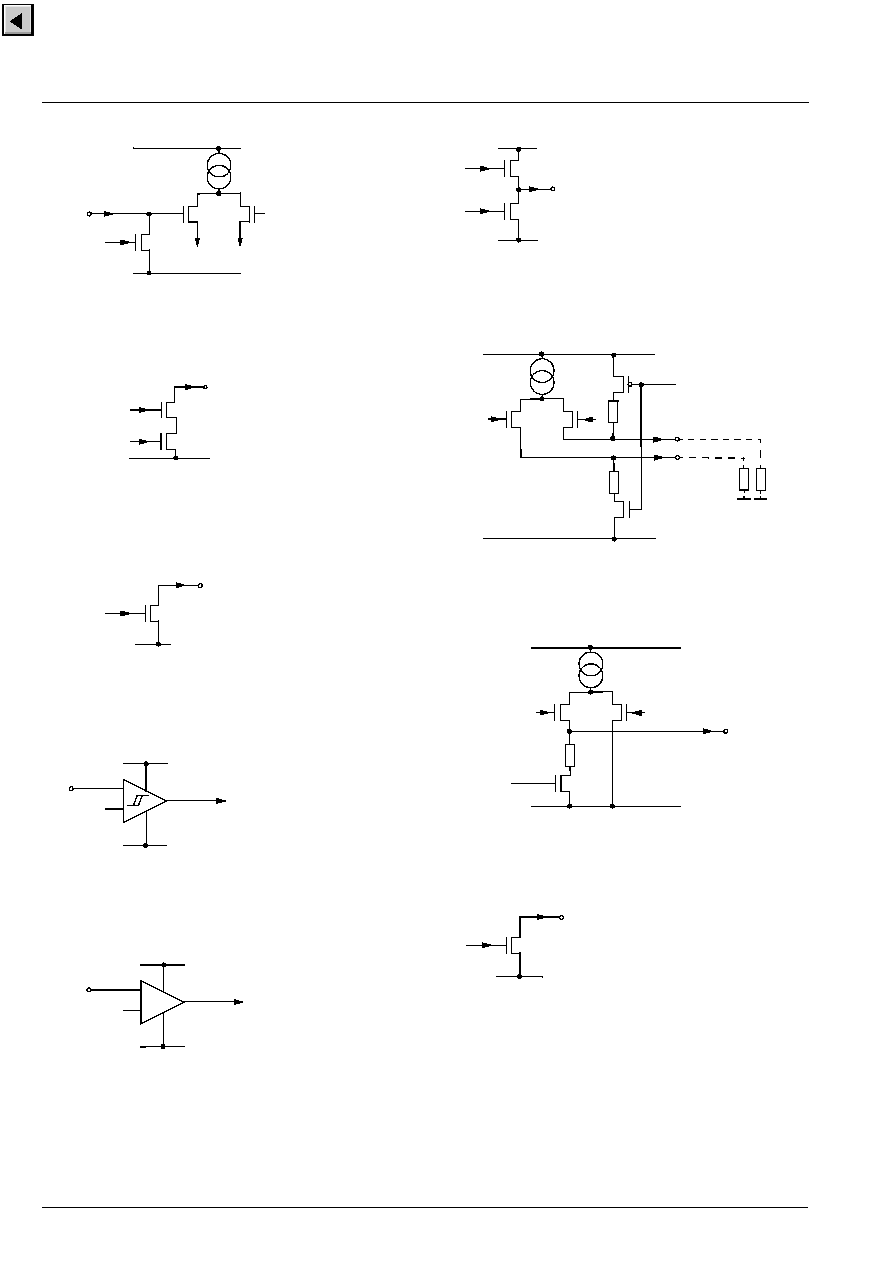

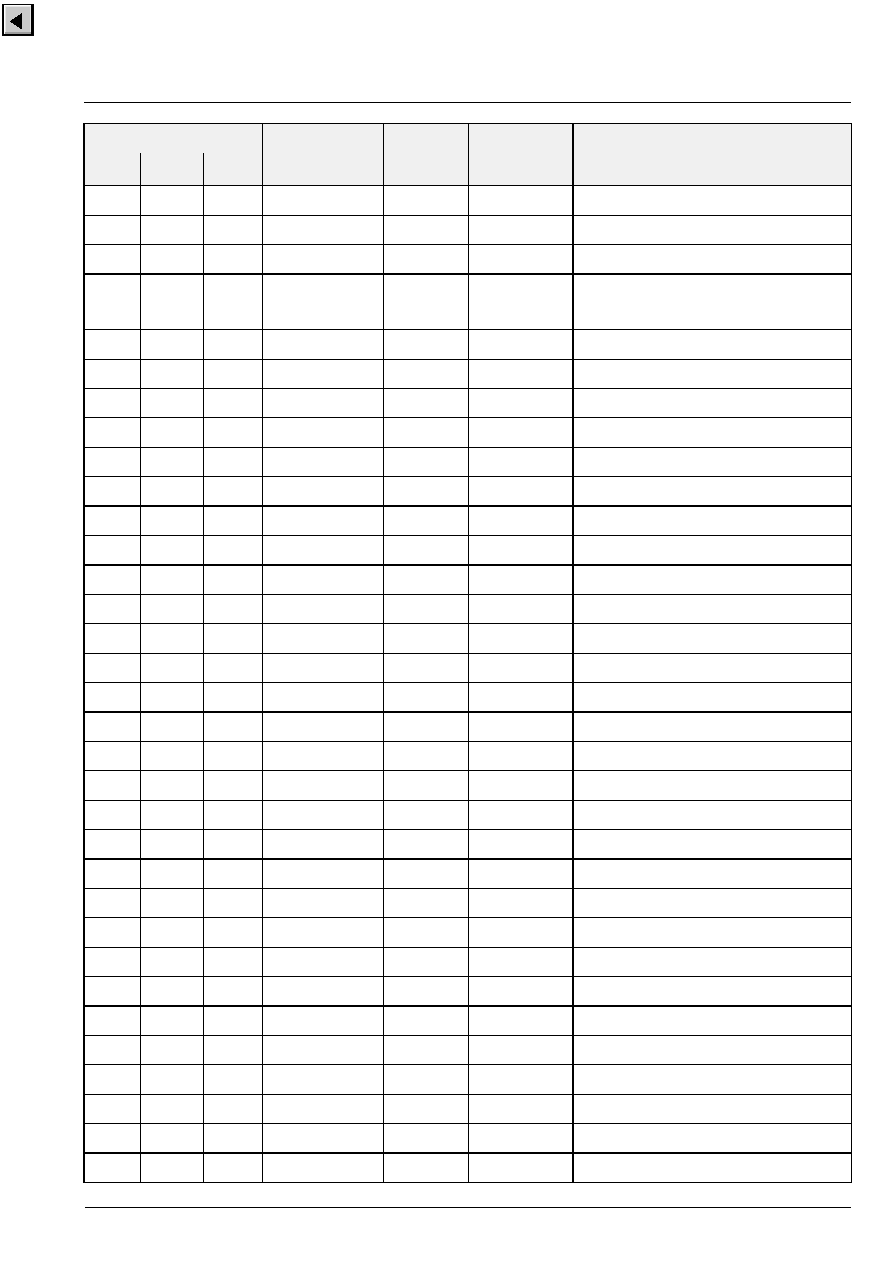

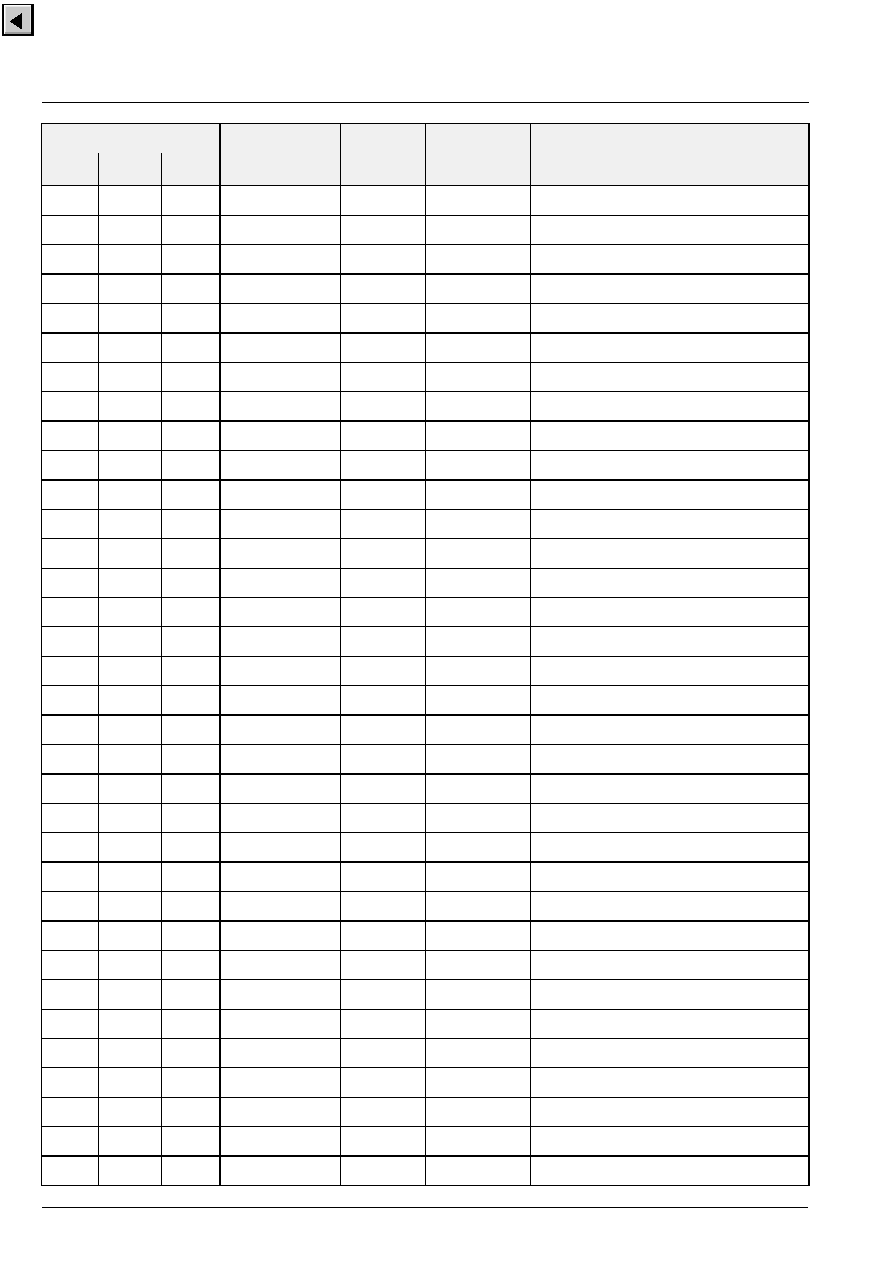

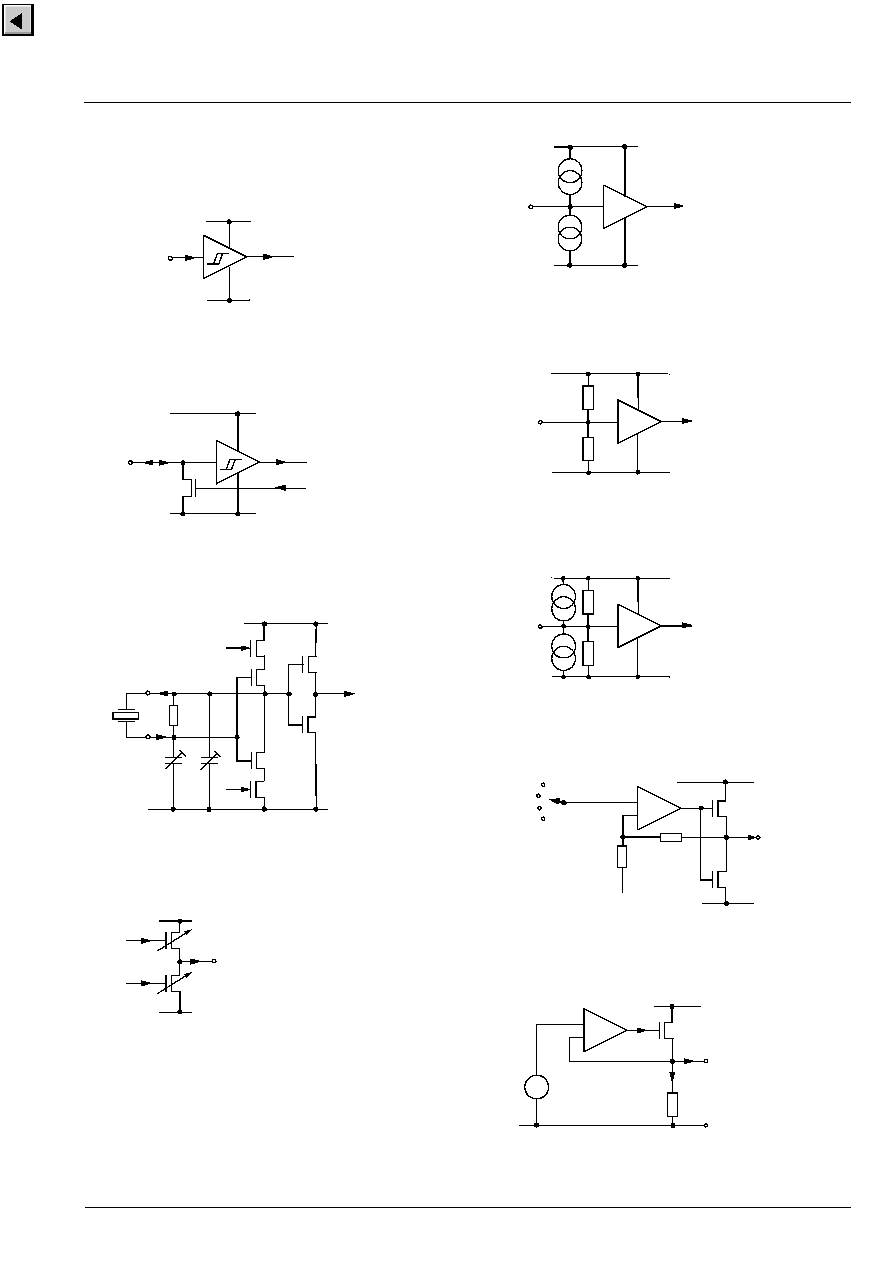

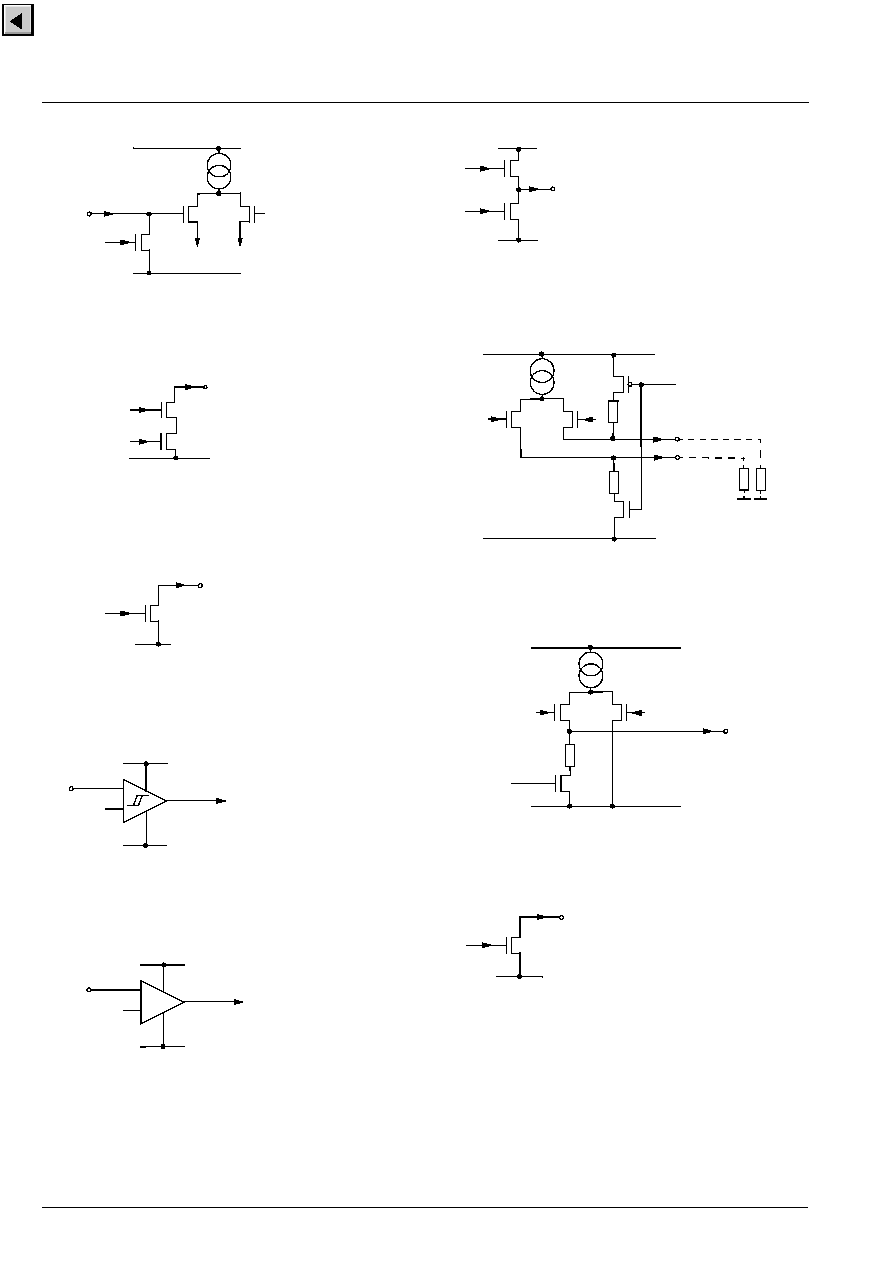

6.6.

Pin Circuits

150

6.7.

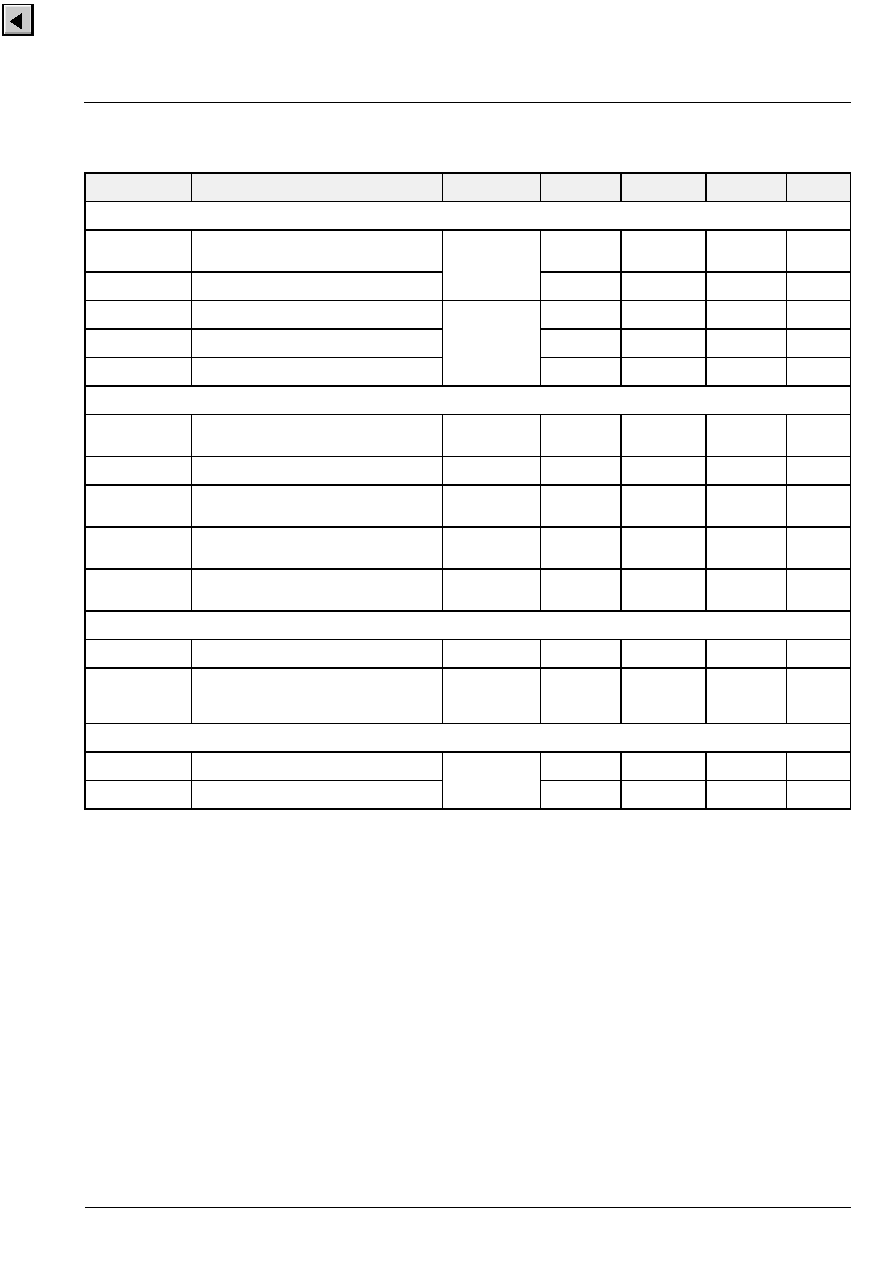

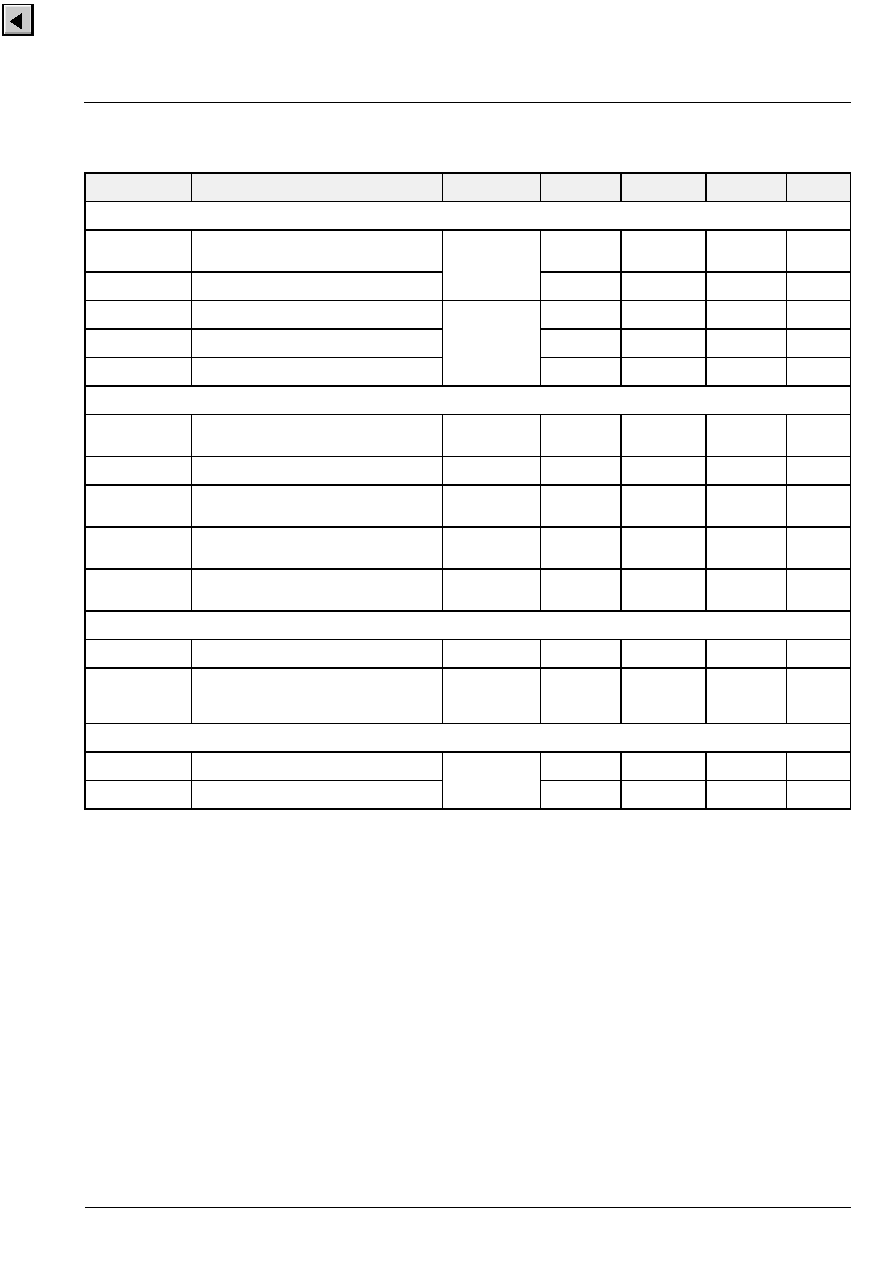

Electrical Characteristics

150

6.7.1.

Absolute Maximum Ratings

150

6.7.2.

Recommended Operating Conditions

150

6.7.2.1.

General Recommendations

151

6.7.2.2.

Analog Input and Output Recommendations

152

6.7.2.3.

Recommended Crystal Characteristics

153

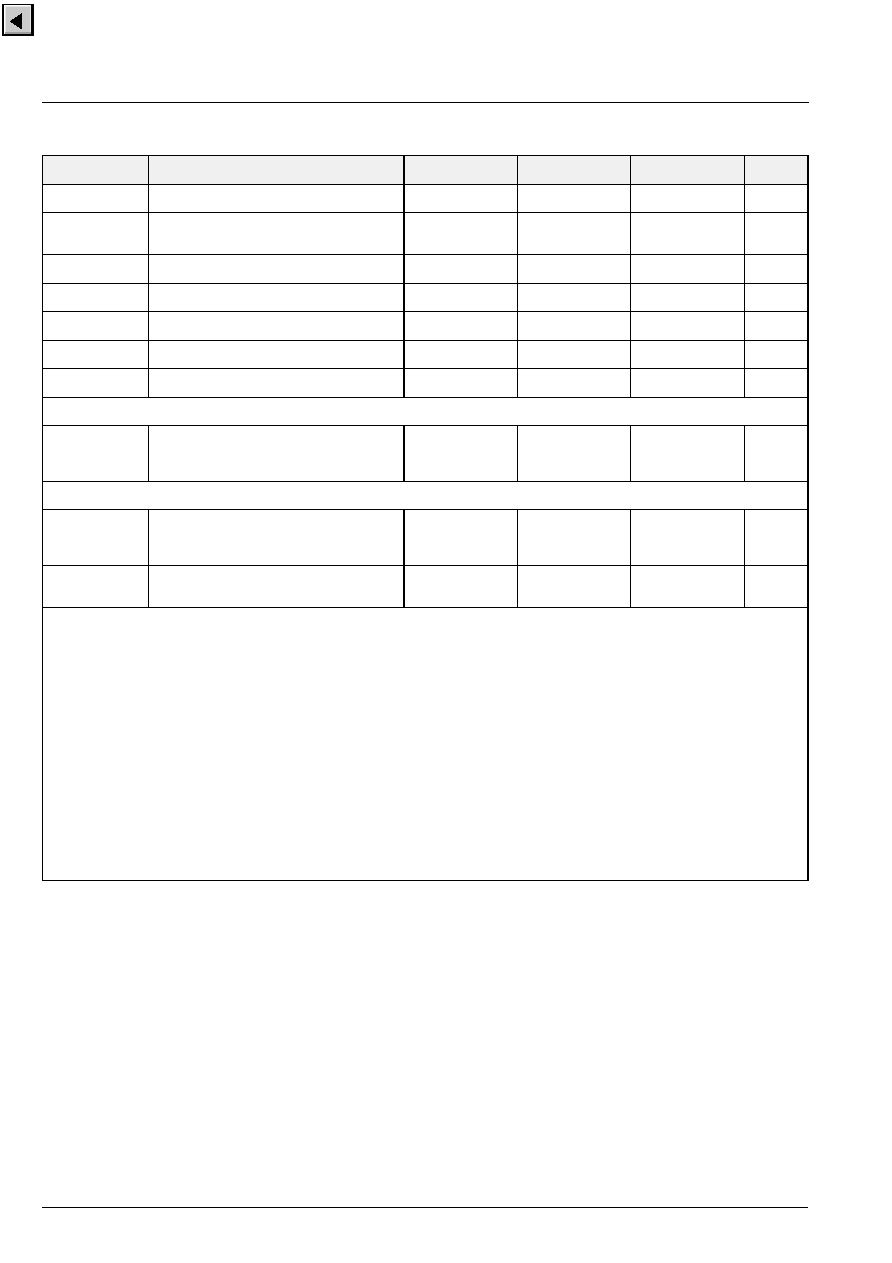

6.7.3.

Characteristics

153

6.7.3.1.

General Characteristics

153

6.7.3.2.

Test Input

154

6.7.3.3.

Reset Input

154

6.7.3.4.

I

2

C Bus Interface

155

6.7.3.5.

20-MHz Clock Output

155

6.7.3.6.

Analog Video Output

155

6.7.3.7.

A/D Converter Reference

156

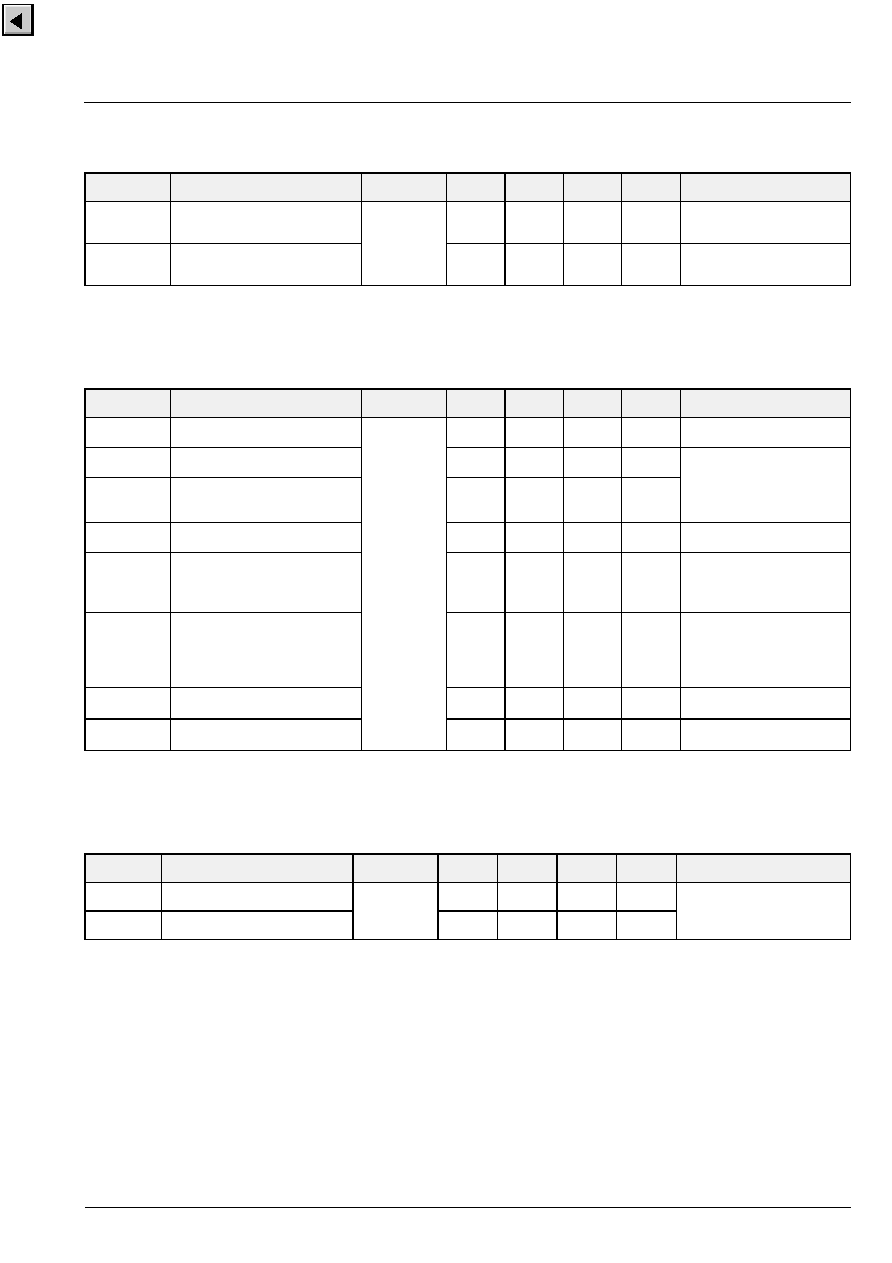

6.7.3.8.

Analog Video Front-End and A/D Converters

158

6.7.3.9.

Analog RGB and FB Inputs

159

6.7.3.10.

Horizontal Flyback Input

159

6.7.3.11.

Horizontal Drive Output

159

6.7.3.12.

Vertical Safety Input

159

6.7.3.13.

Vertical Protection Input

160

6.7.3.14.

Vertical and East/West D/A Converter Output

160

6.7.3.15.

Interlace Output

160

6.7.3.16.

Sense A/D Converter Input

160

6.7.3.17.

Range Switch Output

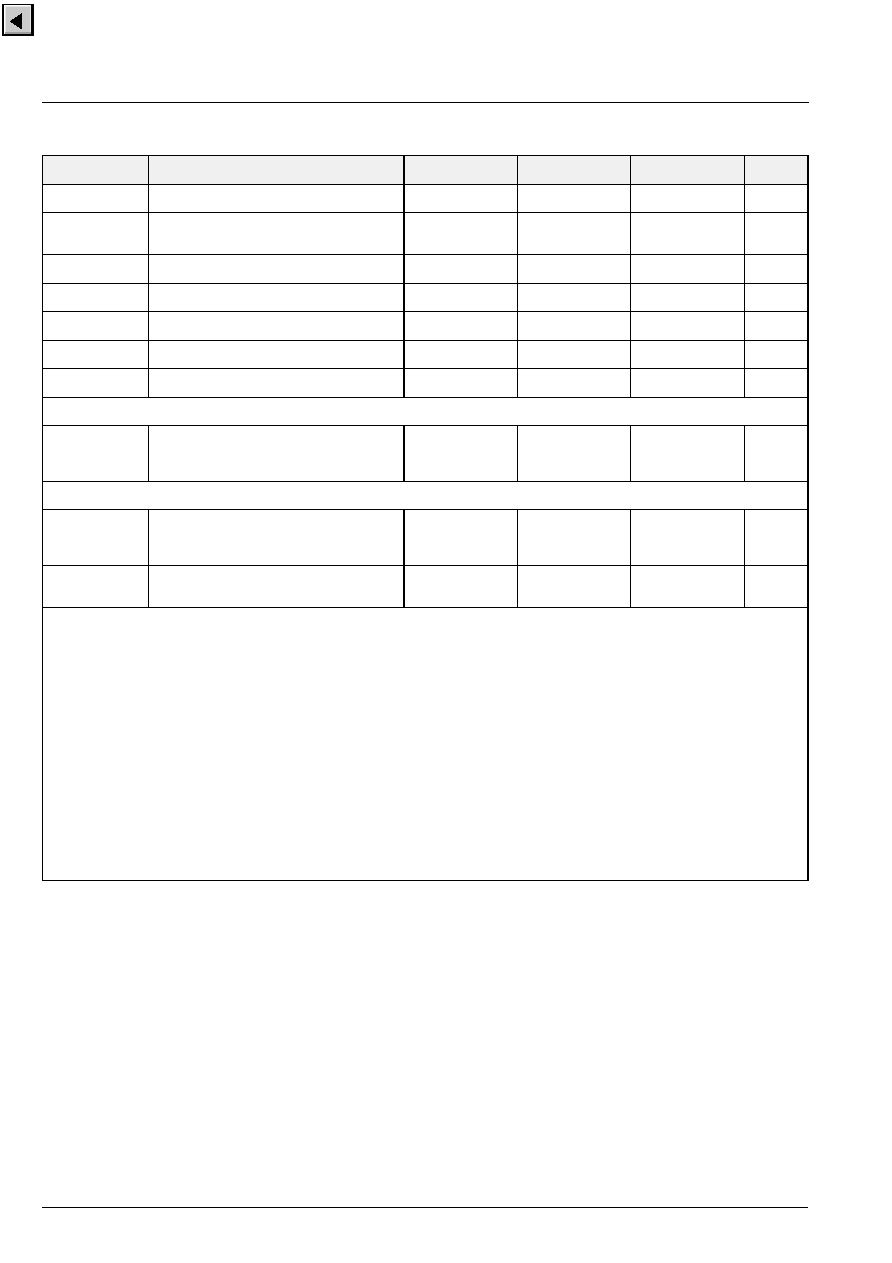

161

6.7.3.18.

D/A Converter Reference

161

6.7.3.19.

Analog RGB Outputs, D/A Converters

164

6.7.3.20.

Scan Velocity Modulation Output

164

6.7.3.21.

Analog Audio Inputs and Outputs

165

6.7.3.22.

ADC Input Port

165

6.7.3.23.

Universal Port

166

6.7.3.24.

Memory Port

167

7.

Application

171

8.

Glossary of Abbreviations

171

9.

References

172

10.

Data Sheet History

ADVANCE INFORMATION

VCT 38xxA

Micronas

7

Video/Controller/Teletext IC Family

Release Note: This data sheet describes functions

and characteristics of the VCT 38xxA-B2.

1. Introduction

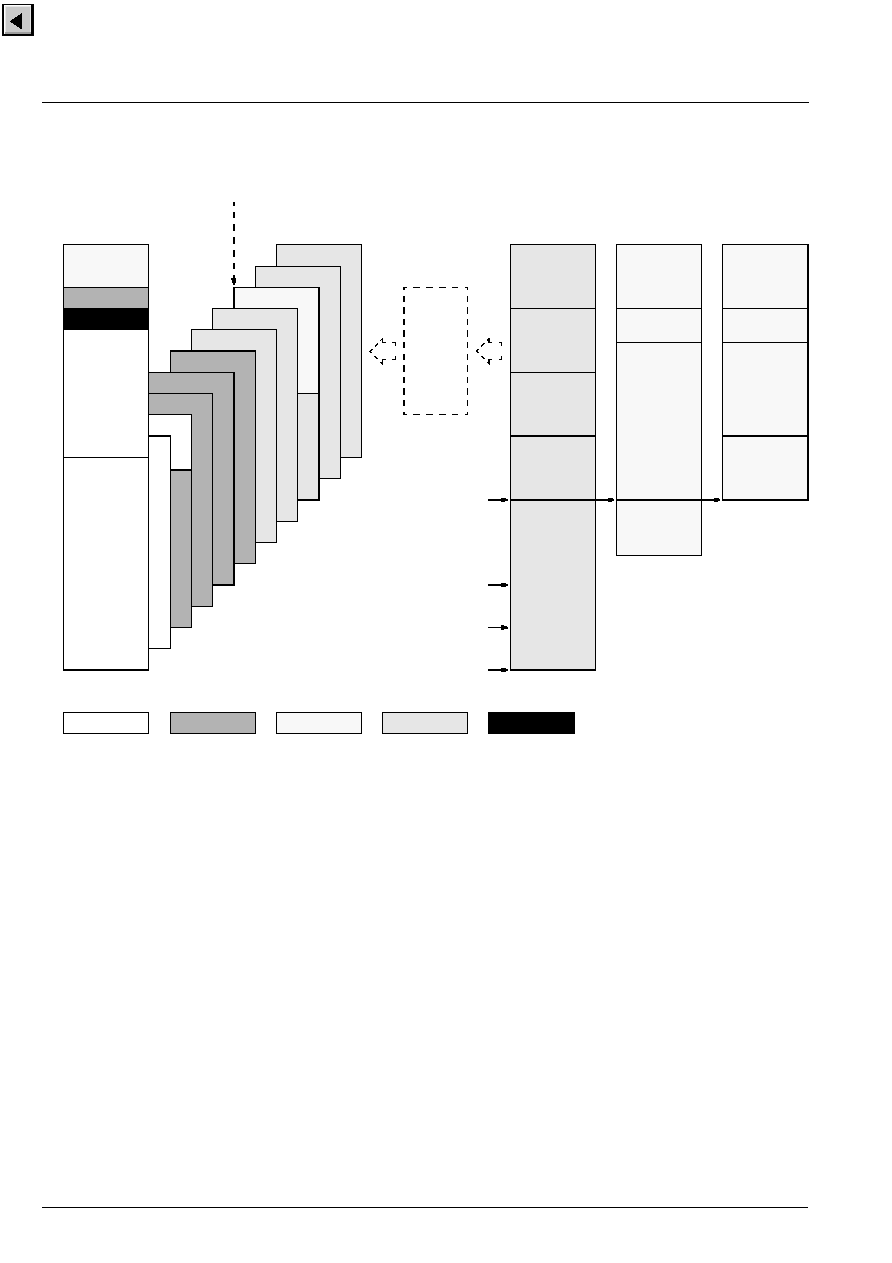

The VCT 38xxA is an IC family of high-quality single-

chip TV processors. Modular design and a submicron

technology allow the economic integration of features

in all classes of TV sets. The VCT 38xxA family is

based on functional blocks contained and approved in

existing products like VDP 3120B, TPU 3050S, and

CCZ 3005K.

Each member of the family contains the entire video,

display and deflection processing for 4:3 and 16:9 50/

60-Hz TV sets. The integrated microcontroller is sup-

ported by a powerful OSD generator with integrated

teletext acquisition which can be upgraded with on-

chip page memory. With volume control and audio

input select the basic audio features for mono TV sets

are integrated. An overview of the VCT 38xxA single-

chip TV processor family is given in Fig. 1�1 on

page 7.

The VCT 38xxA family offers a rich feature set, cover-

ing the whole range of state-of-the-art 50/60-Hz TV

applications.

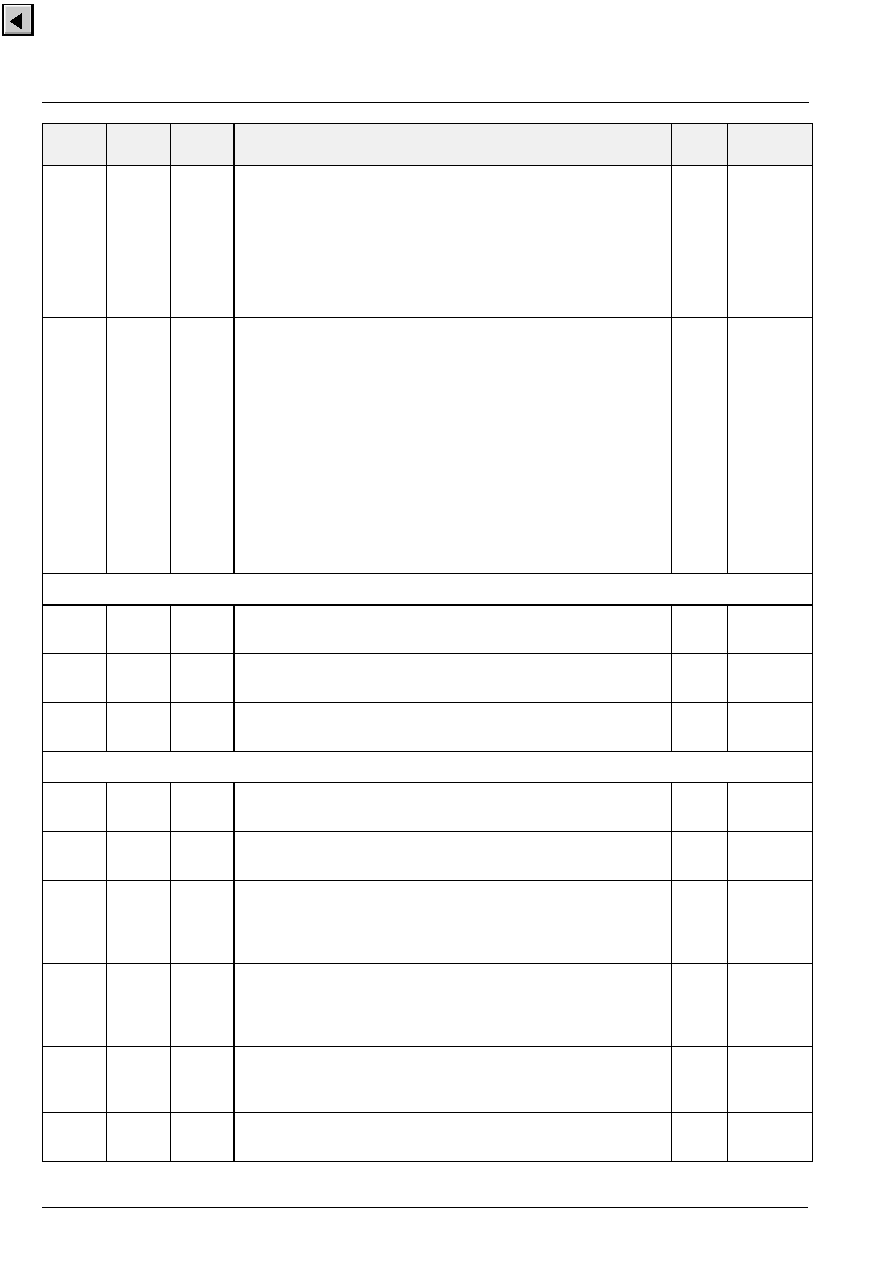

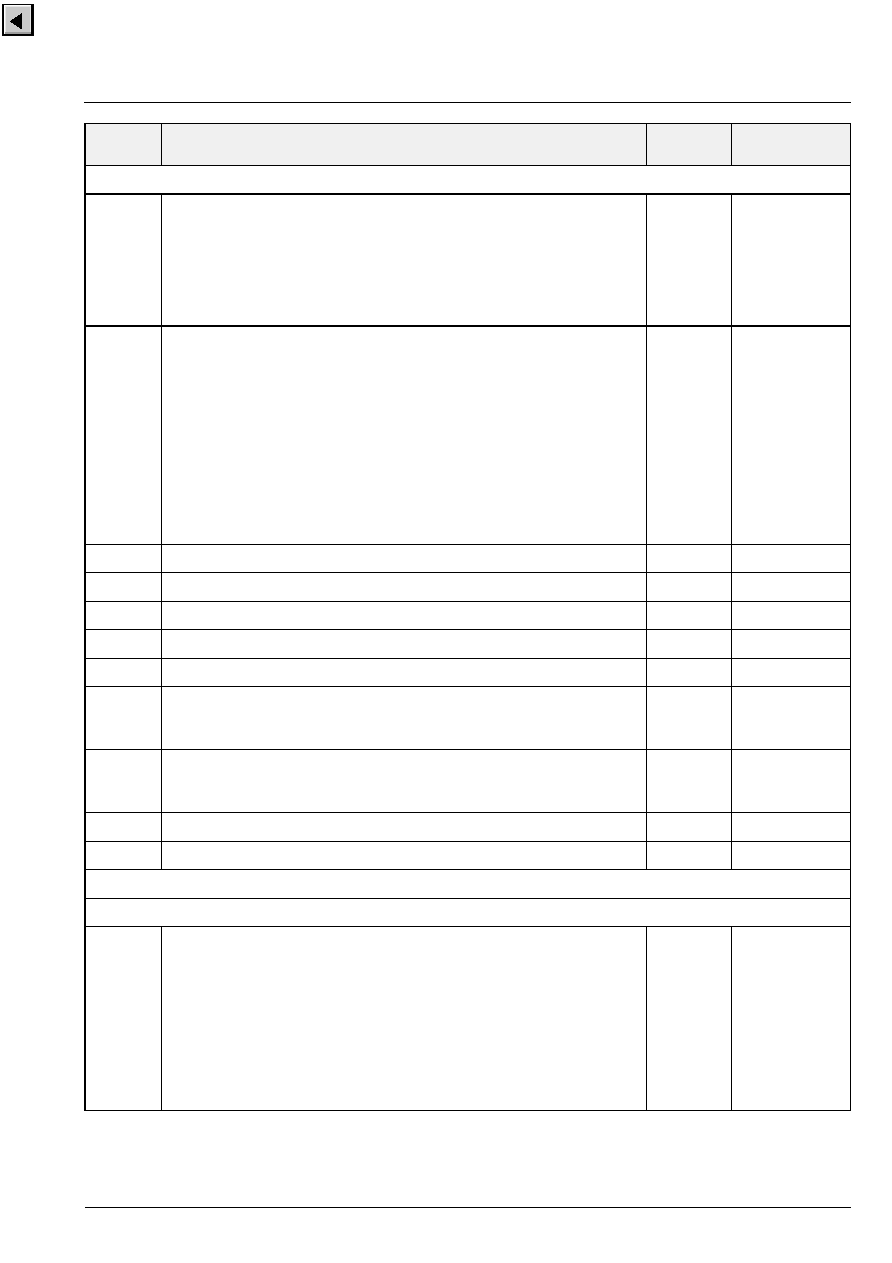

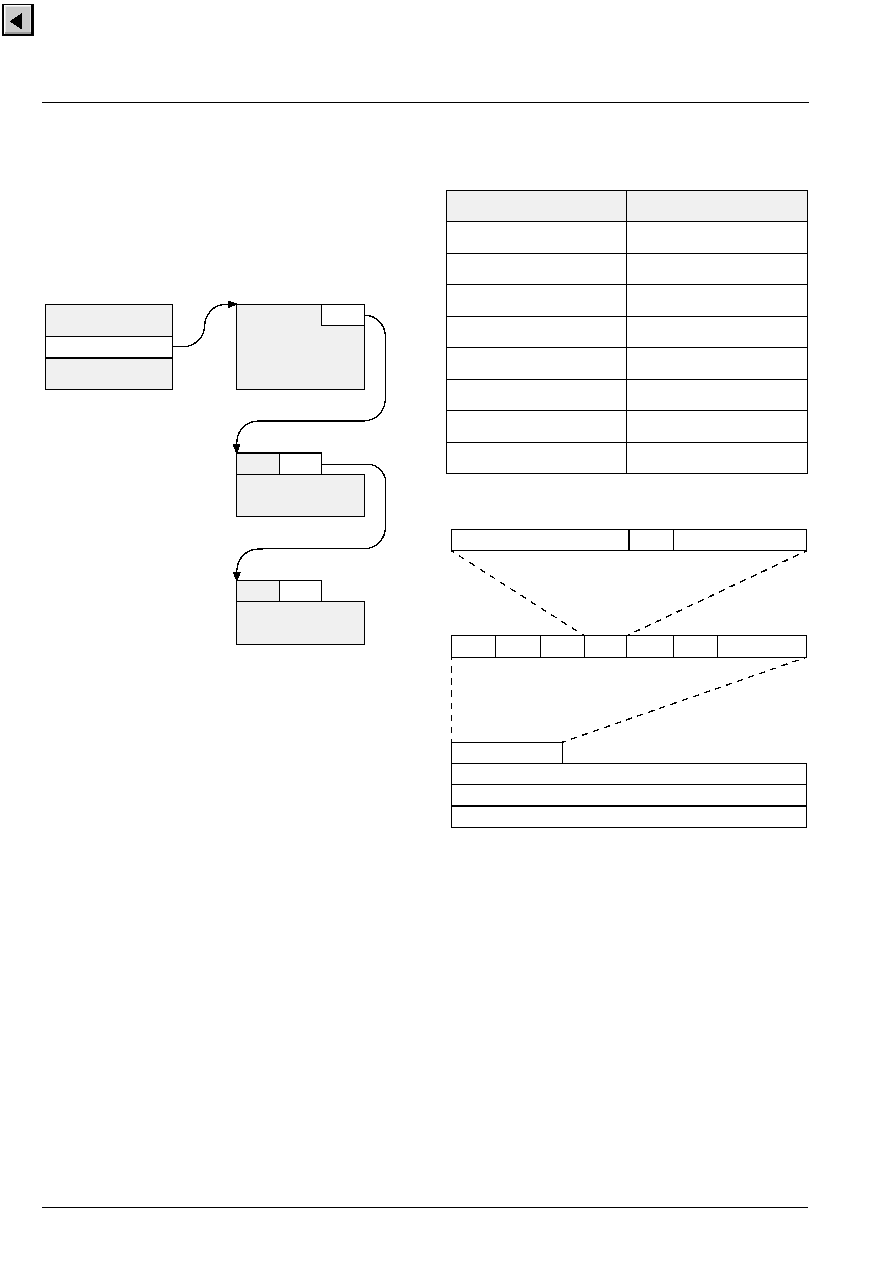

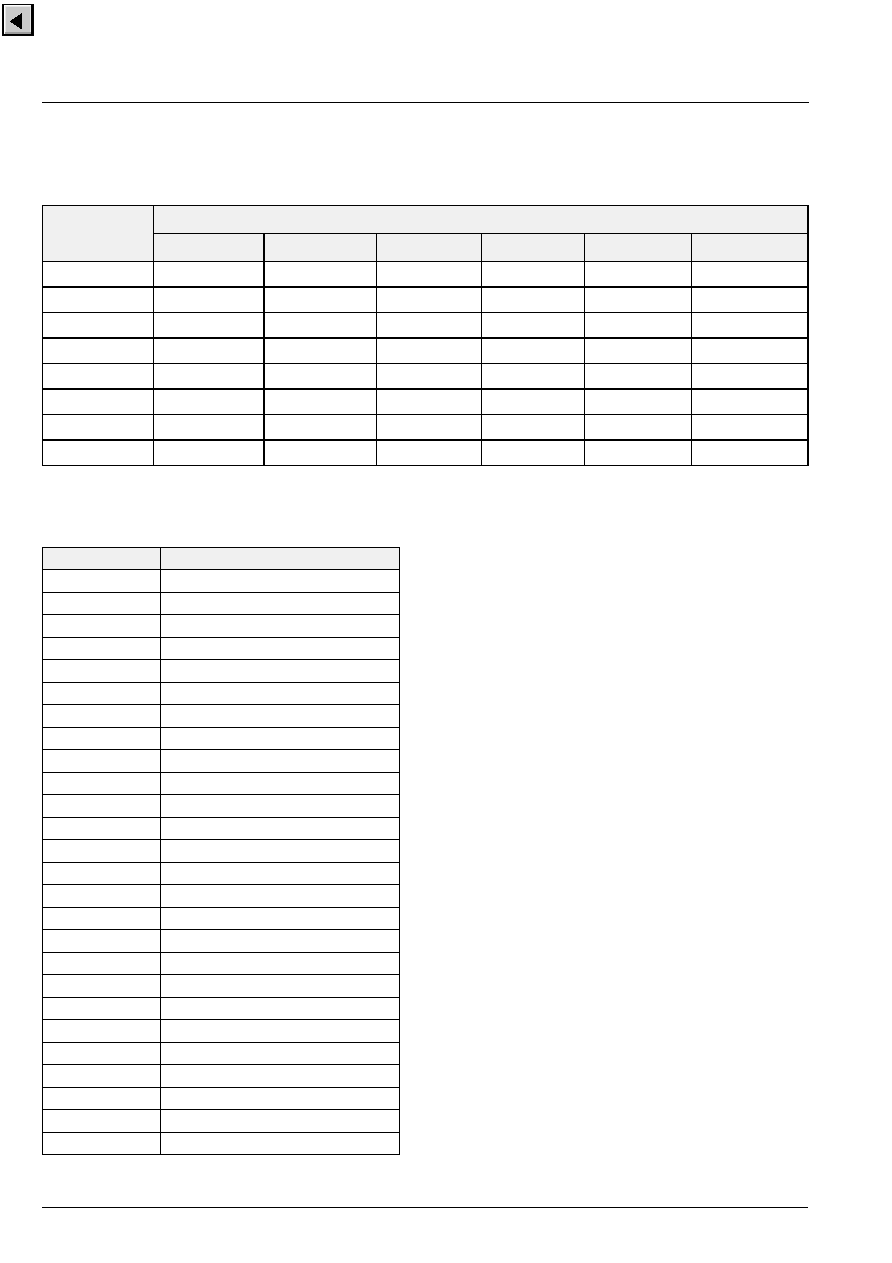

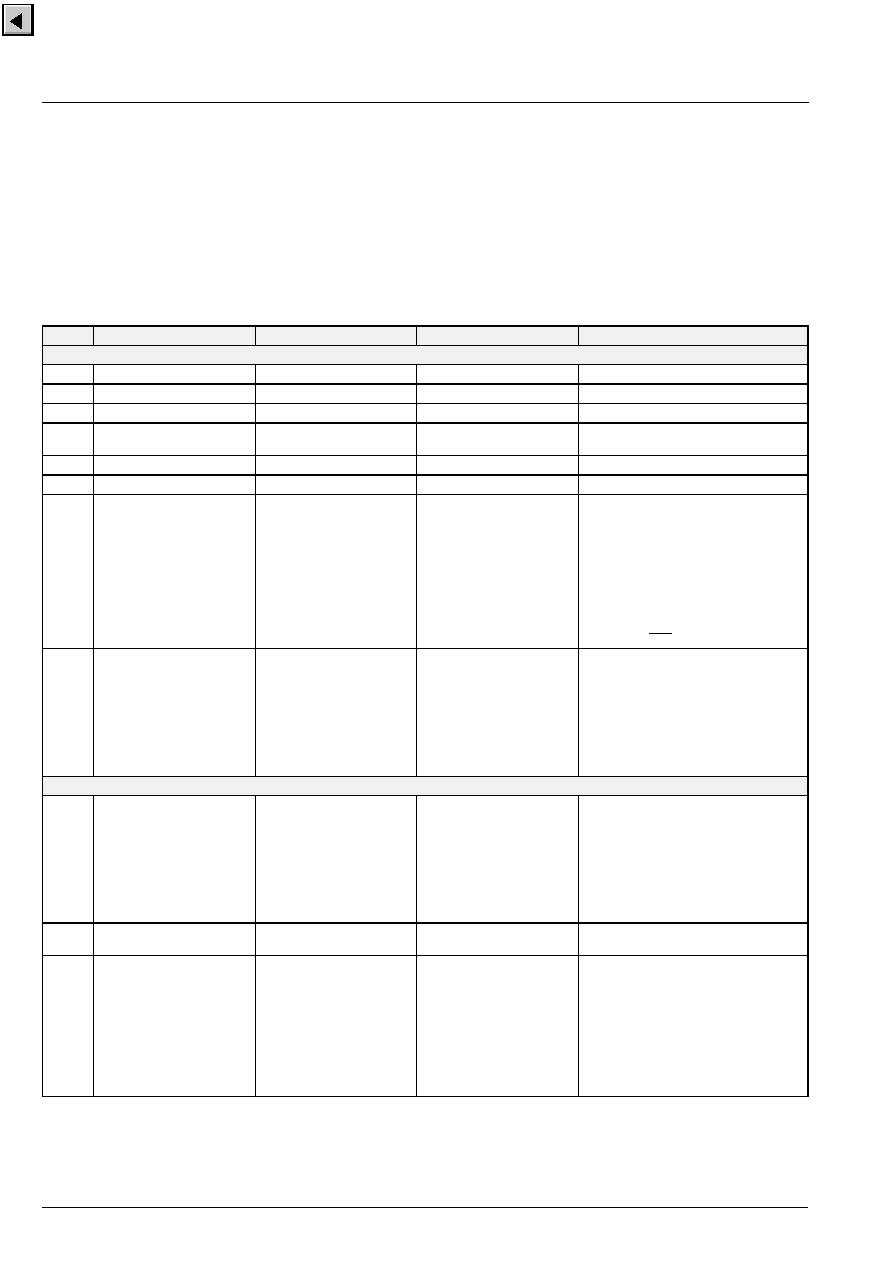

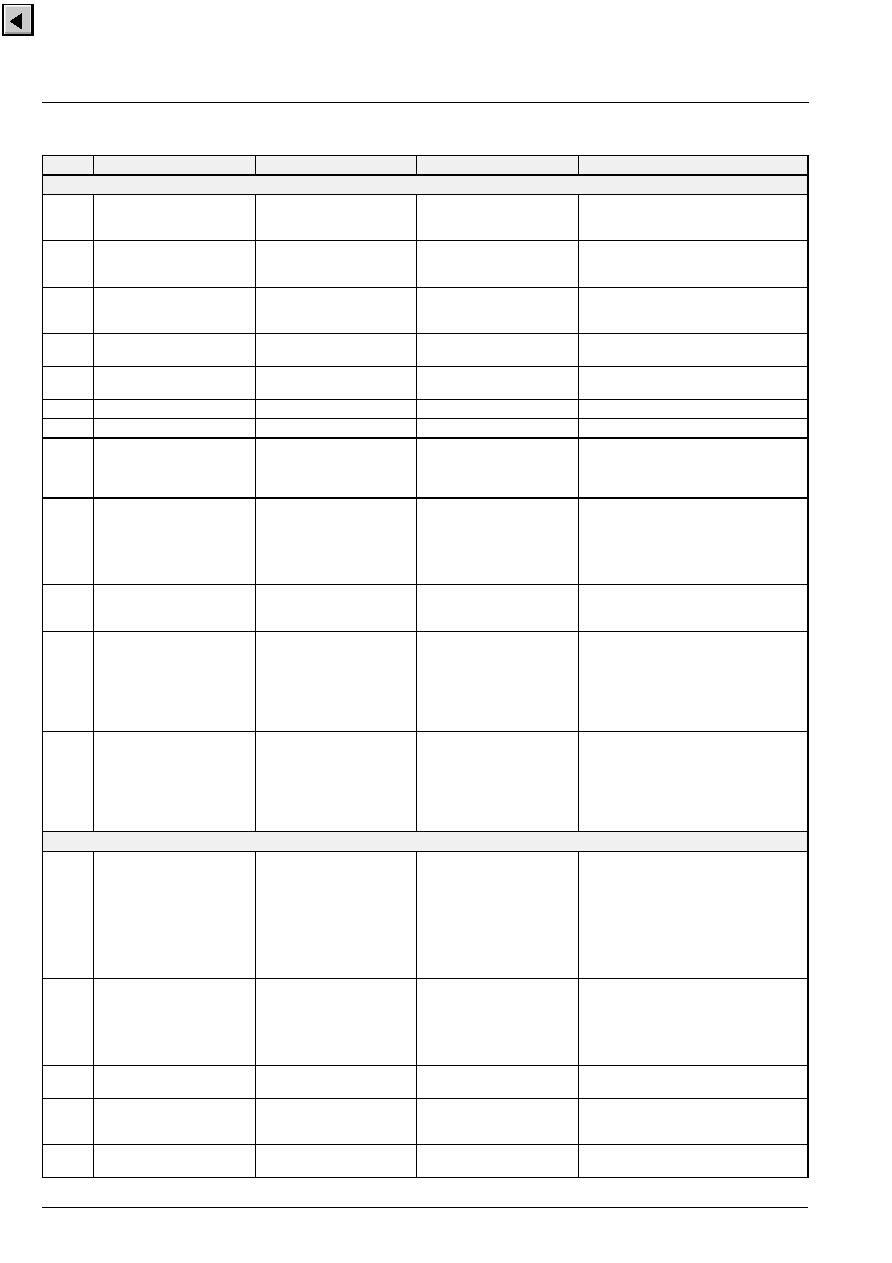

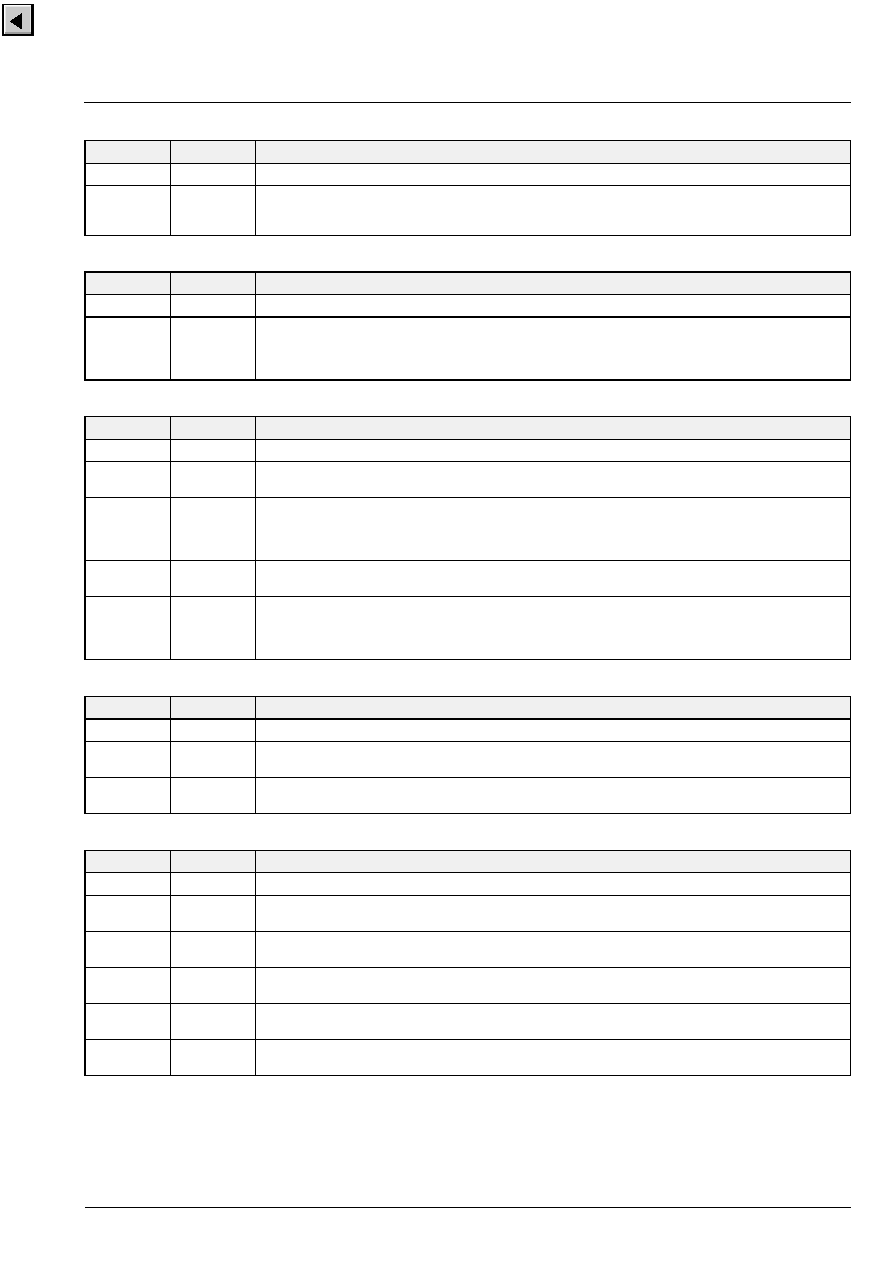

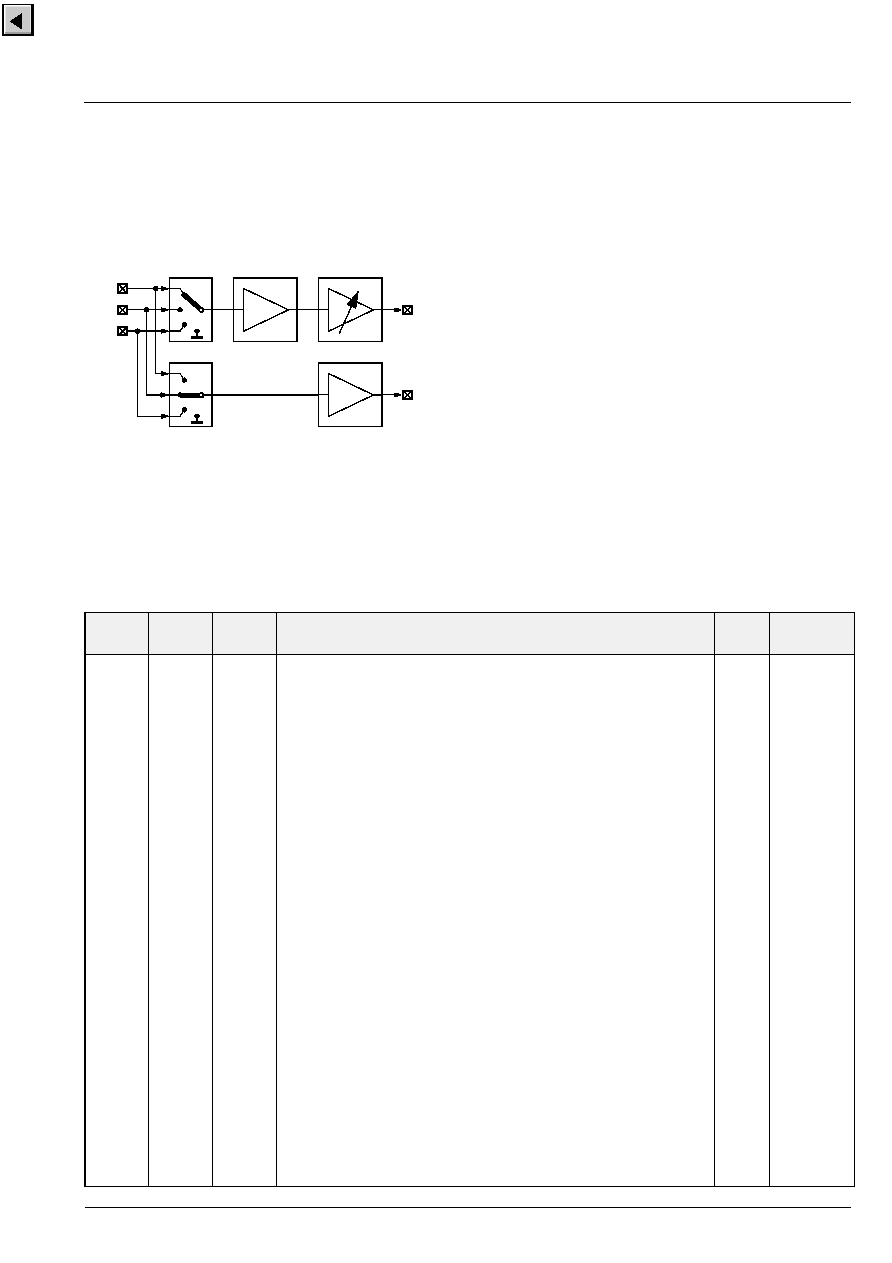

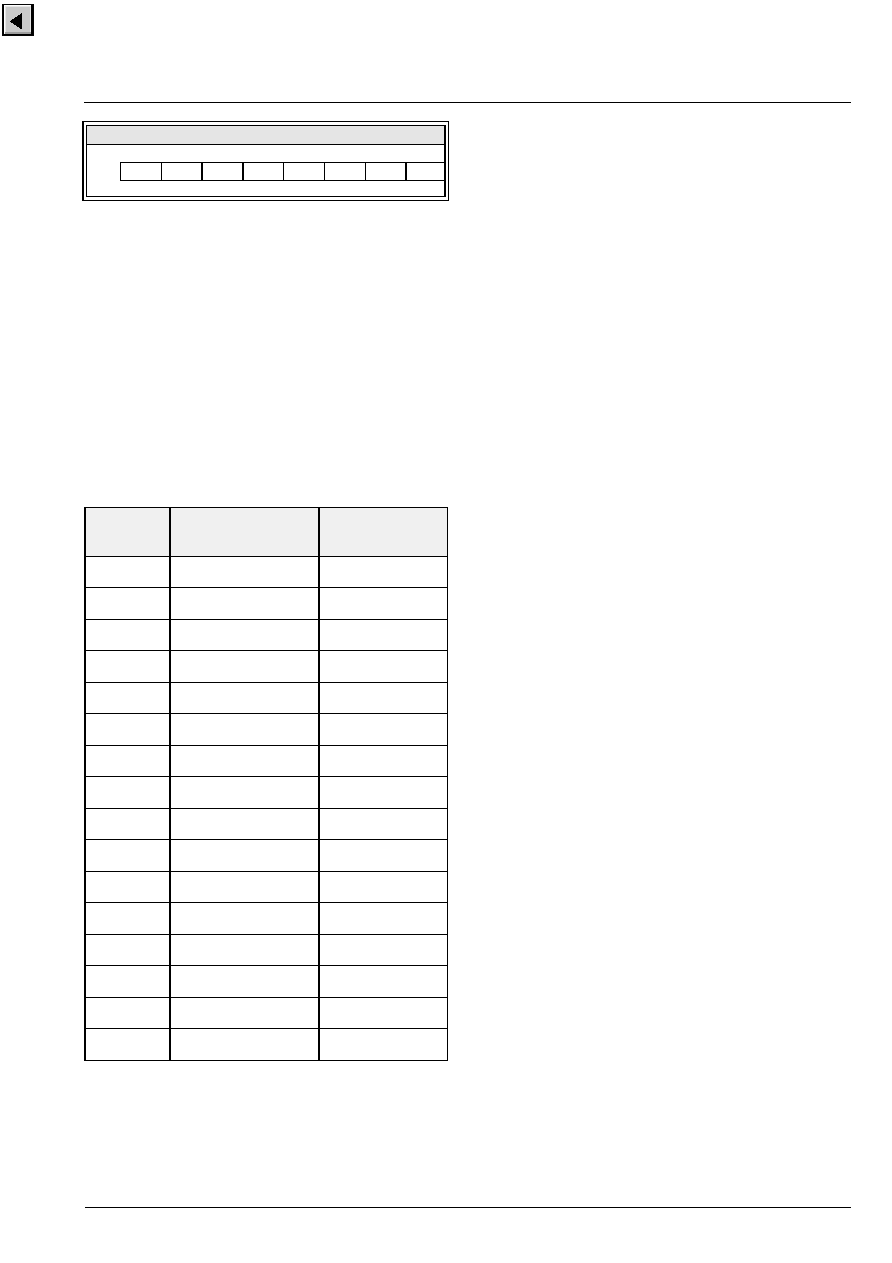

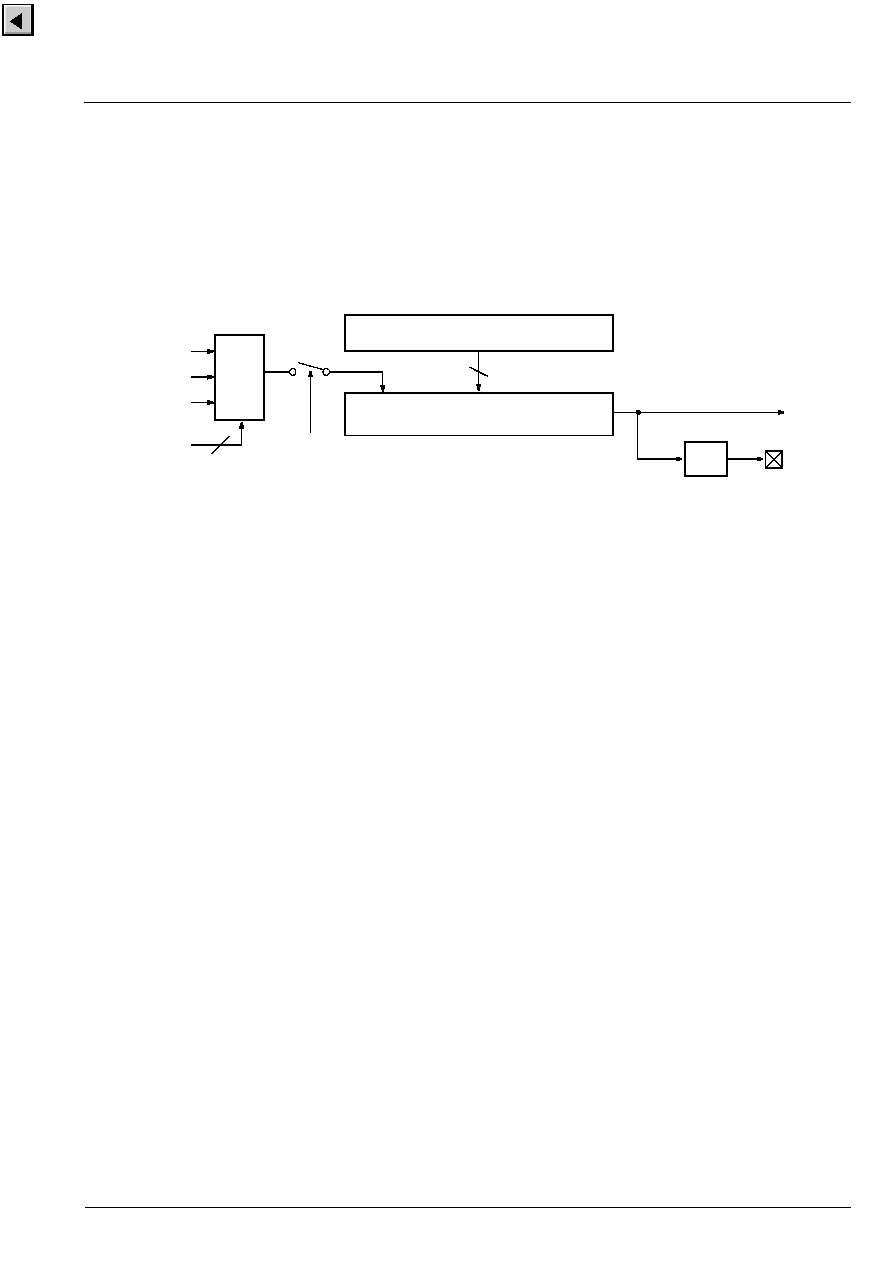

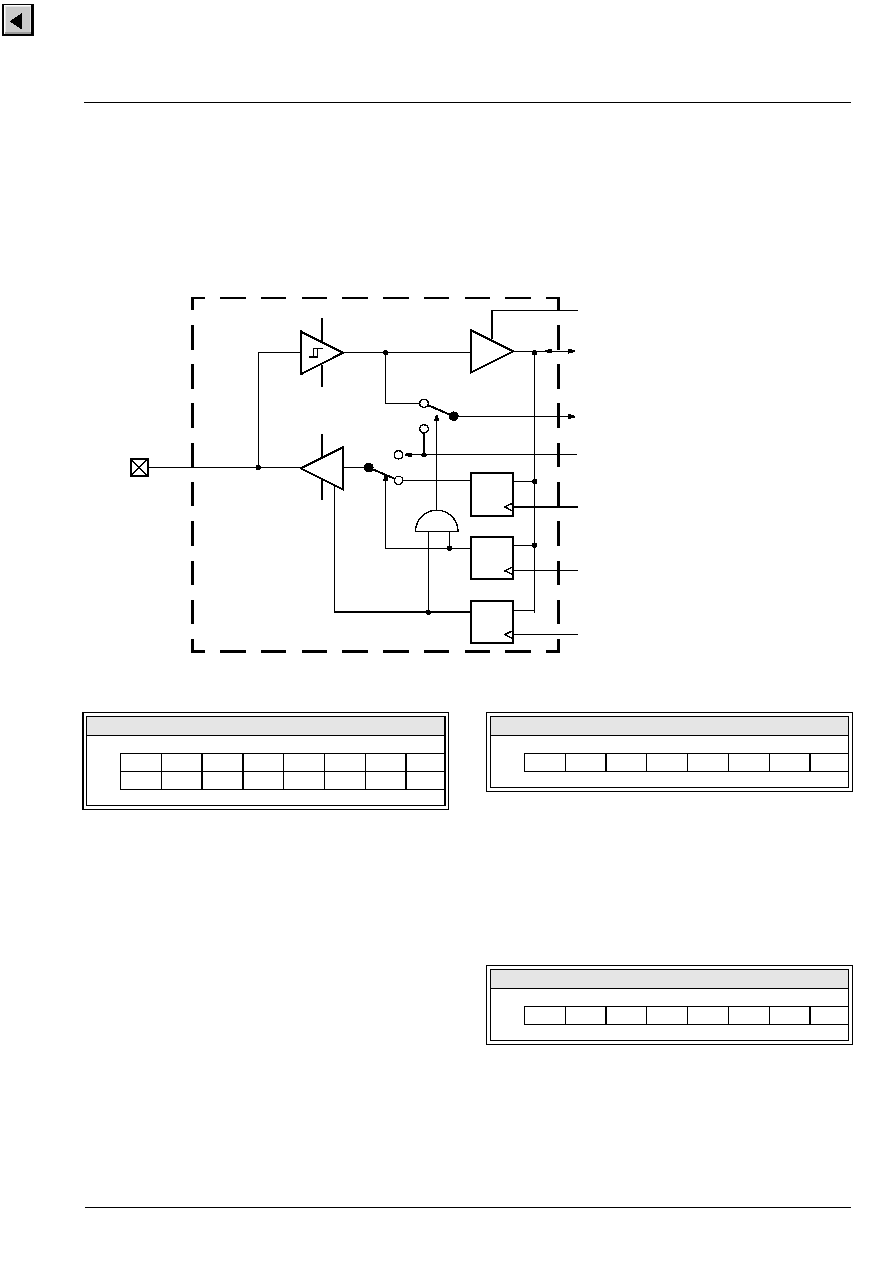

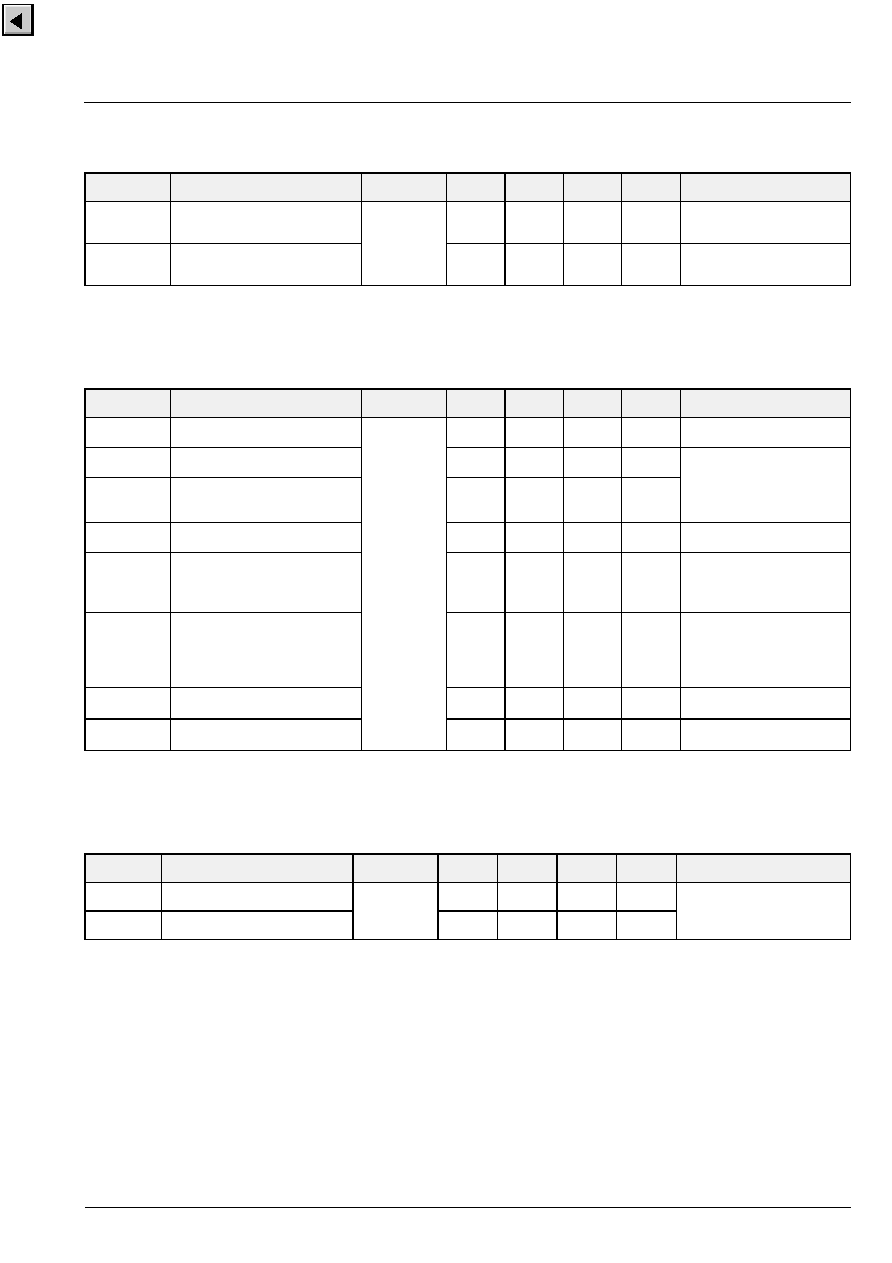

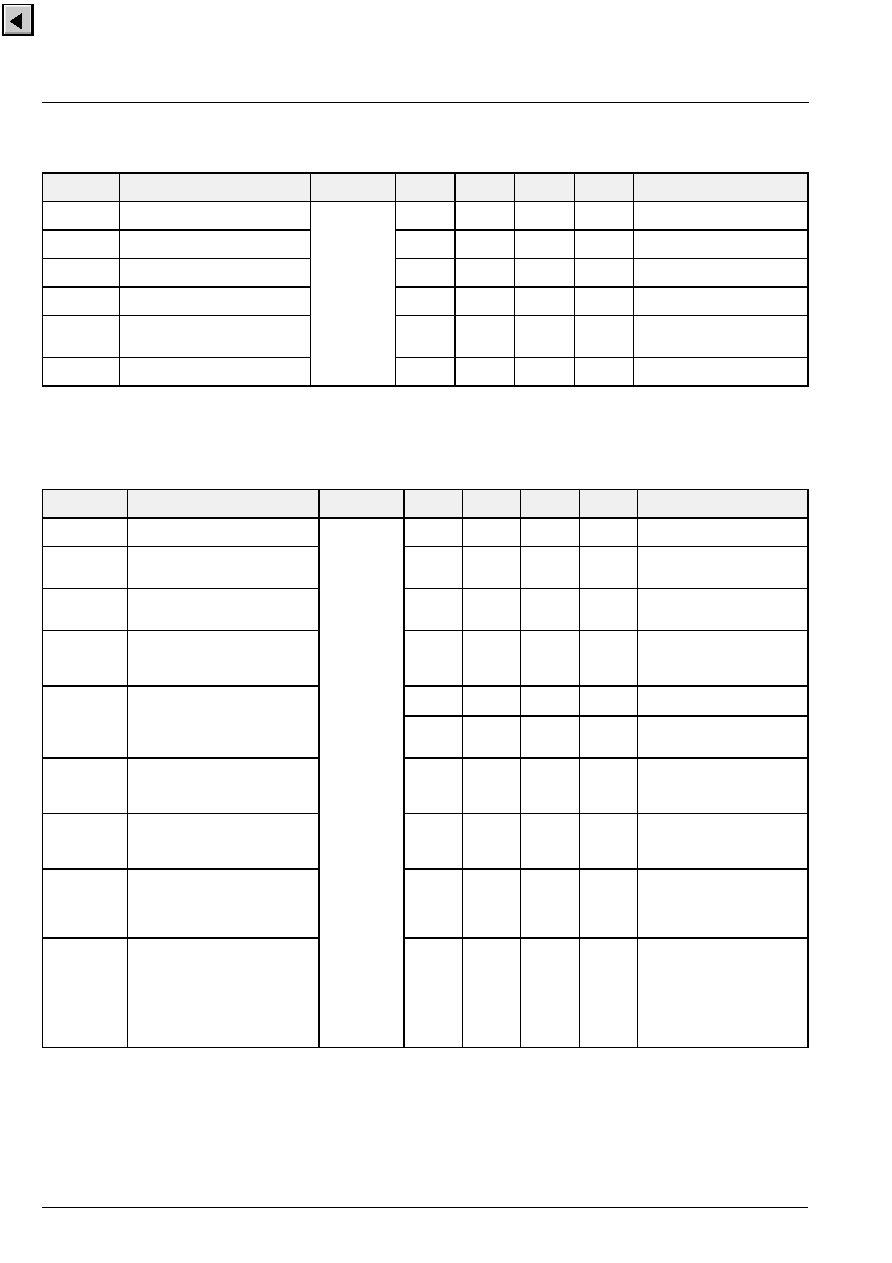

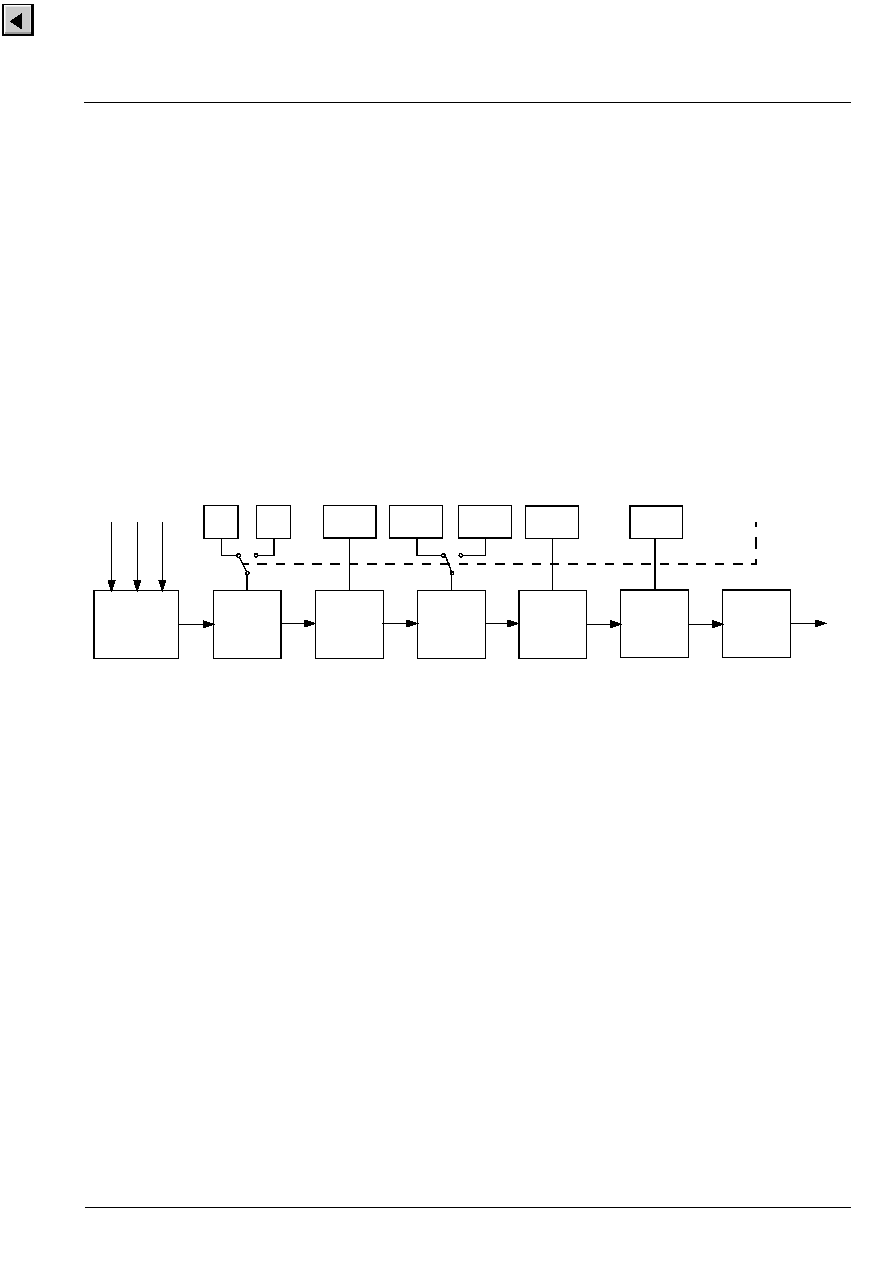

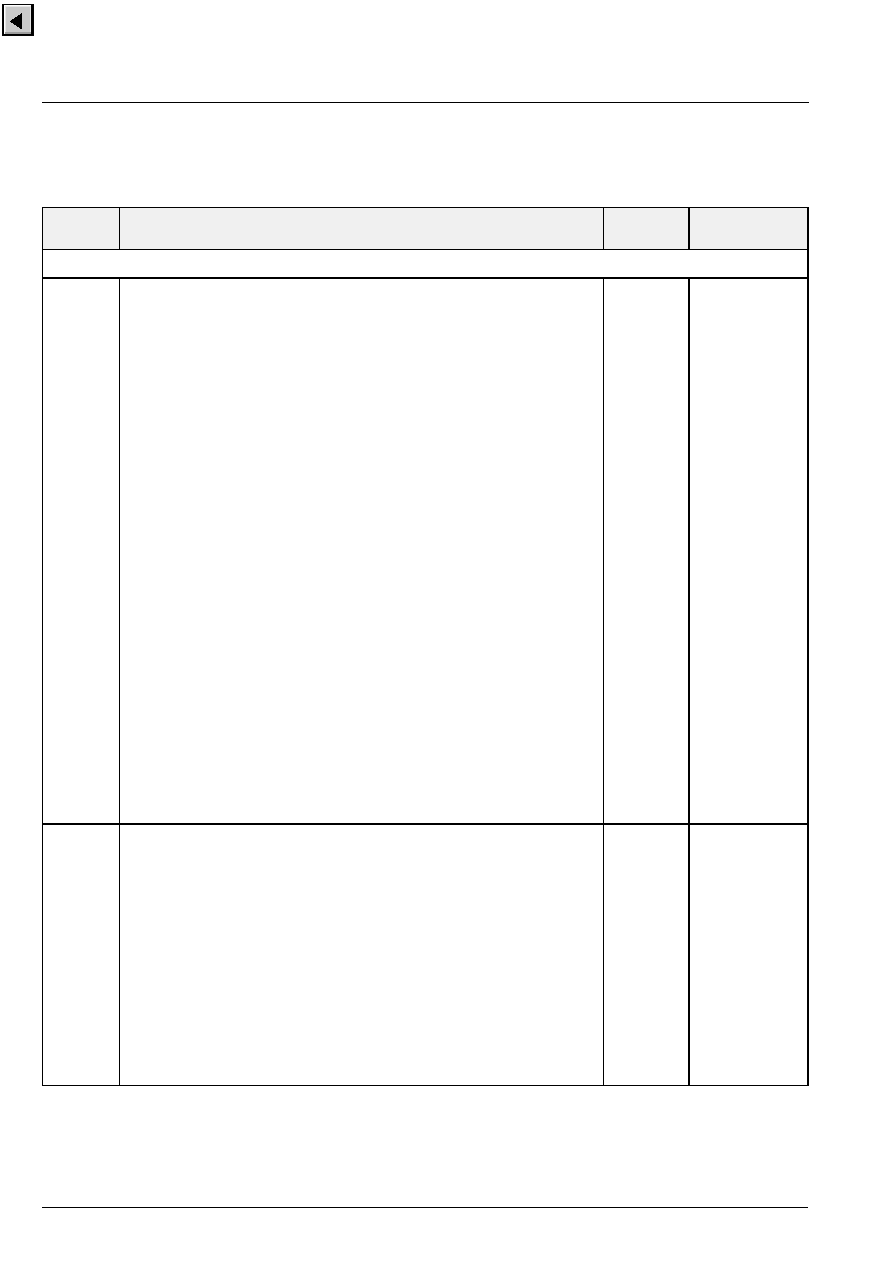

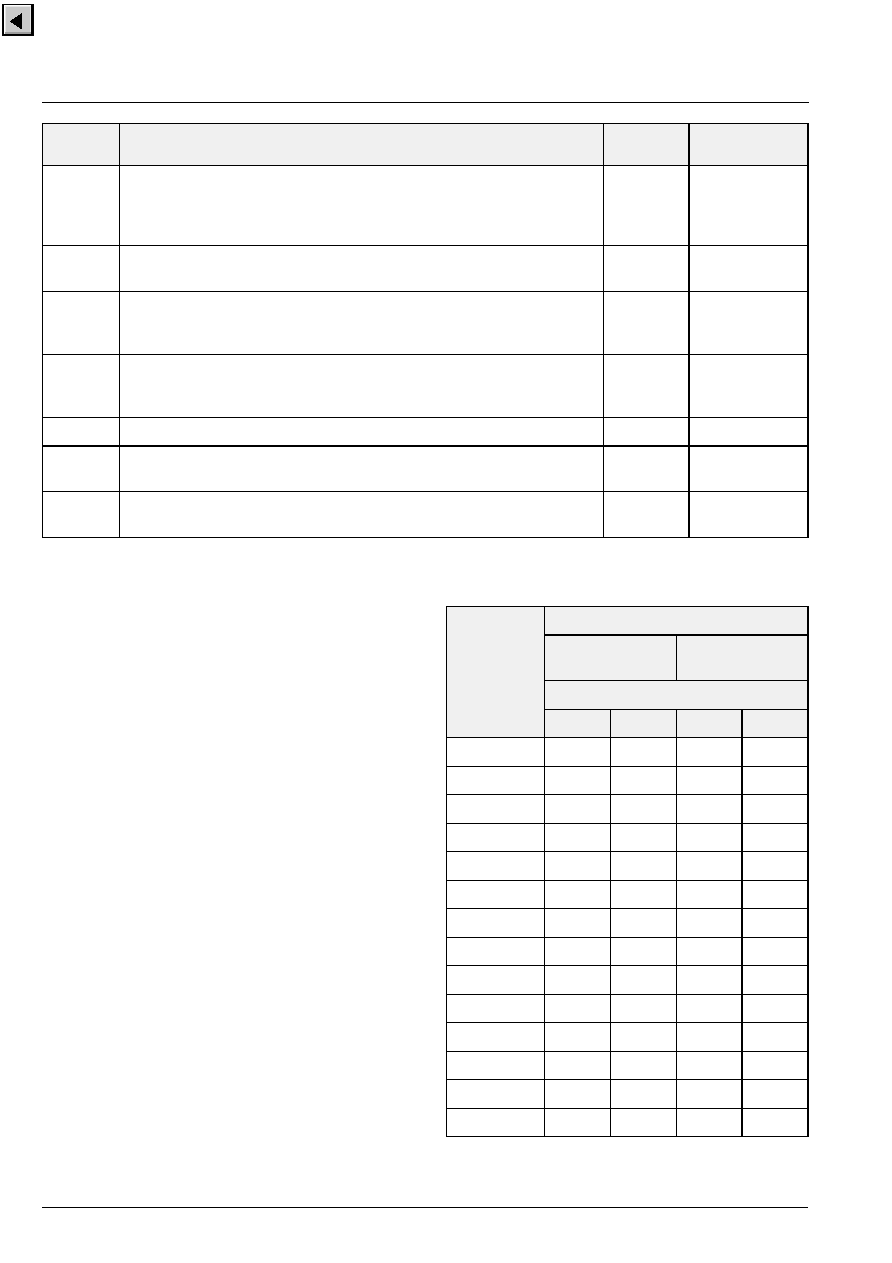

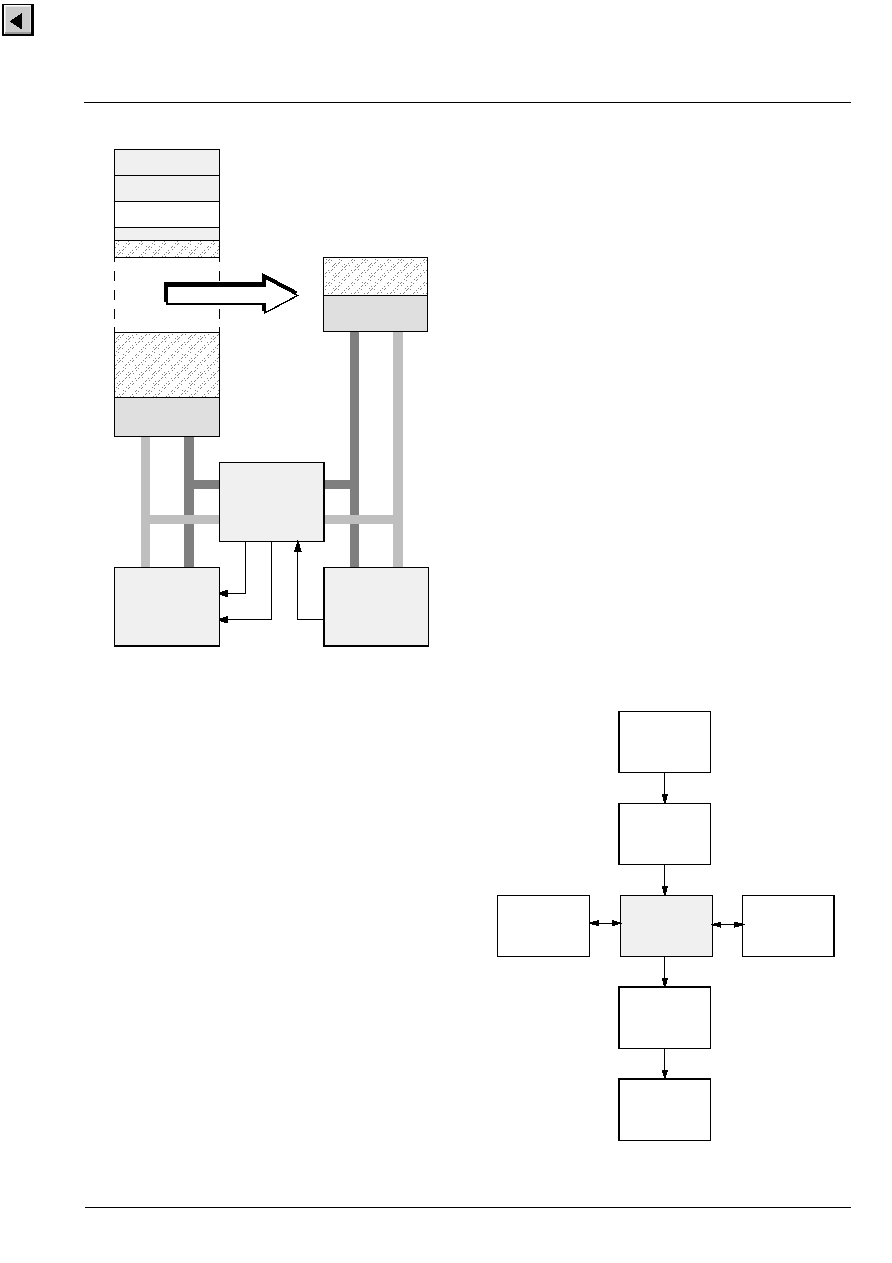

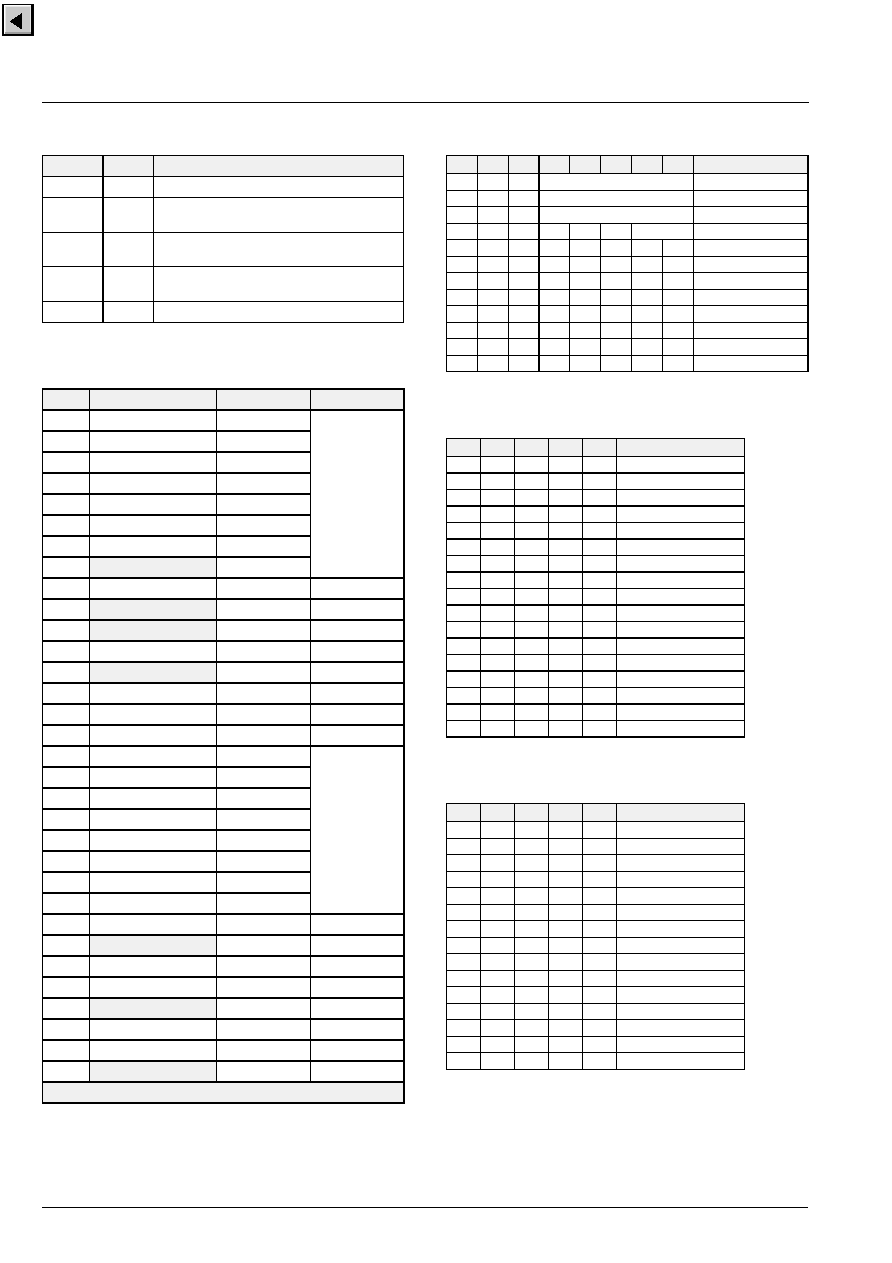

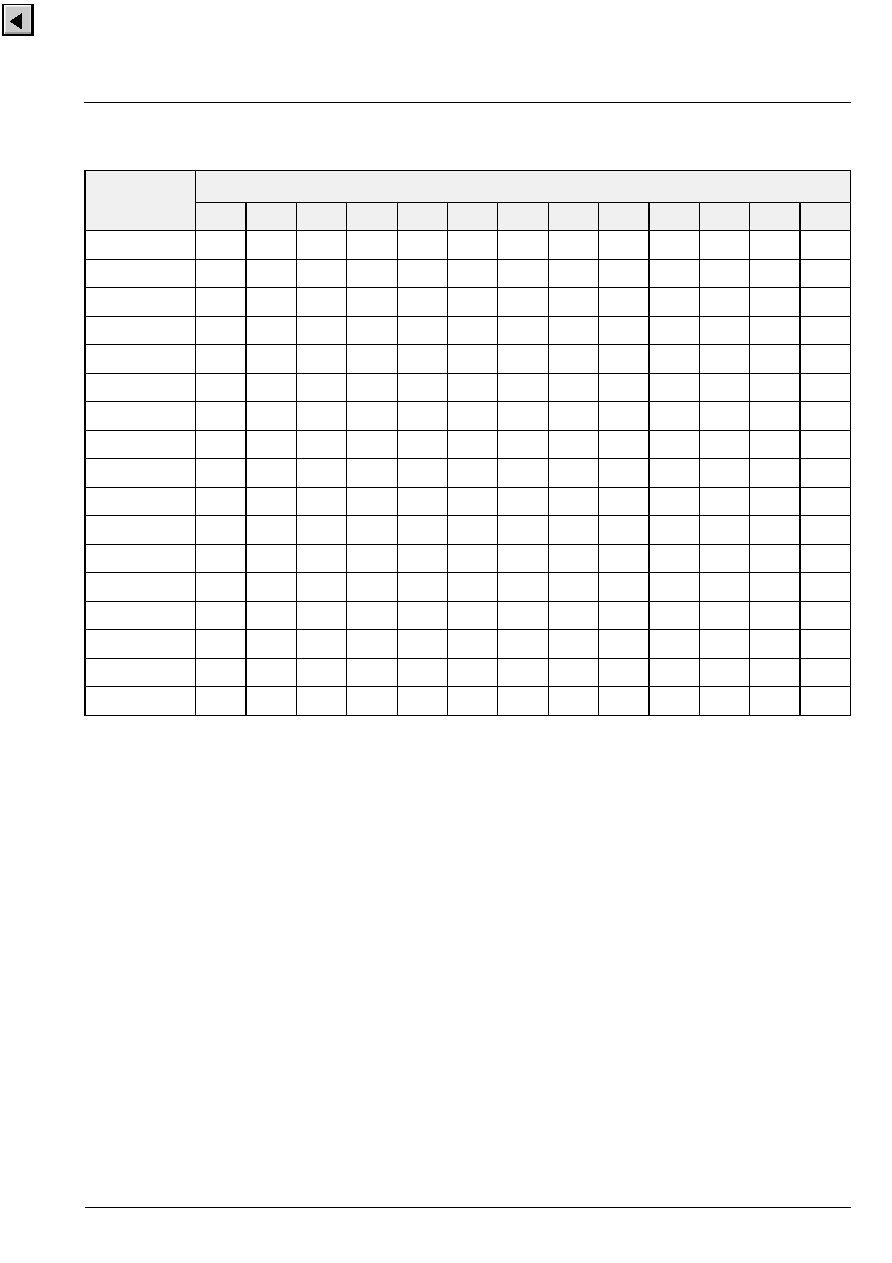

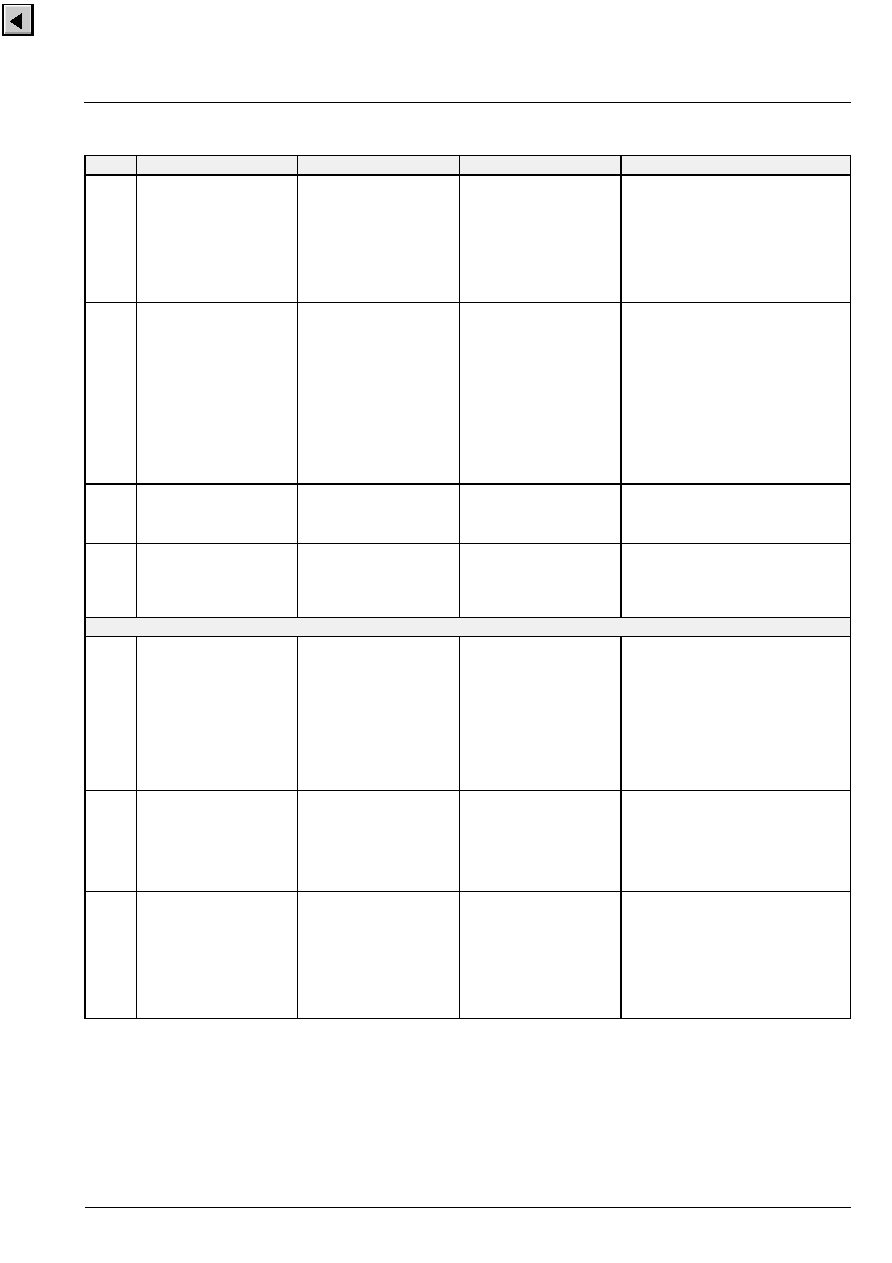

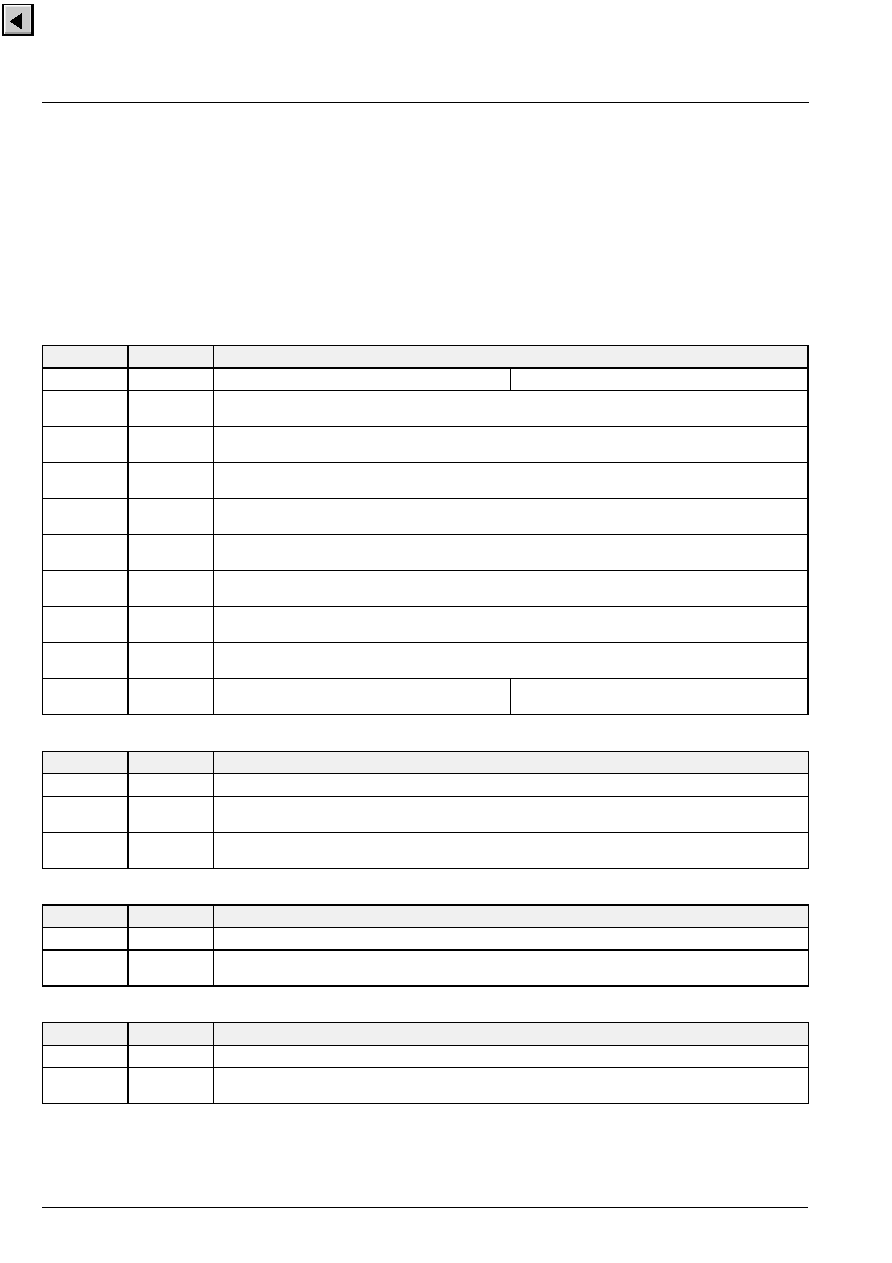

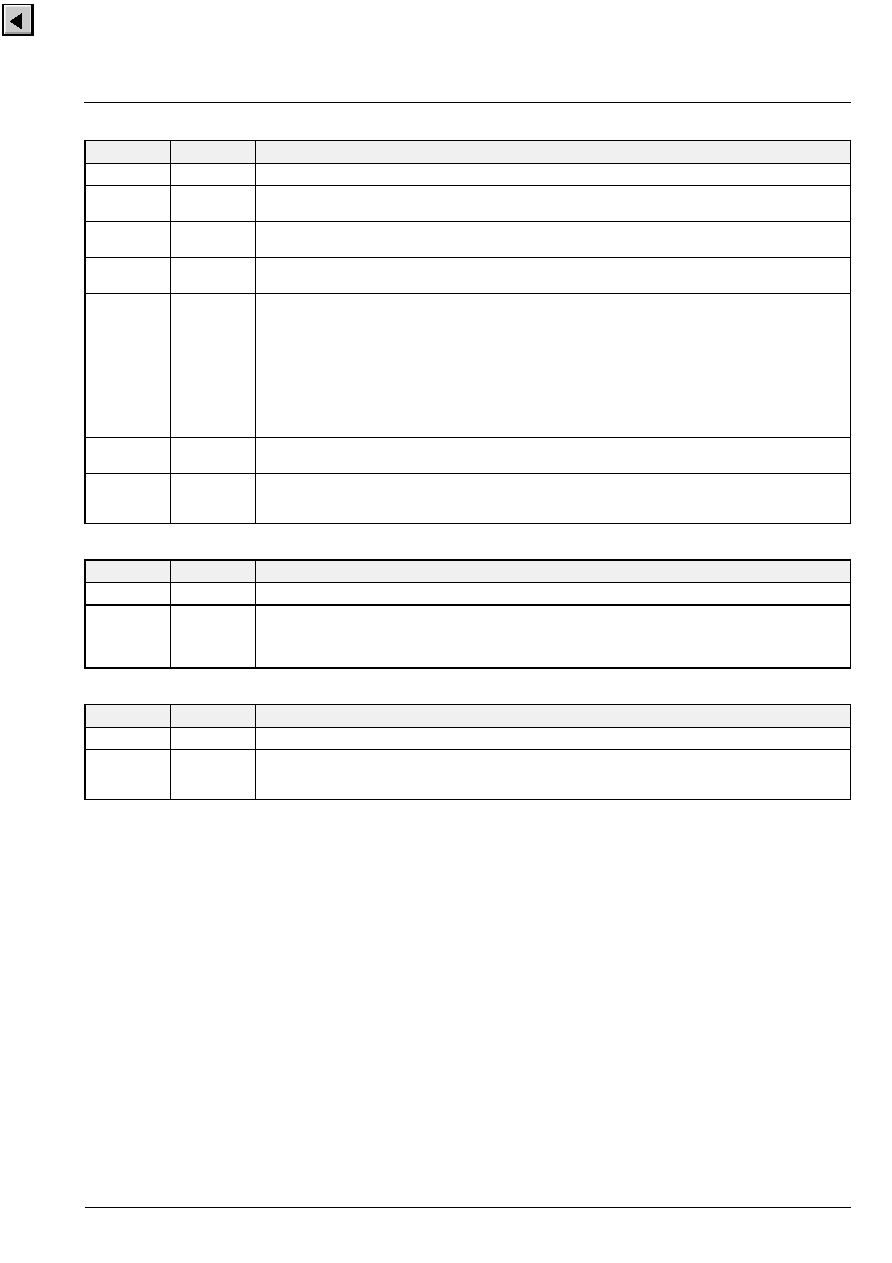

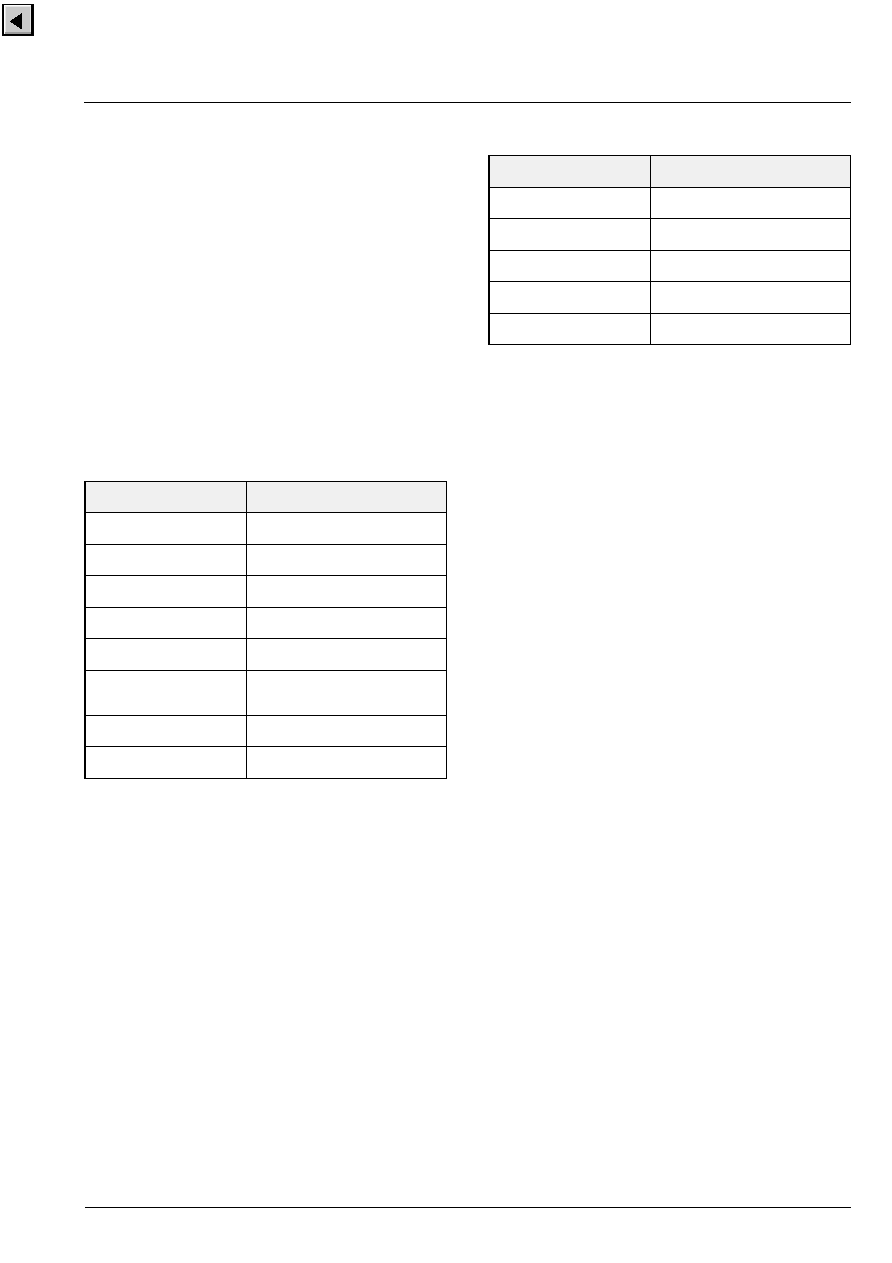

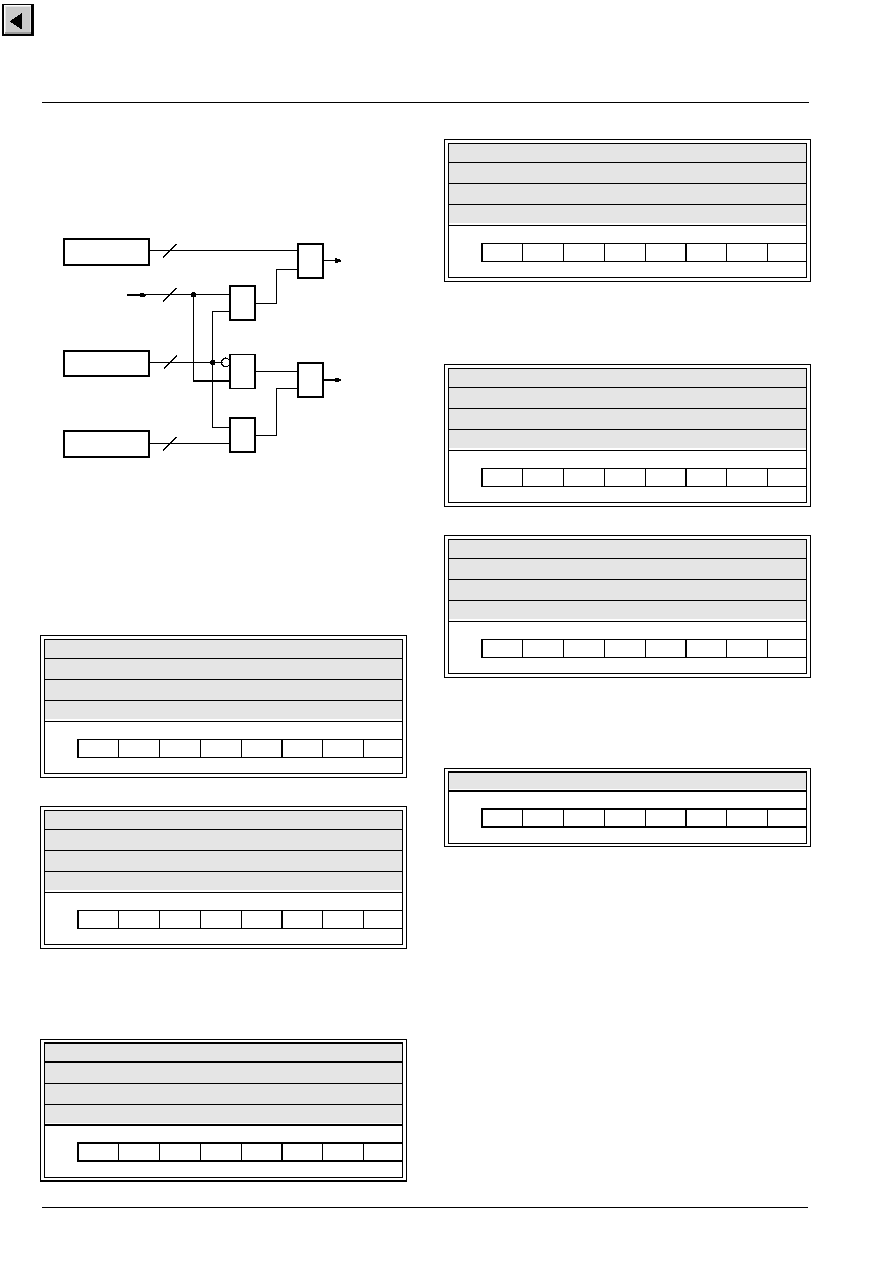

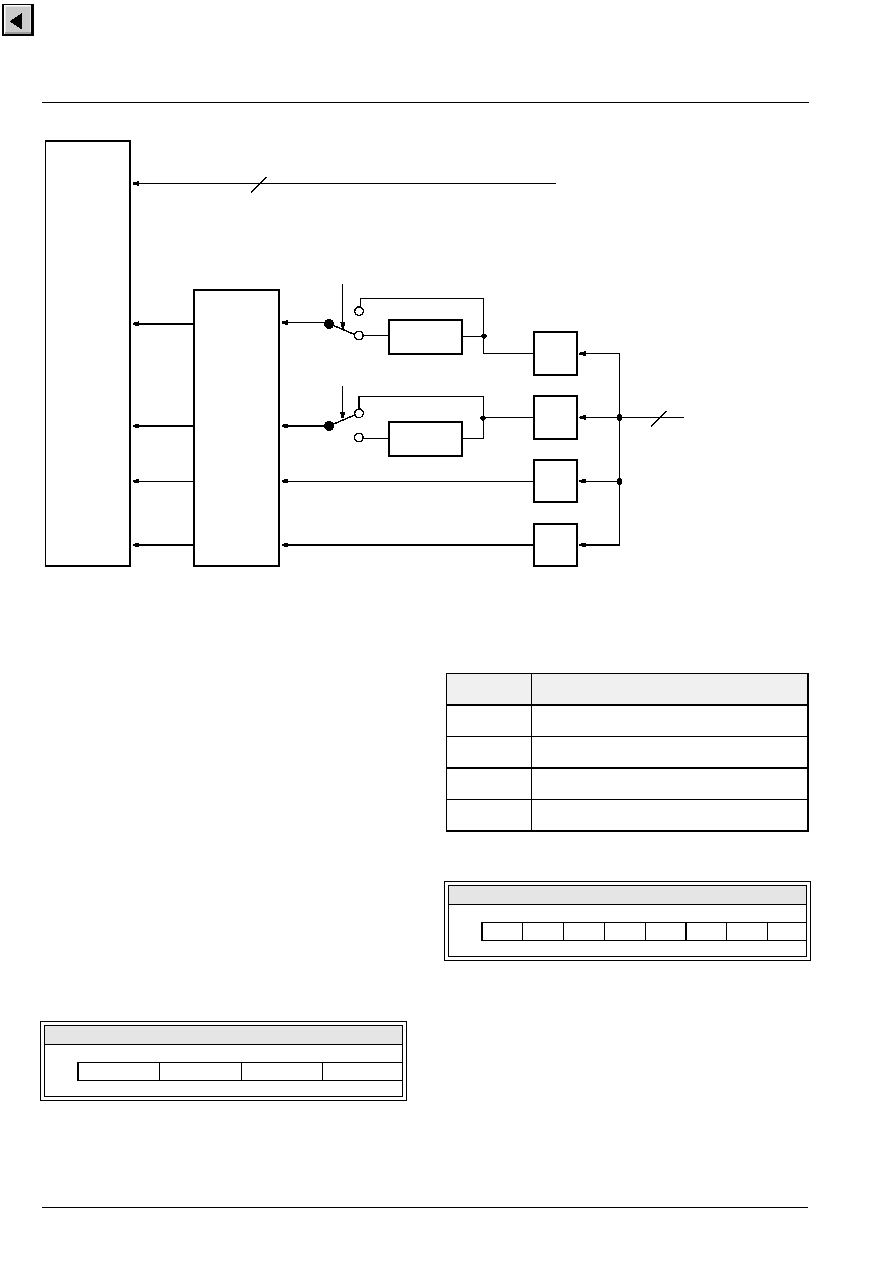

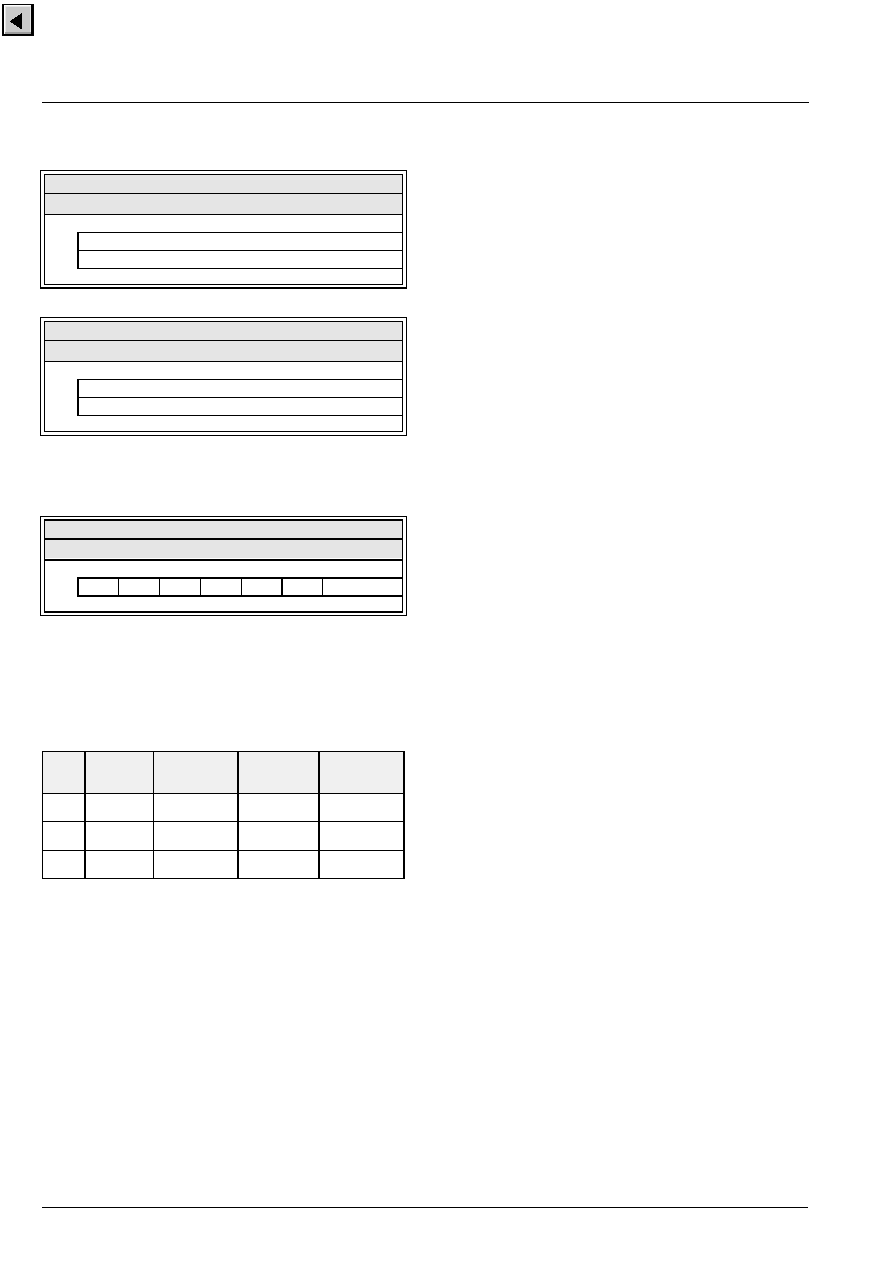

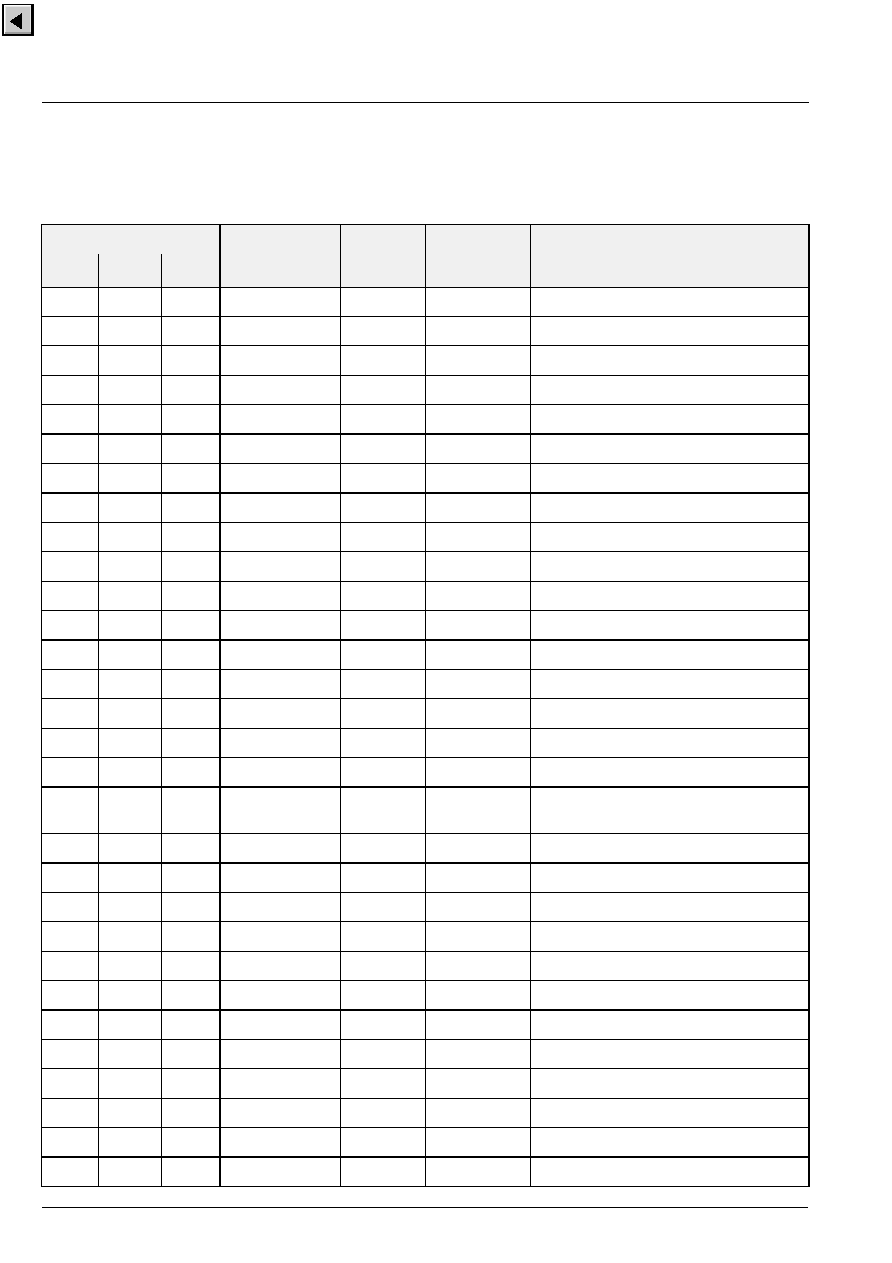

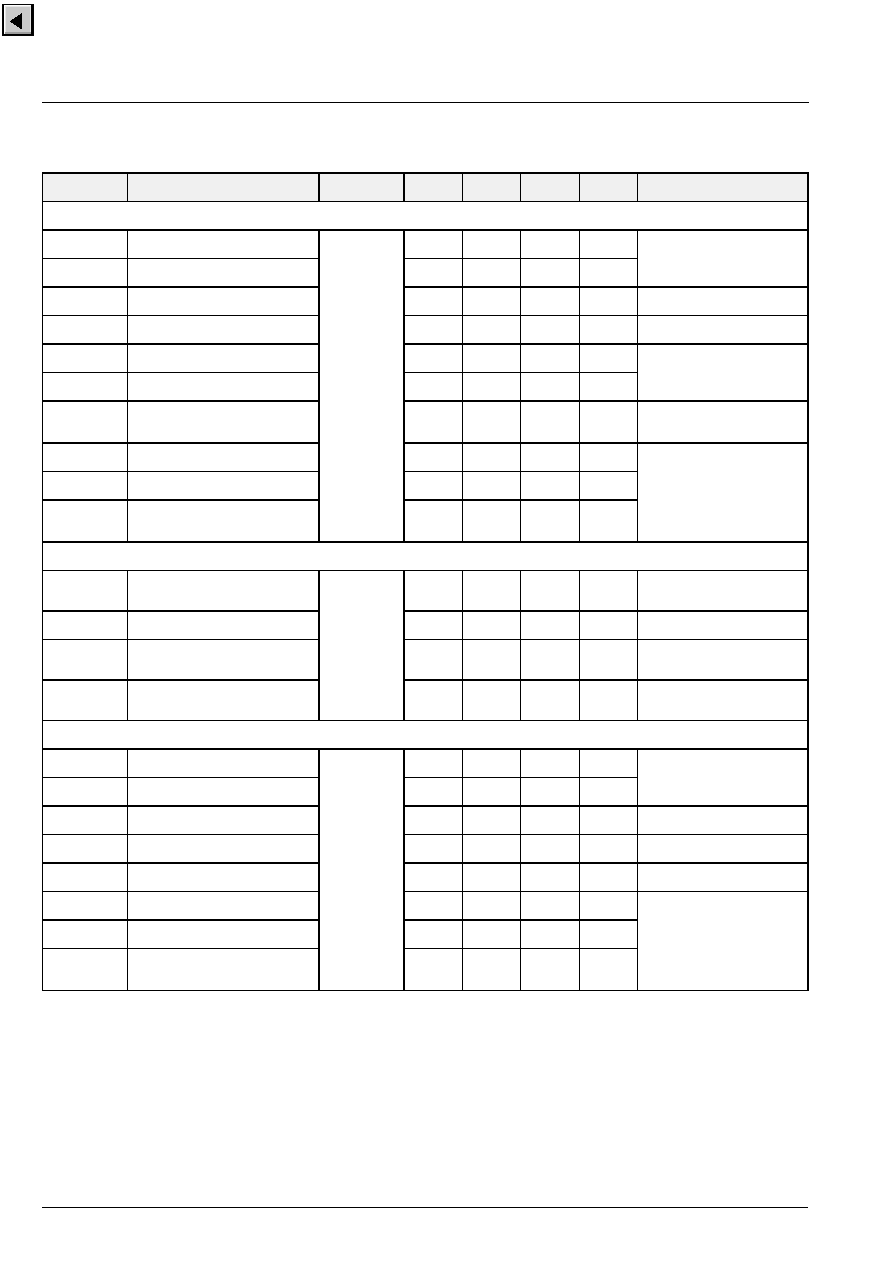

Fig. 1�1: VCT 38xxA family overview

A

d

ap

t

i

ve

C

o

m

b

F

i

l

t

er

Pa

n

o

r

a

m

a

S

c

a

l

e

r

P

i

ct

u

r

e

Imp

r

o

veme

n

t

s

(Color

T

r

a

n

s

i

e

n

t

Impr

o

v

.,

S

o

ft

L

i

m

i

te

r

,

Bl

a

c

k

-

L

e

v

e

l Ex

pa

nde

r

)

1

0

P

a

ge

T

e

let

x

t

VCT 38xxA

Family

VCT 3801A

e

x

t

.

P

r

og. M

e

mor

y

8

-

Bi

t

M

i

c

r

oc

ontr

o

l

l

e

r

9

6

kB R

O

M, 1

kB RAM

Fla

s

h Opt

i

o

n

Color

Dec

o

d

e

r

T

u

b

e

Contr

o

l

OSD Ge

ne

ra

tor

A

udio Contr

o

l

ex

t

.

P

a

g

e

M

e

m

o

r

y

VCT 3803A

VCT 3804A

VCT 3811A

VCT 3831A

VCT 3832A

VCT 3833A

VCT 3834A

PM

QFP1

2

8

PM

QFP1

2

8

VCT 3802A

1

P

a

g

e

T

e

let

x

t

VCT 38xxA

ADVANCE INFORMATION

8

Micronas

1.1. Features

1.1.1. Video Features

� four composite video inputs, two S-VHS inputs

� analog YC

r

C

b

input

� composite video monitor

� multistandard color decoder (1 crystal)

� multistandard sync decoder

� black-line detector

� adaptive 2H comb filter Y/C separator

� horizontal scaling (0.25 to 4)

� Panoramavision

� black-level expander

� dynamic peaking

� soft limiter (gamma correction)

� color transient improvement

� programmable RGB matrix

� analog RGB/Fastblank input

� half-contrast switch

� picture frame generator

� scan velocity modulation output

� high-performance H/V deflection

� angle and bow correction

� separate ADC for tube measurements

� EHT compensation

1.1.2. Microcontroller Features

� 8-bit, 10-MHz CPU (65C02)

� 96 kB program ROM on chip

� 1 kB program RAM on chip

� memory banking

� 16-input, 16-level interrupt controller

� patch modul for 10 ROM locations

� two 16-bit reloadable timers

� capture compare modul

� watchdog timer

� 14-bit PWM for voltage synthesis

� four 8-bit PWMs

� 10-bit ADC with 15:1 input MUX

� I

2

C bus master interface

� 24 programmable I/O ports

1.1.3. OSD Features

� 3 kB OSD RAM on chip

� WST level 1.5 compliant

� WST level 2 parallel attributes

� 32 foreground/background colors

� programmable color look-up table

� 1024 mask programmable characters

� 24 national languages

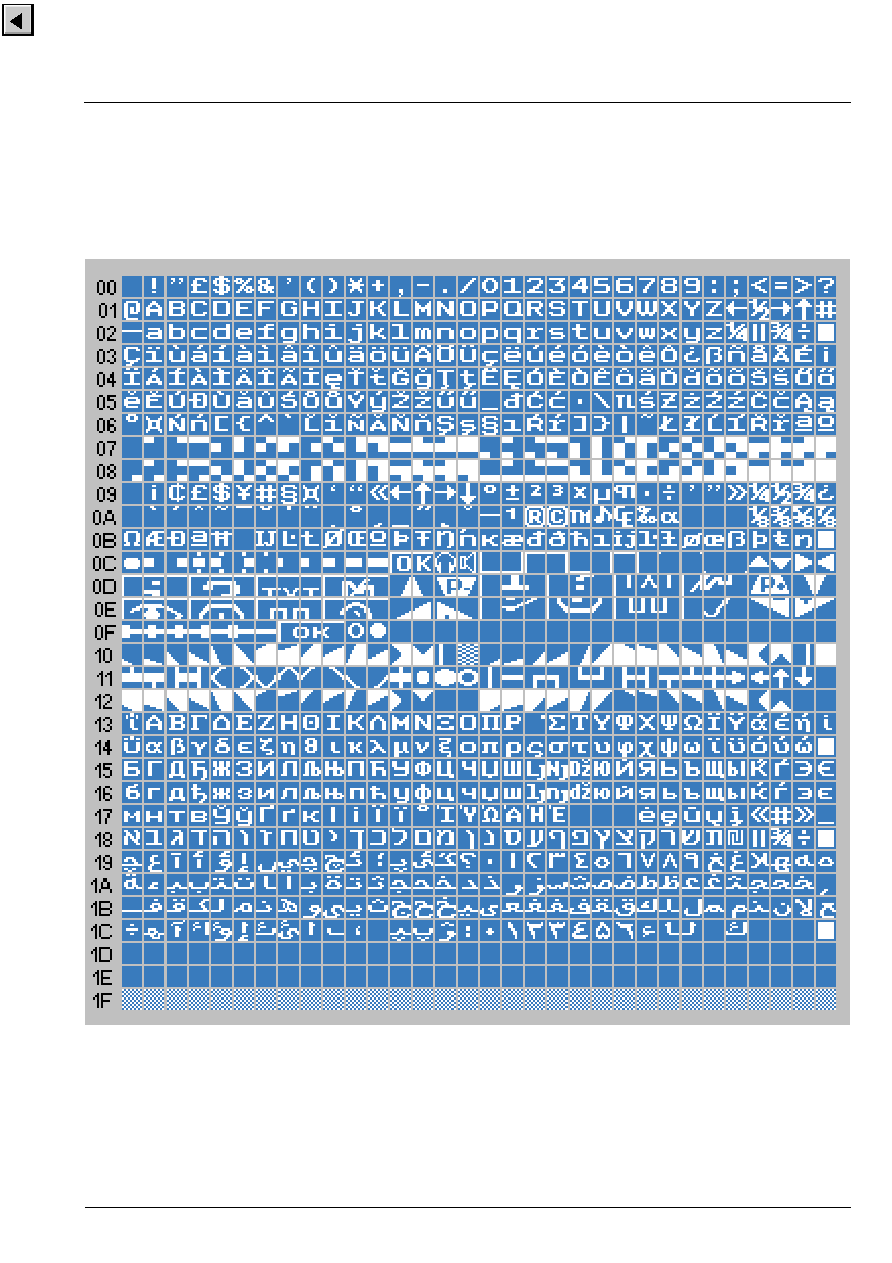

(Latin, Cyrillic, Greek, Arabic, Farsi, Hebrew)

� character matrix 8x8, 8x10, 8x13, 10x8, 10x10, 10x13

� vertical soft scroll

� 4-color mode for user font

1.1.4. Teletext Features

� four programmable video inputs

� acquisition is independent from display part

� adaptive data slicer

� signal quality detection

� WST, PDC, VPS, and WSS acquisition

� high-level command language

� EPG, FLOF, and TOP support

� 10 pages memory on chip

� up to 500 pages with external SRAM

1.1.5. Audio Features

� three mono inputs

� two mono outputs

� programmable channel select

� volume control for one mono channel

1.1.6. General Features

� submicron CMOS technology

� low-power standby mode

� single 20.25-MHz crystal

� 64-pin PSDIP package

� 128-pin PMQFP package

� emulator chip for software development

ADVANCE INFORMATION

VCT 38xxA

Micronas

9

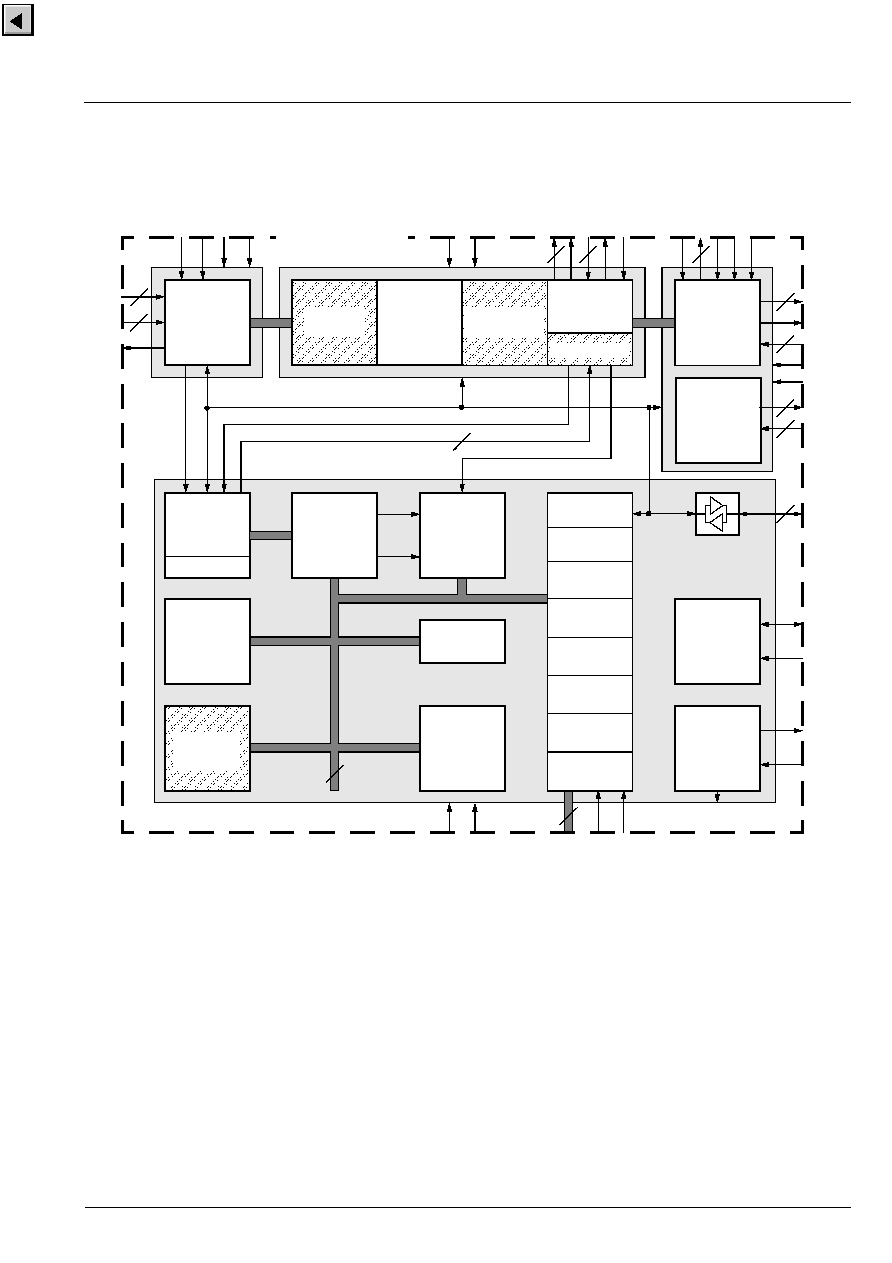

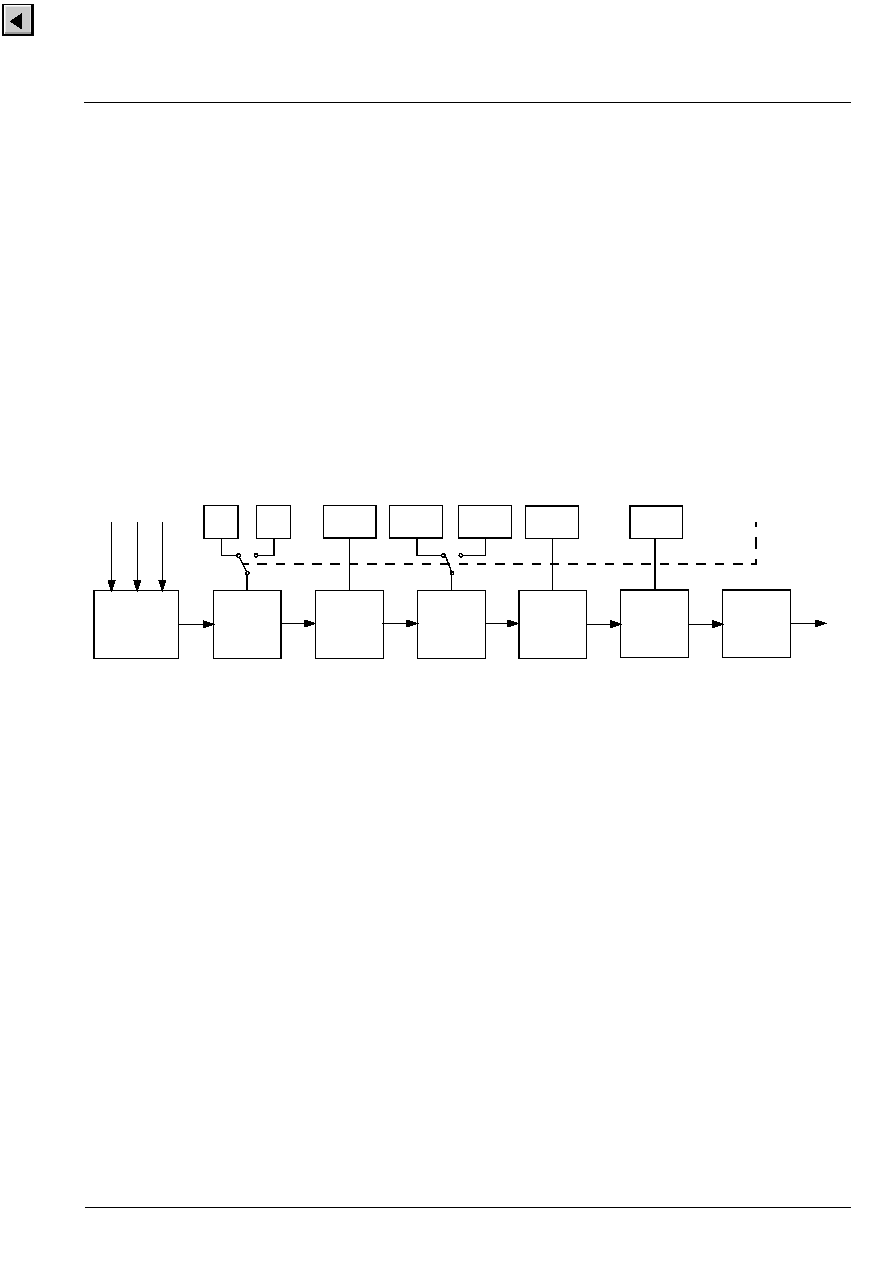

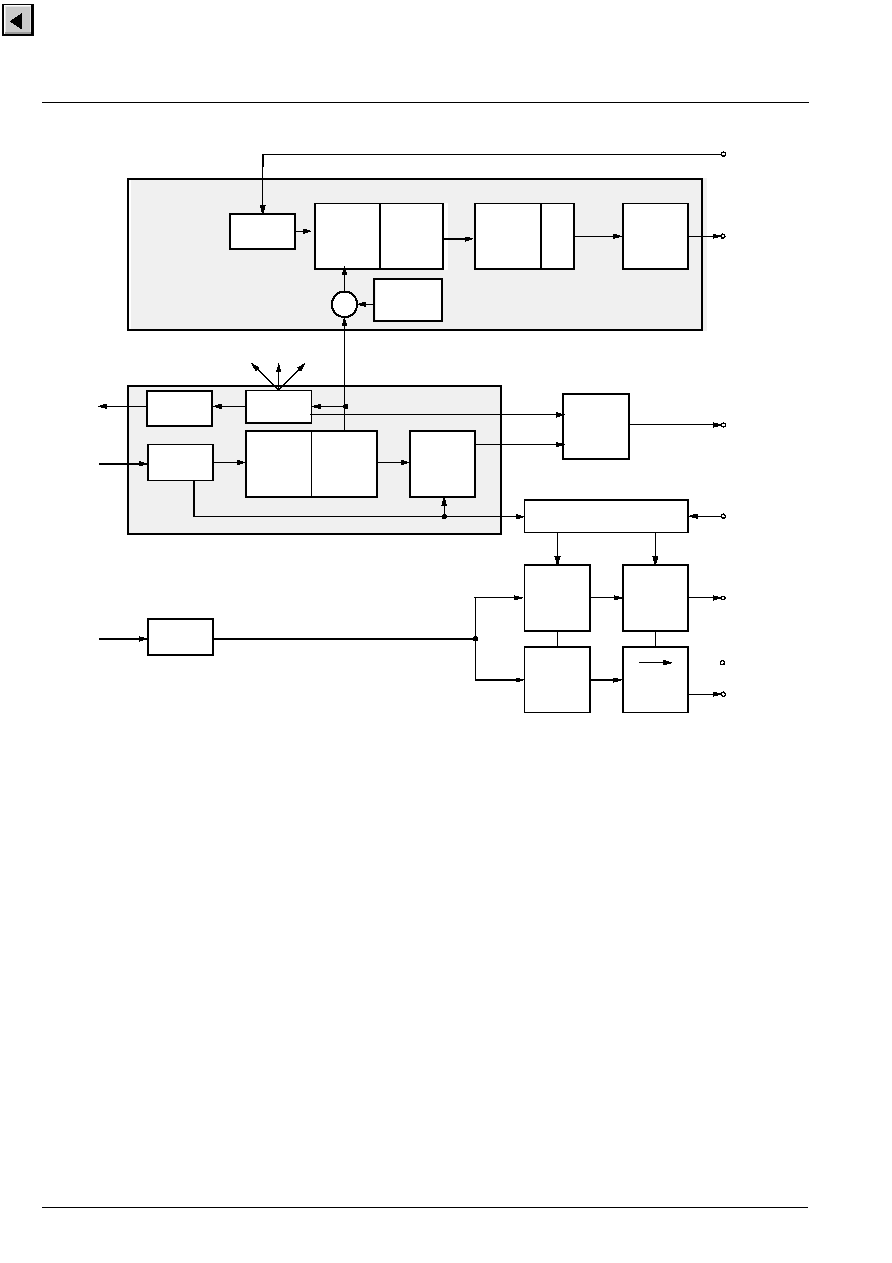

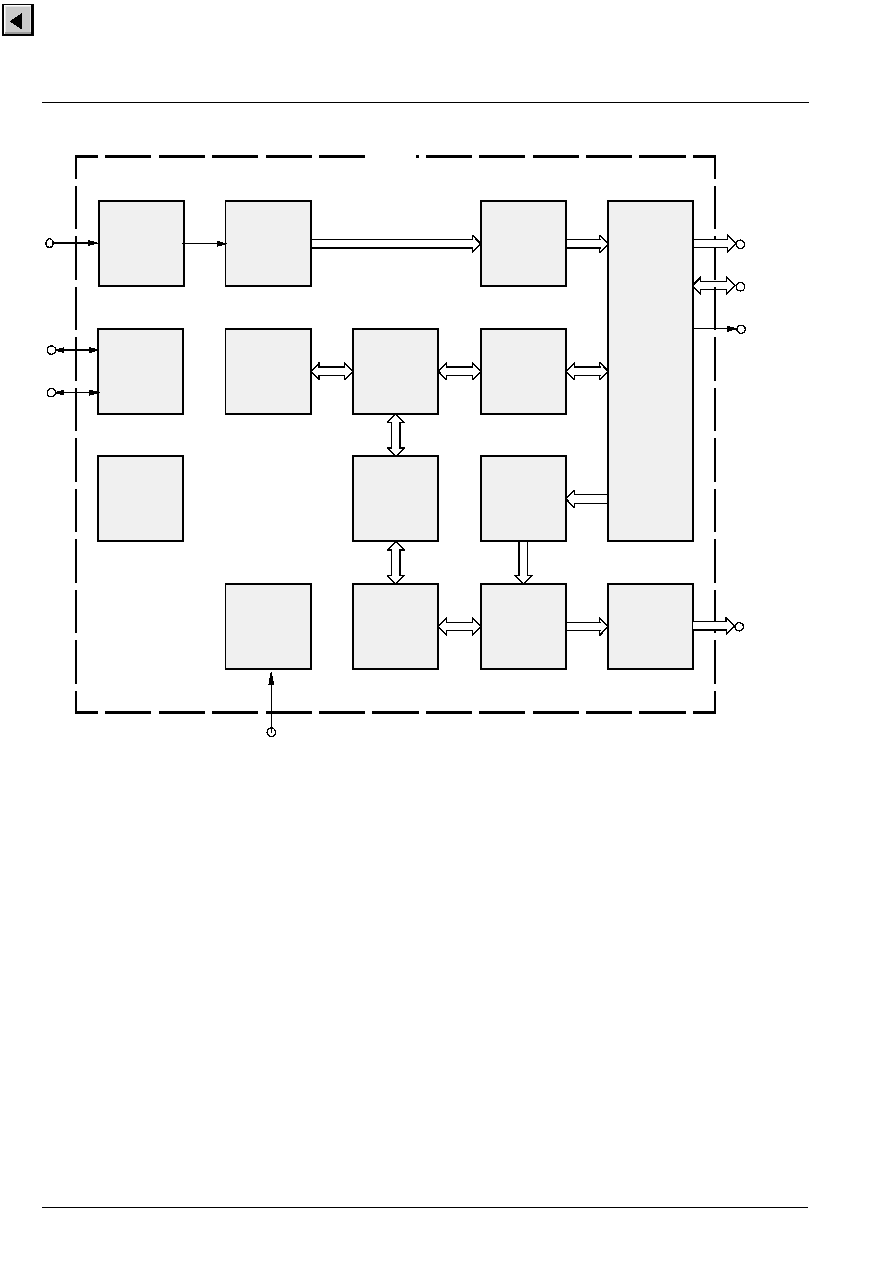

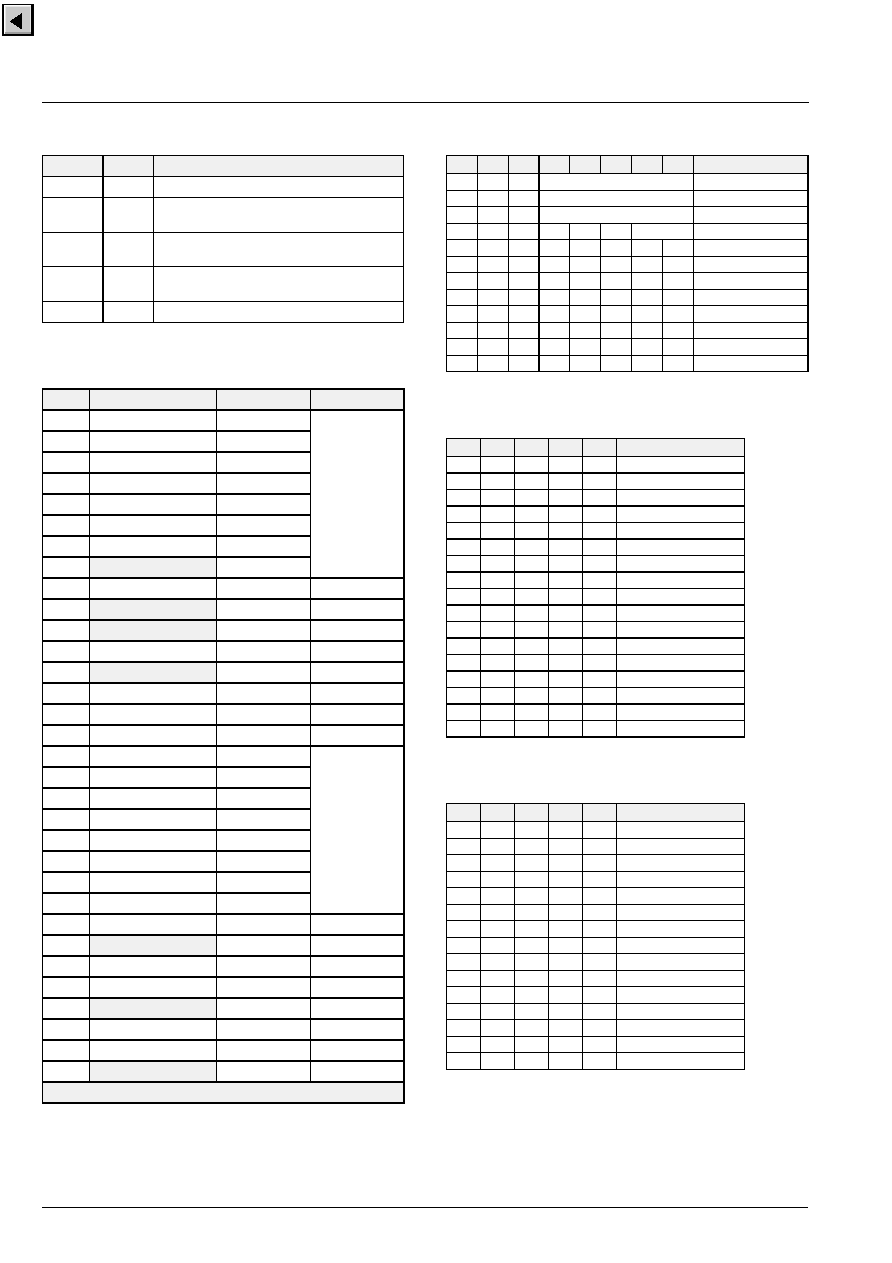

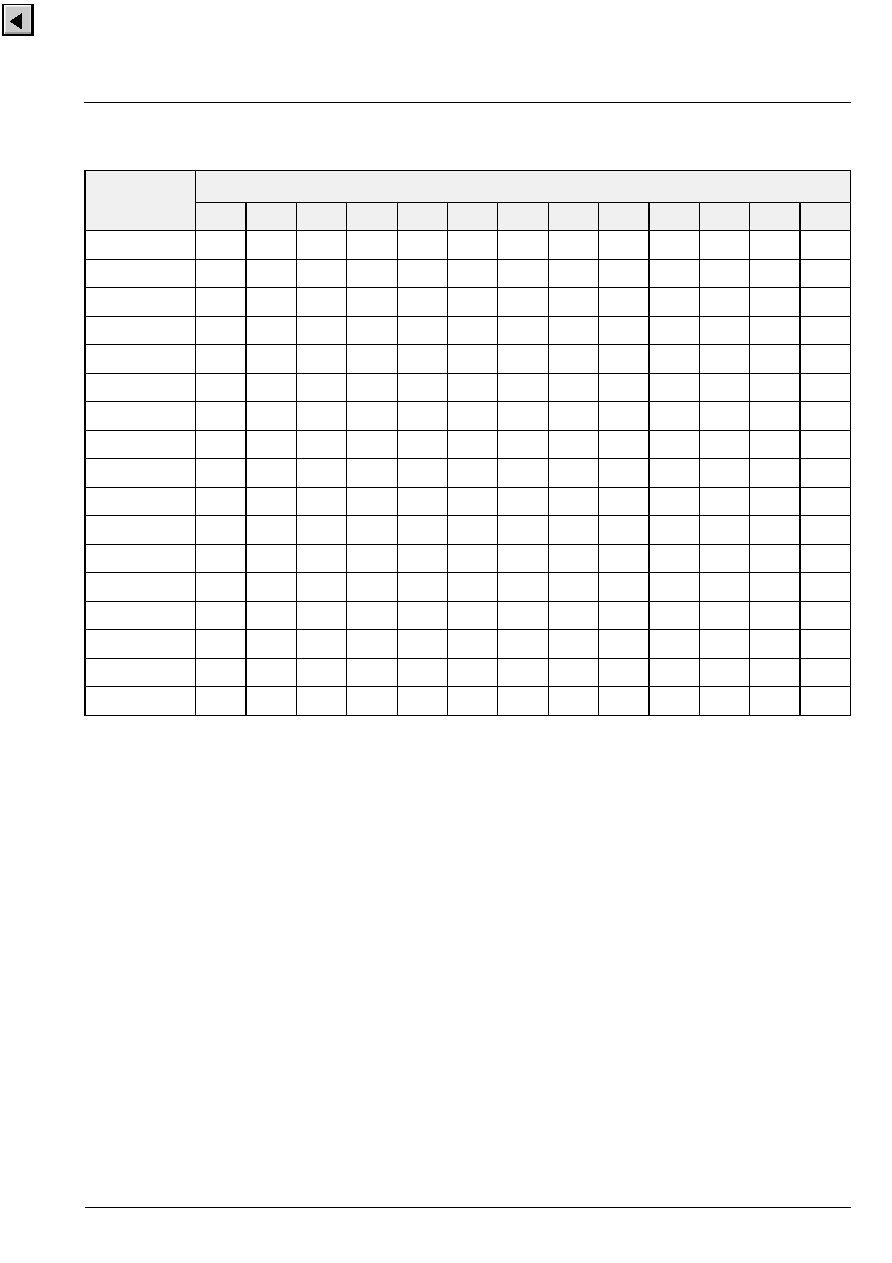

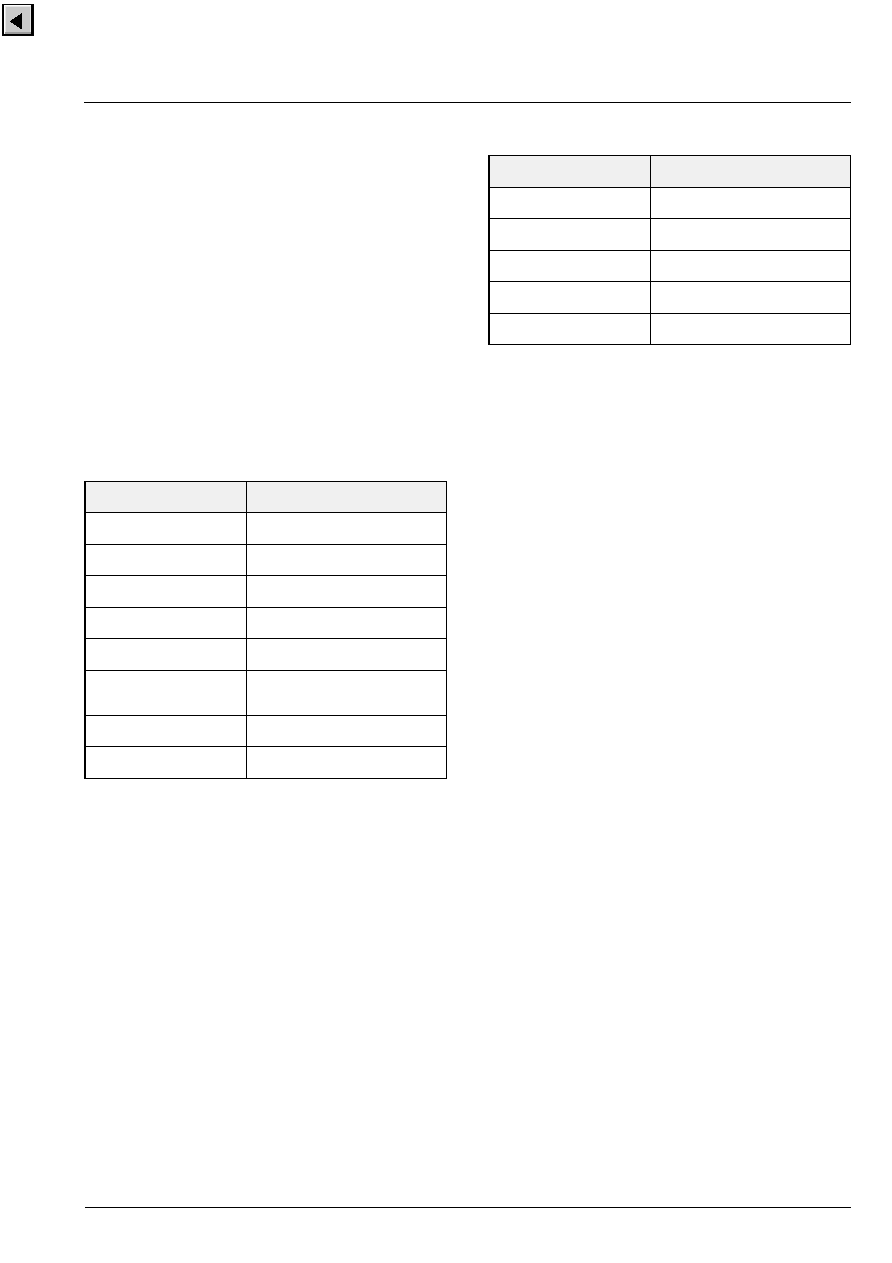

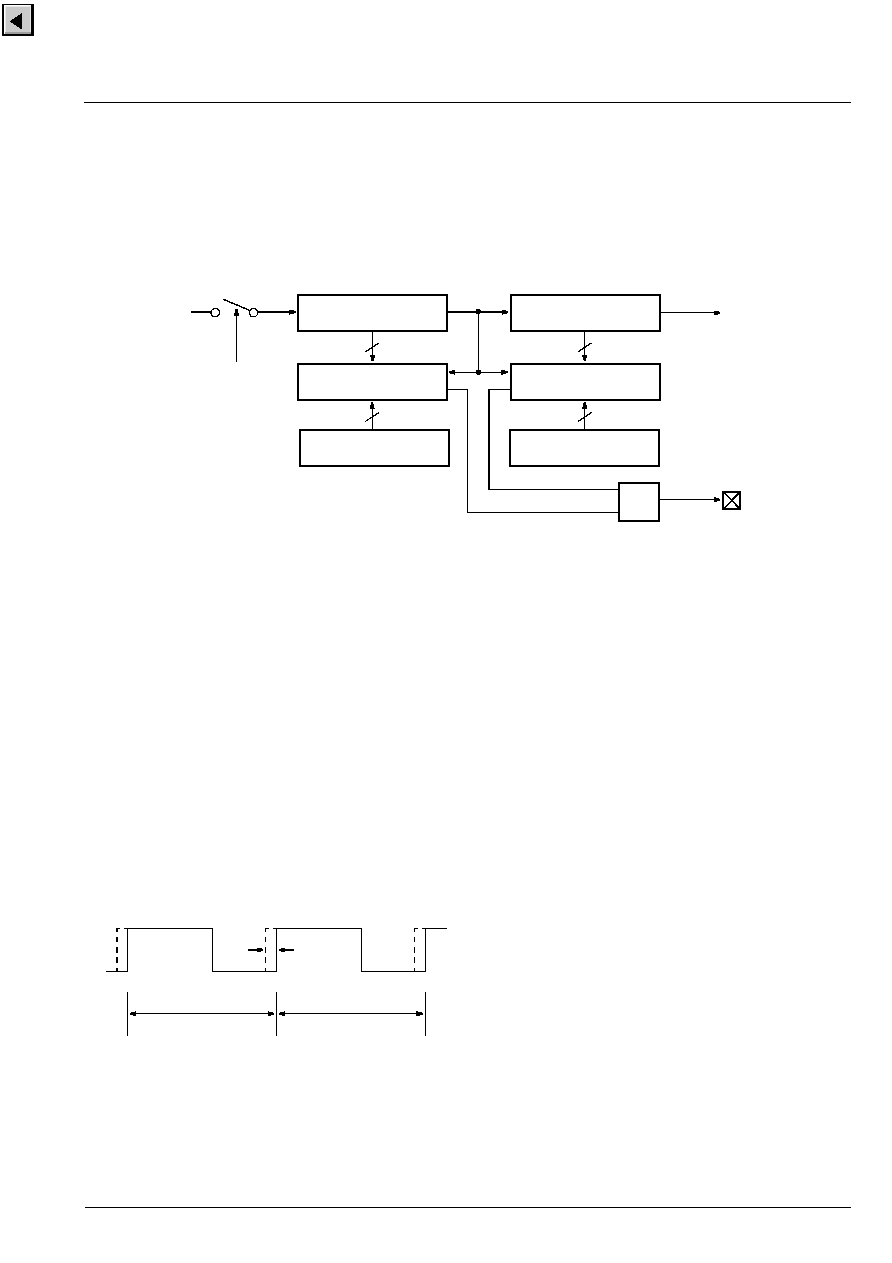

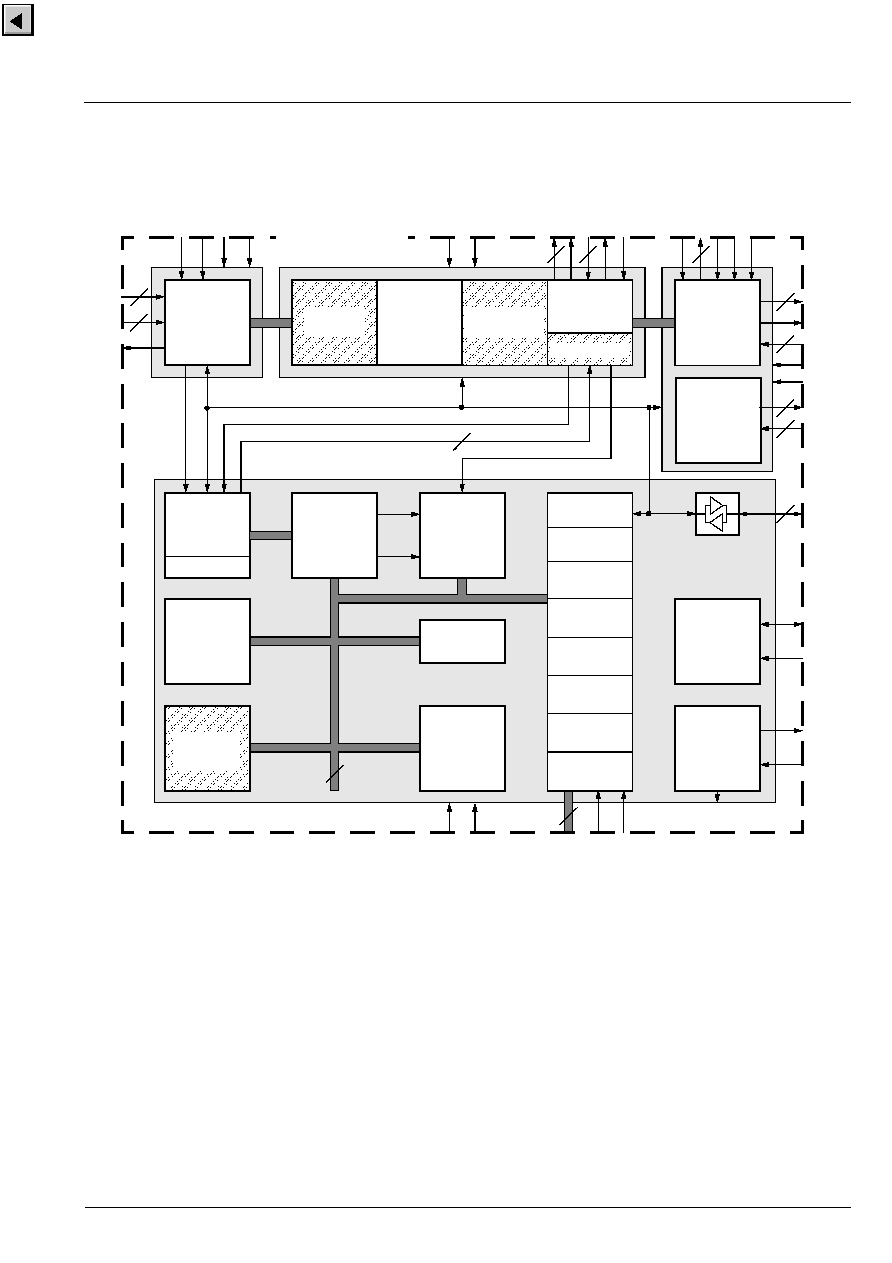

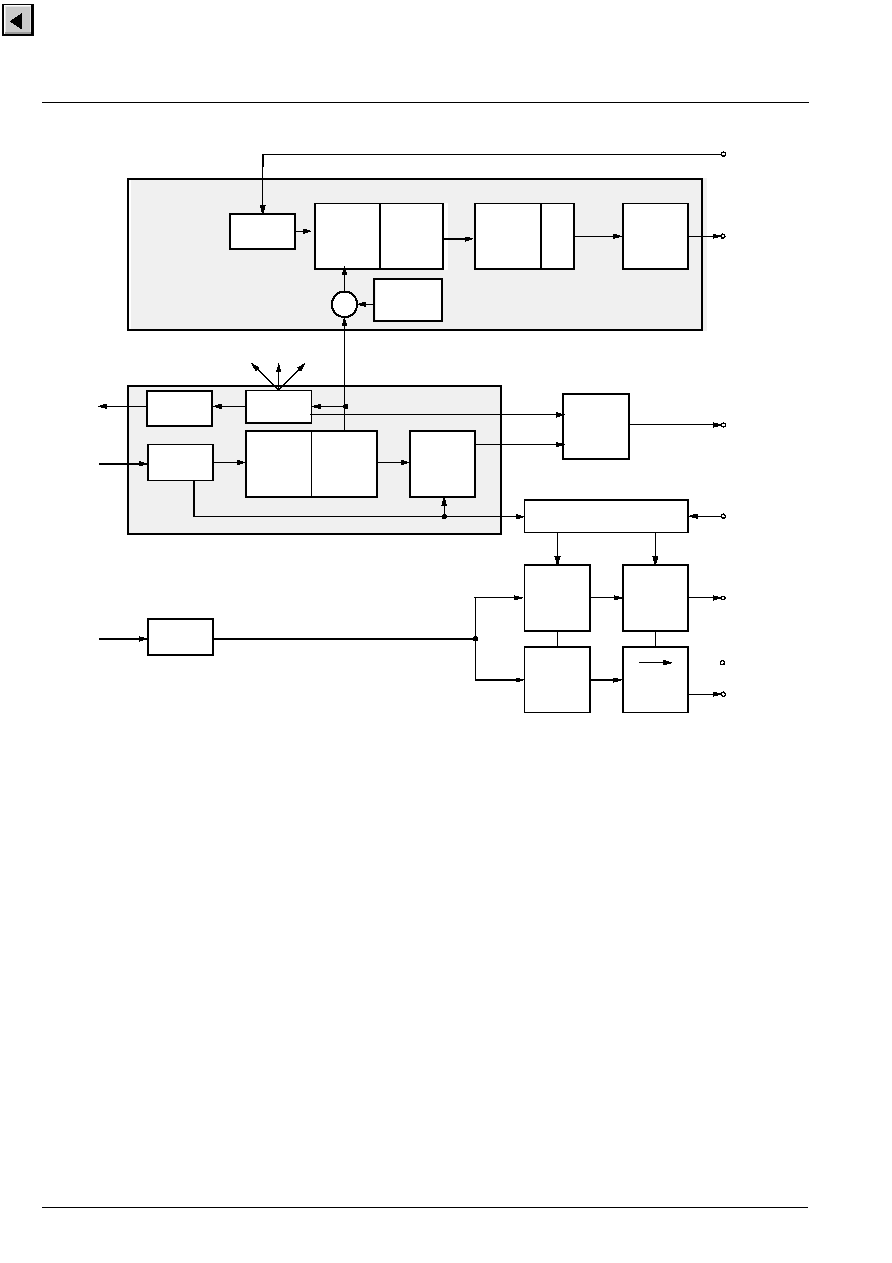

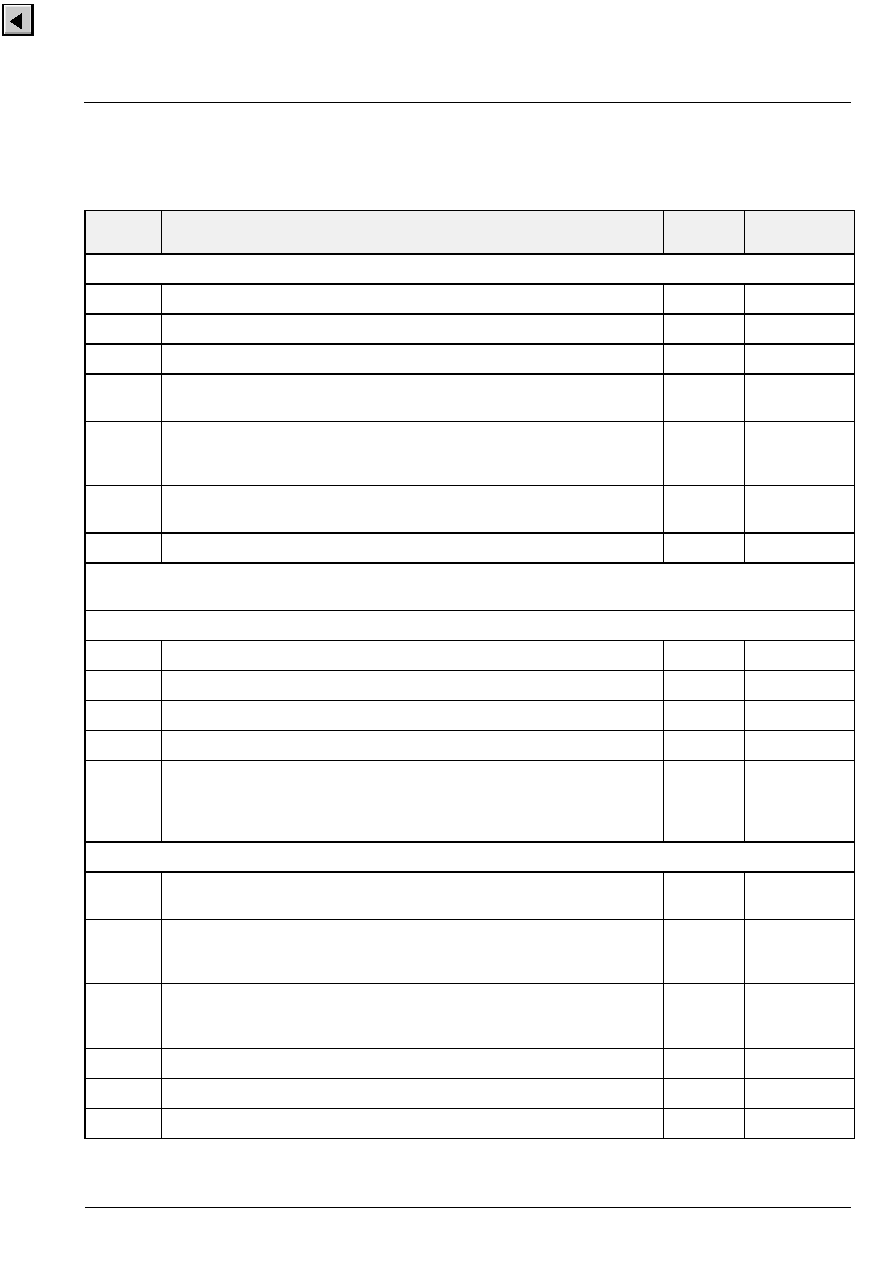

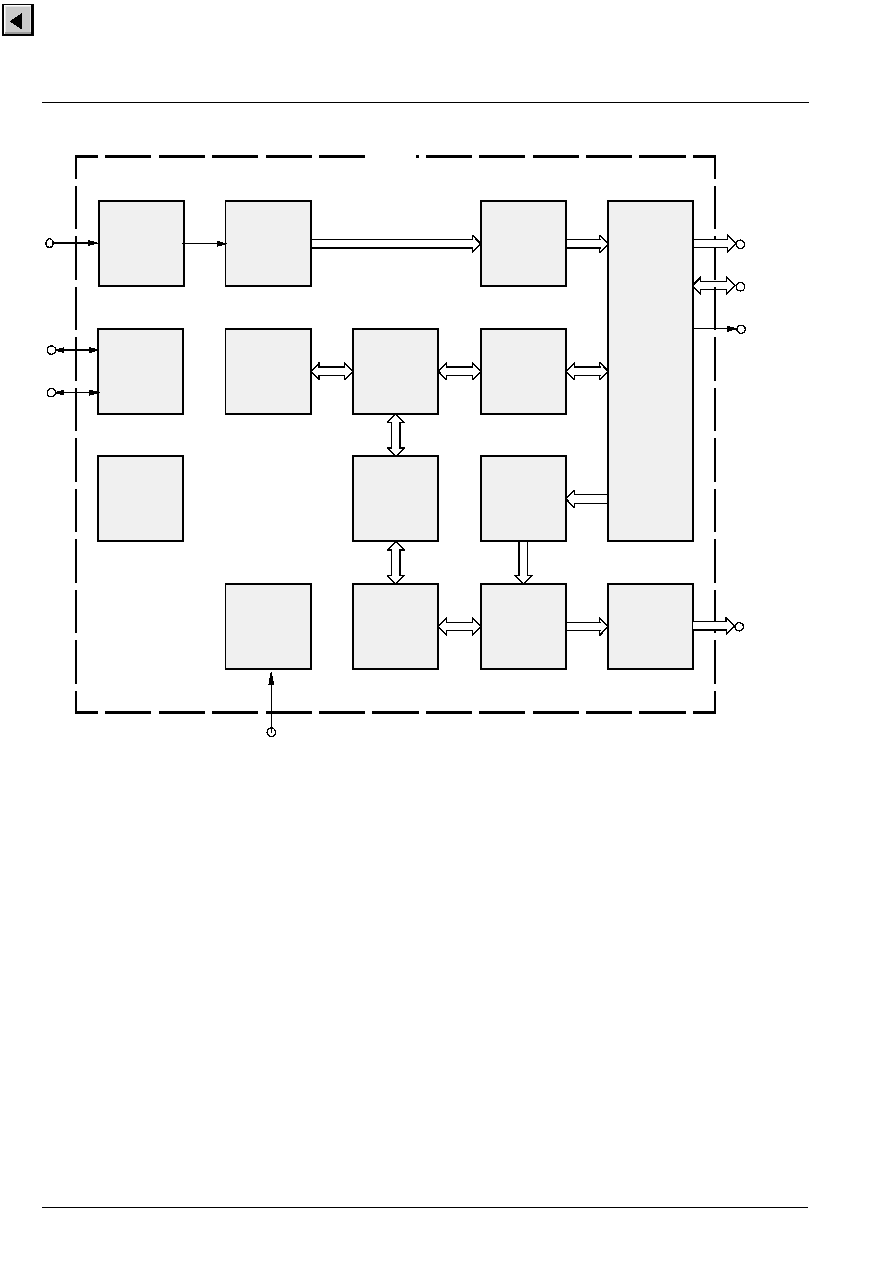

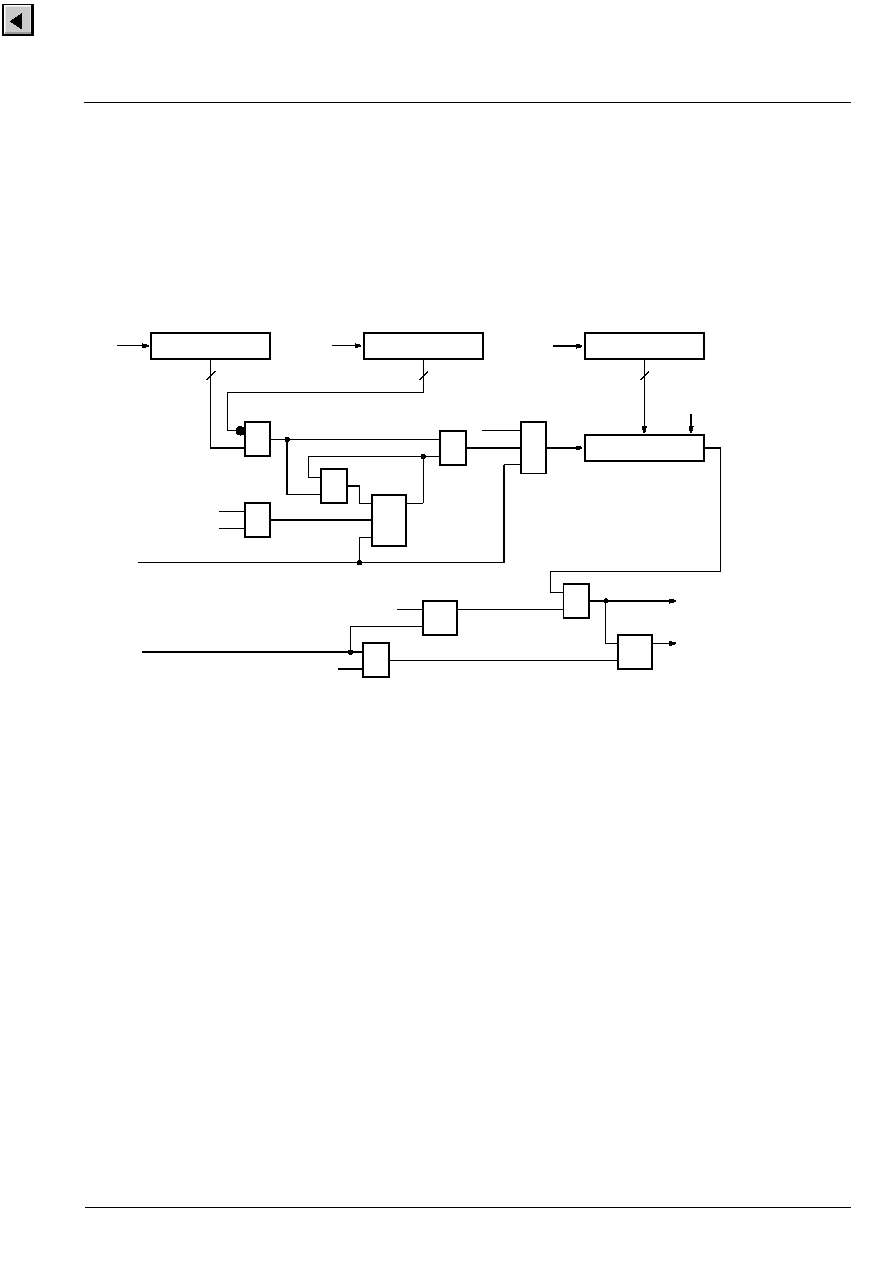

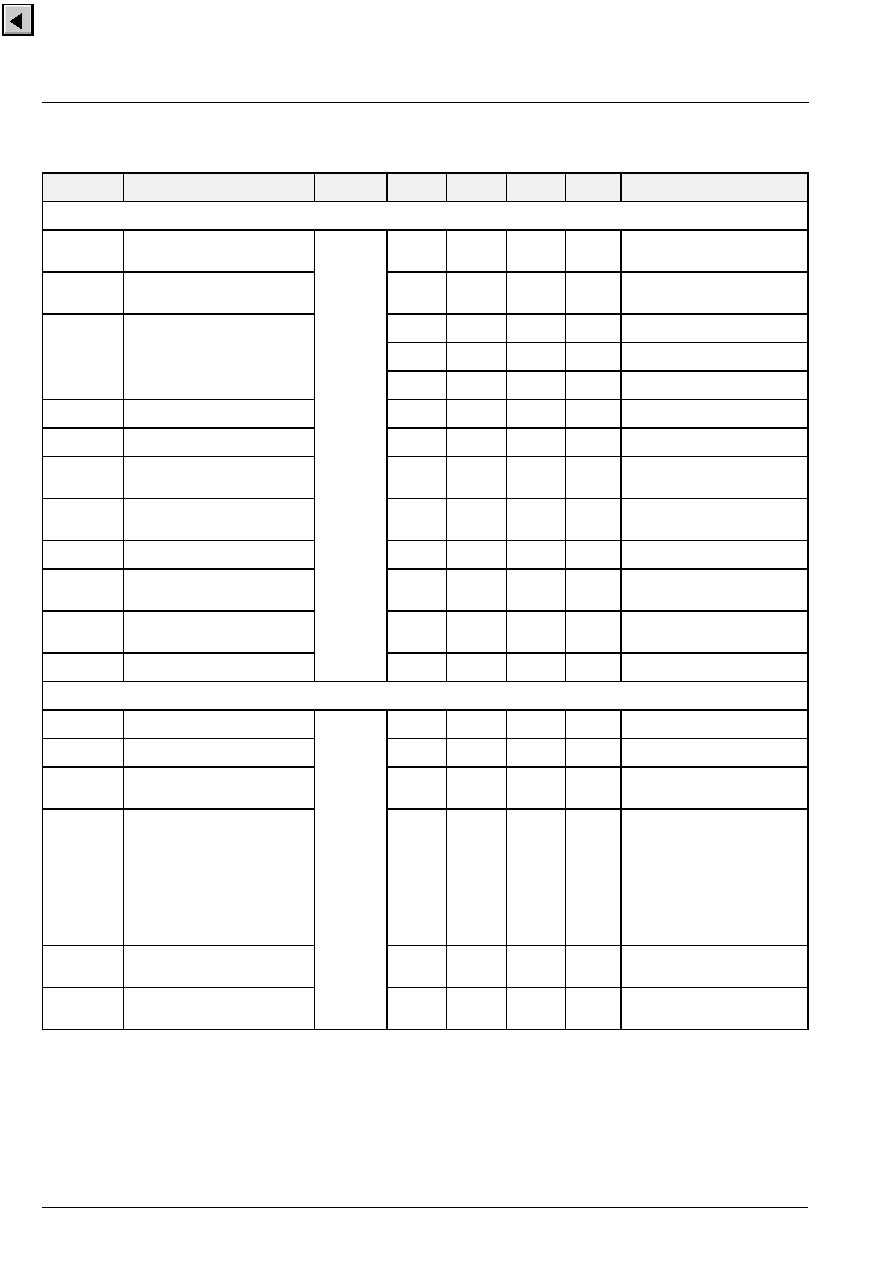

1.2. Chip Architecture

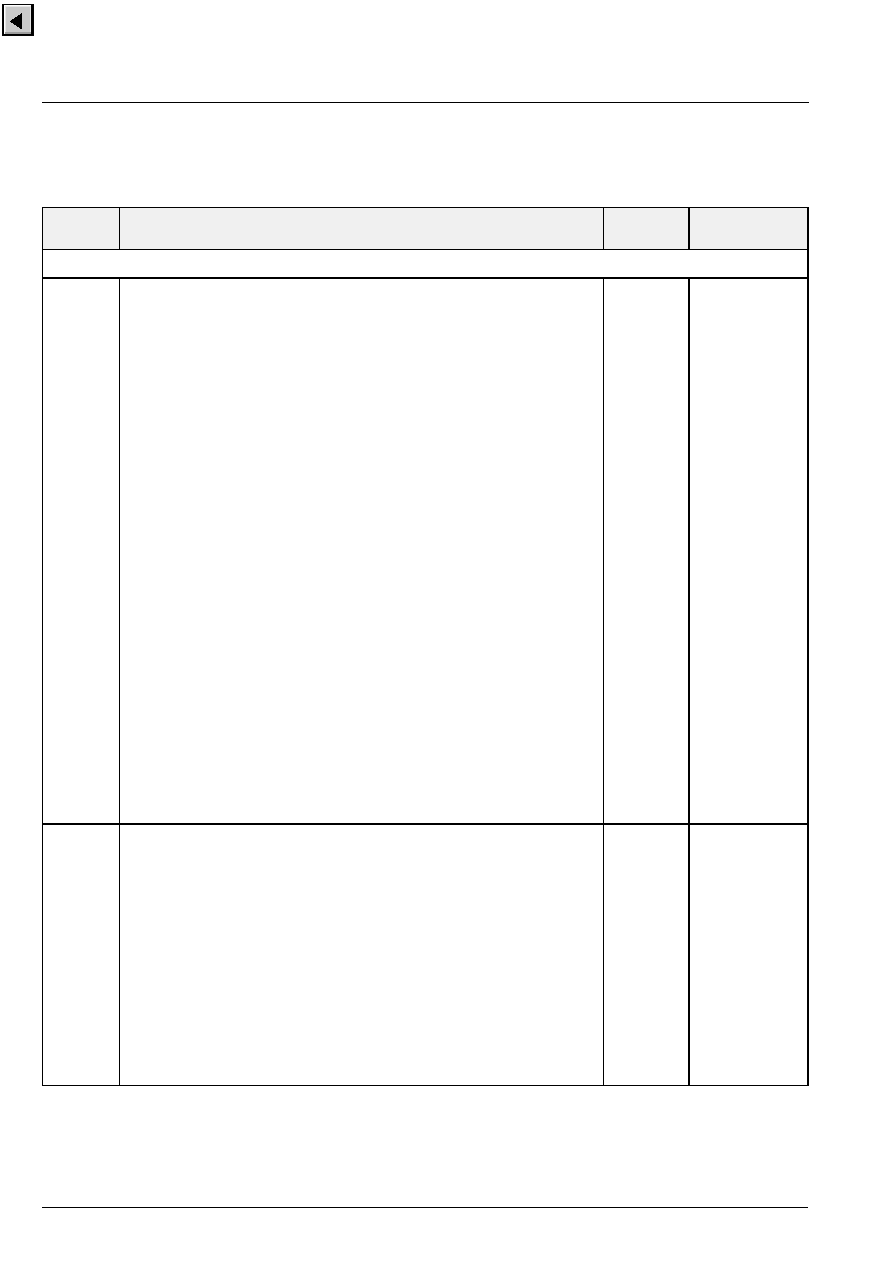

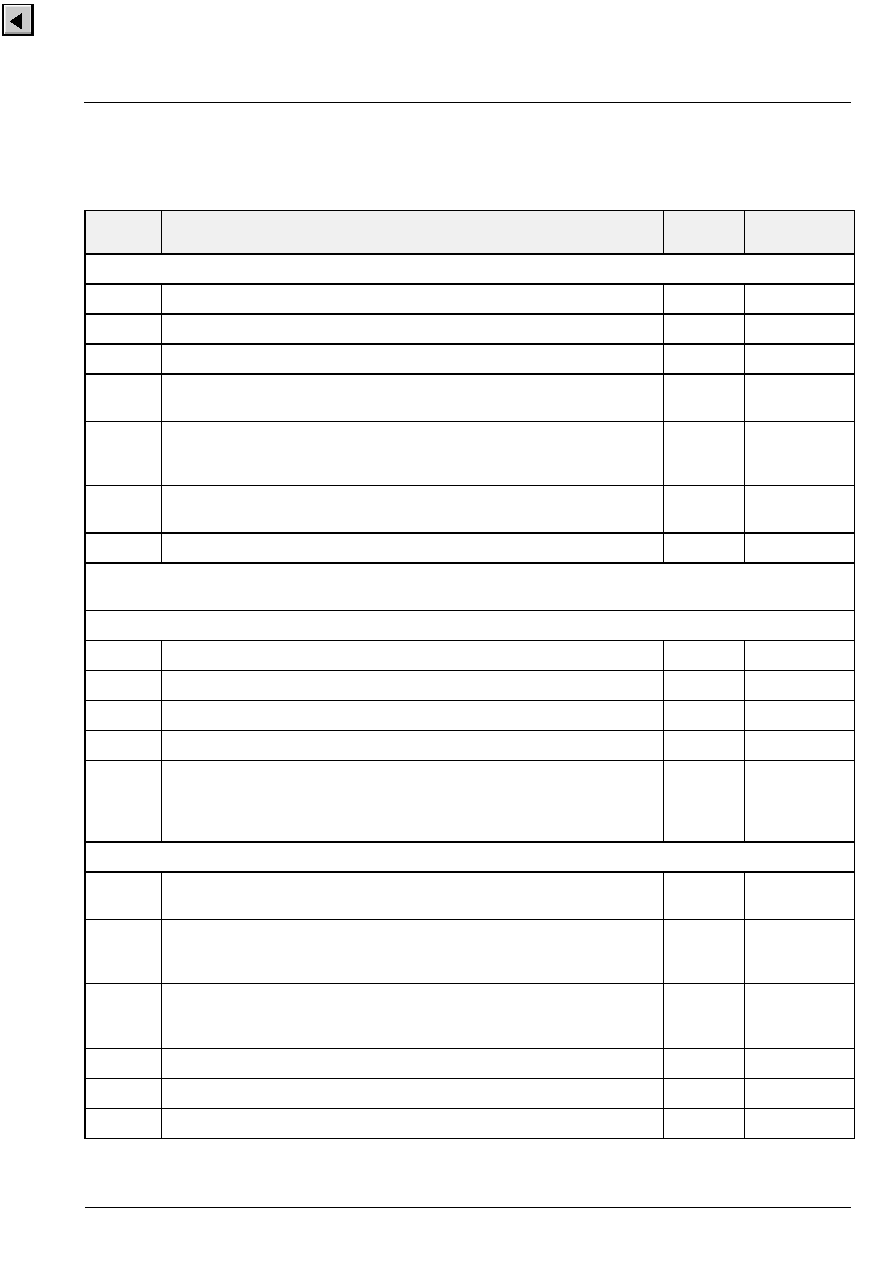

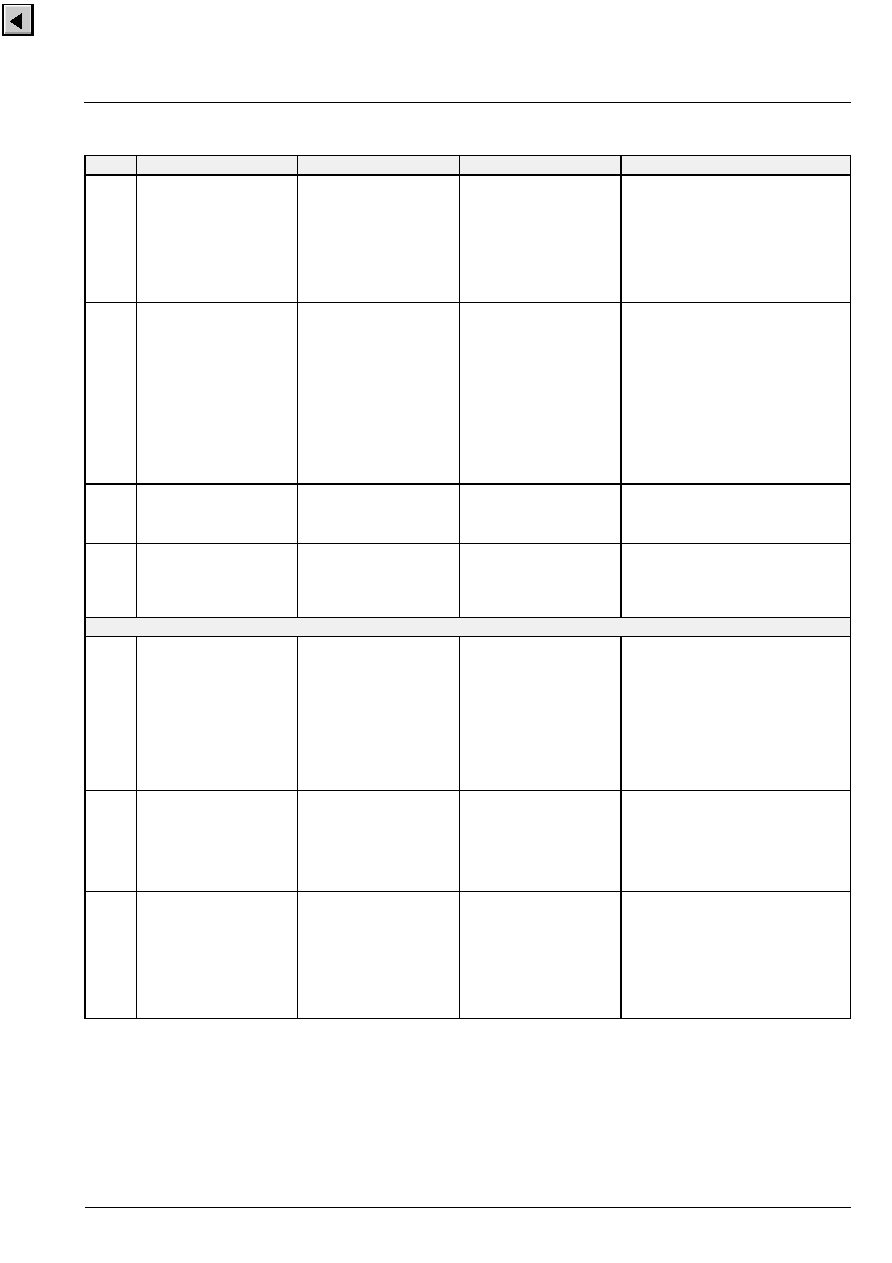

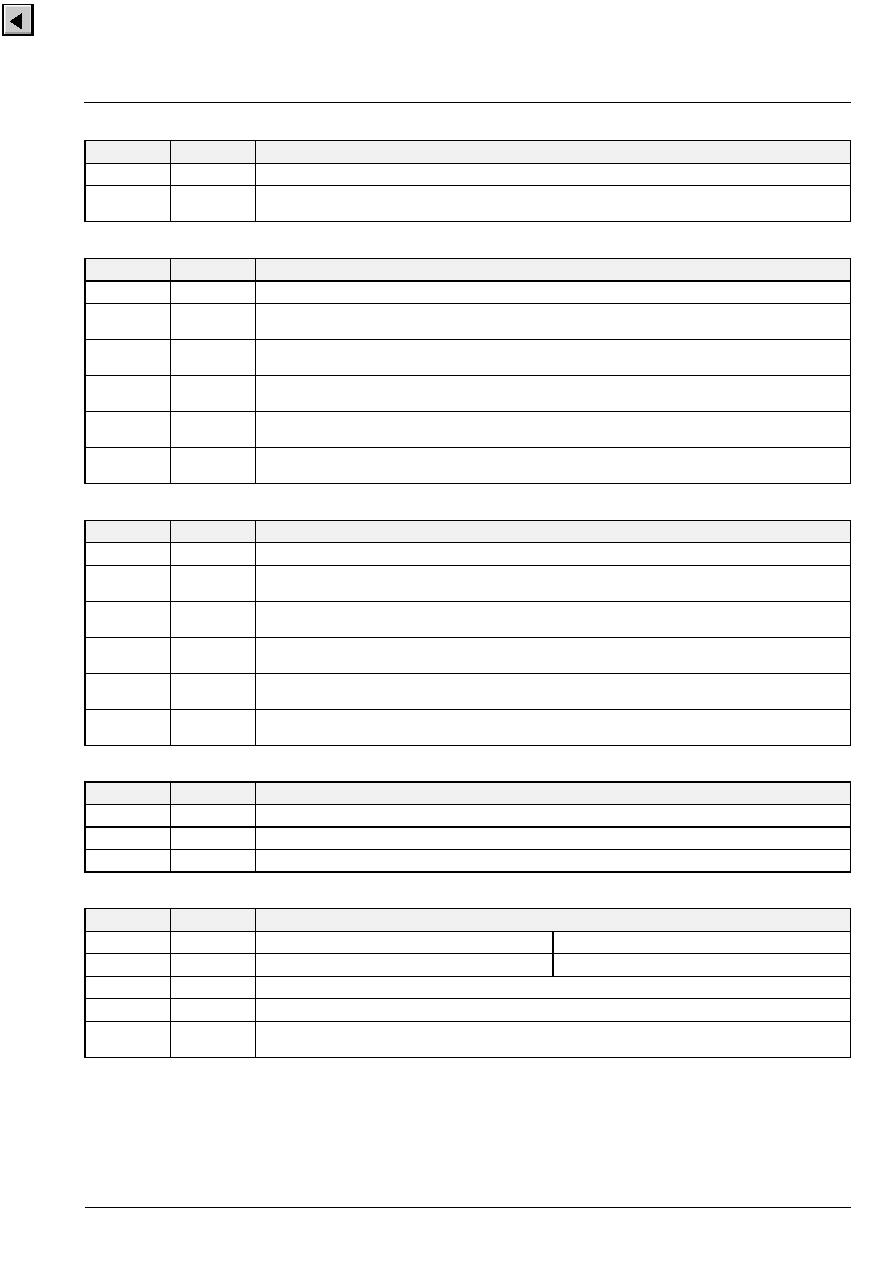

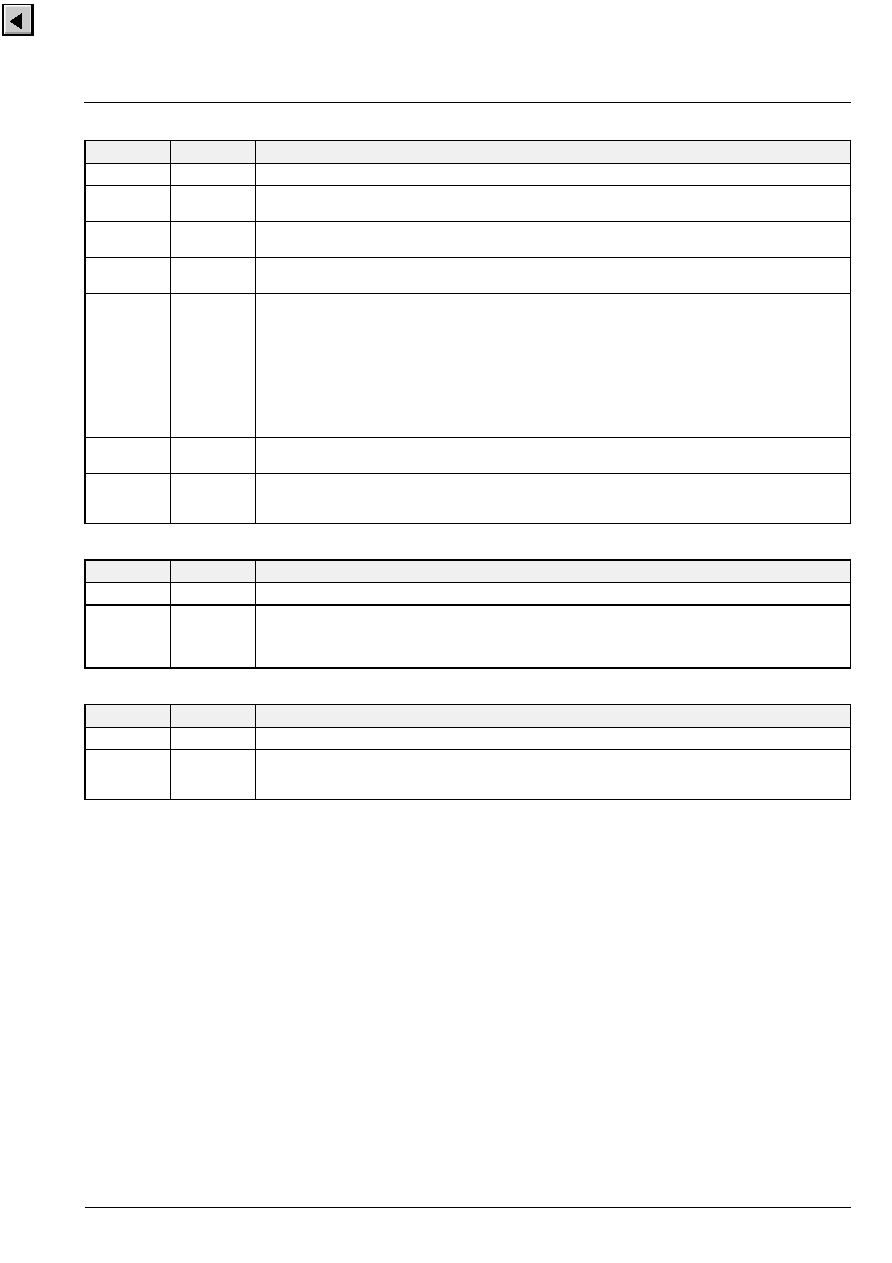

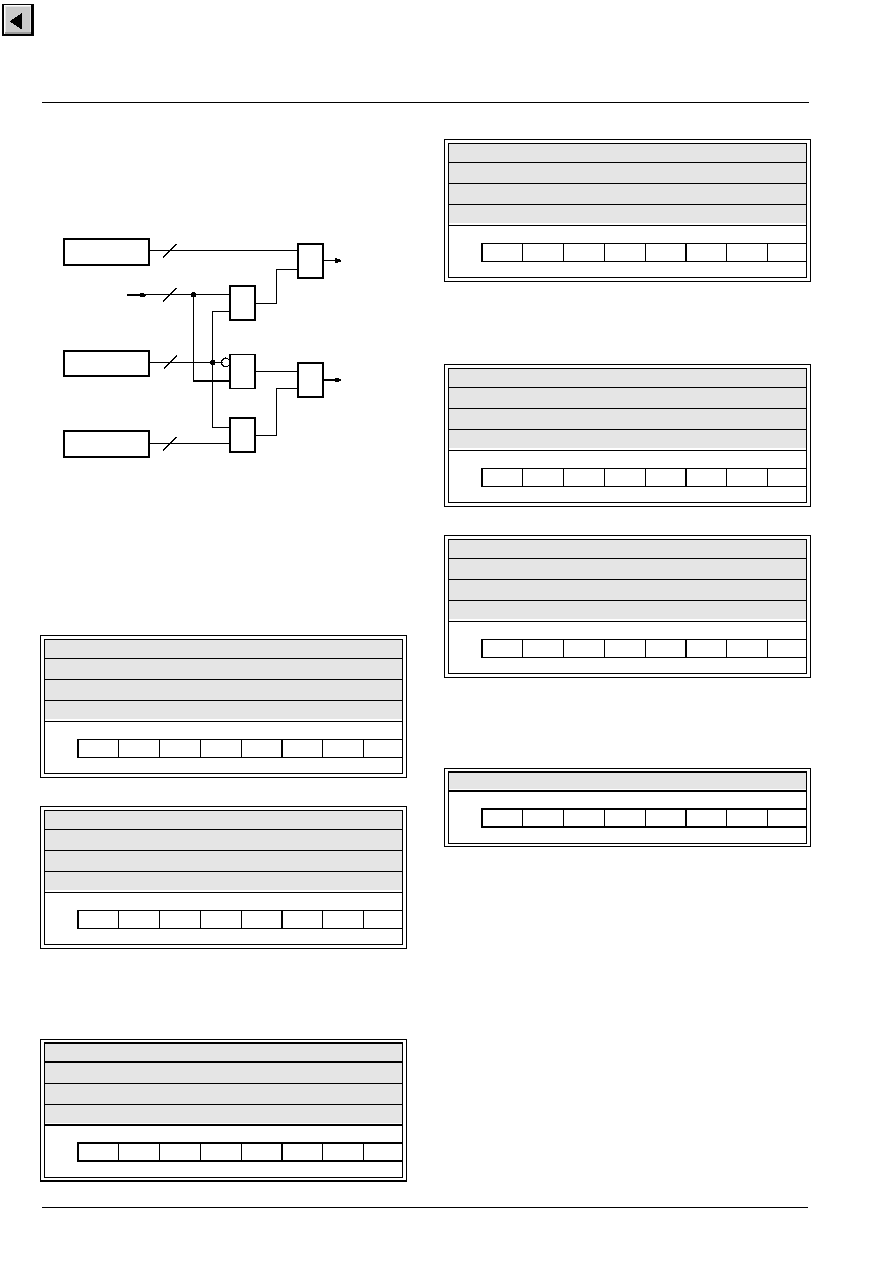

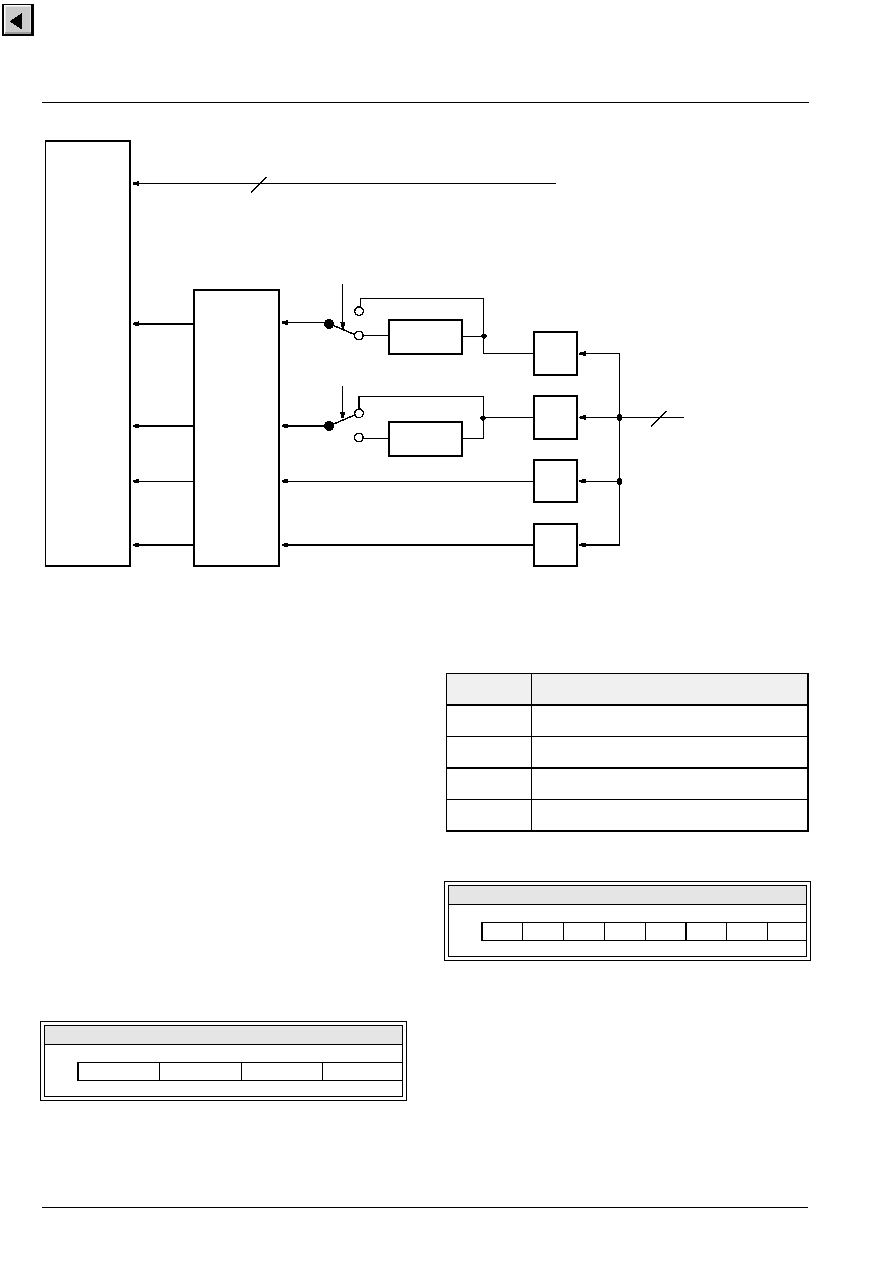

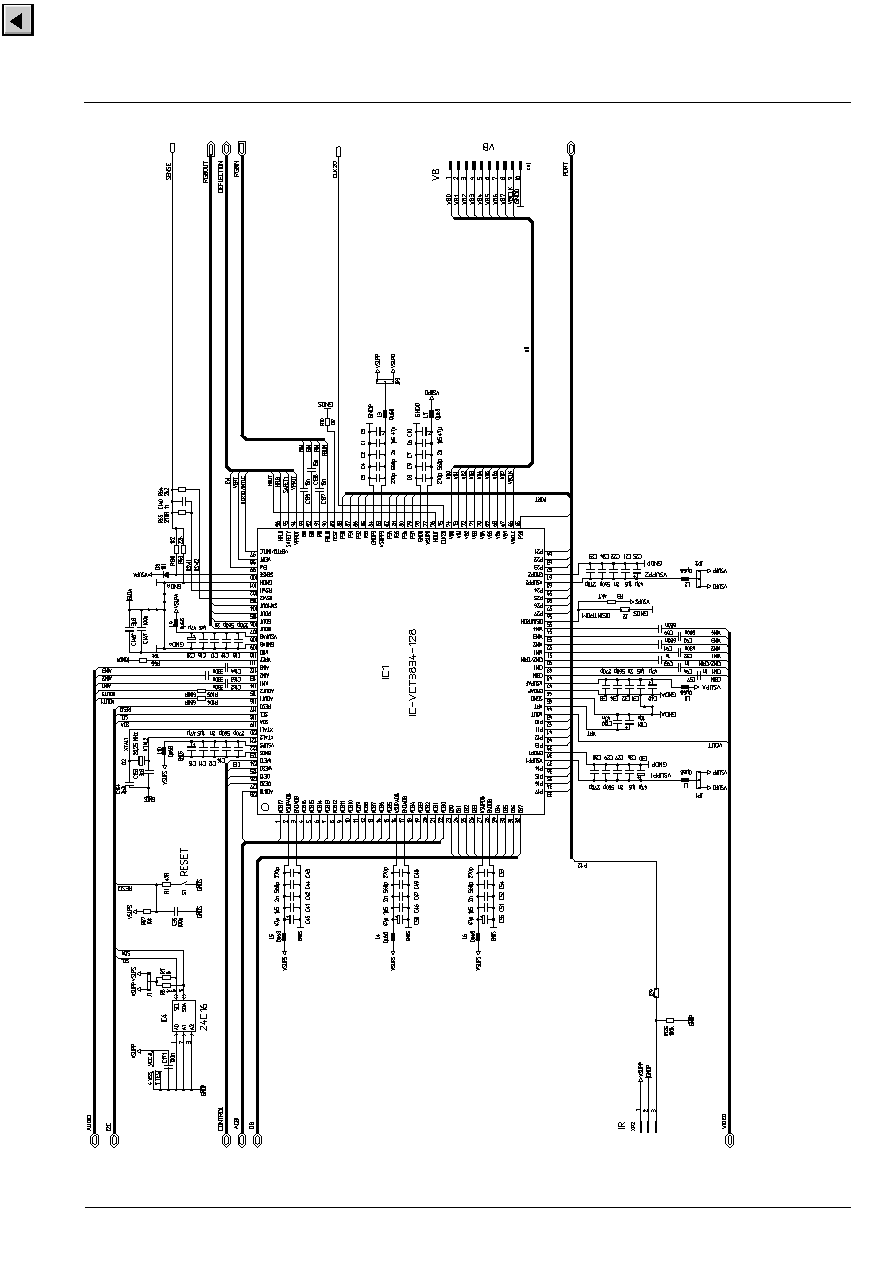

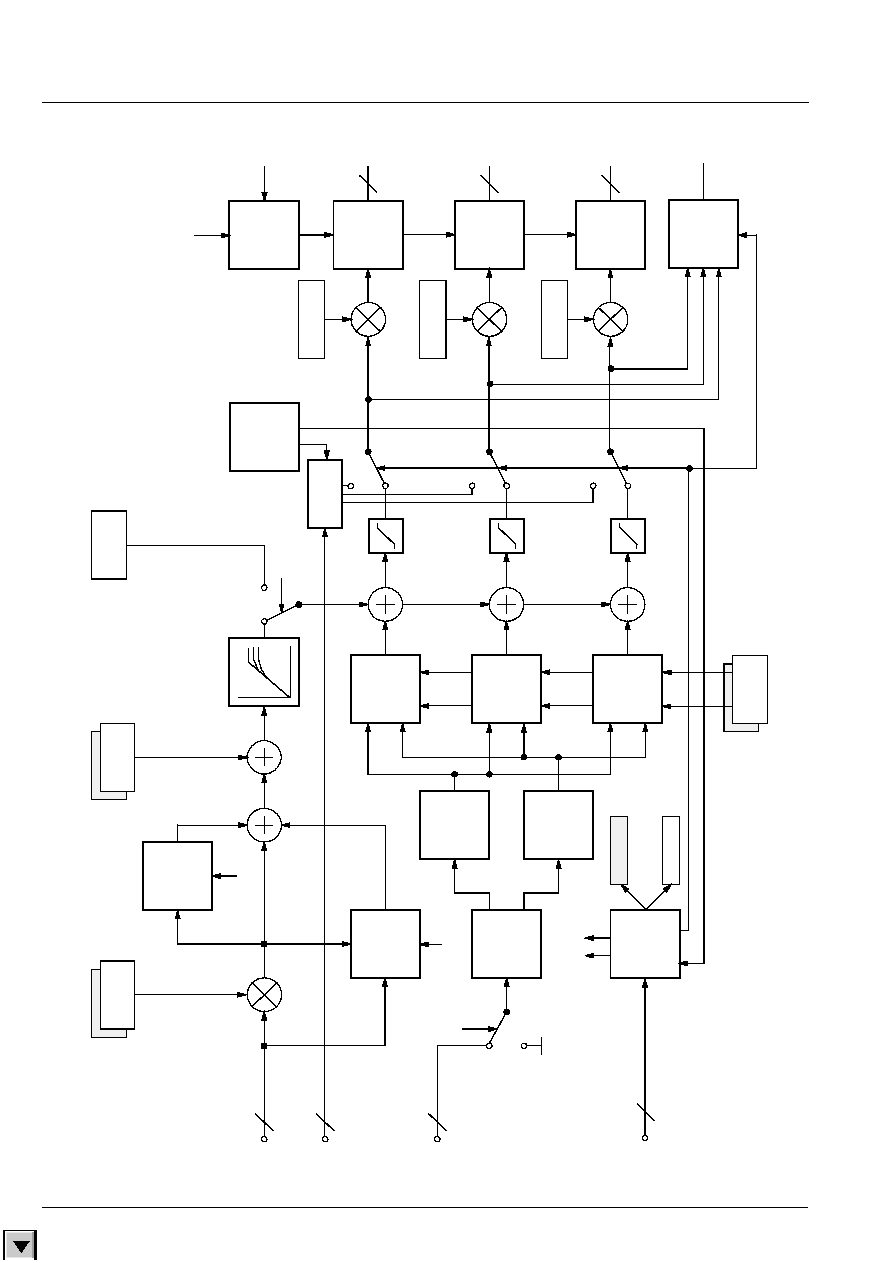

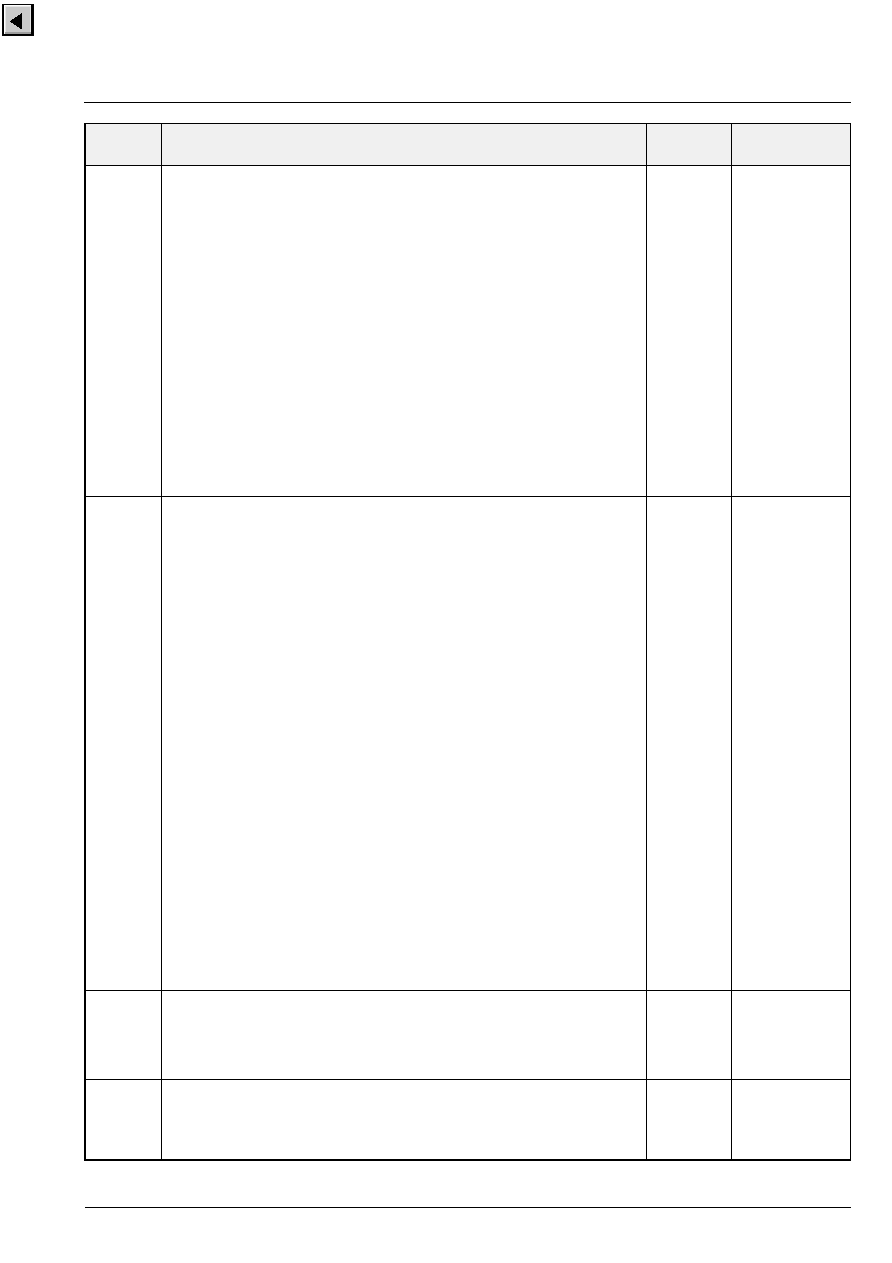

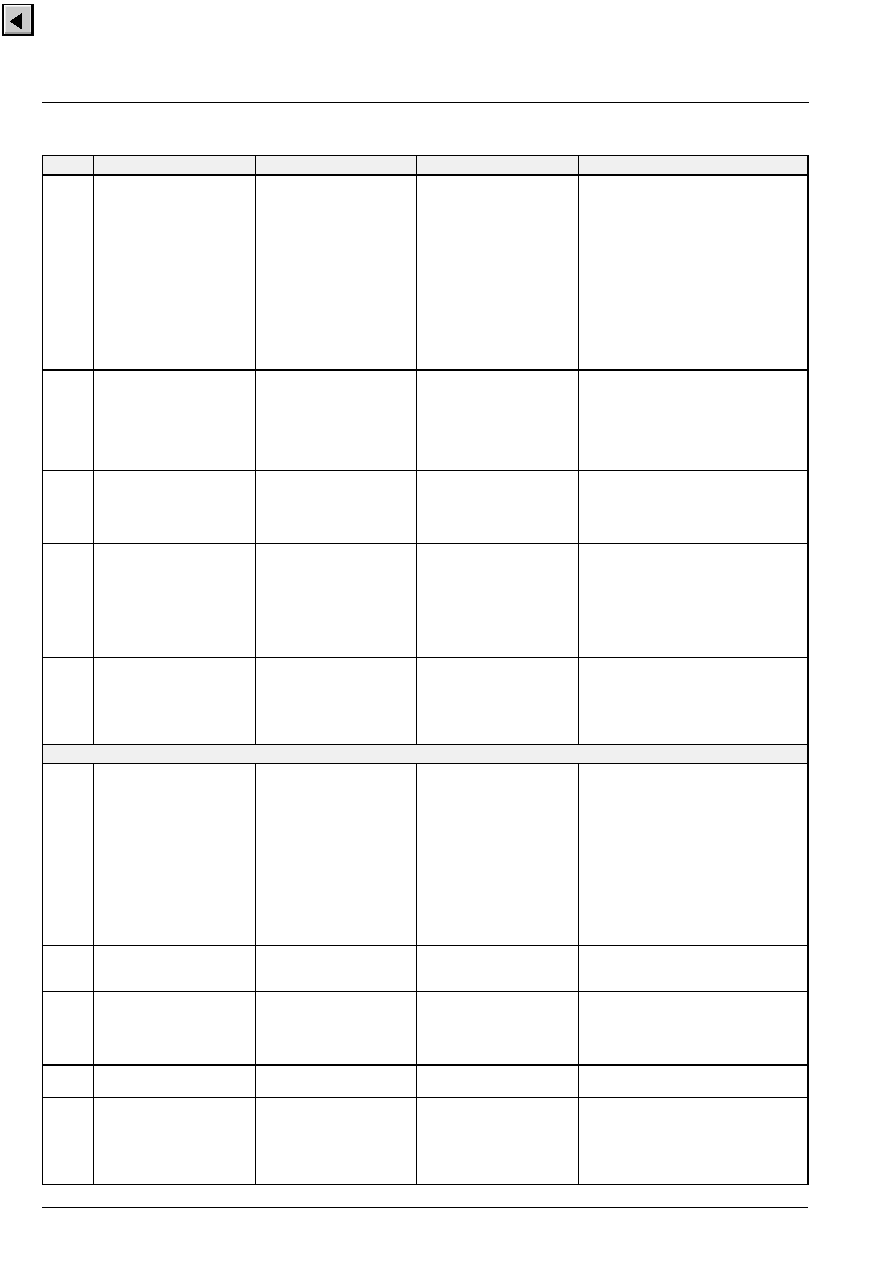

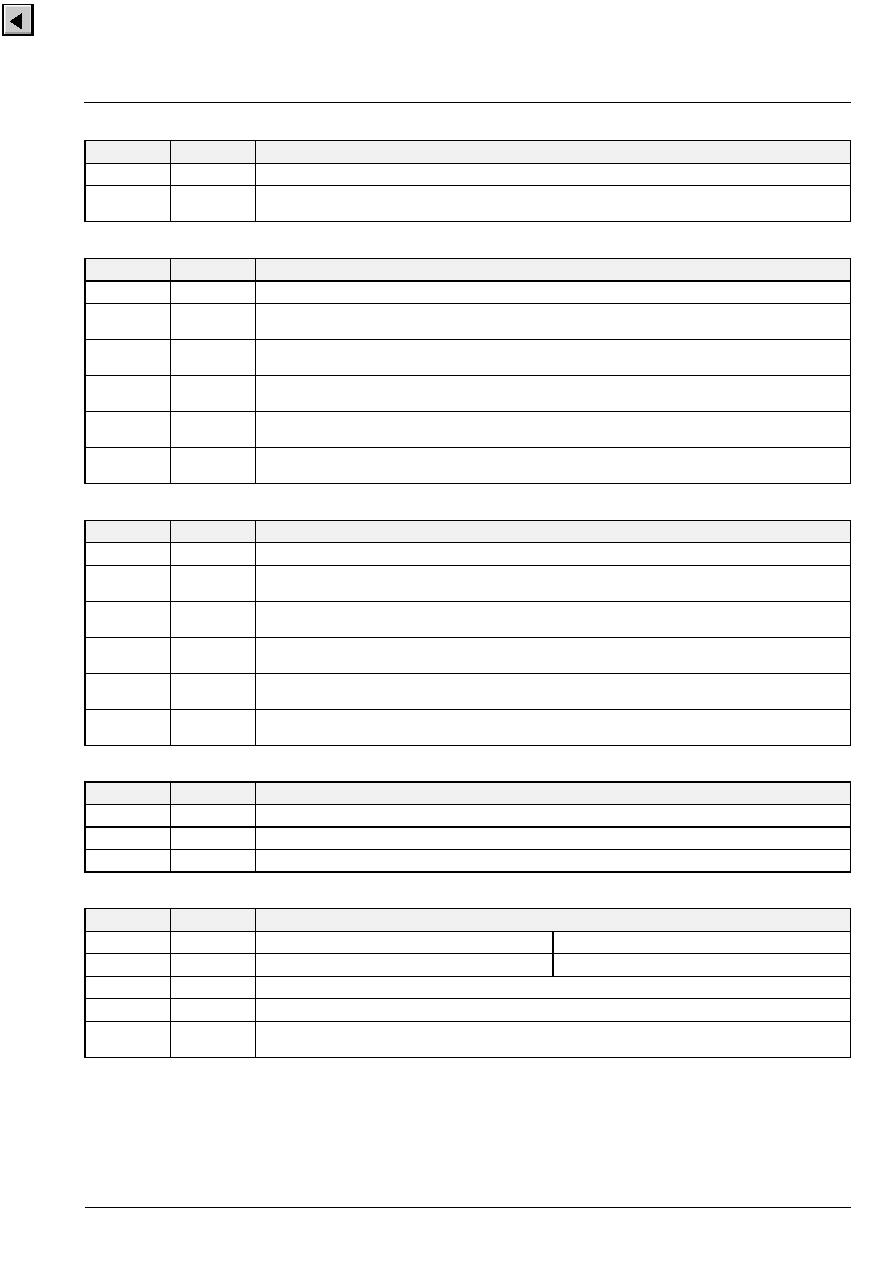

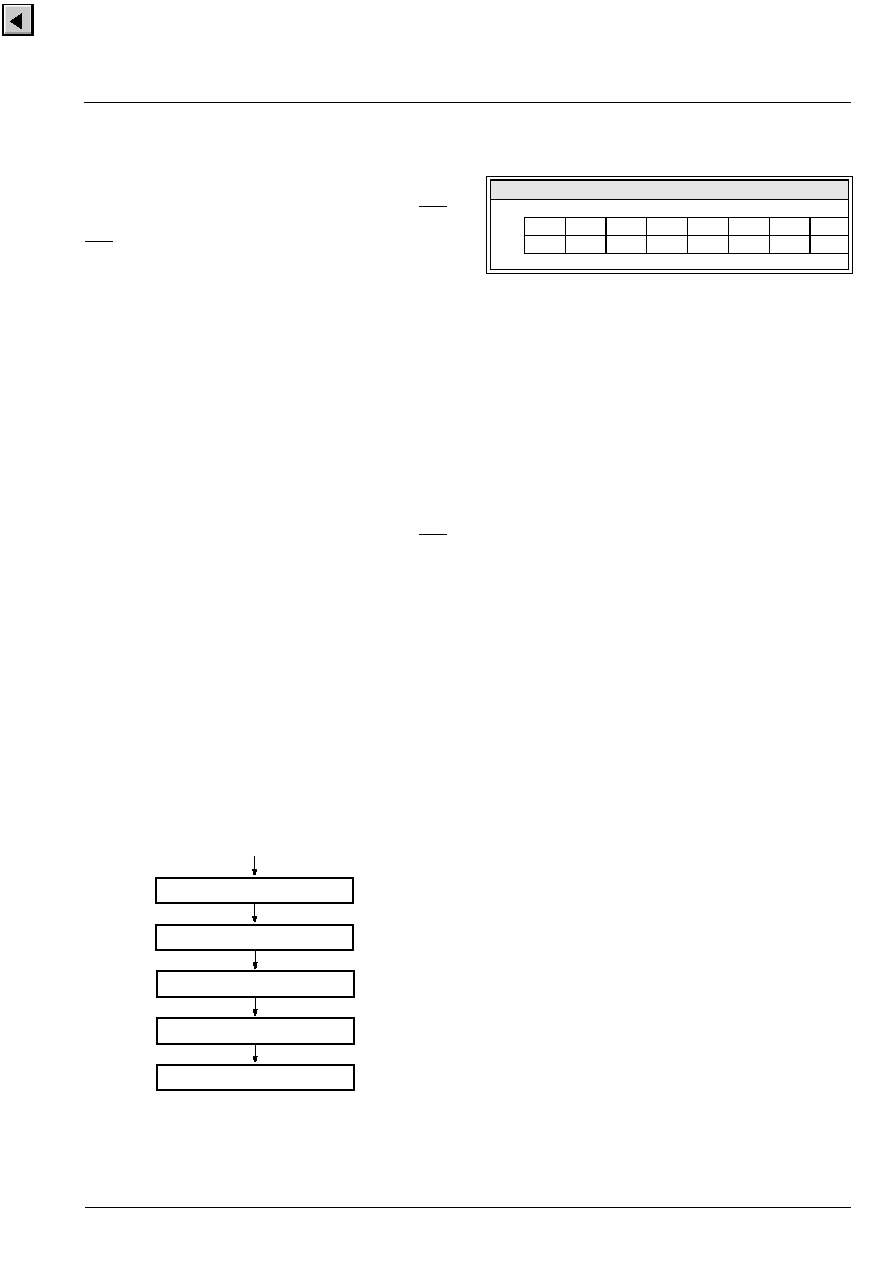

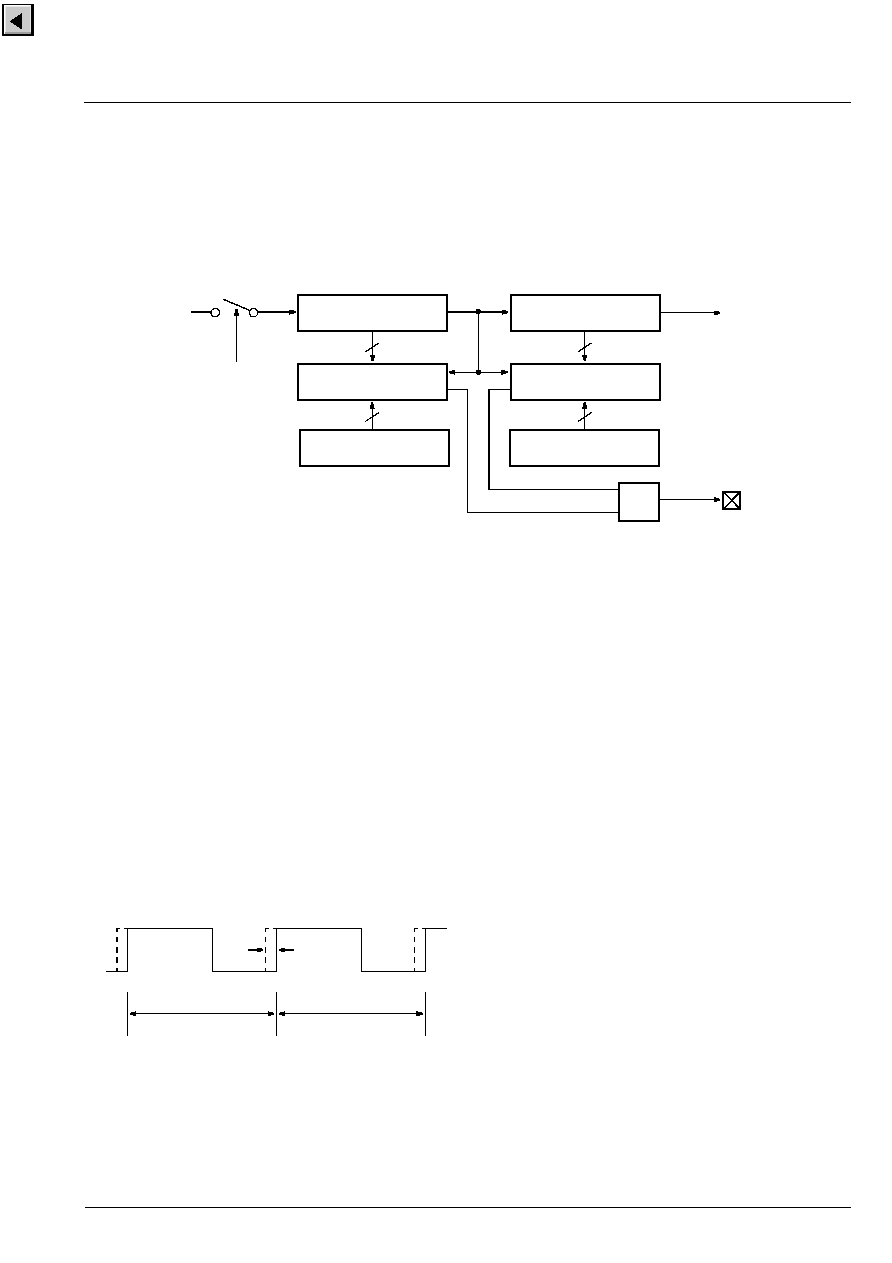

Fig. 1�2: Block diagram of the VCT 38xxA (shaded blocks are optional)

Video

Front-end

Comb

Filter

Color

Decoder

Display

Processor

Video

Back-end

Panorama

Scaler

4

3

4

12

31

2

I

2

C Master

16 kB

Text RAM

3 kB

OSD

96 kB

CPU ROM

TPU

DMA

CPU

24 IO Ports

Watchdog

2 CapCom

2 Timer

15:1 Mux

10-bit ADC

8-bit PWM

Audio

3

2

Clock

Oscillator

1 kB

CPU RAM

XTAL1

XTAL2

VIN

AIN

Px

y

ADB, DB, CB

RGBOUT

RGBIN

VE

R

T

PR

O

T

HFLB

SE

N

S

E

I

2

C

XR

E

F

HOUT

VR

D

VR

T

SG

N

D

Color, Prio

MSync

I

2

C

VSUPAB

VS

U

PP1

GN

D

P

1

Reset

Logic

RESQ

VS

U

P

S

TEST

GNDAB

VS

U

P

A

F

VS

U

P

D

GND

A

F

GNDD

RS

W

2

GNDM

EW

8

14-bit PWM

2

2

3

CIN

SVM

V

i

deo

GNDS

CLK20

RDY

BE

24 kB

VCT 38xx

AOUT

VSync

VOUT

24 kB ROM

3 kB

OSD RAM

Pict.Improv.

VCT 38xxA

ADVANCE INFORMATION

10

Micronas

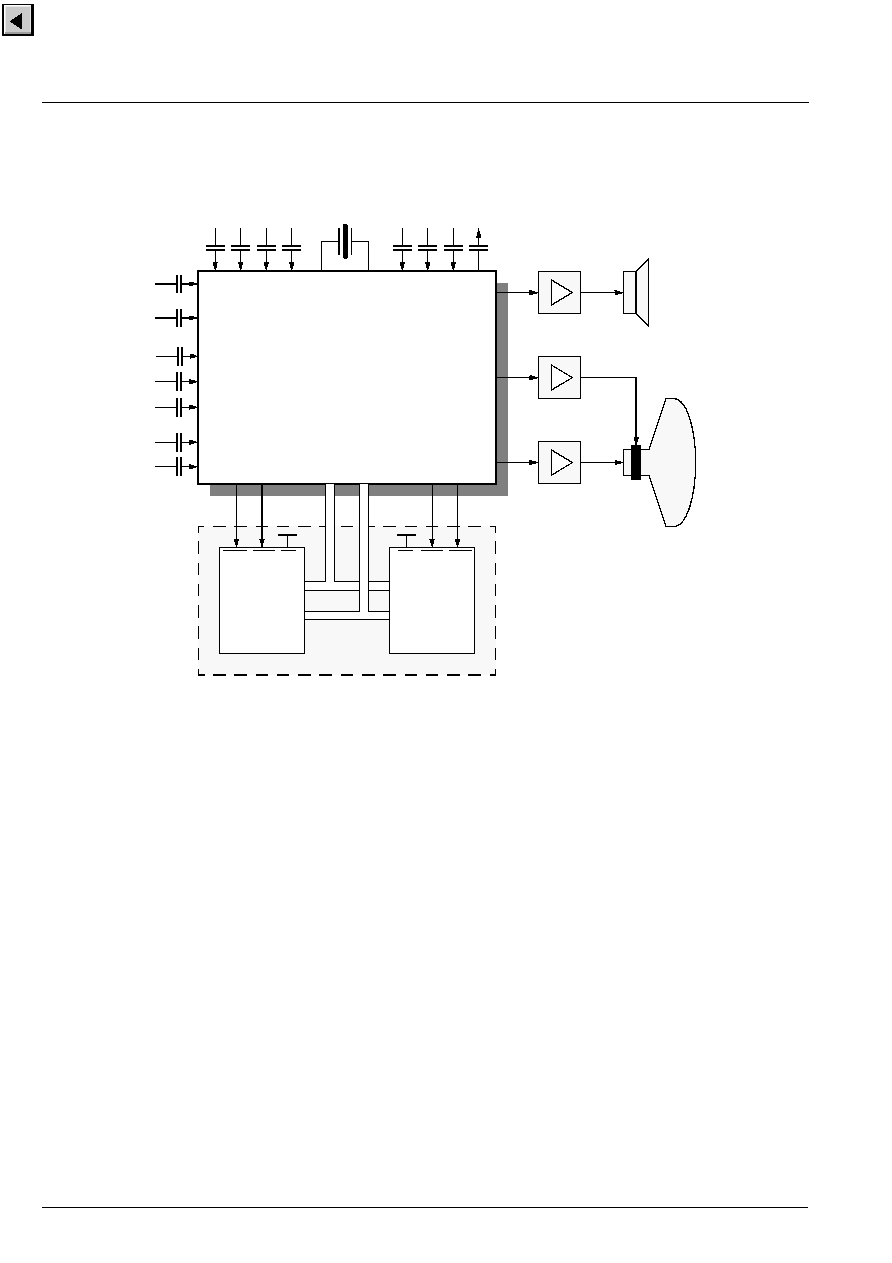

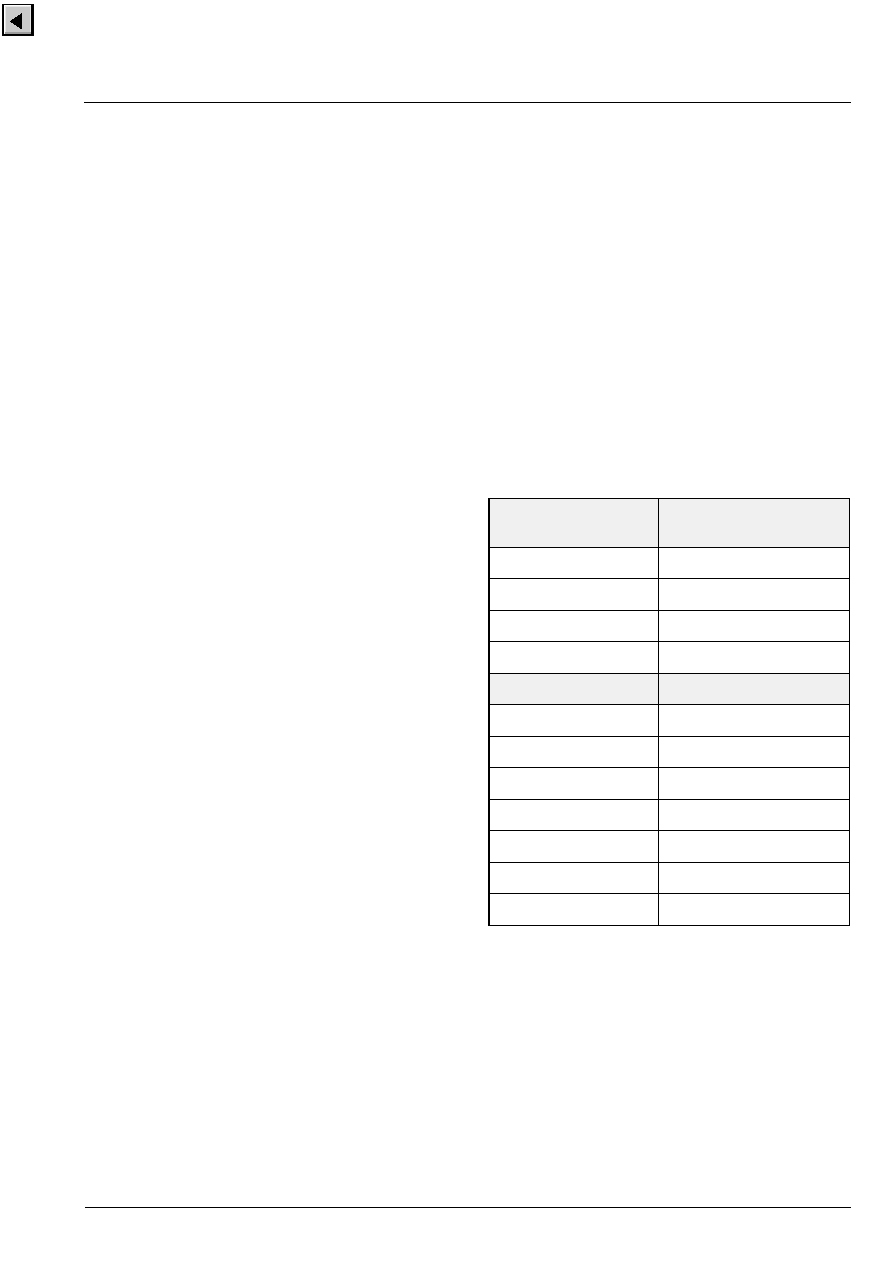

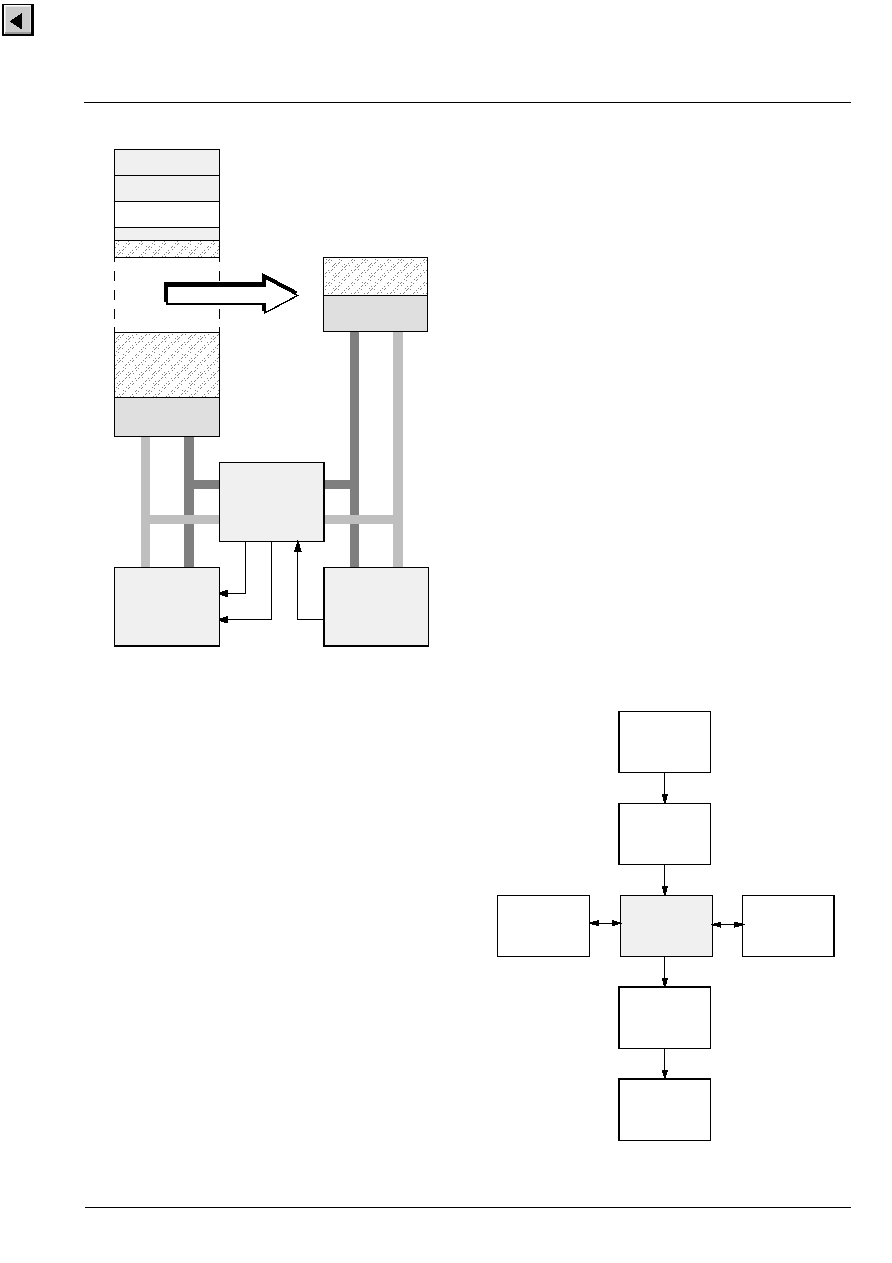

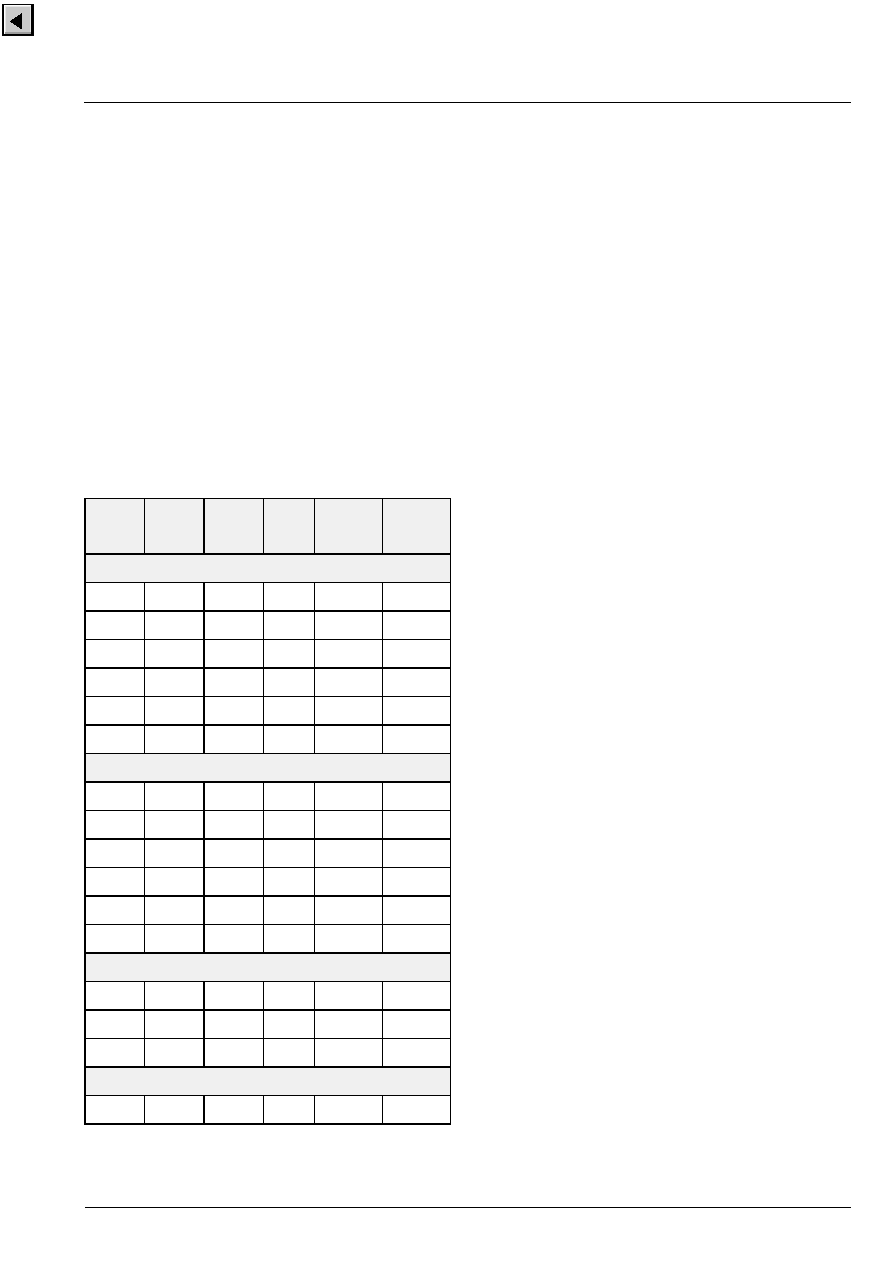

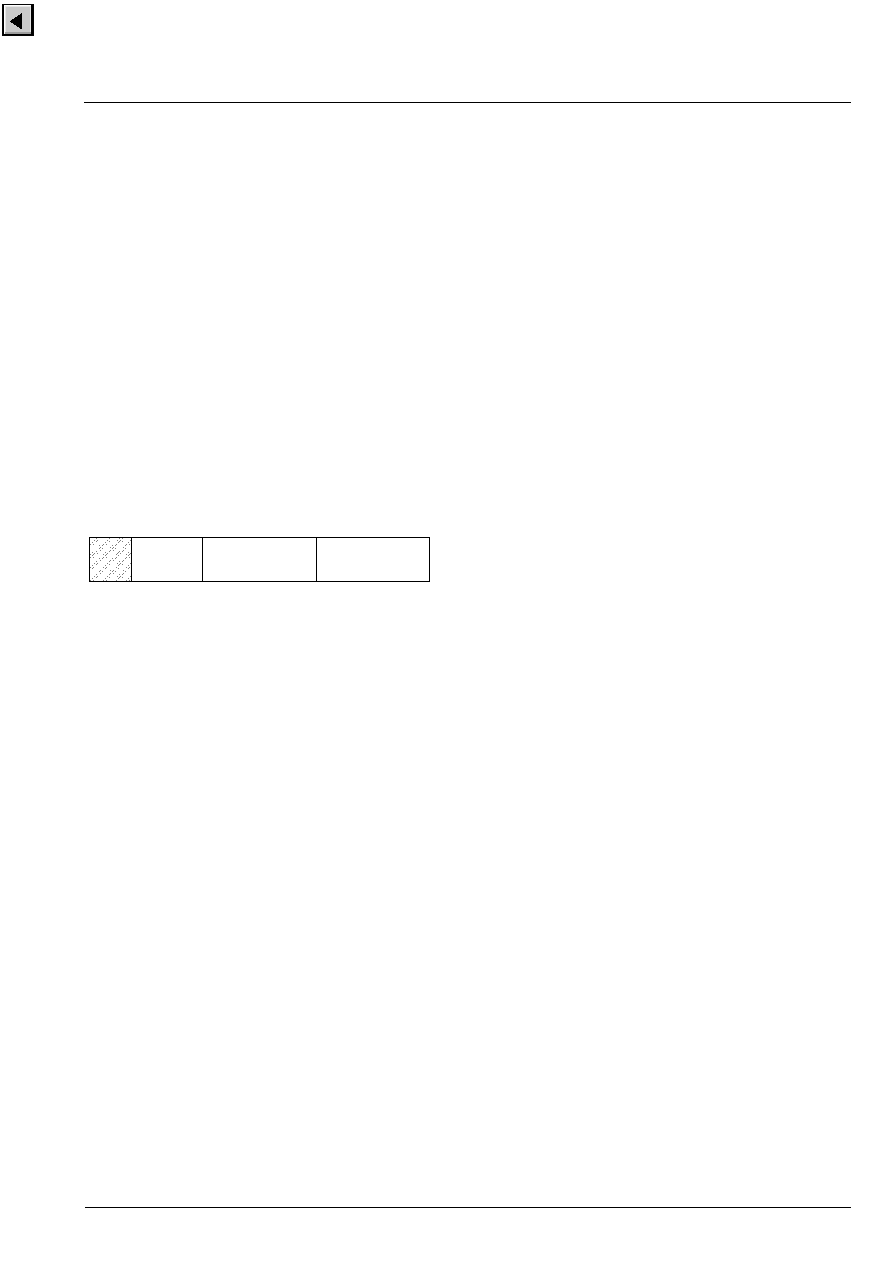

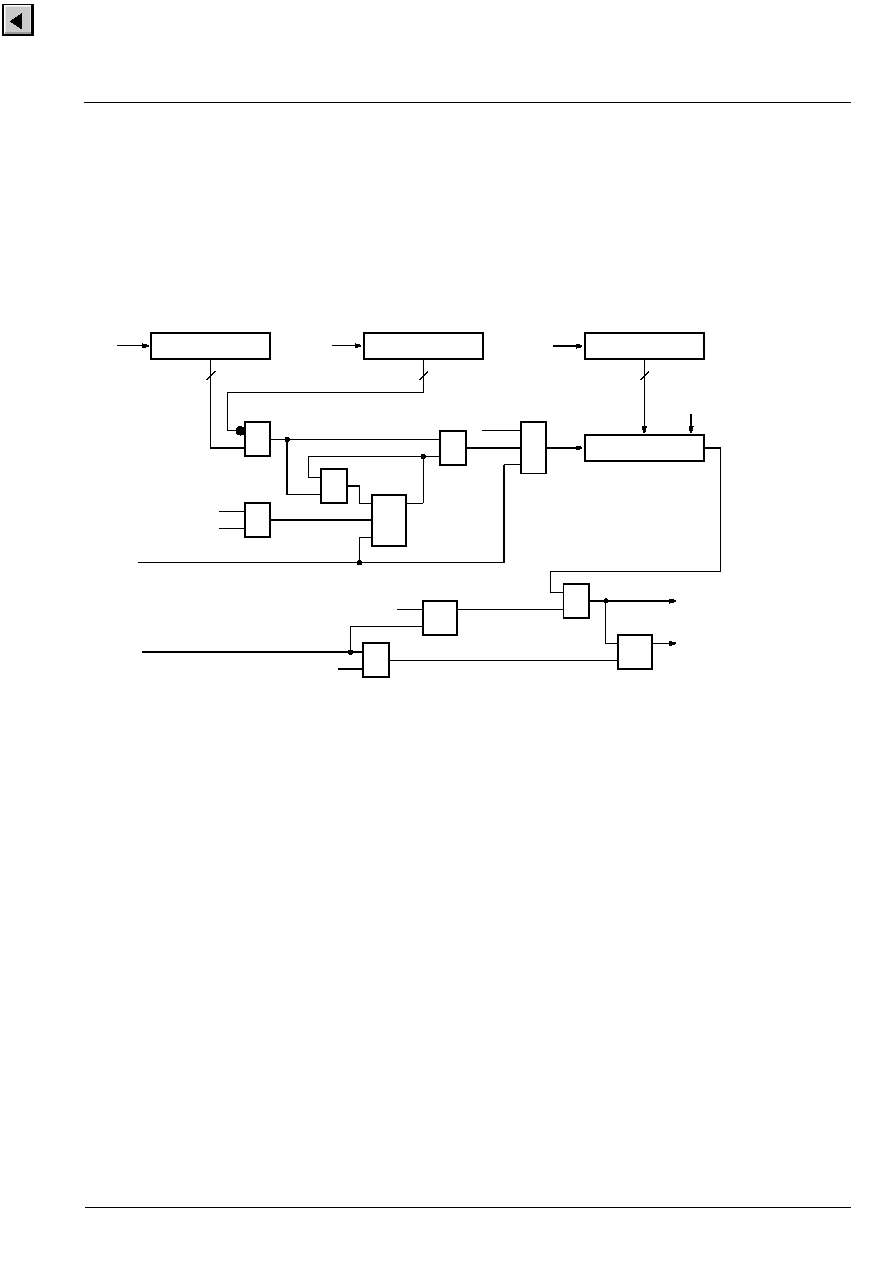

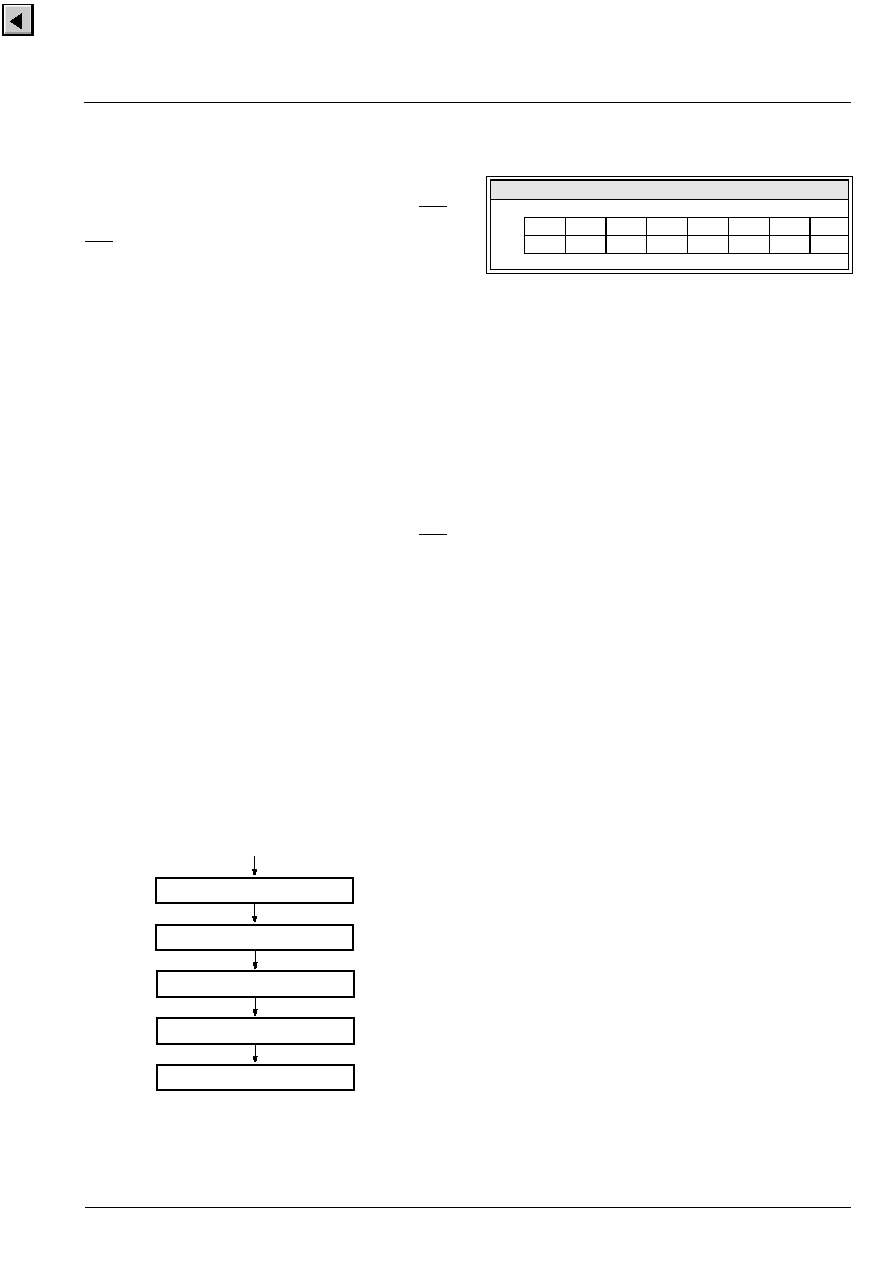

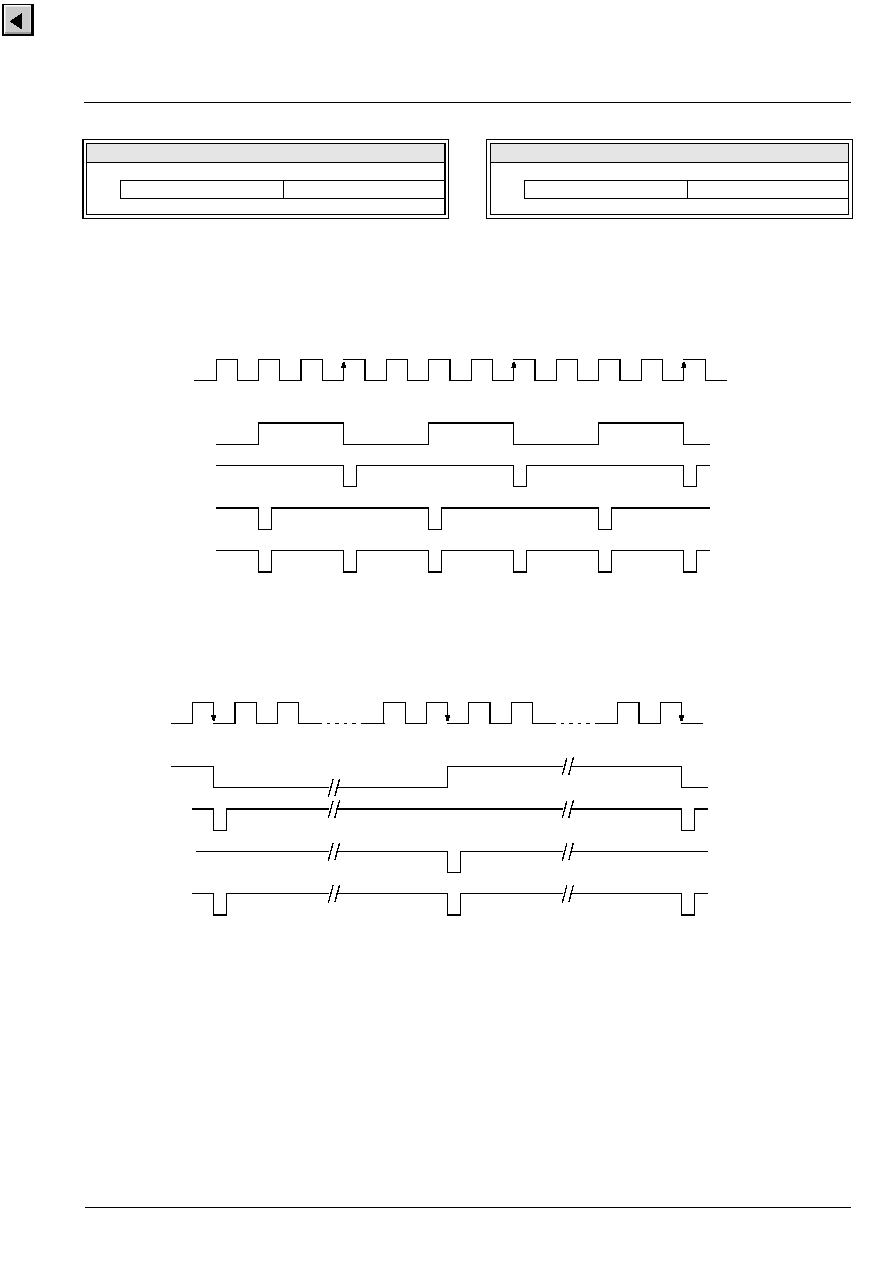

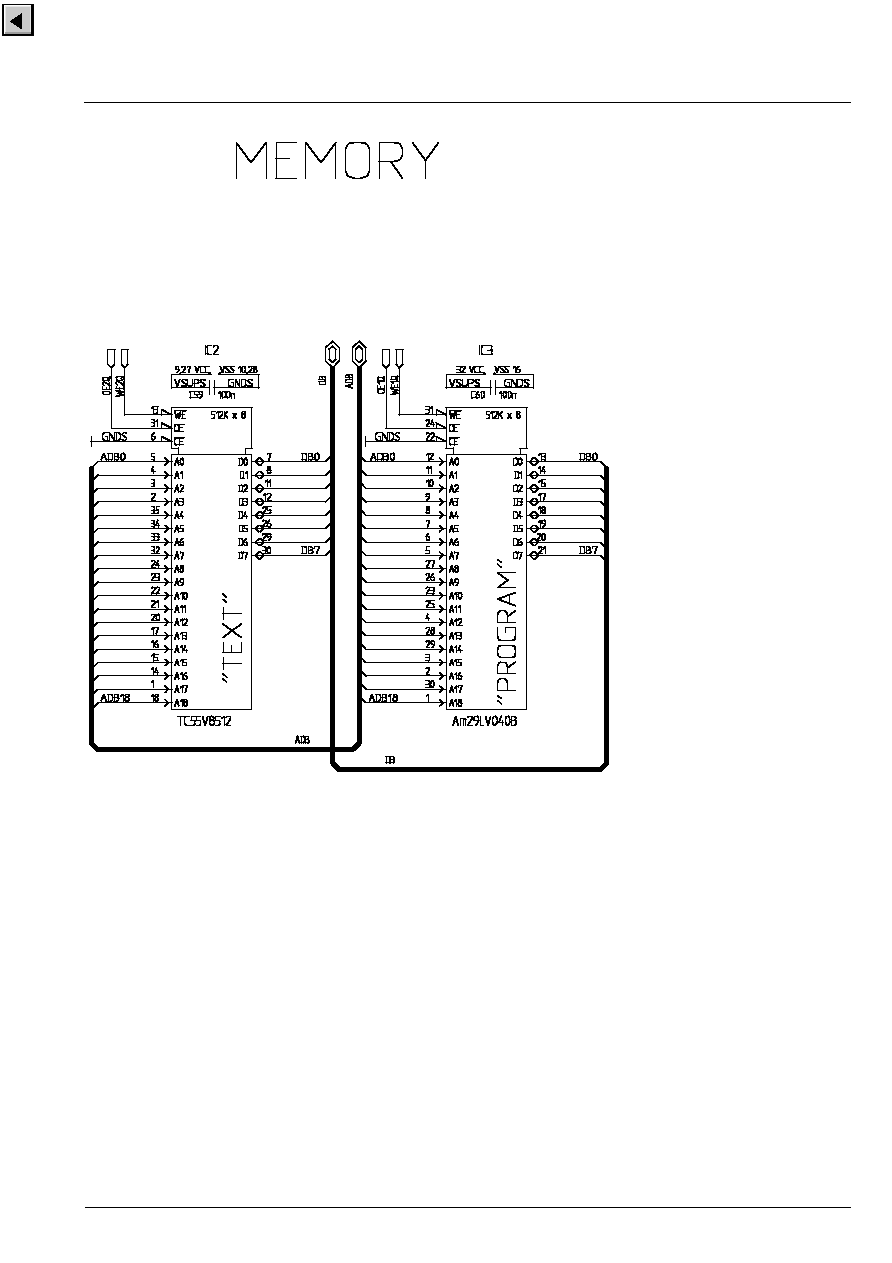

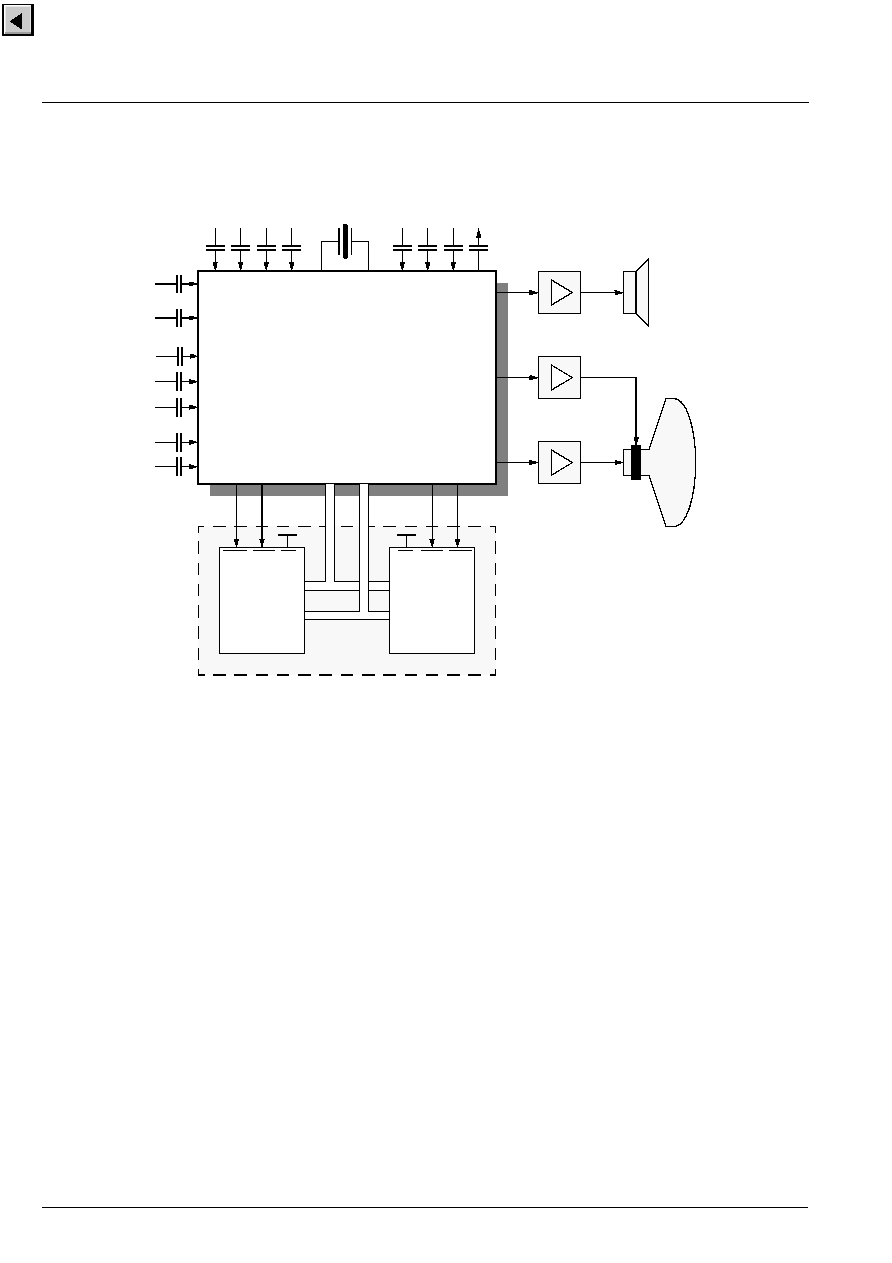

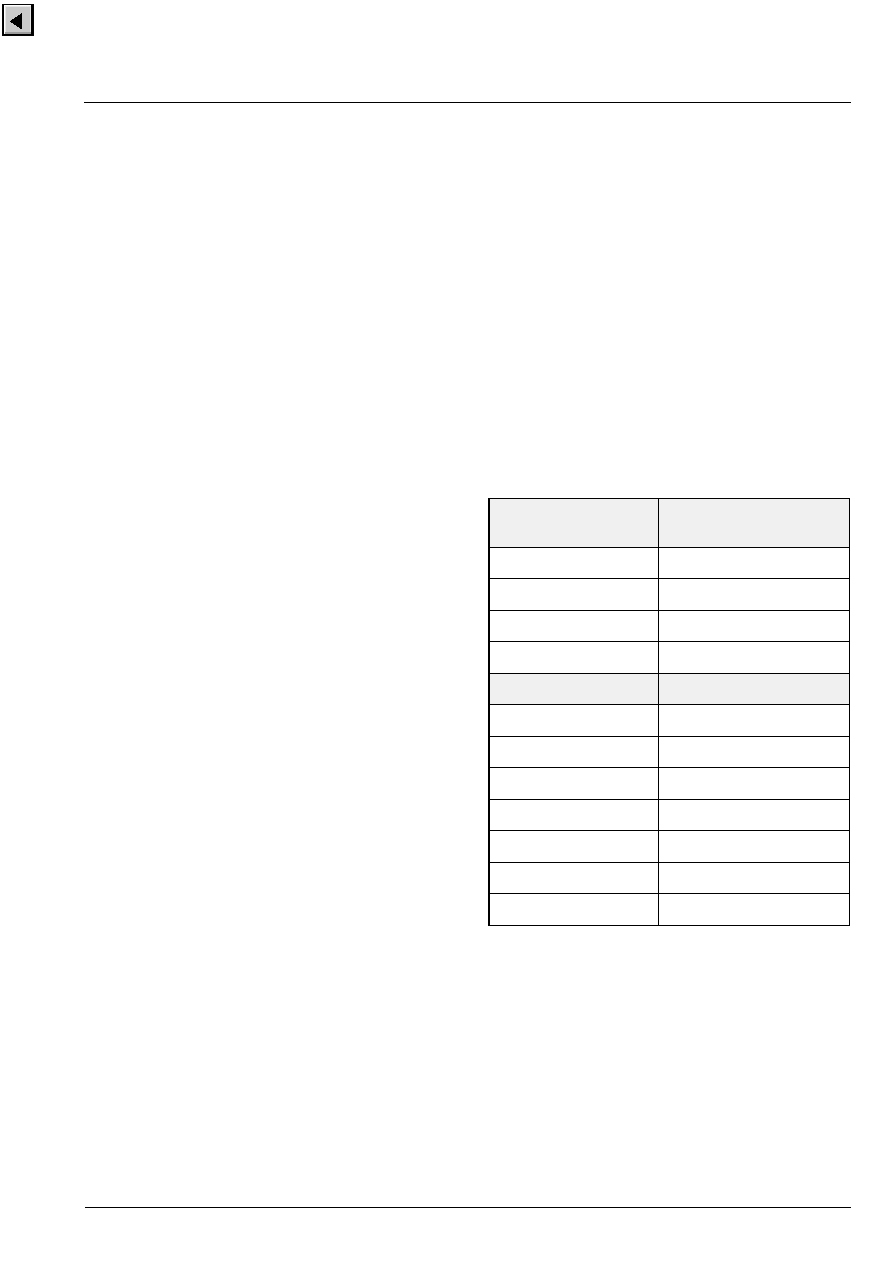

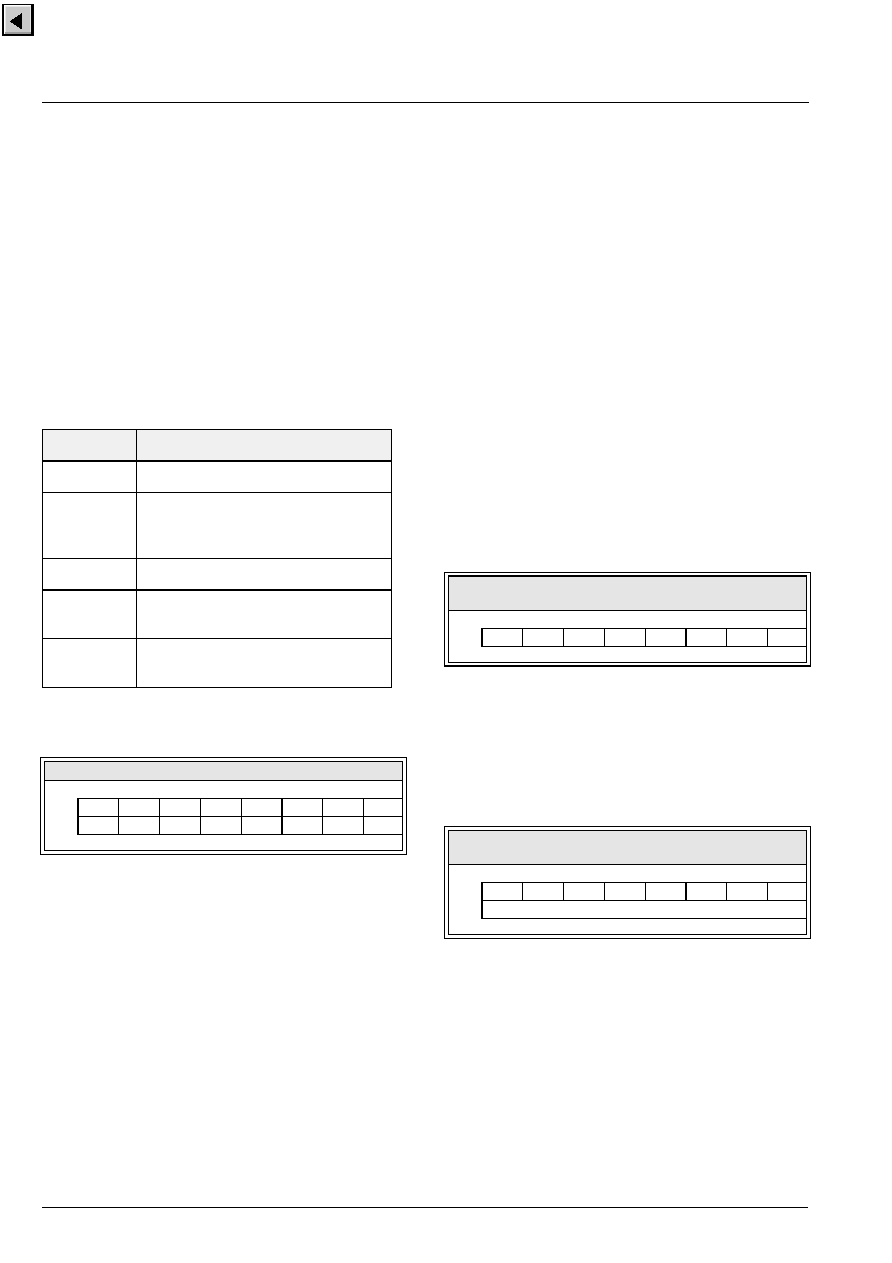

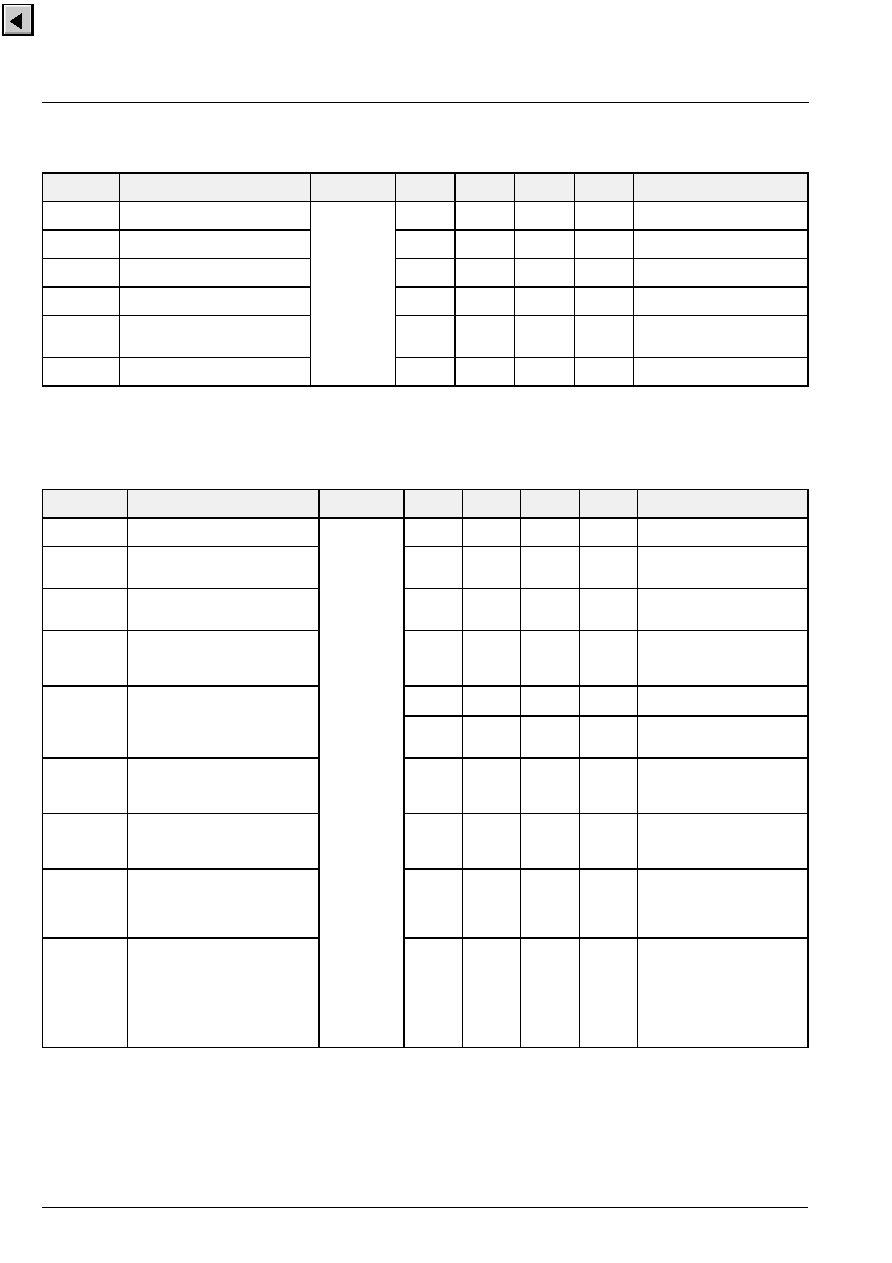

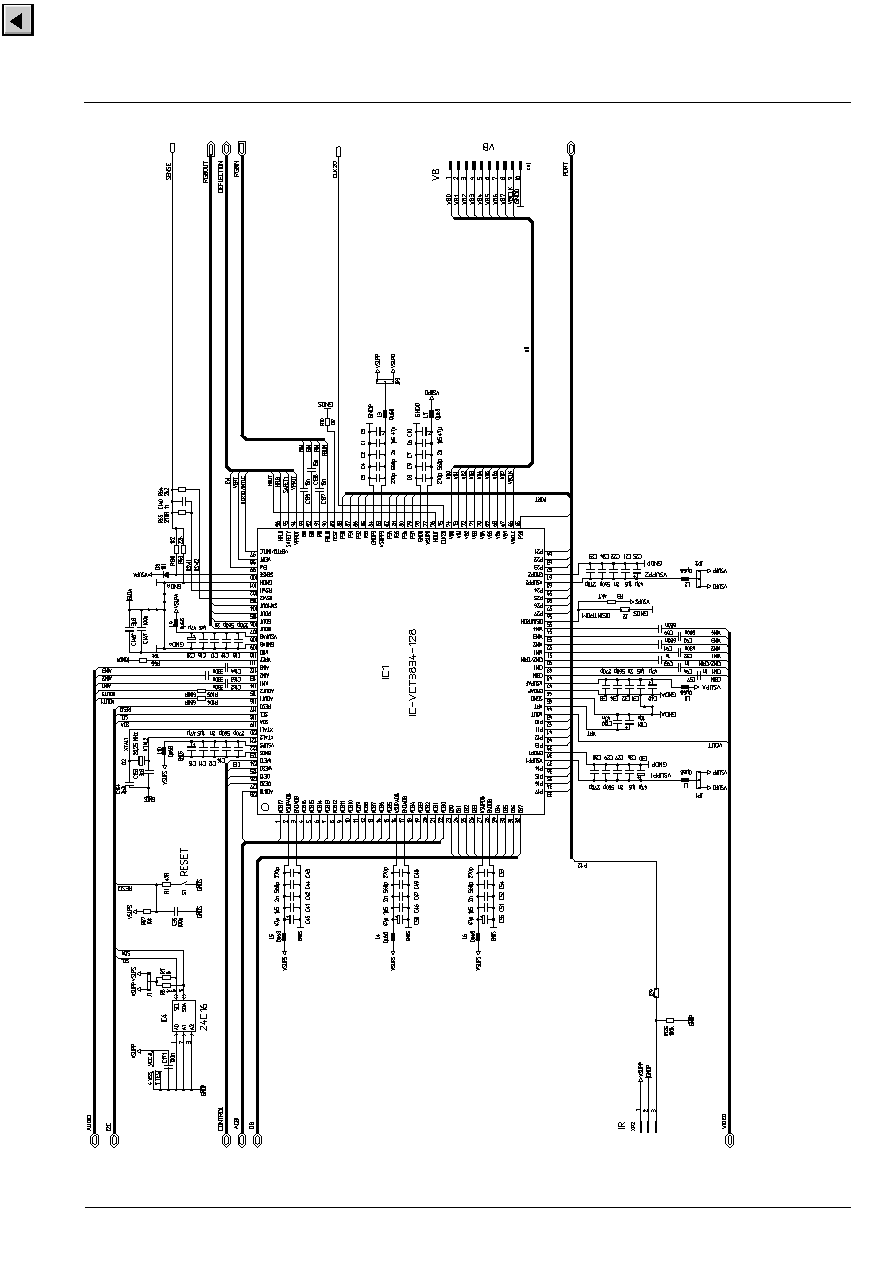

1.3. System Application

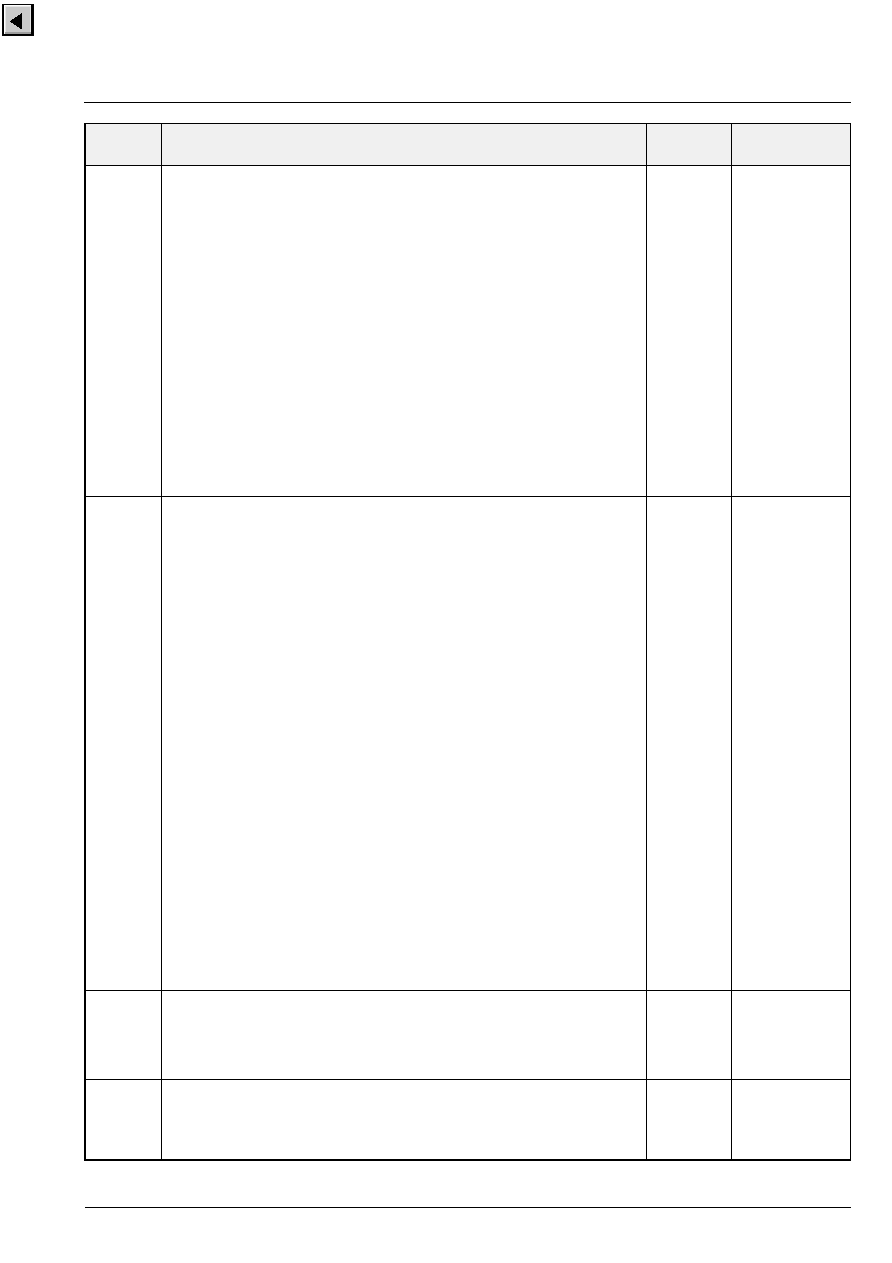

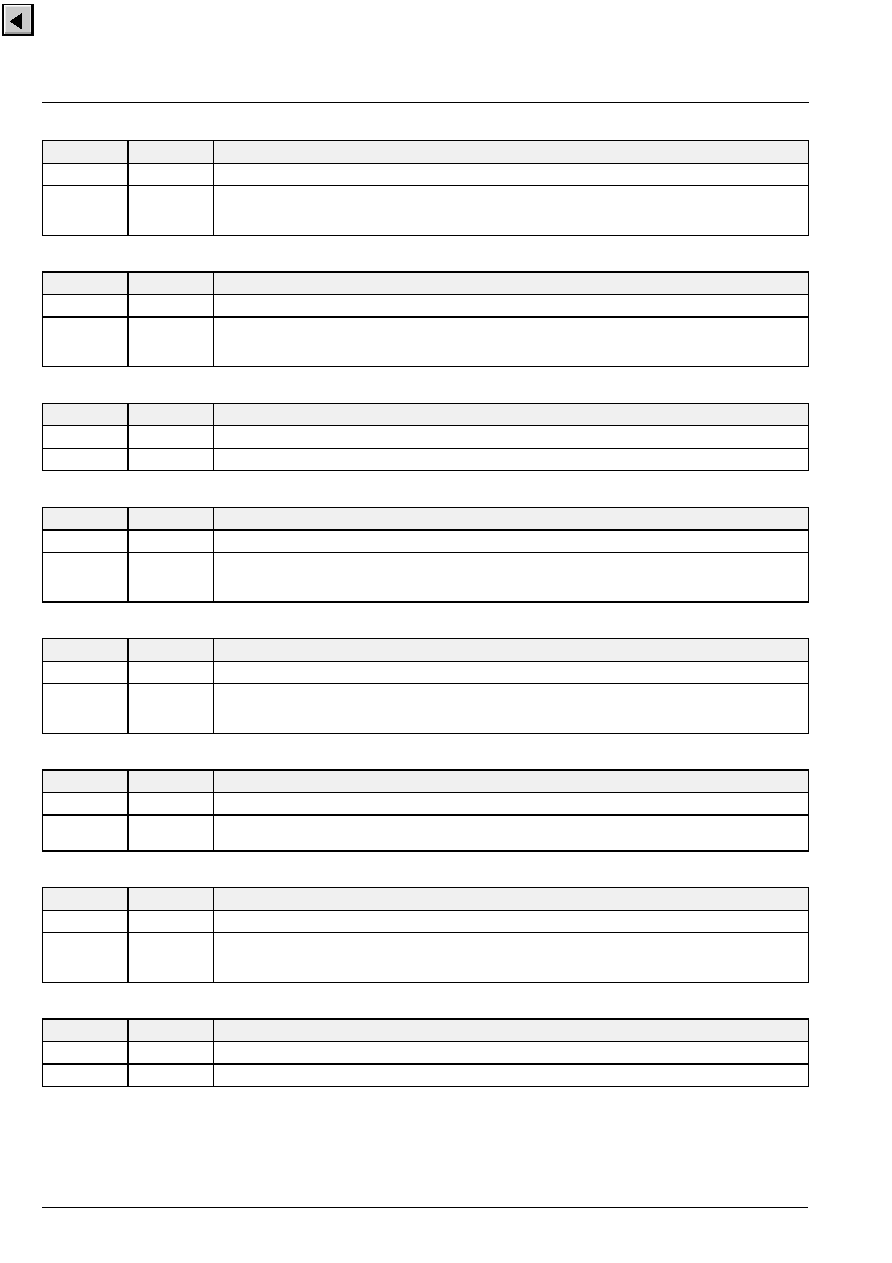

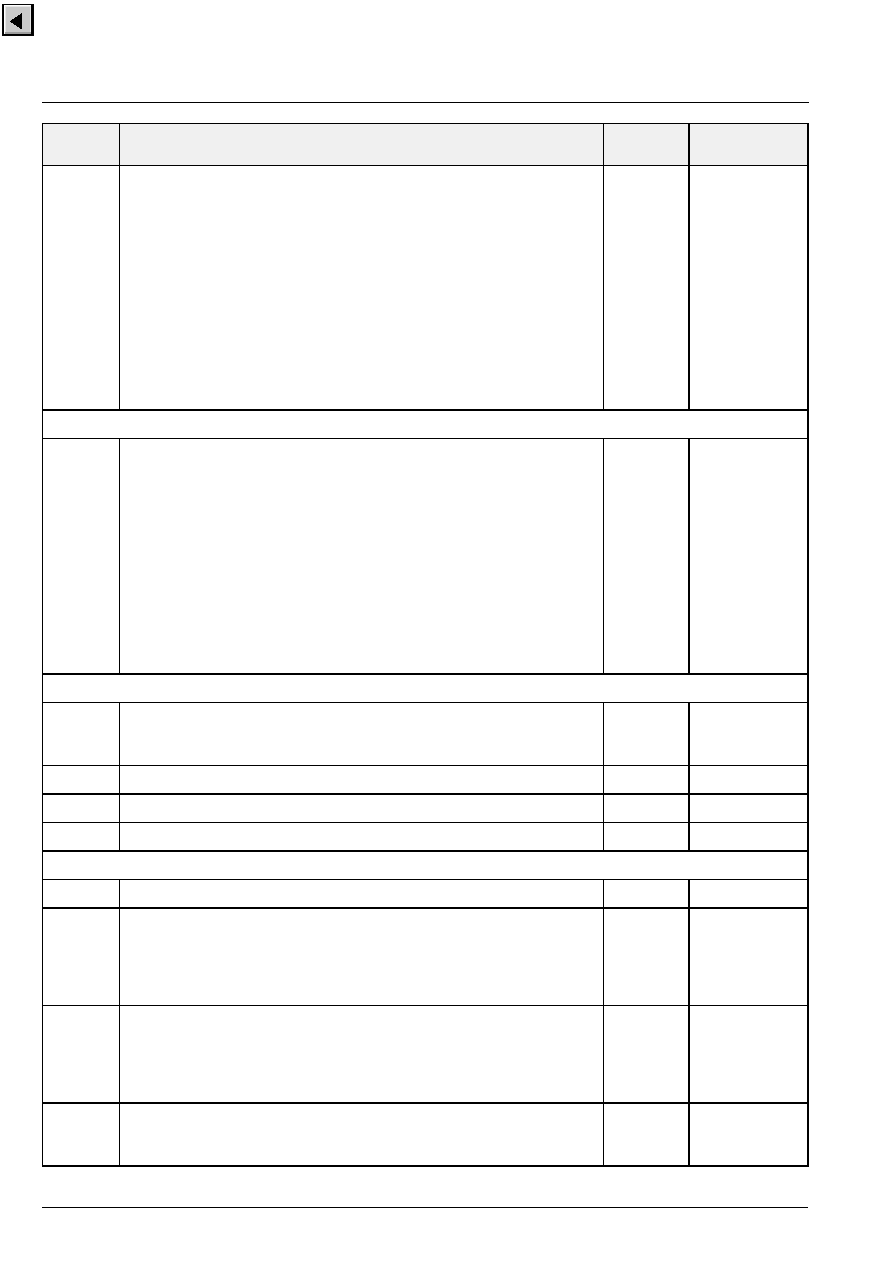

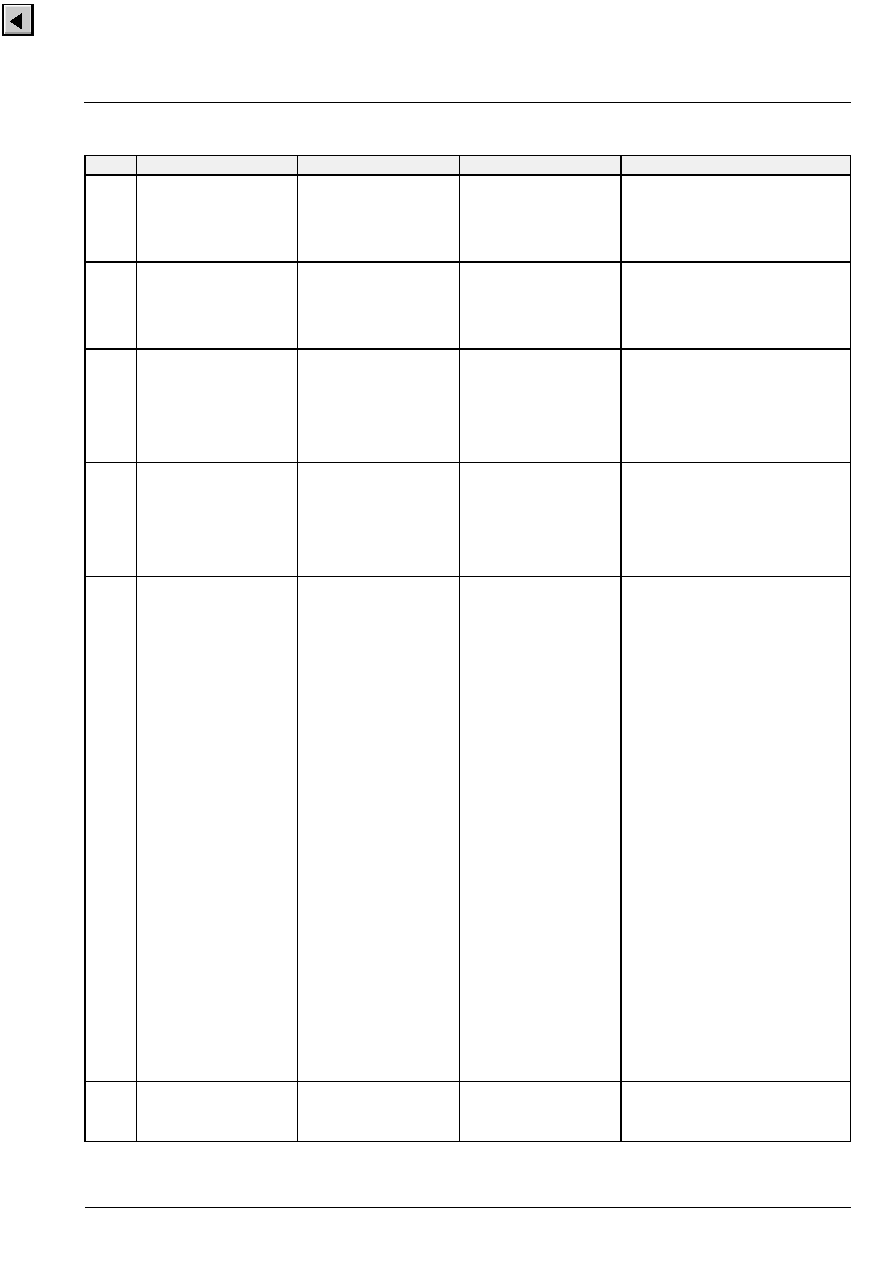

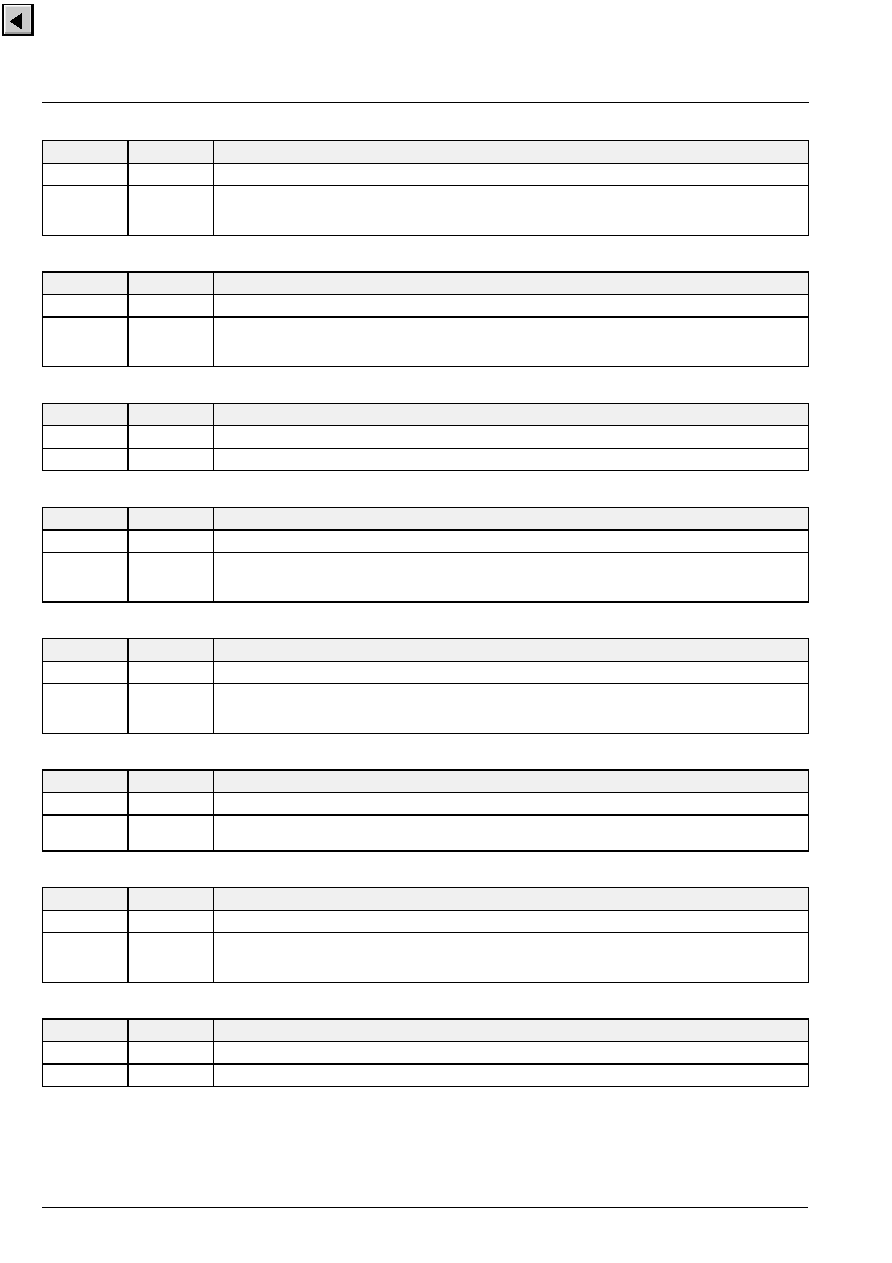

Fig. 1�3: Single-chip TV with VCT 38xxA

VCT 38xxA

20.25 MHz

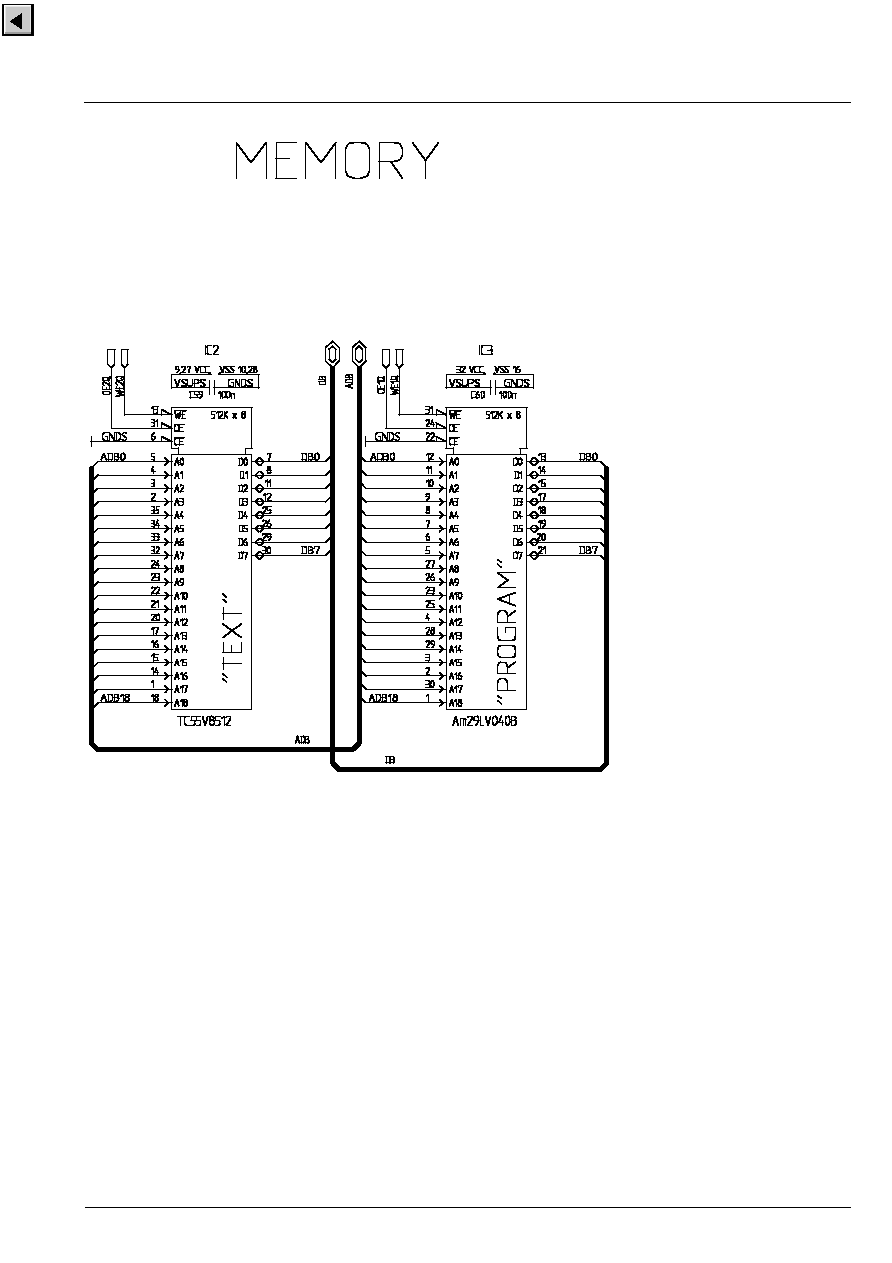

512 kB

SRAM

optional memory extension

Loudspeaker

Tuner/SCART/FrontAV

Anal

og Vi

deo

Analog Audio

CRT

Analog RGB

R

512 kB

ROM/

FLASH

CE

CE

OE2

WE2

ADB

DB

OE1 WE1

CVBS1

CVBS2

C

r

Y

C

b

C

Y

G

B

FB

ADVANCE INFORMATION

VCT 38xxA

Micronas

11

2. Video Processing

2.1. Introduction

The VCT 38xxA includes complete video, display, and

deflection processing. In the following sections the

video processing part of the VCT 38xxA will be named

VDP for short.

All processing is done digitally, the video front-end and

video back-end are interfacing to the analog world.

Most functions of the VDP can be controlled by soft-

ware via I

2

C bus slave interface (see Section 2.15. on

page 32).

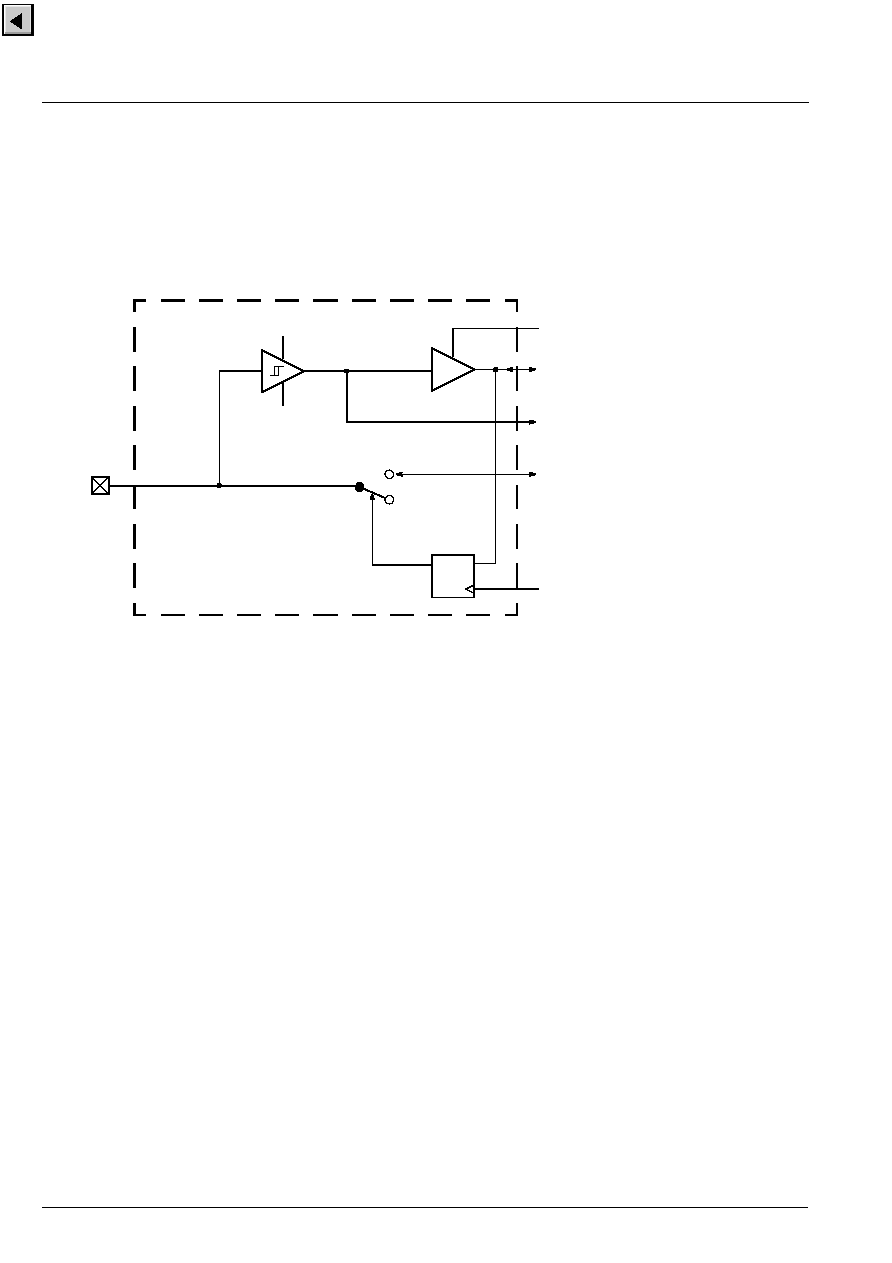

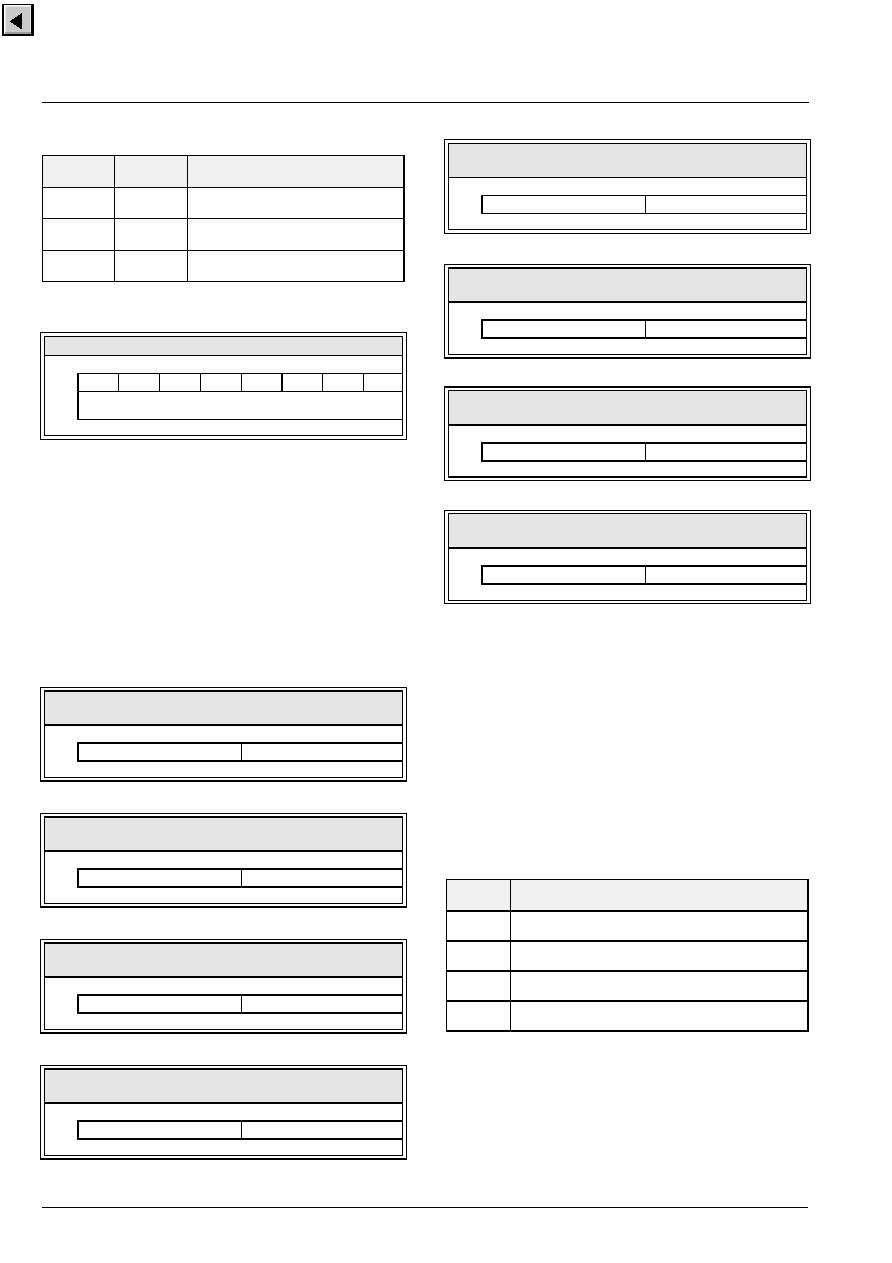

2.2. Video Front-end

This block provides the analog interfaces to all video

inputs and mainly carries out analog-to-digital conver-

sion for the following digital video processing. A block

diagram is given in Fig. 2�1.

Most of the functional blocks in the front-end are digi-

tally controlled (clamping, AGC, and clock-DCO). The

control loops are closed by the Fast Processor (`FP')

embedded in the video decoder.

2.2.1. Input Selector

Up to seven analog inputs can be connected. Four

inputs are for input of composite video or S-VHS luma

signal. These inputs are clamped to the sync back

porch and are amplified by a variable gain amplifier.

Two chroma inputs can be used for connection of

S-VHS carrier-chrominance signal. These inputs are

internally biased and have a fixed gain amplifier. For

analog YC

r

C

b

signals (e.g. from DVD players) one of

the selected luminance inputs is used together with

CBIN and CRIN inputs.

2.2.2. Clamping

The composite video input signals are AC-coupled to

the IC. The clamping voltage is stored on the coupling

capacitors and is generated by digitally controlled cur-

rent sources. The clamping level is the back porch of

the video signal. S-VHS chrominance is also AC-cou-

pled. The input pin is internally biased to the center of

the ADC input range. The chrominance inputs for

YC

r

C

b

need to be AC-coupled by 220 nF clamping

capacitors. It is strongly recommended to use 5-MHz

anti-alias low-pass filters on each input. Each channel

is sampled at 10.125 MHz with a resolution of 8 bit and

a clamping level of 128.

2.2.3. Automatic Gain Control

A digitally working automatic gain control adjusts the

magnitude of the selected baseband by +6/�4.5 dB in

64 logarithmic steps to the optimal range of the ADC.

The gain of the video input stage including the ADC is

213 steps/V with the AGC set to 0 dB. The gain of the

chrominance path in the YC

r

C

b

mode is fix and

adapted to a nominal amplitude of 0.7 V

pp

. However, if

an overflow of the ADC occurs an extended signal

range from 1 V

pp

can be selected.

2.2.4. Analog-to-Digital Converters

Two ADCs are provided to digitize the input signals.

Each converter runs with 20.25 MHz and has 8 bit res-

olution. An integrated bandgap circuit generates the

required reference voltages for the converters. The two

ADCs are of a 2-stage subranging type.

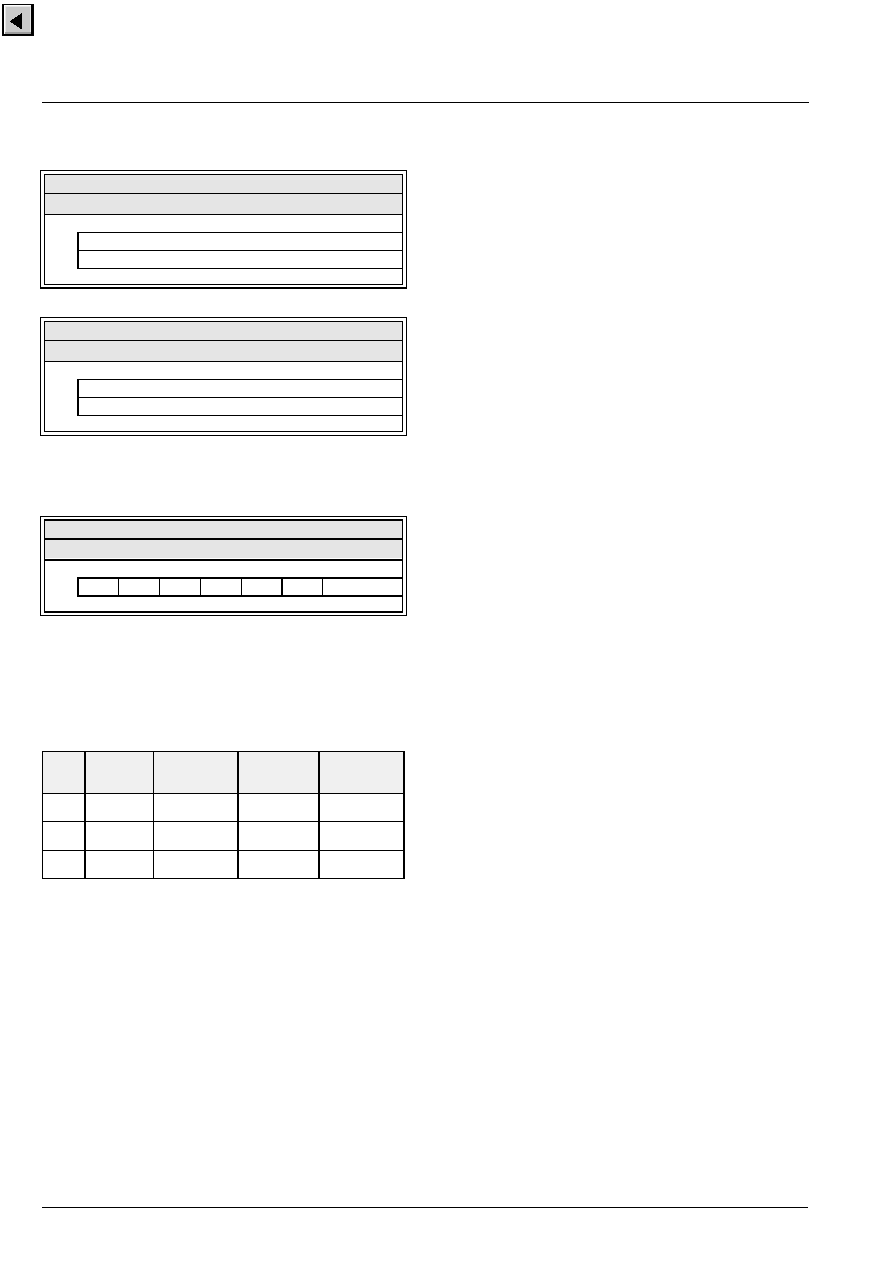

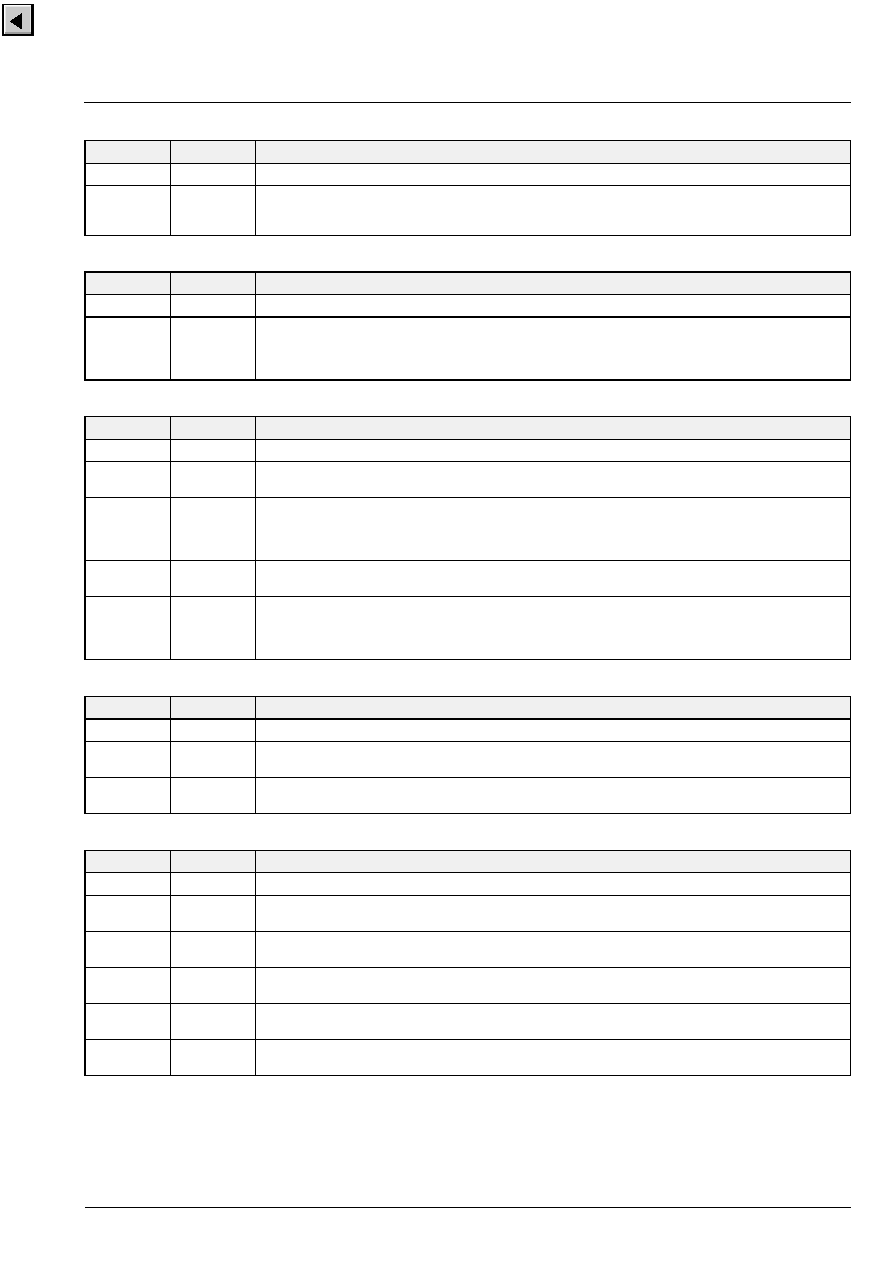

Fig. 2�1: Video front-end

VIN2

VIN3

VIN4

CIN1

VIN1

Bias

ADC

ADC

Gain

Clamp

Inp

u

t

Frequency

Reference

Generation

DVCO

�

150

ppm

AGC

+6/�4.5 dB

digital CVBS or Luma

digital Chroma

System Clocks

20.25 MHz

CVBS/Y

CVBS/Y

CVBS/Y

CVBS/Y

Chroma

Mu

x

CIN2

Chroma

Clamp

CBIN

Chroma

CRIN

mux

VOUT

CVBS/Y

3

VCT 38xxA

ADVANCE INFORMATION

12

Micronas

2.2.5. Digitally Controlled Clock Oscillator

The clock generation is also a part of the analog front-

end. The crystal oscillator is controlled digitally by the

control processor. The clock frequency can be

adjusted within

�

150 ppm.

2.2.6. Analog Video Output

The input signal of the Luma ADC is available at the

analog video output pin. The signal at this pin must be

buffered by a source follower. The output voltage is

2 V, thus the signal can be used to drive a 75-

line.

The magnitude is adjusted with an AGC in 8 steps

together with the main AGC.

2.3. Adaptive Comb Filter

The adaptive comb filter is used for high-quality lumi-

nance/chrominance separation for PAL or NTSC sig-

nals. The comb filter improves the luminance resolu-

tion (bandwidth) and reduces interferences like

cross-luminance and cross-color artifacts. The adap-

tive algorithm can eliminate most of the mentioned

errors without introducing new artifacts or noise.

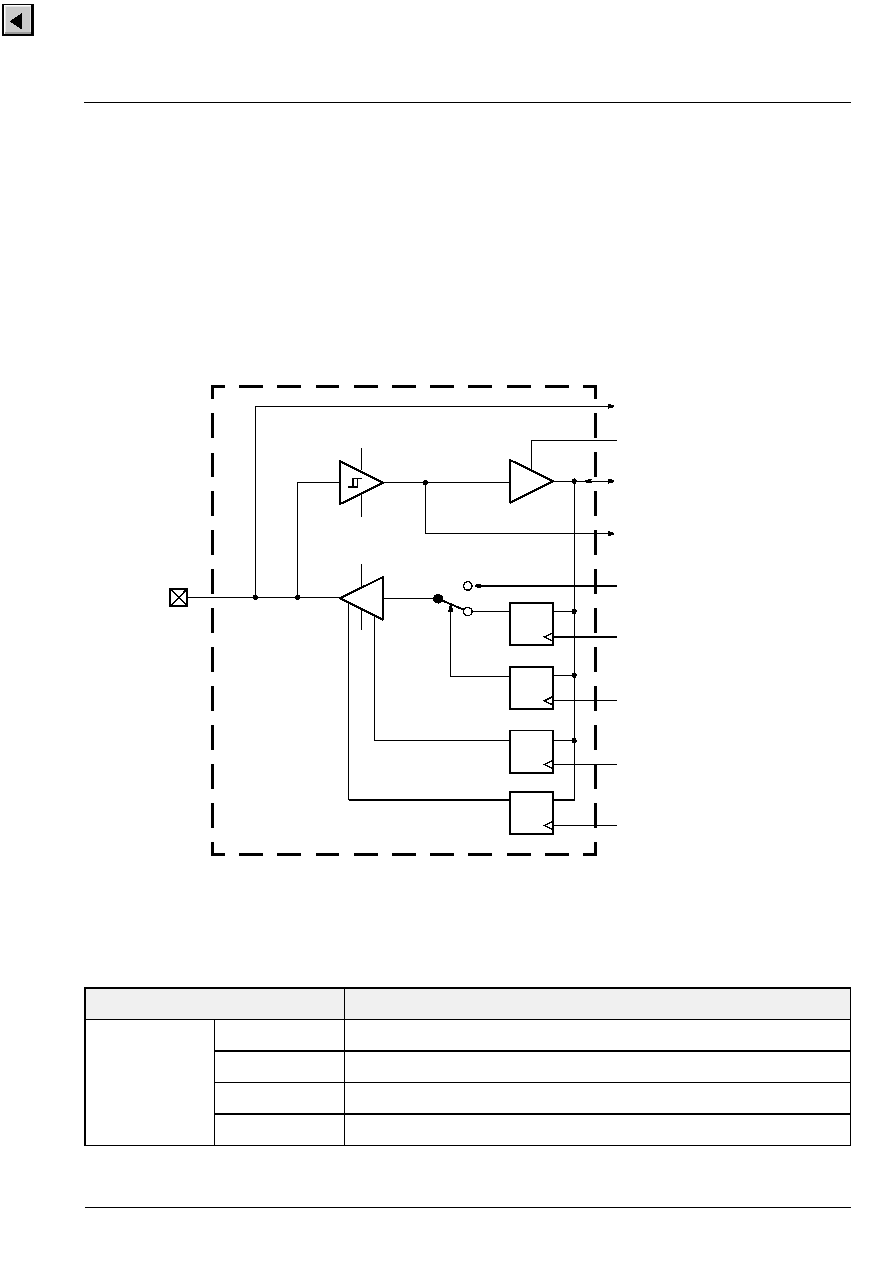

A block diagram of the comb filter is shown in Fig. 2�2.

The filter uses two line delays to process the informa-

tion of three adjacent video lines. To have a fixed

phase relationship of the color subcarrier in the three

channels, the system clock (20.25 MHz) is fractionally

locked to the color subcarrier. This allows the process-

ing of all color standards and substandards using a

single crystal frequency.

The CVBS signal in the three channels is filtered at the

subcarrier frequency by a set of bandpass/notch fil-

ters. The output of the three channels is used by the

adaption logic to select the weighting that is used to

reconstruct the luminance/chrominance signal from

the 4 bandpass/notch filter signals. By using soft mix-

ing of the 4 signals switching artifacts of the adaption

algorithm are completely suppressed.

The comb filter uses the middle line as reference,

therefore, the comb filter delay is one line. If the comb

filter is switched off, the delay lines are used to pass

the luma/ chroma signals from the A/D converters to

the luma/ chroma outputs. Thus, the comb filter delay

is always one line.

Various parameters of the comb filter are adjustable,

hence giving to the user the ability to adjust his own

desired picture quality.

Two parameters (KY, KC) set the global gain of luma

and chroma comb separately; these values directly

weigh the adaption algorithm output. In this way, it is

possible to obtain a luma/chroma separation ranging

from standard notch/bandpass to full comb decoding.

The parameter KB allows to choose between the two

proposed comb booster modes. This so-called feature

widely improves vertical high-to-low frequency transi-

tions areas, the typical example being a multiburst to

DC change. For KB=0, this improvement is kept mod-

erate, whereas, in case of KB=1, it is maximum, but

the risk to increase the "hanging dots" amount for

some given color transitions is higher.

Using the default setting, the comb filter has separate

luma and chroma decision algorithms; however, it is

possible to switch the chroma comb factor to the cur-

rent luma adaption output by setting CC to 1.

Another interesting feature is the programmable limita-

tion of the luma comb amount; proper limitation, asso-

ciated to adequate luma peaking, gives rise to an

enhanced 2-D resolution homogeneity. This limitation

is set by the parameter CLIM, ranging from 0 (no limi-

tation) to 31 (max. limitation).

The DAA parameter (1:off, 0:on) is used to disable/

enable a very efficient built-in "rain effect" suppressor;

many comb filters show this side effect which gives

some vertical correlation to a 2-D uniform random

area, due to the vertical filtering. This unnatural-look-

ing phenomenon is mostly visible on tuner images,

since they are always corrupted by some noise; and

this looks like rain.

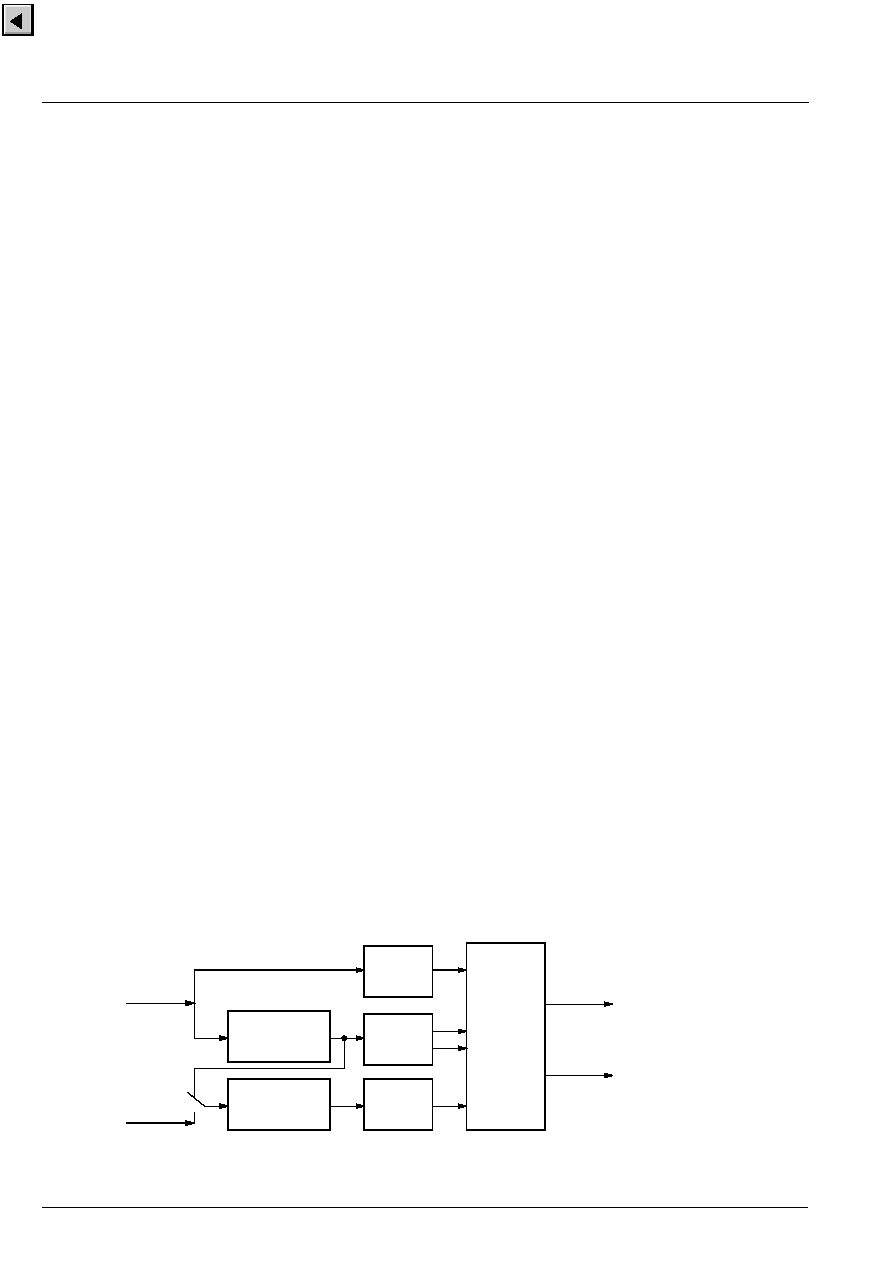

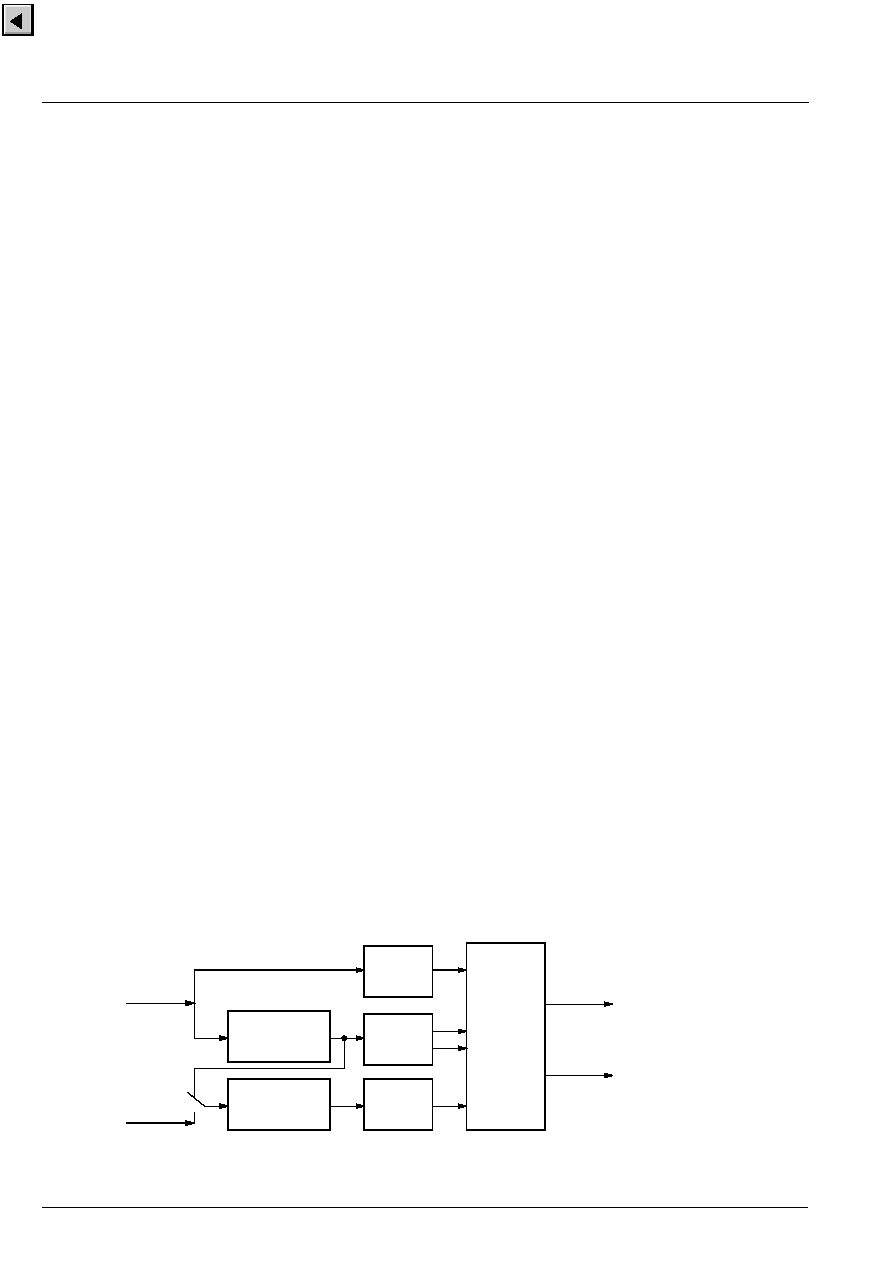

Fig. 2�2: Block diagram of the adaptive comb filter (PAL mode)

1H Delay Line

1H Delay Line

CVBS Input

Chroma Input

Bandpass

Filter

Bandpass

Filter

Bandpass/

Notch

Filter

Lum

a /

Chr

o

ma

Mixer

s

Ada

p

t

i

on L

ogi

c

Luma Output

Chroma Output

ADVANCE INFORMATION

VCT 38xxA

Micronas

13

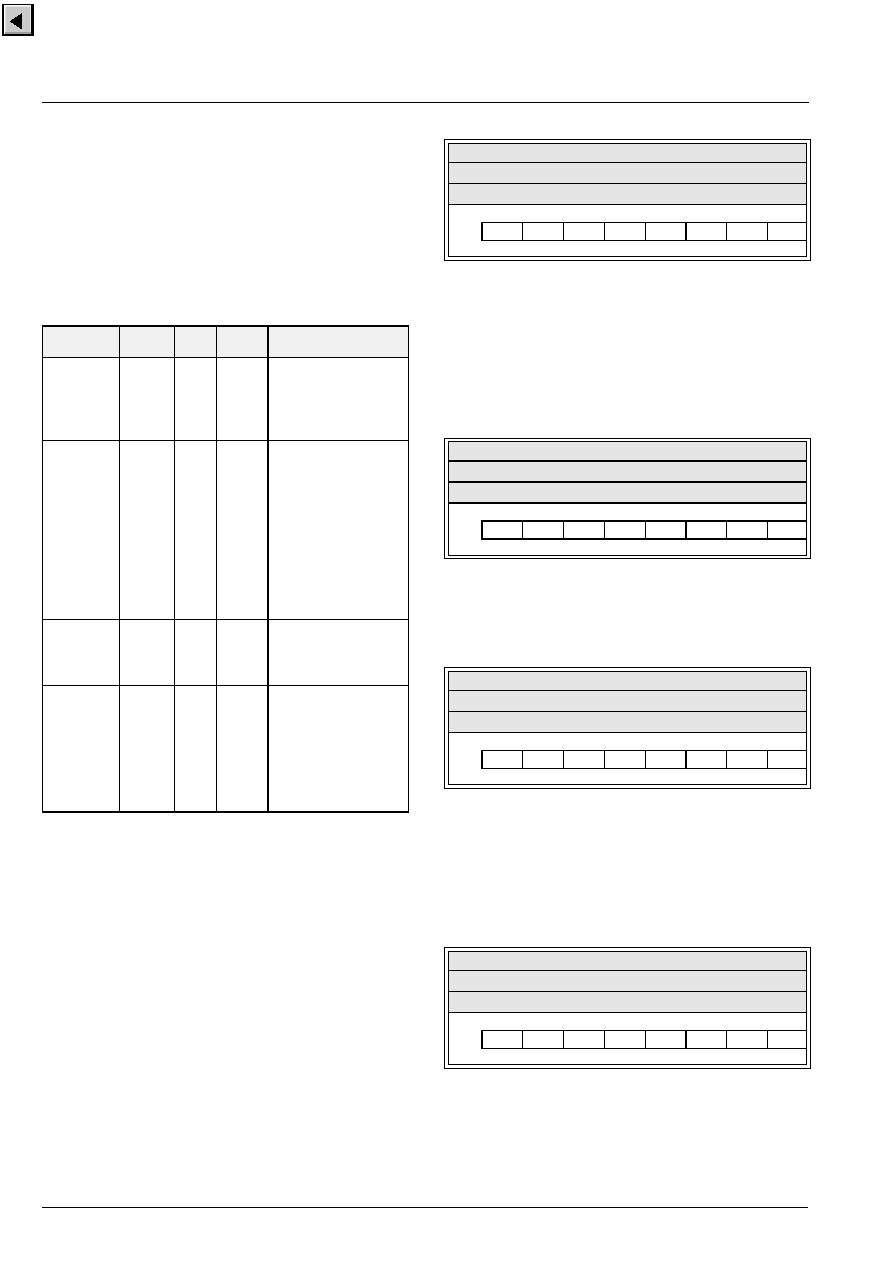

2.4. Color Decoder

In this block, the standard luma/chroma separation and

multi-standard color demodulation is carried out. The

color demodulation uses an asynchronous clock, thus

allowing a unified architecture for all color standards.

A block diagram of the color decoder is shown in Fig.

2�3. The luma as well as the chroma processing, is

shown here. The color decoder provides also some

special modes, e.g. wide band chroma format which is

intended for S-VHS wide bandwidth chroma.

If the adaptive comb filter is used for luma chroma sep-

aration, the color decoder uses the S-VHS mode pro-

cessing. The output of the color decoder is YC

r

C

b

in a

4:2:2 format.

Fig. 2�3: Color decoder

2.4.1. IF-Compensation

With off-air or mistuned reception, any attenuation at

higher frequencies or asymmetry around the color

subcarrier is compensated. Four different settings of

the IF-compensation are possible:

� flat (no compensation)

� 6 dB/octave

� 12 dB/octave

� 10 dB/MHz

The last setting gives a very large boost to high fre-

quencies. It is provided for SECAM signals that are

decoded using a SAW filter specified originally for the

PAL standard.

Fig. 2�4: Frequency response of chroma IF-com-

pensation

ColorPLL/ColorACC

1 H Delay

MUX

MU

X

CrossSwitch

Notch

Filter

Luma / CVBS

Luma

Chroma

Mixer

Low-pass Filter

Phase/Freq

Demodulator

ACC

Chroma

IF Compensation

DC-Reject

VCT 38xxA

ADVANCE INFORMATION

14

Micronas

2.4.2. Demodulator

The entire signal (which might still contain luma) is

now quadrature-mixed to the baseband. The mixing

frequency is equal to the subcarrier for PAL and NTSC,

thus achieving the chroma demodulation. For SECAM,

the mixing frequency is 4.286 MHz giving the quadra-

ture baseband components of the FM modulated

chroma. After the mixer, a low-pass filter selects the

chroma components; a downsampling stage converts

the color difference signals to a multiplexed half-rate

data stream.

The subcarrier frequency in the demodulator is gener-

ated by direct digital synthesis; therefore, substan-

dards such as PAL 3.58 or NTSC 4.43 can also be

demodulated.

2.4.3. Chrominance Filter

The demodulation is followed by a low-pass filter for

the color difference signals for PAL/NTSC. SECAM

requires a modified low-pass function with bell-filter

characteristic. At the output of the low-pass filter, all

luma information is eliminated.

The low-pass filters are calculated in time multiplex for

the two color signals. Three bandwidth settings (nar-

row, normal, broad) are available for each standard.

For PAL/NTSC, a wide band chroma filter can be

selected. This filter is intended for high bandwidth

chroma signals, e.g. a non-standard wide bandwidth

S-VHS signal.

Fig. 2�5: Frequency response of chroma filters

2.4.4. Frequency Demodulator

The frequency demodulator for demodulating the

SECAM signal is implemented as a CORDIC structure.

It calculates the phase and magnitude of the quadra-

ture components by coordinate rotation.

The phase output of the CORDIC processor is differ-

entiated to obtain the demodulated frequency. After

the deemphasis filter, the Dr and Db signals are scaled

to standard C

r

C

b

amplitudes and fed to the crossover

switch.

2.4.5. Burst Detection / Saturation Control

In the PAL/NTSC-system the burst is the reference for

the color signal. The phase and magnitude outputs of

the CORDIC are gated with the color key and used for

controlling the phase-locked-loop (APC) of the demod-

ulator and the automatic color control (ACC) in PAL/

NTSC.

The ACC has a control range of +30...

-

6 dB.

Color saturation can be selected once for all color

standards. In PAL/NTSC it is used as reference for the

ACC. In SECAM the necessary gains are calculated

automatically.

For SECAM decoding, the frequency of the burst is

measured. Thus, the current chroma carrier frequency

can be identified and is used to control the SECAM

processing. The burst measurements also control the

color killer operation; they are used for automatic stan-

dard detection as well.

2.4.6. Color Killer Operation

The color killer uses the burst-phase/burst-frequency

measurement to identify a PAL/NTSC or SECAM color

signal. For PAL/NTSC, the color is switched off (killed)

as long as the color subcarrier PLL is not locked. For

SECAM, the killer is controlled by the toggle of the

burst frequency. The burst amplitude measurement is

used to switch-off the color if the burst amplitude is

below a programmable threshold. Thus, color will be

killed for very noisy signals. The color amplitude killer

has a programmable hysteresis.

PAL/NTSC

SECAM

ADVANCE INFORMATION

VCT 38xxA

Micronas

15

2.4.7. Automatic Standard Recognition

The burst-frequency measurement is also used for

automatic standard recognition (together with the sta-

tus of horizontal and vertical locking) thus allowing a

completely independent search of the line and color

standard of the input signal. The following standards

can be distinguished:

PAL B,G,H,I; NTSC M; SECAM; NTSC 44; PAL M;

PAL N; PAL 60

For a preselection of allowed standards, the recogni-

tion can be enabled/disabled via I

2

C bus for each stan-

dard separately.

If at least one standard is enabled, the VCT 38xxA reg-

ularly checks the horizontal and vertical locking of the

input signal and the state of the color killer. If an error

exists for several adjacent fields a new standard

search is started. Depending on the measured line

number and burst frequency, the current standard is

selected.

For error handling the recognition algorithm delivers

the following status information:

� search active (busy)

� search terminated, but failed

� found standard is disabled

� vertical standard invalid

� no color found

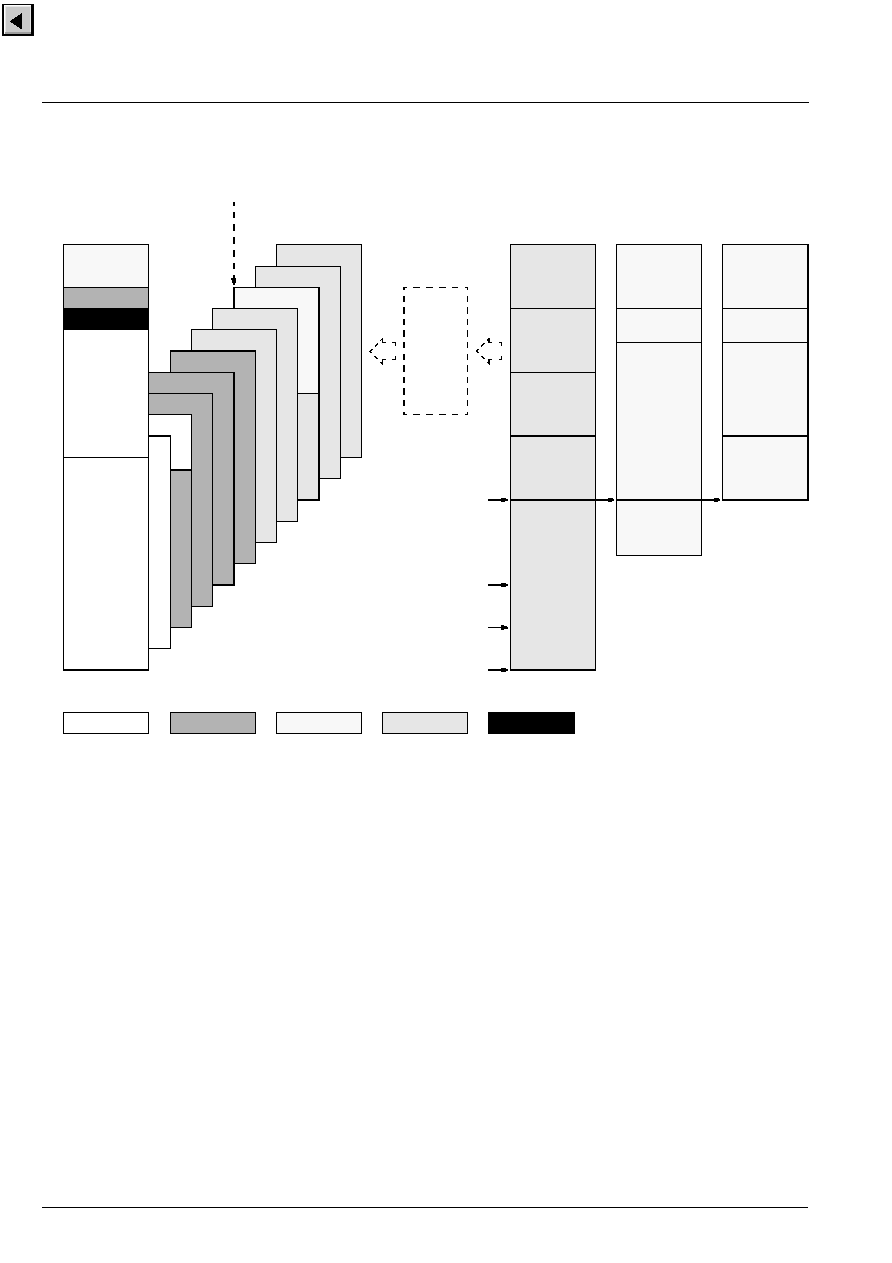

2.4.8. PAL Compensation/1-H Comb Filter

The color decoder uses one fully integrated delay line.

Only active video is stored.

The delay line application depends on the color stan-

dard:

� NTSC:

1-H comb filter or color compensation

� PAL:

color compensation

� SECAM: crossover switch

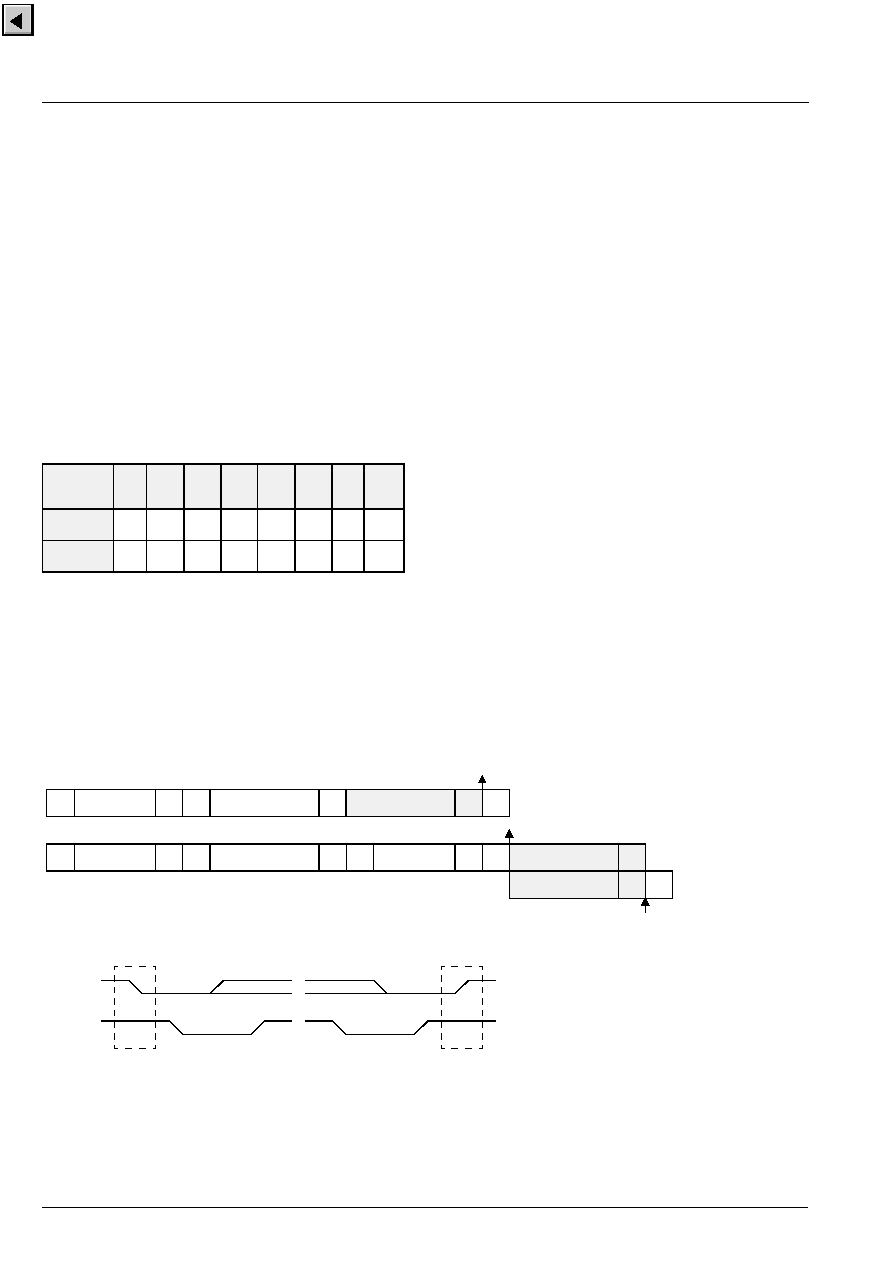

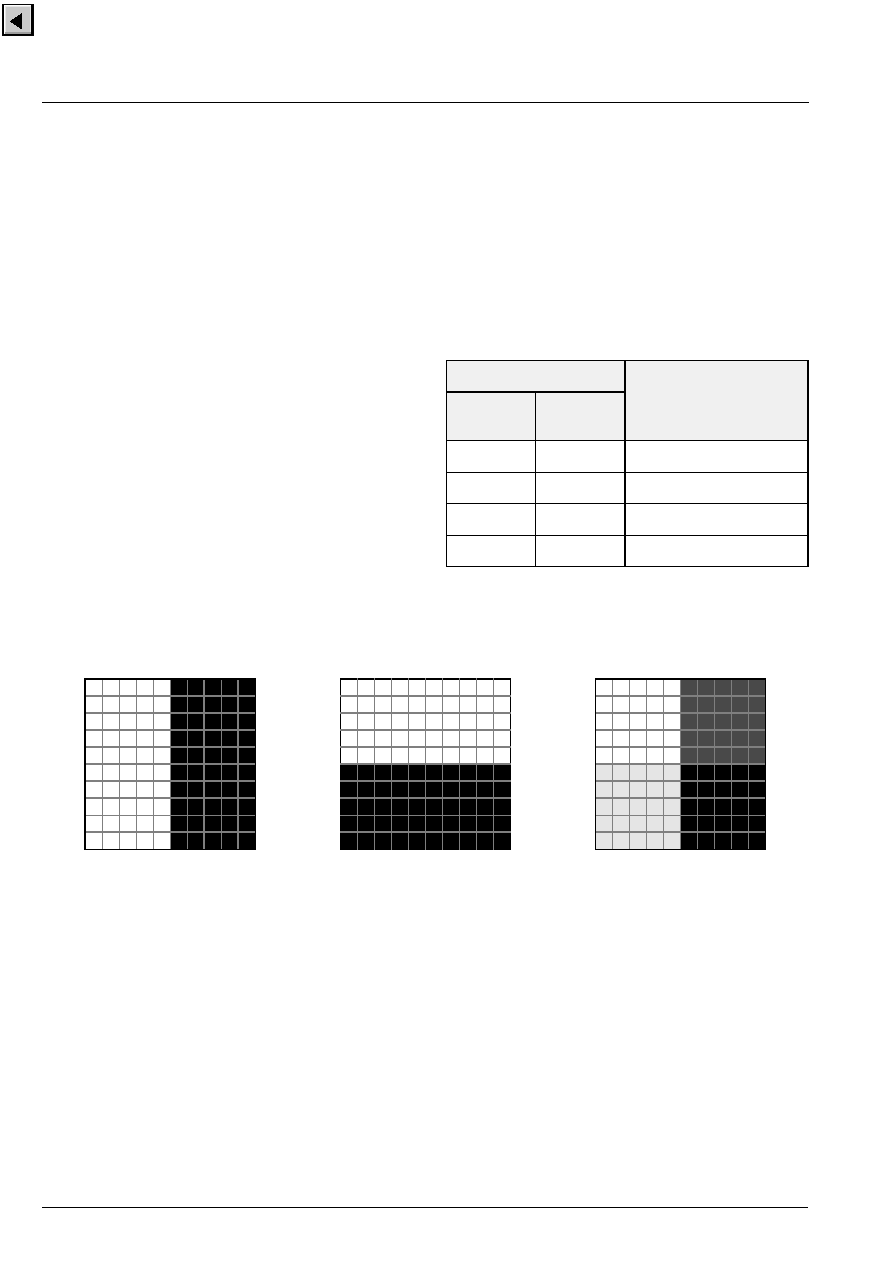

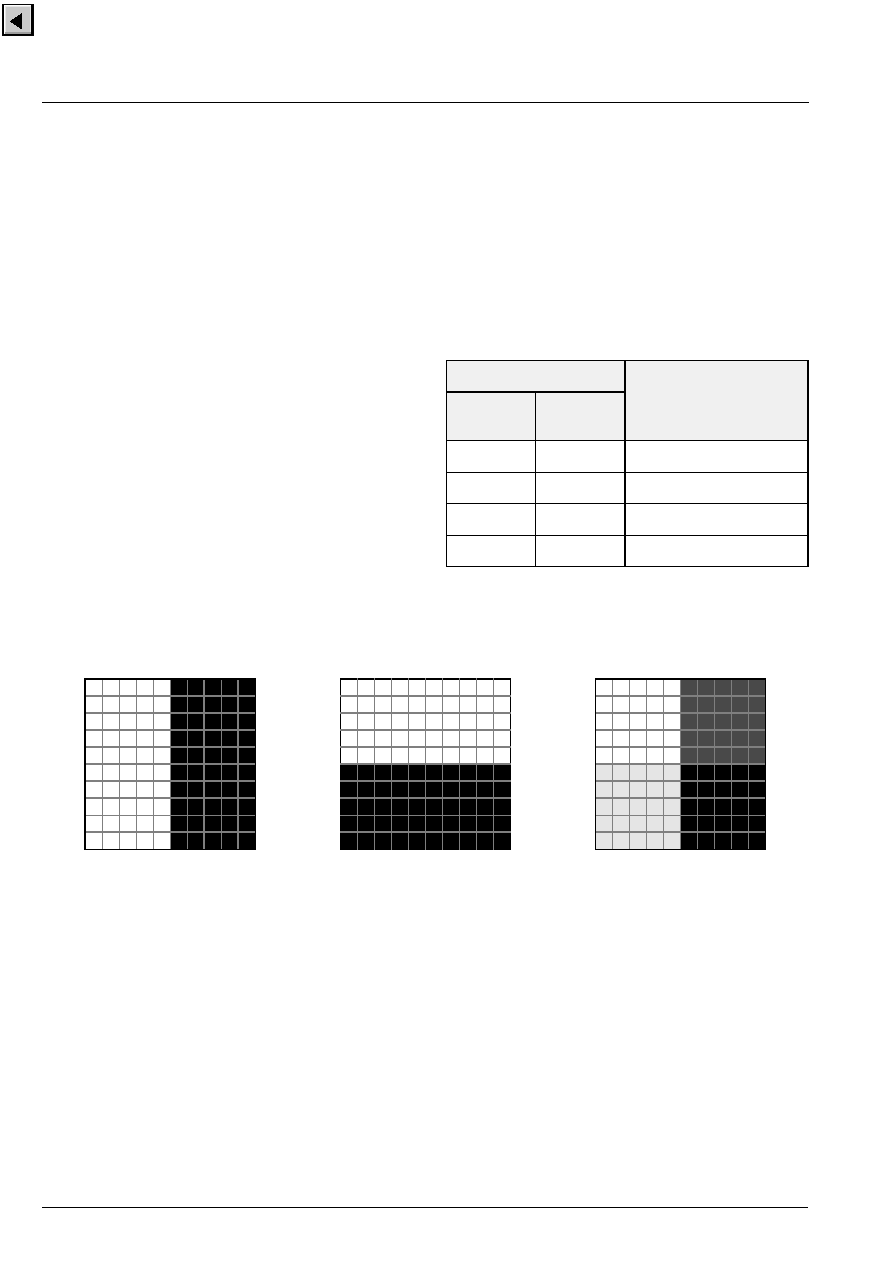

In the NTSC compensated mode, (Fig. 2�6c), the color

signal is averaged for two adjacent lines. Thus,

cross-color distortion and chroma noise is reduced. In

the NTSC comb filter mode, (Fig. 2�6d), the delay line

is in the composite signal path, thus allowing reduction

of cross-color components, as well as cross-lumi-

nance. The loss of vertical resolution in the luminance

channel is compensated by adding the vertical detail

signal with removed color information.

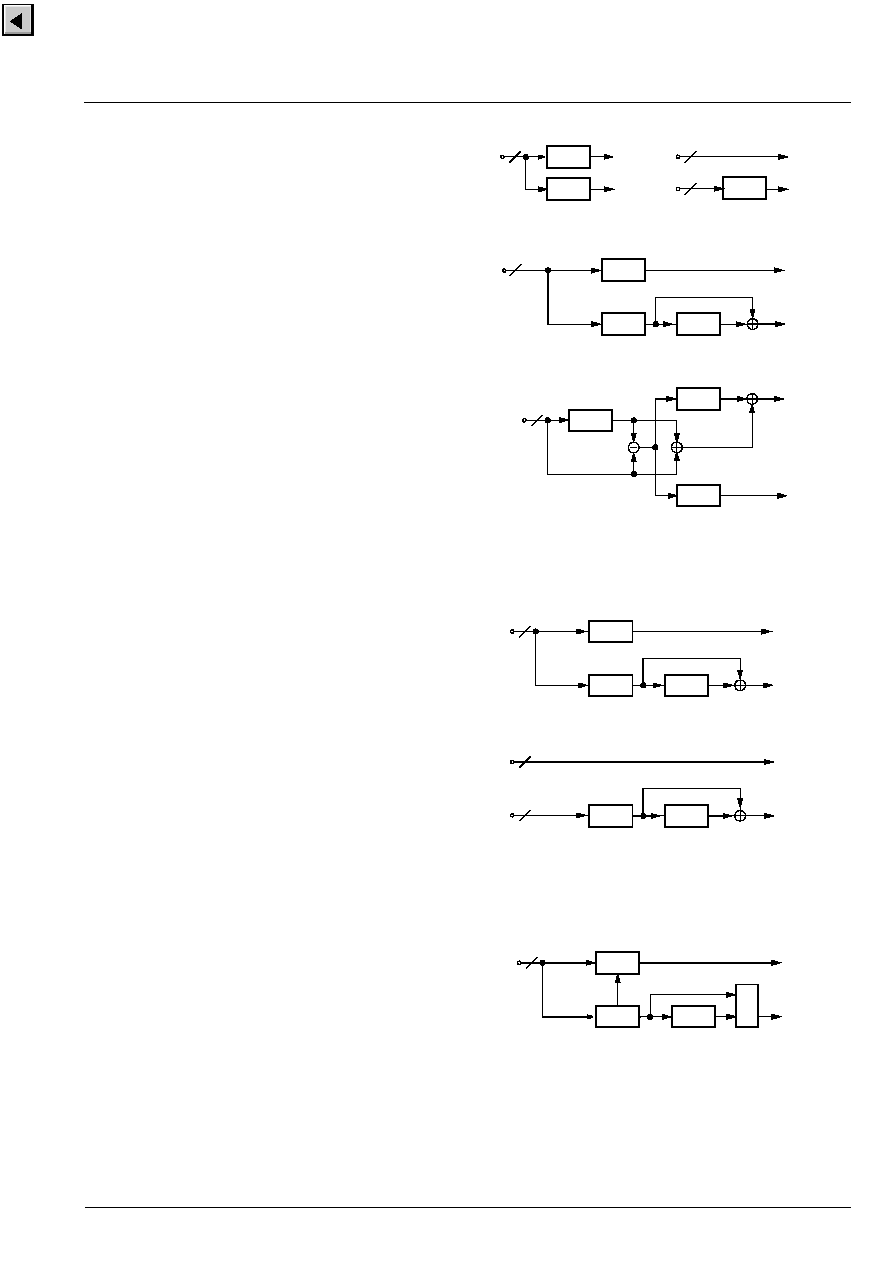

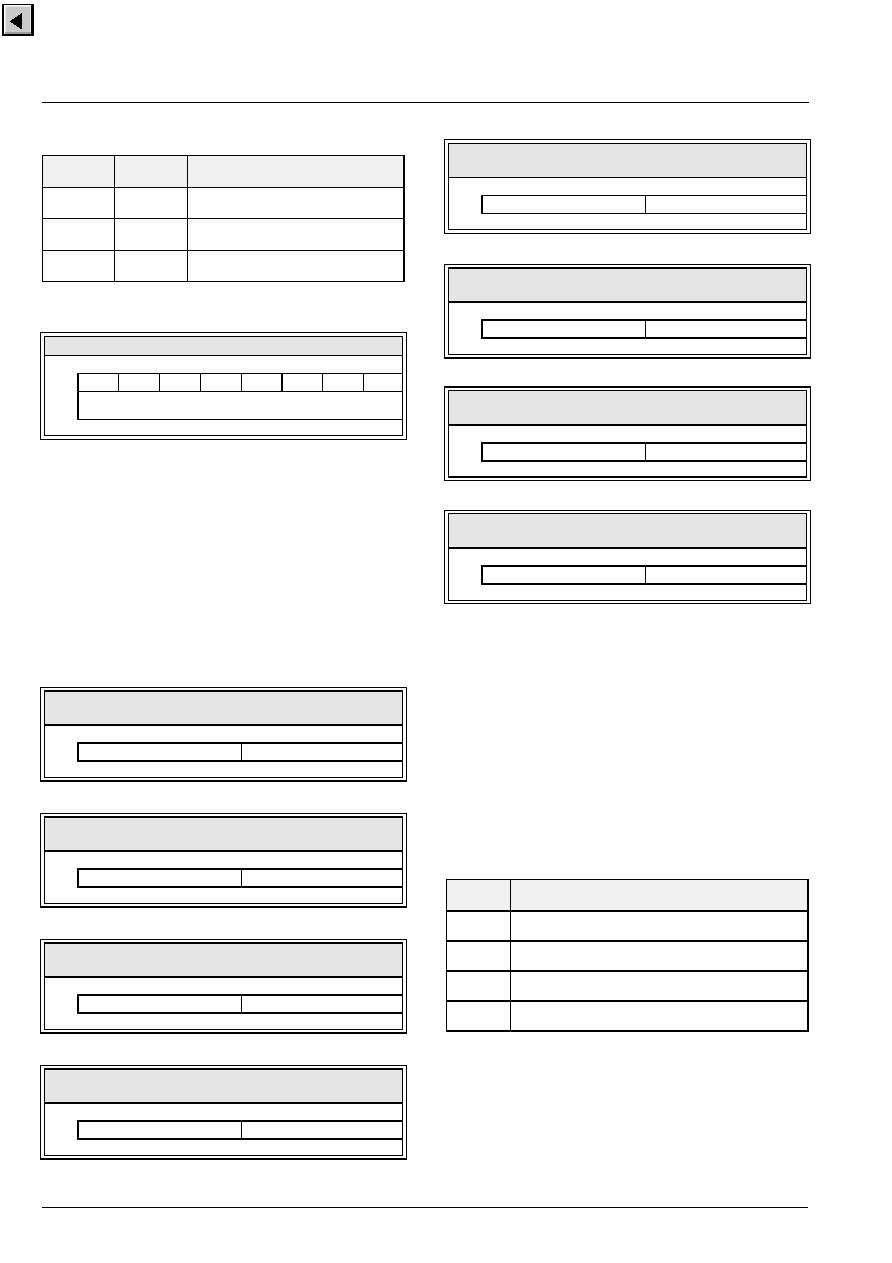

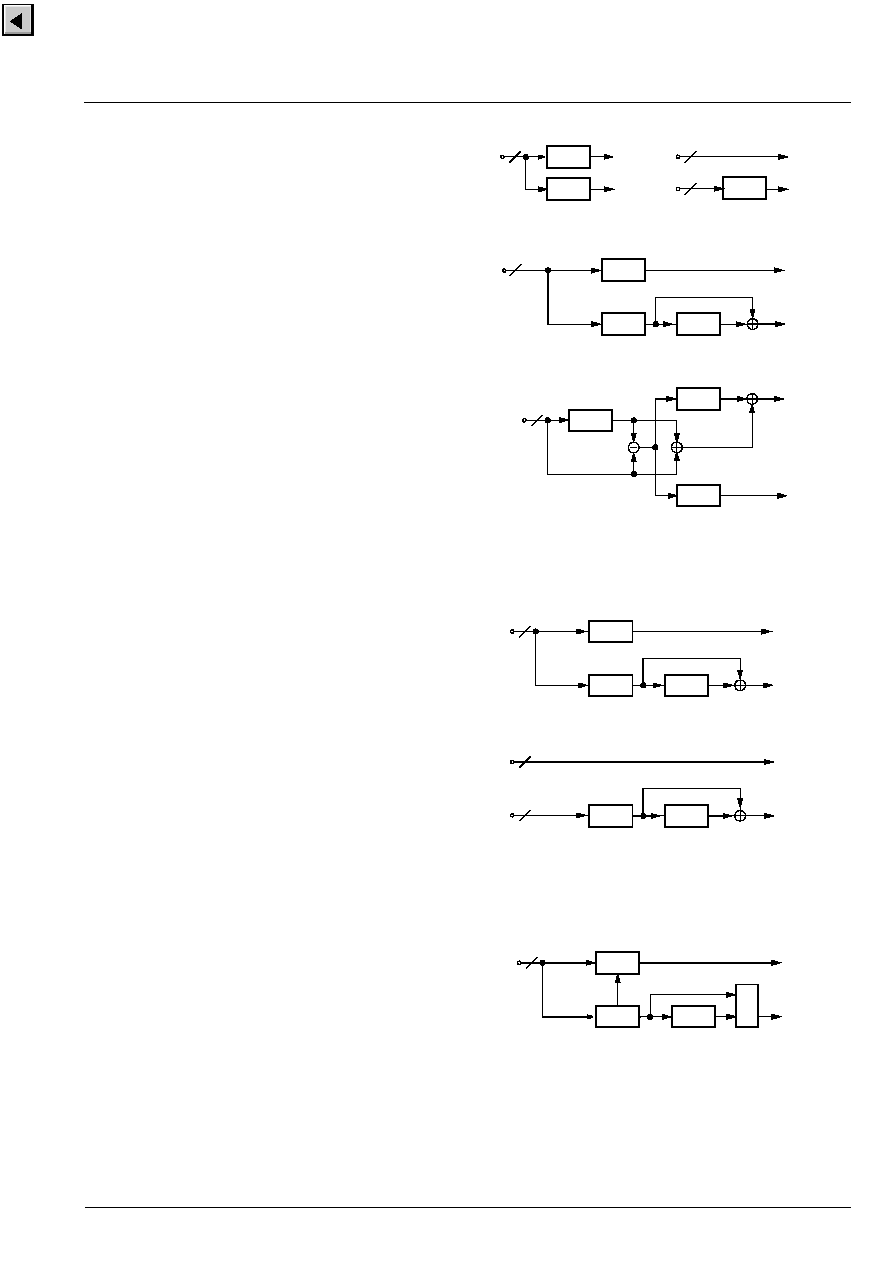

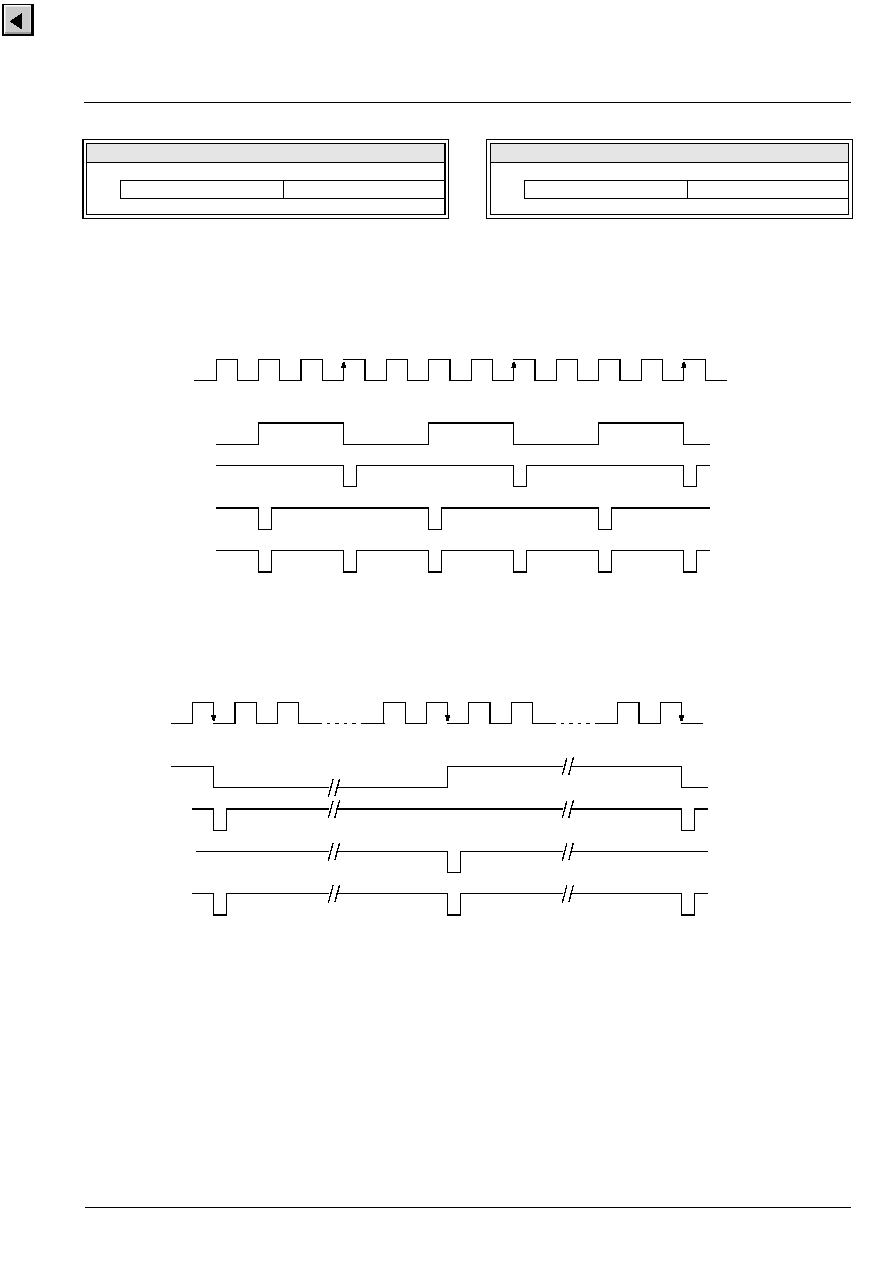

Fig. 2�6: NTSC color decoding options

Fig. 2�7: PAL color decoding options

Fig. 2�8: SECAM color decoding

chroma

Notch

filter

8

Chroma

Process.

CVBS

Y

1 H

Delay

8

CVBS

Chroma

Process.

Notch

filter

Y

8

Chroma

Process.

Luma

Y

8

C C

r b

C C

r b

C C

r b

Notch

filter

1 H

Delay

8

Chroma

Process.

CVBS

Y

C C

r b

d) comb filter

c) compensated

a) conventional

b) S-VHS

Chroma

Notch

filter

1 H

Delay

8

Chroma

Process.

CVBS

Y

8

Chroma

Process.

Luma

Y

8

1 H

Delay

C C

r b

C C

r b

a) conventional

b) S-VHS

MUX

Notch

filter

1 H

Delay

8

Chroma

Process.

CVBS

Y

C C

r b

VCT 38xxA

ADVANCE INFORMATION

16

Micronas

2.4.9. Luminance Notch Filter

If a composite video signal is applied, the color infor-

mation is suppressed by a programmable notch filter.

The position of the filter center frequency depends on

the subcarrier frequency for PAL/NTSC. For SECAM,

the notch is directly controlled by the chroma carrier

frequency. This considerably reduces the cross-lumi-

nance. The frequency responses for all three systems

are shown in Fig. 2�9.

Fig. 2�9: Frequency responses of the luma

notch filter for PAL, NTSC, SECAM

2.4.10.Skew Filtering

The system clock is free-running and not locked to the

TV line frequency. Therefore, the ADC sampling pat-

tern is not orthogonal. The decoded YC

r

C

b

signals are

converted to an orthogonal sampling raster by the

skew filters, which are part of the scaler block.

The skew filters allow the application of a group delay

to the input signals without introducing waveform or

frequency response distortion.

The amount of phase shift of this filter is controlled by

the horizontal PLL1. The accuracy of the filters is 1/32

clocks for luminance and 1/4 clocks for chroma. Thus

the 4:2:2 YC

r

C

b

data is in an orthogonal pixel format

even in the case of nonstandard input signals such as

VCR.

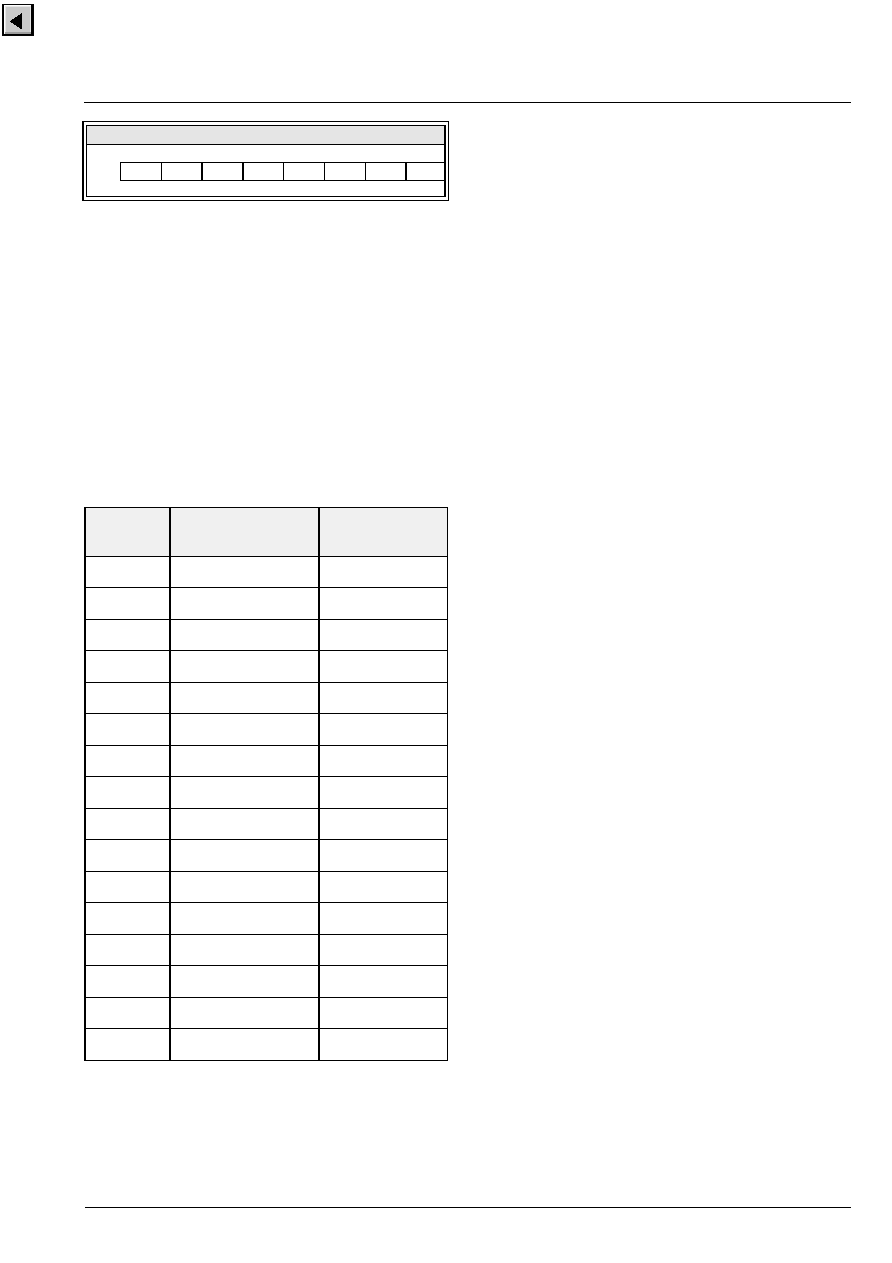

2.5. Horizontal Scaler

The 4:2:2 YC

r

C

b

signal from the color decoder is pro-

cessed by the horizontal scaler. The scaler block

allows a linear or nonlinear horizontal scaling of the

input video signal in the range of 0.25 to 4. Nonlinear

scaling, also called "Panoramavision", provides a geo-

metrical distortion of the input picture. It is used to fit a

picture with 4:3 format on a 16:9 screen by stretching

the picture geometry at the borders. Also, the inverse

effect can be produced by the scaler. A summary of

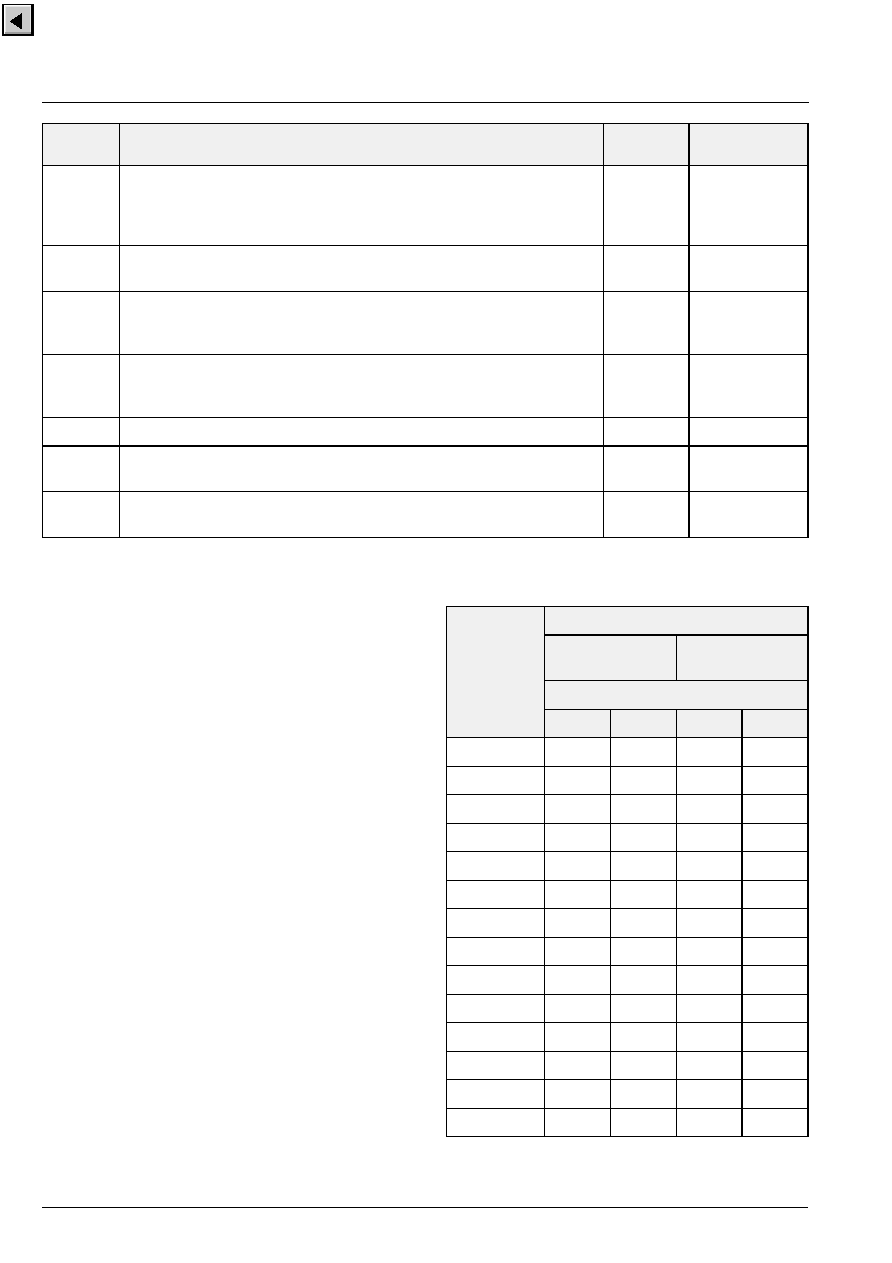

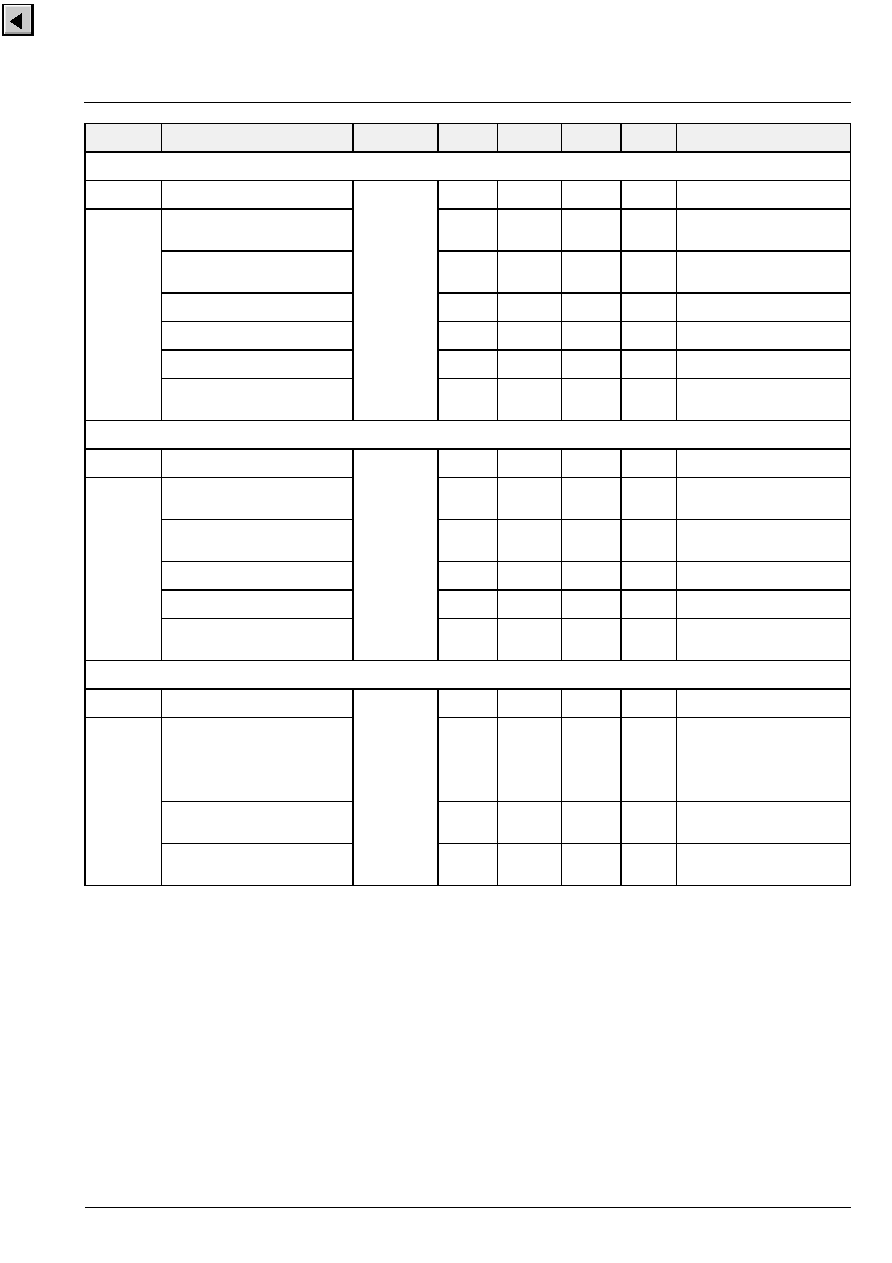

scaler modes is given in Table 2�1.

The scaler contains a programmable decimation filter,

a 1-line FIFO memory, and a programmable interpola-

tion filter. The scaler input filter is also used for pixel

skew correction (see Section 2.4.10. on page 16). The

decimator/interpolator structure allows optimal use of

the FIFO memory. The controlling of the scaler is done

by the internal Fast Processor.

2.6. Black-line Detector

In case of a letterbox format input video, e.g. Cinema-

scope, PAL+ etc., black areas at the upper and lower

part of the picture are visible. It is suitable to remove or

reduce these areas by a vertical zoom and/or shift

operation.

The VCT 38xxA supports this feature by a letterbox

detector. The circuitry detects black video lines by

measuring the signal amplitude during active video.

For every field the number of black lines at the upper

and lower part of the picture are measured, compared

to the previous measurement and the minima are

stored in the I

2

C-register BLKLIN. To adjust the picture

dB

MHz

10

0

2

4

6

8

10

0

�10

�20

�30

�40

dB

MHz

10

0

2

4

6

8

10

0

�10

�20

�30

�40

PAL/NTSC notch filter

SECAM notch filter

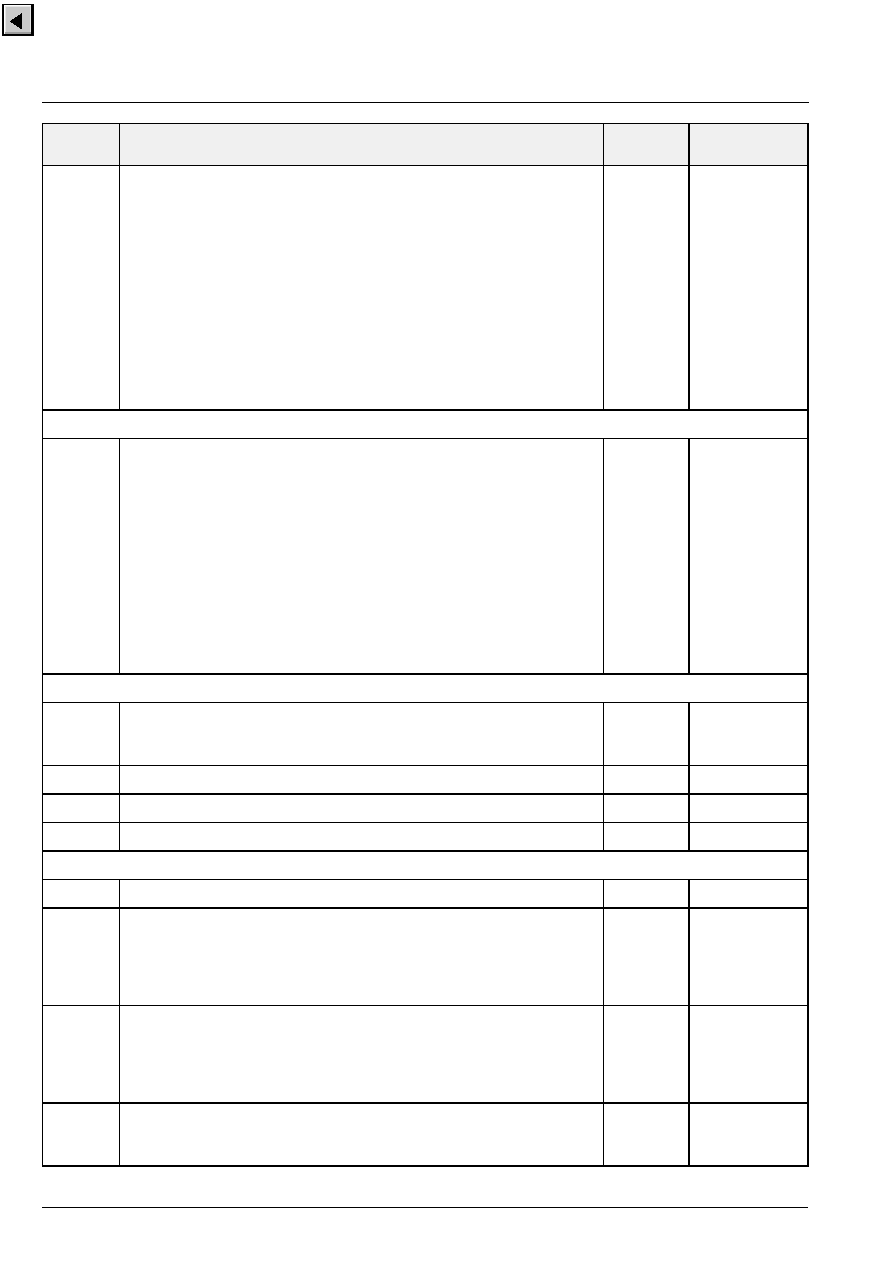

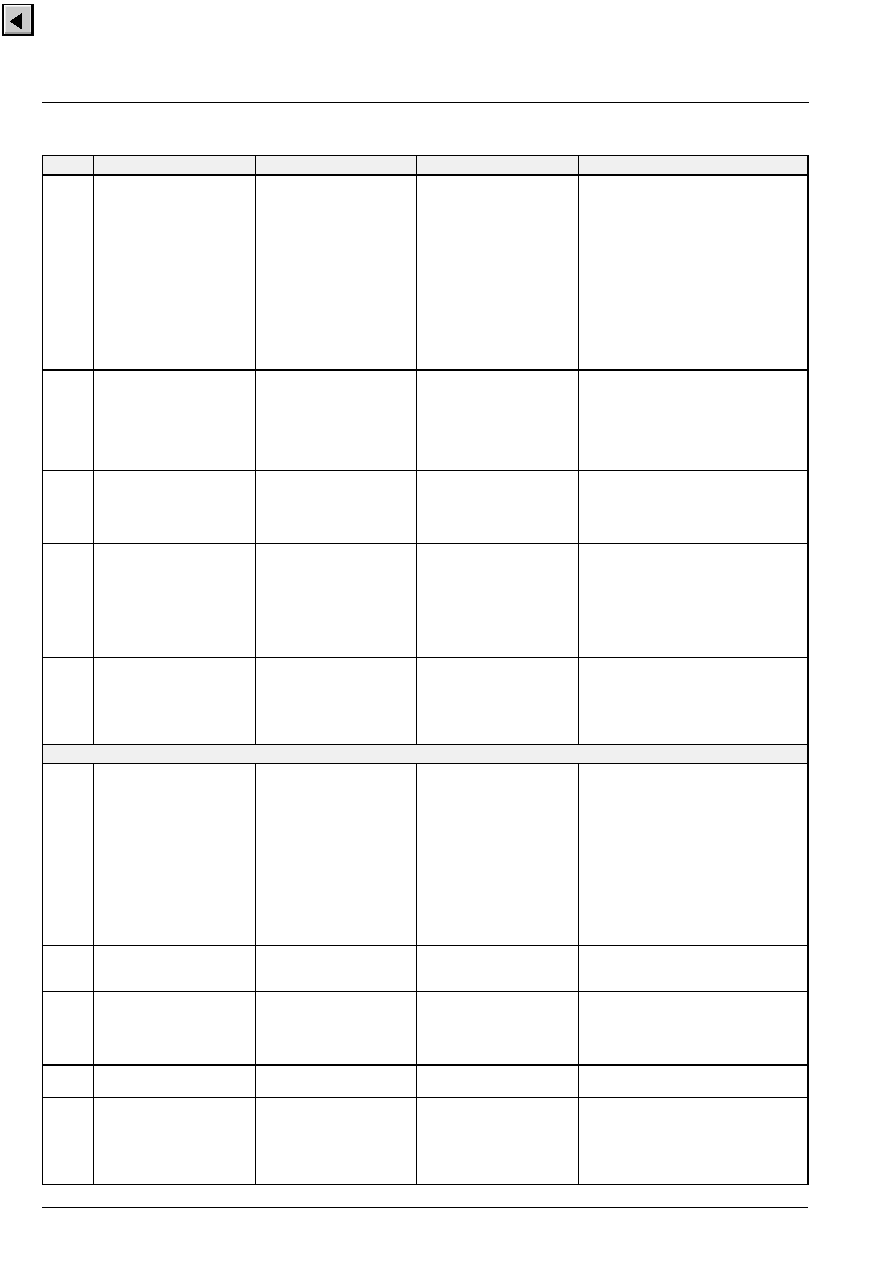

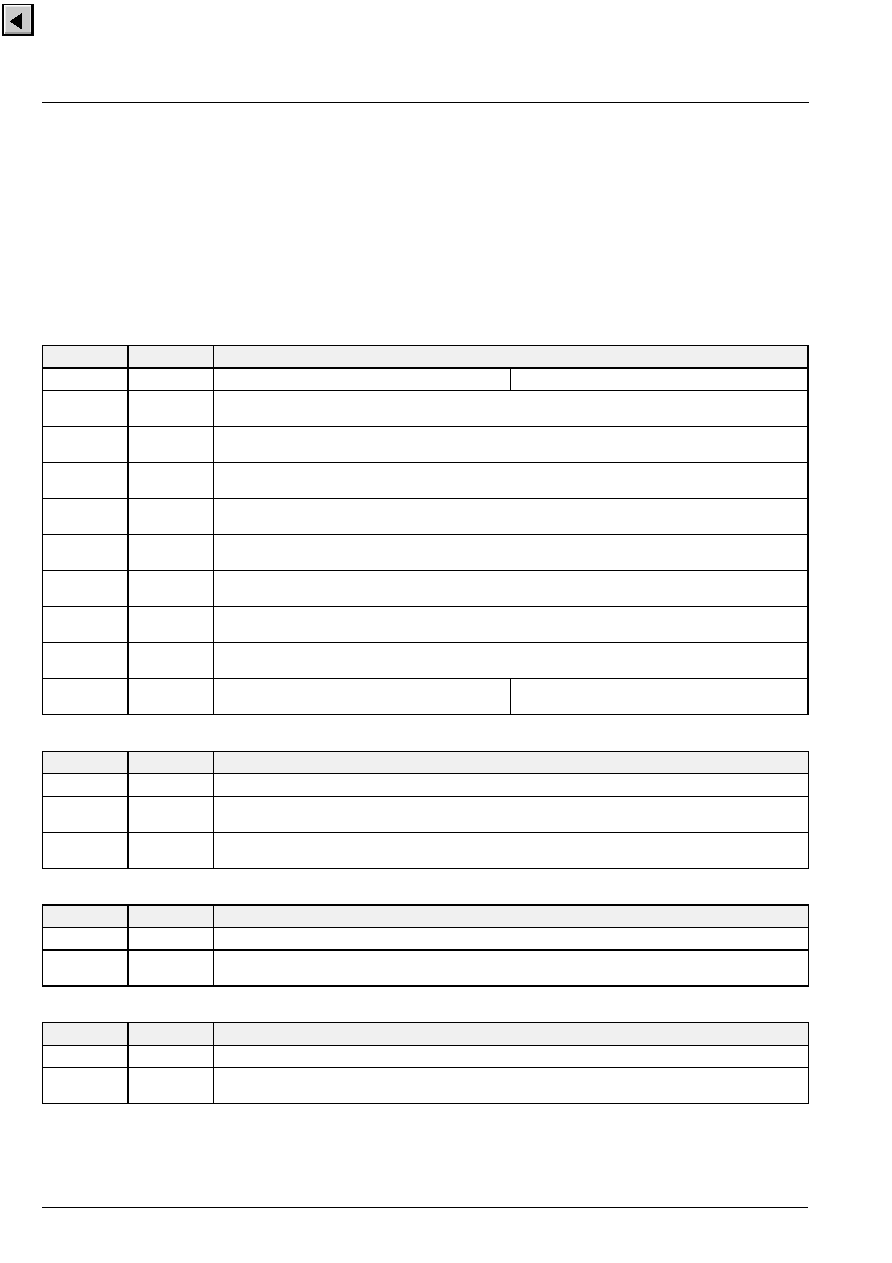

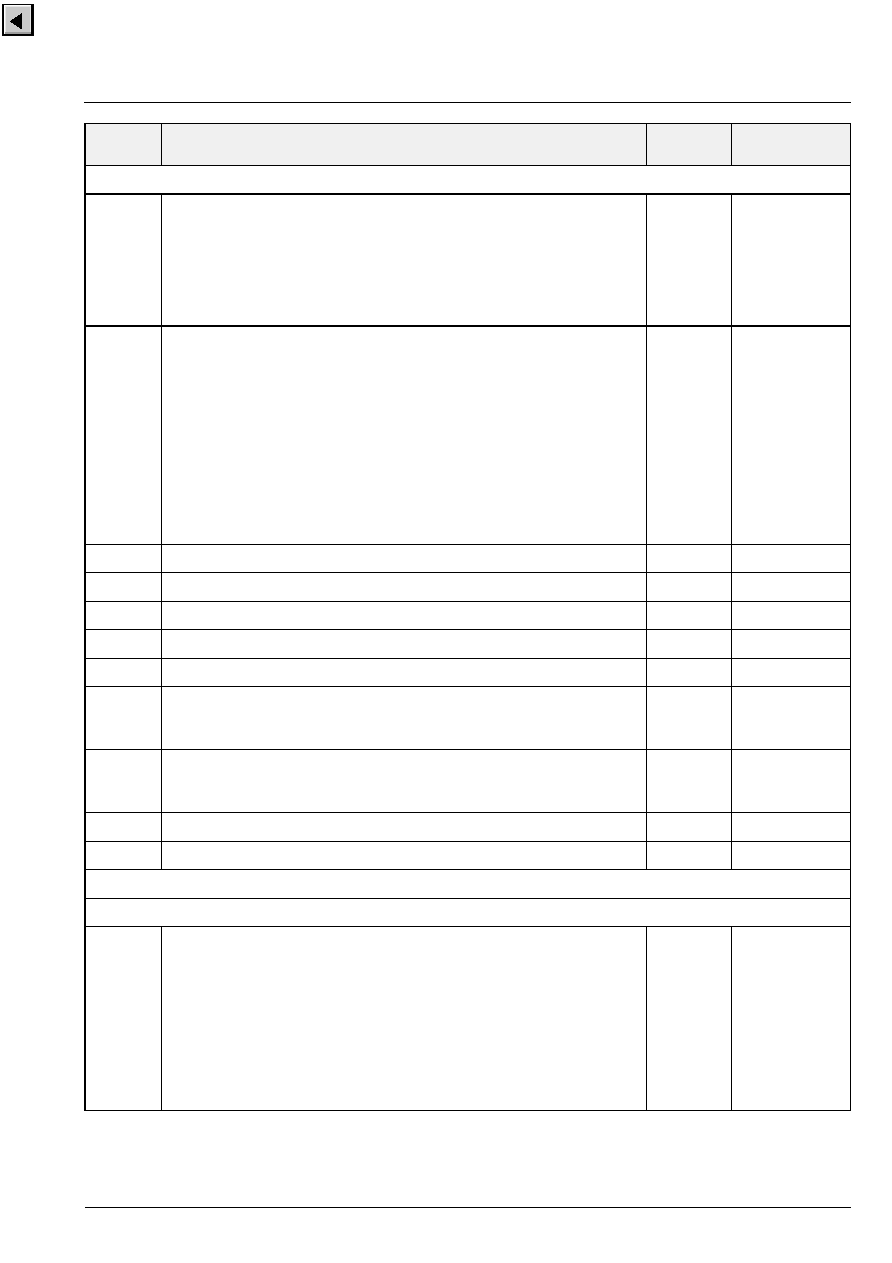

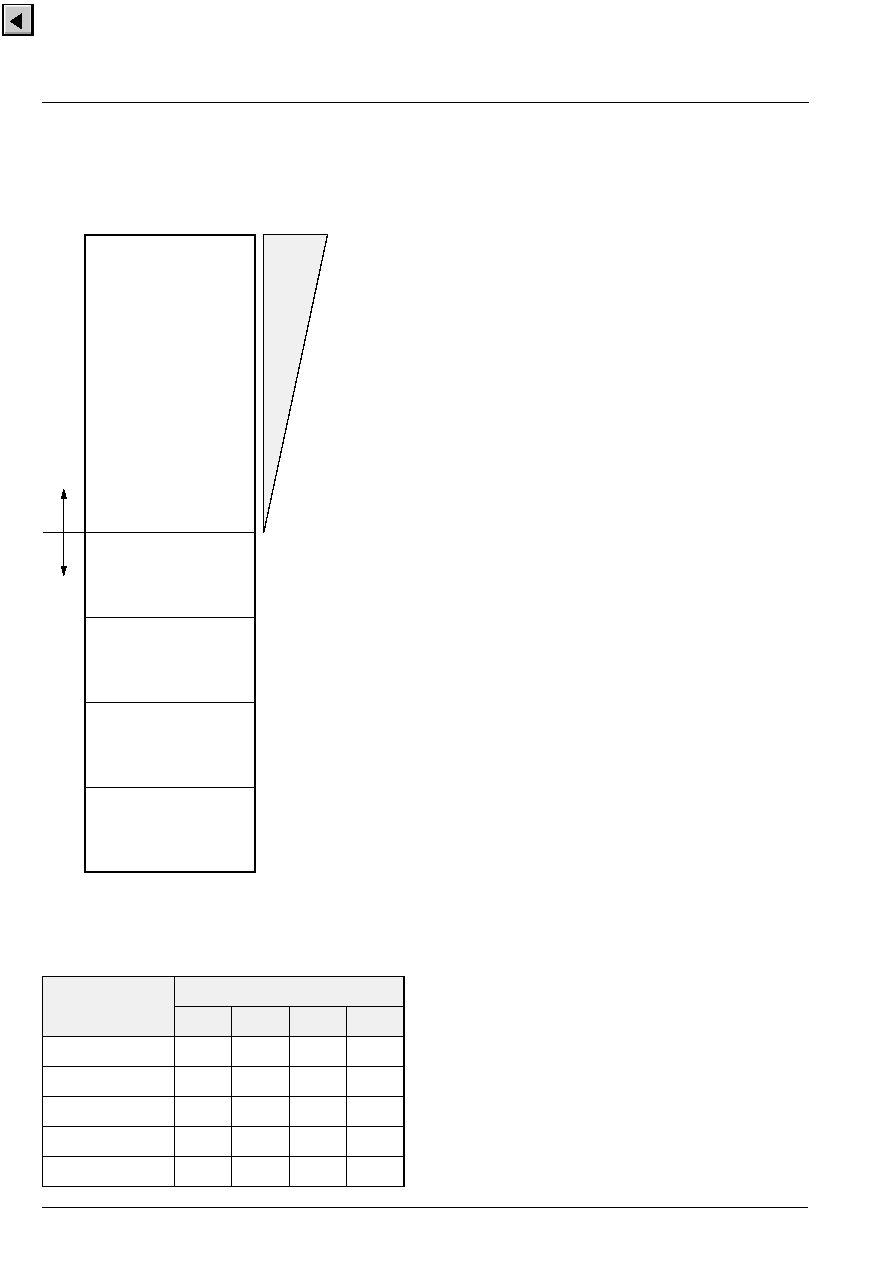

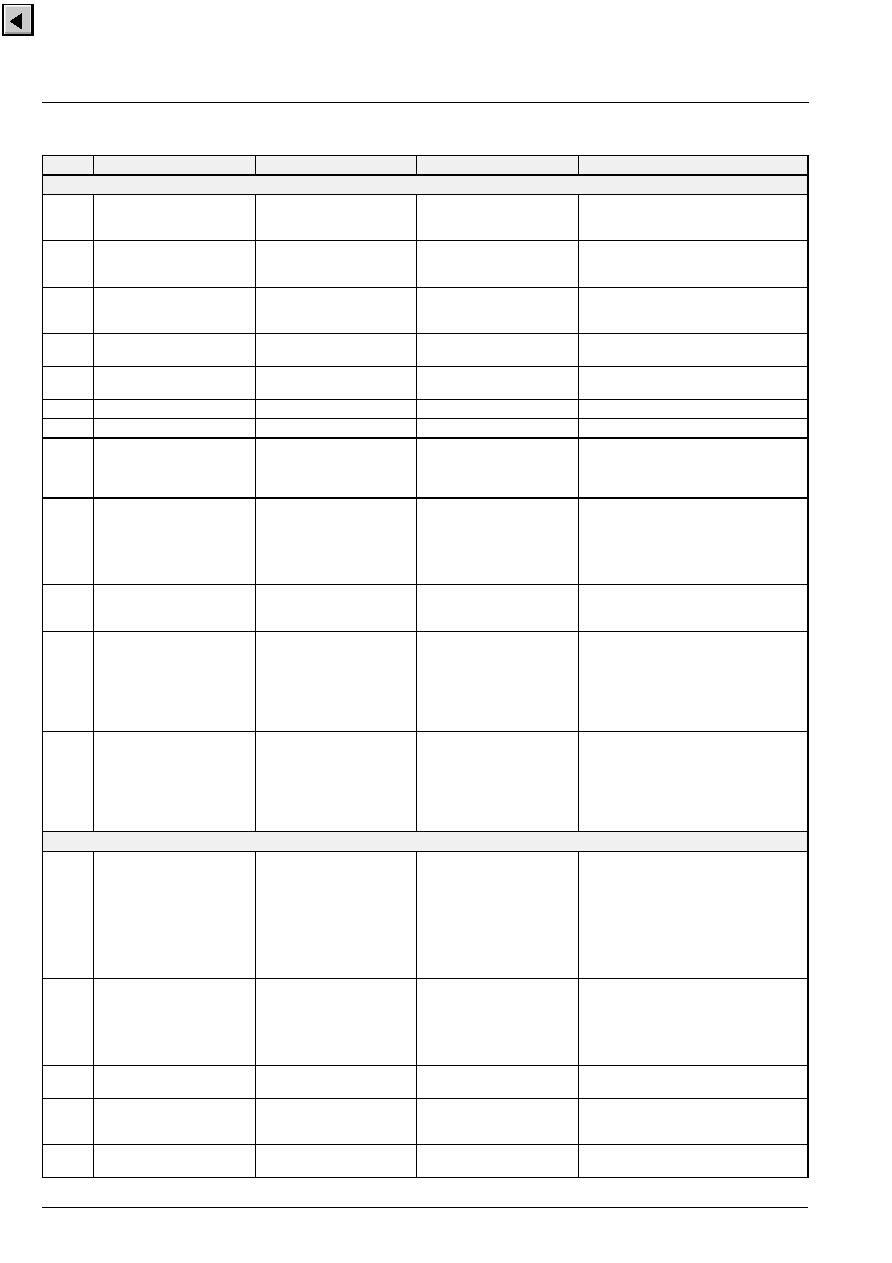

Table 2�1: Scaler modes

Mode

Scale

Factor

Description

Compression

4:3

16:9

0.75

linear

4:3 source displayed on

a 16:9 tube,

with side panels

Panorama

4:3

16:9

non-

linear

compr

4:3 source displayed on

a 16:9 tube,

Borders distorted

Zoom

4:3

4:3

1.33

linear

Letterbox source (PAL+)

displayed on a 4:3 tube,

vertical overscan with

cropping of side panels

Panorama

4:3

4:3

non-

linear

zoom

Letterbox source (PAL+)

displayed on a 4:3 tube,

vertical overscan, bor-

ders distorted, no crop-

ping

ADVANCE INFORMATION

VCT 38xxA

Micronas

17

amplitude, the external controller reads this register,

calculates the vertical scaling coefficient and transfers

the new settings, e.g. vertical sawtooth parameters,

horizontal scaling coefficient etc., to the VCT 38xxA.

Letterbox signals containing logos on the left or right

side of the black areas are processed as black lines,

while subtitles, inserted in the black areas, are pro-

cessed as non-black lines. Therefore, the subtitles are

visible on the screen. To suppress the subtitles, the

vertical zoom coefficient is calculated by selecting the

larger number of black lines only. Dark video scenes

with a low contrast level compared to the letterbox area

are indicated by the BLKPIC bit.

2.7. Test Pattern Generator

The YC

r

C

b

outputs can be switched to a test mode

where YC

r

C

b

data are generated digitally in the

VCT 38xxA. Test patterns include luma/chroma ramps

and flat fields.

2.8. Video Sync Processing

Fig. 2�10 shows a block diagram of the front-end sync

processing. To extract the sync information from the

video signal, a linear phase low-pass filter eliminates

all noise and video contents above 1 MHz. The sync is

separated by a slicer; the sync phase is measured. A

variable window can be selected to improve the noise

immunity of the slicer. The phase comparator mea-

sures the falling edge of sync, as well as the integrated

sync pulse.

The sync phase error is filtered by a phase-locked loop

that is computed by the FP. All timing in the front-end is

derived from a counter that is part of this PLL, and it

thus counts synchronously to the video signal.

A separate hardware block measures the signal back

porch and also allows gathering the maximum/mini-

mum of the video signal. This information is processed

by the FP and used for gain control and clamping.

For vertical sync separation, the sliced video signal is

integrated. The FP uses the integrator value to derive

vertical sync and field information.

The information extracted by the video sync process-

ing is multiplexed onto the hardware front sync signal

(FSY) and is distributed to the rest of the video pro-

cessing system.

The data for the vertical deflection, the sawtooth, and

the East-West correction signal is calculated by the

VCT 38xxA. The data is buffered in a FIFO and trans-

ferred to the back-end by a single wire interface.

Frequency and phase characteristics of the analog

video signal are derived from PLL1. The results are fed

to the scaler unit for data interpolation and orthogonal-

ization and to the clock synthesizer for line-locked

clock generation. Horizontal and vertical syncs are

latched with the line-locked clock.

Fig. 2�10: Sync separation block diagram

Phase

Separator

&

Low-pass

counter

Front-end

Timing

Front Sync

low-pass

1 MHz

&

sync slicer

Horizontal

Sync

Separation

Vertical

Sync

Separation

FIFO

Sawtooth

video

input

Skew

Front

Sync

Generator

Vertical

Serial

Data

Vertical

Sawtooth

E/W

Parabola

Calculation

clamping, colorkey, FIFO_write

PLL1

Clamp &

Signal

Meas.

Vblank

Field

Clock

Synthesizer

Syncs

Clock

H/V Syncs

VCT 38xxA

ADVANCE INFORMATION

18

Micronas

2.9. Macrovision Detection

Video signals from Macrovision encoded VCR tapes

are decoded without loss of picture quality. However, it

might be necessary in some applications to detect the

presence of Macrovision encoded video signals. This

is possible by reading the Macrovision status register

(FP-RAM 0x170).

Macrovision encoded video signals typically have AGC

pulses and pseudo sync pulses added during VBI. The

amplitude of the AGC pulses is modulated in time. The

Macrovision detection logic measures the VBI lines

and compares the signal against thresholds.

The window wherein the video lines are checked for

Macrovision pulses can be defined in terms of start

and stop line (e.g. 6-15 for NTSC).

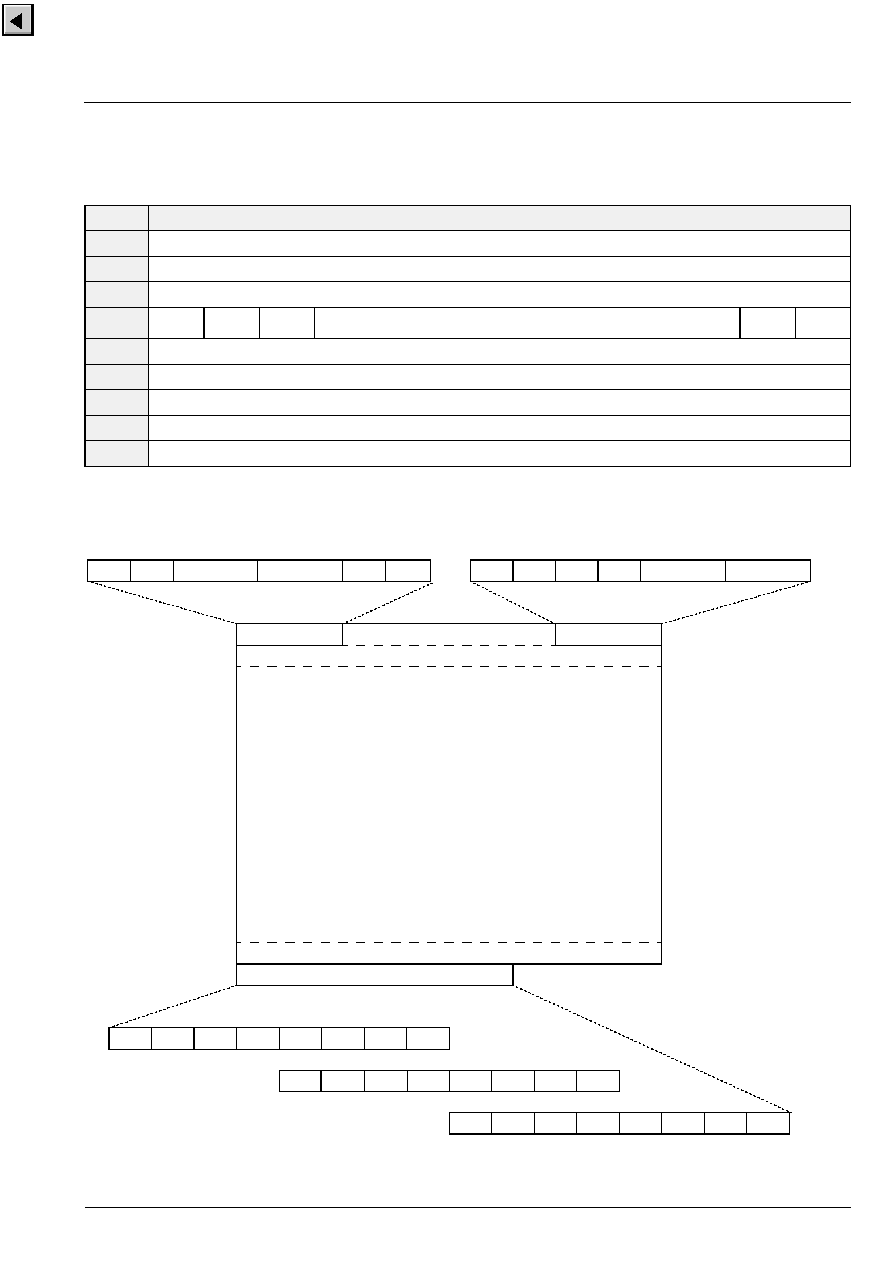

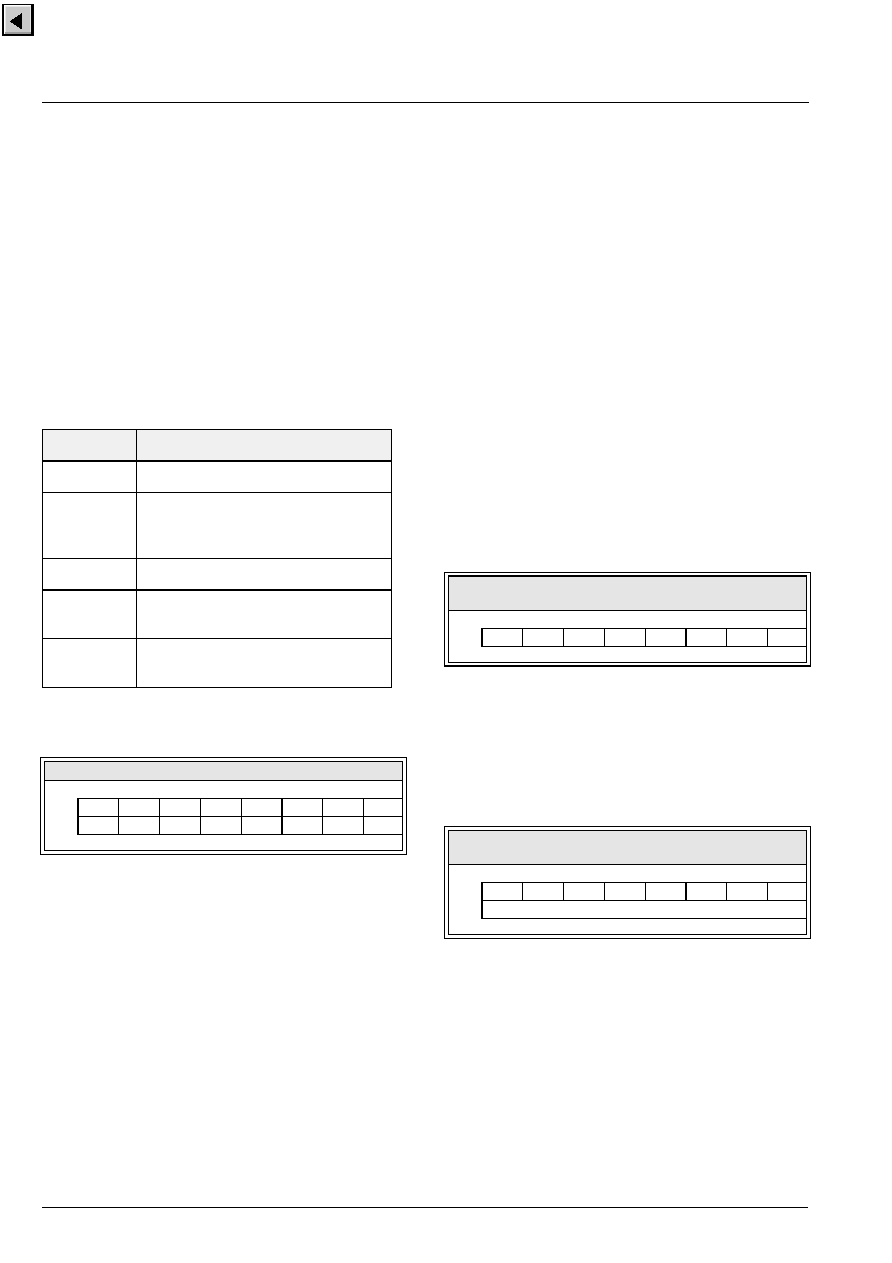

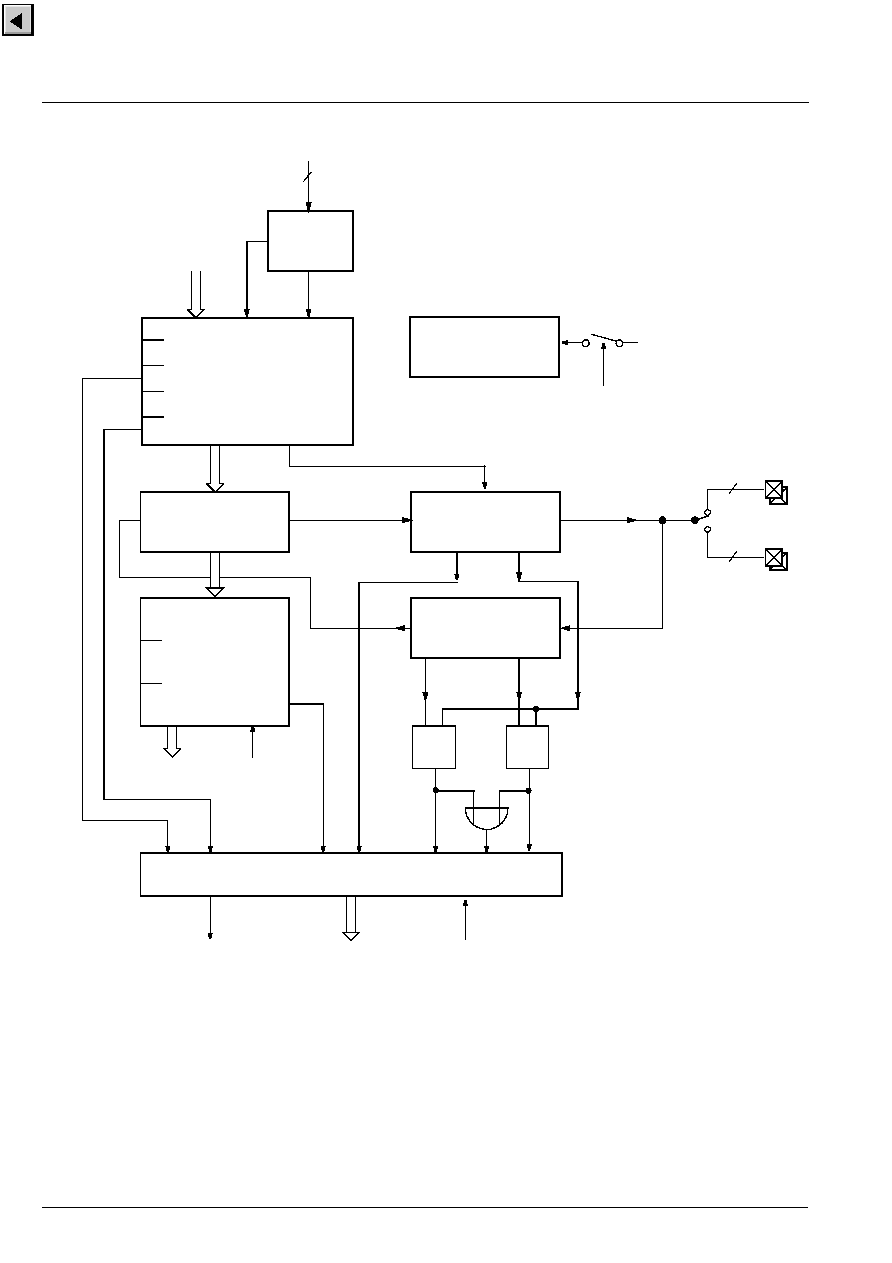

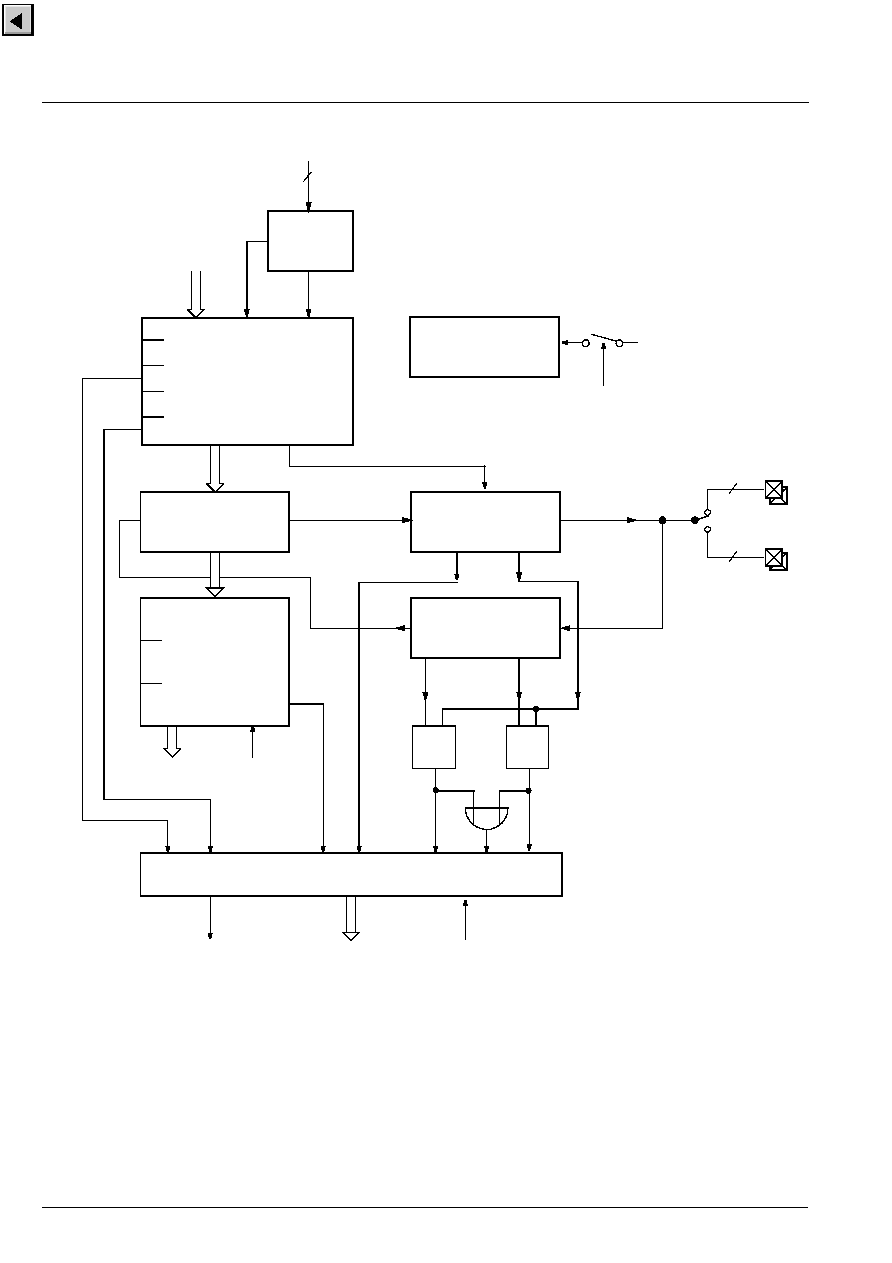

2.10.Display Processing

In the display processing the conversion from digital

YC

r

C

b

to analog RGB is carried out. A block diagram is

shown in Fig. 2�18 on page 24. In the luminance pro-

cessing path, contrast and brightness adjustments and

a variety of features, such as black-level expansion,

dynamic peaking and soft limiting, are provided. In the

chrominance path, the C

r

C

b

signals are converted to

4:4:4 format and filtered by a color transient improve-

ment circuit. The YC

r

C

b

signals are converted by a

programmable matrix to RGB color space.

The display processor provides separate control set-

tings for two pictures, i.e. different coefficients for a

`main' and a `side' picture.

The digital OSD insertion circuit allows the insertion of

a 5-bit OSD signal. The color space for this signal is

controlled by a partially programmable color look-up

table (CLUT) and contrast adjustment.

The OSD signals and the display clock are synchro-

nized to the horizontal flyback. For the display clock, a

gate delay phase shifter is used. In the analog back-

end, three 10-bit digital-to-analog converters provide

the analog output signals.

2.10.1.Luma Contrast Adjustment

The contrast of the luminance signal can be adjusted

by multiplication with a 6-bit contrast value. The con-

trast value corresponds to a gain factor from 0 to 2,

where the value 32 is equivalent to a gain of 1. The

contrast can be adjusted separately for main picture

and side picture.

2.10.2.Black-Level Expander

The black-level expander enhances the contrast of the

picture. Therefore the luminance signal is modified

with an adjustable, non-linear function. Dark areas of

the picture are changed to black, while bright areas

remain unchanged. The advantage of this black-level

expander is that the black expansion is performed only

if it will be most noticeable to the viewer.

The black-level expander works adaptively. Depending

on the measured amplitudes `L

min

' and `L

max

' of the

low-pass-filtered luminance and an adjustable coeffi-

cient BTLT, a tilt point `L

t

' is established by

L

t

= L

min

+ BTLT (L

max

- L

min

).

Above this value there is no expansion, while all lumi-

nance values below this point are expanded according

to:

L

out

= L

in

+ BAM

(L

in

- L

t

)

A second threshold, L

tr

, can be programmed, above

which there is no expansion. The characteristics of the

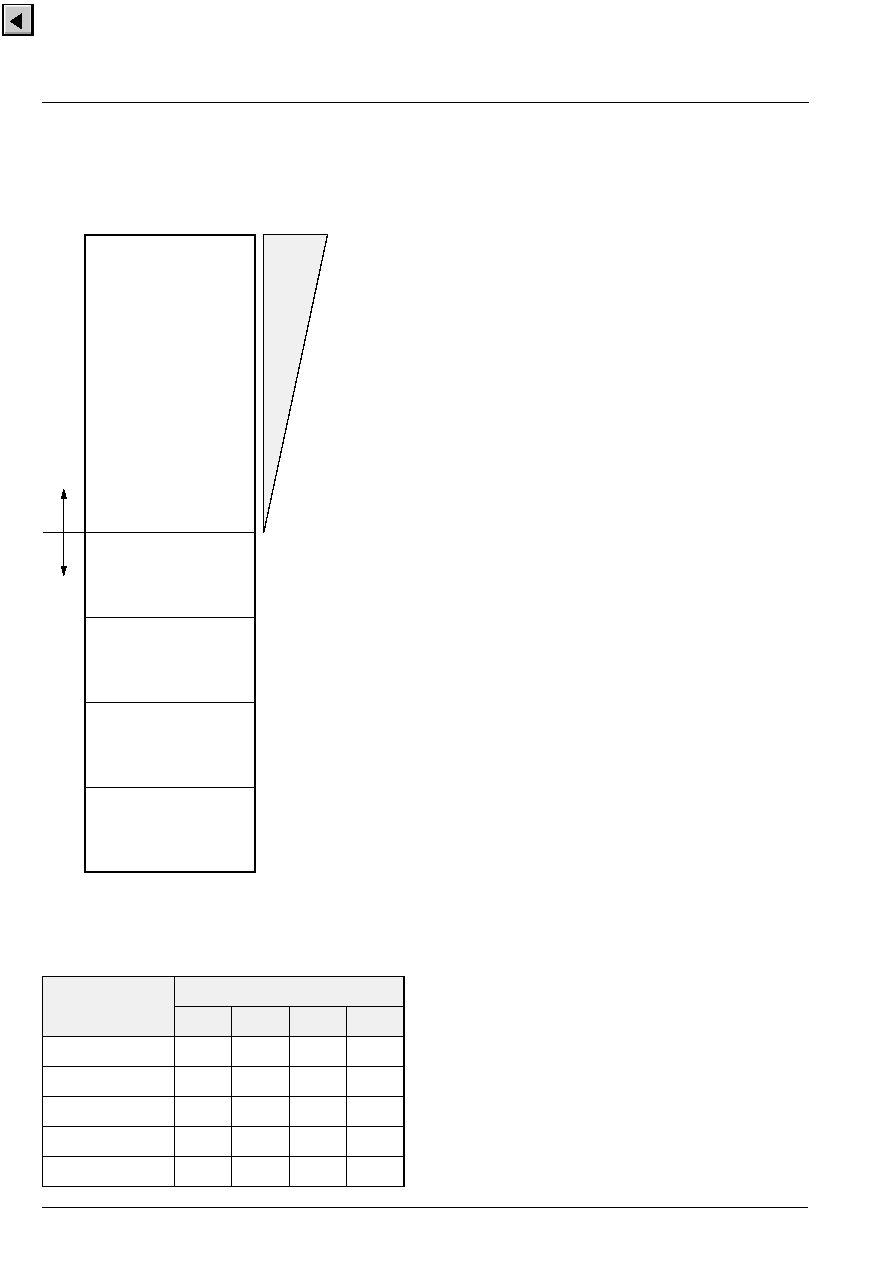

black-level expander are shown in Fig. 2�11and Fig.

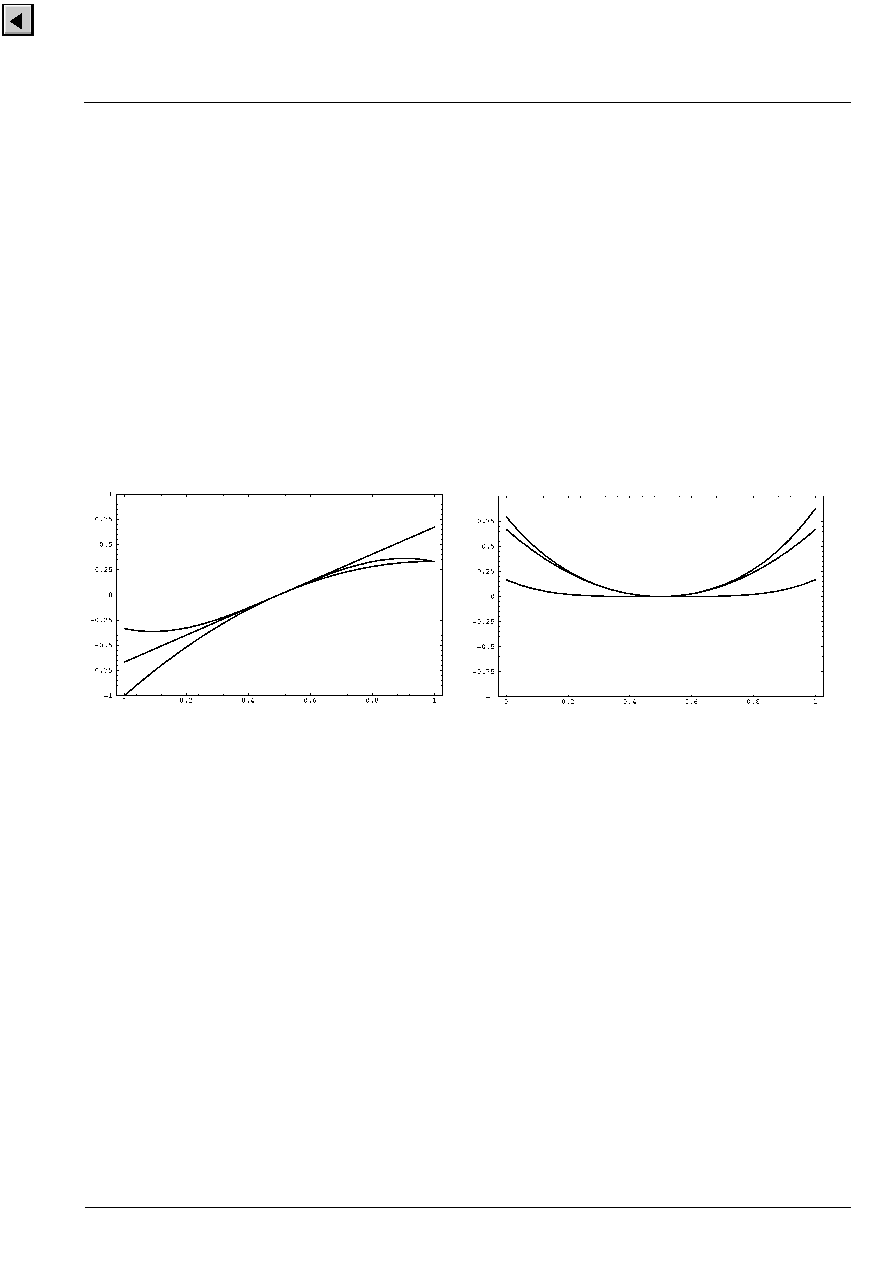

2�12.

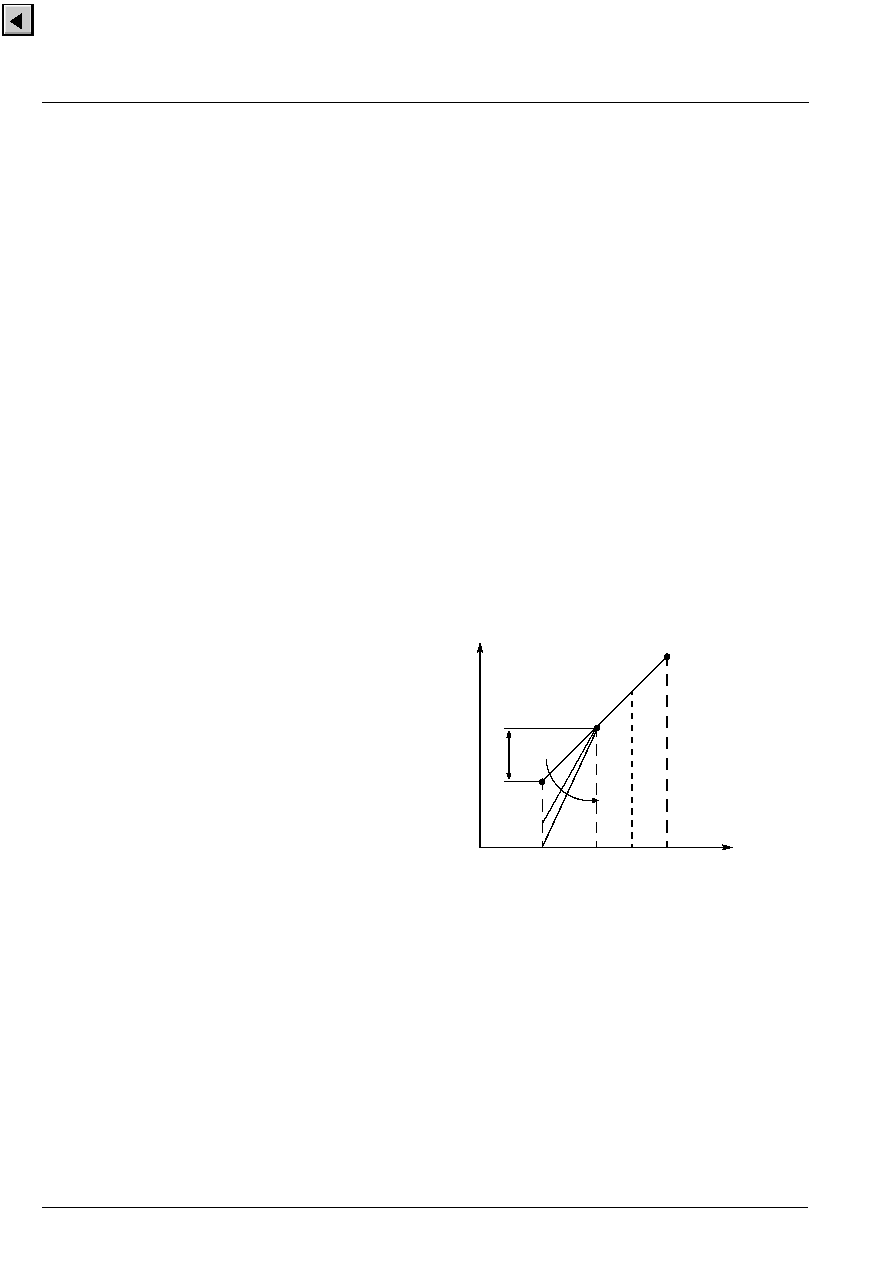

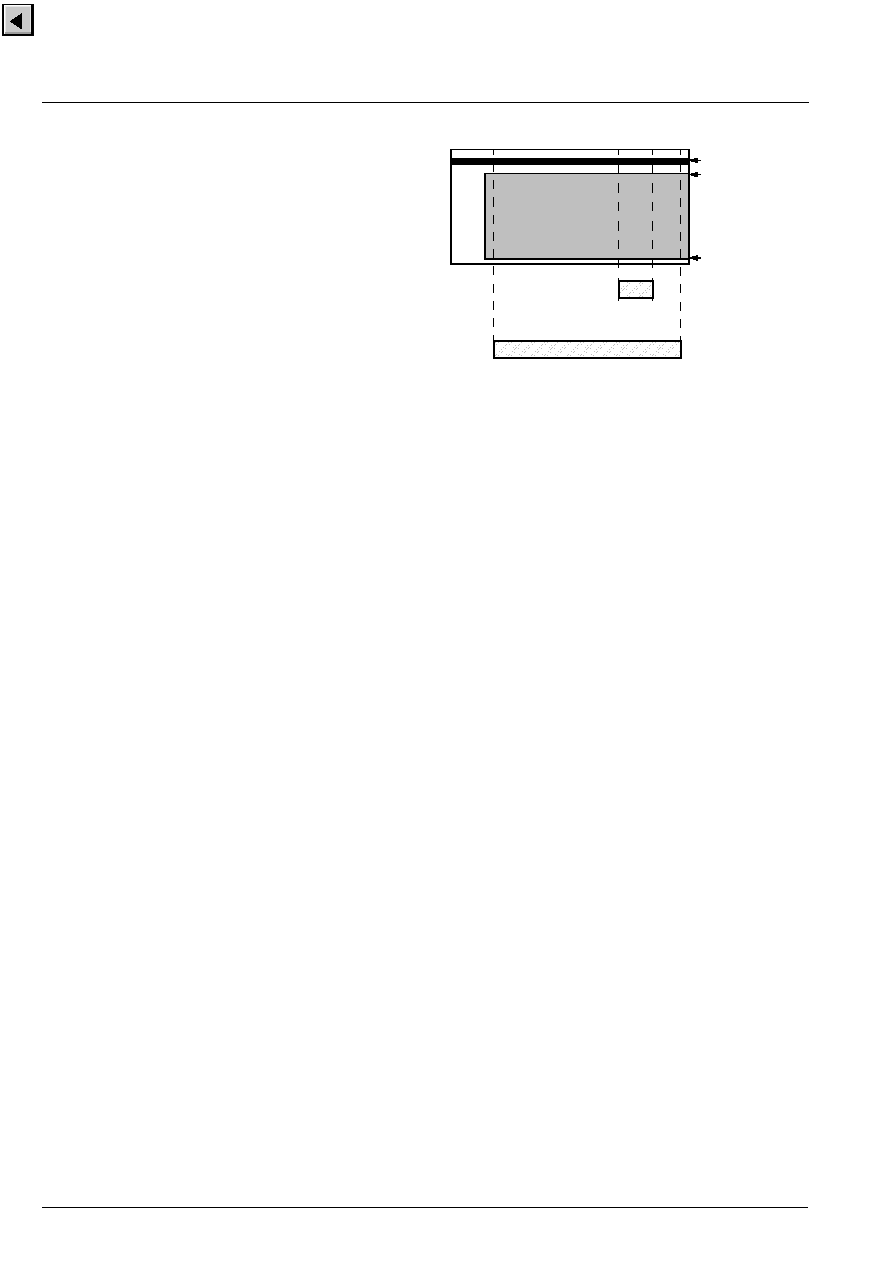

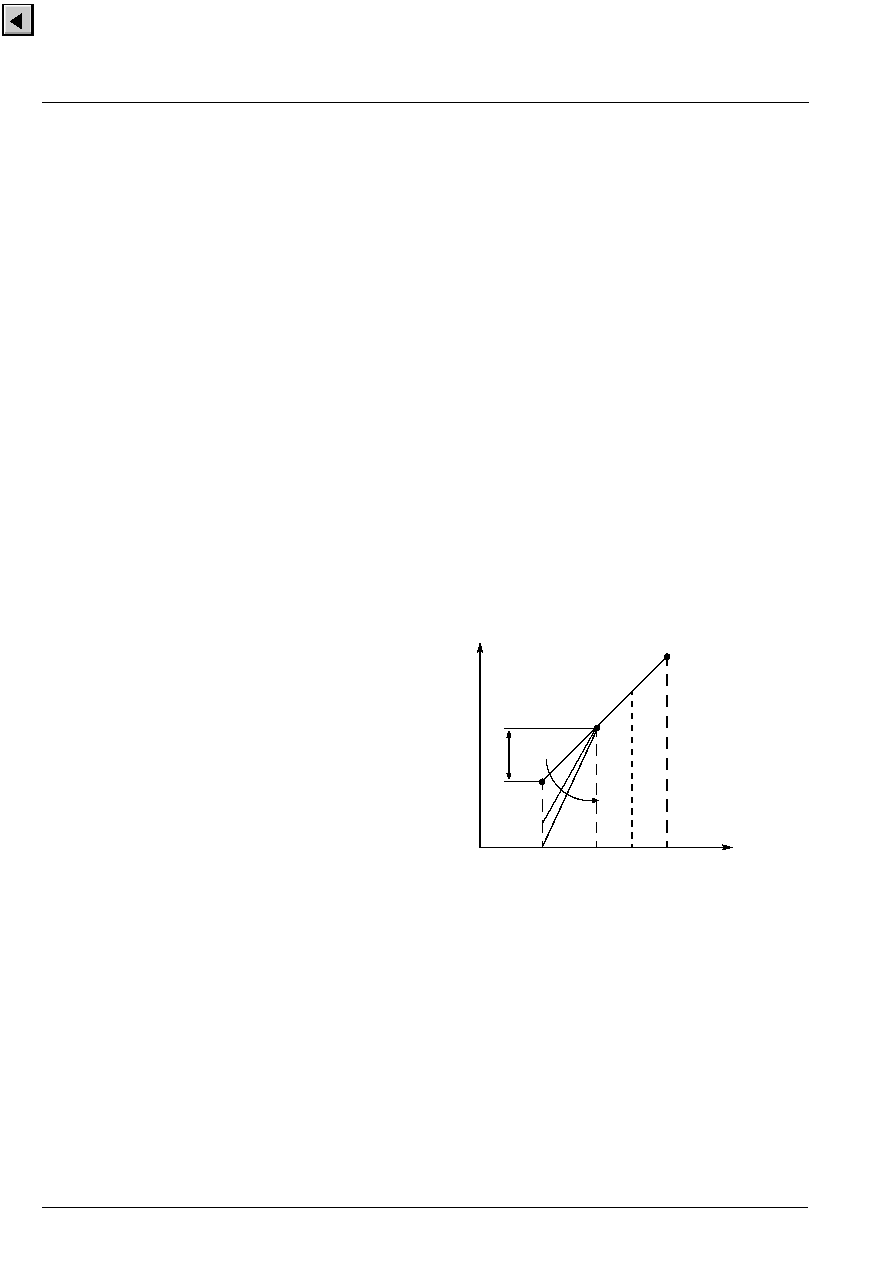

Fig. 2�11: Characteristics of the black-level expander

The tilt point L

t

is a function of the dynamic range of

the video signal. Thus, the black-level expansion is

only performed when the video signal has a large

dynamic range. Otherwise, the expansion to black is

zero. This allows the correction of the characteristics of

the picture tube.

L

min

BTLT

BAM

L

t

L

tr

L

max

L

tr

BTHR

L

in

L

out

ADVANCE INFORMATION

VCT 38xxA

Micronas

19

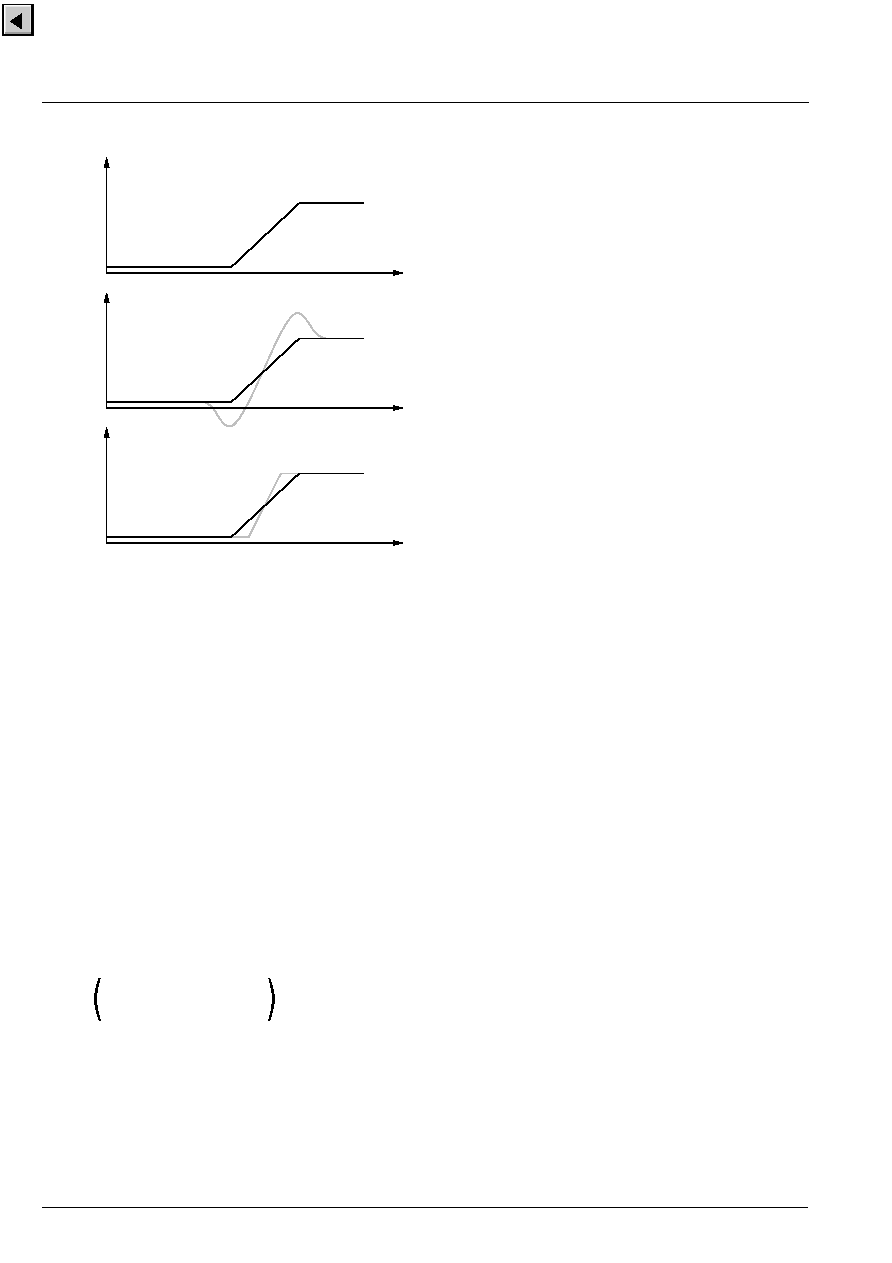

Fig. 2�12: Black-level expansion

a) luminance input

b) luminance input and output

2.10.3.Dynamic Peaking

Especially with decoded composite signals and notch

filter luminance separation, as input signals, it is nec-

essary to improve the luminance frequency character-

istics. With transparent, high-bandwidth signals, it is

sometimes desirable to soften the image.

In the VCT 38xxA, the luma response is improved by

`dynamic' peaking. The algorithm has been optimized

regarding step and frequency response. It adapts to

the amplitude of the high-frequency part. Small AC

amplitudes are processed, while large AC amplitudes

stay nearly unmodified.

The dynamic range can be adjusted from

-

14 to

+

14 dB for small high-frequency signals. There is sep-

arate adjustment for signal overshoot and for signal

undershoot. For large signals, the dynamic range is

limited by a non-linear function that does not create

any visible alias components. The peaking can be

switched over to "softening" by inverting the peaking

term by software.

The center frequency of the peaking filter is switchable

from 2.5 MHz to 3.2 MHz. For S-VHS and for notch filter

color decoding, the total system frequency responses

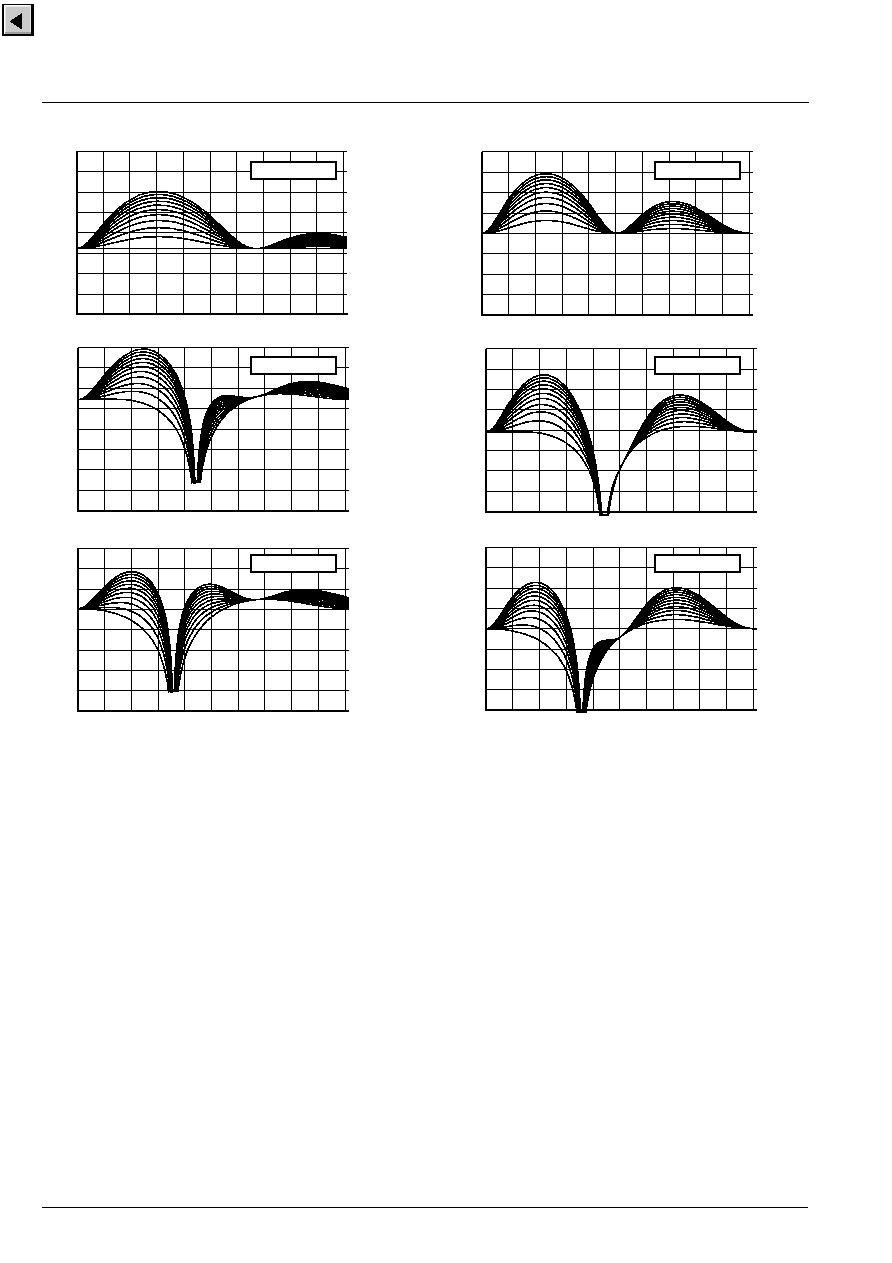

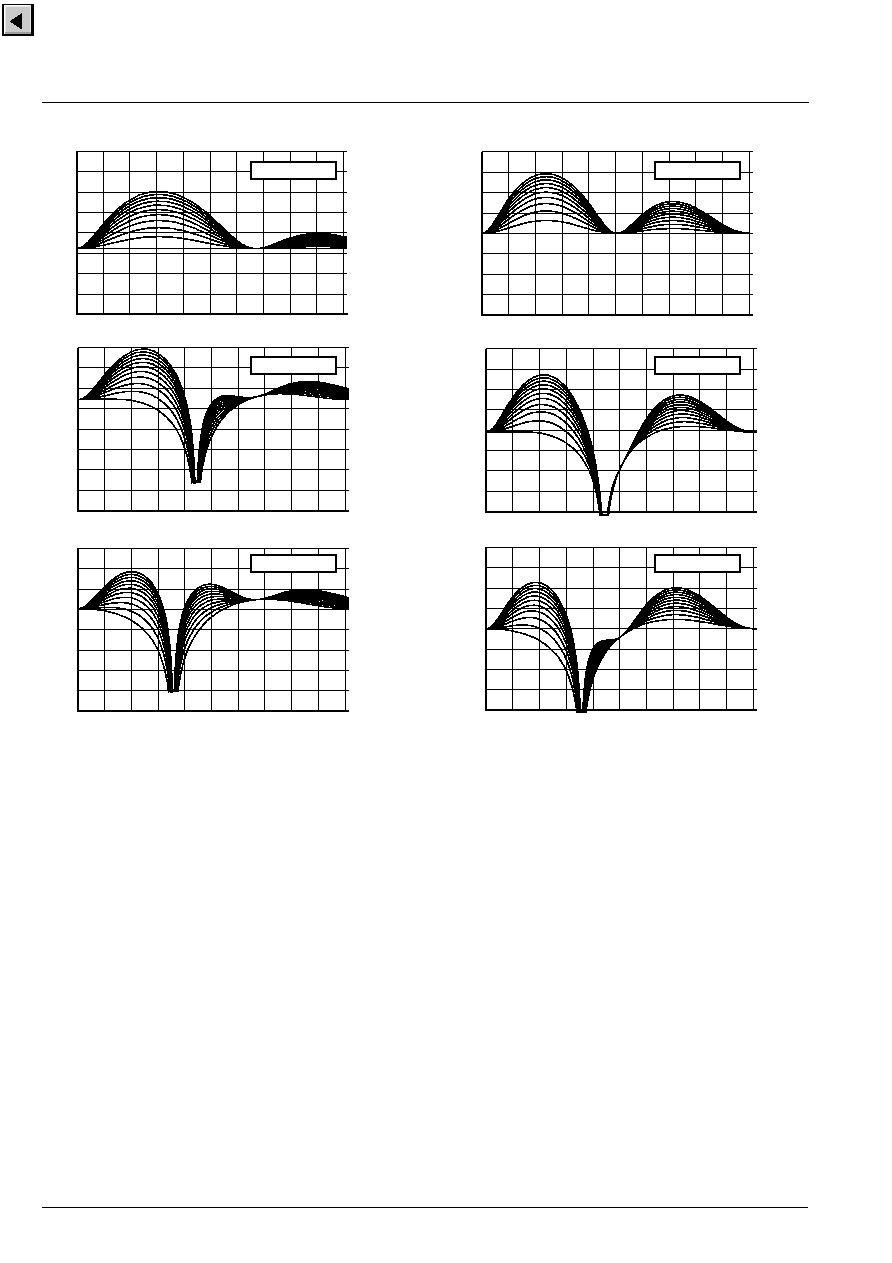

for both PAL and NTSC are shown in Fig. 2�14.

Transients, produced by the dynamic peaking when

switching video source signals, can be suppressed via

the priority bus.

Fig. 2�13: Dynamic peaking frequency response

a)

b)

L

min

L

t

L

max

L

t

dB

MHz

20

5

�5

�10

�15

�20

0

2

4

6

8

10

15

10

0

VCT 38xxA

ADVANCE INFORMATION

20

Micronas

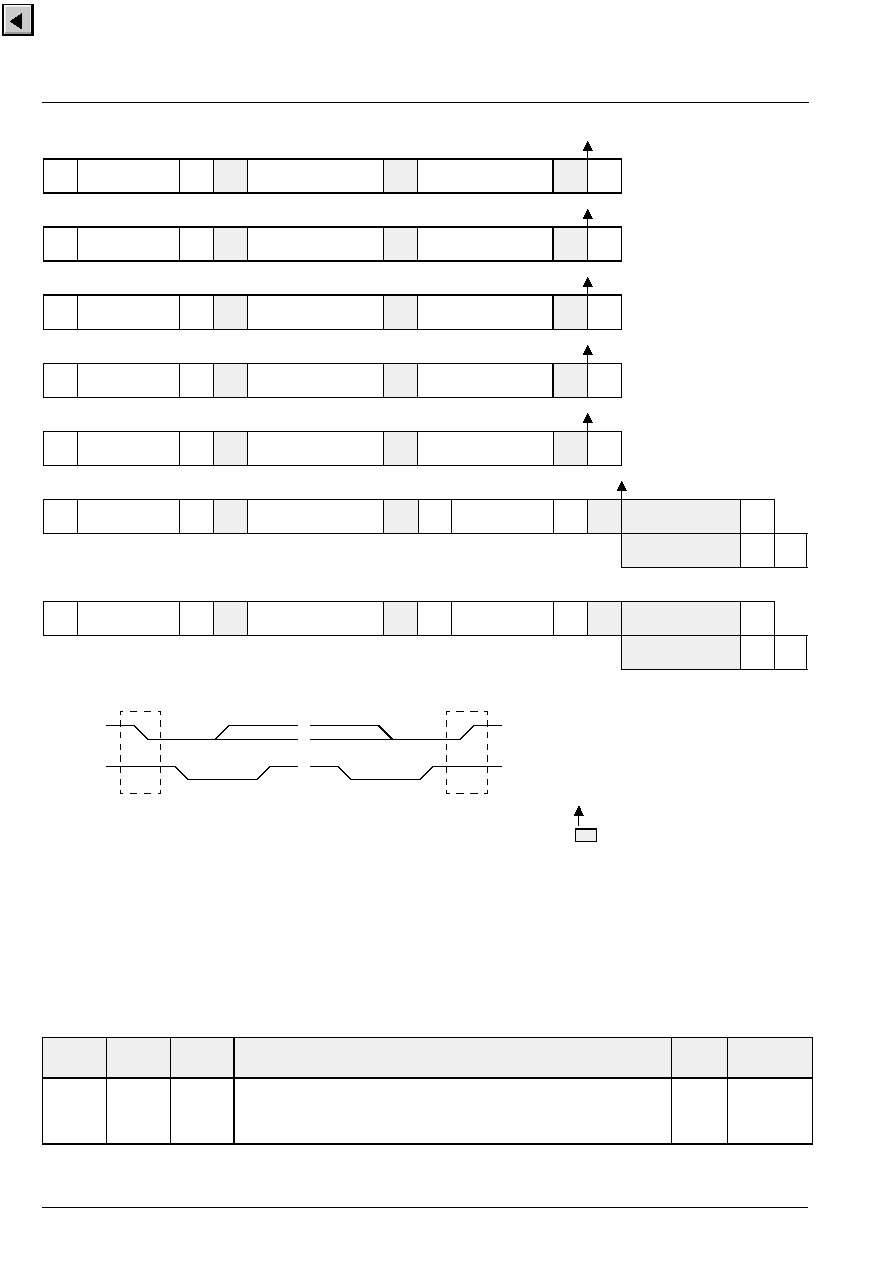

Fig. 2�14: Total frequency response for peaking filter and S-VHS, PAL, NTSC

dB

MHz

20

5

-5

-10

-15

-20

0

2

4

6

8

10

15

10

0

dB

MHz

20

5

-5

-10

-15

-20

0

2

4

6

8

10

15

10

0

dB

MHz

20

5

-5

-10

-15

-20

0

2

4

6

8

10

15

10

0

dB

MHz

20

5

-5

-10

-15

-20

0

2

4

6

8

10

15

10

0

dB

MHz

20

5

-5

-10

-15

-20

0

2

4

6

8

10

15

10

0

dB

MHz

20

5

-5

-10

-15

-20

0

2

4

6

8

10

15

10

0

CF=2.5 MHz

CF=2.5 MHz

CF=2.5 MHz

CF=3.2 MHz

CF=3.2 MHz

CF=3.2 MHz

NTSC

PAL/SECAM

S-VHS

ADVANCE INFORMATION

VCT 38xxA

Micronas

21

2.10.4.Digital Brightness Adjustment

The DC-level of the luminance signal can be adjusted

by adding an 8-bit number in the luminance signal path

in front of the softlimiter.

With a contrast adjustment of 32 (gain

+

1) the signal

can be shifted by 100 %. After the brightness addition,

the negative going signals are limited to zero. It is

desirable to keep a small positive offset with the signal

to prevent undershoots produced by the peaking from

being cut. The digital brightness adjustment works

separately for main and side picture.

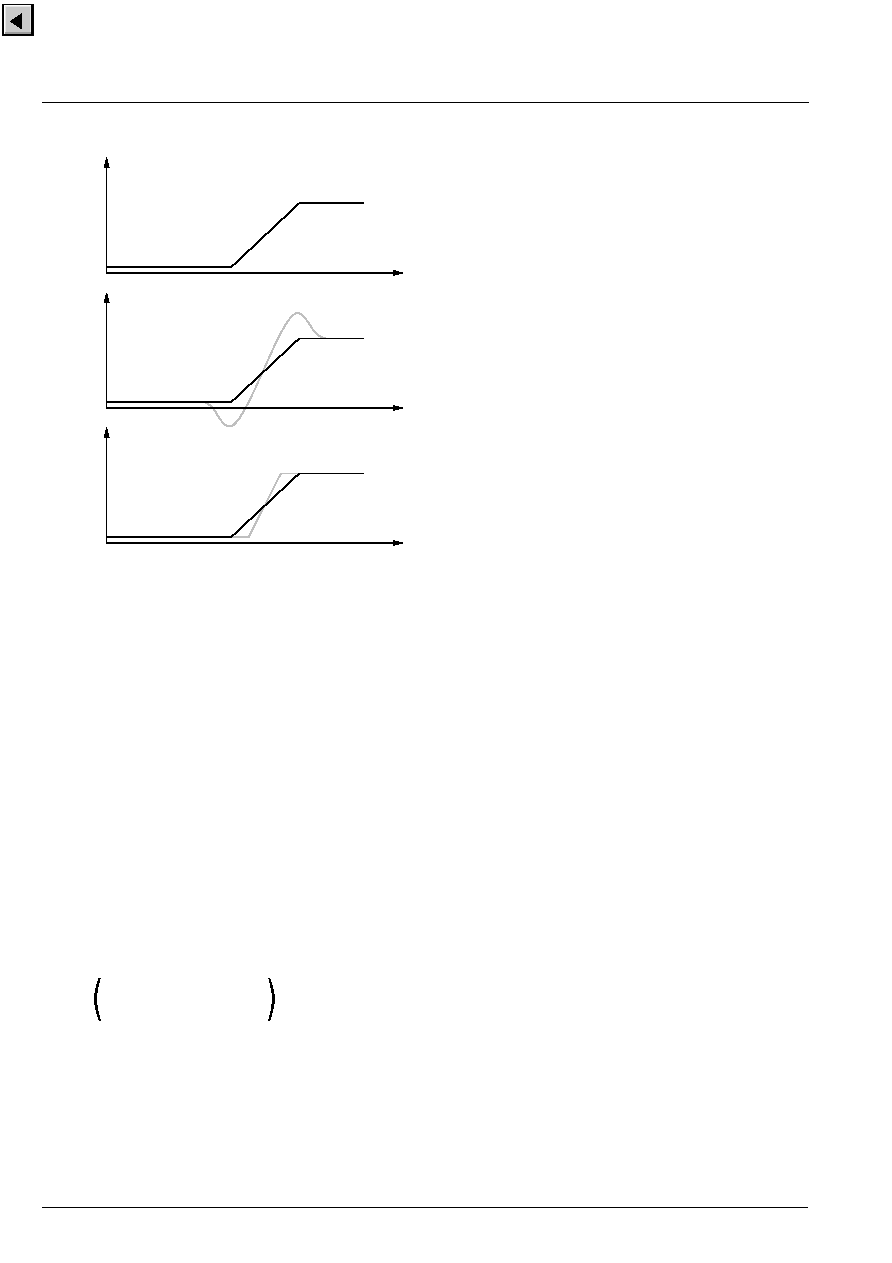

2.10.5.Soft Limiter

The dynamic range of the processed luma signal must

be limited to prevent the CRT from overload. An appro-

priate headroom for contrast, peaking and brightness

can be adjusted by the TV manufacturer according to

the CRT characteristics. All signals above this limit will

be `soft'-clipped. A characteristic diagram of the soft

limiter is shown in Fig. 2�15. The total limiter consists

of three parts:

Part 1 includes adjustable tilt point and gain. The gain

before the tilt value is 1. Above the tilt value, a part

(0...15/16) of the input signal is subtracted from the

input signal itself. Therefore, the gain is adjustable

from 16/16 to 1/16, when the slope value varies from

0 to 15. The tilt value can be adjusted from 0 to 511.

Part 2 has the same characteristics as part 1. The sub-

tracting part is also relative to the input signal, so the

total differential gain will become negative if the sum of

slope 1 and slope 2 is greater than 16 and the input

signal is above the both tilt values (see characteris-

tics).

Finally, the output signal of the soft limiter will be

clipped by a hard limiter adjustable from 256 to 511.

2.10.6.Chroma Interpolation

A linear phase interpolator is used to convert the

chroma sampling rate from 10.125 MHz (4:2:2) to

20.25 MHz (4:4:4). All further processing is carried out

at the full sampling rate.

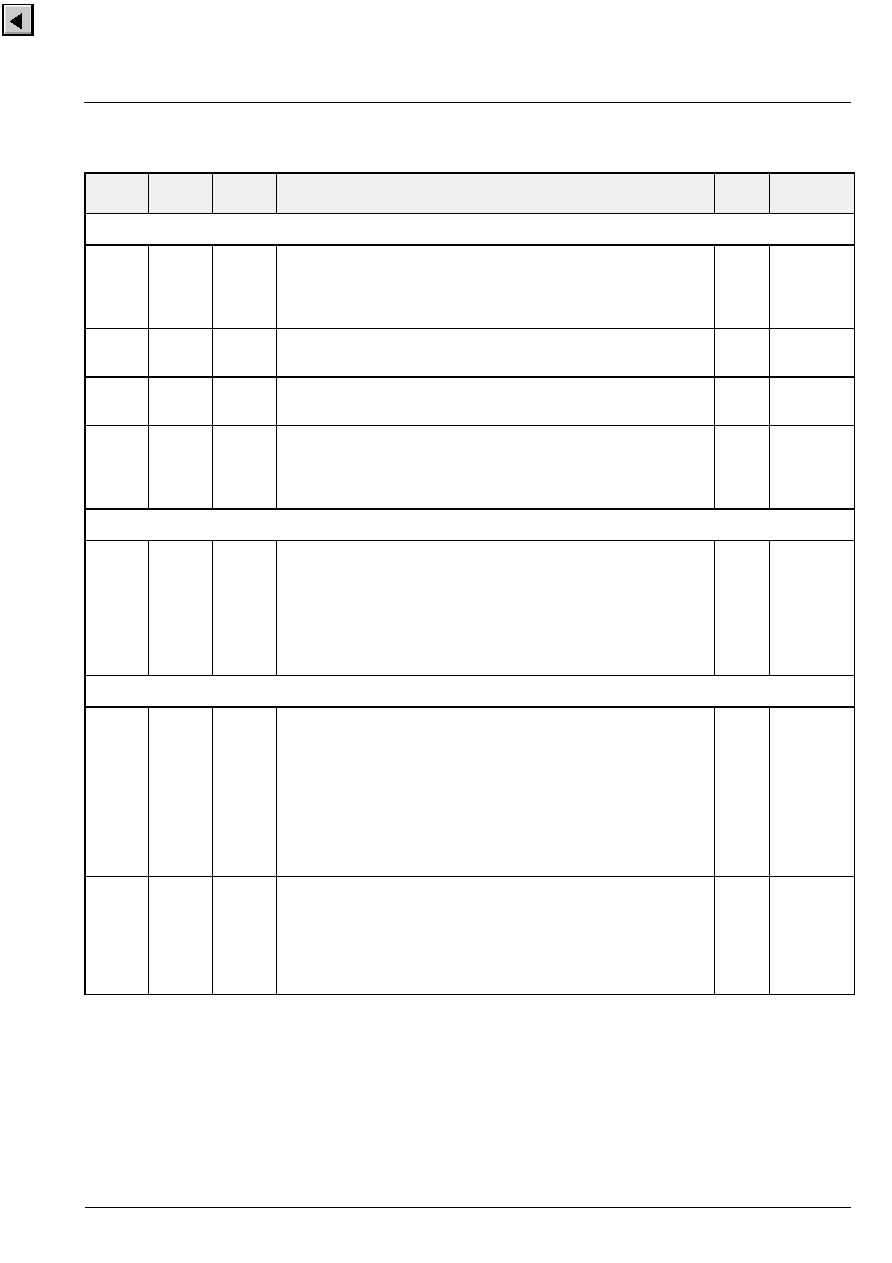

Fig. 2�15: Characteristic of soft limiter A and B and hard limiter

2.10.7.Chroma Transient Improvement

The intention of this block is to enhance the chroma

resolution. A correction signal is calculated by differen-

tiation of the color difference signals. The differentia-

tion can be selected according to the signal bandwidth,

e.g. for PAL/NTSC/SECAM or digital component sig-

nals, respectively. The amplitude of the correction sig-

nal is adjustable. Small noise amplitudes in the correc-

tion signal are suppressed by an adjustable coring

circuit. To eliminate `wrong colors', which are caused

by over and undershoots at the chroma transition, the

sharpened chroma signals are limited to a proper

value automatically.

0

100

200

300

400

500

600

700

800

900

1023

Calculation Example for the

Softlimiter Input Amplitude.

(The real signal processing in

the limiter is 2 bit more than

described here)

Y Input

16...235 (ITUR)

Black Level

16 (constant)

Contrast 63

Dig. Brightness

20

BLE

off

Peaking off

Limiter input signal:

(Yin-Black Level)

Contr./32 + Brightn.

(235-16)

63/32 + 20 = 451

0

2

4

6

8

10

12

14

slope 2

[0...15]

0

2

4

6

8

10

12

14

Hard limiter

range=

256...511

slope 1

[0...15]

tilt 1 [ 0...511]

tilt 2 [ 0...511]

100

200

300

400

511

Output

0

Part 1

Part 2

Limiter Input

VCT 38xxA

ADVANCE INFORMATION

22

Micronas

Fig. 2�16: Digital color transient improvement

2.10.8.Inverse Matrix

A 6-multiplier matrix transcodes the C

r

and C

b

signals

to R-Y, B-Y, and G-Y. The multipliers are also used to

adjust color saturation in the range of 0 to 2. The coef-

ficients are signed and have a resolution of 9 bits.

There are separate matrix coefficients for main and

side pictures. The matrix computes:

R

-

Y

=

MR1*C

b

+

MR2*C

r

G

-

Y

=

MG1*C

b

+

MR2*C

r

B

-

Y

=

MB1*C

b

+

MR2*C

r

The initialization values for the matrix are computed

from the standard ITUR (CCIR) matrix:

For a contrast setting of CTM

+

32, the matrix values

are scaled by a factor of 64 (see Table 2�4 on

page 34).

2.10.9.RGB Processing

After adding the post-processed luma, the digital RGB

signals are limited to 10 bits. Three multipliers are

used to digitally adjust the white drive. Using the same

multipliers an average beam current limiter is imple-

mented (see Section 2.11.1. on page 25).

2.10.10.OSD Color Look-up Table

The VCT 38xxA has five input lines for an OSD signal.

This signal forms a 5-bit address for a color look-up

table (CLUT). The CLUT is a memory with 32 words

where each word holds a RGB value.

Bits 0 to 3 (bit 4

=

0) form the addresses for the ROM

part of the OSD, which generates full RGB signals (bit

0 to 2) and half-contrast RGB signals (bit 3).

Bit 4 addresses the RAM part of the OSD with 16

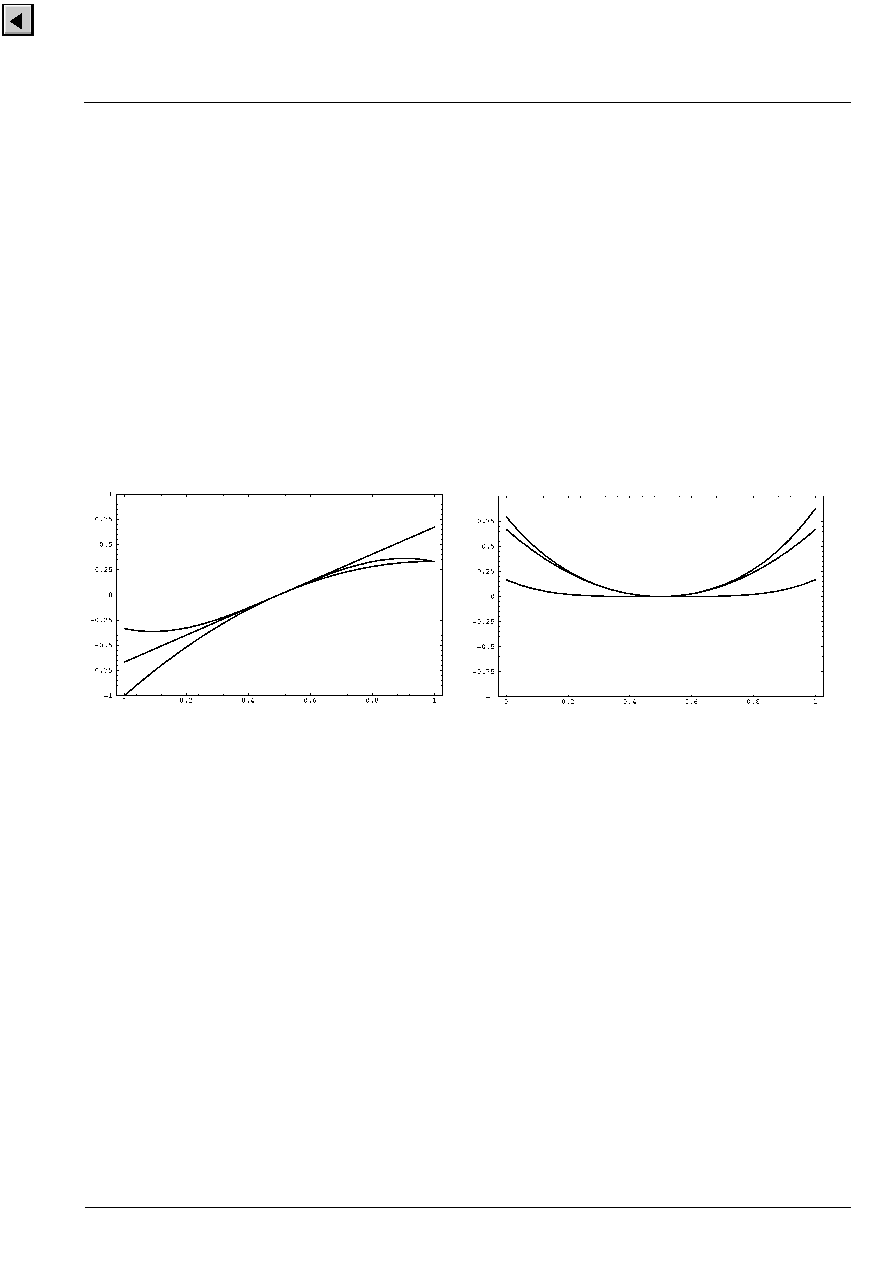

freely programmable colors, addressable with bit 0 to

3. The programming is done via the I

2

C bus.

The amplitude of the CLUT output signals can be

adjusted separately for R, G, and B via the I

2

C bus.

The switchover between video RGB and OSD RGB is

done via the priority decoder.

2.10.11.Picture Frame Generator

When the picture does not fill the total screen (height

or width too small) it is surrounded with black areas.

These areas (and more) can be colored with the pic-

ture frame generator. This is done by switching over

the RGB signal from the matrix to the signal from the

OSD color look-up table.

The width of each area (left, right, upper, lower) can be

adjusted separately. The generator starts on the right,

respectively lower side of the screen and stops on the

left, respectively upper side of the screen. This means,

it runs during horizontal, respectively vertical flyback.

The color of the complete border can be stored in the

programmable OSD color look-up table in a separate

address. The format is 3 x 4-bit RGB. The contrast can

be adjusted separately.

The picture frame generator includes a priority master

circuit. Its priority is programmable and the border is

generated only if the priority is higher than the priority

of the other sources (video/OSD). Therefore, the bor-

der can be underlay or overlay depending on the pic-

ture source.

a) C

r

C

b

input of DTI

b) C

r

C

b

input

+

correction signal

c) sharpened and limited C

r

C

b

t

t

t

C

r

in

C

b

in

a)

b)

Ampl.

C

r

out

C

b

out

c)

R

G

B

=

1

1

1

0

-

0.345

1.773

1.402

-

0.713

0

Y

C

b

C

r

ADVANCE INFORMATION

VCT 38xxA

Micronas

23

2.10.12.Priority Decoder

The priority decoder selects the picture source

depending on the programmed priorities. Up to eight

levels can be selected for OSD and the picture frame �

where 0 is the highest. The video source always has

the lowest priority. A 5-bit information is attached to

each priority (see Table 2�4 on page 34). These bits

are programmable via the I

2

C bus and have the follow-

ing meanings:

� one of two contrast, brightness and matrix values for

main and side picture

� RGB from video signal or color look-up table

� disable/enable black-level expander

� disable/enable peaking transient suppression when

signal is switched

� disable/enable analog Fast-Blank input

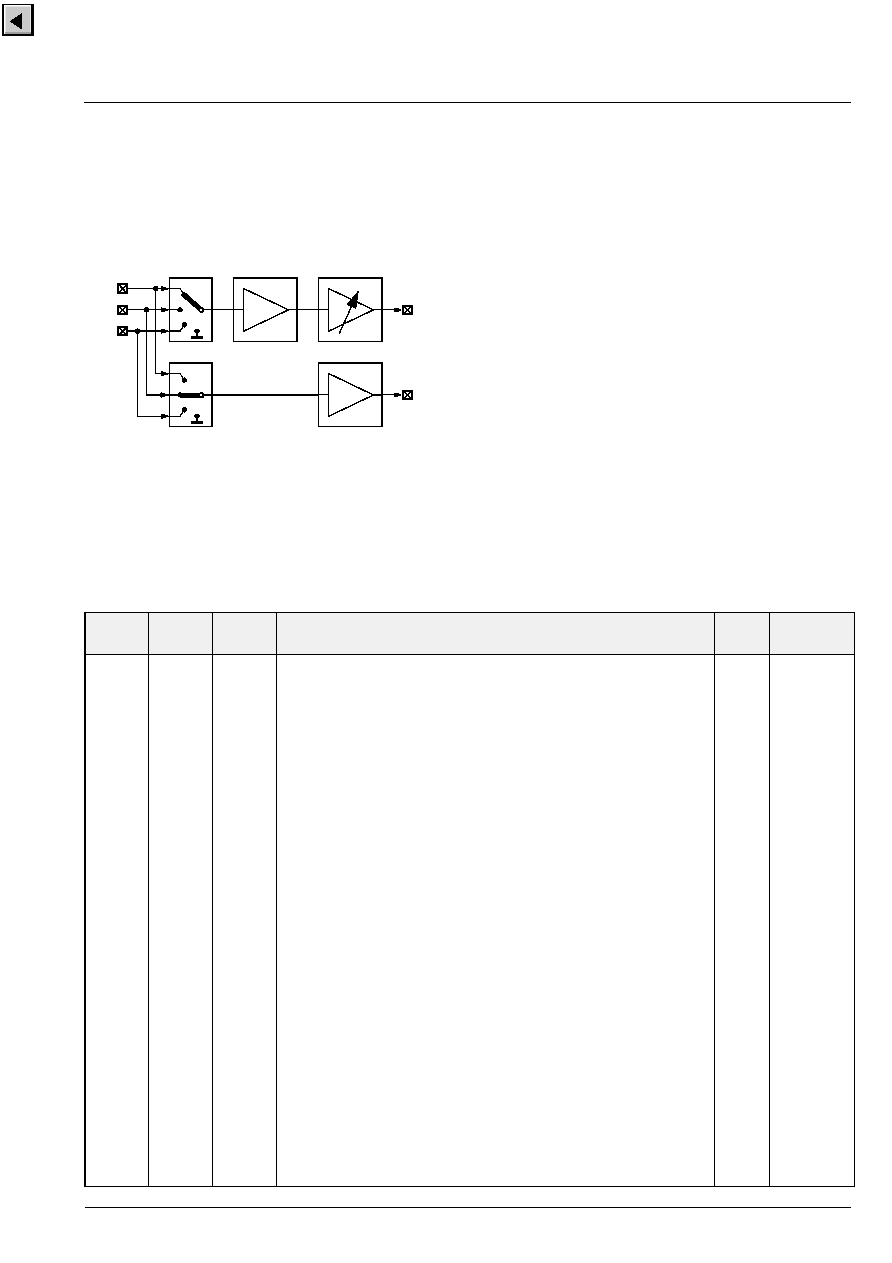

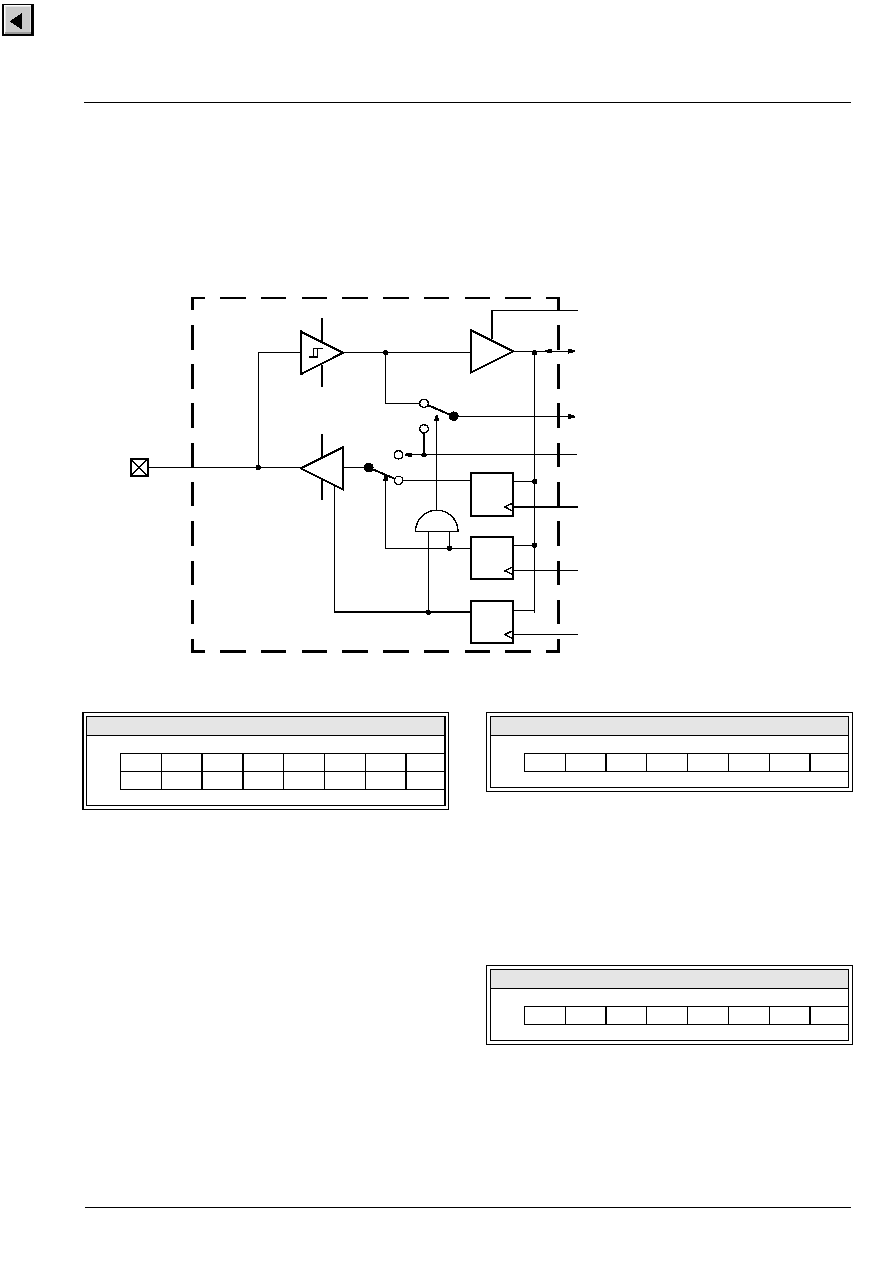

2.10.13.Scan Velocity Modulation

The RGB input signal of the SVM is converted to Y in a

simple matrix. Then the Y signal is differentiated by a

filter of the transfer function 1-Z

-N

, where N is program-

mable from 1 to 6. With a coring, some noise can be

suppressed. This is followed by a gain adjustment and

an adjustable limiter. The analog output signal is gen-

erated by an 8-bit D/A converter.

The signal delay can be adjusted by

�

3.5 clocks in

half-clock steps. For the gain and filter adjustment

there are two parameter sets. The switching between

these two sets is done with the same RGB switch sig-

nal that is used for switching between video-RGB and

OSD-RGB for the RGB outputs (see Fig. 2�17).

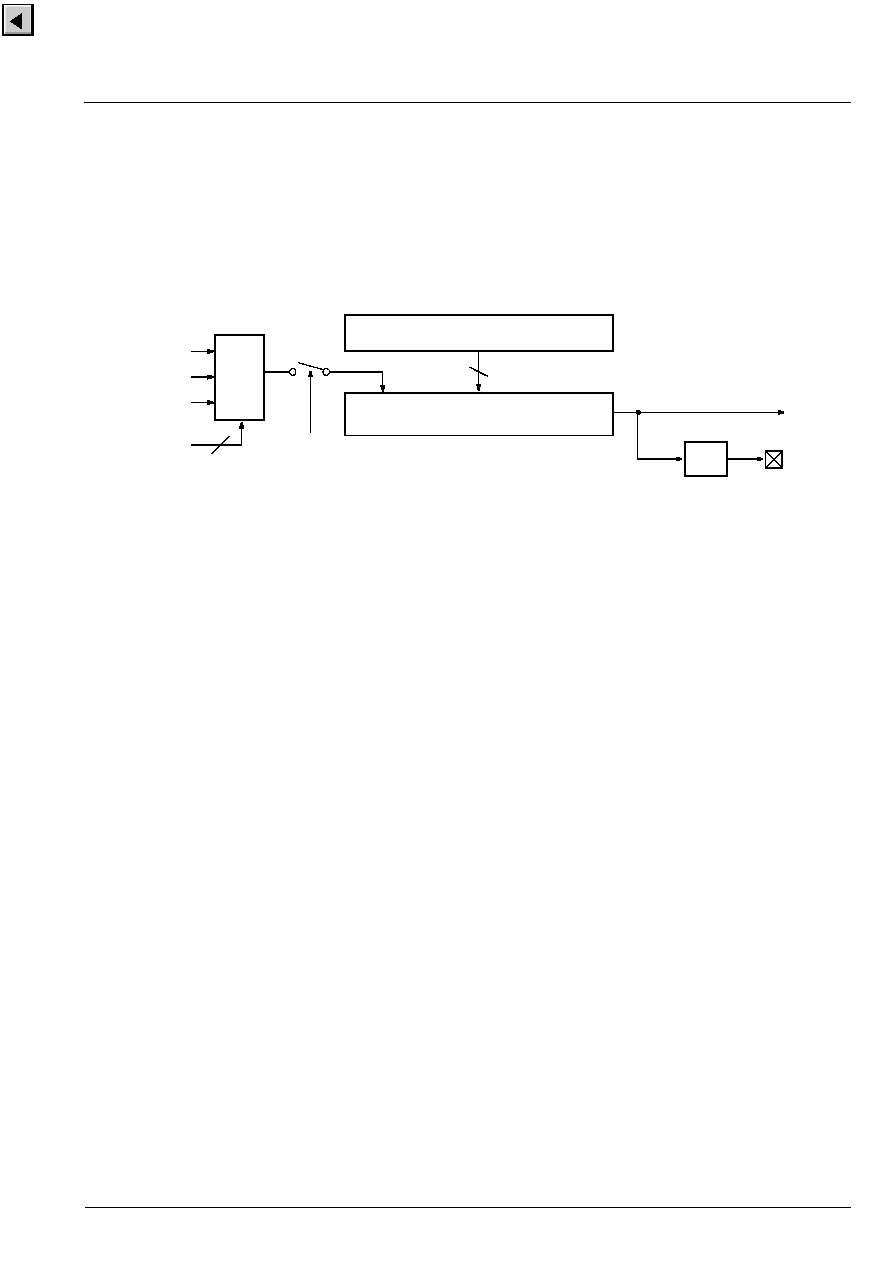

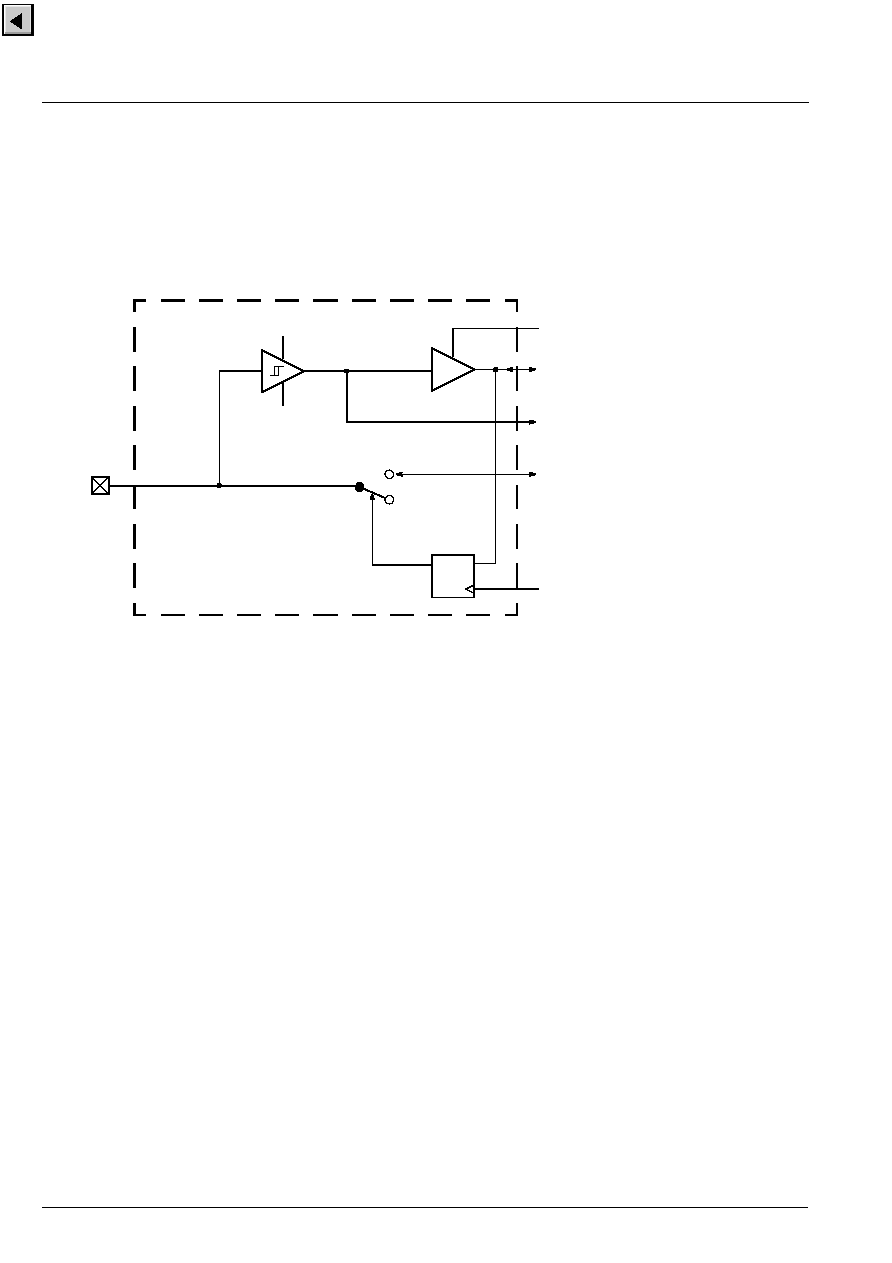

Fig. 2�17: SVM Block diagram

2.10.14.Display Phase Shifter

A phase shifter is used to partially compensate the

phase differences between the video source and the

flyback signal. By using the described clock system,

this phase shifter works with an accuracy of approxi-

mately 1 ns. It has a range of 1 clock period which is

equivalent to

�

24.7 ns at 20.25 MHz. The large

amount of phase shift (full clock periods) is realized in

the front-end circuit.

N1

N2

Coring

Gain1

Gain2

Limiter

Limit

Delay

RGB Switch

R

G

B

Matrix and

Shaping

Modulation

Notch

Differen-

tiator

1-Z

-Nx

Coring

adjustment

Gain

adjustment

Delay

adjustment

D/A

Converter

Output

VCT

38xxA

A

D

V

A

NCE

INFORM

A

T

ION

24

M

i

c

r

onas

Fig. 2

�

18:

Di

gi

tal

ba

ck

-

end

Contrast

Dynamic

peaking

Brightness

+ Offset

Softlimiter

White-Drive

Measurement

C

LOCK

Horizontal

Flyback

DTI

(C

r

)

DTI

(C

b

)

Interpol

4:4:4

Black-

Level

Expander

10

dig.

Rout

dig.

Gout

dig.

Bout

Cr

Cb

dig.

Y in

dig.

C

r

C

b

in

8

8

Matrix

Saturation

White-Drive R

x beam Curr. Lim.

Display

& Clock

Control

PRIO in

PRIO

Decoder

select

Coefficients

Main Picture

Side Picture

3

Matrix

R'

Matrix

G'

Matrix

B'

Y

R

G

B

luma insert

for CRTmeasurement

CLUT,

for CRT Measurement

Blanking

dig. OSD in

5

Contrast

SVMout

10

10

Scan

Velocity

Modulation

Picture

Frame

Generator

prio

prio

White-Drive G

x Beam curr. Lim.

White-Drive

x Beam Curr. Lim.

Phase

Shift

0...1 Clock

Phase

Shift

0...1 Clock

Phase

Shift

0...1 Clock

ADVANCE INFORMATION

VCT 38xxA

Micronas

25

2.11.Video Back-end

The digital RGB signals are converted to analog RGBs

using three video digital-to-analog converters (DAC)

with 10-bit resolution. An analog brightness value is

provided by three additional DACs. The adjustment

range is 40 % of the full RGB range.

Controlling the white-drive/analog brightness and also

the external contrast and brightness adjustments is

done via the Fast Processor, located in the front-end.

Control of the cutoff DACs is done via I

2

C bus regis-

ters.

Finally cutoff and blanking values are added to the

RGB signals. Cutoff (dark current) is provided by three

9-bit DACs. The adjustment range is 60 % of full scale

RGB range.

The analog RGB-outputs are current outputs with cur-

rent-sink characteristics. The maximum current drawn

by the output stage is obtained with peak white RGB.

An external half contrast signal can be used to reduce

the output current of the RGB outputs to 50 %.

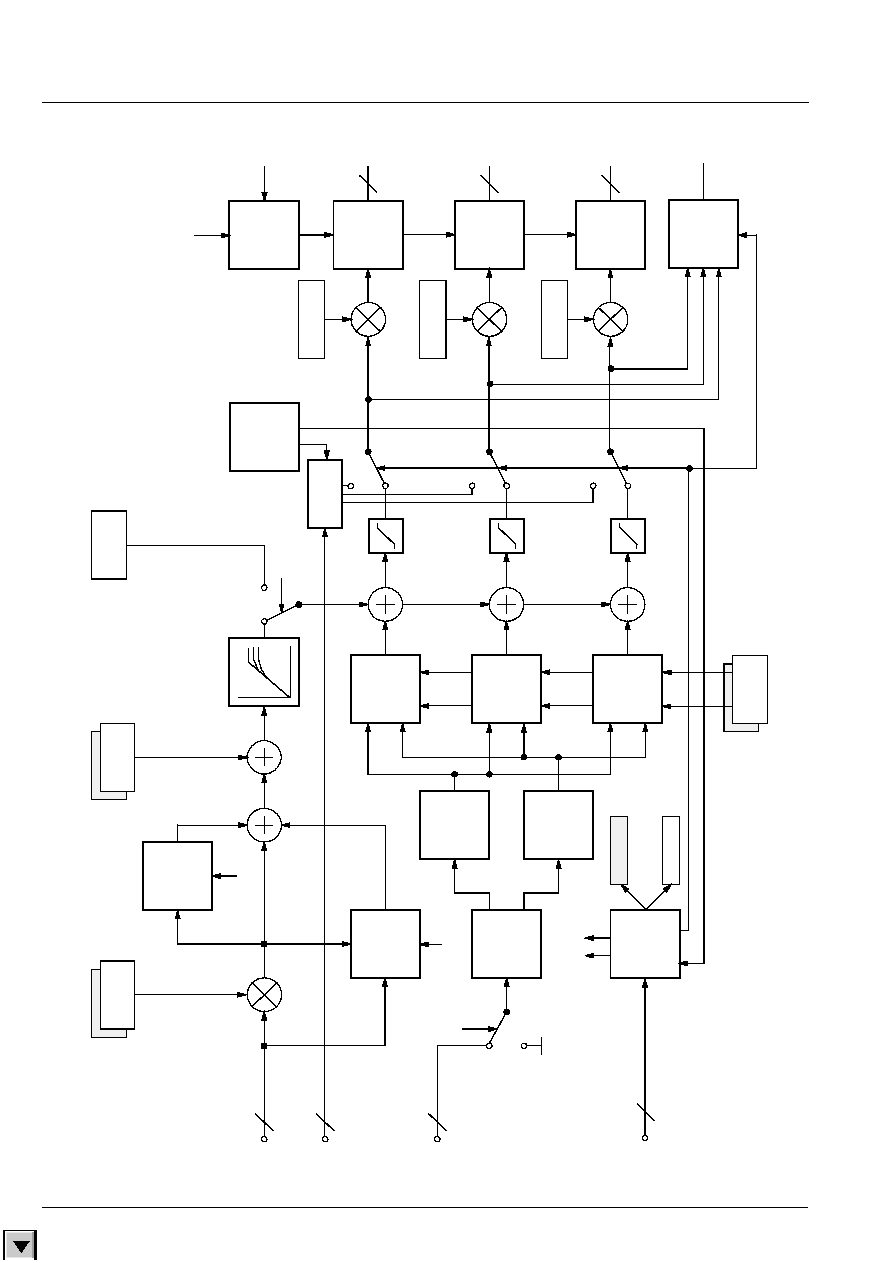

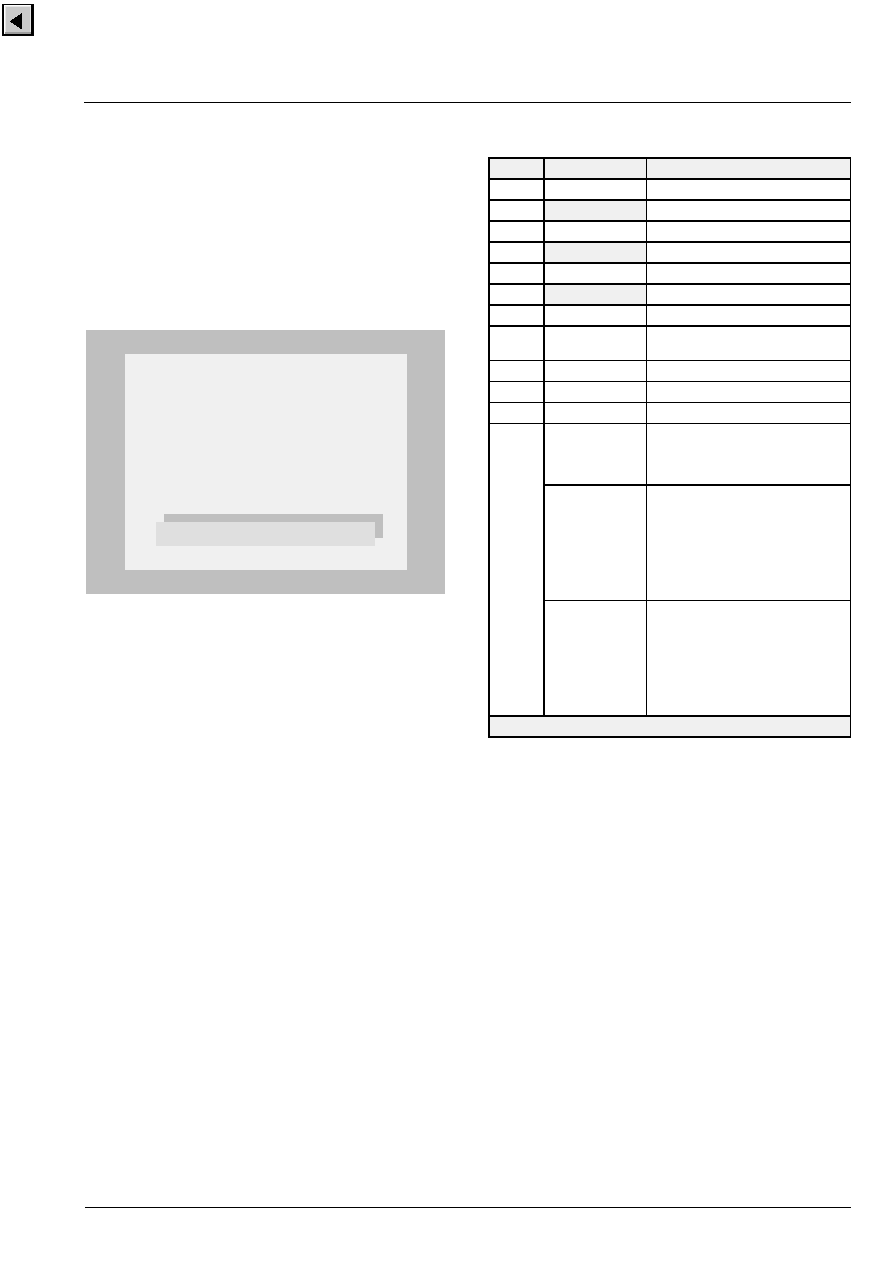

2.11.1.CRT Measurement and Control

The display processor is equipped with an 8-bit

PDM-ADC for all measuring purposes. The ADC is

connected to the SENSE input pin, the input range is 0

to 1.5V. The bandwidth of the PDM filter can be

selected; it is 40/80 kHz for small/large bandwidth set-

ting. The input impedance is more than 1 M

.

Cutoff and white-drive current measurement are car-

ried out during the vertical blanking interval. They

always use the small bandwidth setting. The current

range for the cutoff measurement is set by connecting

a sense resistor to the MADC input. For the white-drive

measurement, the range is set by using another sense

resistor and the range select switch 2 output pin

(RSW2). During the active picture, the minimum and

maximum beam current is measured. The measure-

ment range can be set by using the range select

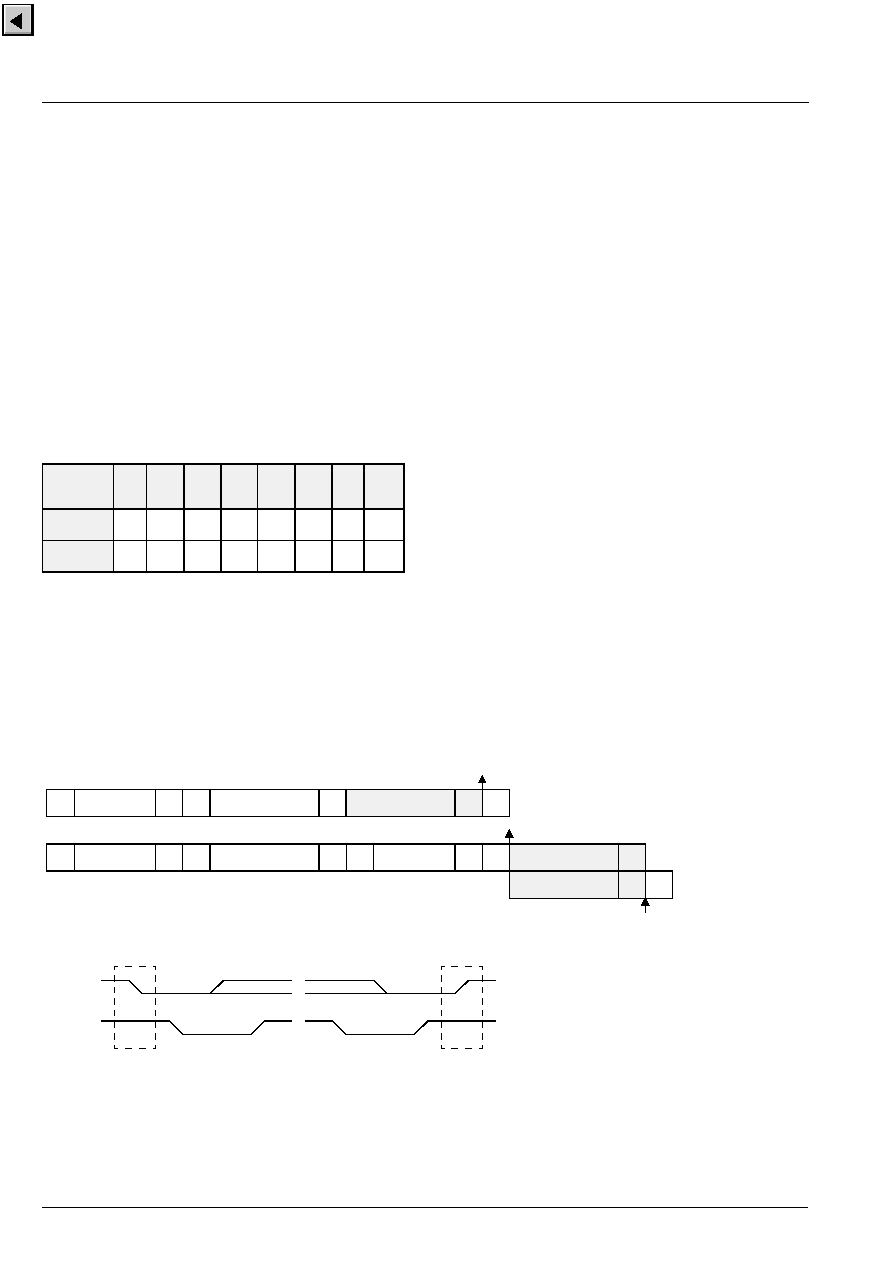

switch 1 pin (RSW1) as shown in Fig. 2�19 and Fig. 2�

20. The timing window of this measurement is pro-

grammable. The intention is, to automatically detect

letterbox transmission or to measure the actual beam

current. All control loops are closed via the external

control microprocessor.

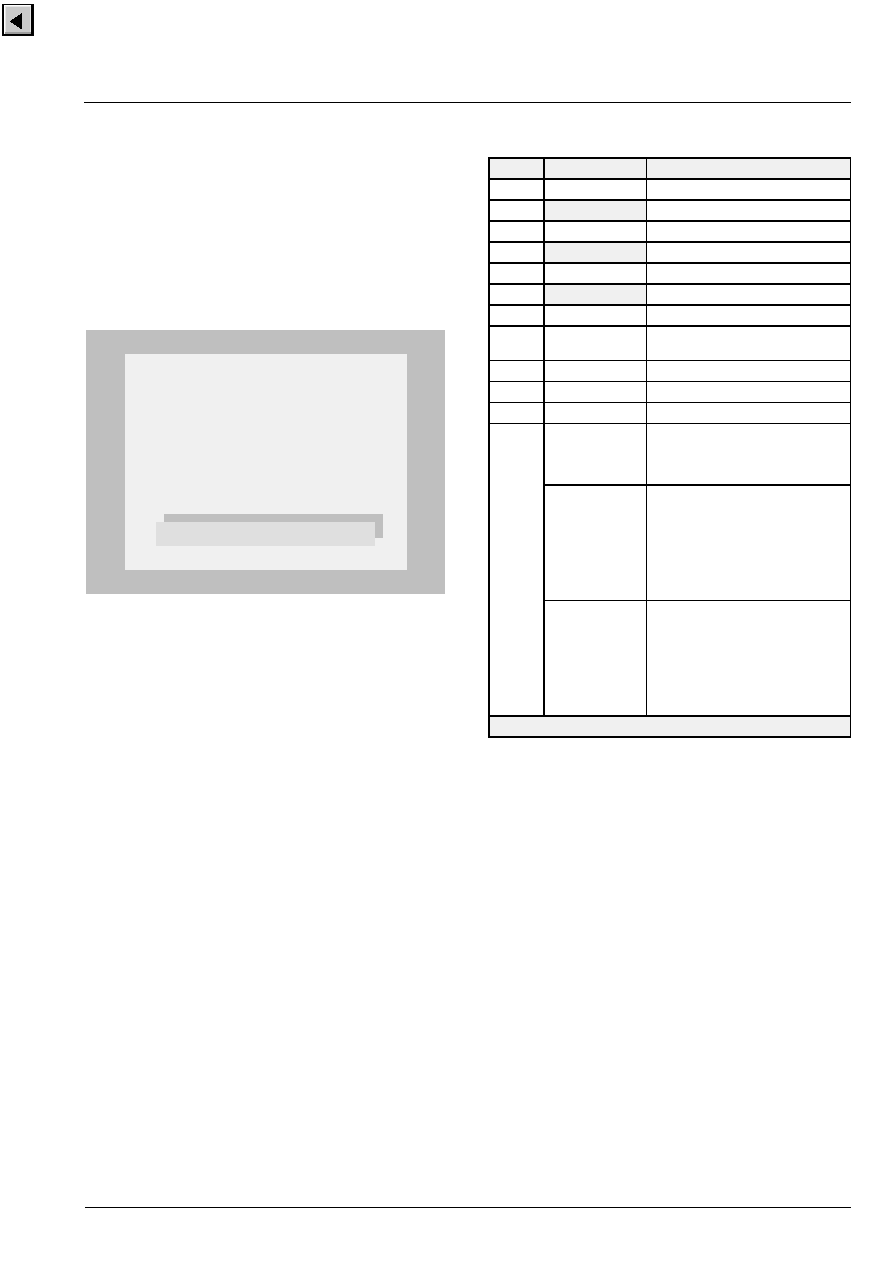

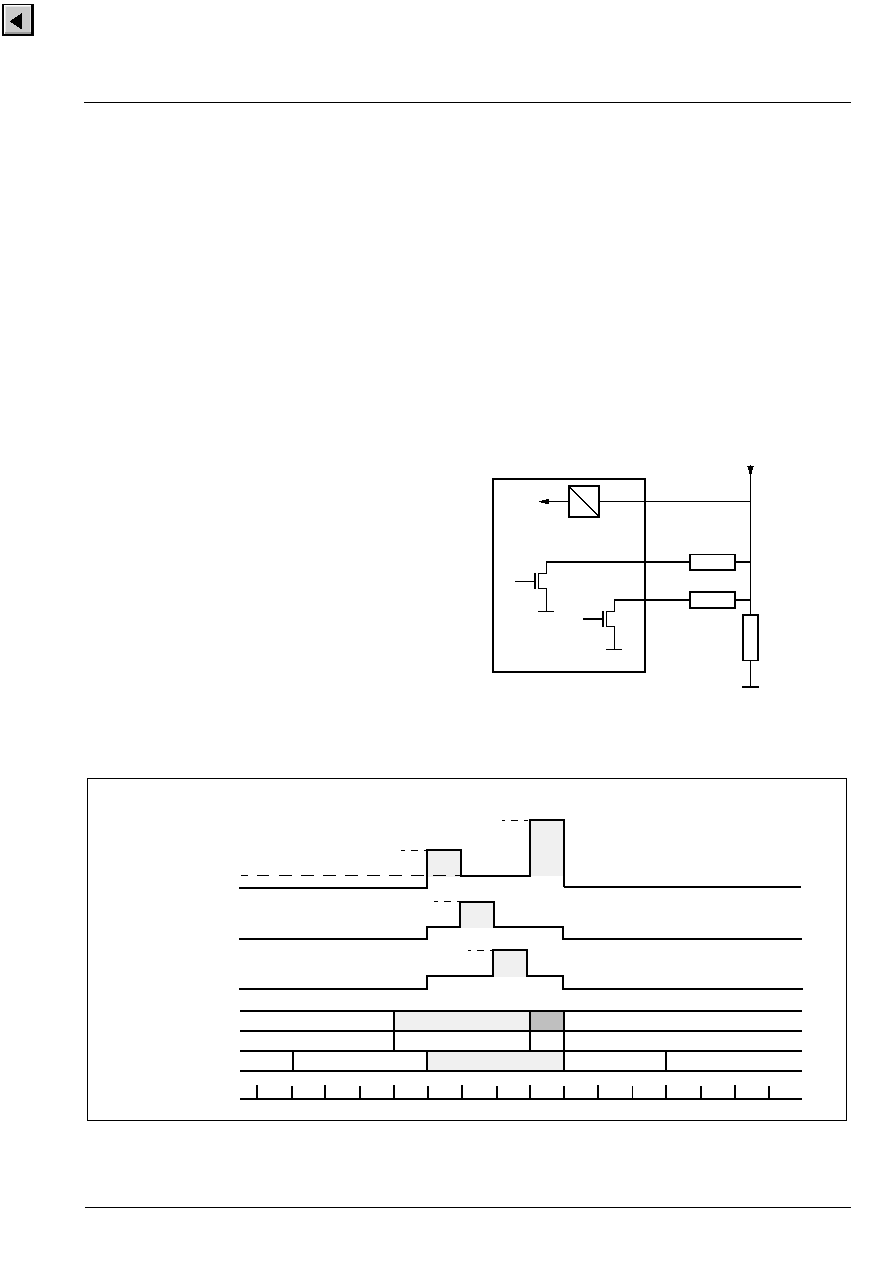

Fig. 2�19: MADC range switches

Fig. 2�20: MADC measurement timing

A

D

MADC

Beam Current

SENSE

RSW1

RSW2

R3

R2

R1

Lines

active measure-

ment resistor

ultra black

black

R1

||

R2

||

R3

RSW1=on, RSW2=on

PICTURE MEAS.

PMSO

R1

CB + IBRM

B

cutoff

CR + IBRM + WDRV

WDR

CR + IBRM

CG + IBRM

G

cutoff

R

cutoff

R1

||

R3

R1

||

R2

||

R3

RSW1=on, RSW2=on

PICTURE MEAS.

PMST

TML

RSW2

=on

TUBE MEASUREMENT

R

G

B

white

drive

R

VCT 38xxA

ADVANCE INFORMATION

26

Micronas

In each field two sets of measurements can be taken:

a) The picture tube measurement returns results for

� cutoff R

� cutoff G

� cutoff B

� white-drive R or G or B (sequentially)

b) The picture measurement returns data on

� active picture maximum current

� active picture minimum current

The tube measurement is automatically started when

the cutoff blue result register is read. Cutoff control for

RGB requires one field only, whereas a complete

white-drive control requires three fields. If the mea-

surement mode is set to `offset check', a measurement

cycle is run with the cutoff/white-drive signals set to

zero. This allows to compensate the MADC offset as

well as input the leakage currents. During cutoff and

white-drive measurements, the average beam current

limiter function (see Section 2.11.3. on page 27) is

switched off and a programmable value is used for the

brightness setting. The start line of the tube measure-

ment can be programmed via I

2

C bus, the first line

used for the measurement, i.e. measurement of cutoff

red, is 2 lines after the programmed start line.

The picture measurement must be enabled by the con-

trol microprocessor after reading the min./max. result

registers. If a `1' is written into bit 2 in subaddress 25,

the measurement runs for one field. For the next mea-

surement a `1' has to be written again. The measure-

ment is always started at the beginning of active video.

The vertical timing for the picture measurement is pro-

grammable, and may even be a single line. Also the

signal bandwidth is switchable for the picture measure-

ment.

Two horizontal windows are available for the picture

measurement. The large window is active for the entire

active line. Tube measurement is always carried out

with the small window. Measurement windows for pic-

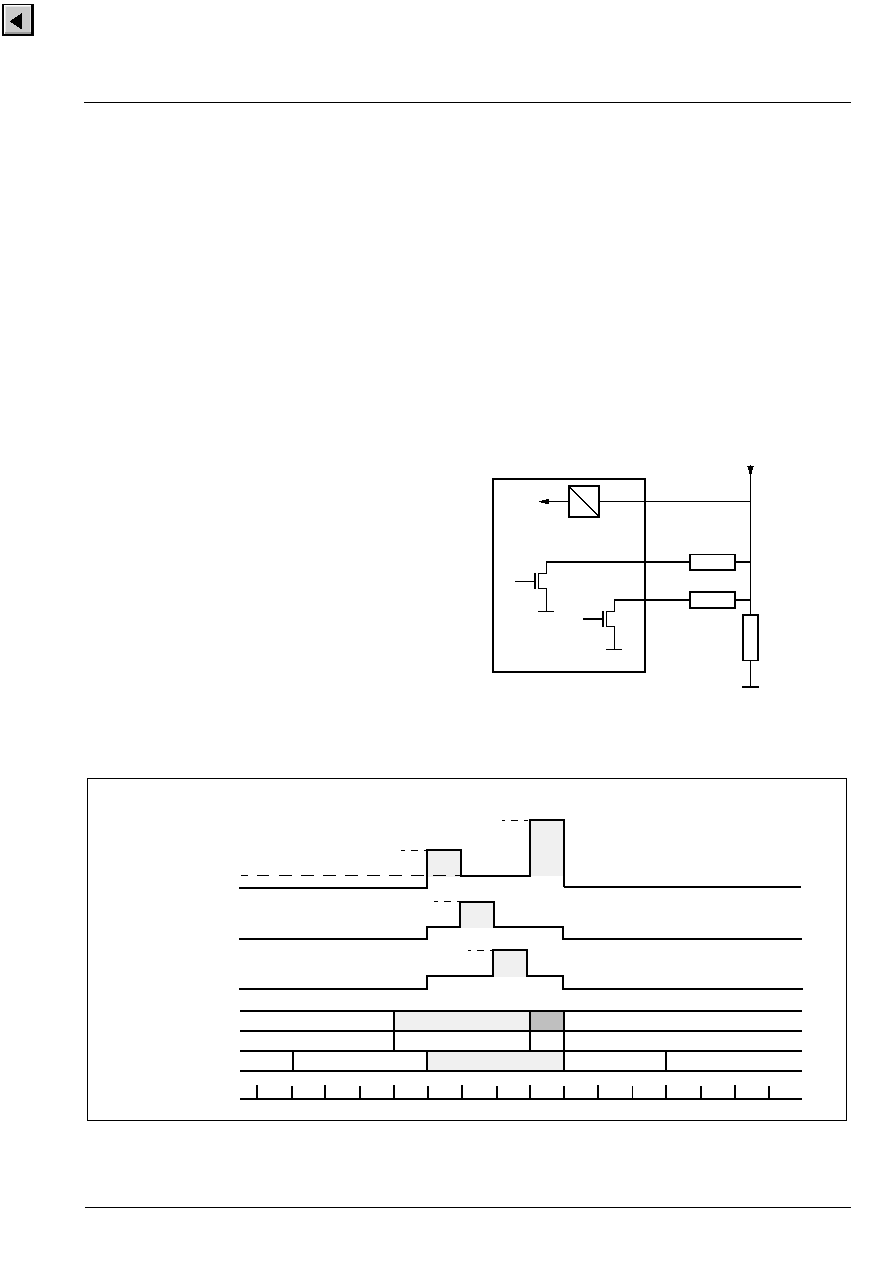

ture and tube measurement are shown in Fig. 2�21.

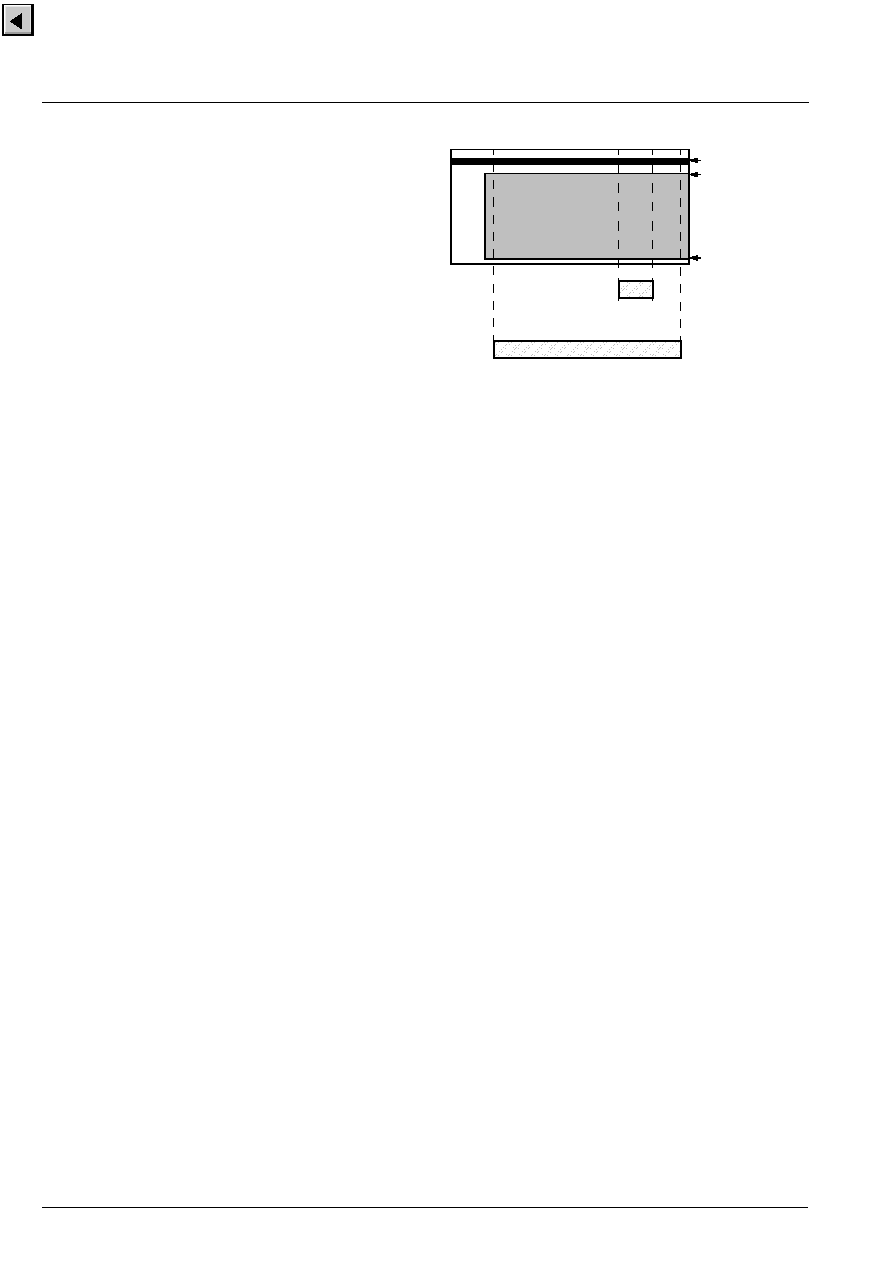

Fig. 2�21: Windows for tube and picture measure-

ments

2.11.2.SCART Output Signal

The RGB output of the VCT 38xxA can also be used to

drive a SCART output. In the case of the SCART sig-

nal, the parameter CLMPR (clamping reference) has to

be set to 1. Then, during blanking, the RGB outputs

are automatically set to 50 % of the maximum bright-

ness. The DC offset values can be adjusted with the

cutoff parameters CR, CG, and CB. The amplitudes

can be adjusted with the drive parameters WDR,

WDG, and WDB.

active video

field 1/ 2

tube measurement

picture meas. start

picture meas. end

small window for tube

measurement (cutoff, white drive)

large window for active picture

picture meas. start

ADVANCE INFORMATION

VCT 38xxA

Micronas

27

2.11.3.Average Beam Current Limiter

The average beam current limiter (BCL) uses the

SENSE input for the beam current measurement. The

BCL uses a different filter to average the beam current

during the active picture. The filter bandwidth is

approx. 2 kHz. The beam current limiter has an auto-

matic offset adjustment that is active two lines before

the first cutoff measurement line.

The beam current limiter function is located in the

front-end. The data exchange between the front-end

and the back-end is done via a single-wire serial inter-

face.

The beam current limiter allows the setting of a thresh-

old current. If the beam current is above the threshold,

the excess current is low-pass filtered and used to

attenuate the RGB outputs by adjusting the white-drive

multipliers for the internal (digital) RGB signals, and

the analog contrast multipliers for the analog RGB

inputs, respectively. The lower limit of the attenuator is

programmable, thus a minimum contrast can always

be set. During the tube measurement, the ABL attenu-

ation is switched off. After the white-drive measure-

ment line it takes 3 lines to switch back to BCL limited

drives and brightness.

Typical characteristics of the ABL for different loop

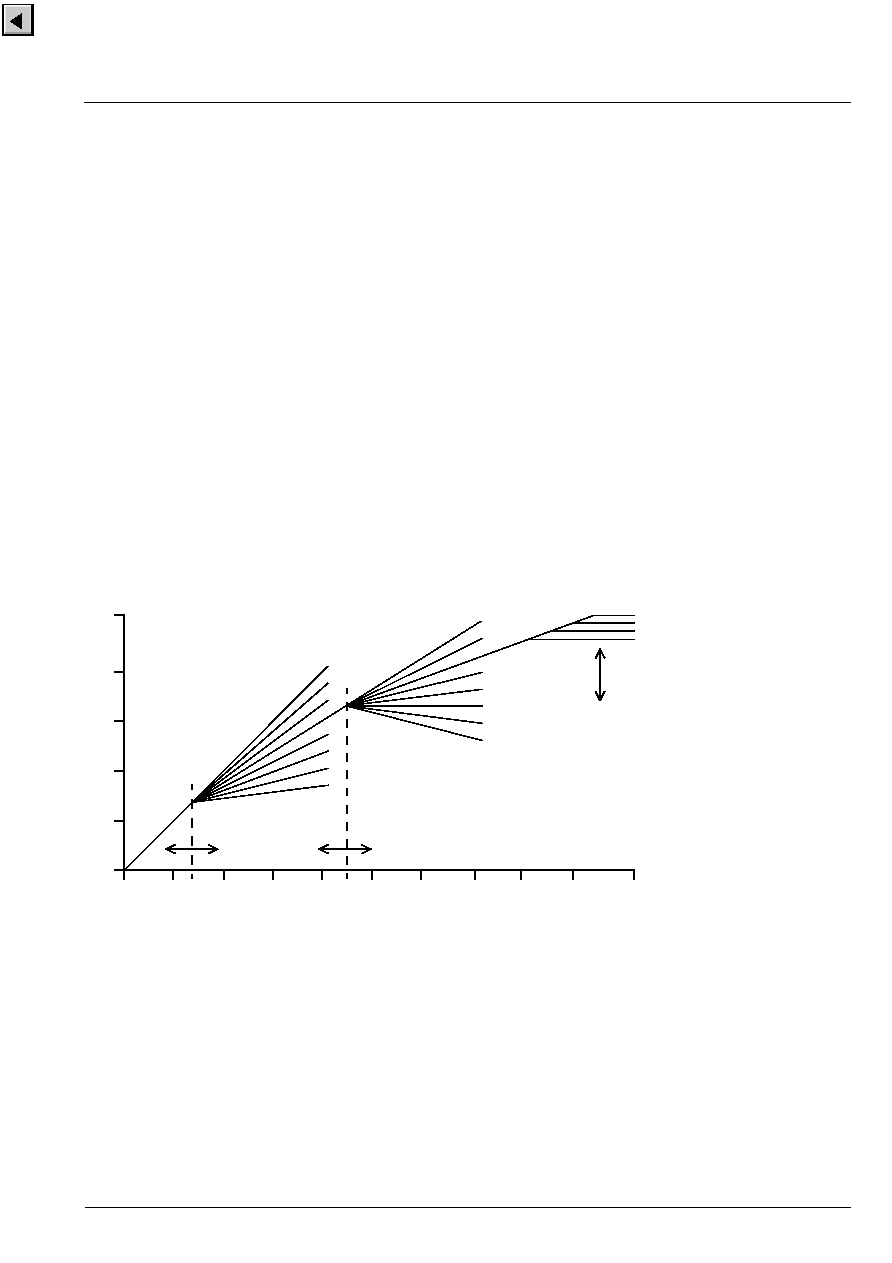

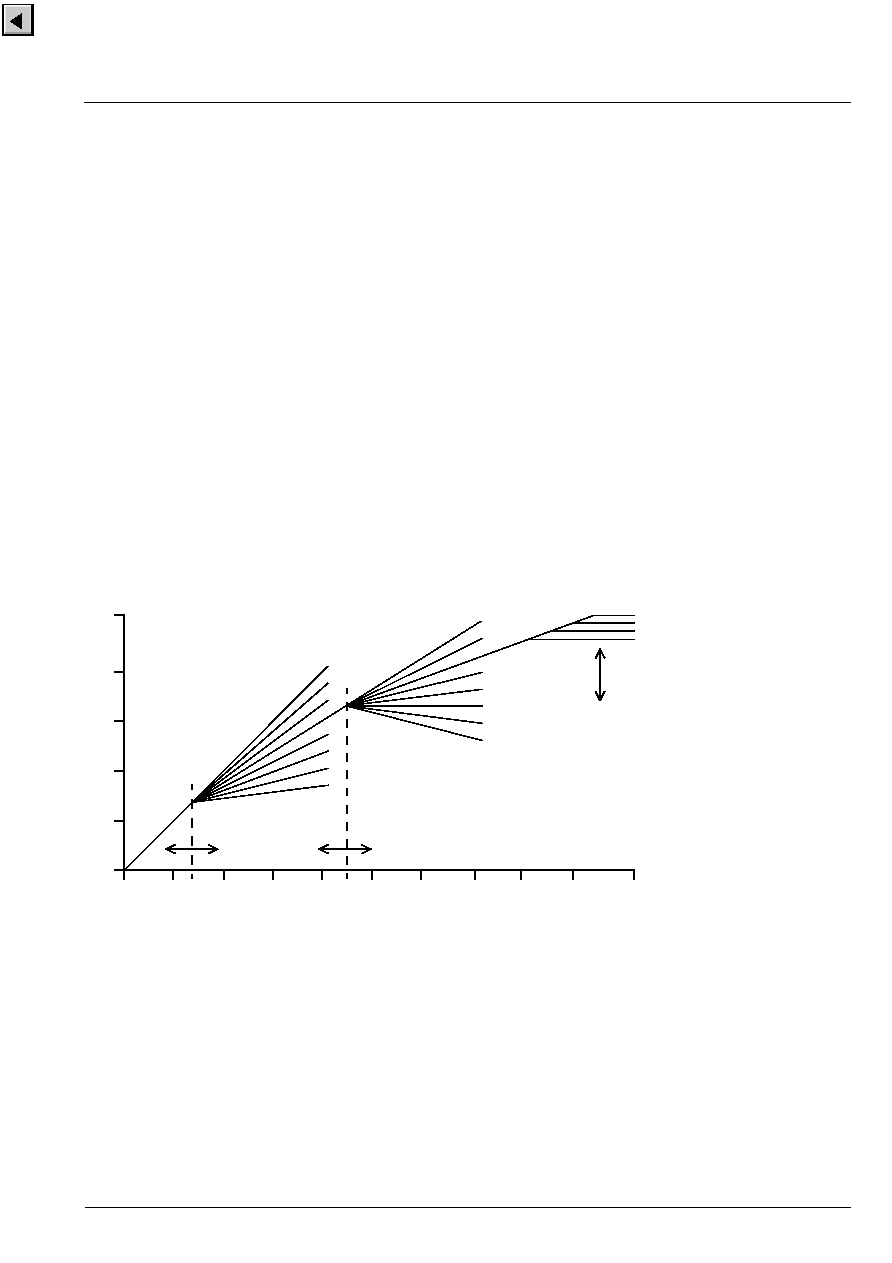

gains are shown in Fig. 2�22; for this example the tube

has been assumed to have square law characteristics.

Fig. 2�22: Beam current limiter characteristics:

beam current output vs. drive

BCL threshold: 1

2.11.4.Analog RGB Insertion

The VCT 38xxA allows insertion of external analog

RGB signals. The RGB signal is key-clamped and

inserted into the main RGB by the Fast-Blank switch.

The external RGB input can be overlaid or underlaid to

the digital picture. The external RGB signals can be

adjusted independently as regards DC level (bright-

ness) and magnitude (contrast).

All signals for analog RGB insertion (RIN, GIN, BIN,

FBLIN) must be synchronized to the horizontal flyback,

otherwise a horizontal jitter will be visible. The

VCT 38xxA has no means for timing correction of the

analog RGB input signals.

2.11.5.Fast-Blank Monitor

The presence of external analog RGB sources can be

detected by means of a Fast-Blank monitor. The status

of the Fast-Blank input can be monitored via an I

2

C

bus register. There is a 2 bit information, giving static

and dynamic indication of a Fast-Blank signal. The

static bit is directly reading the Fast-Blank input line,

whereas the dynamic bit is reading the status of a

flip-flop triggered by the negative edge of the Fast-

Blank signal.

With this monitor logic it is possible to detect if there is

an external RGB source active and if it is a full screen

insertion or only a box. The monitor logic is connected

directly to the FBLIN pin.

VCT 38xxA

ADVANCE INFORMATION

28

Micronas

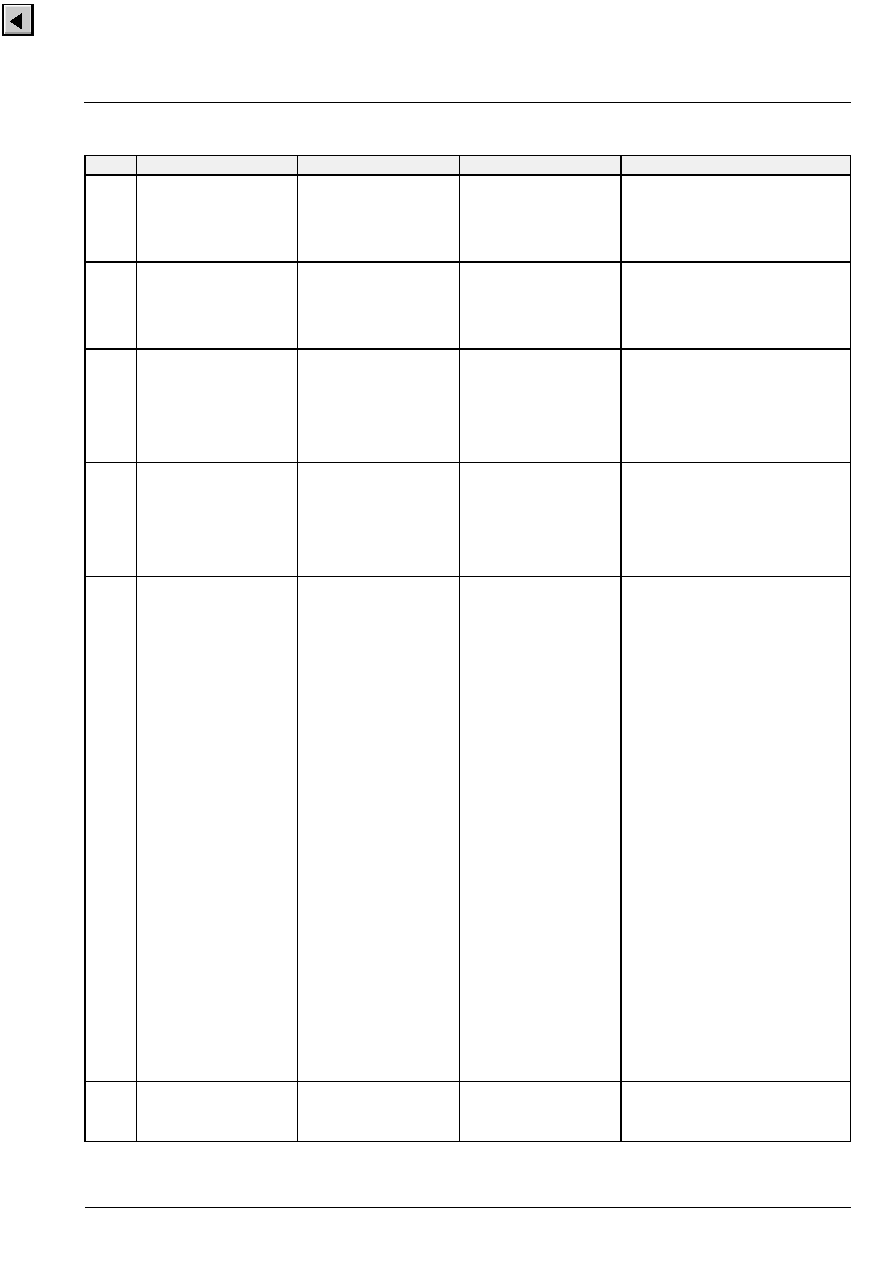

Fig. 2�23: Video back-end

ext.

contr

a

st *

w

h

i

t

e

dri

v

e R

*

bea

m cur

r

en

t l

i

m

.

cut

o

ff R

10-bit

DAC

Video

3.75 mA

blank &

timing

8 bit

ADC

measurm.

9-bit

U/I-DAC

3.75 mA

clamp

key

analog

R in

SENSE

analog

R out

analog

G out

analog

B out

analog

G in

analog

B in

me

asure

m

ent

bu

ffer

digital

R in

H

V

measurem.

10

9-bit

DAC

1.5 mA

ext. br

i

g

htne

ss *

w

h

i

t

e dr

i

v

e R

digital

G in

digital

B in

9-bit

DAC

2.2 mA

10-bit

DAC

Video

3.75 mA

10-bit

DAC

Video

3.75 mA

9-bit

U/I-DAC

3.75 mA

9-bit

U/I-DAC

3.75 mA

cutof

f

G

9 bit

DAC

2.2 mA

cutoff B

9 bit

DAC

2.2 mA

9-bit

DAC

1.5 mA

9-bit

DAC

1.5 mA

Input

I/O

ext. br

i

ghtne

ss *

wh

ite

d

r

ive

G

ext

.

bri

g

h

t

ness *

wh

ite

d

r

ive

B

9-bit

DAC

1.5 mA

wh

ite

d

r

ive

G

9-bit

DAC

1.5 mA

i

n

t. bri

g

htness *

w

h

i

t

e dri

v

e

B

9-bit

DAC

1.5 mA

w

h

i

t

e dr

i

v

e R

in

t. b

r

ig

h

t

n

e

ss

*

i

n

t

.

bri

g

h

t

ness *

fast

ext.

contr

a

st *

w

h

i

t

e dri

v

e

G *

bea

m cur

r

en

t l

i

m

.

ext.

contr

a

st *

w

h

i

t

e

dri

v

e B

*

bea

m cur

r

en

t l

i

m

.

10

10

analog

SVM out

8

8-bit

DAC

SVM

1.88 mA

0.94 mA

digital

SVM in

serial interface

clamp

clamp

blank in

blanking

750

�

A

blanking

750

�

A

blanking

750

�

A

ext. brightness

ext. contrast

int . brightness

white drive B

white drive G

white drive R

ADVANCE INFORMATION

VCT 38xxA

Micronas

29

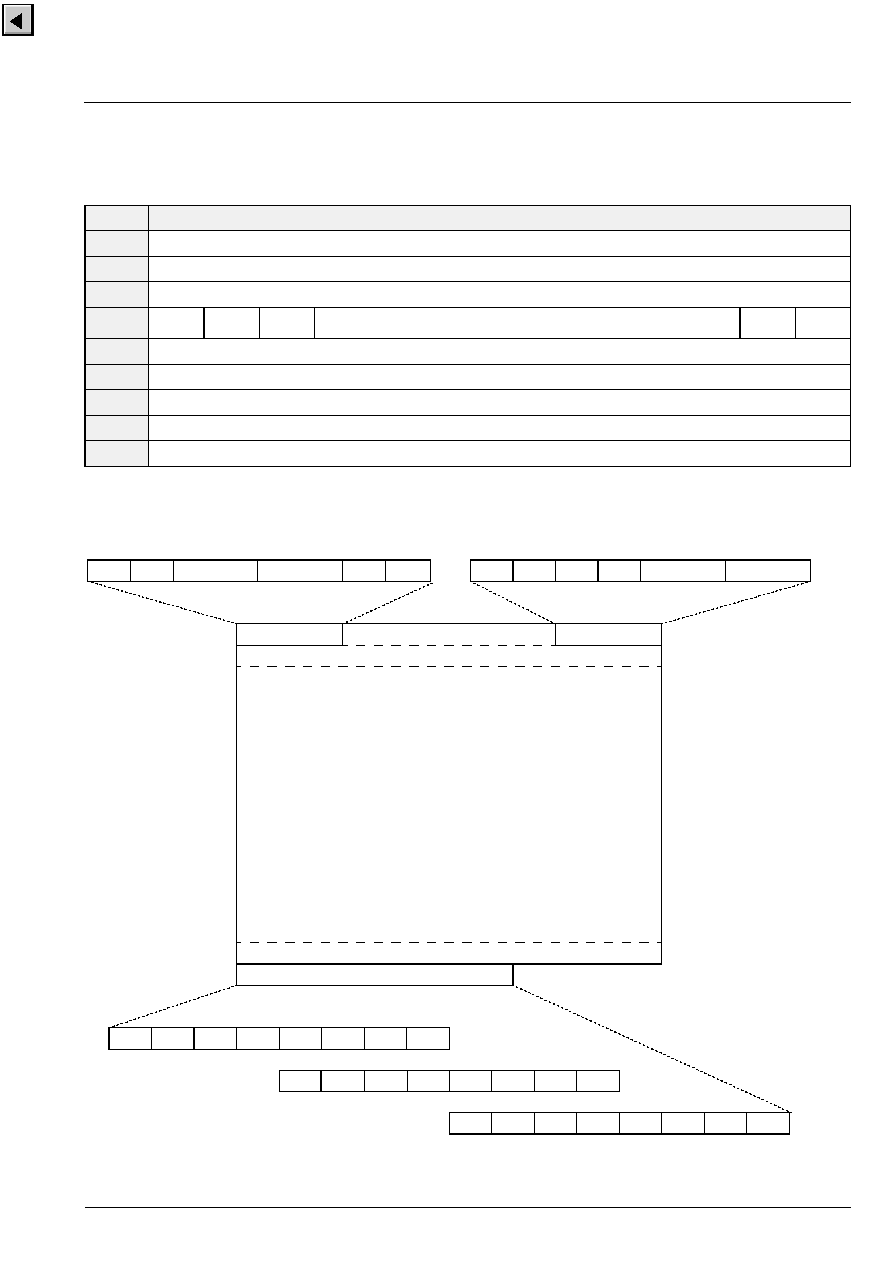

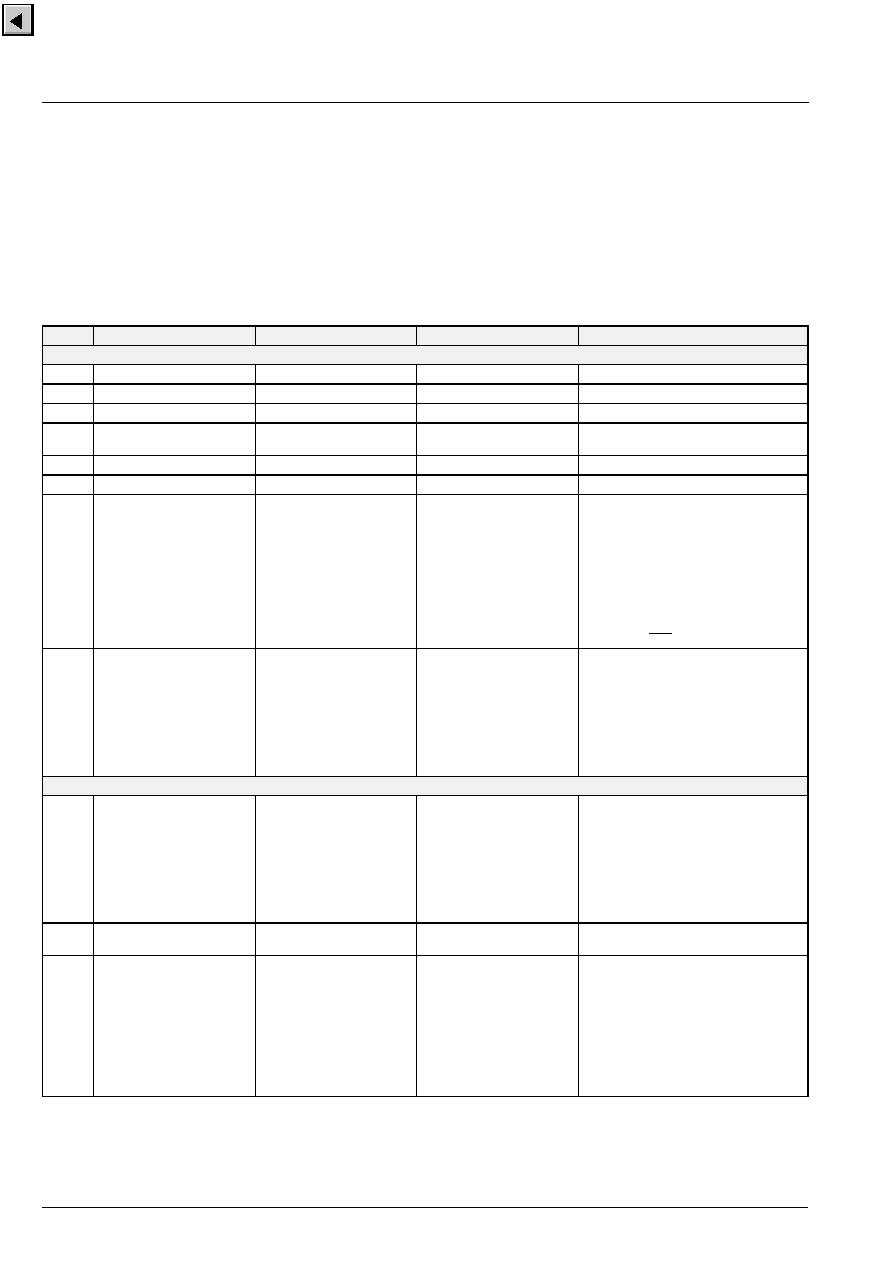

2.12.Synchronization and Deflection

The synchronization and deflection processing is dis-

tributed over front-end and back-end. The video

clamping, horizontal and vertical sync separation and

all video related timing information are processed in

the front-end. Most of the processing that runs at the

horizontal frequency is programmed on the internal

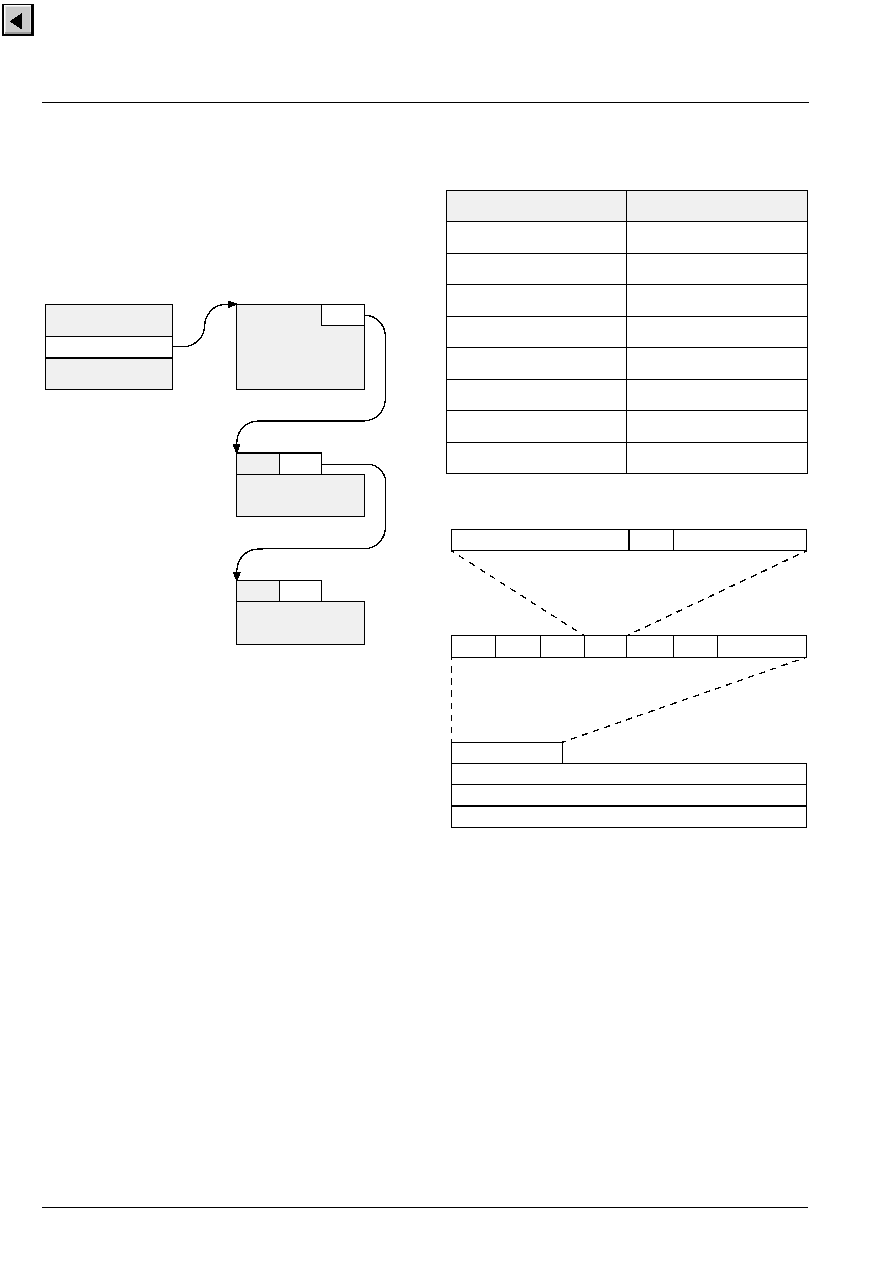

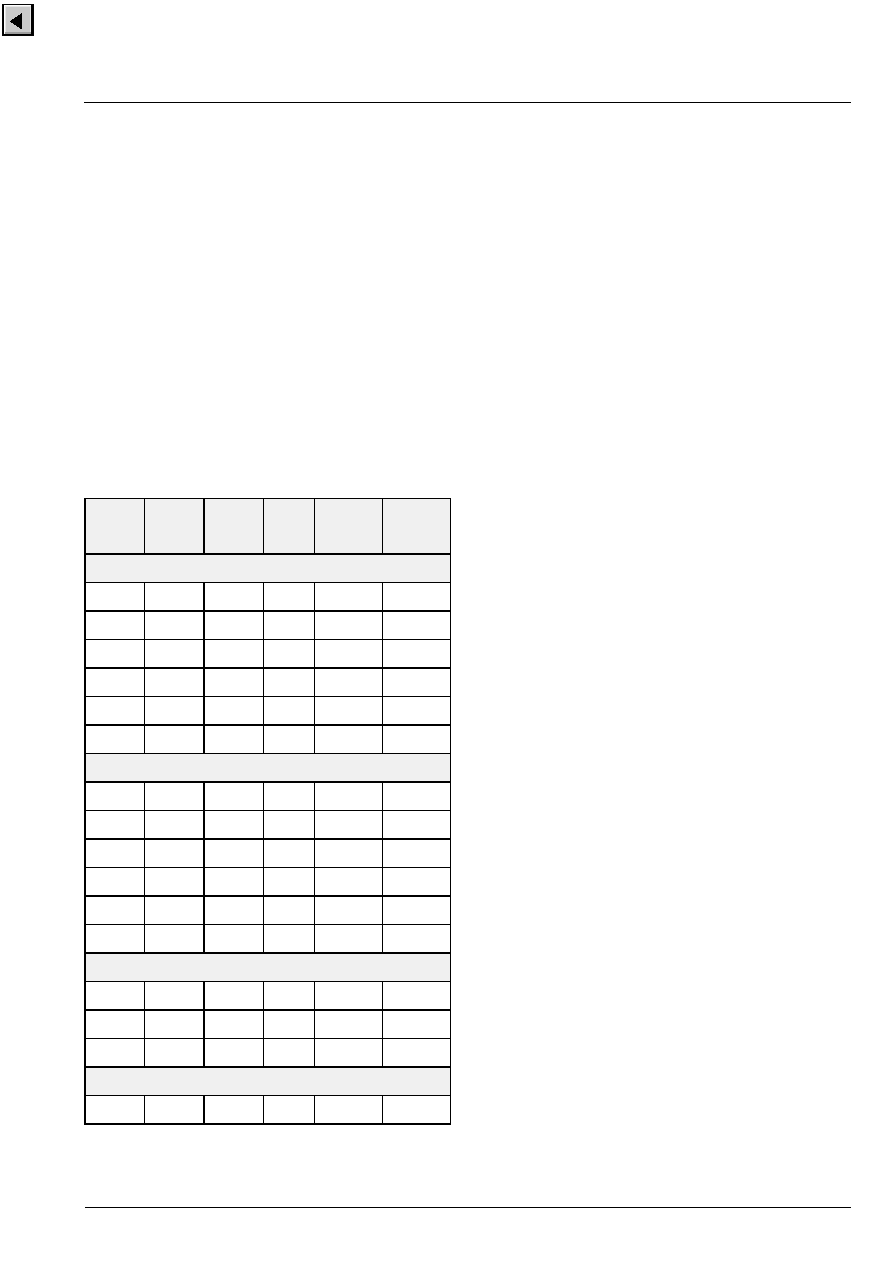

Fast Processor (FP). Also the values for vertical and