REGULATING PULSE WIDTH MODULATOR

FEATURES

∑∑

∑∑

∑

8V to 35V operation

∑∑

∑∑

∑

5.1V reference trimmed to ±1%

∑∑

∑∑

∑

100Hz to 500KHz oscillator range

∑∑

∑∑

∑

Separate oscillator sync terminal

∑∑

∑∑

∑

Adjustable deadtime control

∑∑

∑∑

∑

Internal soft-start

∑∑

∑∑

∑

Input undervoltage lockout

∑∑

∑∑

∑

Latching P.W.M. to prevent multiple

pulses

∑∑

∑∑

∑

Dual source/sink output drivers

HIGH RELIABILITY FEATURES

- SG1525A, SG1527A

Available to MIL-STD-883B

MIL-M38510/12602BEA - JAN1525AJ

MIL-M38510/12604BEA - JAN1527AJ

Radiation data available

LMI level "S" processing available

DESCRIPTION

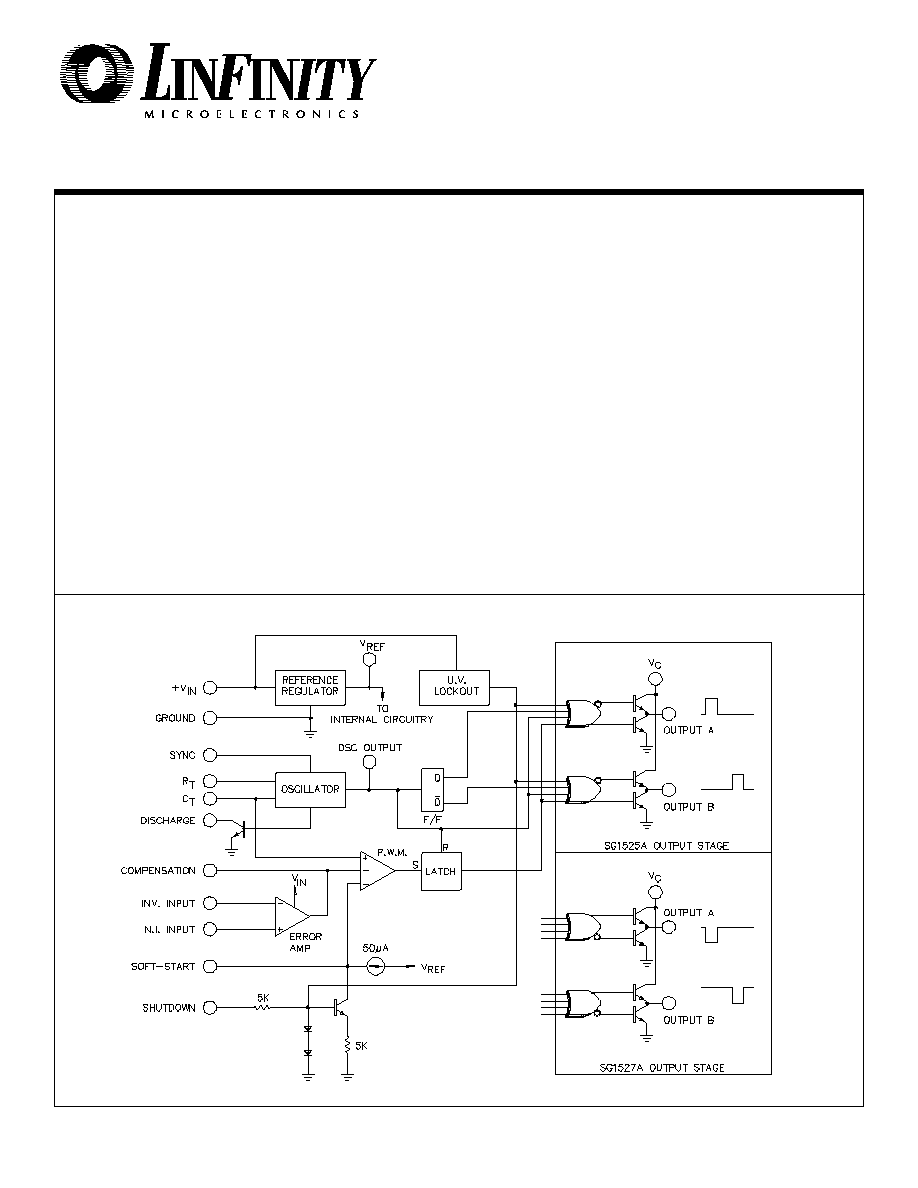

The SG1525A/1527A series of pulse width modulator integrated circuits are

designed to offer improved performance and lower external parts count when used

to implement all types of switching power supplies. The on-chip +5.1 volt reference

is trimmed to ±1% initial accuracy and the input common-mode range of the error

amplifier includes the reference voltage, eliminating external potentiometers and

divider resistors. A Sync input to the oscillator allows multiple units to be slaved

together, or a single unit to be synchronized to an external system clock. A single

resistor between the C

T

pin and the Discharge pin provides a wide range of deadtime

adjustment. These devices also feature built-in soft-start circuitry with only a timing

capacitor required externally. A Shutdown pin controls both the soft-start circuitry

and the output stages, providing instantaneous turn-off with soft-start recycle for

slow turn-on. These functions are also controlled by an undervoltage lockout which

keeps the outputs off and the soft-start capacitor discharged for input voltages less

than that required for normal operation. Another unique feature of these PWM

circuits is a latch following the comparator. Once a PWM pulse has been terminated

for any reason, the outputs will remain off for the duration of the period. The latch

is reset with each clock pulse. The output stages are totem-pole designs capable

of sourcing or sinking in excess of 200mA. The SG1525A output stage features

NOR logic, giving a LOW output for an OFF state. The SG1527A utilizes OR logic

which results in a HIGH output level when OFF.

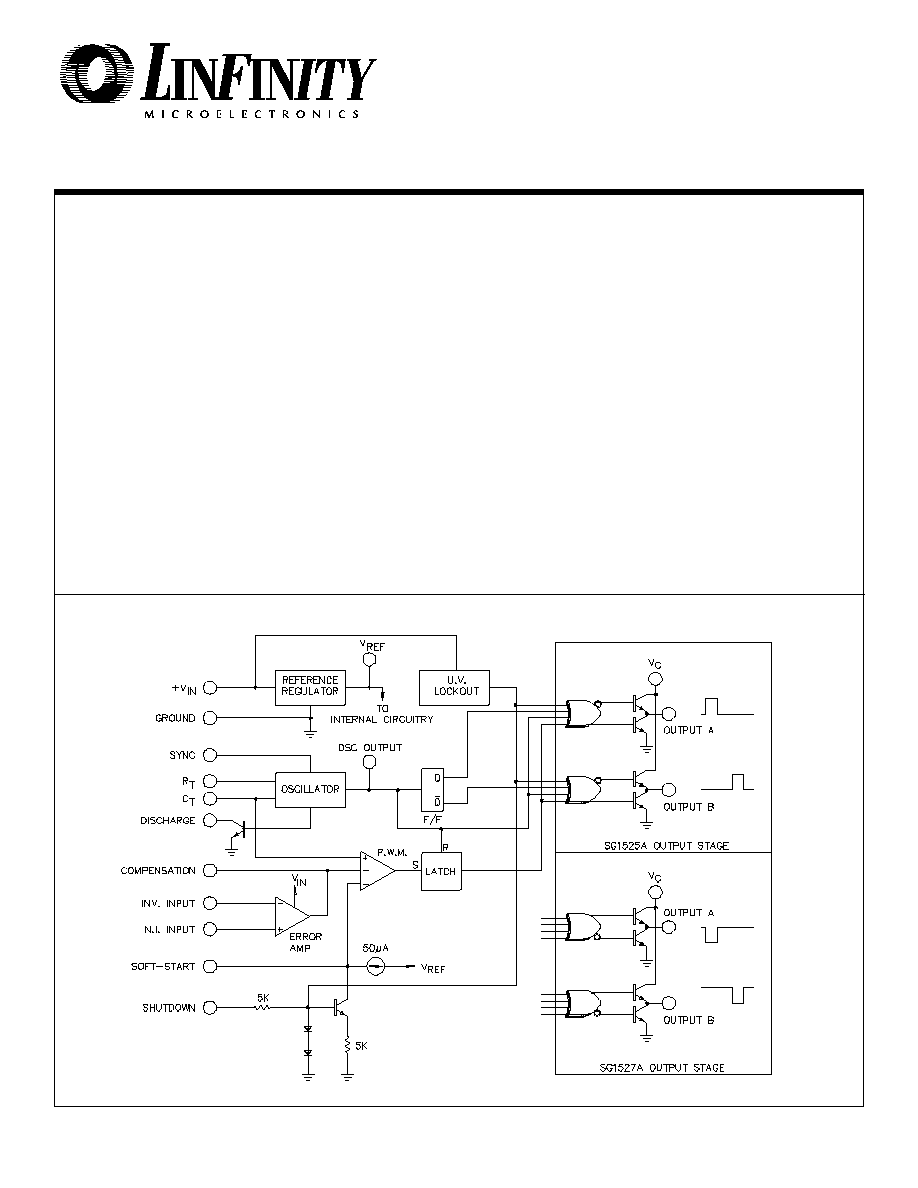

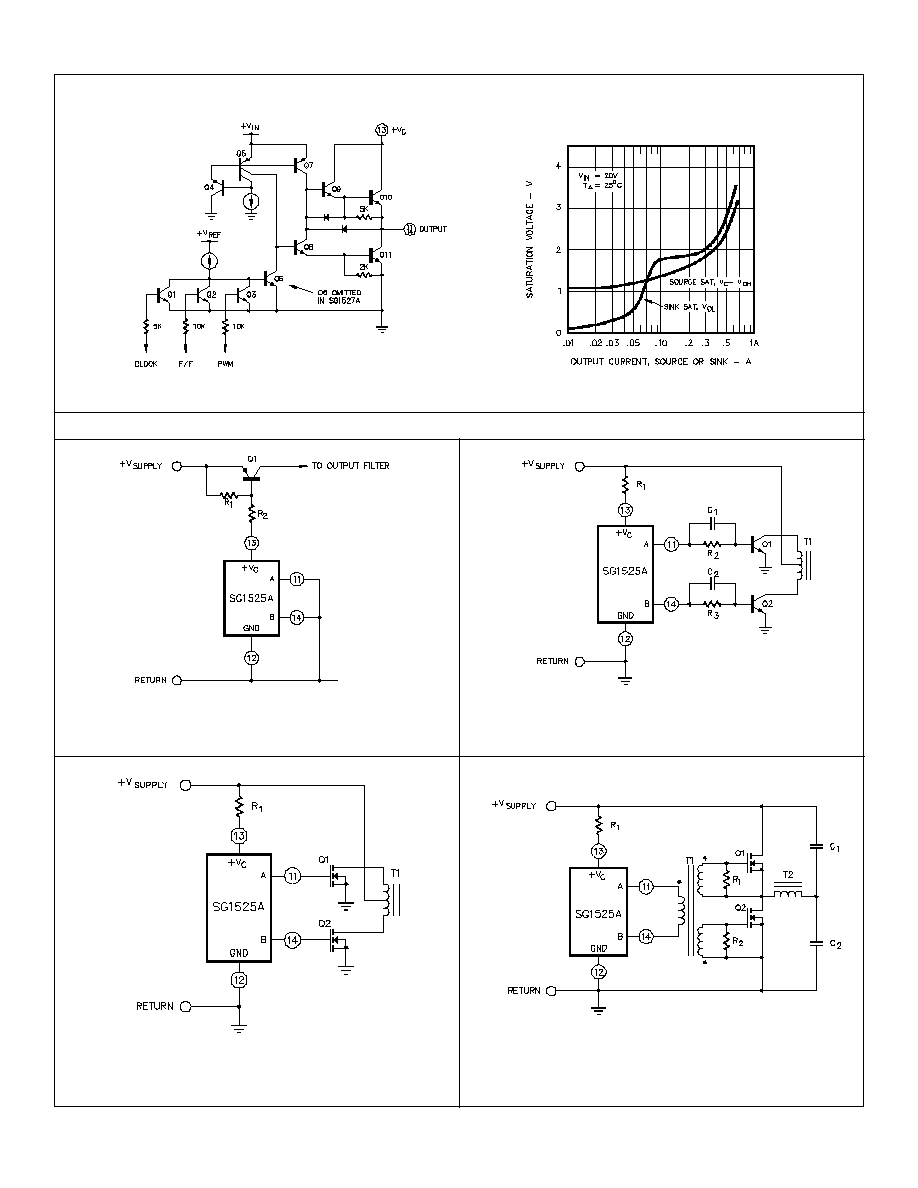

BLOCK DIAGRAM

SG1525A/SG2525A/SG3525A

SG1527A/SG2527A/SG3527A

11/91 Rev 1.3 10/96

L

INFINITY

Microelectronics Inc.

Copyright

©

1996

11861 Western Avenue

Garden Grove, CA 92841

1

(714) 898-8121

FAX: (714) 893-2570

SG1525A/SG1527A SERIES

11/91 Rev 1.3 10/96

L

INFINITY

Microelectronics Inc.

Copyright

©

1996

11861 Western Avenue

Garden Grove, CA 92841

2

(714) 898-8121

FAX: (714) 893-2570

Oscillator Charging Current ............................................

Operating Junction Temperature Range

Hermetic (J, L Packages) .....................................

Plastic (N, DW Packages ) .......................................

Storage Temperature Range ..........................

Lead Temperature (Soldering, 10 seconds) .................

Supply Voltage (+V

IN

) .......................................................

Collector Supply Voltage (V

C

) ...........................................

Logic Inputs .......................................................

Analog Inputs .......................................................

Output Current, Source or Sink ...................................

Reference Load Current ...............................................

40V

40V

-0.3V to 5.5V

-0.3V to V

IN

500mA

50mA

5mA

150

∞

C

150

∞

C

-65

∞

C to 150

∞

C

300

∞

C

ABSOLUTE MAXIMUM RATINGS

(Note 1)

Note 1. Values beyond which damage may occur.

Input Voltage (+V

IN

) ................................................

Collector Voltage (V

C

) ..........................................

Sink/Source Load Current (steady state) .............

Sink/Source Load Current (peak) .........................

Reference Load Current ........................................

Oscillator Frequency Range .......................

Oscillator Timing Resistor (R

T

) ........................

8V to 35V

4.5V to 35V

0 to 100mA

0 to 400mA

0 to 20mA

100Hz to 350KHz

2K

to 150K

Deadtime Resistor Range (R

D

) .............................

Maximum Shutdown Source Impedance .........................

Oscillator Timing Capacitor (C

T

) ...................

Operating Ambient Temperature Range

SG1525A/SG1527A ....................................

SG2525A/SG2527A ......................................

SG3525A/SG3527A .........................................

0

to 500

5K

0.001

µ

F to 0.1

µ

F

-55

∞

C to 125

∞

C

-25

∞

C to 85

∞

C

0

∞

C to 70

∞

C

Note 2: Range over which the device is functional.

RECOMMENDED OPERATING CONDITIONS

(Note 2)

ELECTRICAL CHARACTERISTICS

(Unless otherwise specified, these specifications apply over the operating ambient temperatures for SG1525A/SG1527A with -55

∞

C

T

A

125

∞

C,

SG2525A/SG2527A with -25

∞

C

T

A

85

∞

C, SG3525A/SG3527A with 0

∞

C

T

A

70

∞

C, and +V

IN

= 20V. Low duty cycle pulse testing techniques are

used which maintains junction and case temperatures equal to the ambient temperature.)

5.05

5.00

Reference Section

T

J

= 25

∞

C

V

IN

= 8V to 35V

I

L

= 0 to 20mA

Over Operating Temperature Range

Over Line, Load and Temperature

V

REF

= 0V, T

J

= 25

∞

C

10Hz

f

10KHz, T

J

= 25

∞

C

T

J

= 125

∞

C

Output Voltage

Line Regulation

Load Regulation

Temperature Stability

(Note 3)

Total Output Voltage Range

(Note 3)

Short Circuit Current

Output Noise Voltage

(Note 3)

Long Term Stability

(Note 3)

Min. Typ. Max. Min. Typ. Max.

Note 3. These parameters, although guaranteed over the recommended operating conditions, are not 100% tested in production.

Note 4. F

OSC

= 40KHz (R

T

= 3.6K

, C

T

= 0.01

µ

F, R

D

= 0

)

Note 5. Applies to SG1525A/2525A/3525A only, due to polarity of output pulses.

SG3525A

SG3527A

SG1525A/2525A

SG1527A/2527A

Units

Test Conditions

Parameter

V

mV

mV

mV

V

mA

µ

Vrms

mV/khr

5.20

30

50

50

5.25

100

200

50

5.10

10

20

20

80

40

20

5.00

4.95

5.15

30

50

50

5.20

100

200

50

5.10

10

20

20

80

40

20

THERMAL DATA

J Package:

Thermal Resistance-

Junction to Case

,

JC

.................. 30∞C/W

Thermal Resistance-

Junction to Ambient

,

JA

.............. 80∞C/W

DW Package:

Thermal Resistance-

Junction to Case

,

JC

.................. 40∞C/W

Thermal Resistance-

Junction to Ambient

,

JA

............. 95∞C/W

L Package:

Thermal Resistance-

Junction to Case

,

JC

.................. 35∞C/W

Thermal Resistance-

Junction to Ambient

,

JA

........... 120∞C/W

N Package:

Thermal Resistance-

Junction to Case

,

JC

................... 40∞C/W

Thermal Resistance-

Junction to Ambient

,

JA

............. 65∞C/W

Note A. Junction Temperature Calculation: T

J

= T

A

+ (P

D

x

JA

).

Note B. The above numbers for

JC

are maximums for the limiting

thermal resistance of the package in a standard mount-

ing configuration. The

JA

numbers are meant to be

guidelines for the thermal performance of the device/pc-

board system. All of the above assume no ambient

airflow.

SG1525A/SG1527A SERIES

11/91 Rev 1.3 10/96

L

INFINITY

Microelectronics Inc.

Copyright

©

1996

11861 Western Avenue

Garden Grove, CA 92841

3

(714) 898-8121

FAX: (714) 893-2570

18

17

6

Output Drivers Section

(each transistor, V

C

= 20V)

I

SOURCE

= 20mA

I

SOURCE

= 100mA

I

SINK

= 20mA

I

SINK

= 100mA

V

COMP

and V

SS

= High

V

C

= 35V

C

L

= 1nF, T

J

= 25

∞

C

C

L

= 1nF, T

J

= 25

∞

C

V

SD

= 3V, C

S

= 0, T

J

= 25

∞

C

Output High Level

Output Low Level

Undervoltage Lockout

Collector Leakage

(Note 5)

Rise Time

Fall Time

Shutdown Delay

(Note 3)

50

0.4

0.4

25

Soft-Start Section

V

SHUTDOWN

= 0V

V

SHUTDOWN

= 2V

V

SHUTDOWN

= 2.5V

Soft Start Current

Soft Start Voltage

Shutdown Input Current

µ

A

V

mA

P.W.M. Comparator Section

V

COMP

= 0.6V

V

COMP

= 3.6V

Zero Duty Cycle

Maximum Duty Cycle

Minimum Duty Cycle

Maximum Duty Cycle

Input Threshold

(Note 4)

Input Bias Current

%

%

V

V

µ

A

0.4

2.2

8

200

600

300

0.5

19

18

0.2

1.0

7

100

50

0.2

37.6

350

1.7

3.0

0.3

1.2

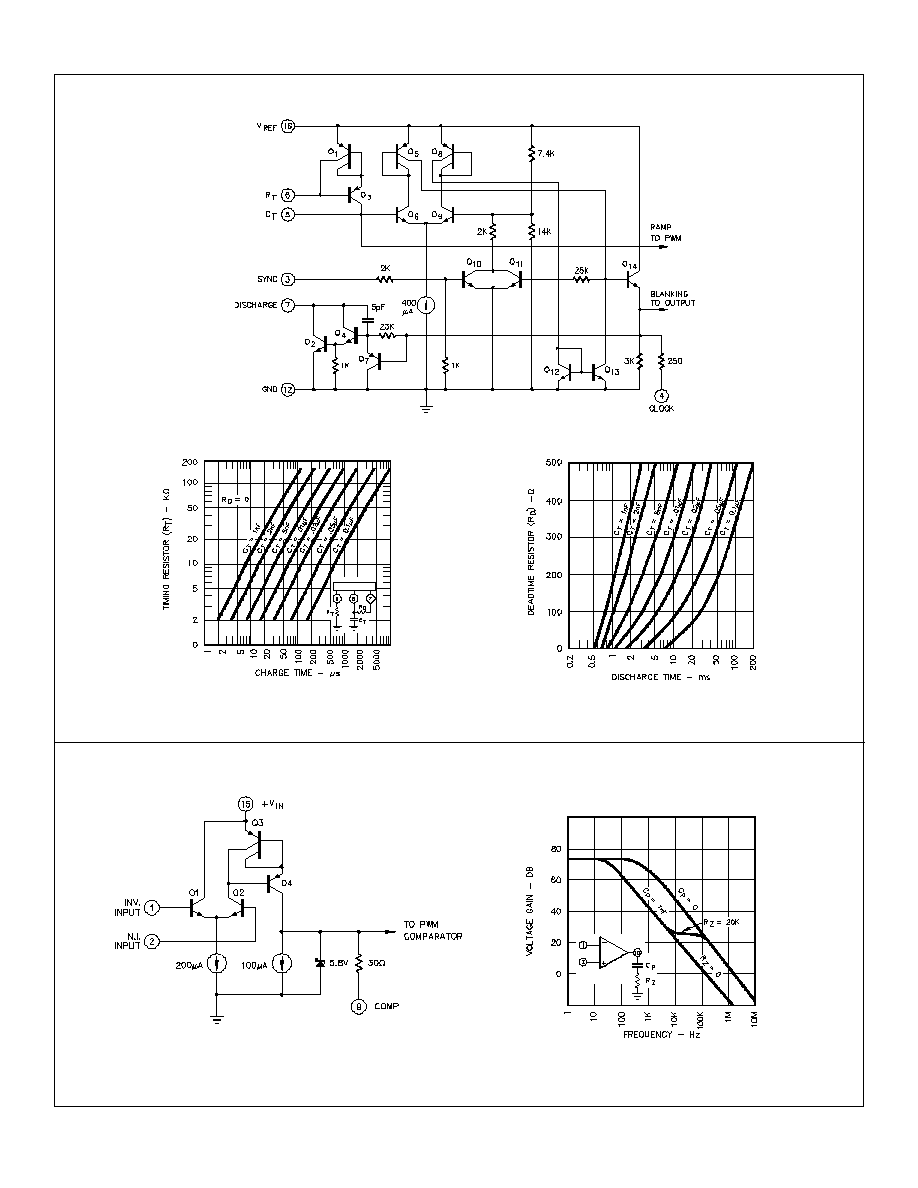

Oscillator Section

(Note 4)

T

J

= 25

∞

C

V

IN

= 8V to 35V

MIN

T

J

MAX

R

T

= 150K

, C

T

= 0.1

µ

F

R

T

= 2K

, C

T

= 1nF

I

RT

= 2mA

T

J

= 25

∞

C

Sync Voltage = 3.5V

Initial Accuracy

Voltage Stability

Temperature Stability

(Note 3)

Minimum Frequency

(Note 3)

Maximum Frequency

(Note 3)

Current Mirror

Clock Amplitude

Clock Width

Sync Threshold

Sync Input Current

Min. Typ. Max. Min. Typ. Max.

SG3525A

SG3527A

SG1525A/2525A

SG1527A/2527A

Units

Test Conditions

Parameter

ELECTRICAL CHARACTERISTICS

(continued)

KHz

%

%

Hz

KHz

mA

V

µ

s

V

mA

42.4

±2

±6

150

2.2

1.0

2.8

2.5

40

±1

±3

2.0

3.5

0.5

2.0

1.0

37.6

350

1.7

3.0

0.3

1.2

42.4

±1

±6

150

2.2

1.0

2.8

2.5

40

±0.3

±3

2.0

3.5

0.5

2.0

1.0

Error Amplifier Section

(V

CM

= 5.1V)

Input Offset Voltage

Input Bias Current

Input Offset Current

DC Open Loop Gain

Gain-Bandwidth Product

(Note 3)

Output Low Level

Output High Level

Common Mode Rejection

Supply Voltage Rejection

R

L

10M

,

T

J

= 25

∞

C

A

V

= 0dB, T

J

= 25

∞

C

V

CM

= 1.5V to 5.2V

V

IN

= 8V to 35V

60

1

3.8

60

50

0.5

1

75

2

0.2

5.6

75

60

5

10

1

0.5

60

1

3.8

60

50

2

1

75

2

0.2

5.6

75

60

10

10

1

0.5

mV

µ

A

µ

A

dB

MHz

V

V

dB

dB

45

0.6

0

3.6

2.0

49

0.9

3.3

.05

45

0.6

0

3.6

2.0

49

0.9

3.3

.05

80

0.6

1.0

25

50

0.4

0.4

80

0.6

1.0

19

18

0.2

1.0

7

100

50

0.2

18

17

6

0.4

2.2

8

200

600

300

0.5

V

V

V

V

V

µ

A

ns

ns

µ

s

Total Standby Current

Standby Current

V

IN

= 35V

mA

20

14

20

14

SG1525A/SG1527A SERIES

11/91 Rev 1.3 10/96

L

INFINITY

Microelectronics Inc.

Copyright

©

1996

11861 Western Avenue

Garden Grove, CA 92841

5

(714) 898-8121

FAX: (714) 893-2570

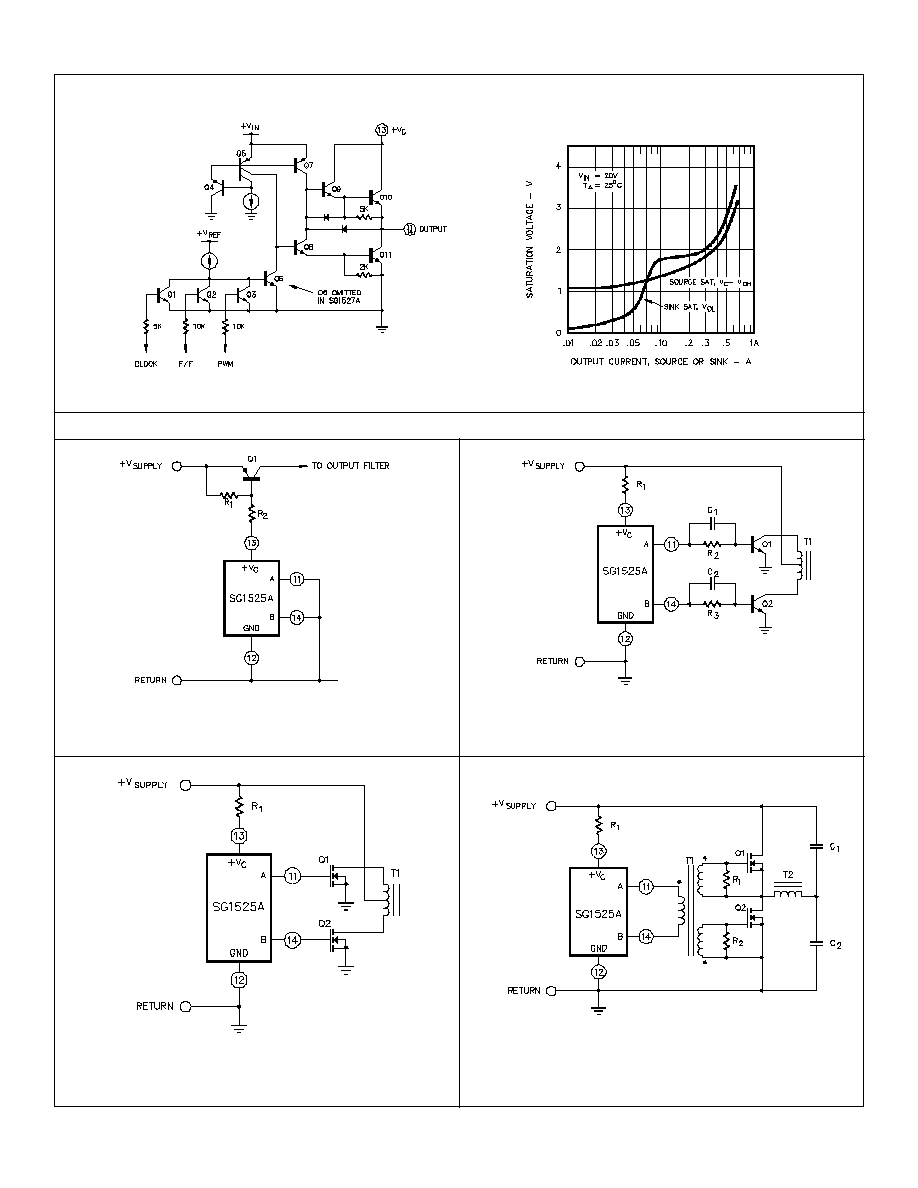

FIGURE 7 - OUTPUT SATURATION CHARACTERISTICS

FIGURE 6 -OUTPUT CIRCUIT (Ω Circuit Shown)

APPLICATION INFORMATION

Low power transformers can be driven directly by the SG1525A.

Automatic reset occurs during deadtime, when both ends of the

primary winding are switched to ground.

The low source impedance of the output drivers provides rapid

charging of power FET input capacitance while minimizing exter-

nal components.

For single-ended supplies, the driver outputs are grounded. The

V

C

terminal is switched to ground by the totem-pole source

transistors on alternate oscillator cycles.

In conventional push-pull bipolar designs, forward base drive is

controlled by R

1

- R

3

. Rapid turn-off times for the power devices

are achieved with speed-up capacitors C

1

and C

2

.

OUTPUT SECTION