Mitsubishi microcomputers

M16C / 62 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Description

1

------Table of Contents------

Description

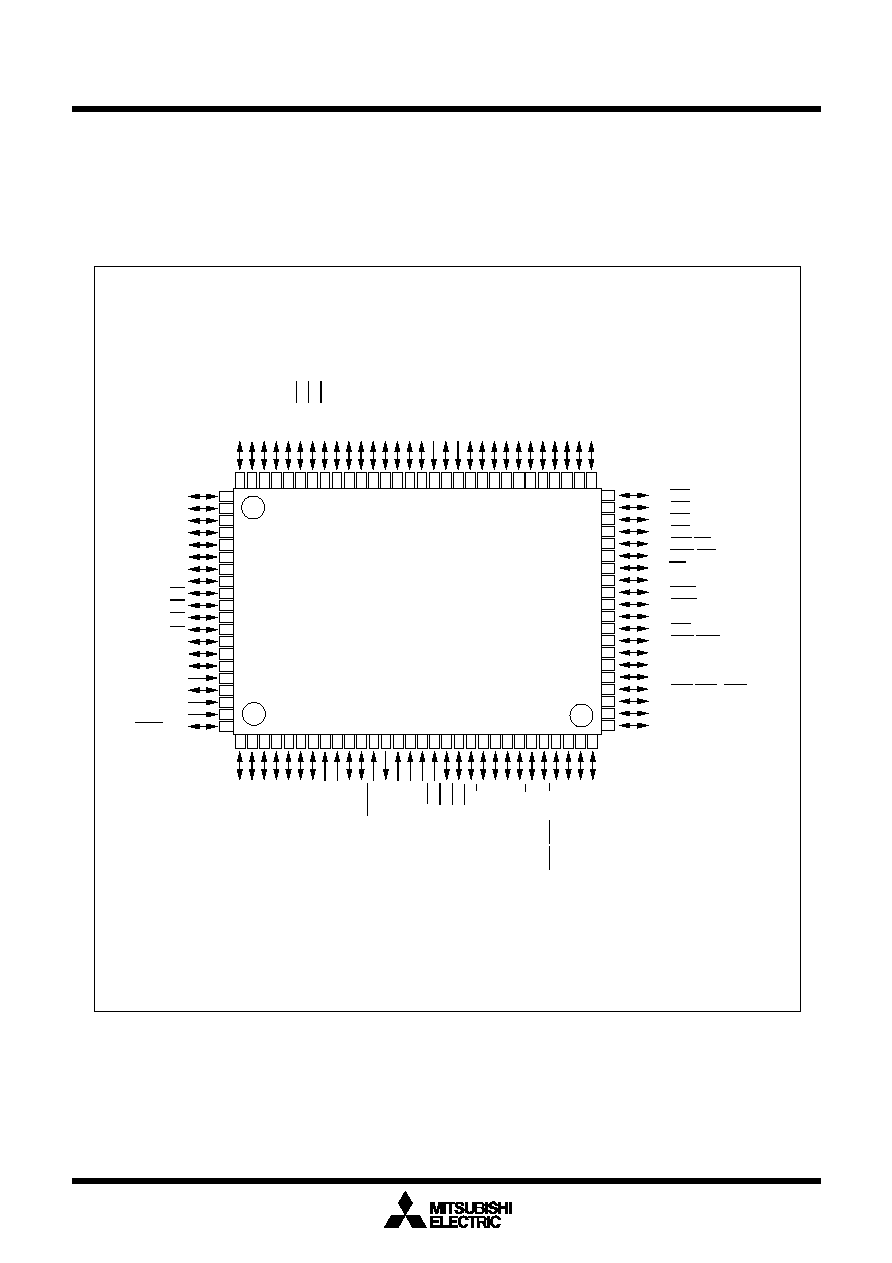

The M16C/62 group of single-chip microcomputers are built using the high-performance silicon gate CMOS

process using a M16C/60 Series CPU core and are packaged in a 100-pin plastic molded QFP. These

single-chip microcomputers operate using sophisticated instructions featuring a high level of instruction

efficiency. With 1M bytes of address space, they are capable of executing instructions at high speed. They

also feature a built-in multiplier and DMAC, making them ideal for controlling office, communications, indus-

trial equipment, and other high-speed processing applications.

The M16C/62 group includes a wide range of products with different internal memory types and sizes and

various package types.

Features

∑ Memory capacity .................................. ROM (See Figure 1.1.4. ROM Expansion)

RAM 3K to 20K bytes

∑ Shortest instruction execution time ...... 62.5ns (f(X

IN

)=16MH

Z

, V

CC

=5V)

100ns (f(X

IN

)=10MH

Z

, V

CC

=3V, with software one-wait) : Mask ROM, flash memory 5V version

142.9ns (f(X

IN

)=7MH

Z

, V

CC

=3V, with software one-wait) : One-time PROM version

∑ Supply voltage ..................................... 4.2 to 5.5V (f(X

IN

)=16MH

Z

, without software wait) : Mask ROM, flash memory 5V version

4.5 to 5.5V (f(X

IN

)=16MH

Z

, without software wait) : One-time PROM version

2.7 to 5.5V (f(X

IN

)=10MH

Z

with software one-wait) : Mask ROM, flash memory 5V version

2.7 to 5.5V (f(X

IN

)=7MH

Z

with software one-wait) : One-time PROM version

∑ Low power consumption ...................... 25.5mW ( f(X

IN

)=10MH

Z

, with software one-wait, V

CC

= 3V)

∑ Interrupts .............................................. 25 internal and 8 external interrupt sources, 4 software

interrupt sources; 7 levels (including key input interrupt)

∑ Multifunction 16-bit timer ...................... 5 output timers + 6 input timers

∑ Serial I/O .............................................. 5 channels (3 for UART or clock synchronous, 2 for clock synchro-

nous)

∑ DMAC .................................................. 2 channels (trigger: 24 sources)

∑ A-D converter ....................................... 10 bits X 8 channels (Expandable up to 10 channels)

∑ D-A converter ....................................... 8 bits X 2 channels

∑ CRC calculation circuit ......................... 1 circuit

∑ Watchdog timer .................................... 1 line

∑ Programmable I/O ............................... 87 lines

∑ Input port ..............................................

_______

1 line (P8

5

shared with NMI pin)

∑ Memory expansion .............................. Available (to 1.2M bytes or 4M bytes)

∑ Chip select output ................................ 4 lines

∑ Clock generating circuit ....................... 2 built-in clock generation circuits

(built-in feedback resistor, and external ceramic or quartz oscillator)

Applications

Audio, cameras, office equipment, communications equipment, portable equipment

Timer ............................................................. 82

Serial I/O ..................................................... 112

A-D Converter ............................................. 152

D-A Converter ............................................. 162

CRC Calculation Circuit .............................. 164

Programmable I/O Ports ............................. 166

Electrical characteristic ............................... 181

Flash memory version ................................. 234

Central Processing Unit (CPU) ..................... 11

Reset ............................................................. 14

Processor Mode ............................................ 27

Clock Generating Circuit ............................... 40

Protection ...................................................... 49

Interrupts ....................................................... 50

Watchdog Timer ............................................ 70

DMAC ........................................................... 72

Mitsubishi microcomputers

M16C / 62 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Description

4

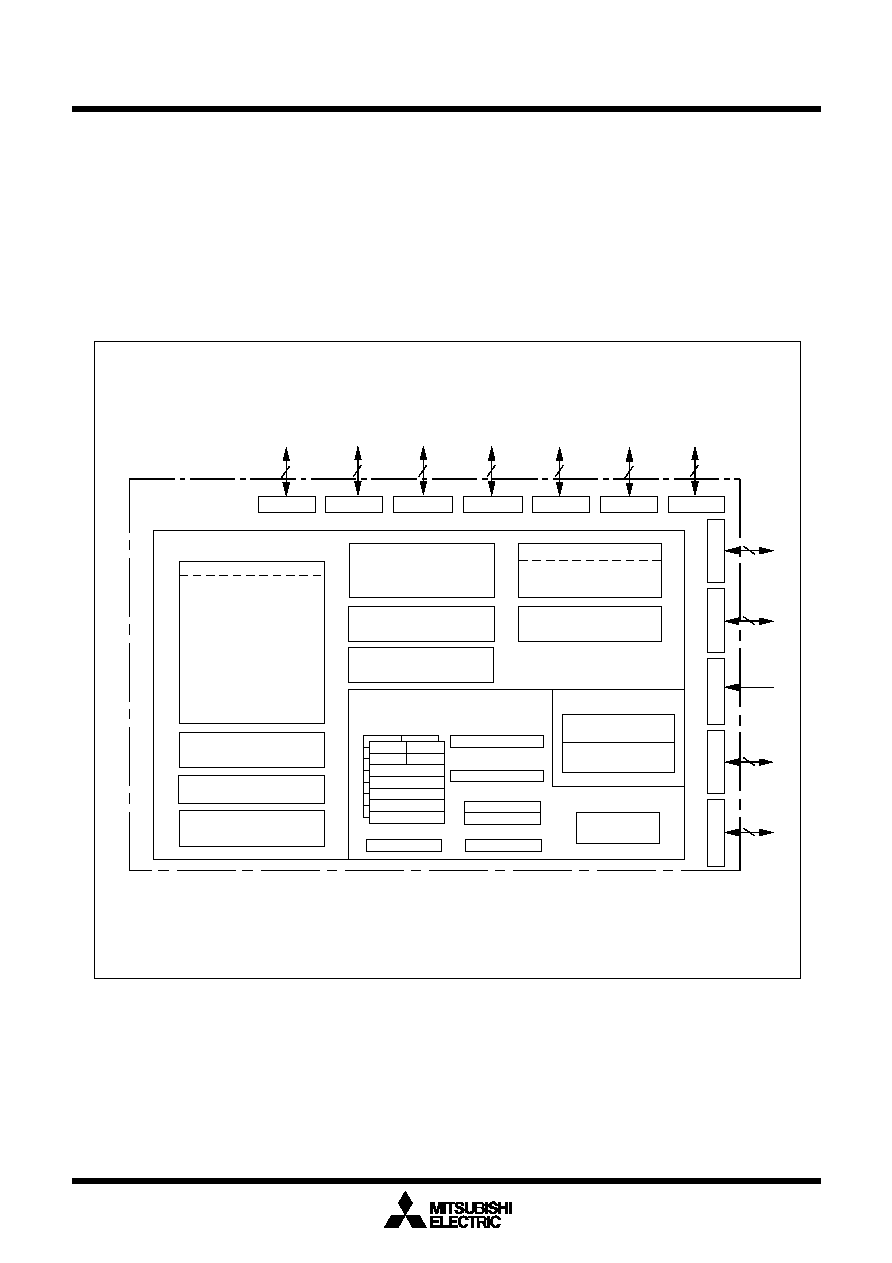

Block Diagram

Figure 1.1.3 is a block diagram of the M16C/62 group.

Block diagram of the M16C/62 group

Timer

Timer TA0 (16 bits)

Timer TA1 (16 bits)

Timer TA2 (16 bits)

Timer TA3 (16 bits)

Timer TA4 (16 bits)

Timer TB0 (16 bits)

Timer TB1 (16 bits)

Timer TB2 (16 bits)

Timer TB3 (16 bits)

Timer TB4 (16 bits)

Timer TB5 (16 bits)

Internal peripheral functions

Watchdog timer

(15 bits)

DMAC

(2 channels)

D-A converter

(8 bits X 2 channels)

A-D converter

(10 bits

X

8 channels

Expandable up to 10 channels)

UART/clock synchronous SI/O

(8 bits

X

3 channels)

System clock generator

X

IN

-X

OUT

X

CIN

-X

COUT

M16C/60 series16-bit CPU core

I/O ports

Port P0

8

Port P1

8

Port P2

8

Port P3

8

Port P4

8

Port P5

8

Port P6

8

8

R0L

R0H

R1H

R1L

R2

R3

A0

A1

FB

R0L

R0H

R1H

R1L

R2

R3

A0

A1

FB

Registers

ISP

USP

Stack pointer

CRC arithmetic circuit (CCITT )

(Polynomial : X

16

+X

12

+X

5

+1)

Multiplier

7

8

8

Port P10

Port P9

Port P8

Port P7

Memory

Port P8

5

ROM

(Note 1)

RAM

(Note 2)

Note 1: ROM size depends on MCU type.

Note 2: RAM size depends on MCU type.

SB

FLG

PC

Program counter

Clock synchronous SI/O

(8 bits

X

2 channels)

Vector table

INTB

Flag register

Figure 1.1.3. Block diagram of M16C/62 group

Mitsubishi microcomputers

M16C / 62 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Description

5

Item

Performance

Number of basic instructions

91 instructions

Shortest instruction execution time

62.5ns(f(X

IN

)=16MH

Z

, V

CC

=5V)

100ns (f(X

IN

)=10MH

Z

, V

CC

=3V, with software one-wait)

: Mask ROM, flash memory 5V version

142.9ns (f(X

IN

)=7MH

Z

, V

CC

=3V, with software one-wait)

: One-time PROM version

Memory

ROM

(See the figure 1.1.4. ROM Expansion)

capacity

RAM

3K to 20K bytes

I/O port

P0 to P10 (except P8

5

)

8 bits x 10, 7 bits x 1

Input port

P8

5

1 bit x 1

Multifunction TA0, TA1, TA2, TA3, TA4

16 bits x 5

timer

TB0, TB1, TB2, TB3, TB4, TB5

16 bits x 6

Serial I/O

UART0, UART1, UART2

(UART or clock synchronous) x 3

SI/O3, SI/O4

(Clock synchronous) x 2

A-D converter

10 bits x (8 + 2) channels

D-A converter

8 bits x 2

DMAC

2 channels (trigger: 24 sources)

CRC calculation circuit

CRC-CCITT

Watchdog timer

15 bits x 1 (with prescaler)

Interrupt

25 internal and 8 external sources, 4 software sources, 7 levels

Clock generating circuit

2 built-in clock generation circuits

(built-in feedback resistor, and external ceramic or quartz oscillator)

Supply voltage

4.2 to 5.5V (f(X

IN

)=16MH

Z

, without software wait)

: Mask ROM, flash memory 5V version

4.5 to 5.5V (f(X

IN

)=16MH

Z

, without software wait)

: One-time PROM version

2.7 to 5.5V (f(X

IN

)=10MH

Z

with software one-wait)

: Mask ROM, flash memory 5V version

2.7 to 5.5V (f(X

IN

)=7MH

Z

with software one-wait)

: One-time PROM version

Power consumption

25.5mW (f(X

IN

) = 10MH

Z

, V

CC

=3V with software one-wait)

I/O

I/O withstand voltage

5V

characteristics Output current

5mA

Memory expansion

Available (to 1.2M bytes or 4M bytes)

Device configuration

CMOS high performance silicon gate

Package

100-pin plastic mold QFP

Table 1.1.1. Performance outline of M16C/62 group

Performance Outline

Table 1.1.1 is a performance outline of M16C/62 group.