MOSEL VITELIC

1

V58C2128(804/404/164)S

HIGH PERFORMANCE

2.5 VOLT 128 Mbit DDR SDRAM

4 BANKS X 4Mbit X 8 (804)

4 BANKS X 2Mbit X 16 (164)

4 BANKS X 8Mbit X 4 (404)

PRELIMINARY

V58C2128(804/404/164)S Rev.1.6 March 2002

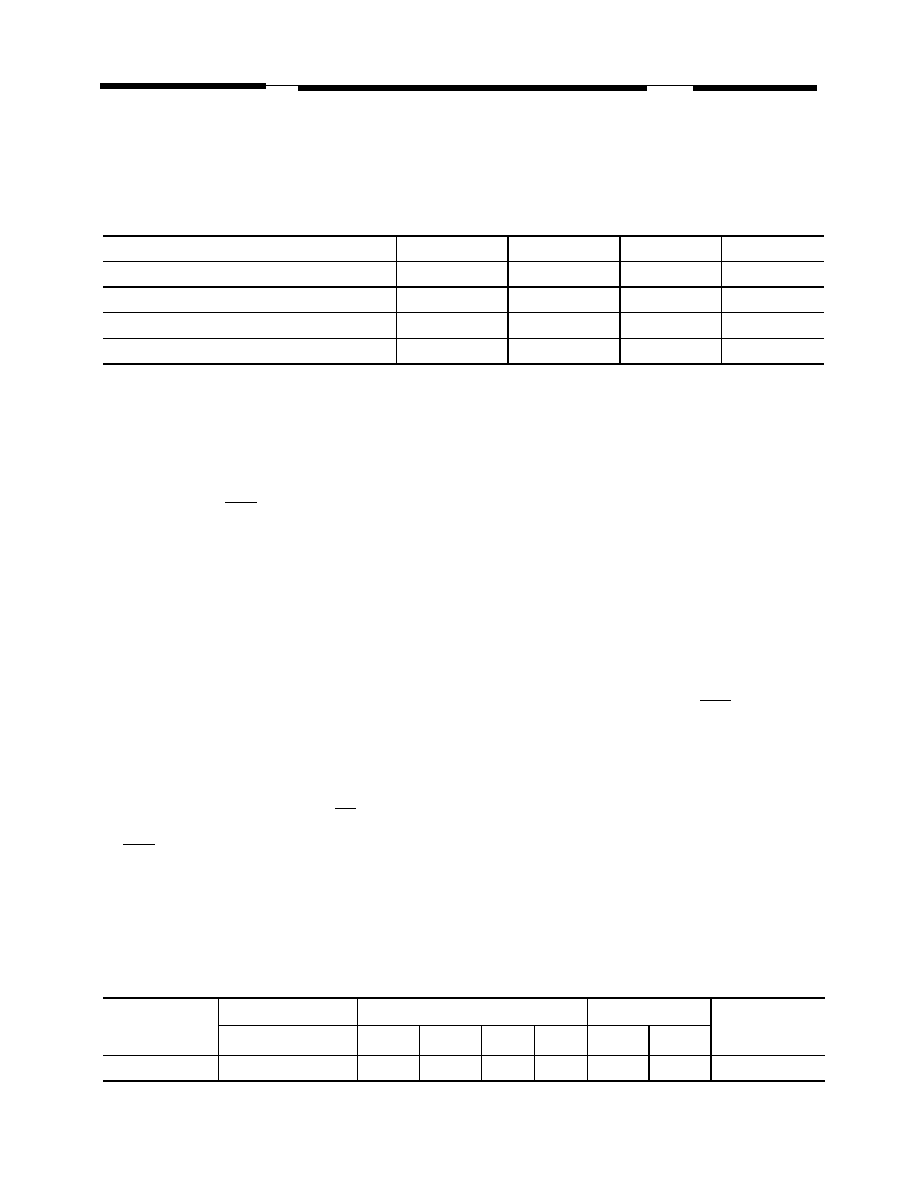

6

7

75

8

DDR333B

DDR266A

DDR266B

DDR200

Clock Cycle Time (t

CK2

)

7.5 ns

7.5ns

10 ns

10 ns

Clock Cycle Time (t

CK2.5

)

6 ns

7ns

7.5 ns

8 ns

System Frequency (f

CK max

)

167 MHz

143 MHz

133 MHz

125 MHz

Features

High speed data transfer rates with system

frequency up to 166 MHz

Data Mask for Write Control

Four Banks controlled by BA0 & BA1

Programmable CAS Latency: 2, 2.5

Programmable Wrap Sequence: Sequential

or Interleave

Programmable Burst Length:

2, 4, 8 for Sequential Type

2, 4, 8 for Interleave Type

Automatic and Controlled Precharge Command

Power Down Mode

Auto Refresh and Self Refresh

Refresh Interval: 4096 cycles/64 ms

Available in 66-pin 400 mil TSOP

SSTL-2 Compatible I/Os

Double Data Rate (DDR)

Bidirectional Data Strobe (DQS) for input and

output data, active on both edges

On-Chip DLL aligns DQ and DQs transitions with

CK transitions

Differential clock inputs CK and CK

Power Supply 2.5V � 0.2V

QFC options for FET control. x4 parts.

*Note: DDR 333B Supports PC2700 module with 2.5-3-3 timing

DDR 266A Supports PC2100 module with 2-3-3 timing

DDR 266B Supports PC2100 module with 2.5-3-3 timing

DDR 200 Supports PC1600 module with 2-2-2 timing

Description

The V58C2128(804/404/164)S is a four bank

DDR DRAM organized as 4 banks x 4Mbit x 8 (804),

4 banks x 2Mbit x 16 (404), or 4 banks x 8Mbit x 4

(164). The V58C2128(804/404/164)S achieves high

speed data transfer rates by employing a chip archi-

tecture that prefetches multiple bits and then syn-

chronizes the output data to a system clock.

All of the control, address, circuits are synchro-

nized with the positive edge of an externally sup-

plied clock. I/O transactions are ocurring on both

edges of DQS.

Operating the four memory banks in an inter-

leaved fashion allows random access operation to

occur at a higher rate than is possible with standard

DRAMs. A sequential and gapless data rate is pos-

sible depending on burst length, CAS latency and

speed grade of the device.

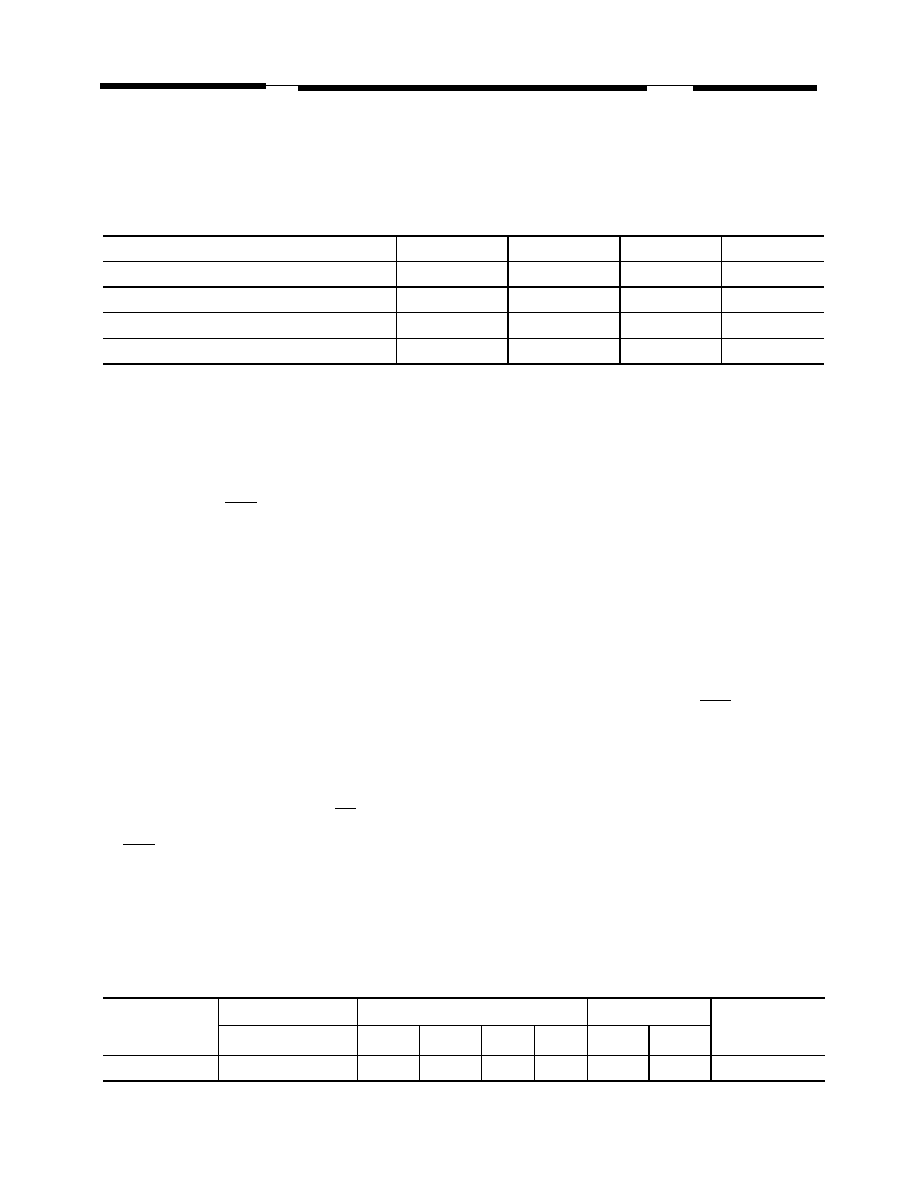

Device Usage Chart

Operating

Temperature

Range

Package Outline

CK Cycle Time (ns)

Power

Temperature

Mark

JEDEC 66 TSOP II

-6

-7

-75

-8

Std.

L

0�C to 70�C

�

�

�

�

�

�

�

Blank

MOSEL VITELIC

V58C2128(804/404/164)S

3

V58C2128(804/404/164)S Rev. 1.6 March 2002

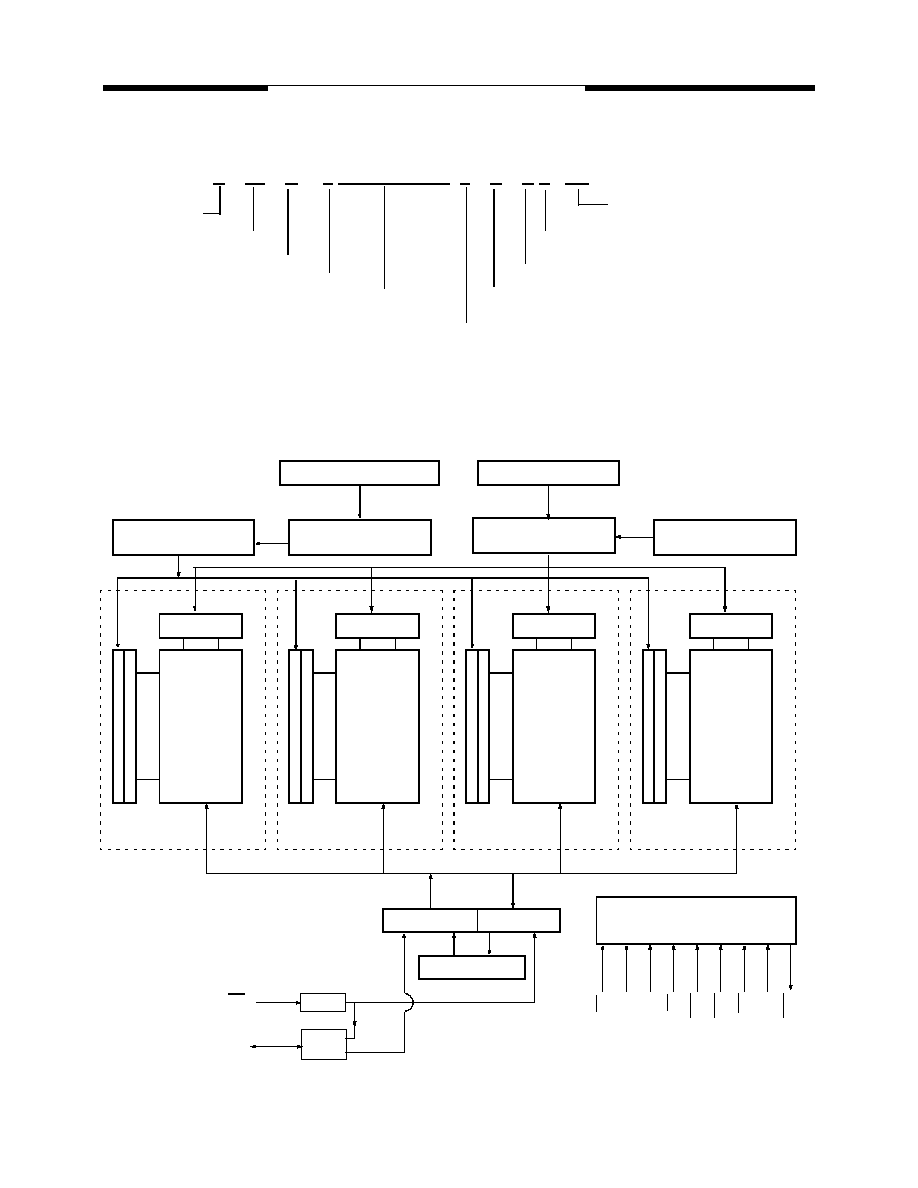

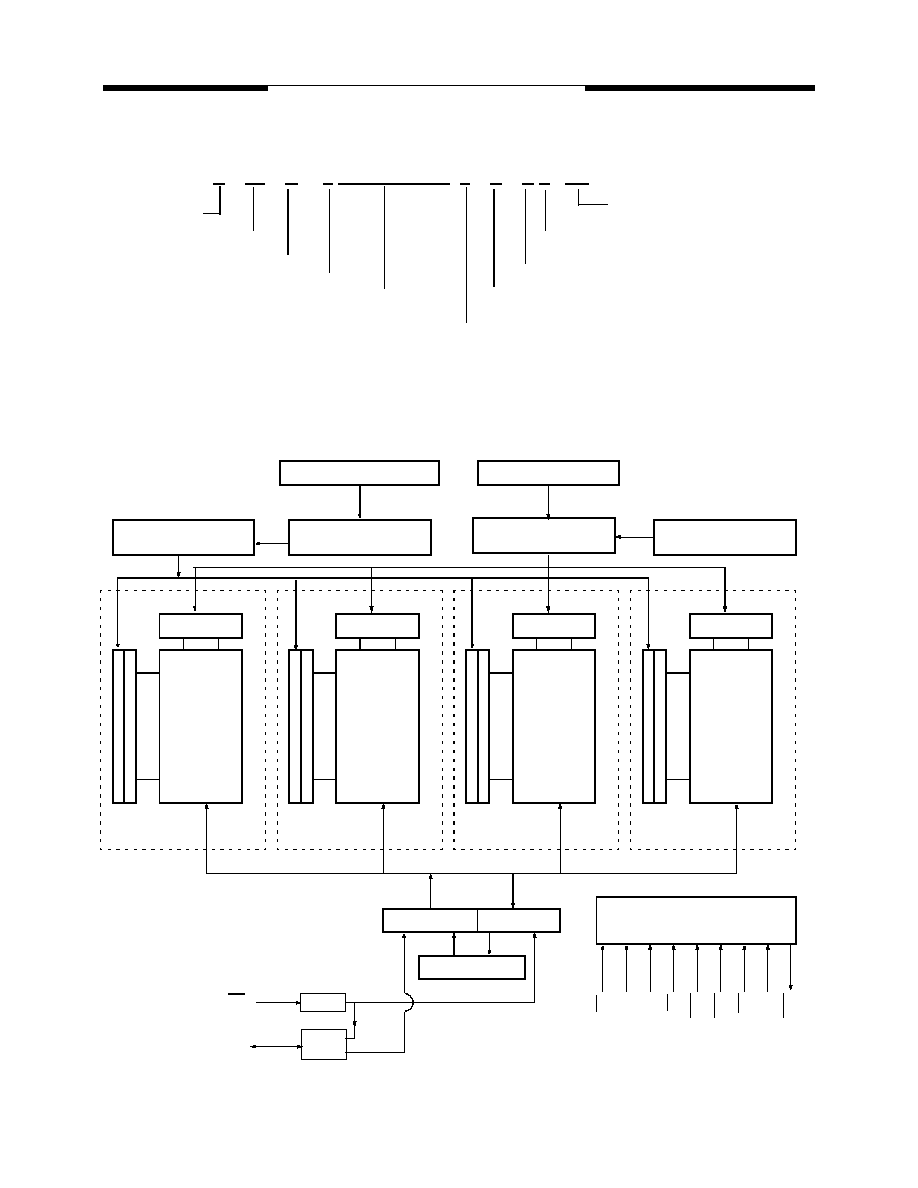

Block Diagram

Row decoder

Memory array

Bank 0

4096 x 1024

x 8

C

o

l

u

m

n

de

c

o

de

r

S

e

n

s

e a

m

pl

i

f

i

e

r

&

I(

O

)

bu

s

Row decoder

Memory array

Bank 1

C

o

l

u

m

n

dec

ode

r

S

ens

e am

pl

i

f

i

e

r

&

I(

O

)

bu

s

Row decoder

Memory array

Bank 2

C

o

l

u

m

n

dec

oder

S

e

n

s

e a

m

pl

i

f

i

e

r

&

I(

O

)

bu

s

Row decoder

Memory array

Bank 3

C

o

l

u

m

n

dec

oder

S

e

ns

e

am

p

l

i

f

i

e

r

&

I

(

O

)

bu

s

Input buffer

Output buffer

DQ

0

-DQ

3

Column address

counter

Column address

buffer

Row address

buffer

Refresh Counter

A0 - A11, BA0, BA1

A0 - A9, A11, AP, BA0, BA1

Control logic & timing generator

CK

CK

E

CS

RA

S

CA

S

WE

DM

Row Addresses

Column Addresses

DLL

Strobe

Gen.

Data Strobe

CK, CK

CK

DQS

QF

C

4096 x 1024

x 8

4096 x 1024

x 8

4096 x 1024

x 8

32M x 4

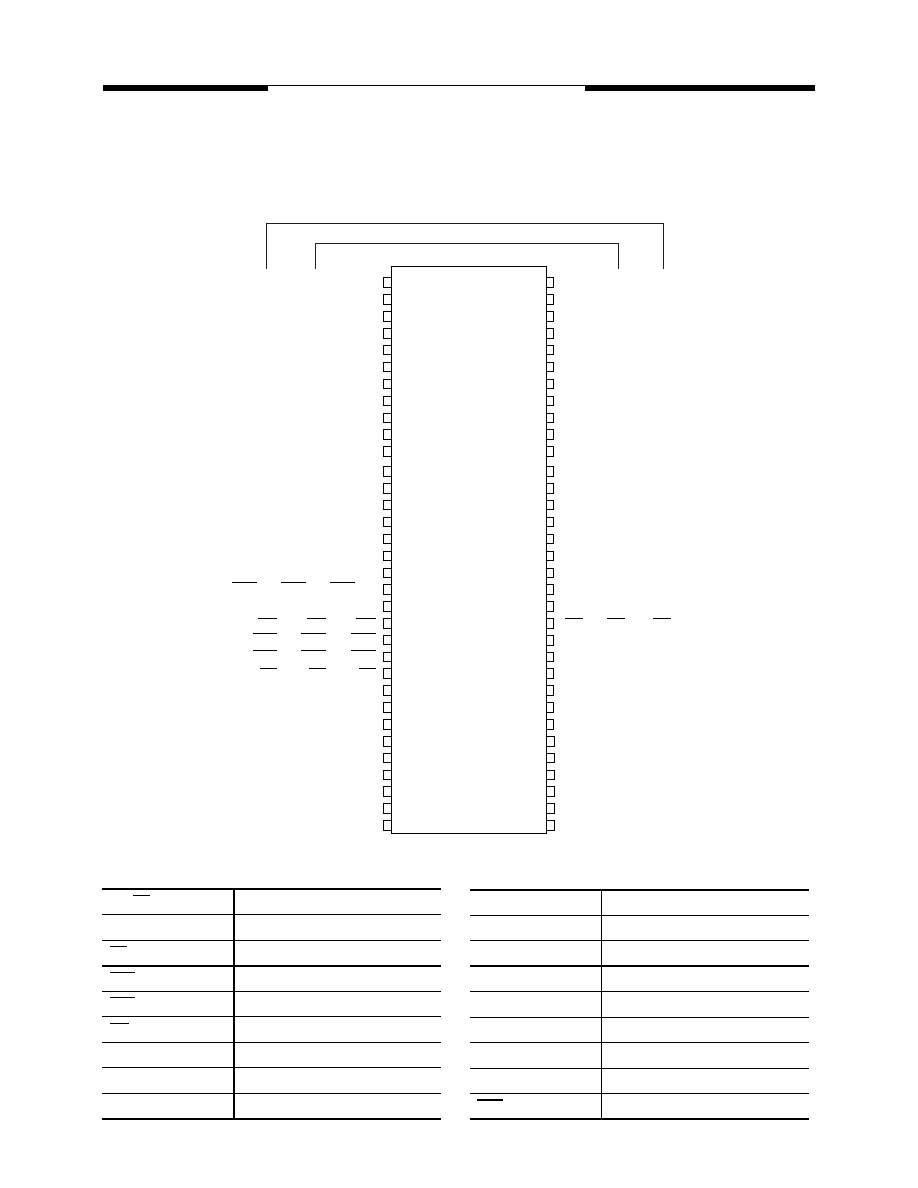

V 58 C 2 128(80/40/16) 4 S X T XX

DDRSDRAM

CMOS

2.5V

128Mb, 4K Refresh

4 Banks

COMPONENT

REV LEVEL

COMPONENT

PACKAGE, T = TSOP

SSTL

SPEED

6 (166MHZ@CL2.5)

MOSEL VITELIC

MANUFACTURED

7 (143MHZ@CL2.5))

75(133MHZ@CL2.5)

x8, x4, x16

8 (125MHZ@CL2.5)

5

MOSEL VITELIC

V58C2128(804/404/164)S

V58C2128(804/404/164)S Rev. 1.6 March 2002

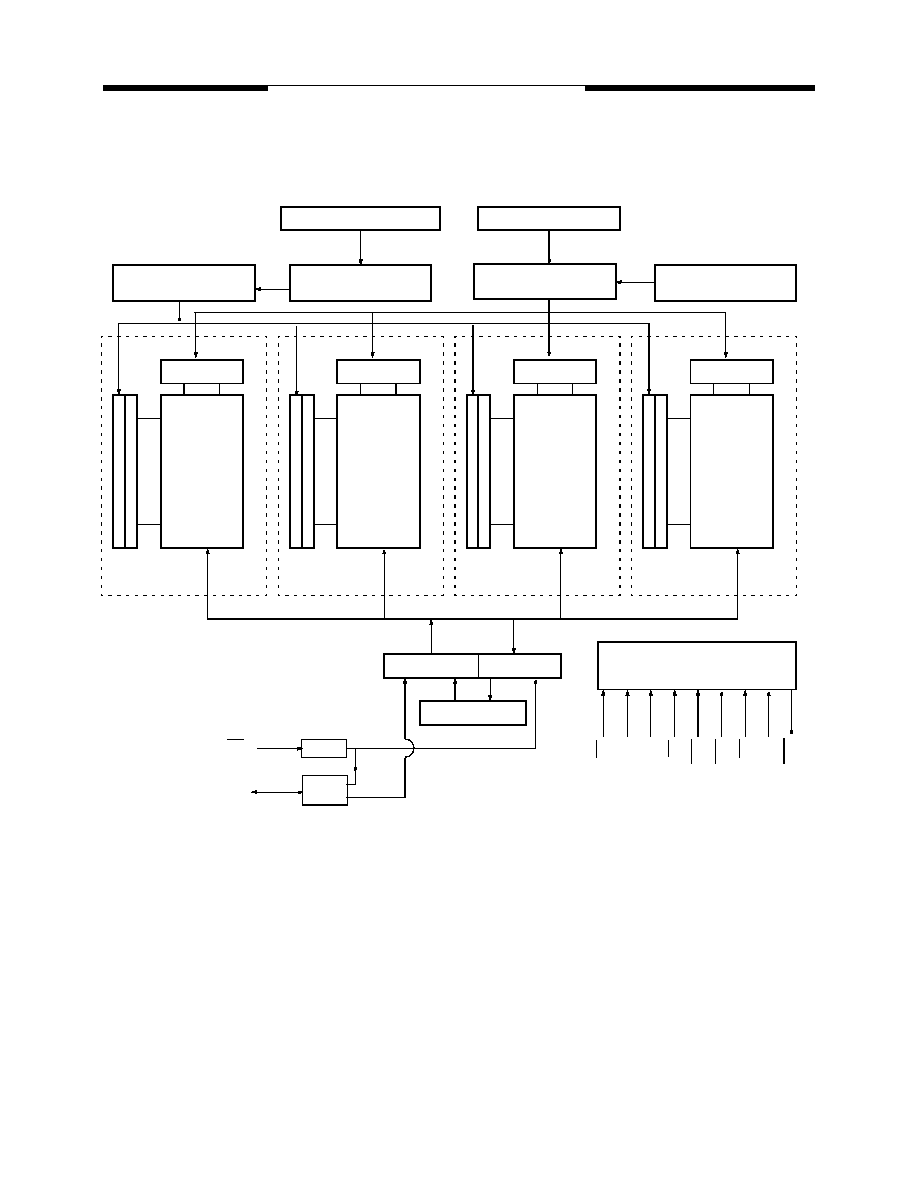

Block Diagram

Row decoder

Memory array

Bank 0

4096 x 256

x 32 bit

C

o

l

u

mn

dec

oder

S

ens

e

ampl

i

f

i

e

r

&

I(

O

)

bus

Row decoder

Memory array

Bank 1

C

o

l

u

mn d

e

c

o

der

S

e

ns

e

ampl

i

f

i

e

r

&

I(

O

)

bus

Row decoder

Memory array

Bank 2

C

o

l

u

m

n

de

c

o

de

r

S

ens

e

ampl

i

f

i

e

r

&

I

(

O

)

bus

Row decoder

Memory array

Bank 3

Co

l

u

m

n

d

e

c

o

d

e

r

S

ens

e ampl

i

f

i

e

r

&

I

(

O

)

bus

Input buffer

Output buffer

DQ

0

-DQ

15

Column address

counter

Column address

buffer

Row address

buffer

Refresh Counter

A0 - A11, BA0, BA1

A0 - A8, AP, BA0, BA1

Control logic & timing generator

CK

CK

E

CS

RA

S

CA

S

WE

DM

Row Addresses

Column Addresses

DLL

Strobe

Gen.

Data Strobe

CK, CK

CK

DQS

QF

C

4096 x 256

x 32 bit

4096 x 256

x 32 bit

4096 x 256

x 32 bit

8M x 16

Capacitance*

T

A

= 0 to 70

�

C, V

CC

= 2.5V

�

0.2V, f = 1 Mhz

*Note: Capacitance is sampled and not 100% tested.

Absolute Maximum Ratings*

Operating temperature range ..................0 to 70 �C

Storage temperature range ................-55 to 150 �C

V

DD

Supply Voltage Relative to V

SS

.....-1V to +3.6V

V

DDQ

Supply Voltage Relative to V

SS

......................................................-1V to +3.6V

VREF and Inputs Voltage Relative to V

SS

......................................................-1V to +3.6V

I/O Pins Voltage Relative to V

SS

.......................................... -0.5V to V

DDQ

+0.5V

Power dissipation .......................................... 1.6 W

Data out current (short circuit) ...................... 50 mA

*Note: Stresses above those listed under "Absolute Maximum

Ratings" may cause permanent damage of the device.

Exposure to absolute maximum rating conditions for

extended periods may affect device reliability.

Input Capacitance

Symbol

Min Max Unit

BA0, BA1, CKE, CS, RAS, (CAS,

A0-A11, WE)

C

INI

2

3.0

pF

Input Capacitance (CK, CK)

C

IN2

2

3.0

pF

Data & DQS I/O Capacitance

C

OUT

4

5

pF

Input Capacitance (DM)

C

IN3

4

5.0

pF