| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: DSP56001 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

- Cover

- Signal Description

- DSP56001 Electrical Characteristics

- Appendix A - Ordering Information

- Appendix B - Application Examples

- Appendix C - MU-Law/A-Law Expansion Tables

- Appendix D - Sine Wave Table

- Appendix E - Bootstrap Mode - Operating Mode 1

24-Bit General Purpose

Digital Signal Processor

The DSP56001 is a member of Motorola's family of

HCMOS, low-power, general purpose Digital Signal

Processors. The DSP56001 features 512 words of full

speed, on-chip program RAM (PRAM) memory, two

256 word data RAMs, two preprogrammed data

ROMs, and special on-chip bootstrap hardware to per-

mit convenient loading of user programs into the pro-

gram RAM. It is an off-the-shelf part since the program

DSP56001

Order this document

by DSP56001/D

This document contains information on a new product. Specifications and information herein are subject to change without notice.

©

MOTOROLA INC., 1992

MOTOROLA

TECHNICAL DATA

SEMICONDUCTOR

memory is user programmable. The core of the processor consists of three execution units operating in parallel -- the data ALU,

the address generation unit, and the program controller. The DSP56001 has MCU-style on-chip peripherals, program and data

memory, as well as a memory expansion port. The MPU-style programming model and instruction set make writing efficient, com-

pact code, straightforward.

The high throughput of the DSP56001 makes it well-suited for communication, high-speed control, numeric processing, computer

and audio applications. The key features which facilitate this throughput are:

Pin Grid Array (PGA)

Available in an 88 pin ceramic

through-hole package.

Ceramic Quad Flat Pack (CQFP)

Available in a 132 pin, small footprint,

surface mount package.

∑

Speed

At 16.5 million instructions per second (MIPS) with a 33 MHz clock, the DSP56001 can execute

a 1024 point complex Fast Fourier Transform in1.98 milliseconds (66,240 clock cycles).

∑

Precision

The data paths are 24 bits wide thereby providing 144 dB of dynamic range; intermediate results

held in the 56-bit accumulators can range over 336 dB.

∑

Parallelism

The data ALU, address arithmetic units, and program controller operate in parallel so that an in-

struction prefetch, a 24x24-bit multiplication, a 56-bit addition, two data moves, and two address

pointer updates using one of three types of arithmetic (linear, modulo, or reverse carry) can be

executed in a single instruction cycle. This parallelism allows a four coefficient Infinite Impulse Re-

sponse (IIR) filter section to be executed in only four cycles, the theoretical minimum for a single

multiplier architecture.

∑

Integration

In addition to the three independent execution units, the DSP56001 has six on-chip memories,

three on-chip MCU style peripherals (Serial Communication Interface, Synchronous Serial Inter-

face, and Host Interface), a clock generator and seven buses (three address and four data), mak-

ing the overall system functionally complete and powerful, but also very low cost, low power, and

compact.

∑

Invisible Pipeline

The three-stage instruction pipeline is essentially invisible to the programmer thus allowing

straightforward program development in either assembly language or a high-level language such

as ANSI C.

∑

Instruction Set

The 62 instruction mnemonics are MCU-like making the transition from programming micropro-

cessors to programming the DSP56001 digital signal processor as easy as possible. The orthog-

onal syntax supports control of the parallel execution units. This syntax provides 12,808,830 dif-

ferent instruction variations using the 62 instruction mnemonics. The no-overhead DO instruction

and the REPEAT (REP) instruction make writing straight-line code obsolete.

∑

DSP56000/DSP56001

The DSP56001 is identical to the DSP56000 except that it has 512x24-bits of on-chip program

RAM instead of 3.75K of program ROM; a 32x24-bit bootstrap ROM for loading the program RAM

from either a byte-wide memory mapped ROM or via the Host Interface; and the on-chip X and Y

Data ROMs have been preprogrammed as positive Mu- and A-Law to linear expansion tables and

a full, four quadrant sine wave table, respectively.

∑

Low Power

As a CMOS part, the DSP56001 is inherently very low power; however, three other features can

reduce power consumption to an exceptionally low level.

-- The WAIT instruction shuts off the clock in the central processor portion of the DSP56001.

-- The STOP instruction halts the internal oscillator.

-- Power increases linearly (approximately) with frequency; thus, reducing the clock frequency

reduces power consumption.

Compatibility

Plastic Quad Flat Pack (PQFP)

Available in a 132 pin, small footprint,

surface mount package.

Rev. 3

May 4, 1998

2

DSP56001

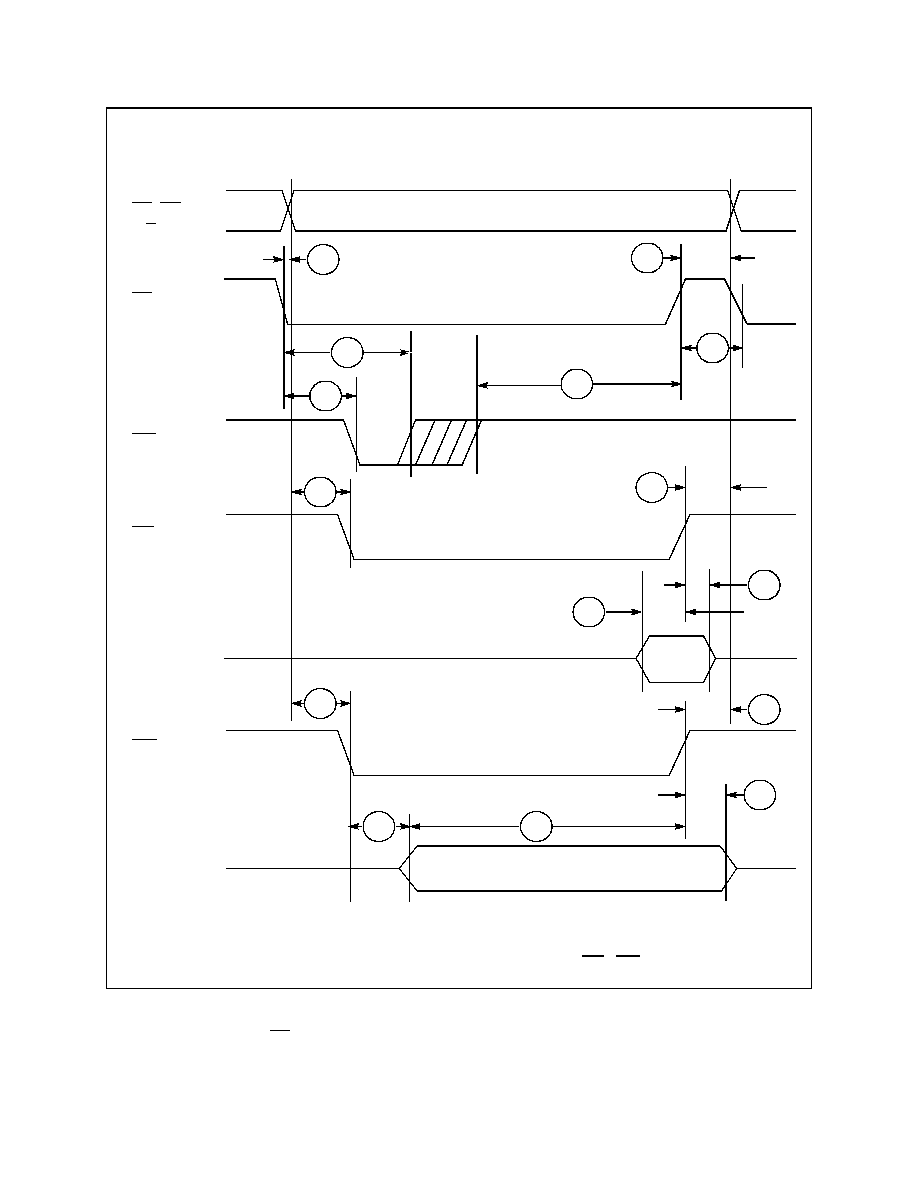

MOTOROLA

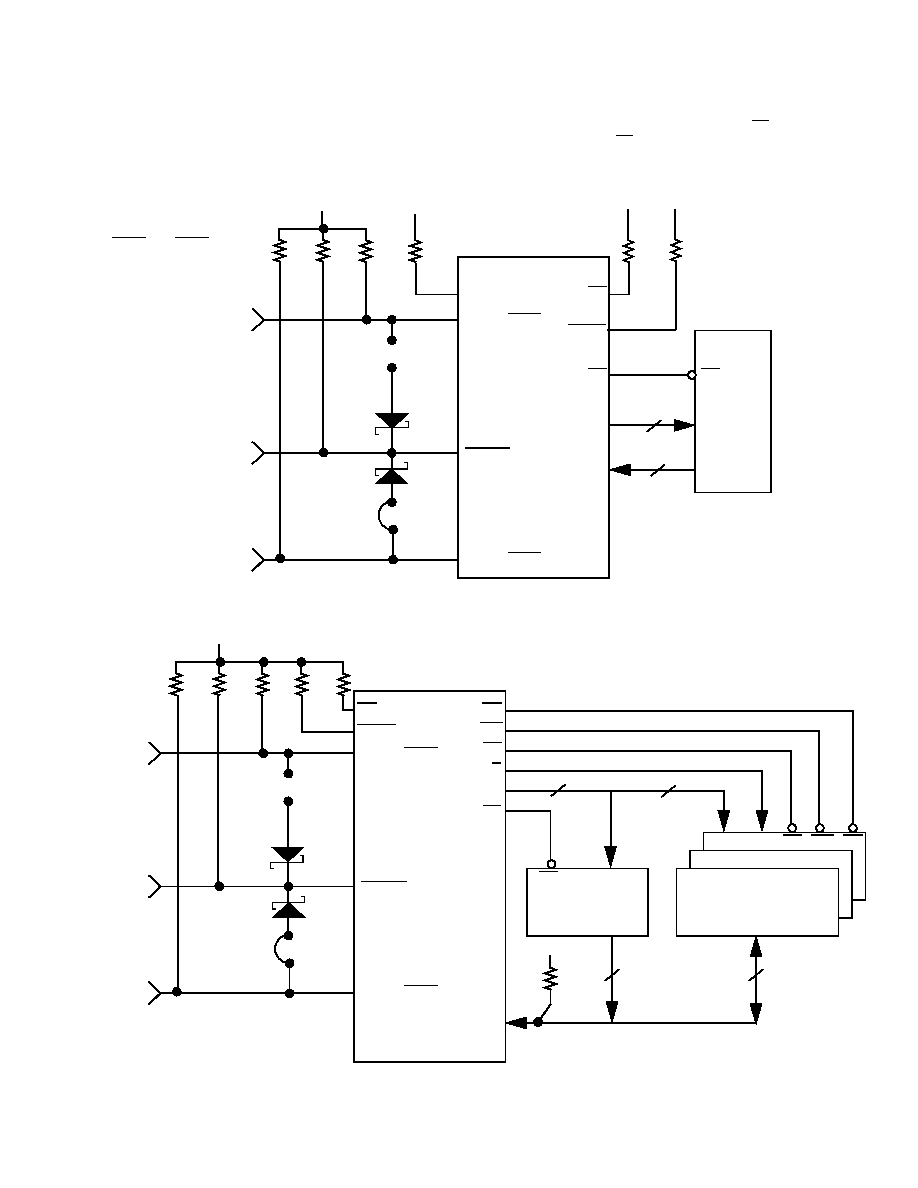

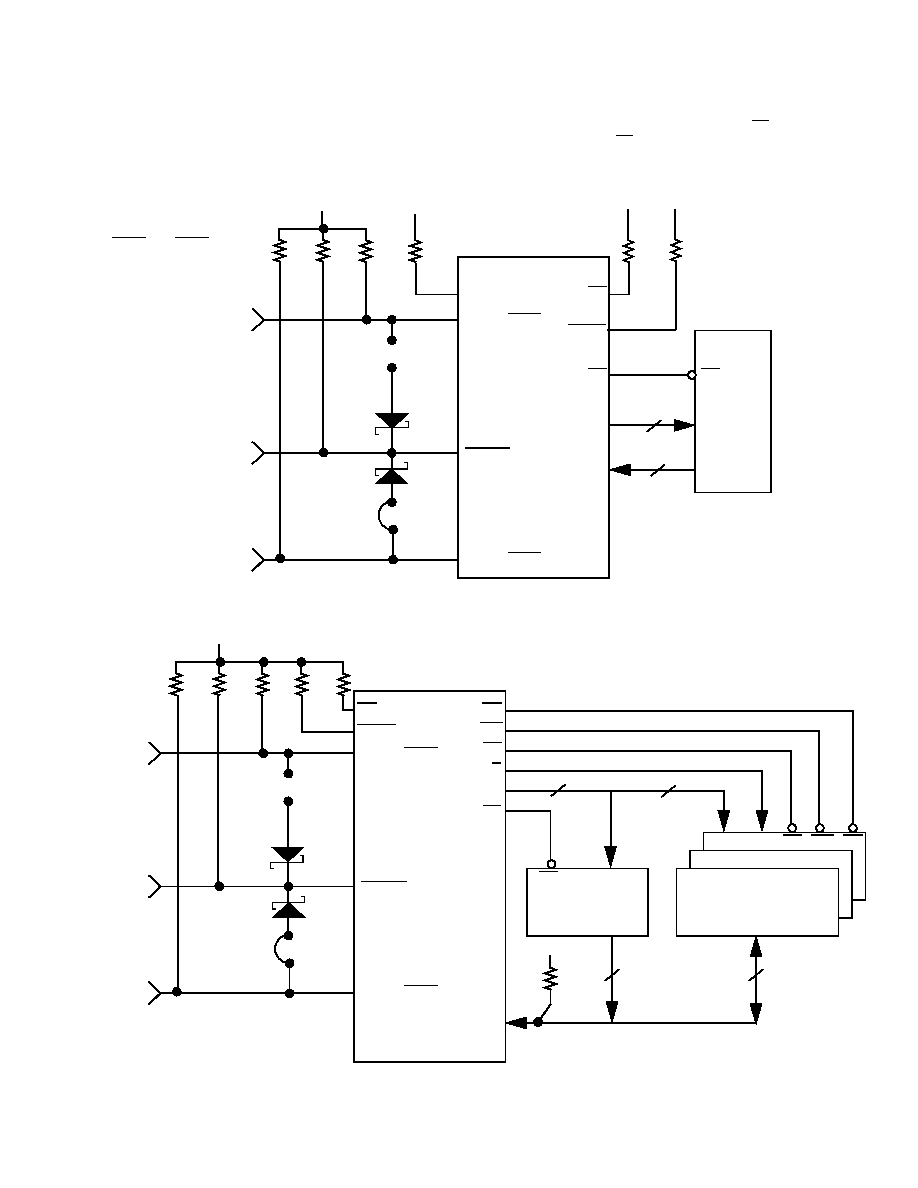

15

9

PORT B

OR HOST

PORT C

AND/OR

SSI, SCI

ADDRESS

GENERATION

UNIT

ON-CHIP

PERIPHERALS:

HOST, SSI,

SCI, PI/O

INTERNAL DATA

BUS SWITCH

AND BIT

MANIPULATION

UNIT

CLOCK

GENERATOR

EXTAL

XTAL

BOOTSTRAP

ROM

32X24

PROGRAM

RAM

512X24

X MEMORY

RAM

256X24

µ

/A ROM

256X24

Y MEMORY

RAM

256X24

SINE ROM

256X24

PROGRAM

ADDRESS

GENERATOR

PROGRAM

DECODE

CONTROLLER

PROGRAM

INTERRUPT

CONTROLLER

YAB

XAB

PAB

YDB

XDB

PDB

GDB

MODB/IRQB

MODA/IRQA

RESET

DATA ALU

24X24+56

56-BIT MAC

TWO 56-BIT ACCUMULATORS

EXTERNAL

ADDRESS

BUS

SWITCH

BUS

CONTROL

EXTERNAL

DATA BUS

SWITCH

ADDRESS

7

DATA

16 BITS

24 BITS

PO

R

T

A

Figure 1. DSP56001 Block Diagram

In the USA:

For technical assistance call:

DSP Applications Helpline (512) 891-3230

For availability and literature call your local Motorola Sales Office or Authorized Motorola Distributor.

For free application software and information call the Dr. BuB electronic bulletin board:

9600/4800/2400/1200/300 baud

(512) 891-3771

(8 data bits, no parity, 1 stop)

In Europe, Japan and Asia Pacific

Contact your regional sales office or Motorola distributor.

3

DSP56001

MOTOROLA

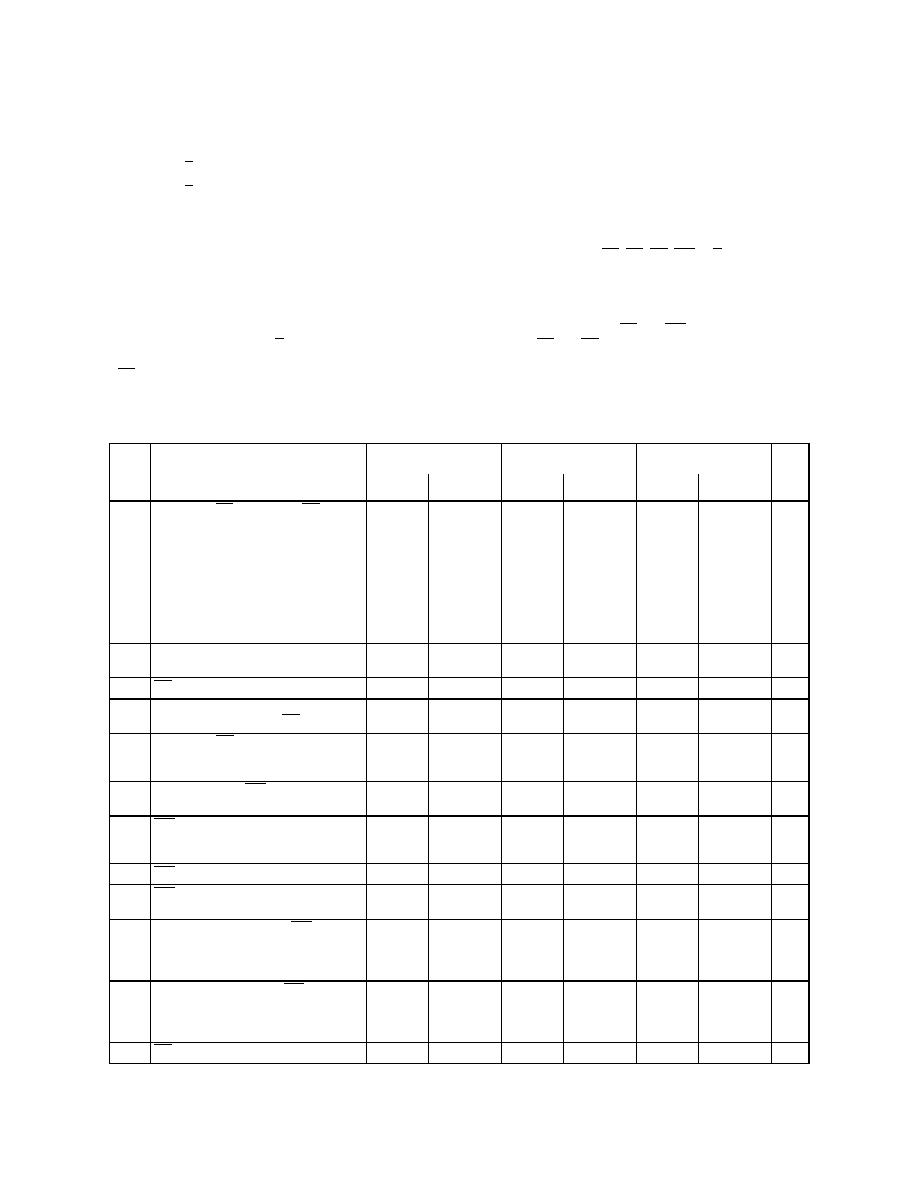

SIGNAL DESCRIPTION

The DSP56001 is available in 132 pin surface mount (CQFP and

PQFP) or an 88-pin pin-grid array packaging. Its input and output sig-

nals are organized into seven functional groups which are listed below

and shown in Figure 1.

Port A Address and Data Buses

Port A Bus Control

Interrupt and Mode Control

Power and Clock

Host Interface or Port B I/O

Serial Communications Interface or Port C I/O

Synchronous Serial Interface or Port C I/O

PORT A ADDRESS AND DATA BUS

Address Bus (A0-A15)

These three-state output pins specify the address for external program

and data memory accesses. To minimize power dissipation, A0-A15

do not change state when external memory spaces are not being ac-

cessed.

Data Bus (D0-D23)

These pins provide the bidirectional data bus for external program and

data memory accesses. D0-D23 are in the high-impedance state when

the bus grant signal is asserted.

PORT A BUS CONTROL

Program Memory Select (PS)

This three-state output is asserted only when external program mem-

ory is referenced. This pin is three-stated during RESET.

Data Memory Select (DS)

This three-state output is asserted only when external data memory is

referenced. This pin is three-stated during RESET.

X/Y Select (X/Y)

This three-state output selects which external data memory space (X

or Y) is referenced by data memory select (DS). This pin is three-stat-

ed during RESET.

Read Enable (RD)

This three-state output is asserted to read external memory on the

data bus D0-D23. This pin is three-stated during RESET.

Write Enable (WR)

This three-state output is asserted to write external memory on the

data bus D0-D23. This pin is three-stated during RESET.

Bus Request (BR/WT)

The bus request input BR allows another device such as a processor

or DMA controller to become the master of external data bus D0-D23

and external address bus A0-A15. When operating mode register

(OMR) bit 7 is clear and BR is asserted, the DSP56001 will always re-

lease the external data bus D0-D23, address bus A0-A15, and bus

control pins PS, DS, X/Y, RD, and WR (i. e., Port A), by placing these

pins in the high-impedance state after execution of the current instruc-

tion has been completed. The BR pin should be pulled up when not

in use.

If OMR bit 7 is set, this pin is an input that allows an external device to

force wait states during an external Port A operation for as long as WT

is asserted.

Bus Grant (BG/BS)

If OMR bit 7 is clear, this output is asserted to acknowledge an external

bus request after Port A has been released. If OMR bit 7 is set, this pin

is bus strobe and is asserted when the DSP accesses Port A. This pin

is three-stated during RESET.

INTERRUPT AND MODE CONTROL

Mode Select A/External Interrupt Request A (MODA/IRQA),

Mode Select B/External Interrupt Request B (MODB/IRQB)

These two inputs have dual functions: 1) to select the initial chip oper-

ating mode and 2) to receive an interrupt request from an external

source. MODA and MODB are read and internally latched in the DSP

when the processor exits the RESET state. Therefore these two pins

should be forced into the proper state during reset. After leaving the

RESET state, the MODA and MODB pins automatically change to ex-

ternal interrupt requests IRQA and IRQB. After leaving the reset state

the chip operating mode can be changed by software. IRQA and IRQB

may be programmed to be level sensitive or negative edge triggered.

When edge triggered, triggering occurs at a voltage level and is not di-

rectly related to the fall time of the interrupt signal, however, the prob-

ability of noise on IRQA or IRQB generating multiple interrupts increas-

es with increasing fall time of the interrupt signal. These pins are inputs

during RESET.

Reset (RESET)

This Schmitt trigger input pin is used to reset the DSP56001. When

RESET is asserted, the DSP56001 is initialized and placed in the reset

state. When the RESET signal is deasserted, the initial chip operating

mode is latched from the MODA and MODB pins. When coming out of

reset, deassertion occurs at a voltage level and is not directly related

to the rise time of the reset signal; however, the probability of noise on

RESET generating multiple resets increases with increasing rise time

of the reset signal.

POWER AND CLOCK

Power (Vcc), Ground (GND)

There are five sets of power and ground pins used for the four groups

of logic on the chip, two pairs for internal logic, one power and two

ground for Port A address and control pins, one power and two ground

for Port A data pins, and one pair for peripherals. Refer to the pin as-

signments in the LAYOUT PRACTICES section.

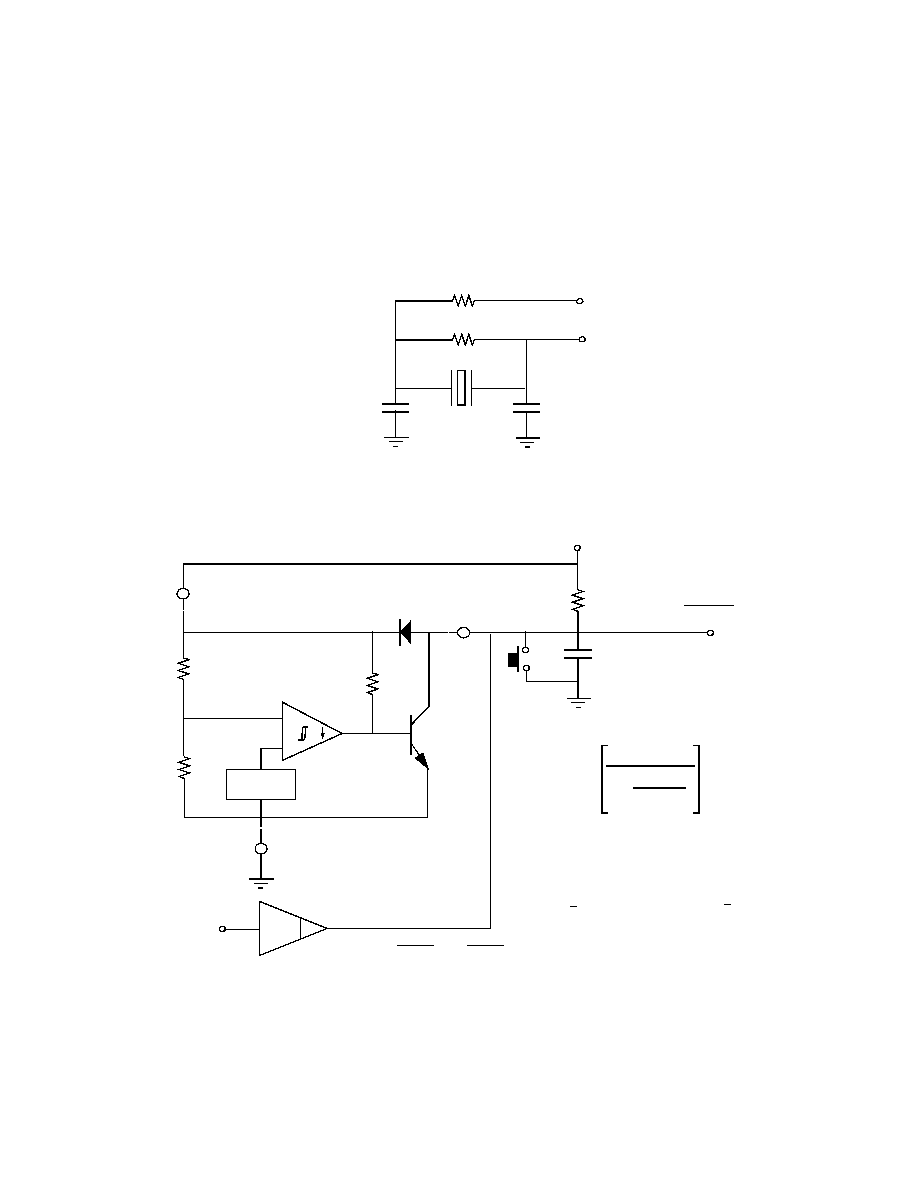

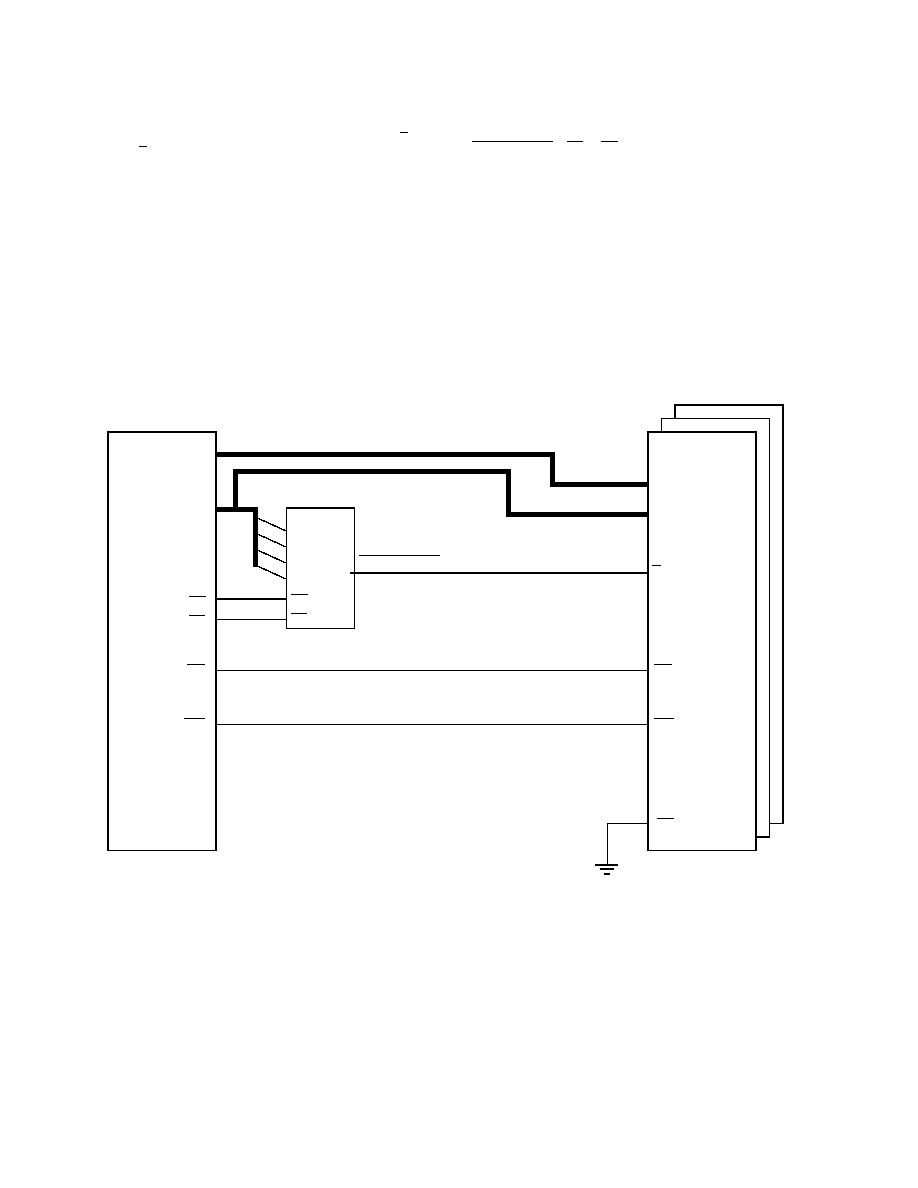

PORT A

PORT B

PORT C

HOST CONTROL

RXD

TXD

SCLK

SC0

SC1

SCK

SRD

STD

A0-A15

D0-D23

PS

DS

RD

WR

X/Y

BR/WT

BG/BS

H0

-

H

7

HA

0

HA

1

HA

2

HR/W

HE

N

HRE

Q

HA

CK

HOST DATA

BUS

VSS

VDD

XT

AL

EX

T

A

L

RES

E

T

MO

D

B

/

IRQB

MO

D

A

/

IRQA

BUS

CONTROL

ADDRESS

DATA

DSP56001

Figure 2. Functional Signal Groups

SCI

SSI

4

DSP56001

MOTOROLA

External Clock/Crystal Input (EXTAL)

EXTAL may be used to interface the crystal oscillator input to an exter-

nal crystal or an external clock.

Crystal Output (XTAL)

This output connects the internal crystal oscillator output to an external

crystal. If an external clock is used, XTAL should not be connected.

HOST INTERFACE

Host Data Bus (H0-H7)

This bidirectional data bus is used to transfer data between the host

processor and the DSP56001. This bus is an input unless enabled by

a host processor read. H0-H7 may be programmed as general pur-

pose parallel I/O pins called PB0-PB7 when the Host Interface is not

being used. These pins are configured as a GPIO input pins during

hardware reset.

Host Address (HA0-HA2)

These inputs provide the address selection for each Host Interface

register. HA0-HA2 may be programmed as general purpose parallel

I/O pins called PB8-PB10 when the Host Interface is not being used.

These pins are configured as a GPIO input pins during hardware reset.

Host Read/Write (HR/W)

This input selects the direction of data transfer for each host processor

access. HR/W may be programmed as a general purpose I/O pin

called PB11 when the Host Interface is not being used. This pin is con-

figured as a GPIO input pins during hardware reset.

Host Enable (HEN)

This input enables a data transfer on the host data bus. When HEN is

asserted and HR/W is high, H0-H7 become outputs, and DSP56001

data may be read by the host processor, When HEN is asserted and

HR/W is low, H0-H7 become inputs and host data is latched inside the

DSP when HEN is deasserted. Normally a chip select signal, derived

from host address decoding and an enable clock, is used to generate

HEN. HEN may be programmed as a general purpose I/O pin called

PB12 when the Host Interface is not being used. This pin is configured

as a GPIO input pins during hardware reset.

Host Request (HREQ)

This open-drain output signal is used by the DSP56001 Host Interface

to request service from the host processor, DMA controller, or simple

external controller. HREQ may be programmed as a general purpose

I/O pin (not open-drain) called PB13 when the Host interface is not be-

ing used. HREQ should be pulled high when not in use. This pin is con-

figured as a GPIO input pins during hardware reset.

Host Acknowledge (HACK)

This input has two functions: 1) to receive a Host Acknowledge hand-

shake signal for DMA transfers and, 2) to receive a Host Interrupt Ac-

knowledge compatible with MC68000 Family processors. HACK may

be programmed as a general purpose I/O pin called PB14 when the

Host Interface is not being used. This pin is configured as a GPIO input

pins during hardware reset. HACK should be pulled high when not

in use.

SERIAL COMMUNICATIONS INTERFACE (SCI)

Receive Data (RXD)

This input receives byte-oriented data into the SCI Receive Shift Reg-

ister. Input data is sampled on the positive edge of the Receive Clock.

RXD may be programmed as a general purpose I/O pin called PC0

when the SCI is not being used. This pin is configured as a GPIO input

pins during hardware reset.

Transmit Data (TXD)

This output transmits serial data from the SCI Transmit Shift Register.

Data changes on the negative edge of the transmit clock. This output

is stable on the positive edge of the transmit clock. TXD may be pro-

grammed as a general purpose I/O pin called PC1 when the SCI is not

being used. This pin is configured as a GPIO input pins during hard-

ware reset.

SCI Serial Clock (SCLK)

This bidirectional pin provides an input or output clock from which the

transmit and/or receive baud rate is derived in the asynchronous mode

and from which data is transferred in the synchronous mode. SCLK

may be programmed as a general purpose I/O pin called PC2 when

the SCI is not being used. This pin is configured as a GPIO input pins

during hardware reset.

SYNCHRONOUS SERIAL INTERFACE (SSI)

Serial Control Zero (SC0)

This bidirectional pin is used for control by the SSI. SC0 may be pro-

grammed as a general purpose I/O pin called PC3 when the SSI is not

being used. This pin is configured as a GPIO input pins during hard-

ware reset.

Serial Control One (SC1)

This bidirectional pin is used for control by the SSI. SC1 may be pro-

grammed as a general purpose I/O pin called PC4 when the SSI is not

being used. This pin is configured as a GPIO input pins during hard-

ware reset.

Serial Control Two (SC2)

This bidirectional pin is used for control by the SSI. SC2 may be pro-

grammed as a general purpose I/O pin called PC5 when the SSI is not

being used. This pin is configured as a GPIO input pins during hard-

ware reset.

SSI Serial Clock (SCK)

This bidirectional pin provides the serial bit rate clock for the SSI when

only one clock is used. SCK may be programmed as a general pur-

pose I/O pin called PC6 when the SSI is not being used. This pin is

configured as a GPIO input pins during hardware reset.

SSI Receive Data (SRD)

This input pin receives serial data into the SSI Receive Shift Register.

SRD may be programmed as a general purpose I/O pin called PC7

when the SSI is not being used. This pin is configured as a GPIO input

pins during hardware reset.

SSI Transmit Data (STD)

This output pin transmits serial data from the SSI Transmit Shift Reg-

ister. STD may be programmed as a general purpose I/O pin called

PC8 when the SSI is not being used. This pin is configured as a GPIO

input pins during hardware reset.

5

DSP56001

MOTOROLA

DSP56001 Electrical Characteristics

Electrical Specifications

The DSP is fabricated in high density CMOS with TTL compatible inputs and outputs.

Maximum Ratings (V

SS

= 0 Vdc)

Maximum Electrical Ratings

Thermal Characteristics - PGA Package

Thermal Characteristics - CQFP Package

Thermal Characteristics - PQFP Package

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal

precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability

of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either Gnd or Vcc).

Rating

Symbol

Value

Unit

Supply Voltage

Vcc

-0.3 to +7.0

V

All Input Voltages

Vin

V

SS

- 0.5 to Vcc + 0.5

V

Current Drain per Pin

I

10

mA

excluding Vcc and V

SS

Operating Temperature Range

T

J

-40 to +105

∞

C

Storage Temperature

Tstg

-55 to +150

∞

C

Characteristics

Symbol

Value

Rating

Thermal Resistance - Ceramic

Junction to Ambient

JA

27

∞

C/W

Junction to Case (estimated)

JC

6.5

∞

C/W

Characteristics

Symbol

Value

Rating

Thermal Resistance - Ceramic

Junction to Ambient

JA

40

∞

C/W

Junction to Case (estimated)

JC

7.0

∞

C/W

Characteristics

Symbol

Value

Rating

Thermal Resistance - Plastic

Junction to Ambient

JA

38

∞

C/W

Junction to Case (estimated)

JC

13.0

∞

C/W

6

MOTOROLA

DSP56001 Electrical Characteristics

DSP56001

Power Considerations

The average chip-junction temperature, T

J

, in

∞

C can be obtained from:

T

J

= T

A

+ (P

D

◊

JA

)

(1)

Where:

T

A

= Ambient Temperature,

∞

C

JA

= Package Thermal Resistance, Junction-to-Ambient,

∞

C/W

P

D

= P

INT

+ P

I/O

P

INT

= I

CC

◊

Vcc, Watts - Chip Internal Power

P

I/O

= Power Dissipation on Input and Output Pins - User Determined

For most applications P

I/O

<< P

INT

and can be neglected; however, P

I/O

+ P

INT

must not exceed P

d

. An appropriate relationship

between P

D

and T

J

(if P

I/O

is neglected) is:

P

D

= K/(T

J

+ 273

∞

C)

(2)

Solving equations (1) and (2) for K gives:

K = P

D

◊

(T

A

+ 273

∞

C) +

JA

◊

P

D

2

(3)

Where K is a constant pertaining to the particular part. K can be determined from equation (2) by measuring P

D

(at equilibrium) for a

known T

A

. Using this value of K, the values of P

D

and T

J

can be obtained by solving equations (1) and (2) iteratively for any value of

T

A

. The total thermal resistance of a package (

JA

) can be separated into two components,

JC

and C

A

, representing the barrier to

heat flow from the semiconductor junction to the package (case) surface (

JC

) and from the case to the outside ambient (C

A

). These

terms are related by the equation:

JA

=

JC

+ C

A

(4)

JC

is device related and cannot be influenced by the user. However, C

A

is user dependent and can be minimized by such thermal

management techniques as heat sinks, ambient air cooling, and thermal convection. Thus, good thermal management on the part of

the user can significantly reduce C

A

so that

JA

approximately equals

JC

. Substitution of

JC

for

JA

in equation (1) will result in a

lower semiconductor junction temperature. Values for thermal resistance presented in this document, unless estimated, were derived

using the procedure described in Motorola Reliability Report 7843, "Thermal Resistance Measurement Method for MC68XX

Microcomponent Devices", and are provided for design purposes only. Thermal measurements are complex and dependent on

procedure and setup. User-derived values for thermal resistance may differ.

Layout Practices

Each Vcc pin on the DSP56001 should be provided with a low-impedance path to + 5 volts. Each GND pin should likewise be provided

with a low-impedance path to ground. The power supply pins drive four distinct groups of logic on chip. They are:

Power and Ground Connections for PGA

Power and Ground Connections for CQFP and PQFP

G12,C6

G11,B7

Internal Logic supply pins

L8

L6,L9

Address bus output buffer supply pins

G3

D3,J3

Data bus output buffer supply pins

C9

E11

Port B and C output buffer supply pins

Vcc

GND

Function

35, 36, 128, 129 33, 34, 130, 131

Internal Logic supply pins

63, 64

55, 56, 73, 74

Address bus output buffer supply pins

100, 101

90, 91, 111, 112

Data bus output buffer supply pins

12, 13

23, 24

Port B and C output buffer supply pins

Vcc

GND

Function

7

DSP56001

MOTOROLA

DSP56001 Electrical Characteristics

Power and Ground Connections

The Vcc power supply should be bypassed to ground using at least four 0.1 uF by- pass capacitors located either underneath the chip

or as close as possible to the four sides of the package. The capacitor leads and associated printed circuit traces connecting to chip

Vcc and Gnd should be kept to less than 1/2" per capacitor lead. A four-layer board is recommended, employing two inner layers as

Vcc and Gnd planes. All output pins on the DSP56001 have fast rise and fall times -- typically less than 3 ns. with a 10 pf. load. Printed

circuit (PC) trace interconnection length should be minimized in order to minimize undershoot and reflections caused by these fast

output switching times. This recommendation particularly applies to the address and data buses as well as the RD, WR, IRQA, IRQB,

and HEN pins. Maximum PC trace lengths on the order of 6" are recommended. Capacitance calculations should consider all device

loads as well as parasitic capacitances due to the PC traces. Attention to proper PCB layout and bypassing becomes especially critical

in systems with higher capacitive loads because these loads create higher transient currents in the Vcc and GND circuits. Pull up/down

all unused inputs or signals that will be inputs during reset.

Signal Stability

When designing hardware to interface with the Host Interface, it is important to ensure that all signals be clean and free from noise.

Particular attention should be given to the quality of the Host Enable (HEN). All inputs to the port should be stable when HEN is

asserted and should remain stable until HEN has fully returned to the deasserted state. It is important to note that such phenomena

as ground-bounce and cross-talk can inadvertently cause HEN to temporarily rise above V

il max

.

Should this occur without completing

the full logic transition to V

ih min

, the DSP56001 Host Port may not correctly update the port status information which can result in

storing two or more copies of a single down loaded data word. Of course, if a full logic transition occurs, the part will complete a normal

data transfer operation.

8

MOTOROLA

DSP56001 Electrical Characteristics

DSP56001

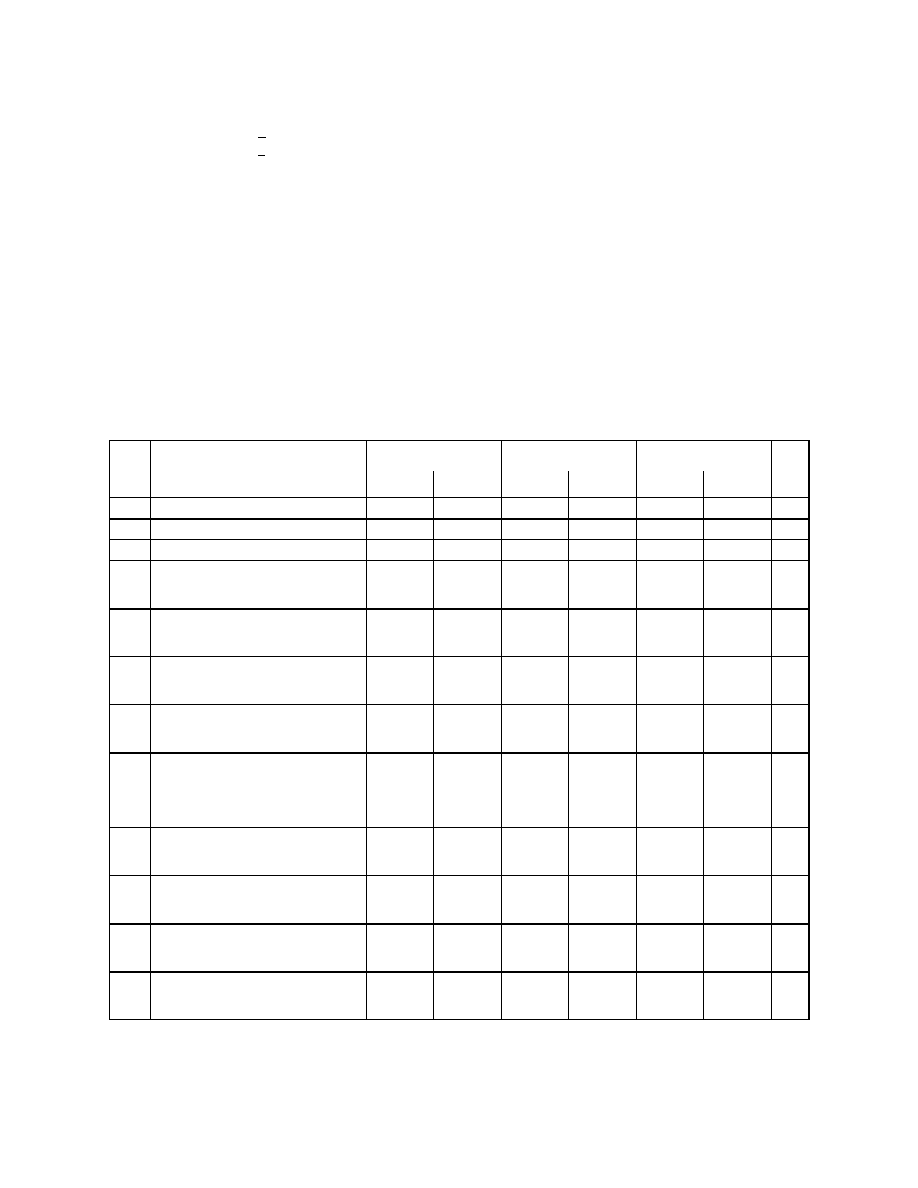

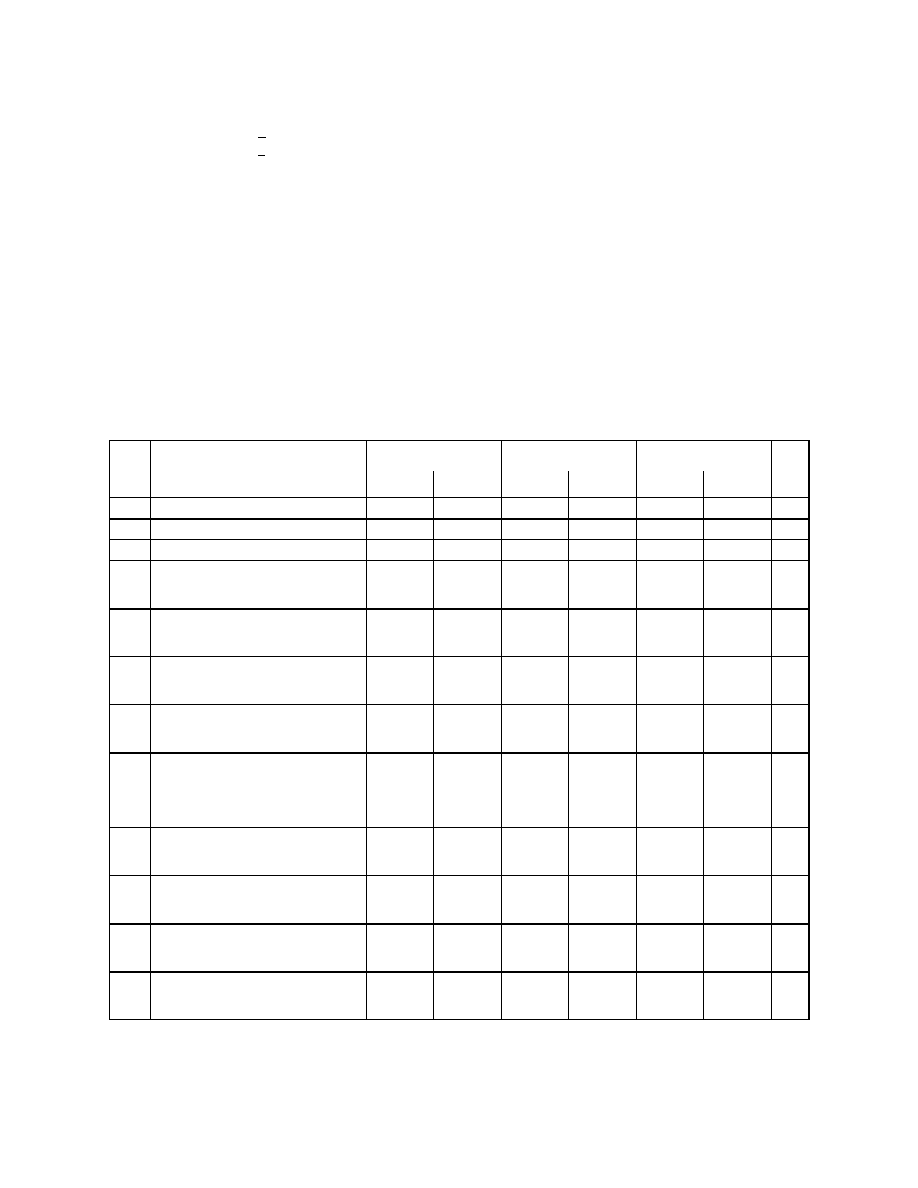

DC Electrical Characteristics (Vcc = 5.0 Vdc + 10%; T

J

= -40 to +105∞ C at 20.5 MHz and 27 MHz)

(Vcc = 5.0 Vdc + 5%; T

J

= -40 to +105∞ C at 33 MHz)

Notes:

1. In order to obtain these results all inputs must be terminated (i.e., not allowed to float).

2. Periodically sampled and not 100% tested.

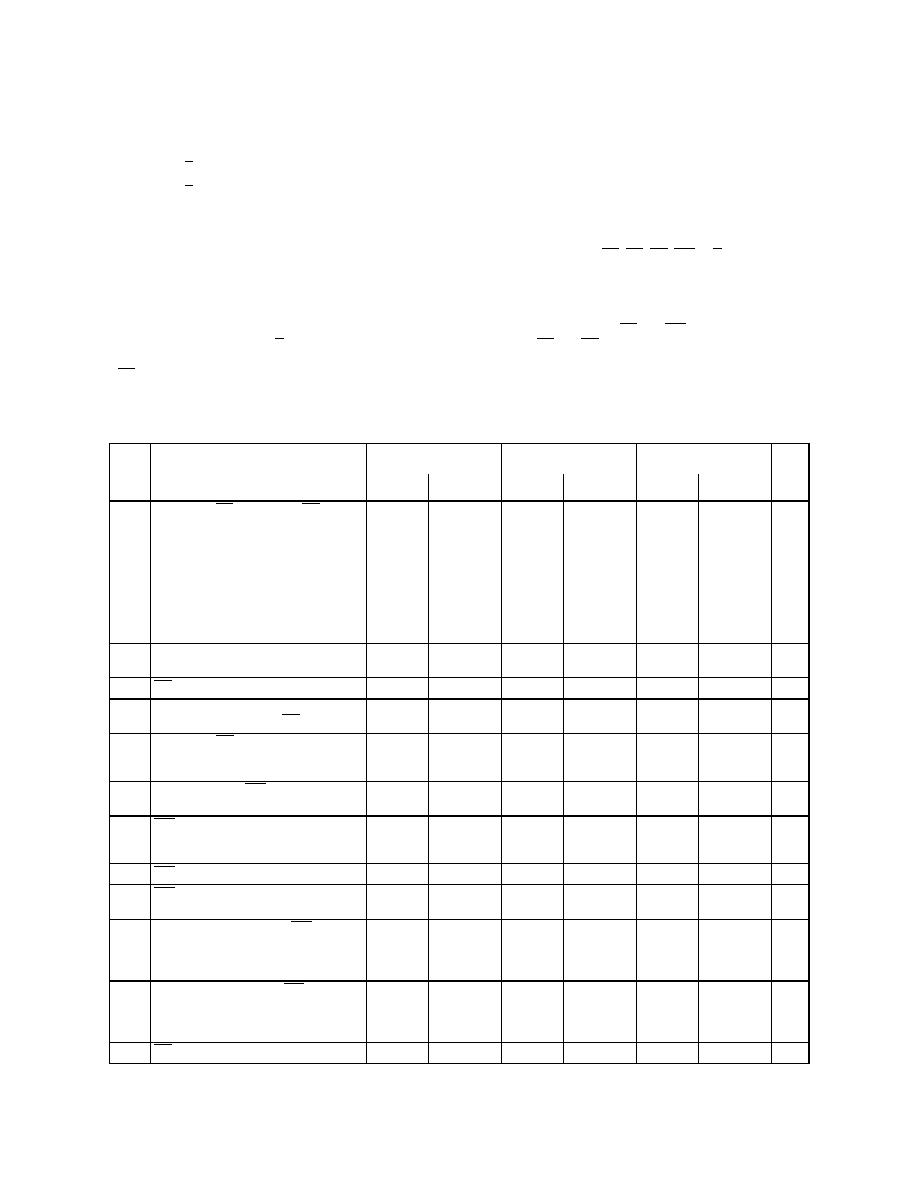

Characteristic

Symbol

Min

Typ

Max

Unit

Supply Voltage 20, 27 MH z

33 MHz

Vcc

4.5

4.75

5.0

5.5

5.25

V

Input High Voltage

Except EXTAL, RESET, MODA/IRQA, MODB/IRQB

V

IH

2.0

--

Vcc

V

Input Low Voltage

Except EXTAL, MODA/IRQA, MODB/IRQB

V

IL

-0.5

--

0.8

V

Input High Voltage EXTAL

V

IHC

4.0

--

Vcc

V

Input Low Voltage EXTAL

V

ILC

-0.5

--

0.6

V

Input High Voltage RESET

V

IHR

2.5

--

Vcc

V

Input High Voltage MODA/IRQA and MODB/IRQB

V

IHM

3.5

--

Vcc

V

Input Low Voltage MODA/IRQA and MODB/IRQB

V

ILM

-0.5

--

2.0

V

Input Leakage Current

EXTAL, RESET, MODA/IRQA, MODB/IRQB, BR

I

in

-1

--

1

uA

Three-State (Off-State) Input Current

(@2.4 V/0.4 V)

I

TSI

-10

--

10

uA

Output High Voltage (I

OH

= -0.4 mA)

V

OH

2.4

--

--

V

Output Low Voltage (I

OL

= 1.6 mA;

RD, WR I

OL

= 1.6 mA; Open Drain

HREQ I

OL

= 6.7 mA, TXD IOL = 6.7 mA)

V

OL

--

--

0.4

V

Total Supply Current 5.25 V, 33 MHz

5 . 5 V, 27 MHz

5 . 5 V, 20 MHz

in WAIT Mode (see Note 1)

in STOP Mode (see Note 1)

I

DD33

I

DD27

I

DD20

I

DDW

I

DDS

--

--

--

--

--

160

130

100

10

100

185

155

115

25

2000

mA

mA

mA

mA

µ

A

Input Capacitance (see Note 2)

Cin

--

10

--

pf

9

DSP56001

MOTOROLA

DSP56001 Electrical Characteristics

AC Electrical Characteristics

The timing waveforms in the AC Electrical Characteristics are tested with a V

IL

maximum of 0.5 V and a V

IH

minimum of 2.4 V for

all pins, except EXTAL, RESET, MODA, and MODB. These four pins are tested using the input levels set forth in the DC Electrical

Characteristics. AC timing specifications which are referenced to a device input signal are measured in production with respect to the

50% point of the respective input signal's transition. DSP56001 output levels are measured with the production test machine V

OL

and

V

OH

reference levels set at 0.8 V and 2.0 V respectively.

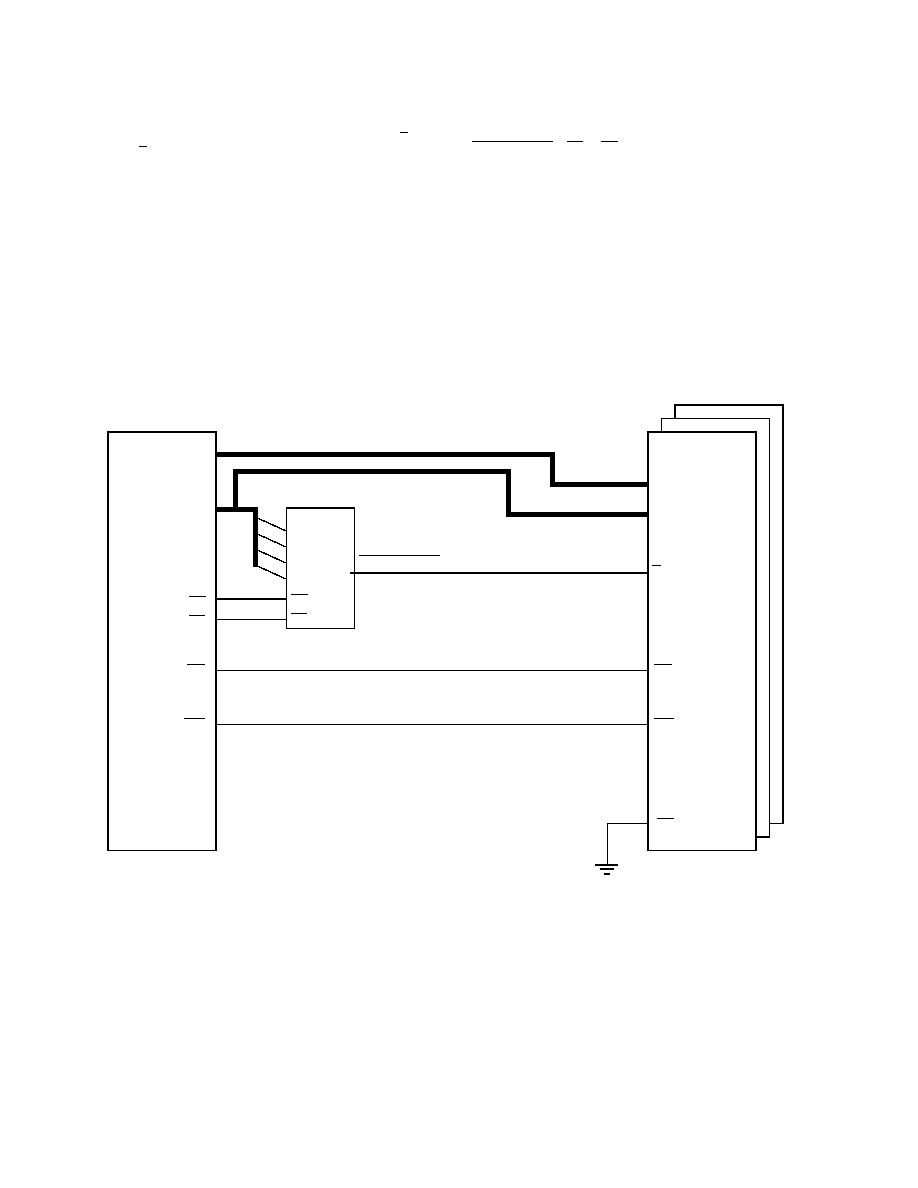

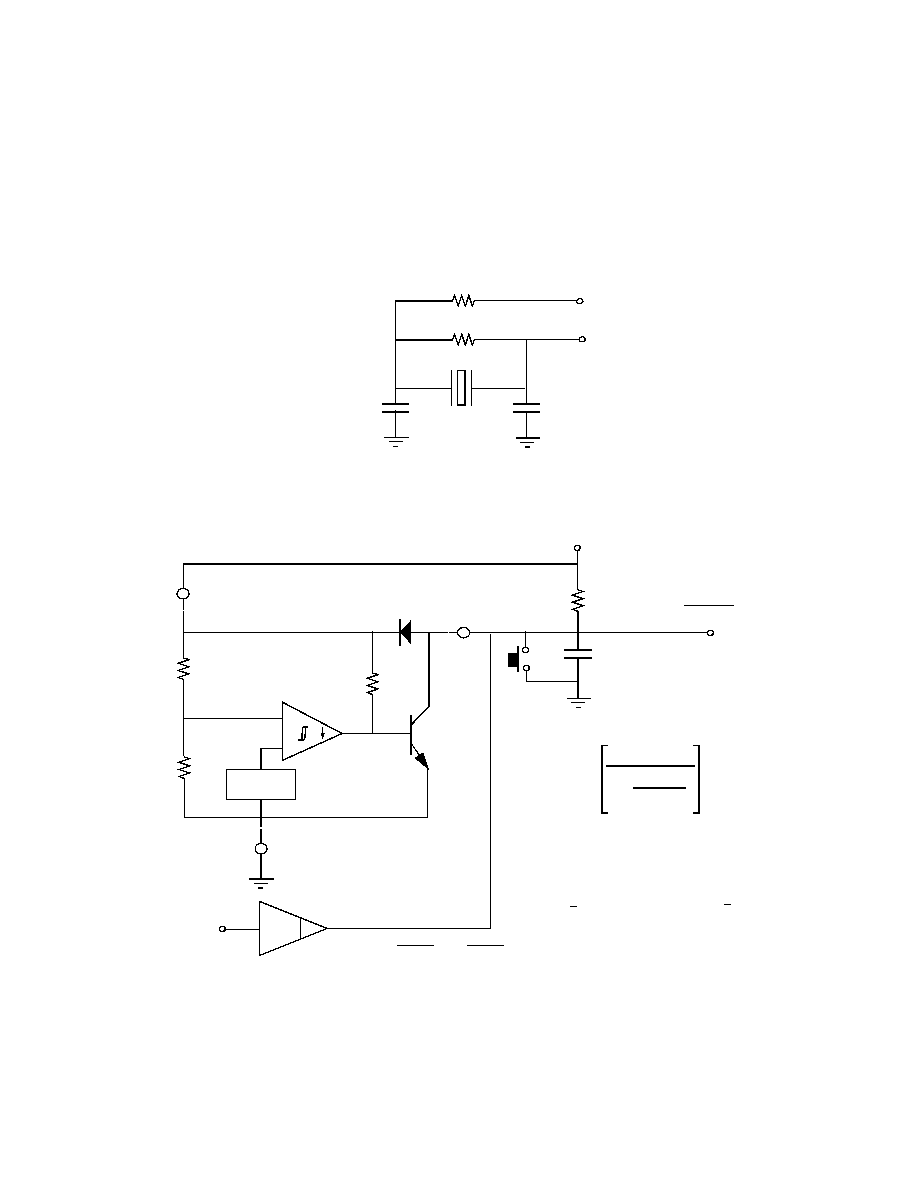

AC Electrical Characteristics - Clock Operation

The DSP56001 system clock may be derived from the on-chip crystal oscillator as shown in Clock Figure 1, or it may be externally

supplied. An externally supplied square wave voltage source should be connected to EXTAL, leaving XTAL physically unconnected

(see Clock Figure 2) to the board or socket. The rise and fall time of this external clock should be 5 ns maximum.

Notes:

1. External Clock Input High and External Clock Input Low are measured at 50% of the

input transition. tch and tcl are dependent on the duty cycle.

2. T = Icyc / 4 is used in the electrical characteristics. T represents an average which is

independent of the duty cycle.

Num

Characteristics

20.5 MHz

27 MHz

33 MHz

Unit

Min

Max

Min

Max

Min

Max

Frequency of Operation (EXTAL Pin)

4.0

20.5

4.0

27.0

4.0

33.0

MHz

1

External Clock Input High (tch) --

EXTAL Pin (see Note 1 and 2)

22

150

17

150

13.5

150

ns

2

External Clock Input Low (tcl) --

EXTAL Pin (see Note 1 and 2)

22

150

17

150

13.5

150

ns

3

Clock Cycle Time = cyc = 2T

48.75

250

37

250

30.33

250

ns

4

Instruction Cycle Time = Icyc = 4T

97.5

500

74

500

60

500

ns

10

MOTOROLA

DSP56001 Electrical Characteristics

DSP56001

Suggested Component Values

For f

osc

= 4 MHz:

R = 680 K

+ 10%

C = 20 pf + 20%

For f

osc

= 30 MHz:

R = 680 K

+ 10%

C = 20 pf + 20%

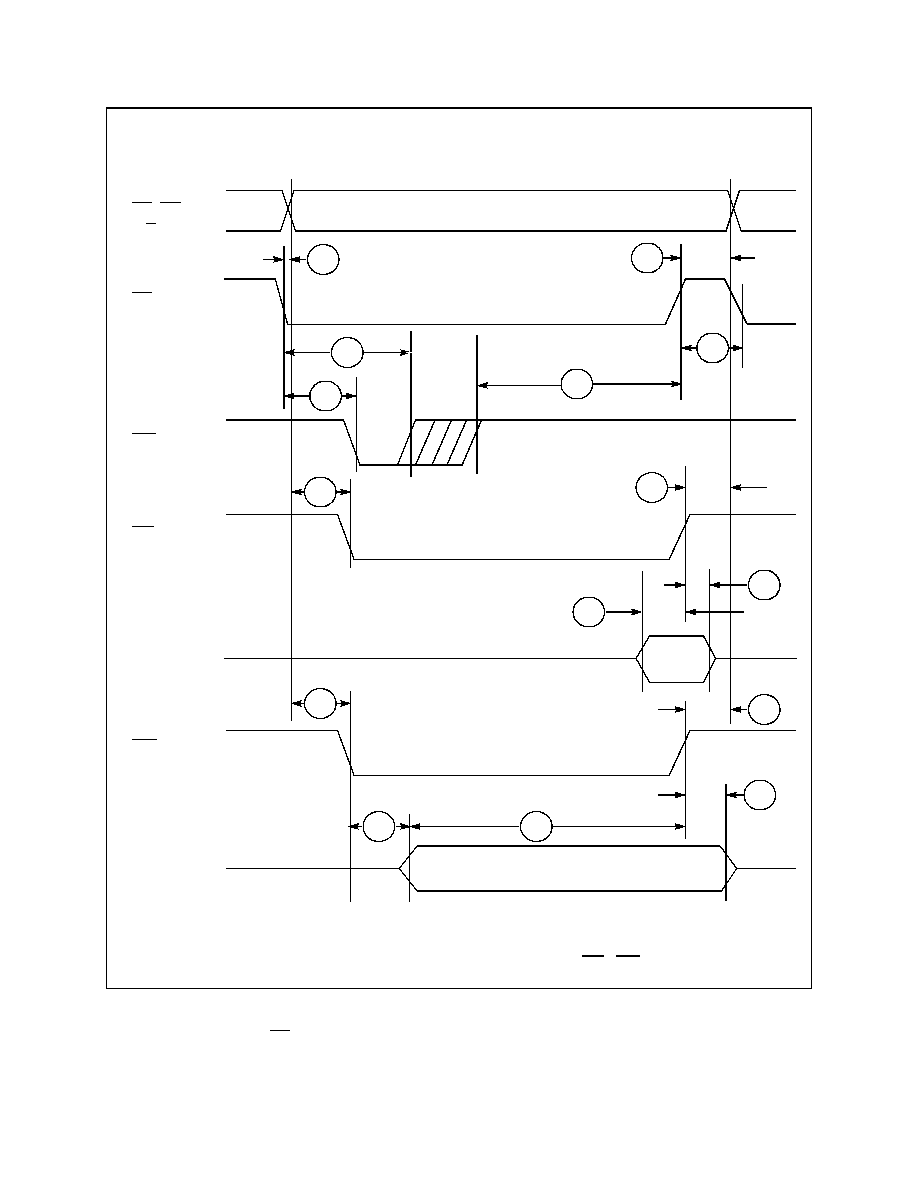

Clock Figure 1. Crystal Oscillator Circuits

XTAL1

∑

∑

∑

∑

C

C

R

Fundamental Frequency

Crystal Oscillator

3

rd

Overtone

Crystal Oscillator

Suggested Component Values

R1 = 470 K

+ 10%

R2 = 330

+ 10%

C1 = 0.1

µ

f + 20%

C2 = 26 pf + 20%

C3 = 20 pf + 10%

L1 = 2.37

µ

H + 10%

XTAL =33 MHz, AT cut, 20 pf load,

5 0

max series resistance

∑

∑

∑

XTAL

EXTAL

∑

R1

C2

C3

XTAL1*

L1

C1

R2

EXTAL

XTAL

Notes:

(1) The suggested crystal source is ICM,

# 433163 - 4.00 (4MHz fundamental, 20

pf load) or # 436163 - 30.00 (30 MHz fun-

damental, 20 pf load).

Notes:

(1) *3

rd

overtone crystal.

(2) The suggested crystal source is ICM, # 471163 - 33.00 (33

MHz 3

rd

overtone, 20 pf load).

(3) R2 limits crystal current

(4) Reference Benjamin Parzen, The Design of Crystal and

Other Harmonic Oscillators, John Wiley& Sons, 1983

EXTAL

V

ILC

V

IHC

Midpoint

1

2

3

4

Clock Figure 2. External Clock Timing

Note: The midpoint is V

ILC

+ 0.5 (V

IHC

- V

ILC

).

11

DSP56001

MOTOROLA

DSP56001 Electrical Characteristics

Num

Characteristics

20.5 MHz

27 MHz

33 MHz

Unit

Min

Max

Min

Max

Min

Max

9

Delay from RESET Assertion to

Address High Impedance (periodically

sampled and not 100% tested)

--

50

--

38

--

31

ns

10

Minimum Stabilization Duration

Internal Osc. (see Note 1)

External Clock (see Note 2)

75000

*

cyc

25

*

cyc

--

--

75000*cyc

25

*

cyc

--

--

75000*cyc

25

*

cyc

--

--

ns

ns

11

Delay from Asynchronous RESET

Deassertion to First External Address

Output (Internal Reset Negation)

8

*

cyc

9

*

cyc+40

8*cyc

9*cyc+31

8*cyc

9*cyc+25

ns

12

Synchronous Reset Setup Time from

RESET Deassertion to Falling Edge of

External Clock

20

cyc-10

15

cyc-8

13

cyc-7

ns

13

Synchronous Reset Delay Time from

the Synchronous Falling Edge of Exter-

nal Clock to the First External Address

Output

8

*

cyc+5

8

*

cyc+30

8*cyc+5

8*cyc+23

8*cyc+5

8*cyc+19

ns

14

Mode Select Setup Time

100

--

77

--

62

--

ns

15

Mode Select Hold Time

0

--

0

0

ns

16

16a

Edge-Triggered Interrupt Request

assertion

deassertion

25

15

--

--

17

10

--

--

16

10

--

--

ns

ns

AC Electrical Characteristics - Reset, Stop, Mode Select and Interrupt Timing

(

Vcc = 5.0 Vdc +10%, T

J

= -40 to +105∞ C, CL = 50 pf + 1 TTL Load at 20.5 MHz and 27 MHz)

(

Vcc = 5.0 Vdc + 5%, T

J

= -40 to +105∞ C, CL = 50 pf + 1 TTL Load at 33 MHz)

(See Control Figure 1 through 8)

cyc = Clock cycle = 1/2 instruction cycle = 2 T cycles

WS = Number of wait states (1 WS = 1 cyc = 2T) programmed into external bus access

using BCR (WS = 0 - 15)

tch = Clock high period

tcl = Clock low period

RESET

A0-A15

9

11

First Fetch

V

IHR

Control Figure 1. Reset Timing

10

12

MOTOROLA

DSP56001 Electrical Characteristics

DSP56001

AC Electrical Characteristics - Reset, Stop, Mode Select, and Interrupt Timing

(Continued)

NOTE

When using fast interrupts and IRQA and IRQB are defined as level-sensitive, then timings 19 through 22 apply

to prevent multiple interrupt service. To avoid these timing restrictions, the negative edge-triggered mode is rec-

ommended when using fast interrupt. Long interrupts are recommended when using level-sensitive mode.

Num

Characteristics

20.5 MHz

27 MHz

33 MHz

Unit

Min

Max

Min

Max

Min

Max

17

Delay from IRQA, IRQB Assertion to

External Memory Access Address Out

Valid Caused by First Interrupt

Instruction Fetch

Instruction Execution

5

*

cyc+tch

9

*

cyc+tch

--

--

5

*

cyc+tch

9

*

cyc+tch

--

--

5

*

cyc+tch

9

*

cyc+tch

--

--

ns

ns

18

Delay from IRQA, IRQB Assertion to

General Purpose Transfer Output Valid

Caused by First Interrupt Instruction

Execution

11+cyc

+tch

--

11

*

cyc

+tch

--

11

*

cyc

+tch

--

ns

19

Delay from Address Output Valid

Caused by First Interrupt Instruction

Execution to Interrupt Request

Deassertion for Level Sensitive Fast

Interrupts

--

2

*

cyc+tcl+

(cyc

*

WS)

-44

--

2

*

cyc+tcl+

(cyc

*

WS)

-34

--

2

*

cyc+tcl+

(cyc

*

WS)

-27

ns

20

Delay from RD Assertion to Interrupt

Request Deassertion for Level

Sensitive Fast Interrupts

--

2

*

cyc+

(cyc

*

WS)

-40

--

2

*

cyc+

(cyc

*

WS)

-31

--

2

*

cyc+

(cyc

*

WS)

-25

ns

21

Delay from WR Assertion to WS=0

Interrupt Request Deassertion for

WS>0 Level Sensitive Fast Interrupts

--

--

2

*

cyc-40

cyc+tcl+

(cyc

*

WS)

-40

--

--

2

*

cyc-31

cyc+tcl+

(cyc

*

WS)

-31

--

--

2

*

cyc-25

cyc+tcl+

(cyc

*

WS)

-25

ns

ns

22

Delay from General-Purpose Output

Valid to Interrupt Request Deassertion

for Level Sensitive Fast Interrupts

- If Second Interrupt Instruction is:

Single Cycle

Two Cycle

--

--

tcl-60

(2

*

cyc)+tcl

-60

--

--

tcl-46

(2

*

cyc)+tcl

-46

--

--

tcl-37

(2

*

cyc)+tcl

-37

ns

ns

13

DSP56001

MOTOROLA

DSP56001 Electrical Characteristics

AC Electrical Characteristics - Reset, Stop, Mode Select, and Interrupt Timing

(Continued)

Notes:

1. A clock stabilization delay is required when using the on-chip crystal oscillator in

two cases:

1) after power-on reset, and

2) when recovering from Stop mode.

During this stabilization period, T will not be constant. Since this stabilization period

varies, a delay of 150,000T is typically allowed to assure that the oscillator is stabilized

before executing programs. While it is possible to set OMR bit 6 = 1 when using

the internal crystal oscillator, it is not recommended and these specifications do not

guarantee timings for that case. See Section 8.5 in the DSP56000/DSP56001 User's Manual for

additional information.

2. Circuit stabilization delay is required during reset when using an external clock in

two cases:

1) after power-on reset, and

2) when recovering from Stop mode.

3. For Revision B silicon, the min and max numbers are 12cyc+Tch+8 and 12cyc+Tch+30, respec-

tively.

4. The minimum is specified for the duration of an edge triggered IRQA interrupt required to recover

from the STOP state without having the IRQA interrupt accepted.

5. Timing #23 is for all IRQx interrupts while timing #24 is only when exiting WAIT.

6. Timing #23 triggers off T1 in the normal state and off T1/T3 when exiting the WAIT state.

7. The timings in the table are for Rev. C parts. The timings for Rev. C parts are shorter by 1 cyc than

the Rev. B parts when OMR6=0

.

Num

Characteristics

20.5 MHz

27 MHz

33 MHz

Unit

Min

Max

Min

Max

Min

Max

23

Synchronous Interrupt Setup Time

from IRQA, IRQB Assertion to the

Synchronous Rising Edge of External

Clock (see Notes 5, 6)

25

cyc-10

19

cyc-8

16

cyc-7

ns

24

Synchronous Interrupt Delay Time

from the Synchronous Rising Edge of

External Clock to the First External

Address Output Valid Caused by the

First Instruction Fetch after Coming out

of Wait State (see Notes 3, 5)

13

*

cyc+

tch+8

13

*

cyc+

tch+30

13

*

cyc+

tch+6

13

*

cyc+

tch+23

13

*

cyc+

tch+5

13

*

cyc+

tch+19

ns

25

Duration for IRQA Assertion to

Recover from Stop State (see Note 4)

25

--

19

--

16

--

ns

26

Delay from IRQA Assertion to Fetch of

First Instruction (for Stop) for

Internal Osc / OMR bit 6 = 0

External Clock / OMR bit 6 = 1

(see Notes 1, 2, and 7)

65545

*

cyc

17

*

cyc

--

--

65545

*

cyc

17

*

cyc

--

--

65545

*

cyc

17

*

cyc

--

--

ns

ns

27

Duration for Level Sensitive IRQA

Assertion to Fetch of First Interrupt

Instruction (for Stop) for

Internal Osc / OMR bit 6 = 0

External Clock / OMR bit 6 = 1

(see Notes 1, 2, and 7)

65533

*

cyc

+tcl

5

*

cyc+tcl

--

--

65533

*

cyc

+tcl

5

*

cyc+tcl

--

--

65533

*

cyc

+tcl

5

*

cyc+tcl

--

--

ns

ns

28

Delay from Level Sensitive IRQA

Assertion to Fetch of First Interrupt

Instruction (for Stop) for

I nternal Osc / OMR bit 6 = 0

External Clock / OMR bit 6 = 1

(see Notes 1, 2, and 7)

65545

*

cyc

17

*

cyc

--

--

65545

*

cyc

17

*

cyc

--

--

65545

*

cyc

17

*

cyc

--

--

ns

ns

14

MOTOROLA

DSP56001 Electrical Characteristics

DSP56001

EXTAL

RESET

A0-A15,

DS, PS

X/Y

13

11

12

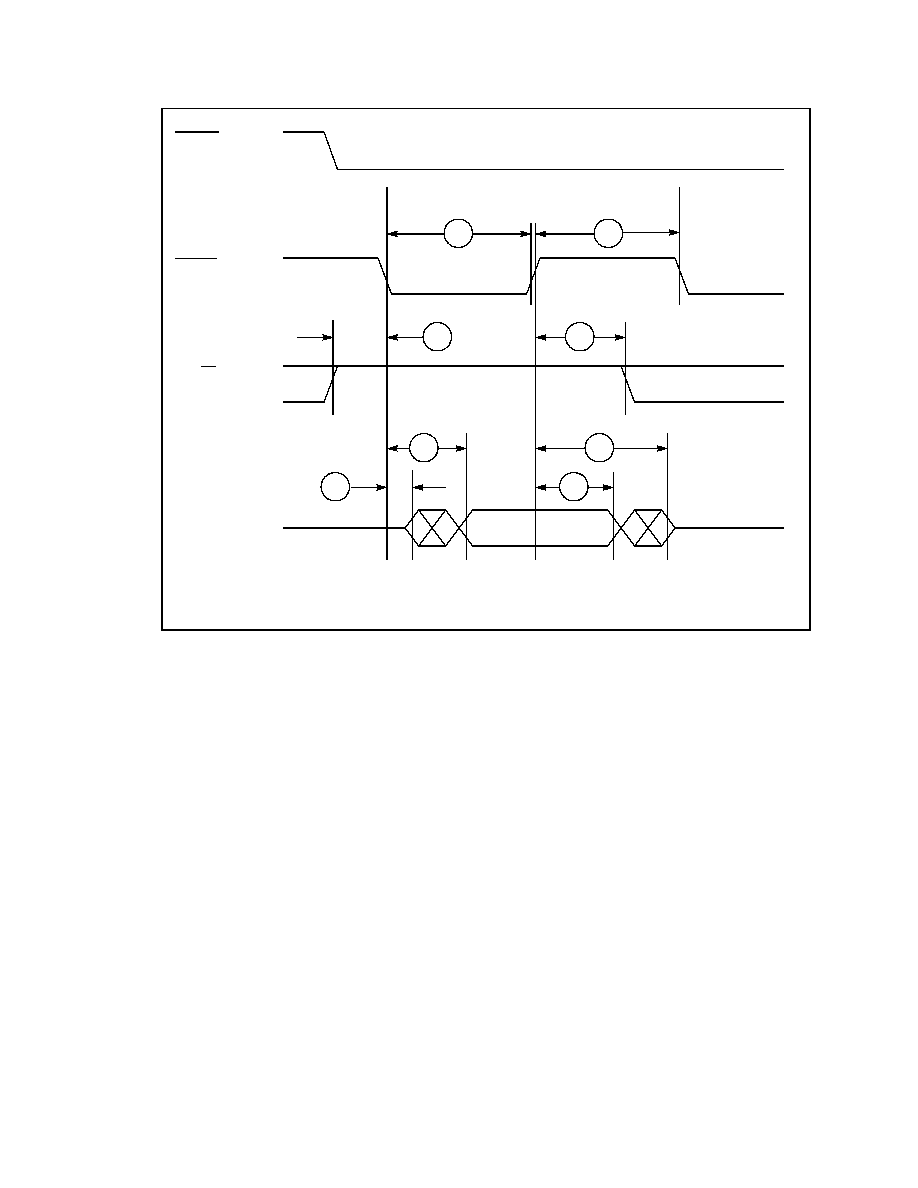

Control Figure 2. Synchronous Reset Timing

RESET

MODA, MODB

V

IHR

IRQA, IRQB

V

IHM

V

ILM

V

IH

V

IL

Control Figure 3. Operating Mode Select Timing

14

15

IRQA, IRQB

16

Control Figure 4. External Interrupt Timing (Negative Edge-Triggered)

16a

15

DSP56001

MOTOROLA

DSP56001 Electrical Characteristics

First Interrupt Instruction Execution

A0-A15

RD

WR

IRQA

IRQB

20

21

19

17

a) First Interrupt Instruction Execution

General

Purpose

I/O

IRQA

IRQB

18

22

b) General Purpose I/O

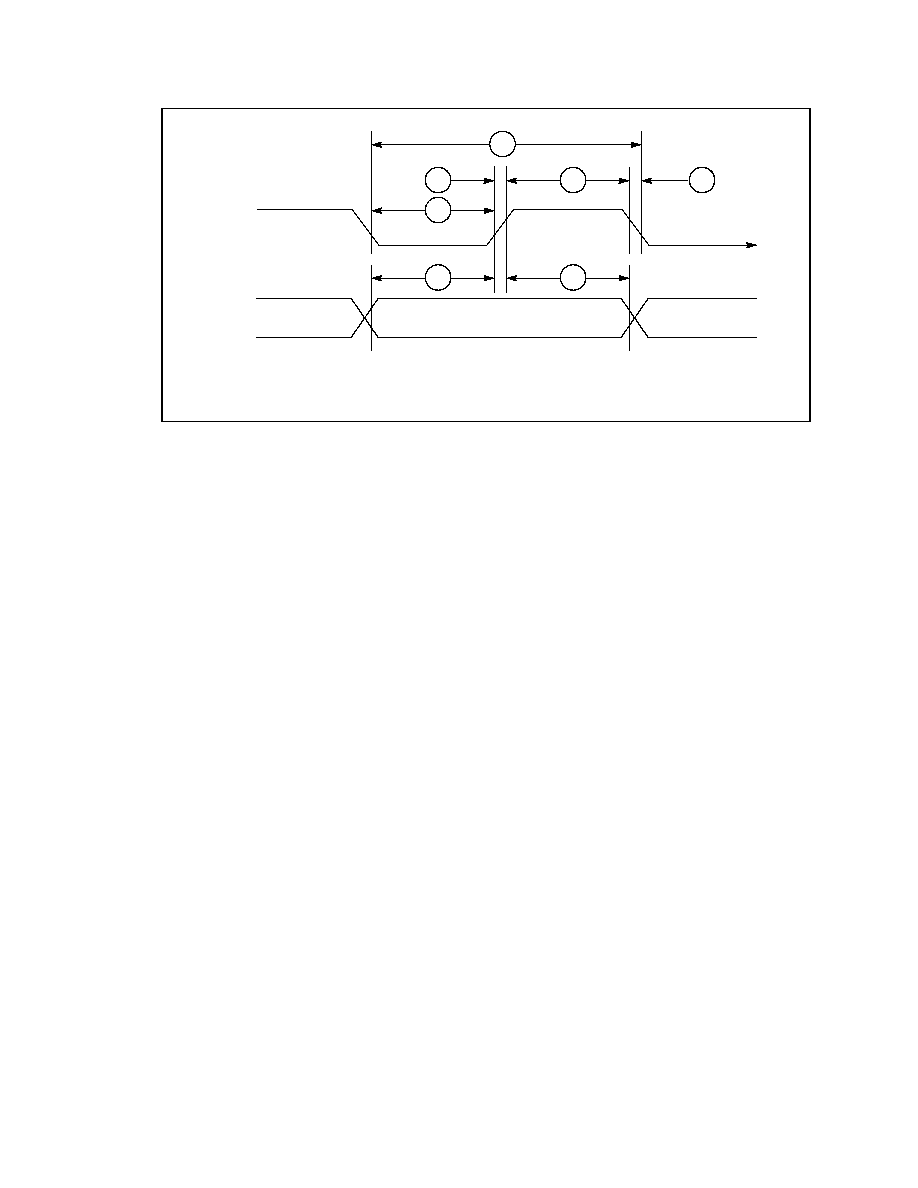

Control Figure 5. External Level-Sensitive Fast Interrupt Timing

16

MOTOROLA

DSP56001 Electrical Characteristics

DSP56001

EXTAL

IRQA, IRQB

A0-A15, DS

PS, X/Y

23

24

T0, T2

T1, T3

Control Figure 6. Synchronous Interrupt and Synchronous Wait State Timing

IRQA

A0-A15, DS,

PS, X/Y

25

26

Control Figure 7. Recovery from Stop State Using IRQA

First Instruction Fetch

IRQA

A0-A15, DS,

PS, X/Y

First IRQA Interrupt

Instruction Fetch

27

28

Control Figure 8. Recovery from Stop State Using IRQA Interrupt Service

17

DSP56001

MOTOROLA

DSP56001 Electrical Characteristics

HOST PORT USAGE CONSIDERATIONS

Careful synchronization is required when reading multibit registers that are written by another asynchronous system. This is a common

problem when two asynchronous systems are connected. The situation exists in the Host port. The considerations for proper operation

are discussed below.

Host Programmer Considerations

1.

Unsynchronized Reading of Receive Byte Registers

When reading receive byte registers, RXH, RXM, or RXL, the Host programmer should use interrupts or poll the RXDF flag which

indicates that data is available. This assures that the data in the receive byte registers will be stable.

2.

Overwriting Transmit Byte Registers

The Host programmer should not write to the transmit byte registers, TXH, TXM, or TXL, unless the TXDE bit is set indicating that

the transmit byte registers are empty. This guarantees that the transmit byte registers will transfer valid data to the HRX register.

3.

Synchronization of Status Bits from DSP to Host

HC, HREQ, DMA, HF3, HF2, TRDY, TXDE, and RXDF (refer to

DSP56000/DSP56001 User's Manual

, I/O Interface section, Host/

DMA Interface Programming Model for descriptions of these status bits) status bits are set or cleared from inside the DSP and

read by the Host processor. The Host can read these status bits very quickly without regard to the clock rate used by the DSP,

but the possibility exists that the state of the bit could be changing during the read operation. This is generally not a system

problem, since the bit will be read correctly in the next pass of any Host polling routine.

However, if the Host asserts the HEN for more than timing number 31a (T31a), with a minimum cycle time of timing number 32a

(T32a), then the status is guaranteed to be stable.

A potential problem exists when reading status bits HF3 and HF2 as an encoded pair. If the DSP changes HF3 and HF2 from 00

to 11, there is a small probability that the Host could read the bits during the transition and receive 01 or 10 instead of 11. If the

combination of HF3 and HF2 has significance, the Host could read the wrong combination.

Solution:

a. Read the bits twice and check for consensus.

b. Assert HEN access for T31a so that status bit transitions are stabilized.

4.

Overwriting the Host Vector

The Host programmer should change the Host Vector register only when the Host Command bit (HC) is clear. This change will

guarantee that the DSP interrupt control logic will receive a stable vector.

5.

Cancelling a Pending Host Command Exception

The Host processor may elect to clear the HC bit to cancel the Host Command Exception request at any time before it is

recognized by the DSP. Because the Host does not know exactly when the exception will be recognized (due to exception

processing synchronization and pipeline delays), the DSP may execute the Host exception after the HC bit is cleared. For these

reasons, the HV bits must not be changed at the same time the HC bit is cleared.

DSP Programmer Considerations

1.

Reading HF0 and HF1 as an Encoded Pair

DMA, HF1, HF0, and HCP, HTDE, and HRDF (refer to

DSP56000/DSP56001 User's Manual

, I/O Interface section, Host/DMA

Interface Programming Model for descriptions of these status bits) status bits are set or cleared by the Host processor side of the

interface. These bits are individually synchronized to the DSP clock.

A potential problem exists when reading status bits HF1 and HF2 as an encoded pair, i.e., the four combinations 00, 01, 10, and

11 each have significance. A very small probability exists that the DSP will read the status bits synchronized during transition.

The solution to this potential problem is to read the bits twice for consensus.

18

MOTOROLA

DSP56001 Electrical Characteristics

DSP56001

AC Electrical Characteristics - Host I/O Timing

(Vcc = 5.0 Vdc + 10%, T

J

= -40 to +105∞ C, CL = 50 pf + 1 TTL Load at 20.5 MHz and 27 MHz)

(Vcc = 5.0 Vdc + 5%, T

J

= -40 to +105∞ C, CL = 50 pf + 1 TTL Load at 33 MHz)

(see Host Figures 1 through 6)

cyc = Clock cycle = 1/2 instruction cycle = 2 T cycles

tHSDL = Host Synchronization Delay Time

Active low lines should be "pulled up" in a manner consistent with the AC and DC specifications

Num

Characteristics

20.5 MHz

27 MHz

33 MHz

Unit

Min

Max

Min

Max

Min

Max

30

Host Synchronous Delay (see Note 1)

tcl

cyc+tcl

tcl

cyc+tcl

tcl

cyc+tcl

ns

31

HEN/HACK Assertion Width

(see Note 2)

a.CVR, ICR, ISR Read (see Note 4)

b.Read

c.Write

cyc+60

50

25

--

--

--

cyc+46

39

19

--

--

--

cyc+37

31

16

--

--

--

ns

ns

ns

32

HEN/HACK Deassertion Width

(see Note 2 and 5)

25

--

19

--

16

--

ns

32a

Minimum Cycle Time Between Two

HEN Assertion for Consecutive CVR,

ICR, and ISR Reads (see Note 2)

2

*

cyc+60

--

2

*

cyc+46

--

2

*

cyc+37

--

ns

33

Host Data Input Setup Time Before

HEN/HACK Deassertion

5

--

4

--

4

--

ns

34

Host Data Input Hold Time After HEN/

HACK Deassertion

5

--

4

--

4

--

ns

35

HEN/HACK Assertion to Output Data

Active from High Impedance

0

--

0

--

0

--

ns

36

HEN/HACK Assertion to Output Data

Valid (periodically sampled, and not

100% tested)

--

50

--

39

--

31

ns

37

HEN/HACK Deassertion to Output

Data High Impedance

--

35

--

27

--

22

ns

38

Output Data Hold Time After HEN/

HACK Deassertion

5

--

4

--

4

--

ns

39

HR/W Low Setup Time Before HEN

Assertion

0

--

0

--

0

--

ns

40

HR/W Low Hold Time After HEN

Deassertion

5

--

4

--

4

--

ns

41

HR/W High Setup Time to HEN

Assertion

0

--

0

--

0

--

ns

42

HR/W High Hold Time After HEN/

HACK Deassertion

5

--

4

--

4

--

ns

43

HA0-HA2 Setup Time Before HEN

Assertion

0

--

0

--

0

--

ns

44

HA0-HA2 Hold Time After HEN

Deassertion

5

--

4

--

4

--

ns

45

DMA HACK Assertion to HREQ

Deassertion (see Note 3)

5

60

4

46

4

49

ns

19

DSP56001

MOTOROLA

DSP56001 Electrical Characteristics

AC Electrical Characteristics - Host I/O Timing (Continued)

(Vcc = 5.0 Vdc + 10%, T

J

= -40 to +105∞ C, CL = 50 pf + 1 TTL Load at 20.5 MHz and 27 MHz

(Vcc = 5.0 Vdc + 5%, T

J

= -40 to +105∞ C, CL = 50 pf + 1 TTL Load at 33 MHz,

see Host Figures 1 through 6)

cyc = Clock cycle = 1/2 instruction cycle = 2 T cycles

tHSDL = Host Synchronization Delay Time

Active low lines should be "pulled up" in a manner consistent with the AC and DC specifications

Notes:

1. "Host synchronization delay (tHSDL)" is the time period required for the

DSP56001 to sample any external asynchronous input signal, determine

whether it is high or low, and synchronize it to the DSP56001 internal clock.

2. See HOST PORT USAGE CONSIDERATIONS.

3. HREQ is pulled up by a 1k

resistor.

4. This timing must be adhered to only if two consecutive reads from one of these registers are executed.

5. It is recommended that timing #32 be 2cyc+tch+10 minimum for 20.5 MHz, 2cyc+tch+7 minimum for 27 MHz,

and 2cyc+tch+6 minimum for 33 MHz if two consecutive writes to TXL are executed without polling TXDE or

HREQ.

Num

Characteristics

20.5 MHz

27 MHz

33 MHz

Unit

Min

Max

Min

Max

Min

Max

46

DMA HACK Deassertion to HREQ

Assertion (see Note 3)

for DMA RXL Read

for DMA TXL Write

for All Other Cases

tHSDL+cyc

+tch+5

tHSDL+cyc+5

5

--

--

--

tHSDL+cyc

+tch+4

tHSDL+cyc+4

4

--

--

--

tHSDL+cyc

+tch+4

tHSDL+cyc+4

4

--

--

--

ns

ns

ns

47

Delay from HEN Deassertion to HREQ

Assertion for RXL Read (see Note 3)

tHSDL+cyc

+tch+5

--

tHSDL+cyc

+tch+4

--

tHSDL+cyc

+tch+4

--

ns

48

Delay from HEN Deassertion to HREQ

Assertion for TXL Write (see Note 3)

tHSDL+cyc+5

--

tHSDL+cyc+4

--

tHSDL+cyc+4

--

ns

49

Delay from HEN Assertion to HREQ

Deassertion for RXL Read, TXL Write

(see Note 3)

5

75

4

70

4

65

ns

EXTERNAL

INTERNAL

30

30

Host Figure 1. Host Synchronization Delay

20

MOTOROLA

DSP56001 Electrical Characteristics

DSP56001

HREQ

(OUTPUT)

HACK

(INPUT)

HR/W

(INPUT)

H0-H7

(OUTPUT)

31

32

41

42

37

36

35

38

Host Figure 2. Host Interrupt Vector Register (IVR) Read

Data Valid

21

DSP56001

MOTOROLA

DSP56001 Electrical Characteristics

HREQ

(OUTPUT)

HEN

(INPUT)

HA2-HA0

(INPUT)

HR/W

(INPUT)

H0-H7

(OUTPUT)

47

49

31

32

43

44

41

42

36

37

35

38

RXM

Read

RXL

Read

RXH

Read

Address

Valid

Address

Valid

Address

Valid

Data

Valid

Data

Valid

Data

Valid

Host Figure 3. Host Read Cycle (Non-DMA Mode)

32A

22

MOTOROLA

DSP56001 Electrical Characteristics

DSP56001

Data

Valid

Data

Valid

Data

Valid

Host Figure 4. Host Write Cycle (Non-DMA Mode)

48

49

31

32

43

44

39

40

33

34

TXM

Write

TXL

Write

TXH

Write

Address

Valid

Address

Valid

Address

Valid

HREQ

(OUTPUT)

HEN

(INPUT)

HA2-HA0

(INPUT)

HR/W

(INPUT)

H0-H7

(INPUT)

Host Figure 5. Host DMA Read Cycle

31

32

45

46

46

36

35

37

38

Data

Valid

Data

Valid

Data

Valid

HREQ

(OUTPUT)

HACK

(INPUT)

H0-H7

(OUTPUT)

RXM

Read

RXL

Read

RXH

Read

46

23

DSP56001

MOTOROLA

DSP56001 Electrical Characteristics

Host Figure 6. Host DMA Write Cycle

HREQ

(OUTPUT)

HACK

(INPUT)

H0-H7

(INPUT)

31

32

45

46

33

34

Data

Valid

Data

Valid

Data

Valid

TXM

Write

TXL

Write

TXH

Write

46

46

24

MOTOROLA

DSP56001 Electrical Characteristics

DSP56001

AC Electrical Characteristics - SCI Timing

(Vcc = 5.0 Vdc + 10%, T

J

= -40 to +105∞ C, CL = 50 pf + 1 TTL Load at 20.5 MHz and 27 MHz,

Vcc = 5.0 Vdc + 5%, T

J

= -40 to +105∞ C, CL = 50 pf + 1 TTL Load at 33 MHz,

see SCI Figures 1 and 2)

cyc = Clock cycle = 1/2 instruction cycle = 2 T cycles

tSCC = Synchronous Clock Cycle Time (for internal clock tSCC is determined by the SCI clock control register and Icyc.)

SCI Synchronous Mode Timing

Num

Characteristics

20.5 MHz

27 MHz

33 MHz

Unit

Min

Max

Min

Max

Min

Max

55

Synchronous Clock Cycle -- tSCC

8

*

cyc

--

8

*

cyc

--

8

*

cyc

--

ns

56

Clock Low Period

4

*

cyc-20

--

4

*

cyc-15

--

4

*

cyc-13

--

ns

57

Clock High Period

4

*

cyc-20

--

4

*

cyc-15

--

4

*

cyc-13

--

ns

59

Output Data Setup to Clock Falling

Edge (Internal Clock)

2

*

cyc

+tcl-50

--

2

*

cyc

+tcl-39

--

2

*

cyc

+tcl-31

--

ns

60

Output Data Hold After Clock Rising

Edge (Internal Clock)

2

*

cyc

-tcl-15

--

2

*

cyc

-tcl-11

--

2

*

cyc

-tcl-9

--

ns

61

Input Data Setup Time Before Clock

Rising Edge (Internal Clock)

2

*

cyc

+tcl+45

--

2

*

cyc

+tcl+35

--

2

*

cyc

+tcl+28

--

ns

62

Input Data Not Valid Before Clock Ris-

ing Edge (Internal Clock)

--

2

*

cyc

+tcl-10

--

2

*

cyc

+tcl-8

--

2

*

cyc

+tcl-6

ns

63

Clock Falling Edge to Output Data

Valid (External Clock)

--

63

--

48

--

39

ns

64

Output Data Hold After Clock Rising

Edge (External Clock)

cyc+12

--

cyc+9

--

cyc+8

--

ns

65

Input Data Setup Time Before Clock

Rising Edge (External Clock)

30

--

23

--

19

--

ns

66

Input Data Hold Time After Clock Ris-

ing Edge (External Clock)

40

--

31

--

25

--

ns

25

DSP56001

MOTOROLA

DSP56001 Electrical Characteristics

AC Electrical Characteristics - SCI Timing

(Vcc = 5.0 Vdc + 10%, T

J

= -40 to +105∞ C, CL = 50 pf + 1 TTL Load at 20.5 MHz and 27 MHz,

Vcc = 5.0 Vdc + 5%, T

J

= -40 to +105∞ C, CL = 50 pf + 1 TTL Load at 33 MHz,

see SCI Figures 1 and 2)

cyc = Clock cycle = 1/2 instruction cycle = 2 T cycles

tACC = Asynchronous clock cycle time

tACC = Asynchronous Clock Cycle Time (for internal clock tACC is determined by the SCI clock control register and Icyc)

SCI Asynchronous Mode Timing - 1X Clock

Num

Characteristics

20.5 MHz

27 MHz

33 MHz

Unit

Min

Max

Min

Max

Min

Max

67

Asynchronous Clock Cycle

64

*

cyc

--

64

*

cyc

--

64

*

cyc

--

ns

68

Clock Low Period

32

*

cyc-20

--

32

*

cyc-15

--

32

*

cyc-13

--

ns

69

Clock High Period

32

*

cyc-20

--

32

*

cyc-15

--

32

*

cyc-13

--

ns

71

Output Data Setup to Clock Rising

Edge (Internal Clock)

32

*

cyc

-100

--

32

*

cyc

-77

--

32

*

cyc

-61

--

ns

72

Output Data Hold After Clock Rising

Edge (Internal Clock)

32

*

cyc

-100

--

32

*

cyc

-77

--

32

*

cyc

-61

--

ns

26

MOTOROLA

DSP56001 Electrical Characteristics

DSP56001

INTERNAL CLOCK

56

57

58

58

55

60

59

62

61

DATA VALID

DATA

VALID

EXTERNAL CLOCK

56

57

55

64

63

66

65

DATA VALID

DATA VALID

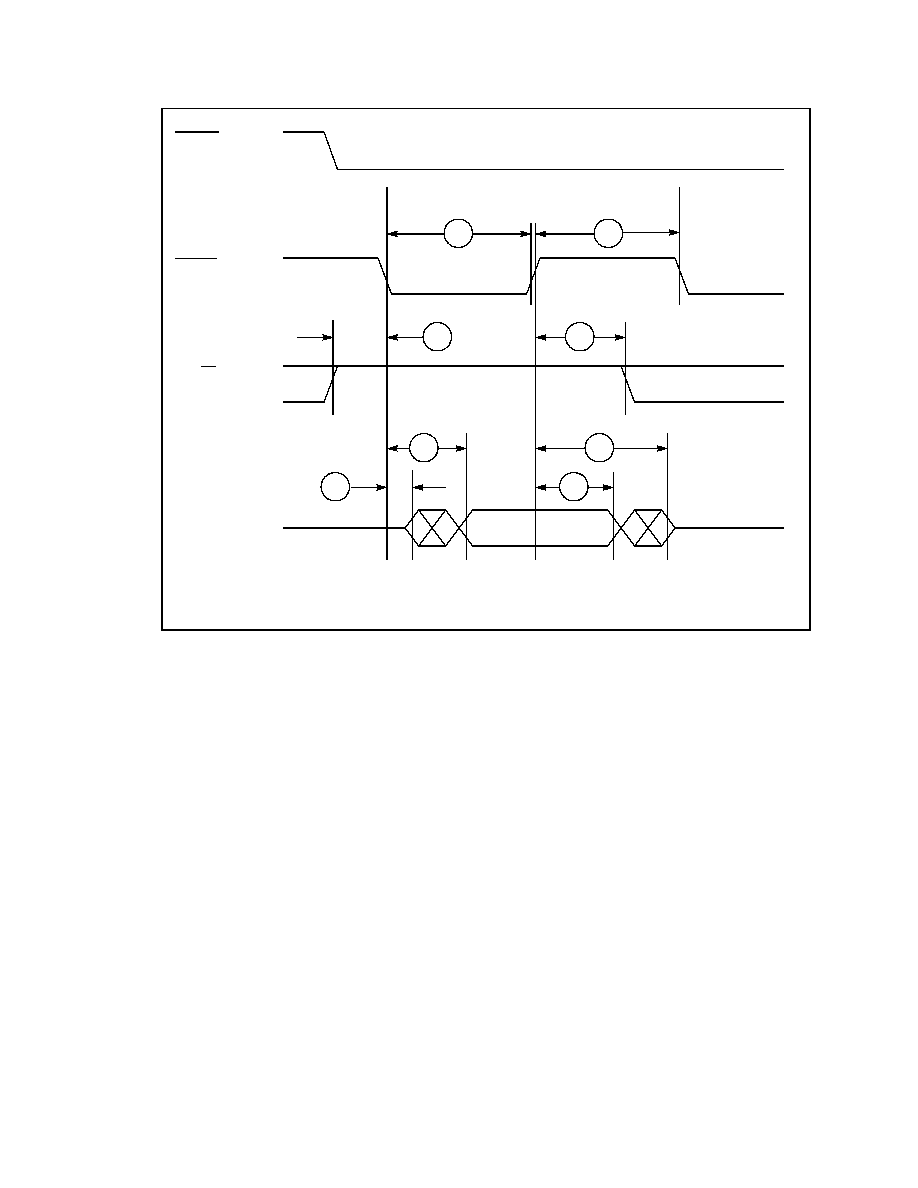

SCI Figure 1. SCI Synchronous Mode Timing

SCLK

(OUTPUT)

TXD

RXD

SCLK

(INPUT)

TXD

RXD

27

DSP56001

MOTOROLA

DSP56001 Electrical Characteristics

1X SCK

(OUTPUT)

TXD

DATA VALID

SCI Figure 2. SCI Asynchronous Mode Timing

68

69

70

70

67

71

72

Note: In the wire-OR mode, TXD can be pulled up by 1K

28

MOTOROLA

DSP56001 Electrical Characteristics

DSP56001

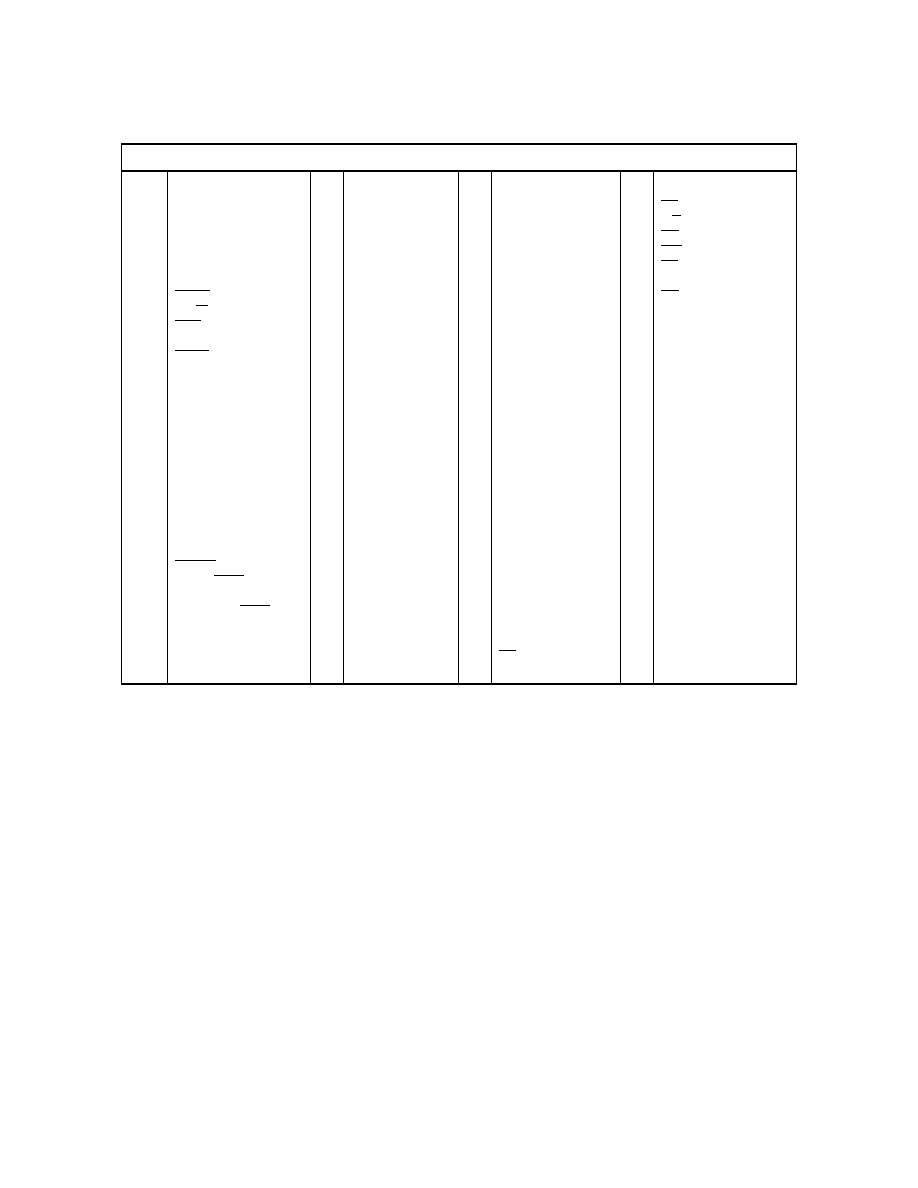

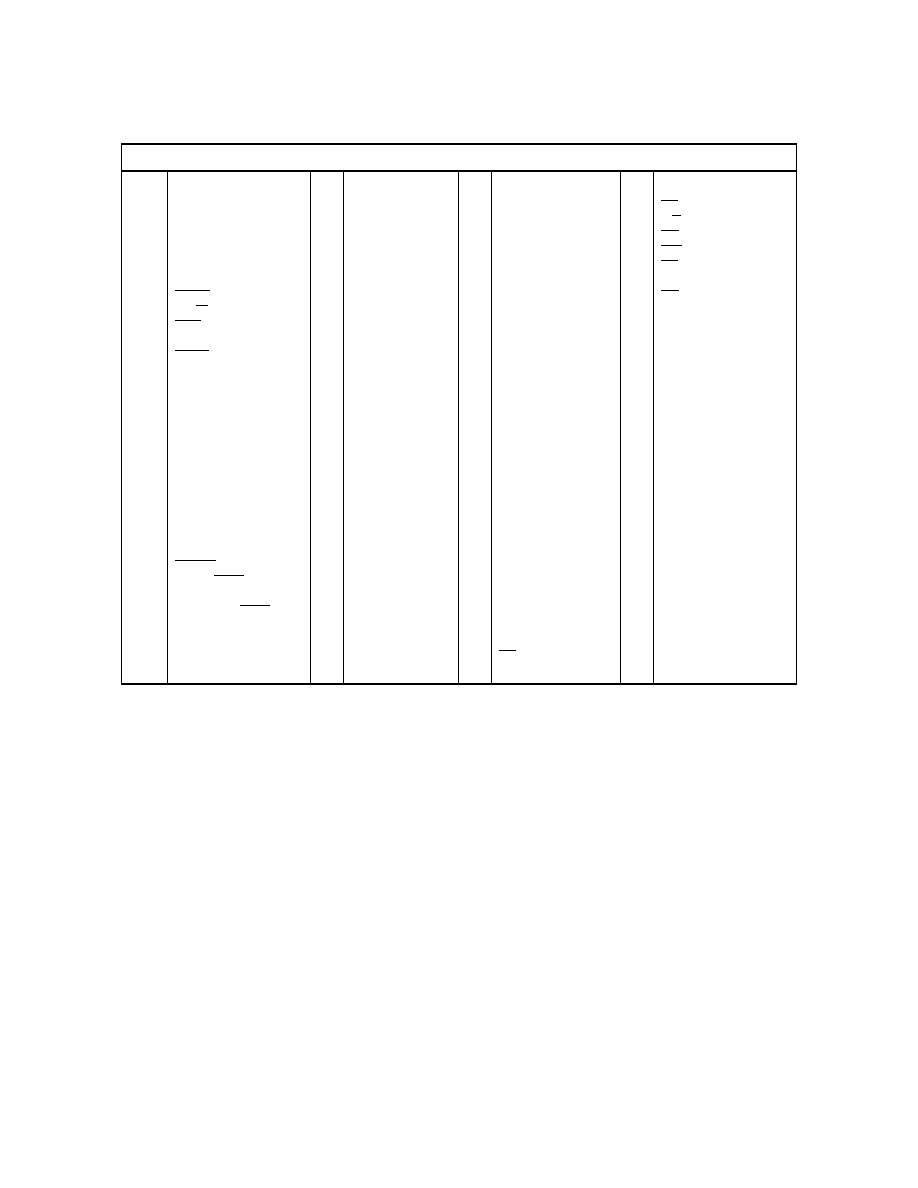

AC Electrical Characteristics - SSI Timing

(Vcc = 5.0 Vdc + 10%, T

J

= -40 to +105∞ C, CL = 50 pf + 1 TTL Load at 20.5 MHz and 27 MHz,

Vcc = 5.0 Vdc + 5%, T

J

= -40 to +105∞ C, CL = 50 pf + 1 TTL Load at 33 MHz,

see SSI Figures 1 and 2)

cyc = Clock cycle = 1/2 instruction cycle = 2 T cycles

tSSICC = SSI clock cycle time

TXC (SCK Pin) = Transmit Clock

RXC (SC0 or SCK Pin) = Receive Clock

FST (SC2 Pin) = Transmit Frame Sync

FSR (SC1 or SC2 Pin) = Receive Frame Sync

i ck = Internal Clock

x ck = External Clock

g ck = Gated Clock

i ck a = Internal Clock, Asynchronous Mode (Asynchronous implies that TXC and

RXC are two different clocks)

i ck s = Internal Clock, Synchronous Mode (Synchronous implies that TXC and

RXC are the same clock)

bl = bit length

wl = word length

Num

Characteristics

20.5 MHz

27 MHz

33 MHz

Unit

Min

Max

Min

Max

Min

Max

80

Clock Cycle (see Note 1)

4

*

cyc

--

4

*

cyc

--

4

*

cyc

--

ns

81

Clock High Period

2

*

cyc-20

--

2

*

cyc-15

--

2

*

cyc-13

--

ns

82

Clock High Period

2

*

cyc-20

--

2

*

cyc-15

--

2

*

cyc-13

--

ns

84

RXC Rising Edge to FSR Out (bl) High

x ck

i ck a

--

--

80

50

--

--

61

38

--

--

48

31

ns

ns

85

RXC Rising Edge to FSR Out (bl) Low

x ck

i ck a

--

--

70

40

--

--

54

31

--

--

43

25

ns

ns

86

RXC Rising Edge to FSR Out (wl) High

x ck

i ck a

--

--

70

40

--

--

54

31

--

--

43

25

ns

ns

87

RXC Rising Edge to FSR Out (wl) Low

x ck

i ck a

--

--

70

40

--

--

54

31

--

--

43

25

ns

ns

88

Data In Setup Time Before RXC (SCK

in Synchronous Mode) Falling Edge

x ck

i ck a

i ck s

15

35

25

--

--

--

12

27

19

--

--

--

10

22

16

--

--

--

ns

ns

ns

89

Data In Hold Time After RXC Falling

Edge x ck

i ck a

35

5

--

--

27

4

--

--

22

4

--

--

ns

ns

90

FSR Input (bl) High Before RXC Falling

Edge x ck

i ck a

15

35

--

--

12

27

--

--

10

23

--

--

ns

ns

91

FSR Input (wl) High Before RXC

Falling Edge x ck

i ck a

20

55

--

--

15

42

--

--

13

34

--

--

ns

ns

92

FSR Input Hold Time After RXC Falling

Edge x ck

i ck a

35

5

--

--

27

4

--

--

22

4

--

--

ns

ns

29

DSP56001

MOTOROLA

DSP56001 Electrical Characteristics

AC Electrical Characteristics - SSI Timing (Continued)

Note:

1. For internal clock, External Clock Cycle is defined by Icyc and SSI control register.

Num

Characteristics

20.5 MHz

27 MHz

33 MHz

Unit

Min

Max

Min

Max

Min

Max

93

Flags Input Setup Before RXC Falling

Edge x ck

i ck a

30

50

--

--

23

39

--

--

19

31

--

--

ns

nss

94

Flags Input Hold Time After RXC

Falling Edge x ck

i ck a

35

5

--

--

27

4

--

--

22

4

--

--

ns

ns

95

TXC Rising Edge to FST Out (bl) High

x ck

i ck a

--

--

70

30

--

--

54

23

--

--

43

19

ns

ns

96

TXC Rising Edge to FST Out (bl) Low

x ck

i ck a

--

--

65

35

--

--

50

27

--

--

40

22

ns

ns

97

TXC Rising Edge to FST Out (wl) High

x ck

i ck a

--

--

65

35

--

--

50

27

--

--

40

22

ns

ns

98

TXC Rising Edge to FST Out (wl) Low

x ck

i ck a

--

--

65

35

--

--

50

27

--

--

40

22

ns

ns

99

TXC Rising Edge to Data Out Enable

from High Impedance x ck

i ck a

--

--

65

40

--

--

50

31

--

--

40

25

ns

ns

100

TXC Rising Edge to Data Out Valid

x ck

i ck a

--

--

65

40

--

--

50

31

--

--

40

25

ns

ns

101

TXC Rising Edge to Data Out High

Impedance (periodically sampled, and

not 100% tested) x ck

i ck a

--

--

70

40

--

--

54

31

--

--

43

25

ns

ns

101a

TXC Falling Edge to Data Out High

Impedance for Gated Clock Mode Only

g ck

cyc+tch

--

cyc+tch

--

cyc+tch

--

ns

102

FST Input (bl) Setup Time Before TXC

Falling Edge x ck

i ck a

15

35

--

--

12

27

--

--

10

23

--

--

ns

ns

103

FST Input (wl) to Data Out Enable from

High Impedance

--

60

--

46

--

37

ns

104

FST Input (wl) Setup Time Before TXC

Falling Edge x ck

i ck a

20

55

--

--

15

42

--

--

13

34

--

--

ns

ns

105

FST Input Hold Time After TXC Falling

Edge x ck

i ck a

35

5

--

--

27

4

--

--

22

4

--

--

ns

ns

106

Flag Output Valid After TXC Rising

Edge x ck

i ck a

--

--

70

40

--

--

54

31

--

--

43

25

ns

ns

Note:

1. For internal clock, External Clock Cycle is defined by Icyc and SSI control register.

30

MOTOROLA

DSP56001 Electrical Characteristics

DSP56001

RXC

(Input/Output)

FSR (Bit)

OUT

FSR (Word)

OUT

DATA IN

FSR (Bit)

IN

FSR (Word)

IN

FLAGS IN

81

82

83

80

84

85

86

87

88

89

First Bit

Last Bit

90

92

92

91

94

93

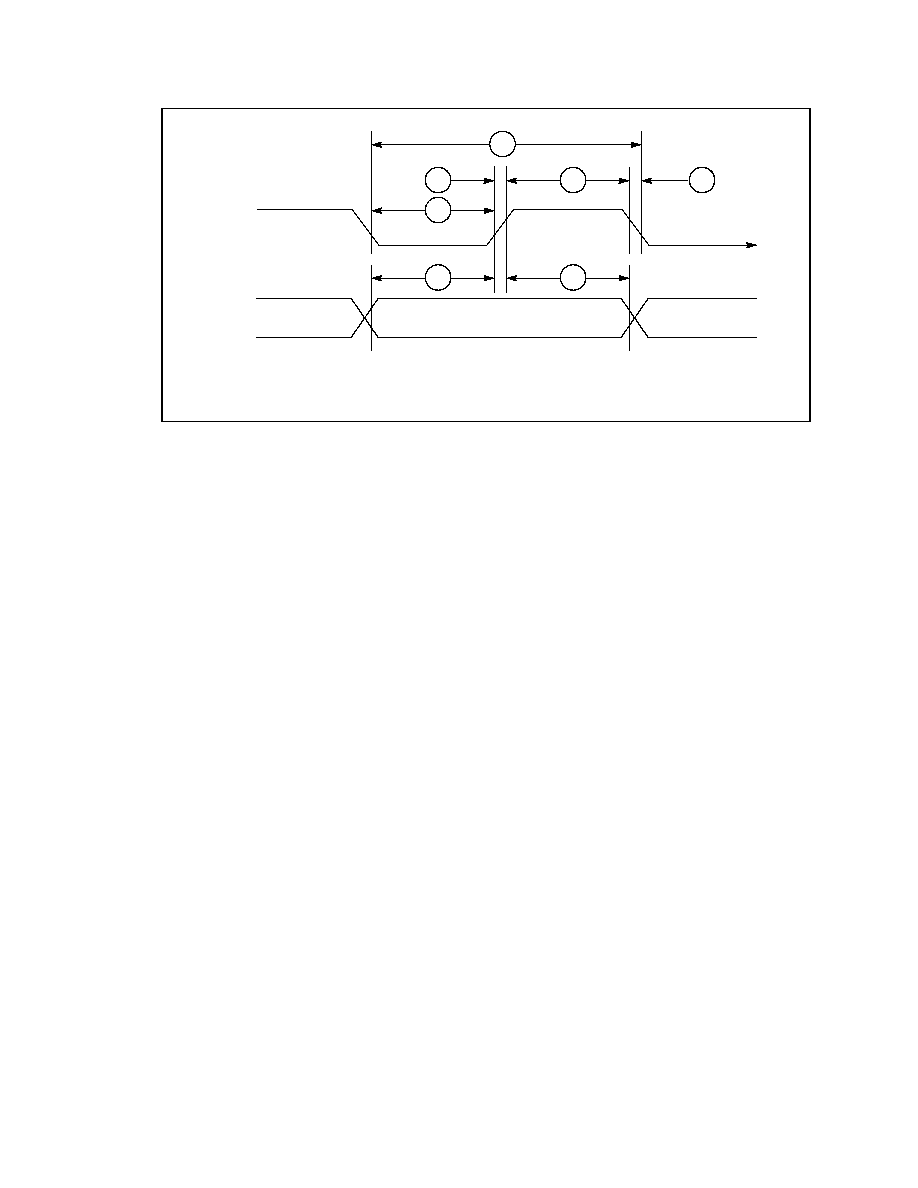

SSI Figure 1. SSI Receiver Timing

83

31

DSP56001

MOTOROLA

DSP56001 Electrical Characteristics

First Bit

Last Bit

(See Note 1)

Note:

1. In the Network mode, output flag transitions can occur at the start of each time slot within

the frame. In the Normal mode, the output flag state is asserted for the entire frame

period.

SSI Figure 2. SSI Transmitter Timing

TXC

(Input/Output)

FST (Bit)

OUT

FST (Word)

OUT

DATA OUT

FST (Bit)

IN

FST (Word)

IN

FLAGS OUT

81

82

83

80

95

96

97

98

100

100

99

105

102

103

104

105

106

101

83

101a

32

MOTOROLA

DSP56001 Electrical Characteristics

DSP56001

AC Electrical Characteristics --

Capacitance Derating -- External Bus Asynchronous Timing

Vcc = 5.0 Vdc + 10%, T

J

= -40 to +105∞ C, CL = 50 pf + 1 TTL Load at 20.5 MHz and 27 MHz,

Vcc = 5.0 Vdc + 5%, T

J

= -40 to +105∞ C, CL = 50 pf + 1 TTL Load at 33 MHz, see Bus Figures 1 and 2

cyc = Clock cycle = 1/2 instruction cycle = 2 T cycles

WS = Number of Wait States, Determined by BCR Register (WS = 0 to 15)

The DSP56001 External Bus Timing Specifications are designed and tested at the maximum capacitive load of 50 pf, including

stray capacitance. Typically, the drive capability of the External Bus pins (A0-A15, D0-D23, PS, DS, RD, WR, X/Y) derates

linearly at 1 ns per 12 pf of additional capacitance from 50 pf to 250 pf of loading. Port B and C pins derate linearly at 1 ns per

5 pf of additional capacitance from 50 pf to 250 pf of loading.

Active low inputs should be "pulled up" in a manner consistent with the AC and DC specifications.

To conserve power, when an internal memory access follows an external memory access, the RD and WR strobes remain

deasserted and A0-A15 and X/Y do not change from their previous state. Both PS and DS will be deasserted (they do not

change between two external accesses to the same memory space) indicating that no external memory access is occurring.

If BR has been asserted, then the bus signals will be three-stated according to the timing information in this data sheet.

Num

Characteristics

20.5 MHz

27 MHz

33 MHz

Unit

Min

Max

Min

Max

Min

Max

115

Delay from BR Assertion to BG

Assertion (see Note 1)

(see Note 2)

(see Note 3)

(see Note 4)

(see Note 5)

2

*

cyc+tch

cyc+tch

cyc+tch

Infinity

tch+4

4*cyc+tch+

20

4*cyc+tch+

cyc*WS+20

6*cyc+tch+

2*cyc*WS+

20

--

cyc+tch+30

2

*

cyc+tch

cyc+tch

cyc+tch

Infinity

tch+3

4*cyc+tch+

15

4*cyc+tch+

cyc*WS+15

6*cyc+tch+

2*cyc*WS+

15

--

cyc+tch+23

2

*

cyc+tch

cyc+tch

cyc+tch

Infinity

tch+3

4*cyc+tch+

13

4*cyc+tch+

cyc*WS+13

6*cyc+tch+

2*cyc*WS+

13

--

cyc+tch+19

ns

ns

ns

ns

ns

116

Flags Input Hold Time After RXC

Falling Edge Deassertion

2*cyc

4*cyc+20

2*cyc

4*cyc+15

2*cyc

4*cyc+13

ns

117

BG Deassertion Duration

2*cyc-10

--

2*cyc-8

--

2*cyc-6

--

ns

118

Delay from Address, Data, and Control

Bus High Impedance to BG Assertion

0

--

0

--

0

--

ns

119

Delay from BG Deassertion to

Address, Data, and Control Bus

Enabled

--

tch-10

--

tch-8

--

tch-6

ns

120

Address Valid to WR Assertion WS=0

WS>0

tcl-9

cyc-9

tcl+5

cyc+5

tcl-7

cyc-7

tcl+5

cyc+5

tcl-5.5

cyc-5.5

tcl+5

cyc+5

ns

ns

121

WR Assertion Width WS=0

WS>0

cyc-9

WS*cyc

+tcl-9

--

--

cyc-7

WS*cyc

+tcl-7

--

--

cyc-5.0

WS*cyc

+tcl-5.0

--

--

ns

ns

122

WR Deassertion to Address Not Valid

tch-12

--

tch-9

--

tch-7.5

--

ns

123

WR Assertion to Data Out Valid WS=0

WS>0

tch-9

0

tch+10

10

tch-7

0

tch+8

8

tch-5.5

0

tch+6.5

6.5

ns

ns

124

Data Out Hold Time from WR

Deassertion (The maximum specifica-

tion is periodically sampled, and not

100% tested.)

tch-9

tch+7

tch-7

tch+6

tch-5.5

tch+4.5

ns

125

Data Out Setup Time to WR

Deassertion (see Note 6) WS=0

WS>0

tcl-5

WS*cyc

+tcl-5

--

--

tcl-5

WS*cyc

+tcl-5

--

--

tcl-5

WS*cyc

+tcl-5

--

--

ns

ns

126

RD Deassertion to Address Not Valid

tch-9

--

tch-7

--

tch-5.5

--

ns

33

DSP56001

MOTOROLA

DSP56001 Electrical Characteristics

AC Electrical Characteristics - External Bus Asynchronous Timing

(Continued)

Notes:

1. With no external access from the DSP.

2. During external read or write access.

3. During external read-modify-write access.

4. During the STOP mode the external bus will not be released and BG will not go low. However,

if the bus is released (BG = 0) and the STOP instruction is executed while BG = 0 then the bus will remain

released while the DSP is in the stop state and BG will remain low.

5. During the WAIT mode the BR/BG circuits remain active.

6. Typical values at 5V are: at 20.5 MHz and WS=0,

Min =

tcl-4

at 20.5 MHz and WS>0,

Min =

WS

*

cyc+tcl-4

at 27

MHz and WS=0,

Min =

tcl-3

at 27

MHz and WS>0,

Min =

WS

*

cyc+tcl-3

at 33

MHz and WS=0,

Min =

tcl-2.5

at 33

MHz and WS>0,

Min = WS

*

cyc+tcl-2.5

Num

Characteristics

20.5 MHz

27 MHz

33 MHz

Unit

Min

Max

Min

Max

Min

Max

127

Address Valid to WS = 0

RD deassertion WS > 0

cyc+tcl-8

((WS+1)

*

cyc)+tcl-8

--

--

cyc+tcl-6

((WS+1)

*

cyc)+tcl-6

--

--

cyc+tcl-6

((WS+1)

*

cyc)+tcl-6

--

--

ns

ns

128

Input Data Hold Time to RD

Deassertion

0

--

0

--

0

--

ns

129

RD Assertion Width WS = 0

WS > 0

cyc-9

((WS+1)*

cyc)-9

--

--

cyc-7

((WS+1)*

cyc)-7

--

--

cyc-5.5

((WS+1)*

cyc)-5.5

--

--

ns

ns

130

Address Valid to WS = 0

Input Data Valid WS > 0

--

--