MOTOROLA CMOS LOGIC DATA

409

MC14518B MC14520B

Dual Up Counters

The MC14518B dual BCD counter and the MC14520B dual binary counter

are constructed with MOS P≠channel and N≠channel enhancement mode

devices in a single monolithic structure. Each consists of two identical,

independent, internally synchronous 4≠stage counters. The counter stages

are type D flip≠flops, with interchangeable Clock and Enable lines for

incrementing on either the positive≠going or negative≠going transition as

required when cascading multiple stages. Each counter can be cleared by

applying a high level on the Reset line. In addition, the MC14518B will count

out of all undefined states within two clock periods. These complementary

MOS up counters find primary use in multi≠stage synchronous or ripple

counting applications requiring low power dissipation and/or high noise

immunity.

∑

Diode Protection on All Inputs

∑

Supply Voltage Range = 3.0 Vdc to 18 Vdc

∑

Internally Synchronous for High Internal and External Speeds

∑

Logic Edge≠Clocked Design -- Incremented on Positive Transition of

Clock or Negative Transition on Enable

∑

Capable of Driving Two Low≠power TTL Loads or One Low≠power

Schottky TTL Load Over the Rated Temperature Range

ŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒ

ŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒ

ŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒ

MAXIMUM RATINGS*

(Voltages Referenced to VSS)

Symbol

Parameter

Value

Unit

VDD

DC Supply Voltage

≠ 0.5 to + 18.0

V

Vin, Vout Input or Output Voltage (DC or Transient)

0.5 to VDD + 0.5

V

Iin, Iout

Input or Output Current (DC or Transient),

per Pin

±

10

mA

PD

Power Dissipation, per Package

500

mW

Tstg

Storage Temperature

≠ 65 to + 150

_

C

TL

Lead Temperature (8≠Second Soldering)

260

_

C

* Maximum Ratings are those values beyond which damage to the device may occur.

Temperature Derating:

Plastic "P and D/DW" Packages: ≠ 7.0 mW/

_

C From 65

_

C To 125

_

C

Ceramic "L" Packages: ≠ 12 mW/

_

C From 100

_

C To 125

_

C

TRUTH TABLE

Clock

Enable

Reset

Action

1

0

Increment Counter

0

0

Increment Counter

X

0

No Change

X

0

No Change

0

0

No Change

1

0

No Change

X

X

1

Q0 thru Q3 = 0

X = Don't Care

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

©

Motorola, Inc. 1995

REV 3

1/94

MC14518B

MC14520B

L SUFFIX

CERAMIC

CASE 620

ORDERING INFORMATION

MC14XXXBCP

Plastic

MC14XXXBCL

Ceramic

MC14XXXBDW

SOIC

TA = ≠ 55

∞

to 125

∞

C for all packages.

P SUFFIX

PLASTIC

CASE 648

DW SUFFIX

SOIC

CASE 751G

This device contains protection circuitry to

guard against damage due to high static

voltages or electric fields. However, pre-

cautions must be taken to avoid applications of

any voltage higher than maximum rated volt-

ages to this high≠impedance circuit. For proper

operation, Vin and Vout should be constrained

to the range VSS

v

(Vin or Vout)

v

VDD.

Unused inputs must always be tied to an

appropriate logic voltage level (e.g., either VSS

or VDD). Unused outputs must be left open.

BLOCK DIAGRAM

VDD = PIN 16

VSS = PIN 8

3

4

5

6

14

13

12

11

C

C

R

R

Q3

Q2

Q1

Q0

Q3

Q2

Q1

Q0

CLOCK

1

2

CLOCK

ENABLE

ENABLE

7

9

10

15

MOTOROLA CMOS LOGIC DATA

MC14518B MC14520B

410

ŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒ

ŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒ

ŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒ

ŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒ

ELECTRICAL CHARACTERISTICS

(Voltages Referenced to VSS)

Characteristic

Symbol

VDD

Vdc

≠ 55

_

C

25

_

C

125

_

C

Unit

Characteristic

Symbol

VDD

Vdc

Min

Max

Min

Typ #

Max

Min

Max

Unit

Output Voltage

"0" Level

Vin = VDD or 0

"1" Level

Vin = 0 or VDD

VOL

5.0

10

15

--

--

--

0.05

0.05

0.05

--

--

--

0

0

0

0.05

0.05

0.05

--

--

--

0.05

0.05

0.05

Vdc

"1" Level

Vin = 0 or VDD

VOH

5.0

10

15

4.95

9.95

14.95

--

--

--

4.95

9.95

14.95

5.0

10

15

--

--

--

4.95

9.95

14.95

--

--

--

Vdc

Input Voltage

"0" Level

(VO = 4.5 or 0.5 Vdc)

(VO = 9.0 or 1.0 Vdc)

(VO = 13.5 or 1.5 Vdc)

"1" Level

(VO = 0.5 or 4.5 Vdc)

(VO = 1.0 or 9.0 Vdc)

(VO = 1.5 or 13.5 Vdc)

VIL

5.0

10

15

--

--

--

1.5

3.0

4.0

--

--

--

2.25

4.50

6.75

1.5

3.0

4.0

--

--

--

1.5

3.0

4.0

Vdc

"1" Level

(VO = 0.5 or 4.5 Vdc)

(VO = 1.0 or 9.0 Vdc)

(VO = 1.5 or 13.5 Vdc)

VIH

5.0

10

15

3.5

7.0

11

--

--

--

3.5

7.0

11

2.75

5.50

8.25

--

--

--

3.5

7.0

11

--

--

--

Vdc

Output Drive Current

(VOH = 2.5 Vdc)

Source

(VOH = 4.6 Vdc)

(VOH = 9.5 Vdc)

(VOH = 13.5 Vdc)

IOH

5.0

5.0

10

15

≠ 3.0

≠ 0.64

≠ 1.6

≠ 4.2

--

--

--

--

≠ 2.4

≠ 0.51

≠ 1.3

≠ 3.4

≠ 4.2

≠ 0.88

≠ 2.25

≠ 8.8

--

--

--

--

≠ 1.7

≠ 0.36

≠ 0.9

≠ 2.4

--

--

--

--

mAdc

(VOL = 0.4 Vdc)

Sink

(VOL = 0.5 Vdc)

(VOL = 1.5 Vdc)

IOL

5.0

10

15

0.64

1.6

4.2

--

--

--

0.51

1.3

3.4

0.88

2.25

8.8

--

--

--

0.36

0.9

2.4

--

--

--

mAdc

Input Current

Iin

15

--

±

0.1

--

±

0.00001

±

0.1

--

±

1.0

µ

Adc

Input Capacitance

(Vin = 0)

Cin

--

--

--

--

5.0

7.5

--

--

pF

Quiescent Current

(Per Package)

IDD

5.0

10

15

--

--

--

5.0

10

20

--

--

--

0.005

0.010

0.015

5.0

10

20

--

--

--

150

300

600

µ

Adc

Total Supply Current**

(Dynamic plus Quiescent,

Per Package)

(CL = 50 pF on all outputs, all

buffers switching)

IT

5.0

10

15

IT = (0.6

µ

A/kHz) f + IDD

IT = (1.2

µ

A/kHz) f + IDD

IT = (1.7

µ

A/kHz) f + IDD

µ

Adc

#Data labelled "Typ" is not to be used for design purposes but is intended as an indication of the IC's potential performance.

** The formulas given are for the typical characteristics only at 25

_

C.

To calculate total supply current at loads other than 50 pF:

IT(CL) = IT(50 pF) + (CL ≠ 50) Vfk

where: IT is in

µ

A (per package), CL in pF, V = (VDD ≠ VSS) in volts, f in kHz is input frequency, and k = 0.002.

PIN ASSIGNMENT

13

14

15

16

9

10

11

12

5

4

3

2

1

8

7

6

Q1B

Q2B

Q3B

RB

VDD

CB

EB

Q0B

Q1A

Q0A

EA

CA

VSS

RA

Q3A

Q2A

MOTOROLA CMOS LOGIC DATA

411

MC14518B MC14520B

ŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒ

ŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒ

ŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒ

ŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒŒ

SWITCHING CHARACTERISTICS*

(CL = 50 pF, TA = 25

_

C)

Characteristic

Symbol

VDD

All Types

Unit

Characteristic

Symbol

VDD

Min

Typ #

Max

Unit

Output Rise and Fall Time

tTLH, tTHL = (1.5 ns/pF) CL + 25 ns

tTLH, tTHL = (0.75 ns/pF) CL + 12.5 ns

tTLH, tTHL = (0.55 ns/pF) CL + 9.5 ns

tTLH,

tTHL

5.0

10

15

--

--

--

100

50

40

200

100

80

ns

Propagation Delay Time

Clock to Q/Enable to Q

tPLH, tPHL = (1.7 ns/pF) CL + 215 ns

tPLH, tPHL = (0.66 ns/pF) CL + 97 ns

tPLH, tPHL = (0.5 ns/pF) CL + 75 ns

tPLH,

tPHL

5.0

10

15

--

--

--

280

115

80

560

230

160

ns

Reset to Q

tPHL = (1.7 ns/pF) CL + 265 ns

tPHL = (0.66 ns/pF) CL + 117 ns

tPHL = (0.66 ns/pF) CL + 95 ns

tPHL

5.0

10

15

--

--

--

330

130

90

650

230

170

ns

Clock Pulse Width

tw(H)

tw(L)

5.0

10

15

200

100

70

100

50

35

--

--

--

ns

Clock Pulse Frequency

fcl

5.0

10

15

--

--

--

2.5

6.0

8.0

1.5

3.0

4.0

MHz

Clock or Enable Rise and Fall Time

tTHL, tTLH

5.0

10

15

--

--

--

--

--

--

15

5

4

µ

s

Enable Pulse Width

tWH(E)

5.0

10

15

440

200

140

220

100

70

--

--

--

ns

Reset Pulse Width

tWH(R)

5.0

10

15

280

120

90

125

55

40

--

--

--

ns

Reset Removal Time

trem

5.0

10

15

≠ 5

15

20

≠ 45

≠ 15

≠ 5

--

--

--

ns

* The formulas given are for the typical characteristics only at 25

_

C.

#Data labelled "Typ" is not to be used for design purposes but is intended as an indication of the IC's potential performance.

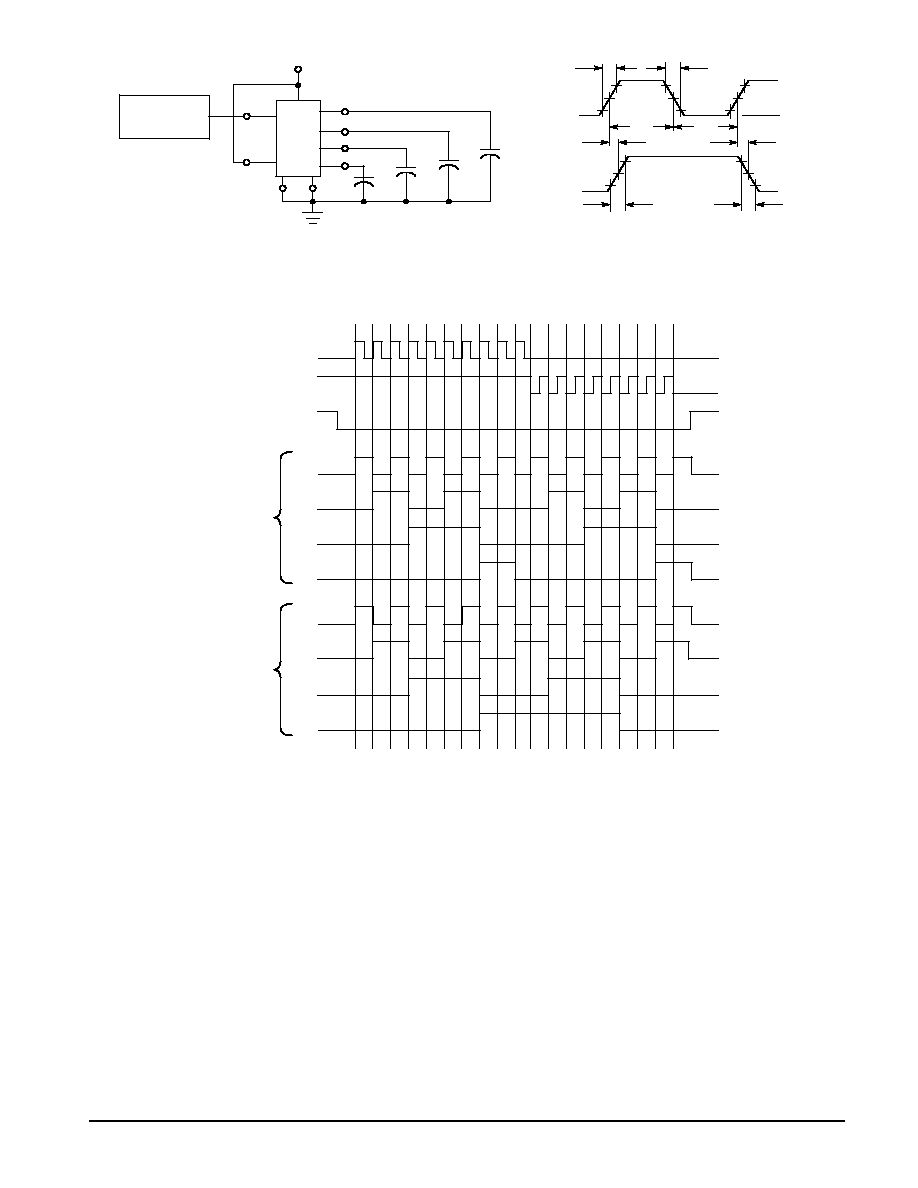

Figure 1. Power Dissipation Test Circuit and Waveform

PULSE

GENERATOR

VARIABLE

WIDTH

CL

CL

CL

CL

VDD

VSS

VSS

500

µ

F

0.01

µ

F

CERAMIC

20 ns

50%

10%

90%

20 ns

ID

Q3

Q2

Q1

Q0

C

E

R

MOTOROLA CMOS LOGIC DATA

MC14518B MC14520B

412

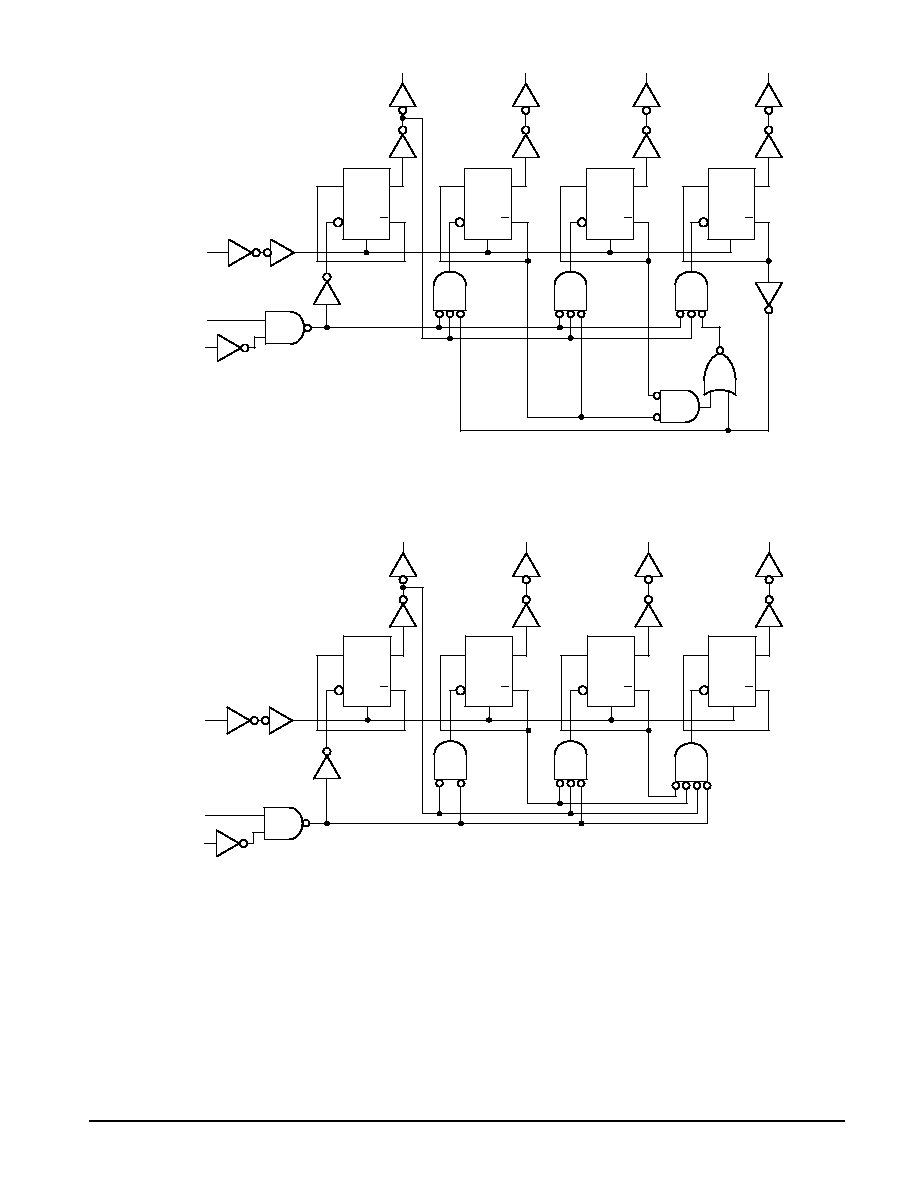

Figure 2. Switching Time Test Circuit and Waveforms

PULSE

GENERATOR

CL

CL

CL

CL

VDD

VSS

Q3

Q2

Q1

Q0

C

E

R

20 ns

Q

tr

tf

VDD

VSS

20 ns

CLOCK

INPUT

90%

50%

10%

tWL

tWH

90%

50%

10%

tPLH tPHL

Figure 3. Timing Diagram

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

9

8

7

6

5

4

3

2

1

2

1

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

4

3

0

9

8

7

6

5

4

3

2

1

CLOCK

ENABLE

RESET

Q0

Q1

Q2

Q3

Q0

Q1

Q2

Q3

MC14518B

MC14520B

MOTOROLA CMOS LOGIC DATA

413

MC14518B MC14520B

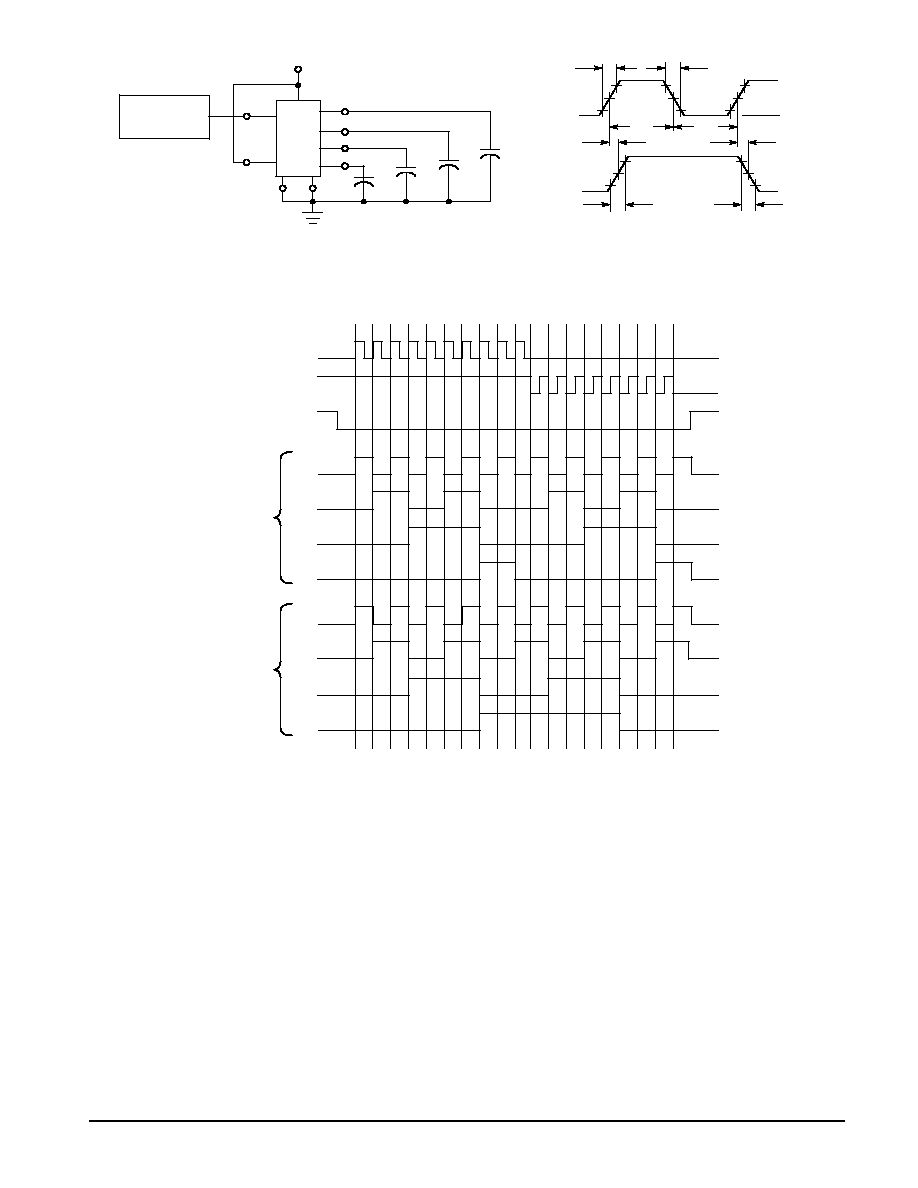

Figure 4. Decade Counter (MC14518B) Logic Diagram

(1/2 of Device Shown)

D

C

R

Q

Q

D

C

R

Q

Q

D

C

R

Q

Q

D

C

R

Q

Q

Q0

Q1

Q2

Q3

RESET

ENABLE

CLOCK

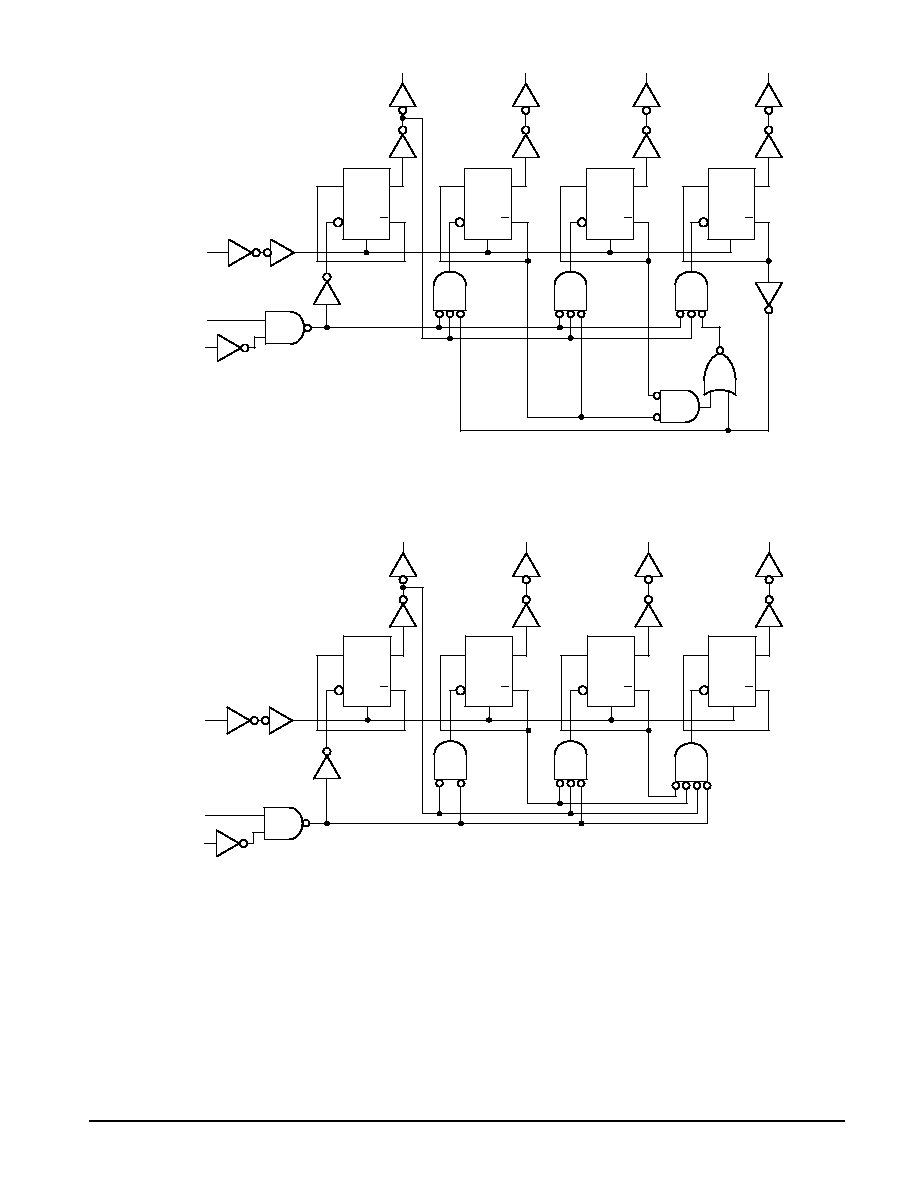

Figure 5. Binary Counter (MC14520B) Logic Diagram

(1/2 of Device Shown)

D

C

R

Q

Q

D

C

R

Q

Q

D

C

R

Q

Q

D

C

R

Q

Q

Q0

Q1

Q2

Q3

RESET

ENABLE

CLOCK