1

MRFIC0912

MOTOROLA RF DEVICE DATA

The MRFIC Line

900 MHz GaAs

Integrated Power Amplifier

Designed primarily for use in high efficiency Analog Cellular applications,

the MRFIC0912 is a two≠stage power amplifier in Motorola's proprietary

Power Flat Pack 16≠lead package. This integrated circuit requires minimal

off-chip matching while allowing for the maximum in flexibility in optimizing

gain and efficiency. The design employs Motorola's planar, self≠aligned GaAs

MESFET IC process to give the highest efficiency possible.

∑

Usable Frequency Range = 800 ≠ 1000 MHz, Specified for 824 ≠ 905 MHz

∑

30.8 dBm Minimum Output Power

∑

470 mA Maximum Supply Current at 30.8 dBm Output

∑

23.8 dB Minimum Gain

∑

Simple Off≠chip Matching for Maximum Power/Efficiency Flexibility

∑

4.6 Volt Supply

∑

45 dB/Volt Typical Power Output Control

∑

Order MRFIC0912R2 for Tape and Reel Option.

R2 Suffix = 1,500 Units per 16 mm, 13 inch Reel.

∑

Device Marking = M0912

RF IN

1

2

3

4

7

6

5

GND

Pin Connections and Functional Block Diagram

8

9

10

11

12

13

14

15

16

VG1

RF OUT/VD2

VG2

VD1

GND

N/C

N/C

N/C

N/C

N/C

N/C

N/C

RF OUT/VD2

RF OUT/VD2

Order this document

by MRFIC0912/D

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

MRFIC0912

900 MHz

GaAs INTEGRATED

POWER AMPLIFIER

CASE 978≠02

(PFP≠16)

©

Motorola, Inc. 1997

REV 1

MRFIC0912

2

MOTOROLA RF DEVICE DATA

MAXIMUM RATINGS

(TA = 25

∞

C unless otherwise noted)

Ratings

Symbol

Limit

Unit

Supply Voltage

VD1, VD2

8

Vdc

RF Input Power

PRF

20

dBm

Gate Voltage

VG1, VG2, VGG

≠5

Vdc

Storage Temperature Range

Tstg

≠ 65 to +150

∞

C

Operating Case Temperature

TC

≠ 35 to +100

∞

C

Thermal Resistance, Junction to Case

R

JC

18

∞

C/W

RECOMMENDED OPERATING RANGES

Parameter

Symbol

Value

Unit

RF Frequency

fRF

824≠905

MHz

Supply Voltage

VD1, VD2

4.0≠6.0

Vdc

Gate Voltage

VG1, VG2

≠2.3 to ≠1.5

Vdc

ELECTRICAL CHARACTERISTICS

(VD1, VD2 = 4.6 V, TA = 25

∞

C, fRF = 840 MHz, Pin = 7 dBm, VGG set for ID2Q = 200 mA, Tested in

Circuit Shown in Figure 1)

Characteristic

Min

Typ

Max

Unit

RF Output Power

30.8

31.2

--

dBm

Power Slump (VD1, VD2 = 4.0 V, TC = 100

_

C)

28.5

--

--

dBm

Load Mismatch Survival (VD1, VD2 = 7 V, Load VSWR = 10:1, all phases,

10 sec)

No Degradation

Spurious Output (VD1,VD2 = 0 to 7 V, Pin = 5 to 9 dBm, Load

VSWR = 10:1)

--

--

≠60

dBc

Input Return Loss

--

10

--

dB

Harmonic Output (Pout = 30.8 dBm)

2f0

3f0

4f0

--

--

--

--

--

--

≠25

≠40

≠40

dBc

Noise Power (VDD = 0 to 7 V, 45 MHz Above fRF at 30 kHz BW)

--

--

≠93

dBm

Maximum Power Control Voltage Slope (Change in Pout for Change on

VD1)

--

45

--

dB/V

Total Supply Current (VD1 set for Pout = 30.8 dBm)

--

430

470

mA

VGG Required for ID2Q = 200 mA

≠2.3

≠2.0

≠1.7

Vdc

Gate Current during RF Operation

≠2

--

2

mA

DESIGN AND APPLICATIONS INFORMATION

The MRFIC0912 has been designed for high efficiency

900 MHz applications such as analog cellular and Industrial,

Medical and Scientific (ISM) equipment. The two stage MES-

FET design utilizes Motorola's planar refractory gate process

to allow high performance GaAs to be applied to consumer

applications. The proprietary PFP≠16 package assures good

grounding and low thermal resistance.

As shown in Figure 1, the gate voltage pins can be ganged

together and one voltage applied to both gates to set the

quiescent operating current. Alternatively, VG1 and VG2 can

be set separately. VD1 can be used as power control with a

45 dB per volt sensitivity. The placement of C3 in the VD1

supply line can be varied to optimize RF performance since

T2 is part of a shunt L matching section. On the output, pins

11, 12 and 13, the placement of C11 is adjusted for best RF

performance.

Layout is important for amplifier stability and RF perfor-

mance. Ground vias must be located as close to circuit

ground connections as possible. Power supply bypassing

C3, C6, C9, and C10 must be included to reduce out≠of≠

band gain and prevent spurious output.

Evaluation Boards

Evaluation boards are available for RF Monolithic Inte-

grated Circuits by adding a "TF" suffix to the device type.

For a complete list of currently available boards and ones

in development for newly introduced product, please con-

tact your local Motorola Distributor or Sales Office.

MRFIC0912

4

MOTOROLA RF DEVICE DATA

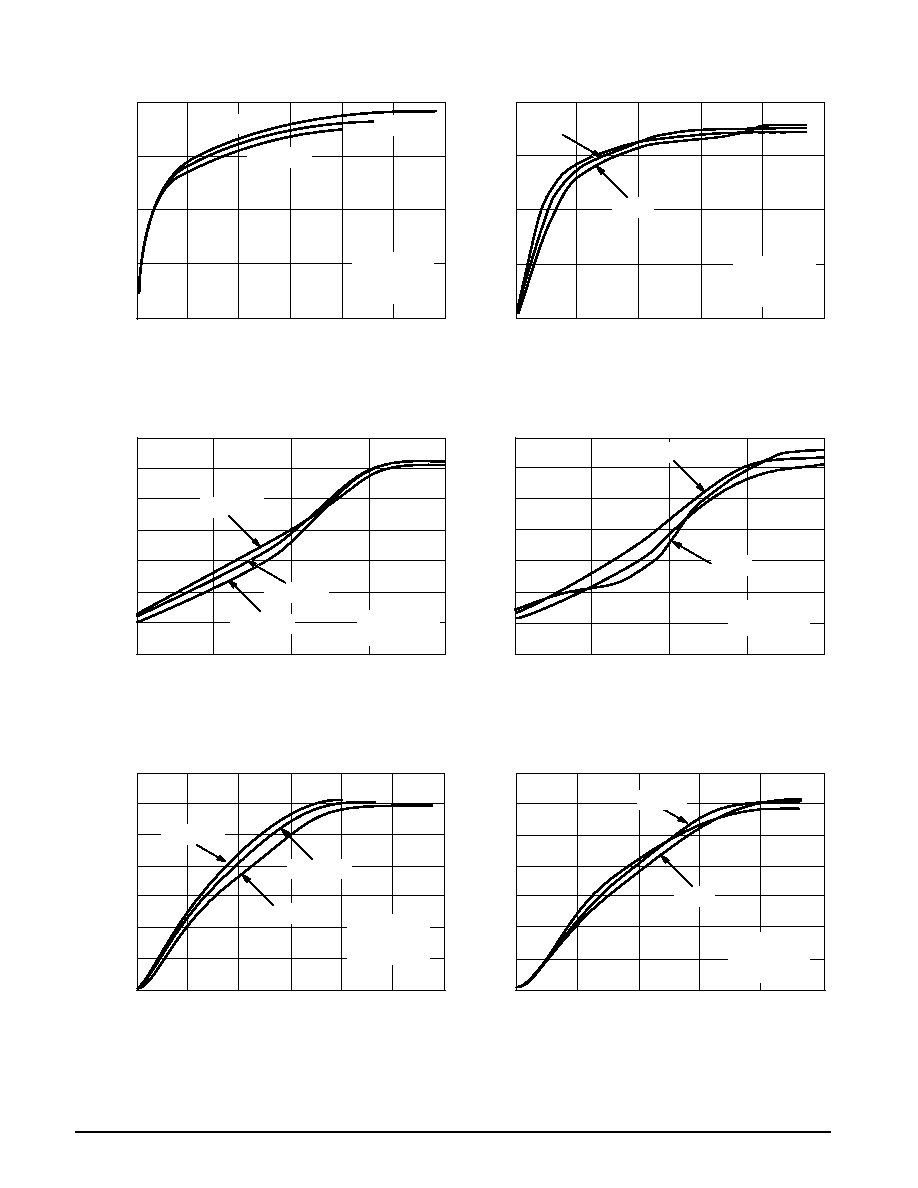

TYPICAL CHARACTERISTICS

T = 25

∞

C

Figure 4. Output Power versus Control Voltage

35

Vcntrl, CONTROL VOLTAGE (VOLTS)

≠5

Figure 5. Output Power versus Control Voltage

25

Vcntrl, CONTROL VOLTAGE (VOLTS)

5

2

4

6

Figure 6. Power Added Efficiency versus

Input Power

≠10

Pin, INPUT POWER (dBm)

30

0

5

60

Figure 7. Power Added Efficiency versus

Input Power

Pin, INPUT POWER (dBm)

0

≠ 5

60

5

≠ 5

10

10

≠10

0

20

40

15

≠ 5

1

2

0

20

50

70

P

AE, POWER

ADDED

EFFICIENCY

(%)

3

4

5

70

35

5

15

25

10

1

3

5

0

0

P

out

,

OUTPUT

POWER (dBm)

P

out

,

OUTPUT

POWER (dBm)

f = 837 MHz

Pin = 7.0 dBm

TEMP = 25

∞

C

VDD = 4.0 V

VDD = 4.6 V

VDD = 5.8 V

VDD = 4.6 V

f = 837 MHz

Pin = 7.0 dBm

≠ 35

∞

C

85

∞

C

VDD = 4.0 V

VDD = 4.6 V

VDD = 5.8 V

f = 837 MHz

TEMP = 25

∞

C

40

P

AE, POWER

ADDED

EFFICIENCY

(%)

VDD = 4.6 V

f = 837 MHz

T = 25

∞

C

≠ 35

∞

C

85

∞

C

50

10

30

P

AE, POWER

ADDED

EFFICIENCY

(%)

P

AE, POWER

ADDED

EFFICIENCY

(%)

Figure 8. Power Added Efficiency versus

Control Voltage

60

Vcntrl, CONTROL VOLTAGE (VOLTS)

10

0

20

40

30

Figure 9. Power Added Efficiency versus

Control Voltage

0

1

Vcntrl, CONTROL VOLTAGE (VOLTS)

70

40

10

6

60

0

5

0

50

2

3

70

20

50

30

5

f = 837 MHz

Pin = 7.0 dBm

TEMP = 25

∞

C

VDD = 4.0 V

VDD = 4.6 V

VDD = 5.8 V

VDD = 4.6 V

f = 837 MHz

Pin = 7.0 dBm

4

3

2

1

4

≠ 35

∞

C

T = 25

∞

C

85

∞

C

5

MRFIC0912

MOTOROLA RF DEVICE DATA

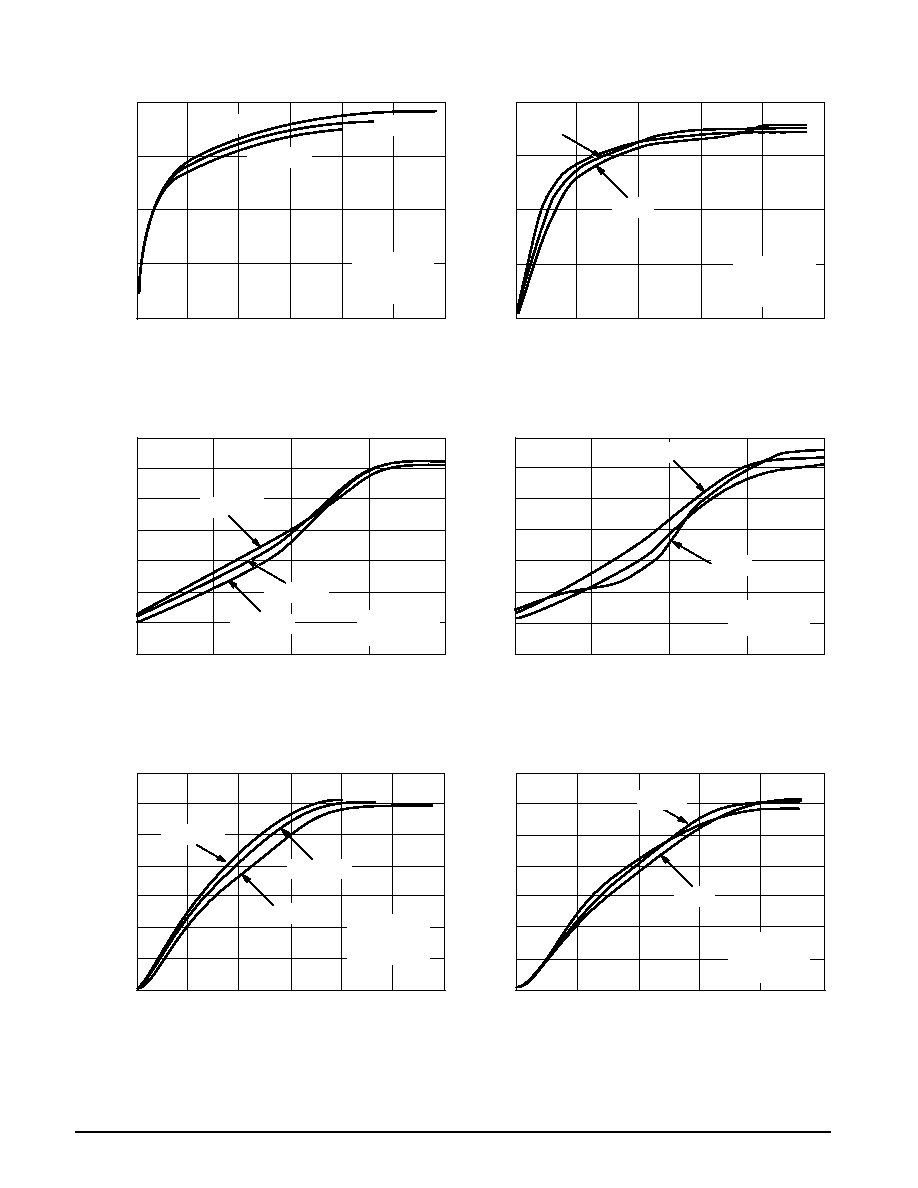

TYPICAL CHARACTERISTICS

85

∞

C

P

AE, POWER

ADDED

EFFICIENCY

(%)

P

AE, POWER

ADDED

EFFICIENCY

(%)

Figure 10. Output Power versus Frequency

34

f, FREQUENCY (MHz)

29

Figure 11. Output Power versus Frequency

31.6

f, FREQUENCY (MHz)

31.2

850

30.6

Figure 12. Power Added Efficiency

versus Frequency

825

f, FREQUENCY (MHz)

59

840

61

Figure 13. Power Added Efficiency

versus Frequency

f, FREQUENCY (MHz)

55

830

61

840

830

850

850

825

825

57

59

31.4

31

30.4

830

835

825

62

840

845

850

63

31.8

30

31

32

33

60

835

830

840

845

T = 25

∞

C

≠ 35

∞

C

P

out

,

OUTPUT

POWER (dBm)

P

out

,

OUTPUT

POWER (dBm)

835

845

845

835

VDD = 5.8 V

VDD = 4.0 V

VDD = 4.6 V

Pin = 7.0 dBm

TEMP = 25

∞

C

30.8

Pin = 7.0 dBm

TEMP = 25

∞

C

VDD = 5.8 V

VDD = 4.0 V

VDD = 4.6 V

T = 25

∞

C

≠ 35

∞

C

85

∞

C

VDD = 4.6 V

Pin = 7.0 dBm

VDD = 4.6 V

Pin = 7.0 dBm

Figure 14. Drain Current versus Control

Voltage

400

Vcntrl, CONTROL VOLTAGE (VOLTS)

0

50

200

100

5

I D2

, DRAIN CURRENT

(mA)

0

300

450

4

VDD = 4.6 V

f = 837 MHz

Pin = 7.0 dBm

ID2

3

2

1

350

150

250

I , D1

ID1