Data Sheet

C-5e NETWORK PROCESSOR

SILICON REVISION A1

C5ENPA1-DS/D

Rev 03 PRELIMINARY

Data Sheet

C-5e Network Processor

Silicon Revision A1

C5ENPA1-DS/D

Rev 03

P

r e

l i

m

i n

a r

y

Copyright � 2002 Motorola, Inc. All rights reserved. No part of this documentation may

be reproduced in any form or by any means or used to make any derivative work (such as

translation, transformation, or adaptation) without written permission from Motorola.

Motorola reserves the right to revise this documentation and to make changes in content

from time to time without obligation on the part of Motorola to provide notification of

such revision or change.

Motorola provides this documentation without warranty, term, or condition of any kind,

either implied or expressed, including, but not limited to, the implied warranties, terms or

conditions of merchantability, satisfactory quality, and fitness for a particular purpose.

Motorola may make improvements or changes in the product(s) and/or the program(s)

described in this documentation at any time.

C-5e, C-3e, C-5, Q-5, Q-3, C-Port, and C-Ware are all trademarks of C-Port, a Motorola

Company. Motorola and the stylized Motorola logo are registered in the US Patent &

Trademark Office. All other product or service names are the property of their respective

owners.

MOTOROLA GENERAL BUSINESS INFORMATION

C5ENPA1-DS/D REV 03

C5ENPA1-DS/D

Rev 03

CONTENTS

About This Guide

Guide Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13

Data Sheet Classifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14

Using PDF Documents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14

Guide Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

16

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

16

Related Product Documentation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

17

C

HAPTER

1

Functional Description

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

19

Massive Processing Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

19

High Functional Integration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

19

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

20

Channel Processors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

22

Executive Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

23

System Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

23

Fabric Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

24

Buffer Management Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

24

Table Lookup Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

25

Queue Management Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

26

C

HAPTER

2

Signal Descriptions

Signal Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

27

Pinout Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

28

Pin Descriptions Grouped by Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

30

LVTTL and LVPECL Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

30

Clock Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

31

CP Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

32

DS1/T1 Framer Interface Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

34

10/100 Ethernet (RMII) Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

34

Gigabit Ethernet (GMII) Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

35

6

CONTENTS

C5ENPA1-DS/D REV 03

MOTOROLA GENERAL BUSINESS INFORMATION

Gigabit Ethernet and Fibre Channel TBI Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

38

SONET OC-3 Transceiver Interface Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

39

SONET OC-12 Transceiver Interface Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

40

Executive Processor System Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

42

PCI Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

42

Serial Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

43

PROM Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

44

General System Interface Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

47

Fabric Processor Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

48

BMU SDRAM Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

52

TLU SRAM Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

54

QMU SRAM (Internal Mode) Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

55

QMU to Q-5 TMC (External Mode) Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

56

Power Supply Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

57

Test Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

58

No Connection Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

58

Signals Grouped by Pin Number . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

59

JTAG Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

69

Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

69

JTAG Data Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

69

Boundary Scan Restriction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

69

Boundary Scan Cell Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

69

IDcode Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

71

JTAG Instruction Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

71

Boundary Scan Description Language . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

72

C

HAPTER

3

Electrical Specifications

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

73

Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

74

DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

75

Power Sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

76

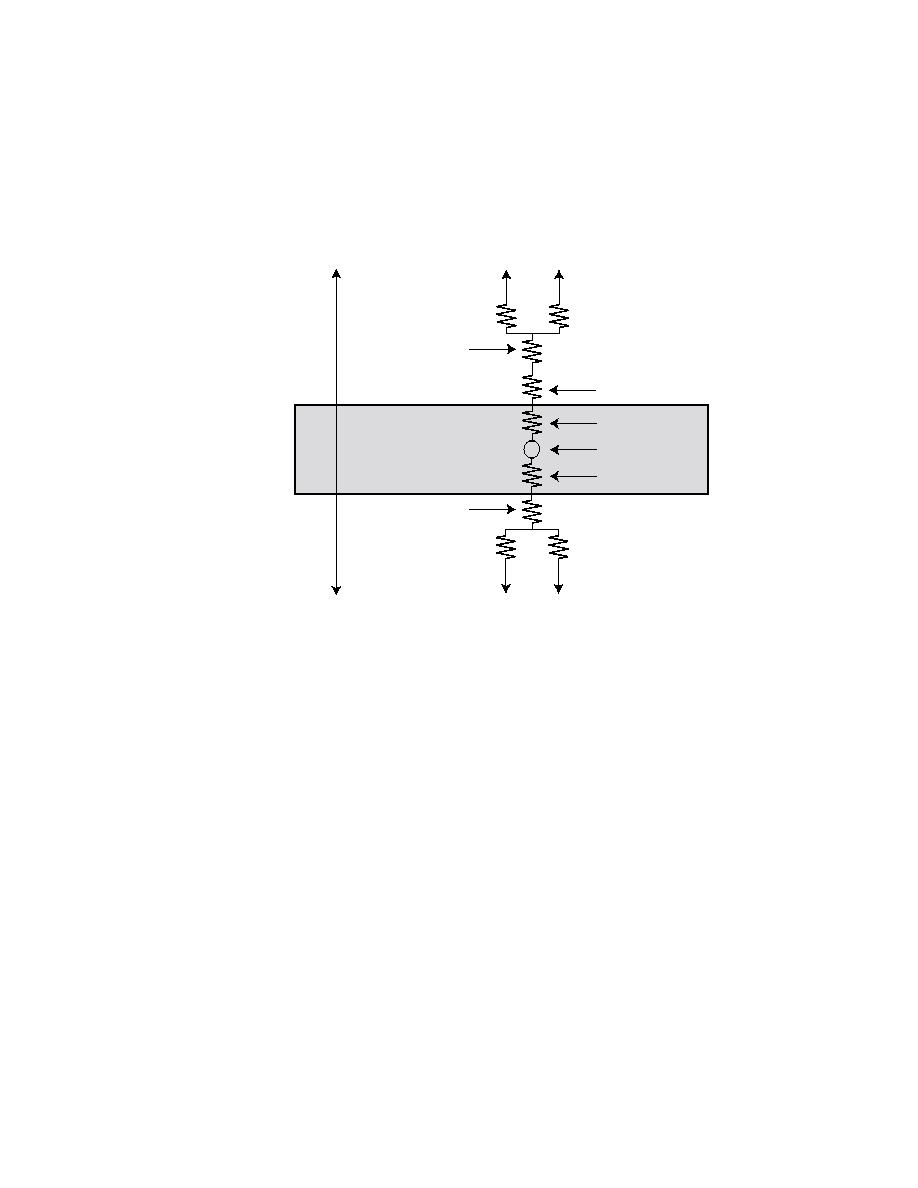

Power and Thermal Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

77

Thermal Management Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

77

Internal Package Conduction Resistance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

78

Heat Sink Selection Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

79

AC Timing Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

81

Clock Timing Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

82

CONTENTS

7

MOTOROLA GENERAL BUSINESS INFORMATION

C5ENPA1-DS/D REV 03

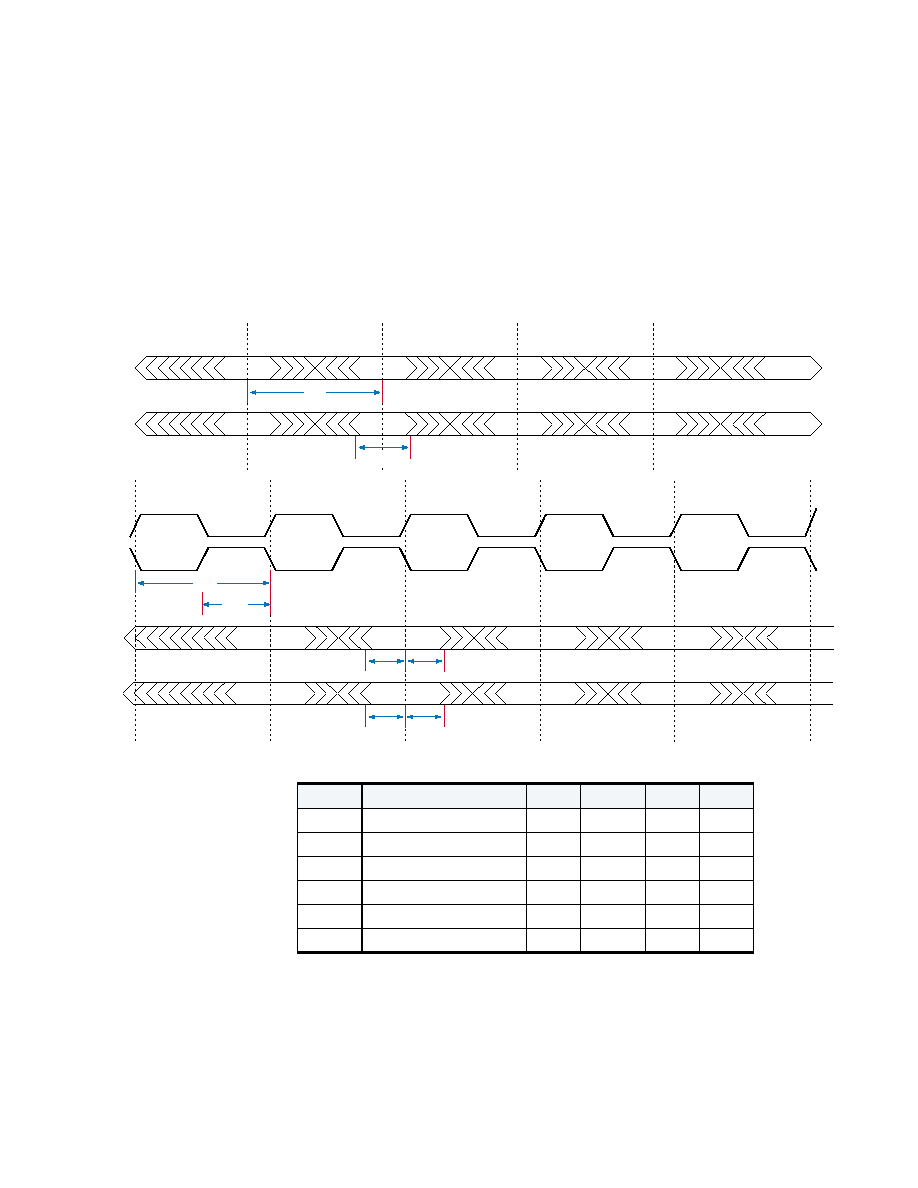

CP Timing Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

83

DS1/DS3 Timing Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

83

10/100 Ethernet Timing Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

84

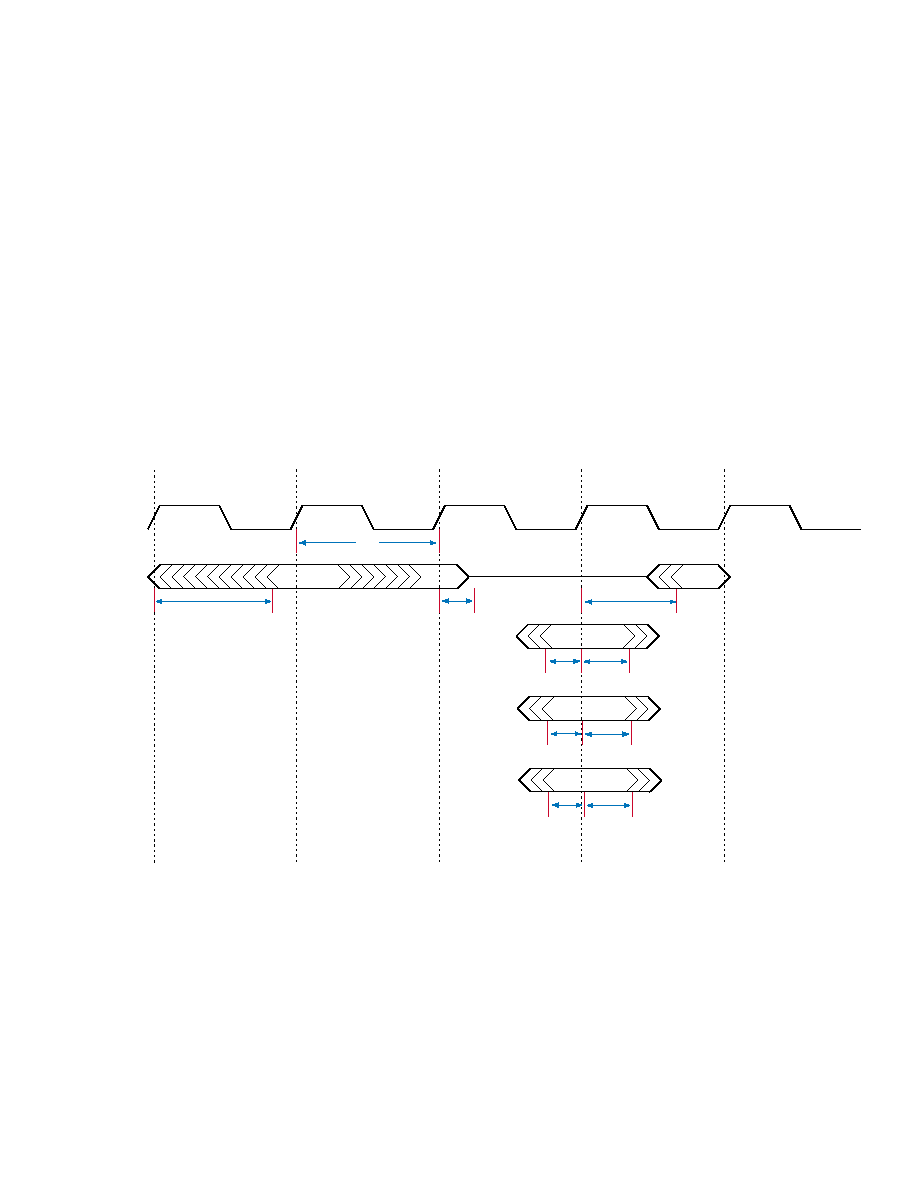

Gigabit GMII Ethernet, TBI and MII Interface Timing Specifications . . . . . . . . . . . . . . . . . .

85

OC-3 Timing Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

87

OC-12 Timing Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

88

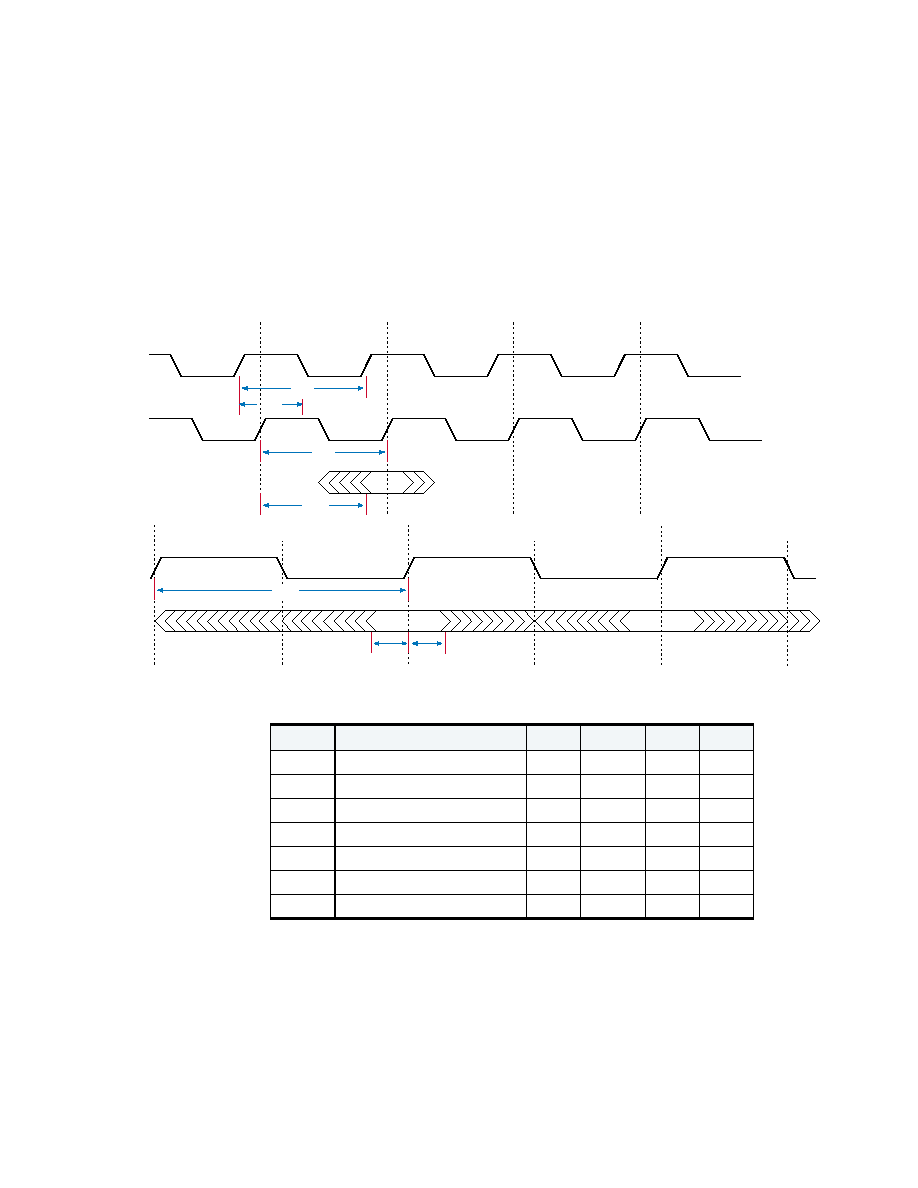

Executive Processor Timing Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

89

PCI Timing Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

89

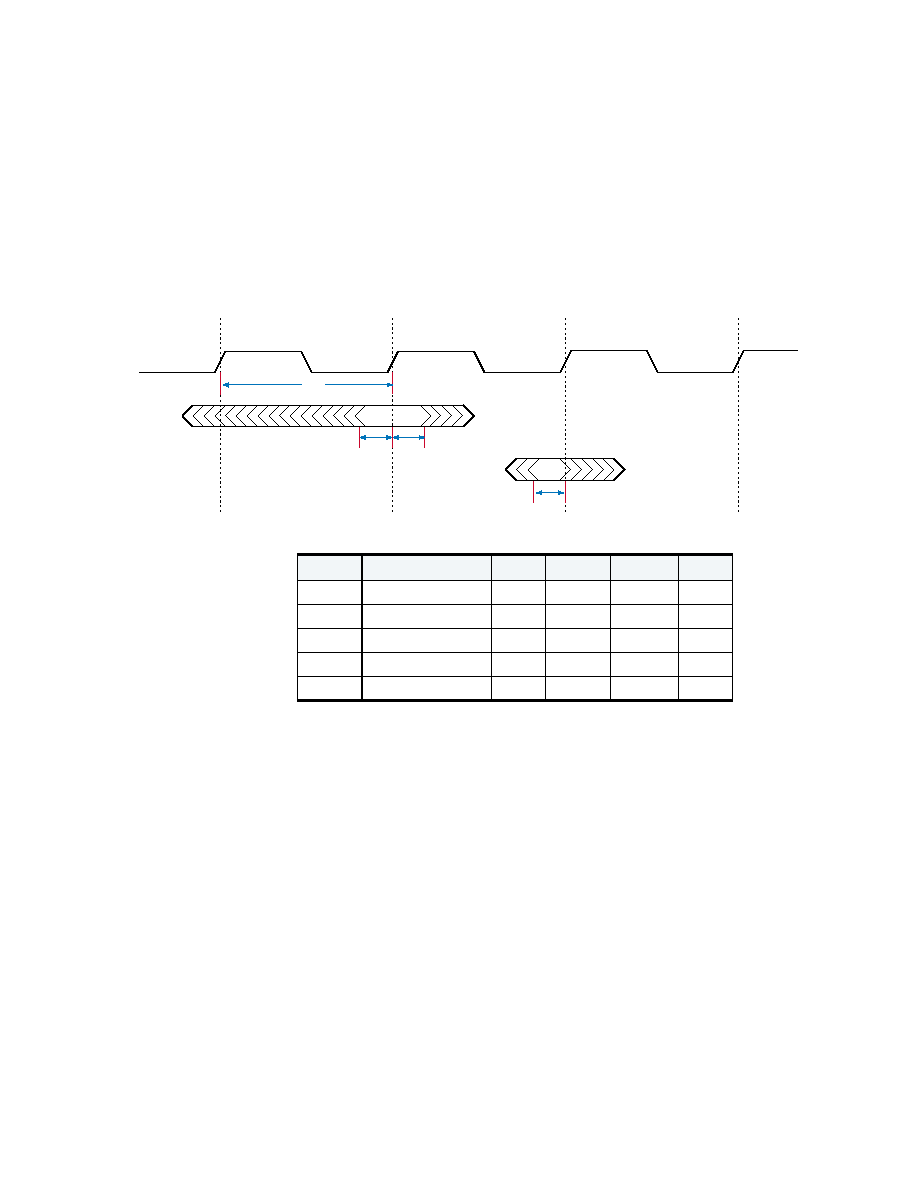

MDIO Serial Interface Timing Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

91

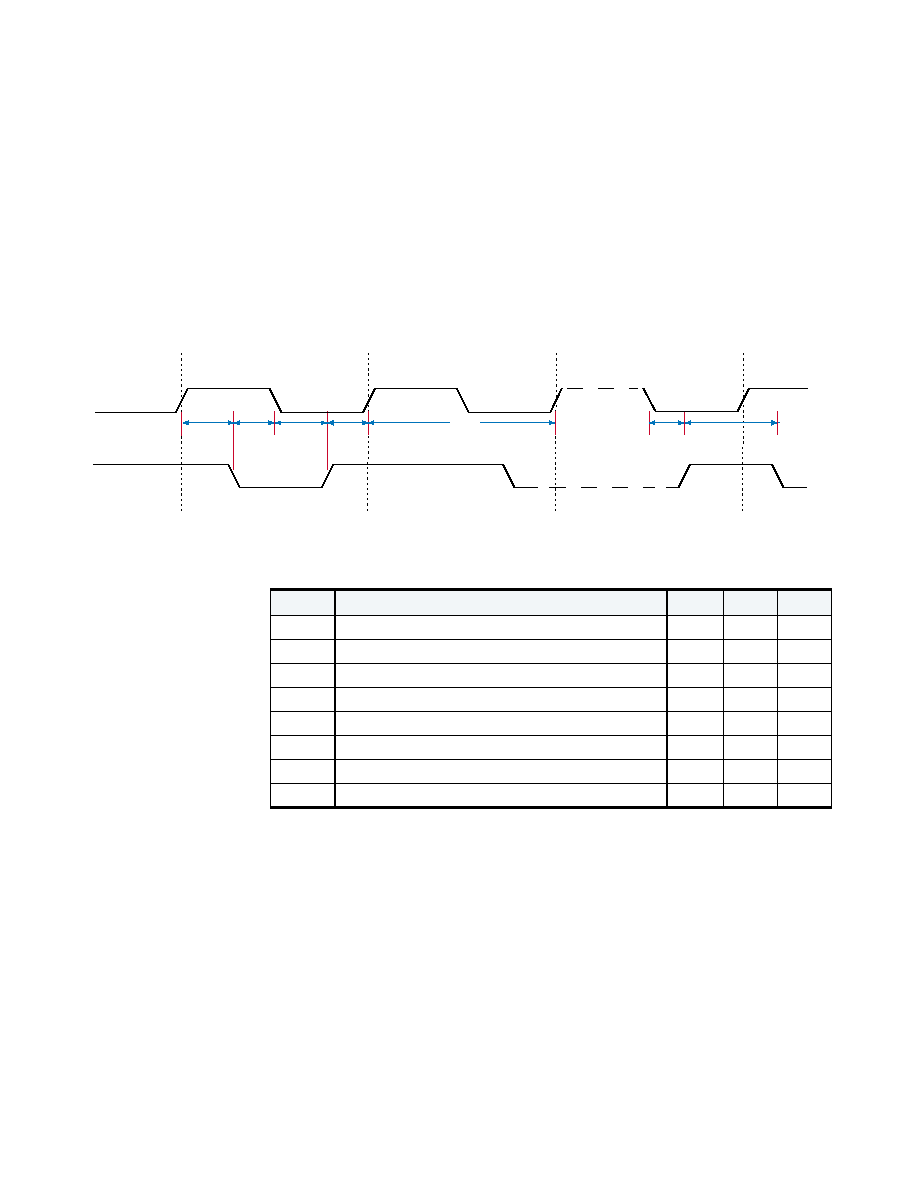

Low Speed Serial Interface Timing Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

92

PROM Interface Timing Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

93

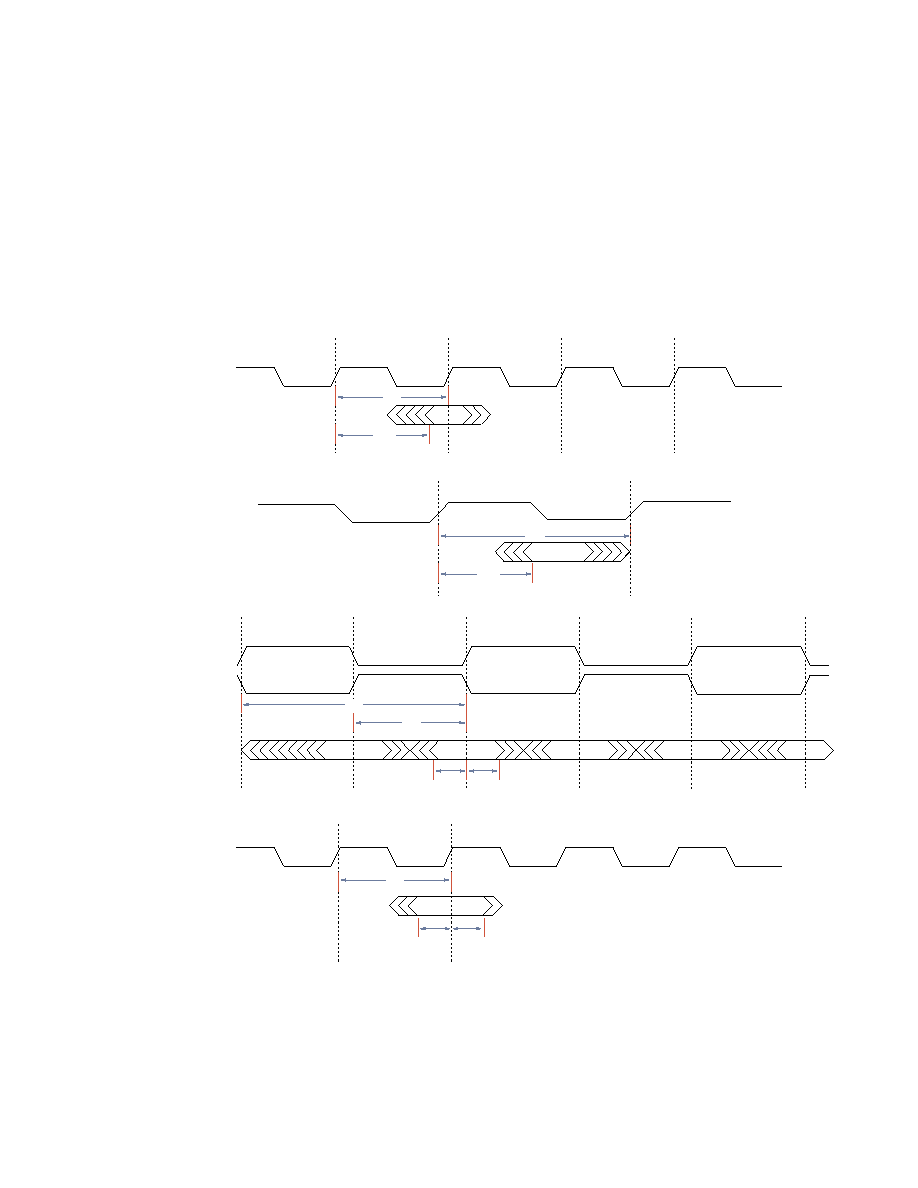

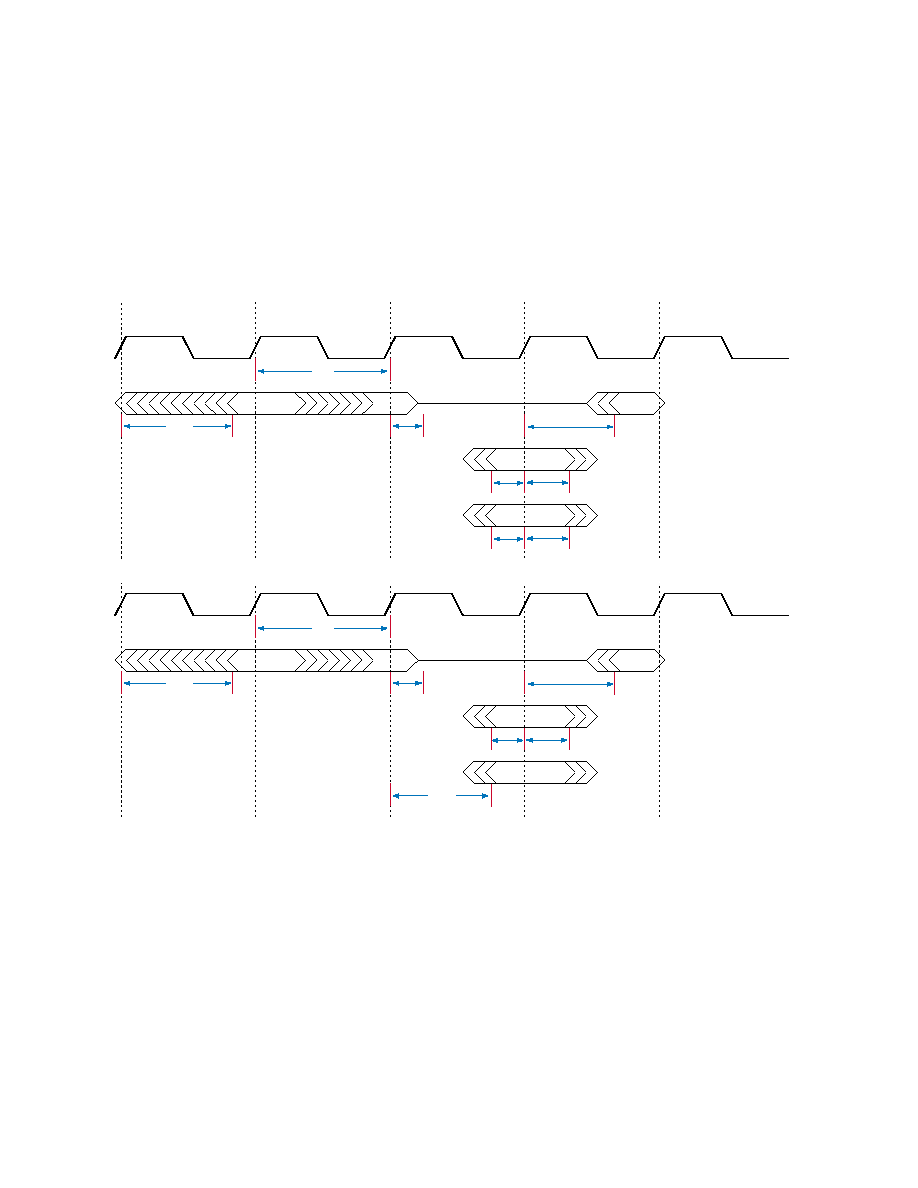

Fabric Processor Timing Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

94

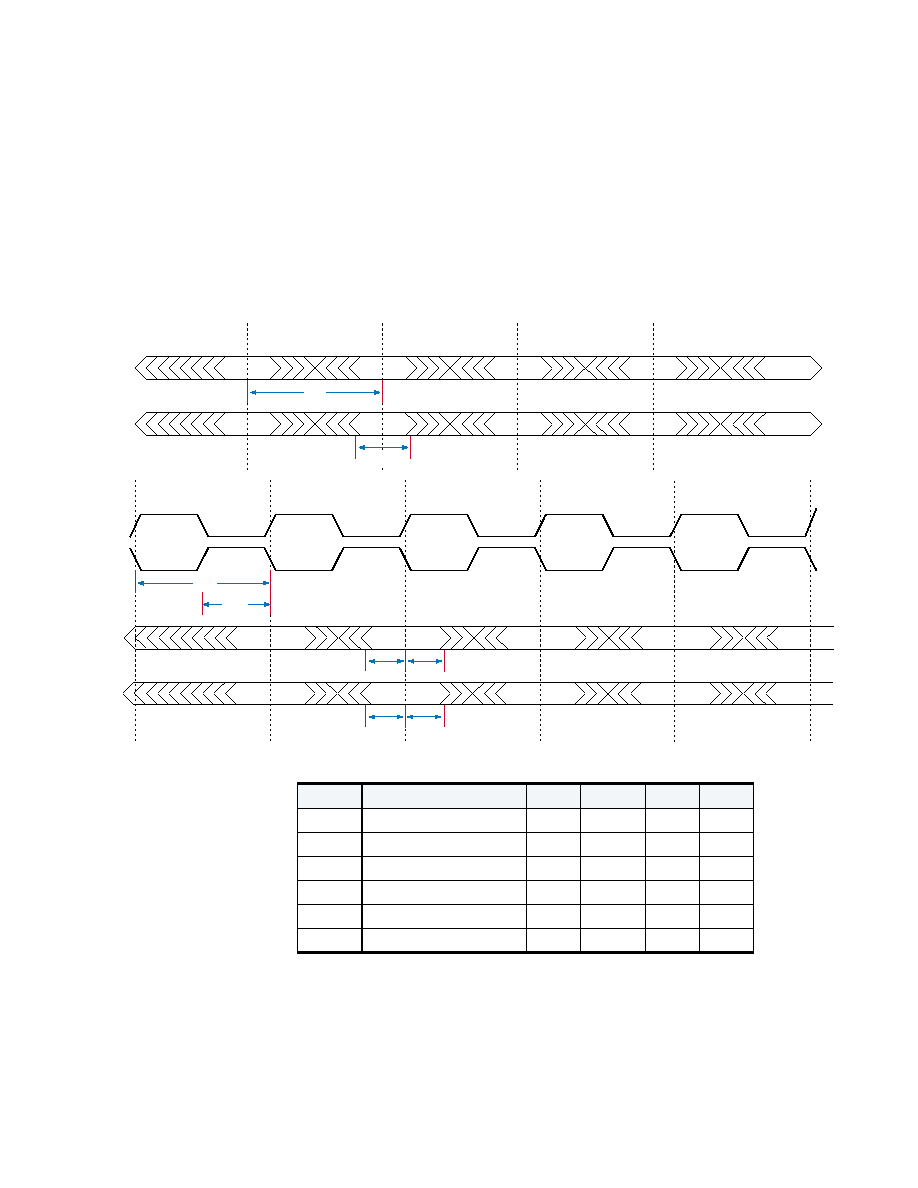

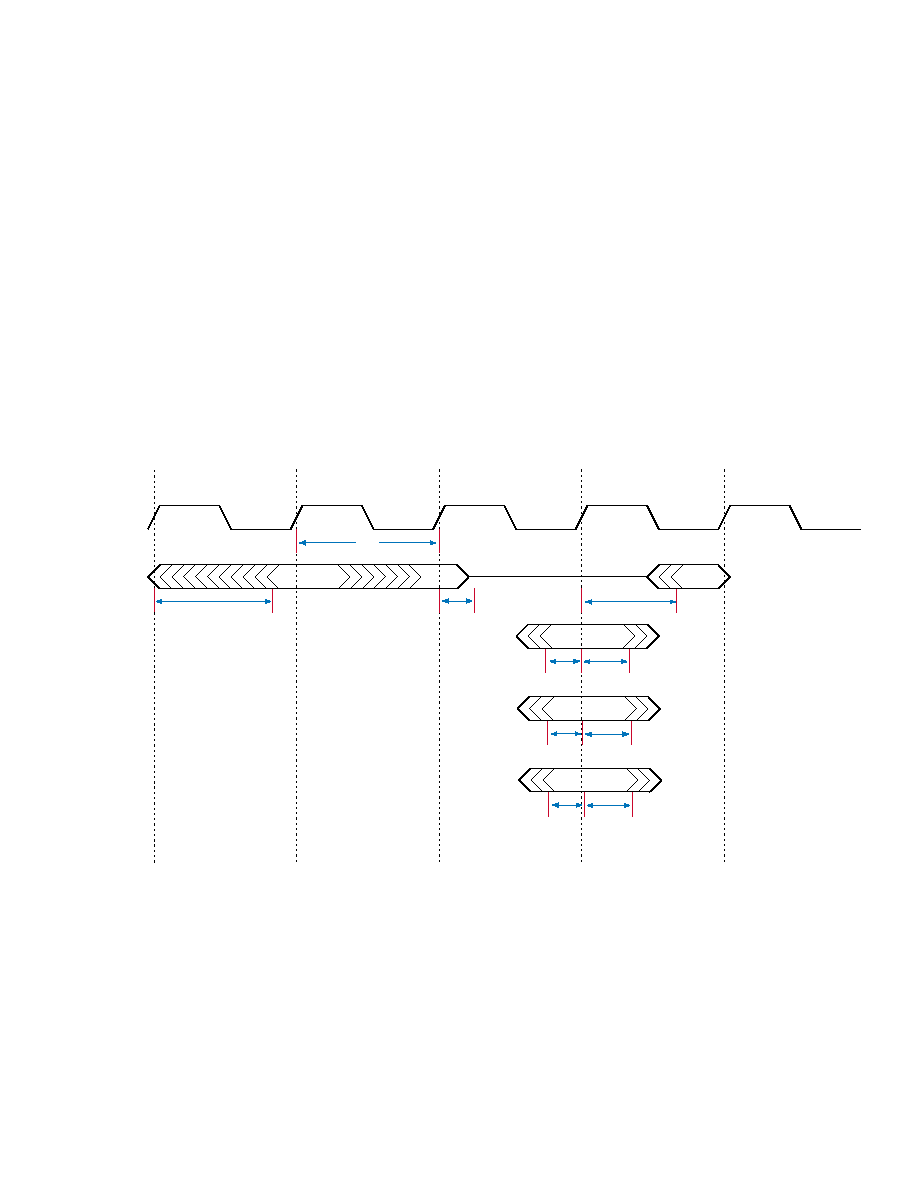

BMU Timing Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

96

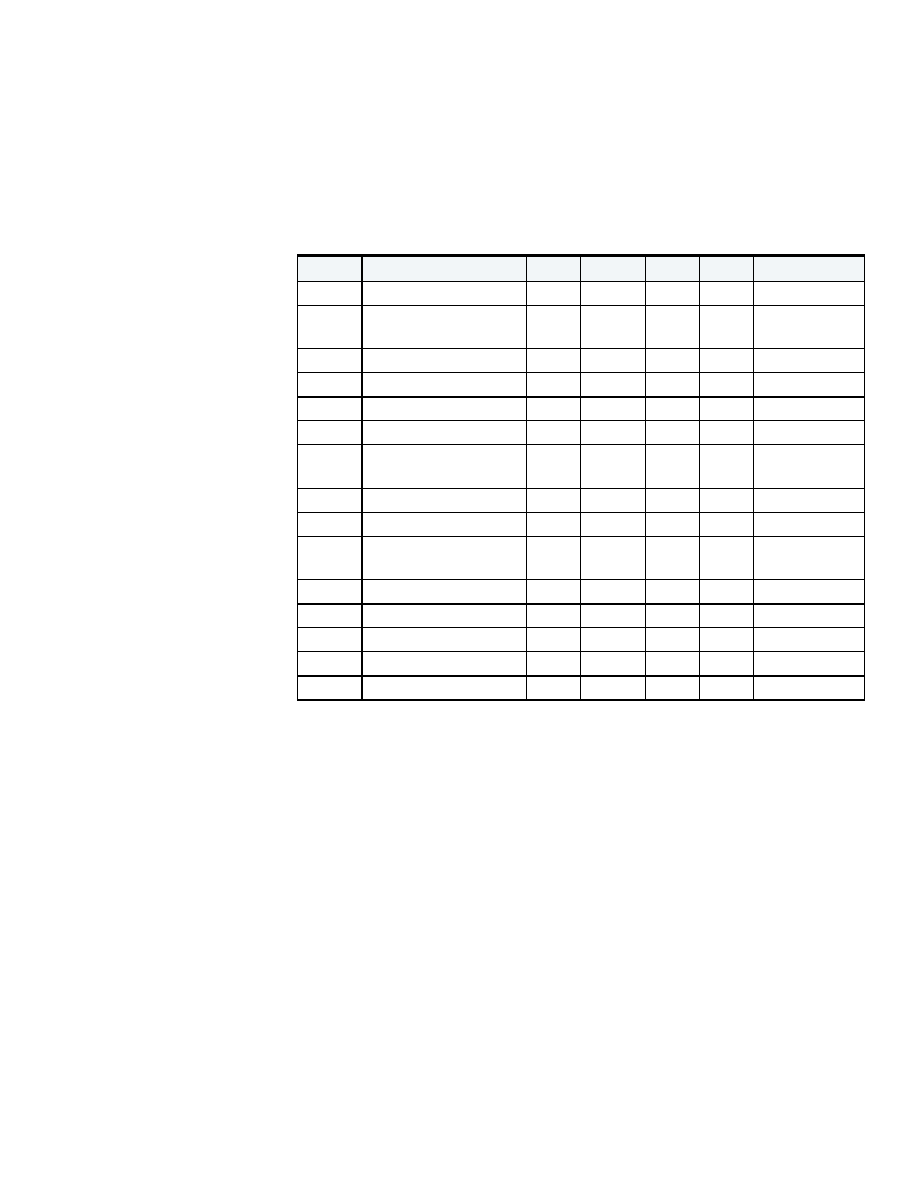

TLU Timing Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

98

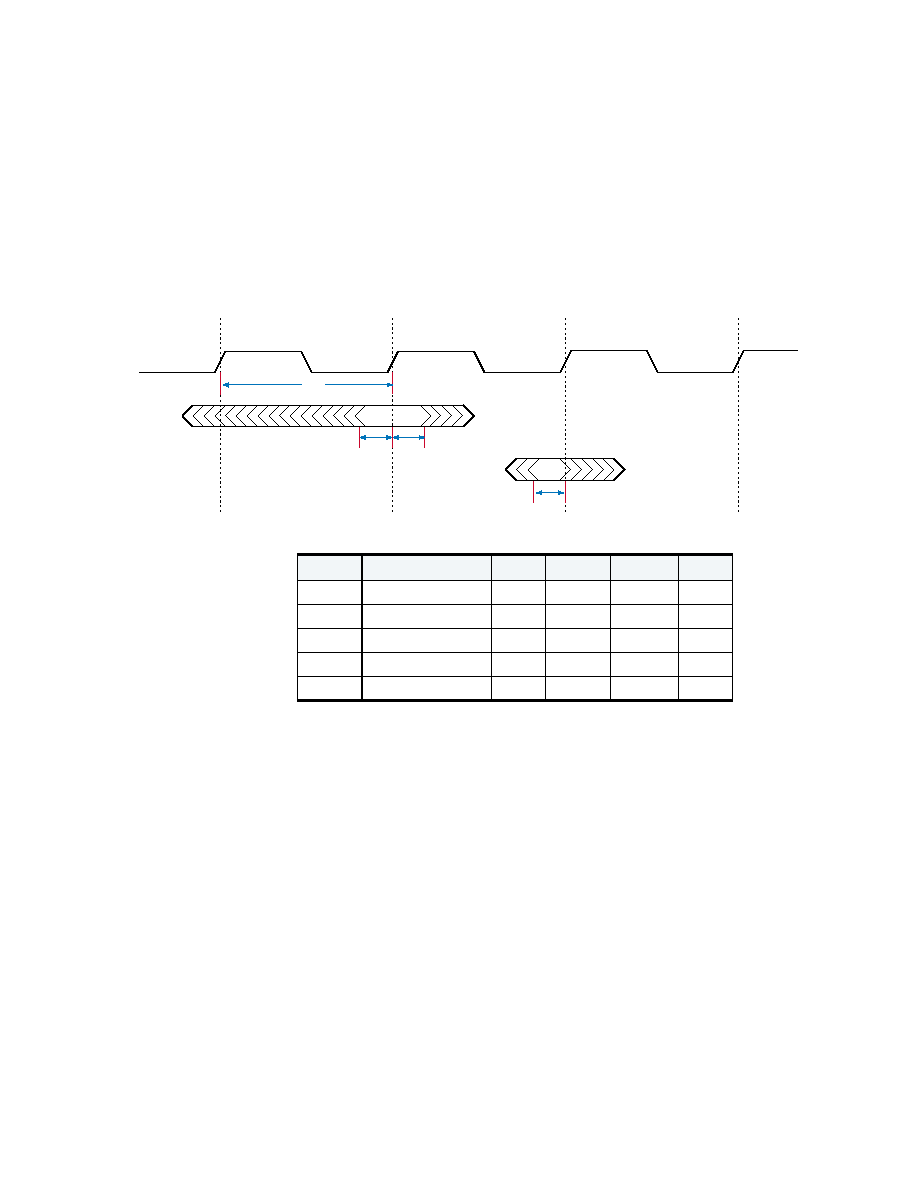

QMU SRAM (Internal Mode) Timing Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

99

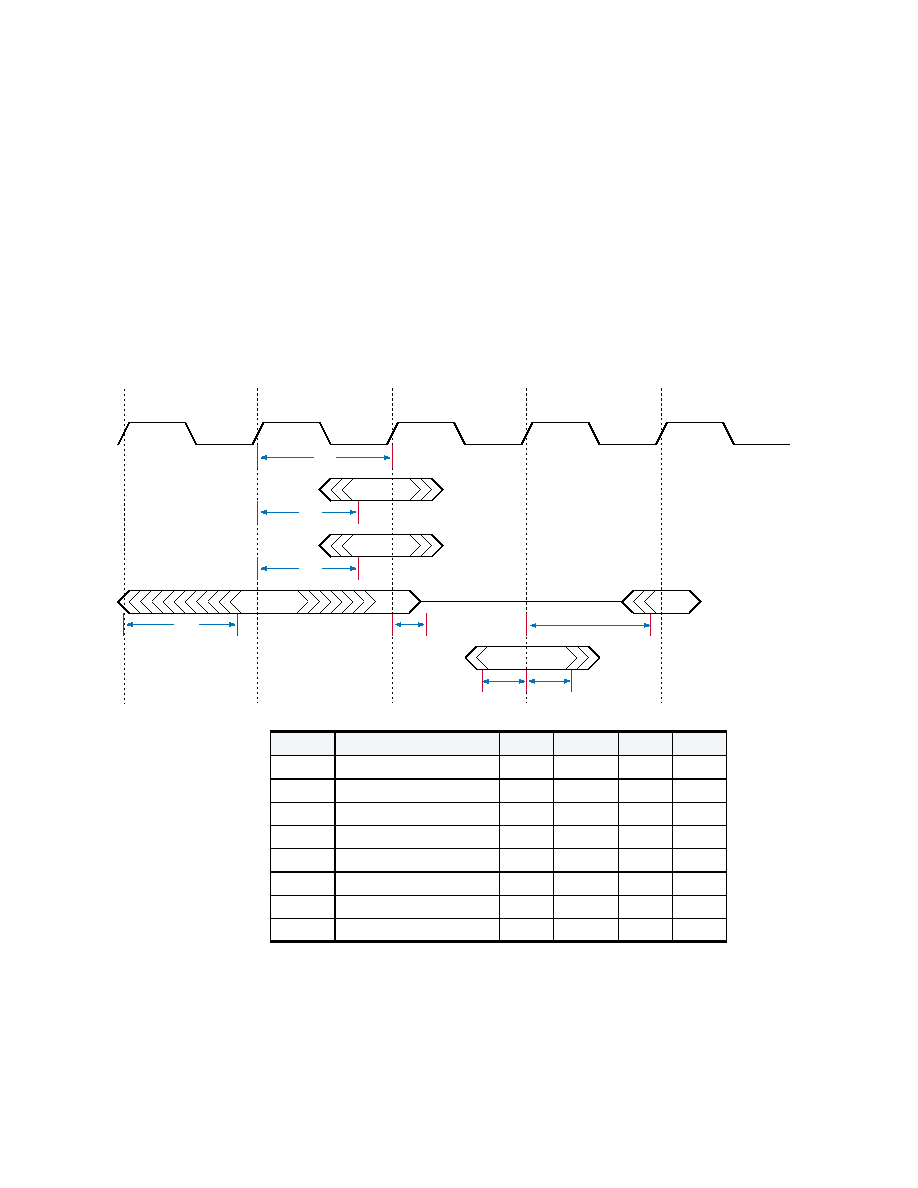

QMU to Q-5 (External Mode) Timing Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

101

C

HAPTER

4

Mechanical Specifications

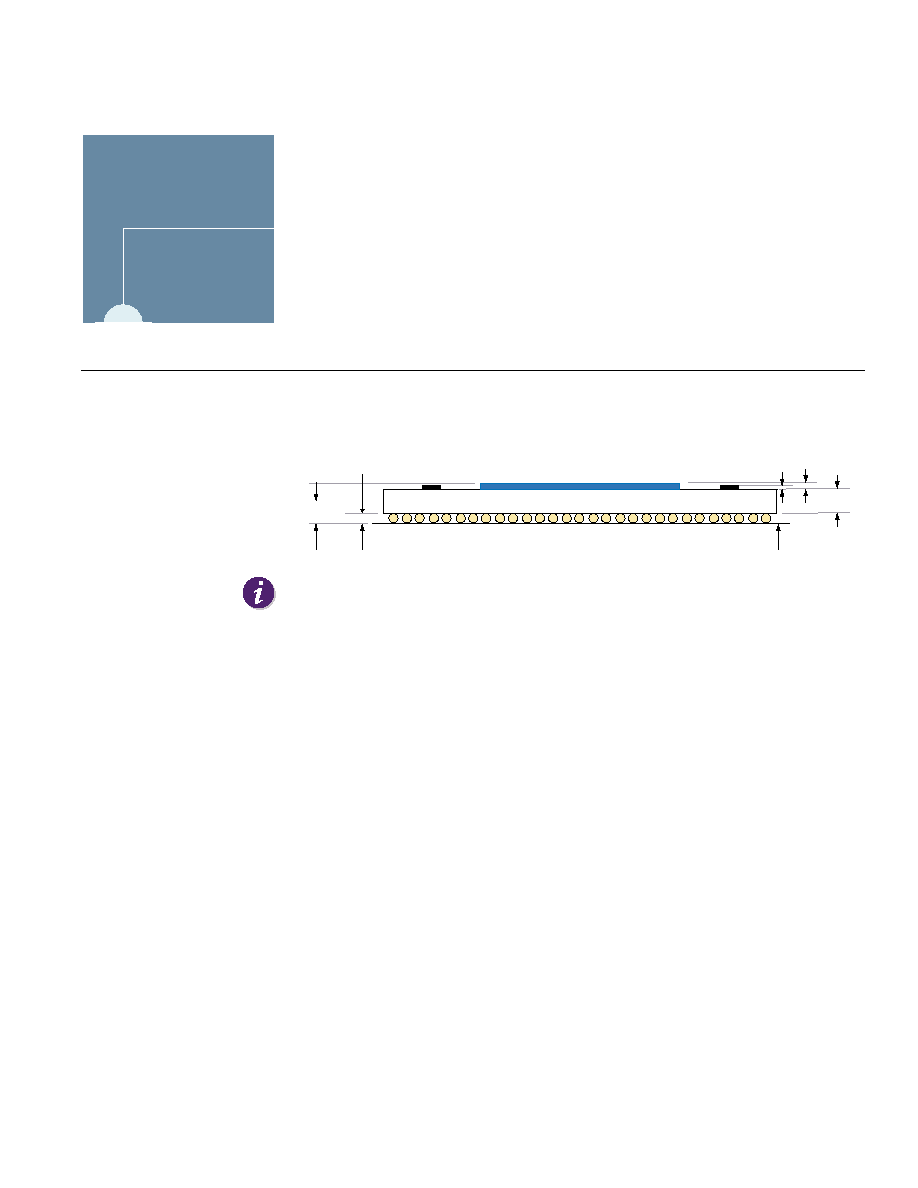

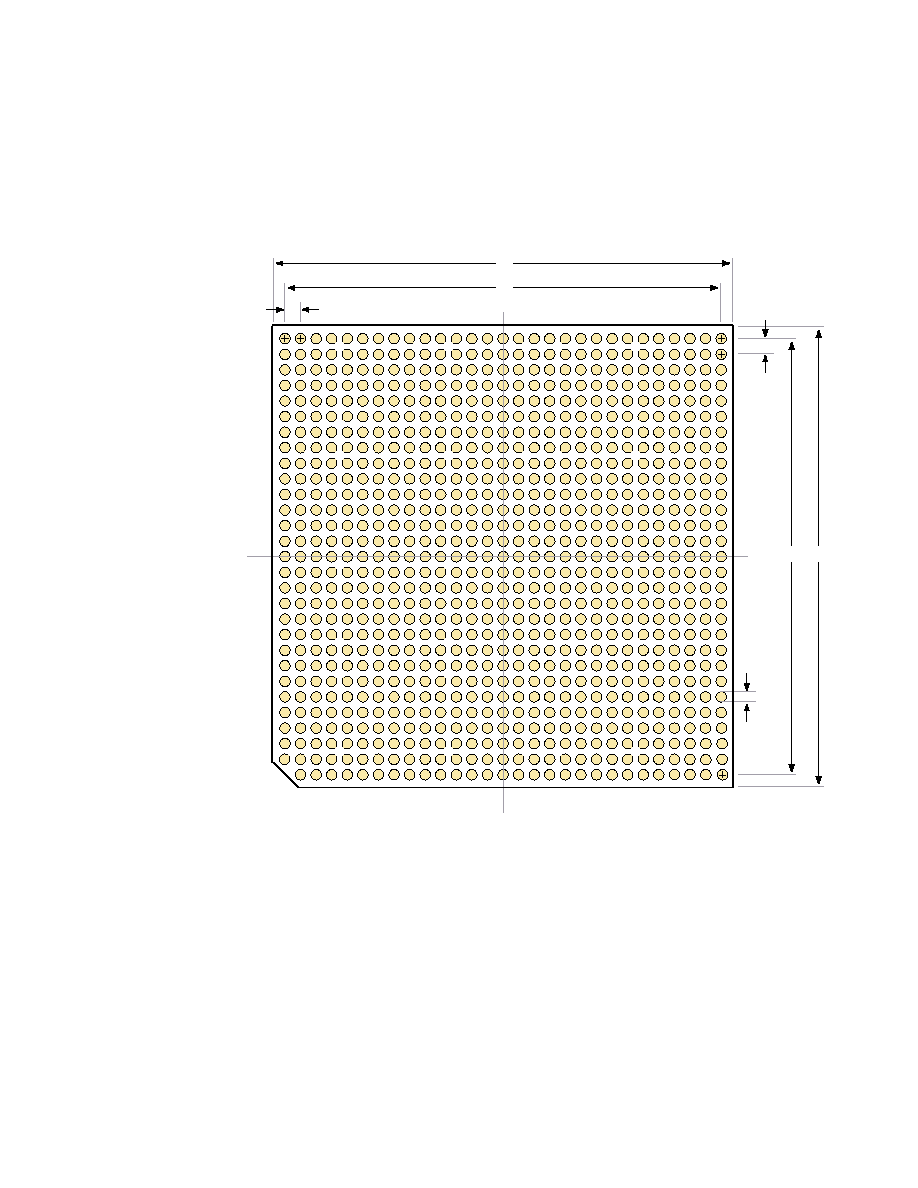

Package Views . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

103

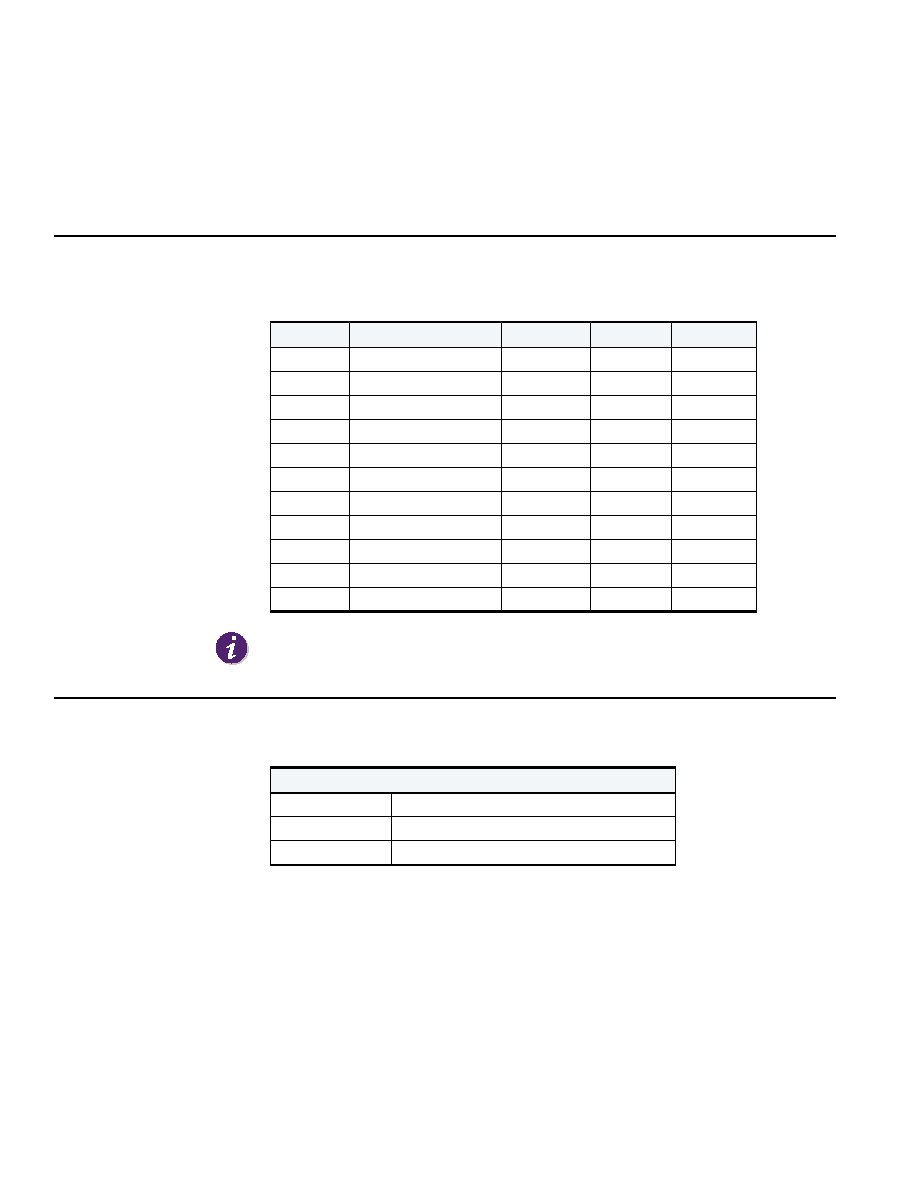

Package Measurements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

106

Marking Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

106

Reflow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

107

Index

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

109

8

CONTENTS

C5ENPA1-DS/D REV 03

MOTOROLA GENERAL BUSINESS INFORMATION

MOTOROLA GENERAL BUSINESS INFORMATION

C5ENPA1-DS/D REV 03

C5ENPA1-DS/D

Rev 03

LIST OF FIGURES

1

C-5e Network Processor Block Diagram

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2

Pin Locations (Top View)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3

Pin Locations (Bottom View)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

4

GMII/TBI Transmit and Receive Pin Configurations

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

5

PROM Interface Diagram

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

6

PROM Interface Timing Outline

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

7

Observe-Only Cell

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

8

Cell Design That Can Be Used for Both Input and Output Pins

. . . . . . . . . . . . . . . . . . . . . . . . . . . 70

9

Bringup Clock Timing Diagram

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

10

Package Cross Section View with Several Heat Sink Options

. . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

11

Package with Heat Sink Mounted to the Printed Circuit Board

. . . . . . . . . . . . . . . . . . . . . . . . . . . 79

12

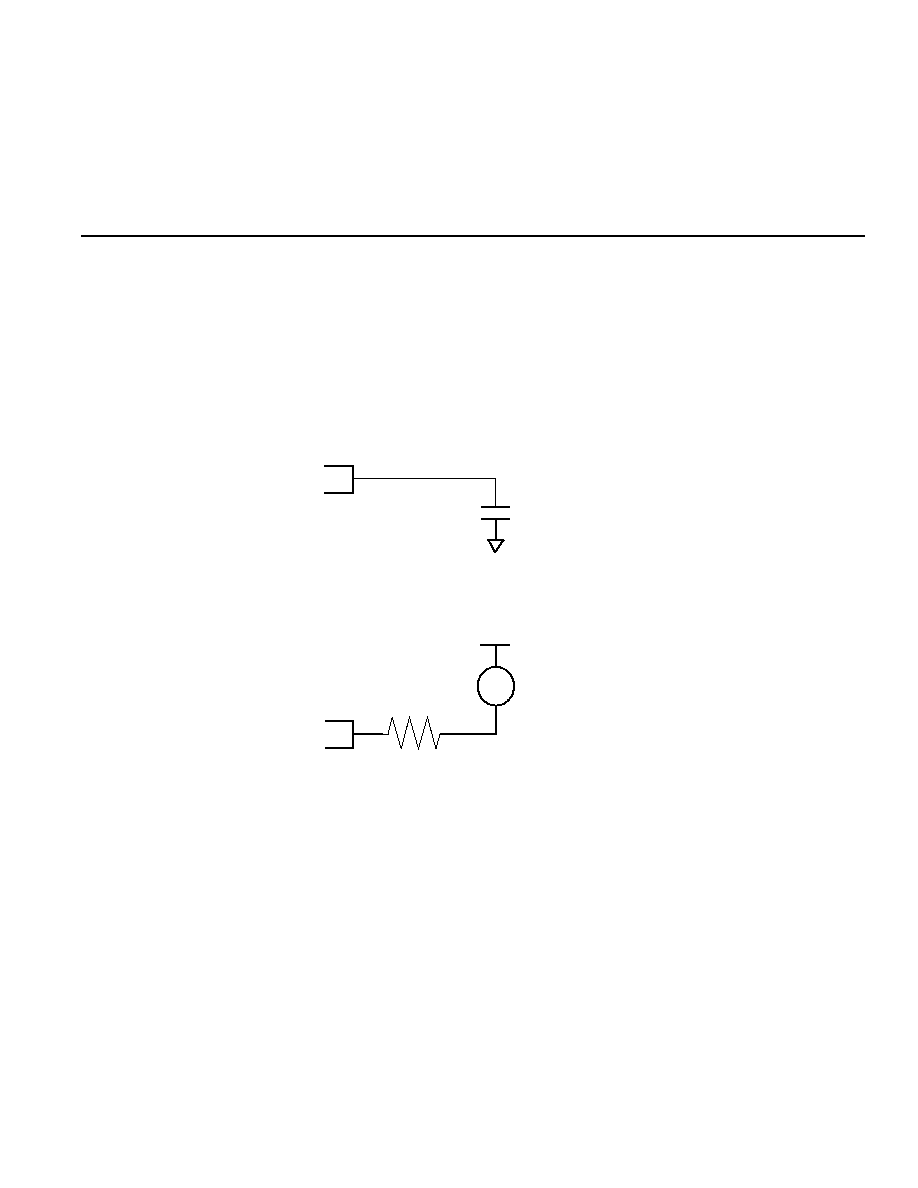

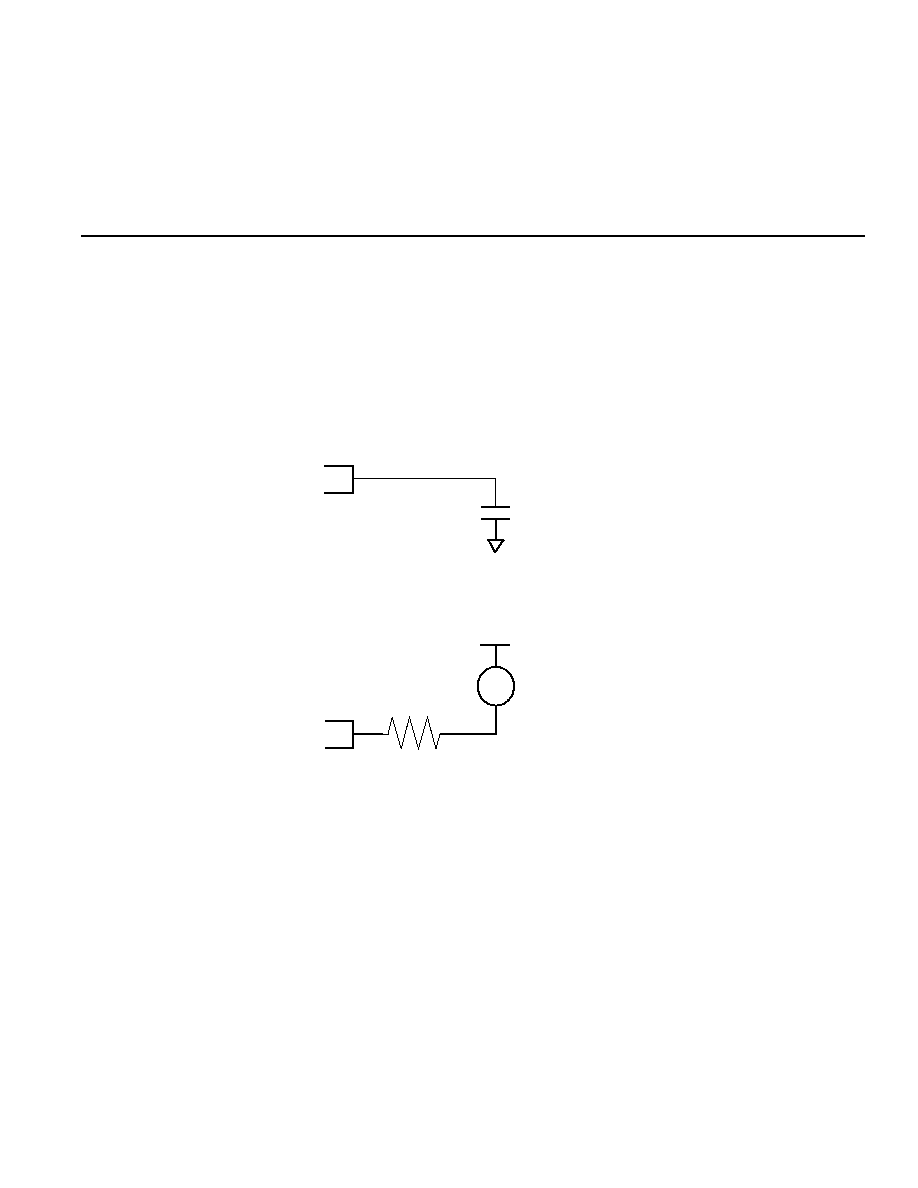

Test Loading Conditions

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

13

System Clock Timing Diagram

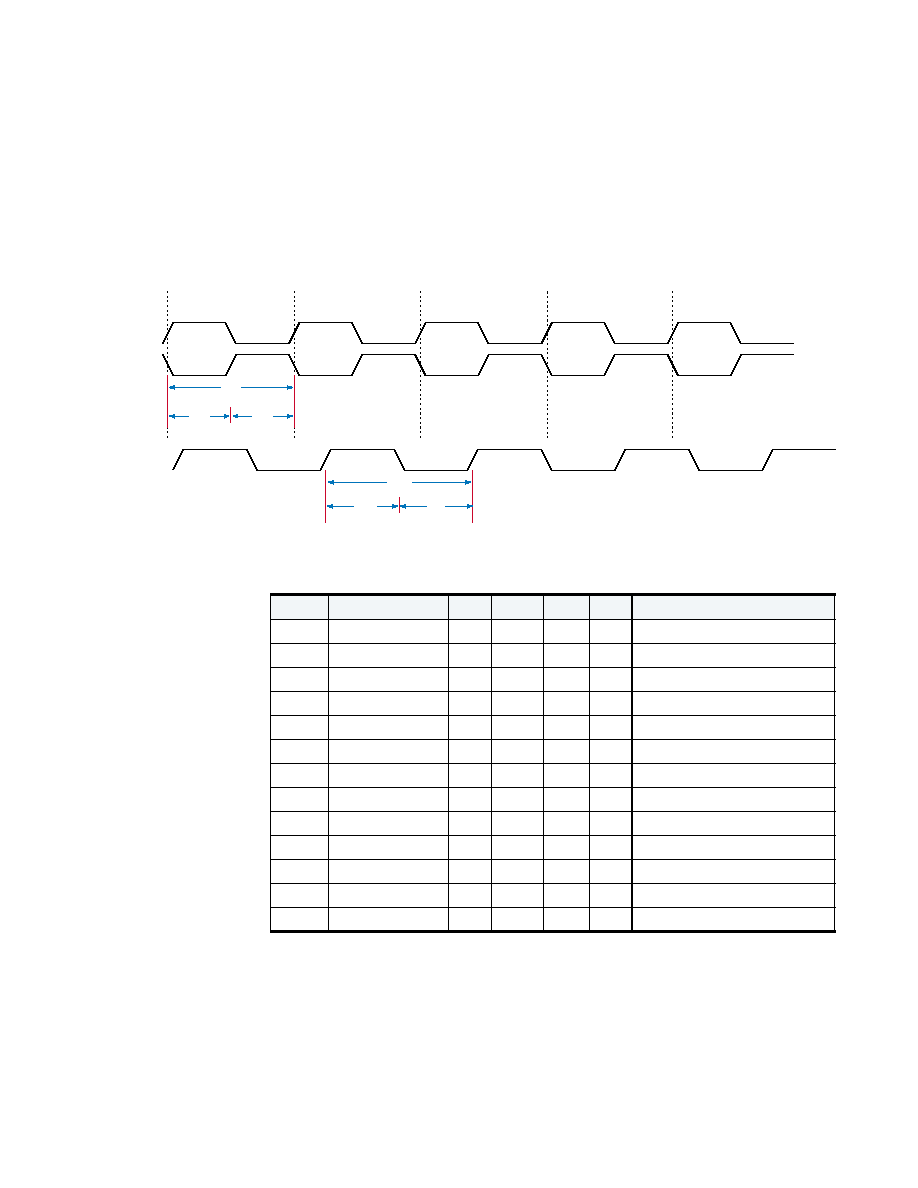

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

14

DS1/DS3 Ethernet Timing Diagram

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

15

10/100 Ethernet Timing Diagram

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

16

Gigabit Ethernet and TBI Interface Timing Diagram

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

17

OC-3 Timing Diagram

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

18

OC-12 Timing Diagram

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

19

PCI Timing Diagram

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

20

MDIO Serial Interface Timing Diagram

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

21

Low Speed Serial Interface Timing Diagram

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

22

PROM Interface Timing Diagram

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

23

Fabric Processor Timing Diagram

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

24

BMU Timing Diagram

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

25

TLU Timing Diagram

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

26

QMU SRAM (Internal Mode) Timing Diagram

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

27

QMU to Q-5 (External Mode) Timing Diagram

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

28

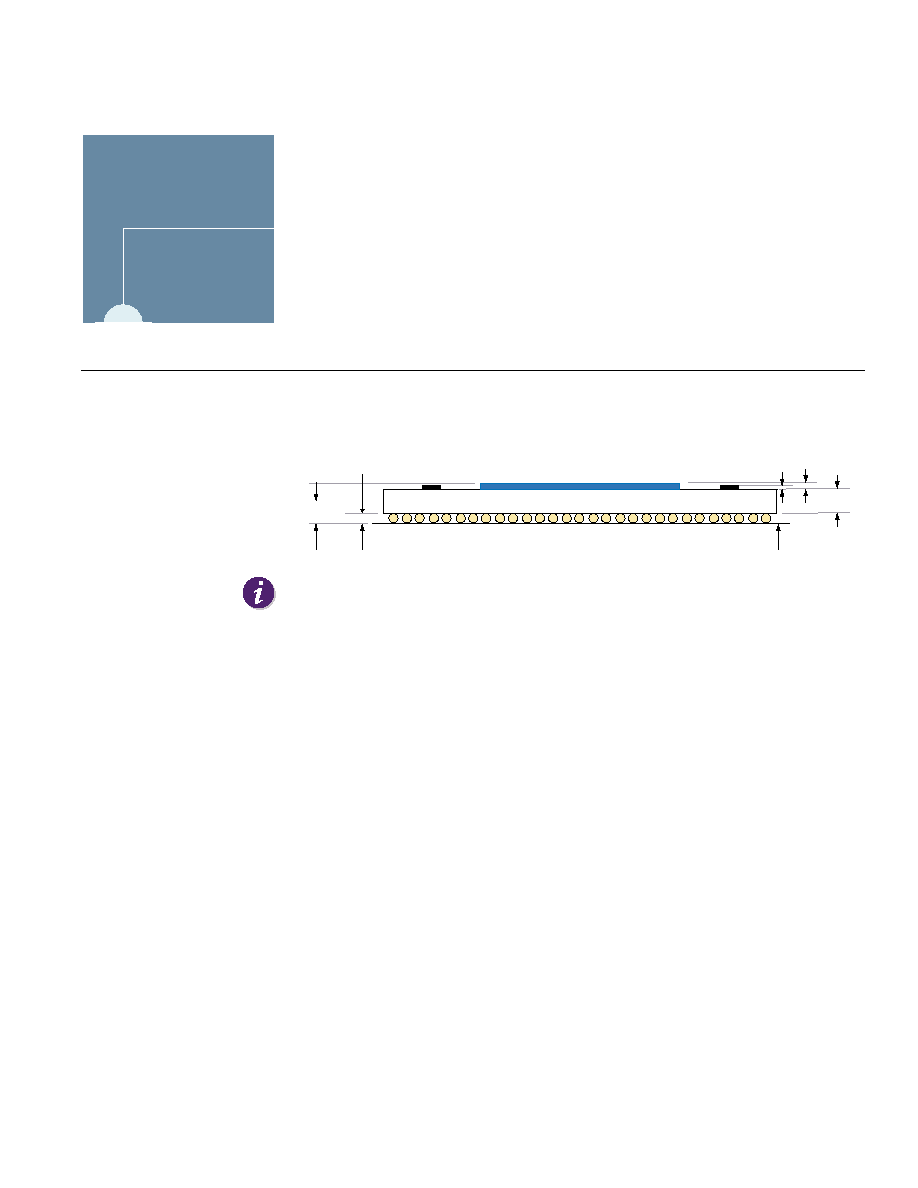

C-5e Network Processor BGA Package Side View

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

29

C-5e Network Processor BGA Package (Bottom View)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

30

C-5e Network Processor BGA Package (Top View)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

10

LIST OF FIGURES

C5ENPA1-DS/D REV 03

MOTOROLA GENERAL BUSINESS INFORMATION

MOTOROLA GENERAL BUSINESS INFORMATION

C5ENPA1-DS/D REV 03

C5ENPA1-DS/D

Rev 03

LIST OF TABLES

1

Data Sheet Classifications

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2

Navigating Within a PDF Document

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3

C-5e Network Processor Data Sheet Revision History

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

4

C-Port Silicon Documentation Set

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5

TLU SRAM Configurations

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

6

Clock and Reference Signals

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

7

CP Physical Interface Signals and Pins (Grouped by Clusters)

. . . . . . . . . . . . . . . . . . . . . . . . . . . 33

8

DS1/T1 Framer Interface Signals

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

9

10/100 Ethernet Signals

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

10

Transmit and Receive Pin Combinations for Gigabit Ethernet and Fibre Channel

. . . . . . . . . . . 35

11

Gigabit Ethernet (GMII/MII) Signals One Cluster Example

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

12

Gigabit Ethernet and Fibre Channel TBI Signals Example

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

13

OC-3 Signals

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

14

OC-12 Signals Example

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

15

PCI Signals

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

16

Serial Interface Signals

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

17

PROM Interface Signals

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

18

General System Interface Signal

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

19

Fabric Interface Signals

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

20

Utopia1*, 2, 3 ATM Mode, C-5e Network Processor to Fabric Interface Pin Mapping

. . . . . . 49

21

Utopia1*, 2, 3 PHY Mode, C-5e Network Processor to Fabric Interface Pin Mapping

. . . . . . . 49

22

PRIZMA Mode, C-5e Network Processor to Fabric Interface Pin Mapping

. . . . . . . . . . . . . . . . 50

23

Power X(CSIX-L0) Mode, C-5e Network Processor to Fabric Interface Pin Mapping

. . . . . . . . 50

24

CSIX-L1 Mode, C-5e Network to Fabric Interface Pin Mapping

. . . . . . . . . . . . . . . . . . . . . . . . . . 51

25

BMU SDRAM Interface Signals

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

26

TLU SRAM Interface Signals

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

27

QMU SRAM (Internal Mode) Interface Signals

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

28

QMU to Q-5 (External Mode) Interface Signals

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

29

Power Supply Signals

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

30

Miscellaneous Test Signals For JTAG, Scan, and Internal Test Routines

. . . . . . . . . . . . . . . . 58

12

LIST OF TABLES

C5ENPA1-DS/D REV 03

MOTOROLA GENERAL BUSINESS INFORMATION

31

No Connection Pins

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

32

Signals Listed by Pin Number

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

33

JTAG Internal Register Descriptions

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

34

JTAG Identification Code and Its Subcomponents

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

35

Instruction Register Instructions

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

36

C-5e Network Processor Absolute Maximum Ratings

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

37

C-5e Network Processor Recommended Operating Conditions

. . . . . . . . . . . . . . . . . . . . . . . . . .74

38

C-5e Network Processor DC Characteristics

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

39

C-5e Network Processor Capacitance Data

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

40

C-5e Network Processor Power and Thermal Characteristics

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

41

System Clock Timing Description

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82

42

DS1/DS3 Ethernet Timing Description

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .84

43

10/100 Ethernet Timing Description

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .84

44

Gigabit GMII/MII Ethernet Interface Timing Description

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .86

45

Gigabit TBI Interface Timing Description

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .86

46

OC-3 Timing Description

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

47

OC-12 Timing Description

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .88

48

PCI Timing Description

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

49

MDIO Serial Interface Timing Description

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91

50

Low Speed Serial Interface Timing Description

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .92

51

PROM Interface Timing Description

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .93

52

Fabric Processor Timing Description

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .95

53

BMU Timing Description

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .96

54

Signal Groups in BMU Timing Diagrams

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .97

55

TLU Timing Description

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .98

56

Signal Groups in TLU Timing Diagrams

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .98

57

QMU SRAM (Internal Mode) Timing Description

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

58

Signal Groups in QMU SRAM (Internal Mode) Timing Diagrams

. . . . . . . . . . . . . . . . . . . . . . . 100

59

QMU to Q-5 (External Mode) Timing Description

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

60

Signal Groups in QMU to Q-5 (External Mode) Timimg Diagrams

. . . . . . . . . . . . . . . . . . . . . . . 102

61

Package Measurements (Reference

Figure 28

,

Figure 29

and

Figure 30

for Symbols)

. . . . 106

62

C-5e Network Processor Marking Codes

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

MOTOROLA GENERAL BUSINESS INFORMATION

C5ENPA1-DS/D REV 03

C5ENPA1-DS/D

Rev 03

ABOUT THIS GUIDE

Guide Overview

The C-5e Network Processor Data Sheet describes hardware layout specifications

including pinouts, memory configuration guidelines, timing diagrams, power and power

sequencing guidelines, thermal design guidelines, and mechanical specifications. This

document contains information on a pre-production product. Specifications and

information herein are subject to change without notice.

This guide assumes a good understanding of the C-5e

TM

Network Processor (NP)

architecture. See the C-5e/C-3e Network Processor Architecture Guide (part number

C5EC3EARCH-RM/D) for more detail about the hardware.

This guide also assumes good working knowledge of the C-Ware Software Toolset.

This guide covers the following topics:

�

Functional Description

�

Signal Descriptions

�

Electrical Specifications

�

Mechanical Specifications

14

ABOUT THIS GUIDE

C5ENPA1-DS/D REV 03

MOTOROLA GENERAL BUSINESS INFORMATION

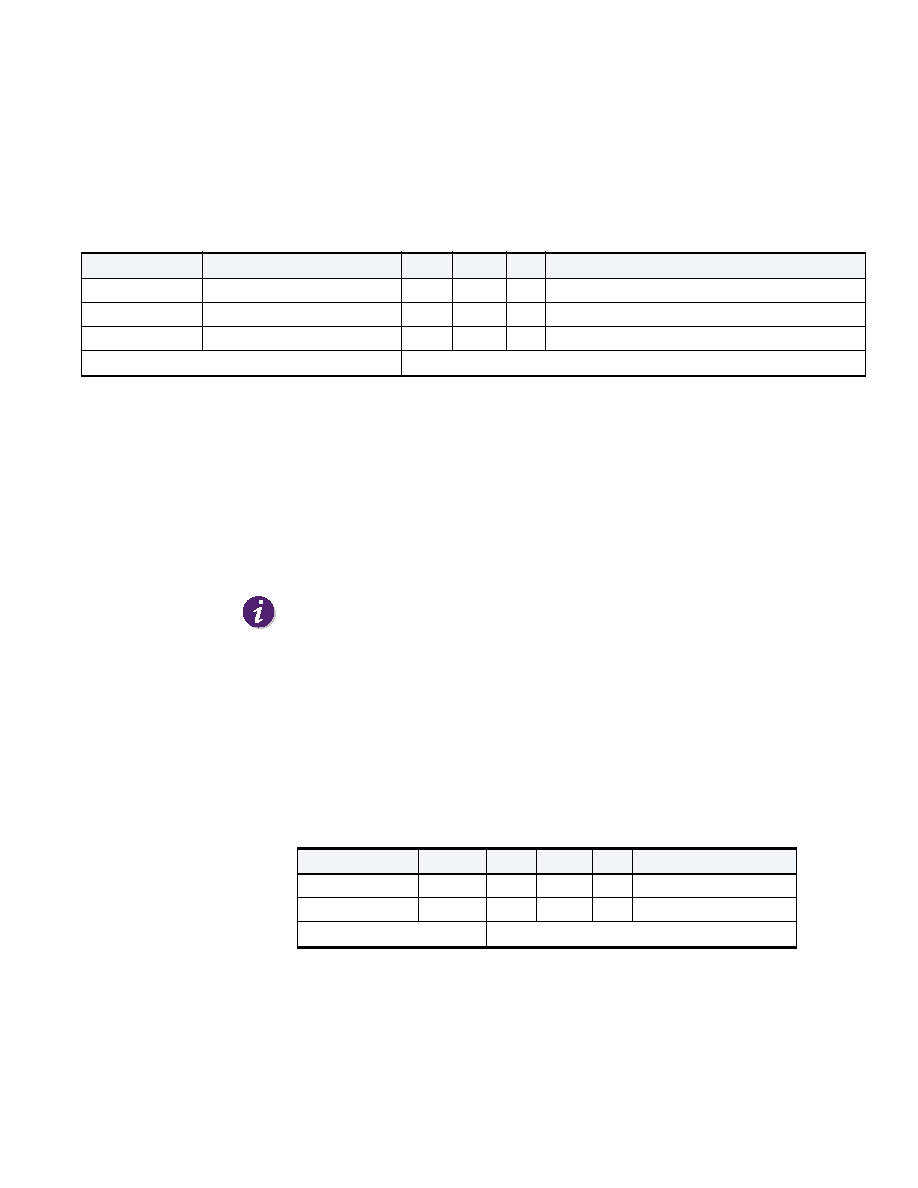

Data Sheet Classifications

Table 1

describes the Data Sheet classifications of Advance, Preliminary, and Production.

Using PDF Documents

Electronic documents are provided as PDF files. Open and view them using the Adobe�

Acrobat� Reader application, version 3.0 or later. If necessary, download the Acrobat

Reader from the Adobe Systems, Inc. web site:

http://www.adobe.com/prodindex/acrobat/readstep.html

PDF files offer several ways for moving among the document's pages, as follows:

�

To move quickly from section to section within the document, use the Acrobat

bookmarks that appear on the left side of the Acrobat Reader window. The bookmarks

provide an expandable outline view of the document's contents. To display the

document's Acrobat bookmarks, press the "Display both bookmarks and page" button

on the Acrobat Reader tool bar.

�

To move to the referenced page of an entry in the document's Contents or Index, click

on the entry itself, each of which is hyperlinked.

�

To follow a

cross-reference

to a heading, figure, or table, click the blue text.

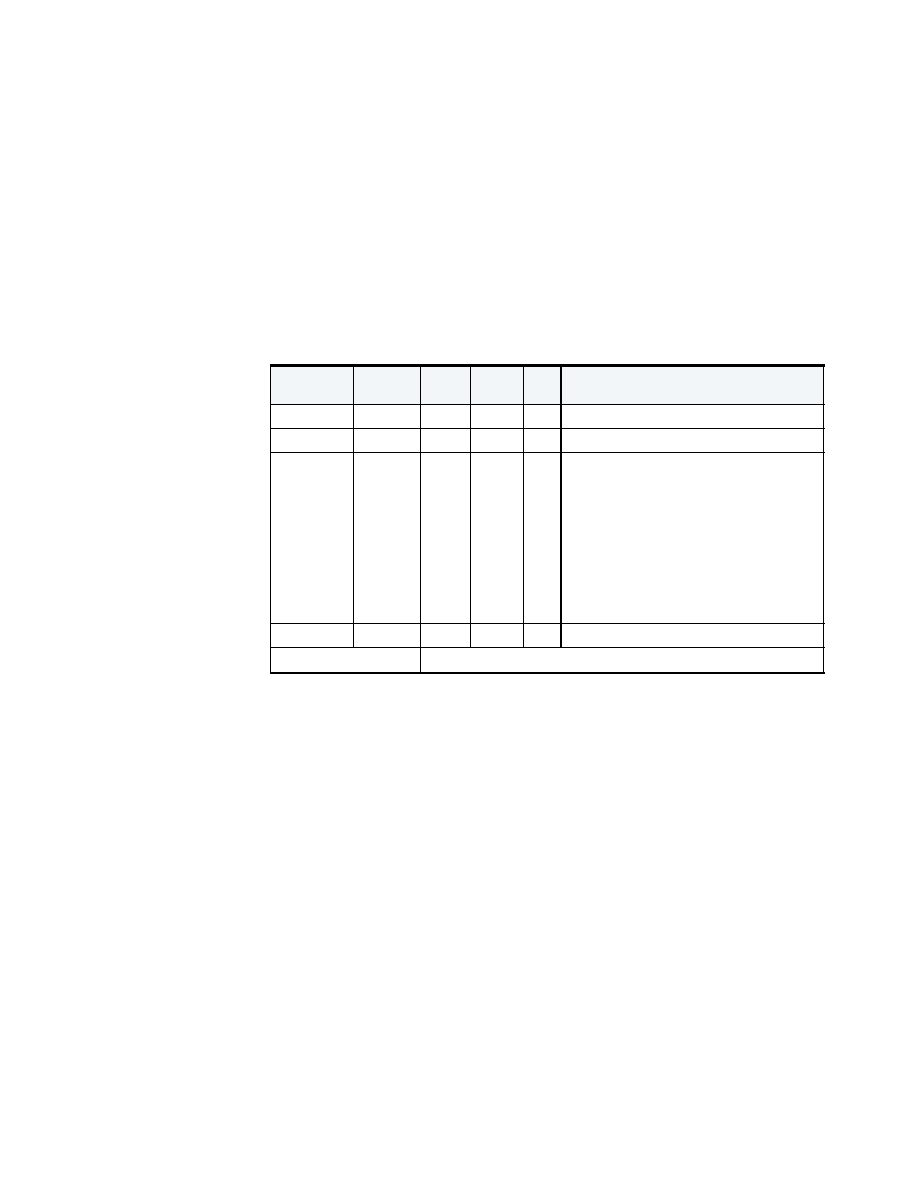

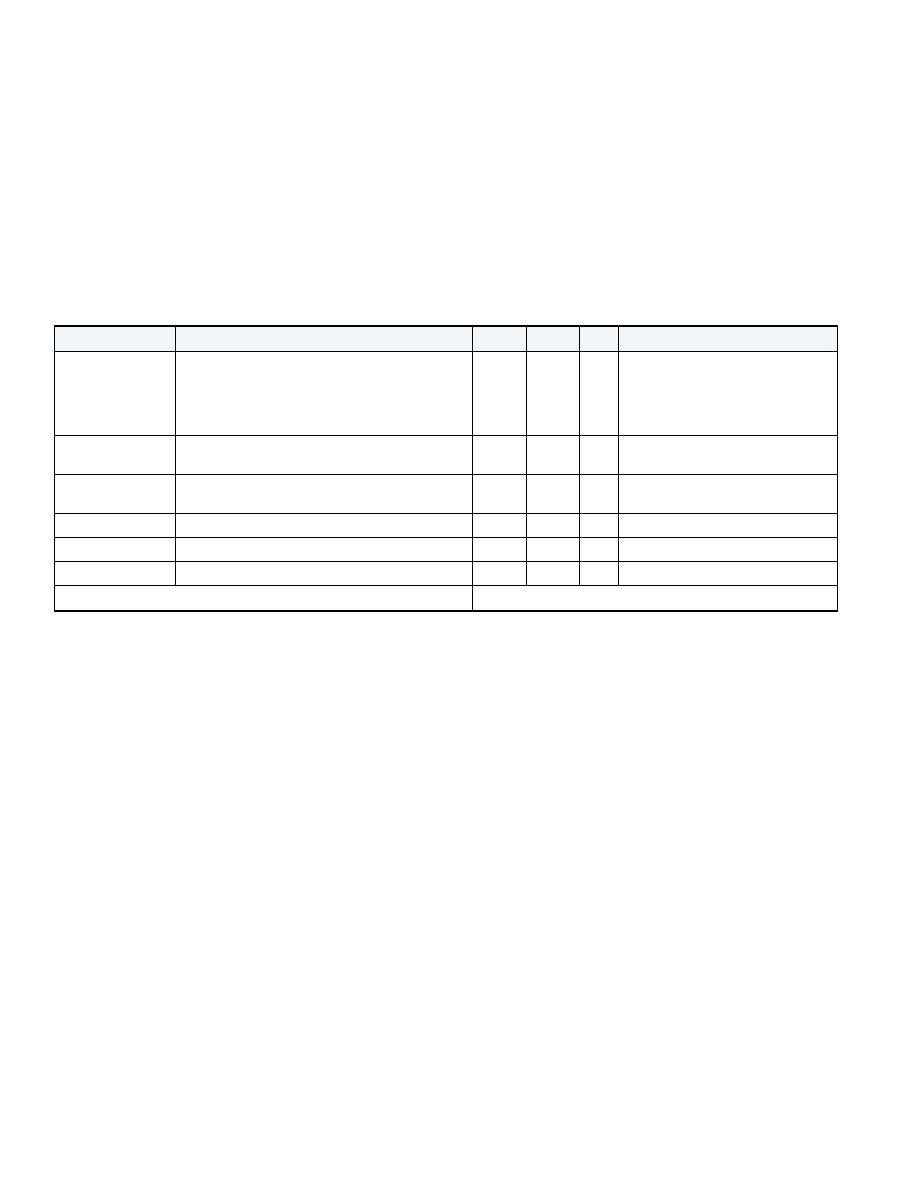

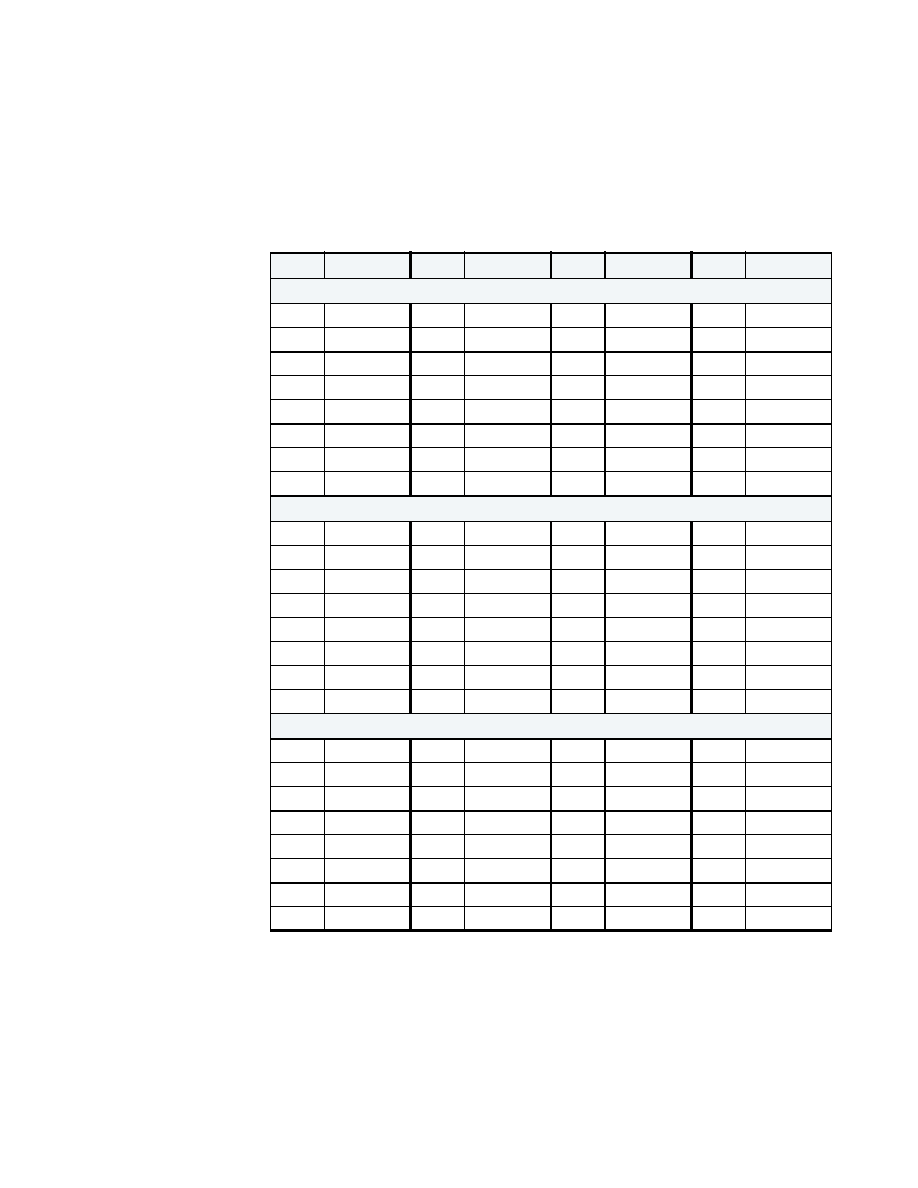

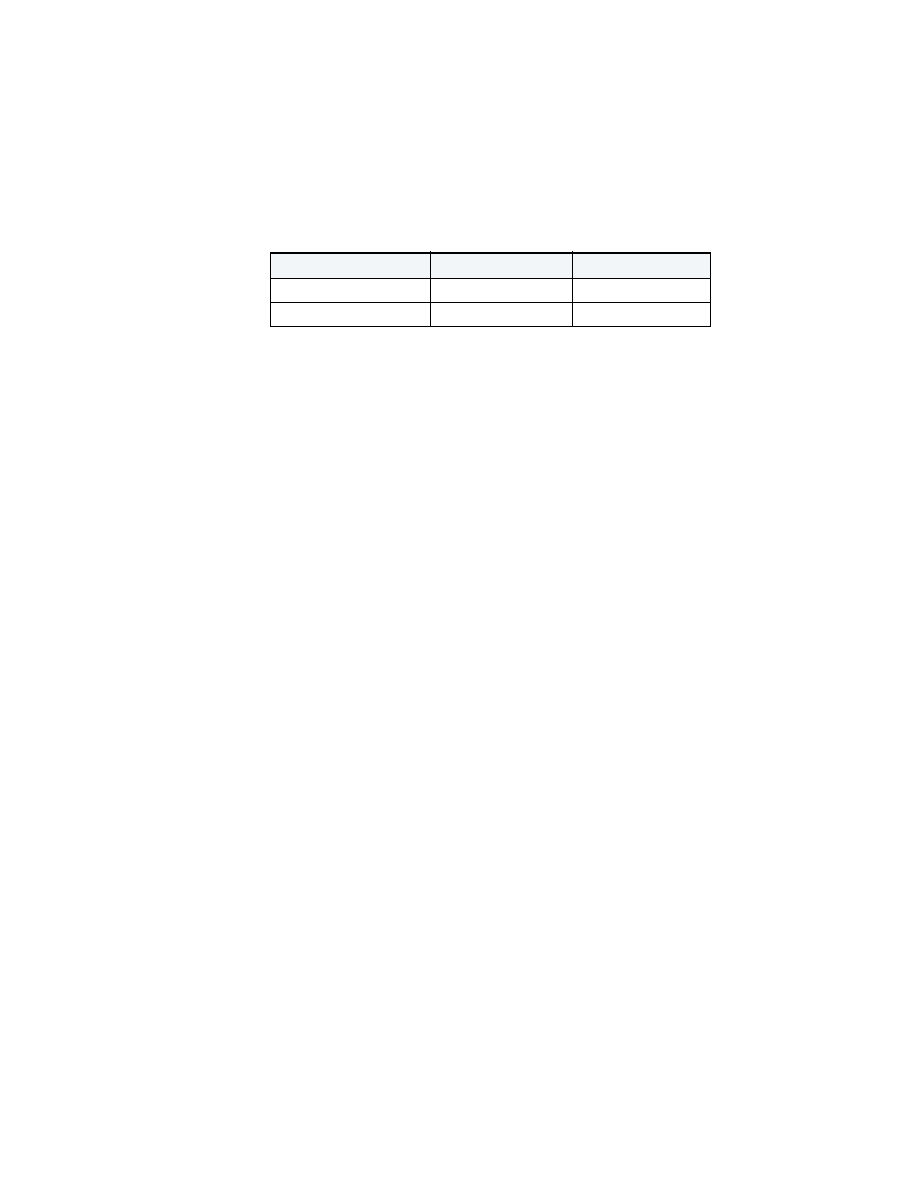

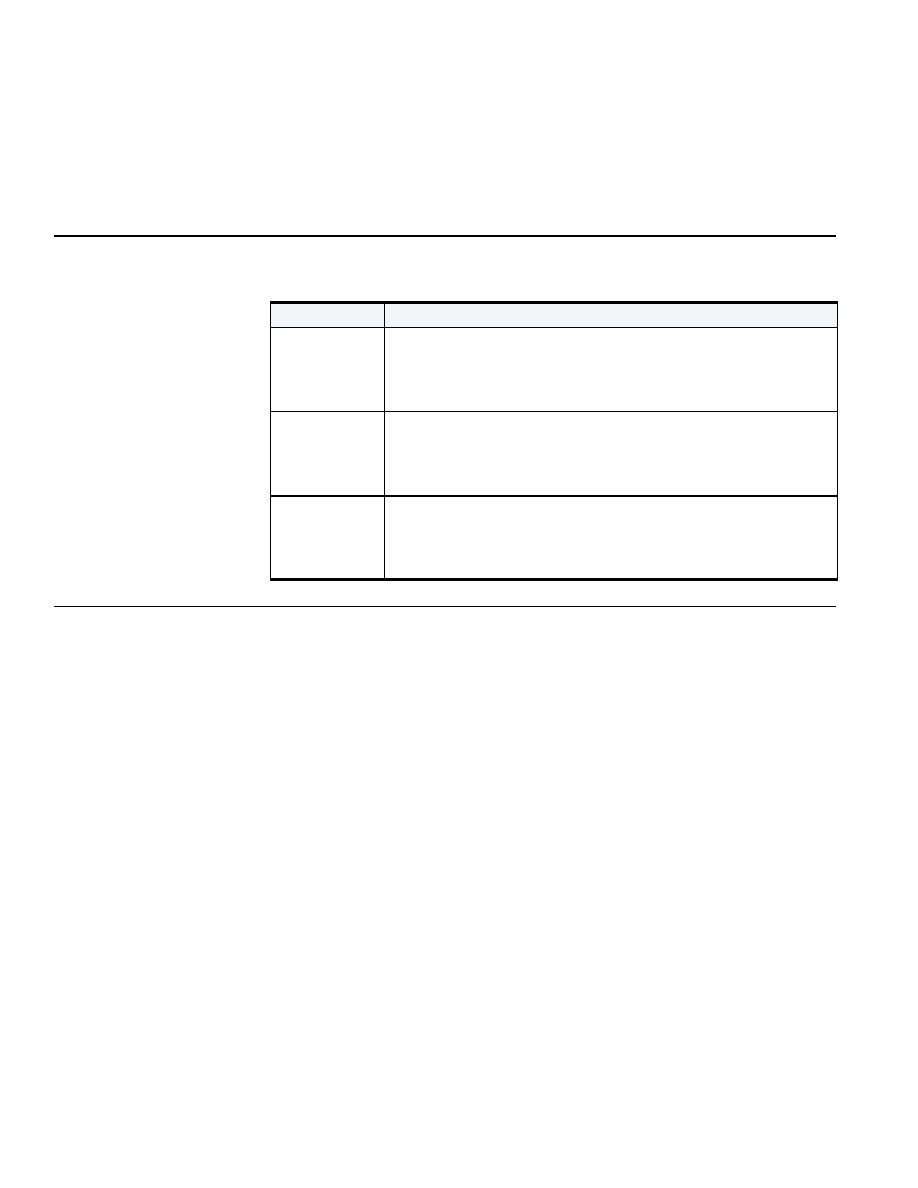

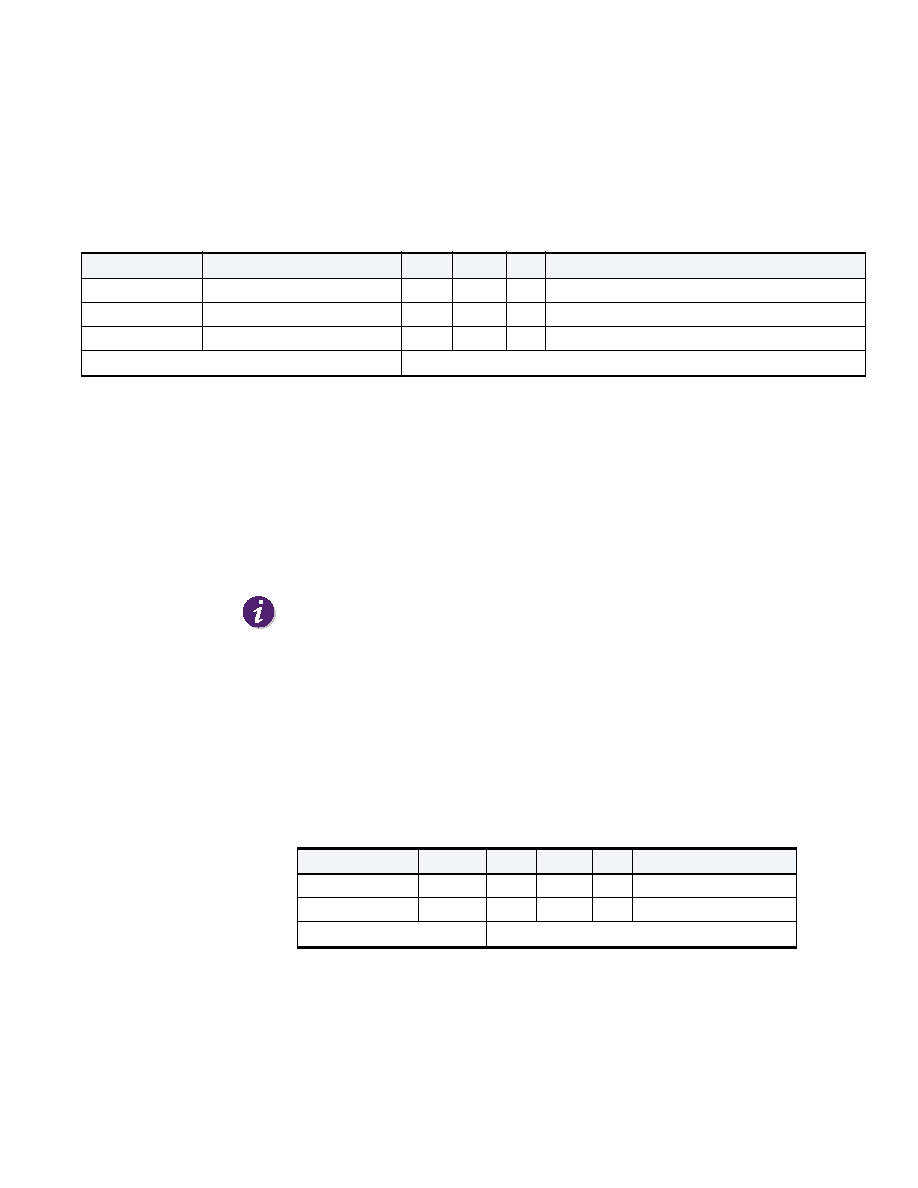

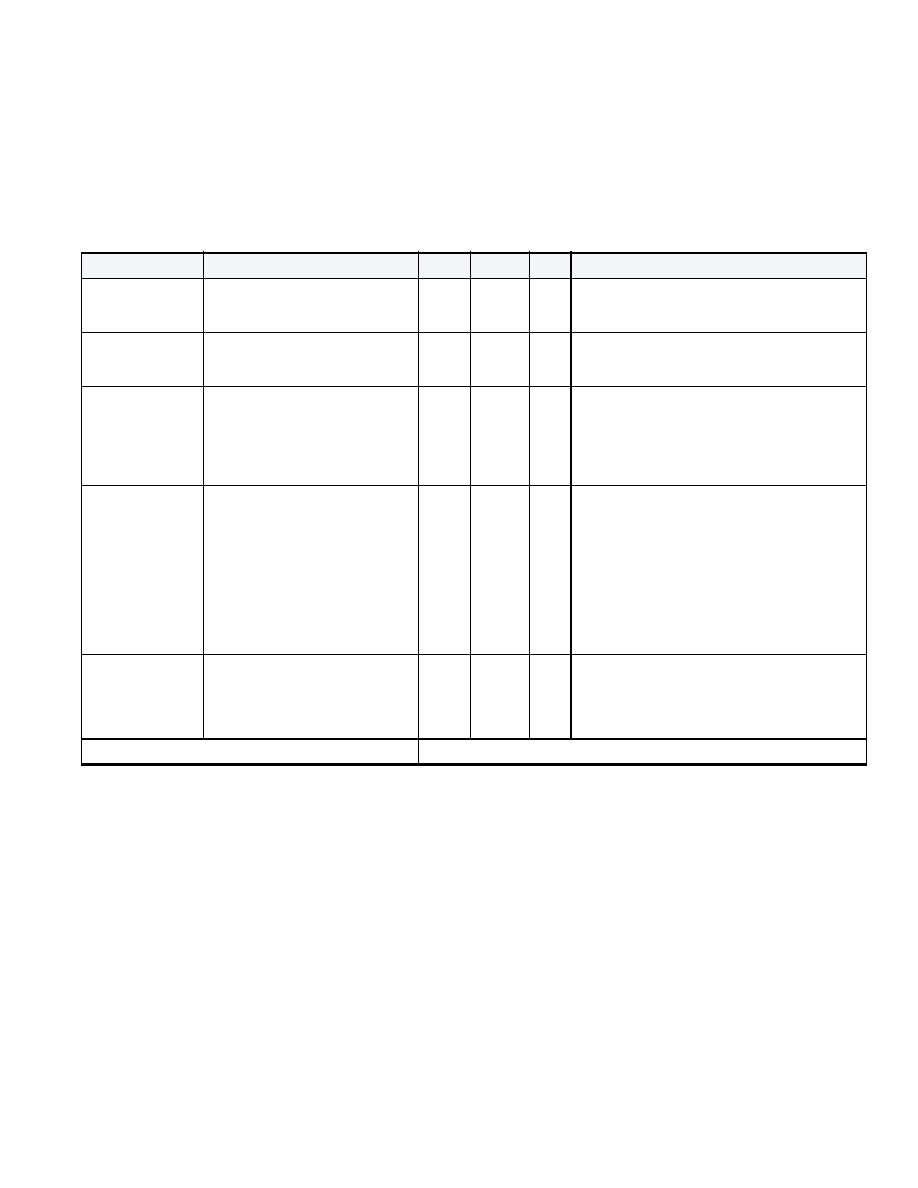

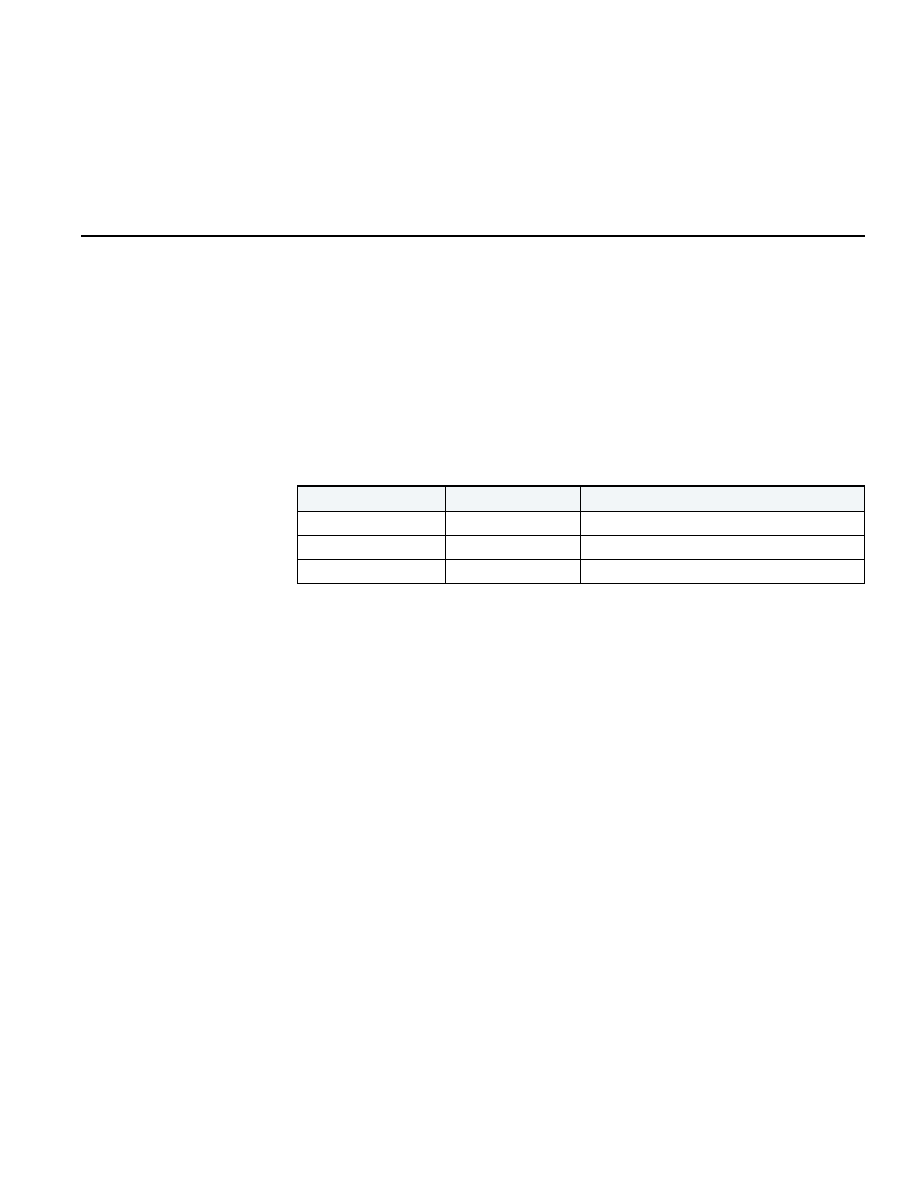

Table 1 Data Sheet Classifications

CLASSIFICATION

DESCRIPTION

Advance

Information

Used to advise customers of the proposed addition to the product line. This

document will typically contain some useful information including

interfacing with the user's system and some specifications. The goal of this

document is to allow customers to begin designs but with expectation of

changes. Specification details may be changed later without notice.

Preliminary

Information

Describes pre-production or first production devices and is usually indicative

of production stage performance. Minor changes should be expected as

characteristic spreads become better controlled. Specification details may be

changed slightly without notice, but the customer can design their product

based on this data sheet.

Production Data

Defines the long-term specified production limits based on fully

characterized data. It includes a disclaimer to allow improvements in

specifications and modifications that do not affect form, fit or function in

original applications; if absolute maximum ratings are changed, they should

improve rather than downgrade.

Using PDF Documents

15

MOTOROLA GENERAL BUSINESS INFORMATION

C5ENPA1-DS/D REV 03

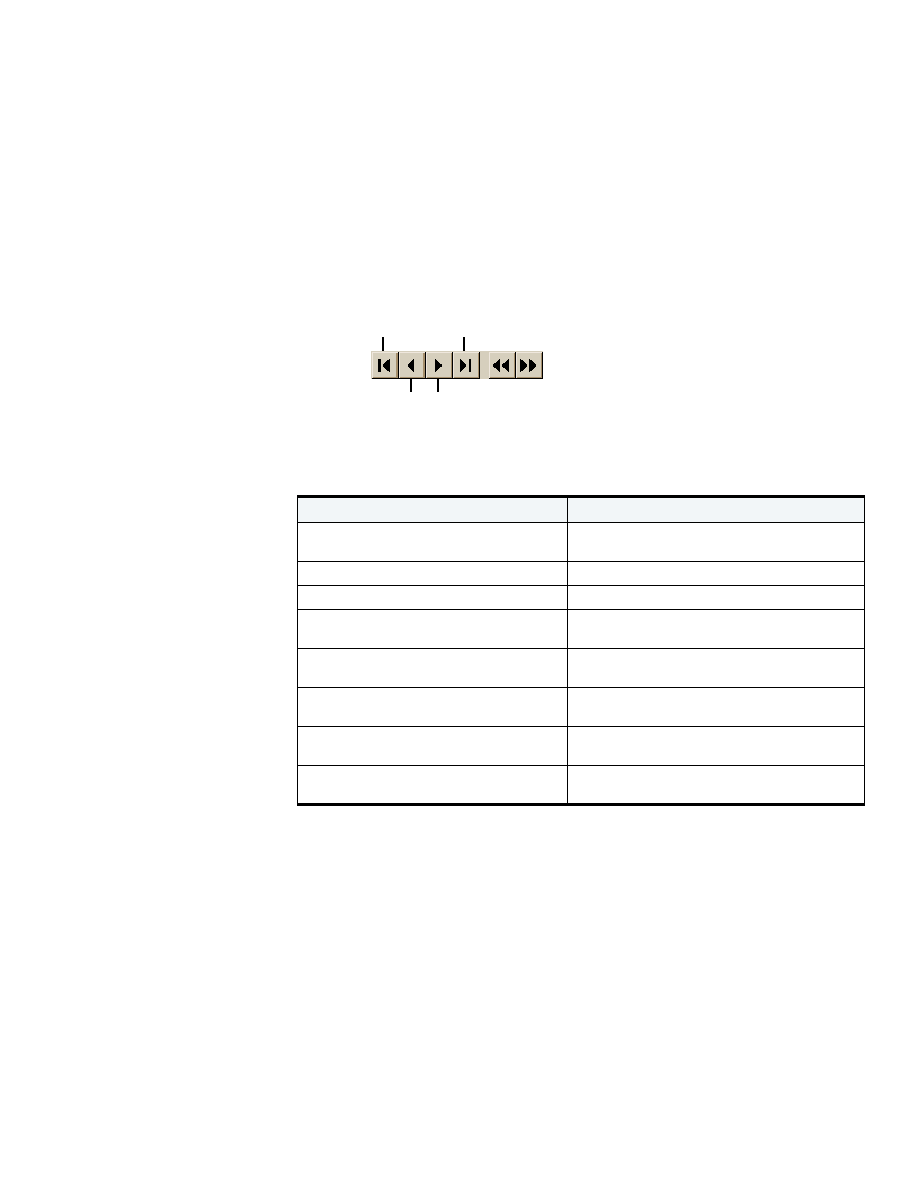

�

To move to the beginning or end of the document, to move page by page within the

document, or to navigate among the pages you displayed by clicking on hyperlinks,

use the Acrobat Reader navigation buttons shown in this figure:

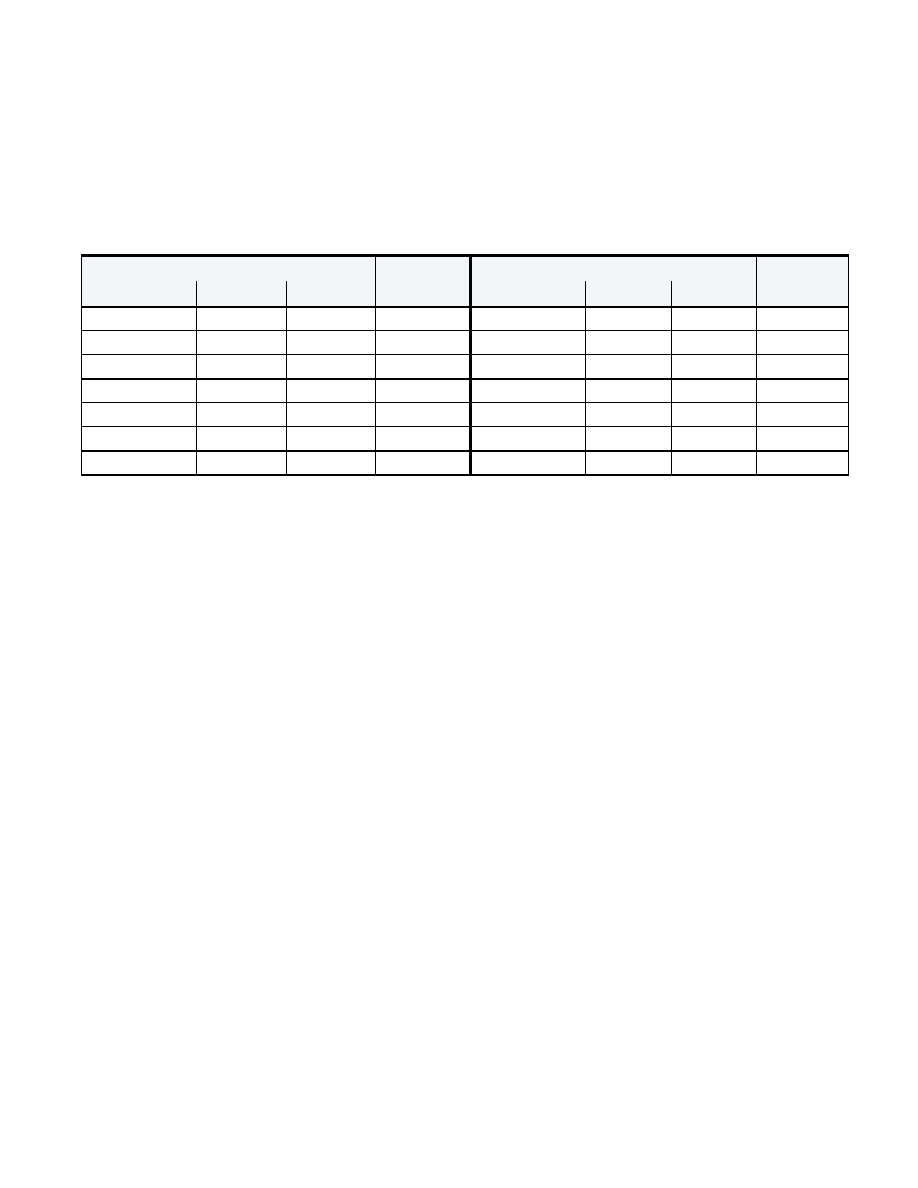

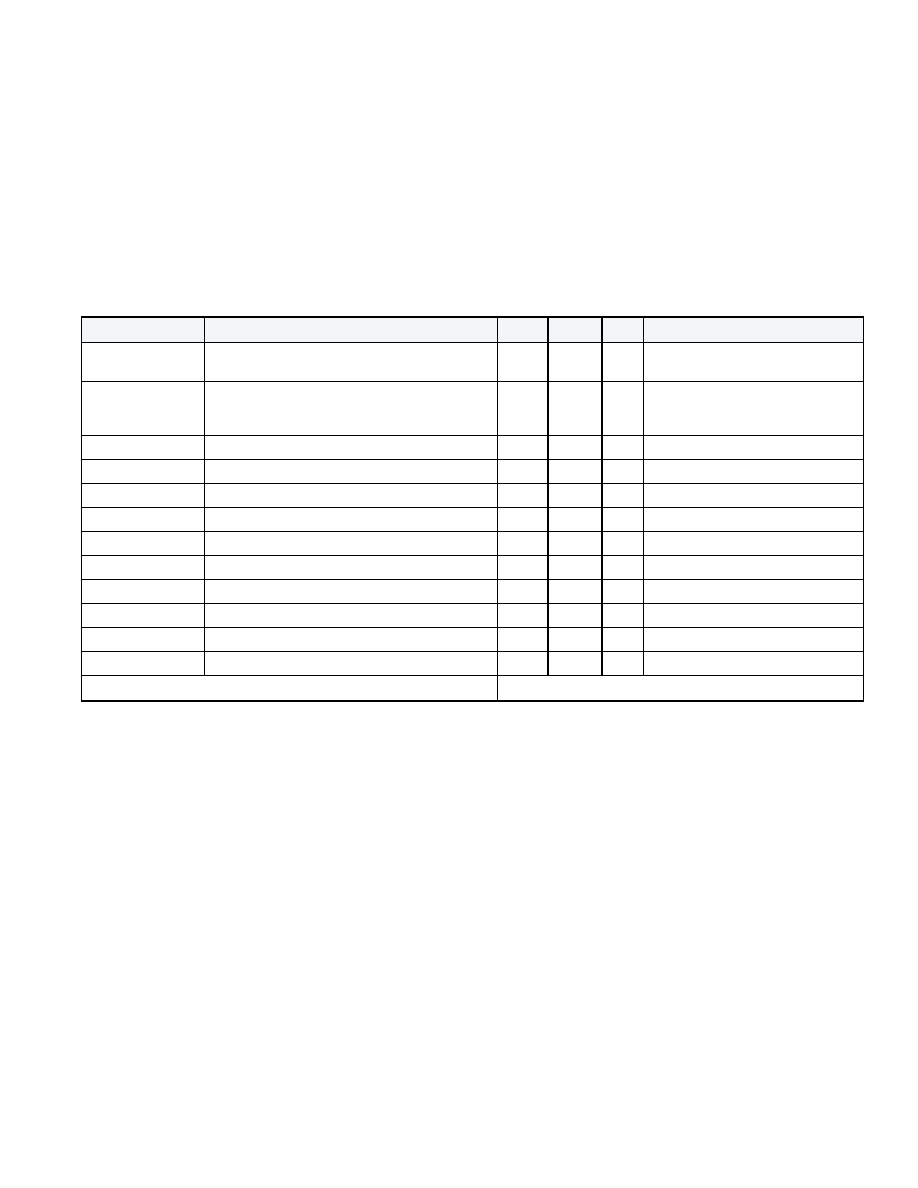

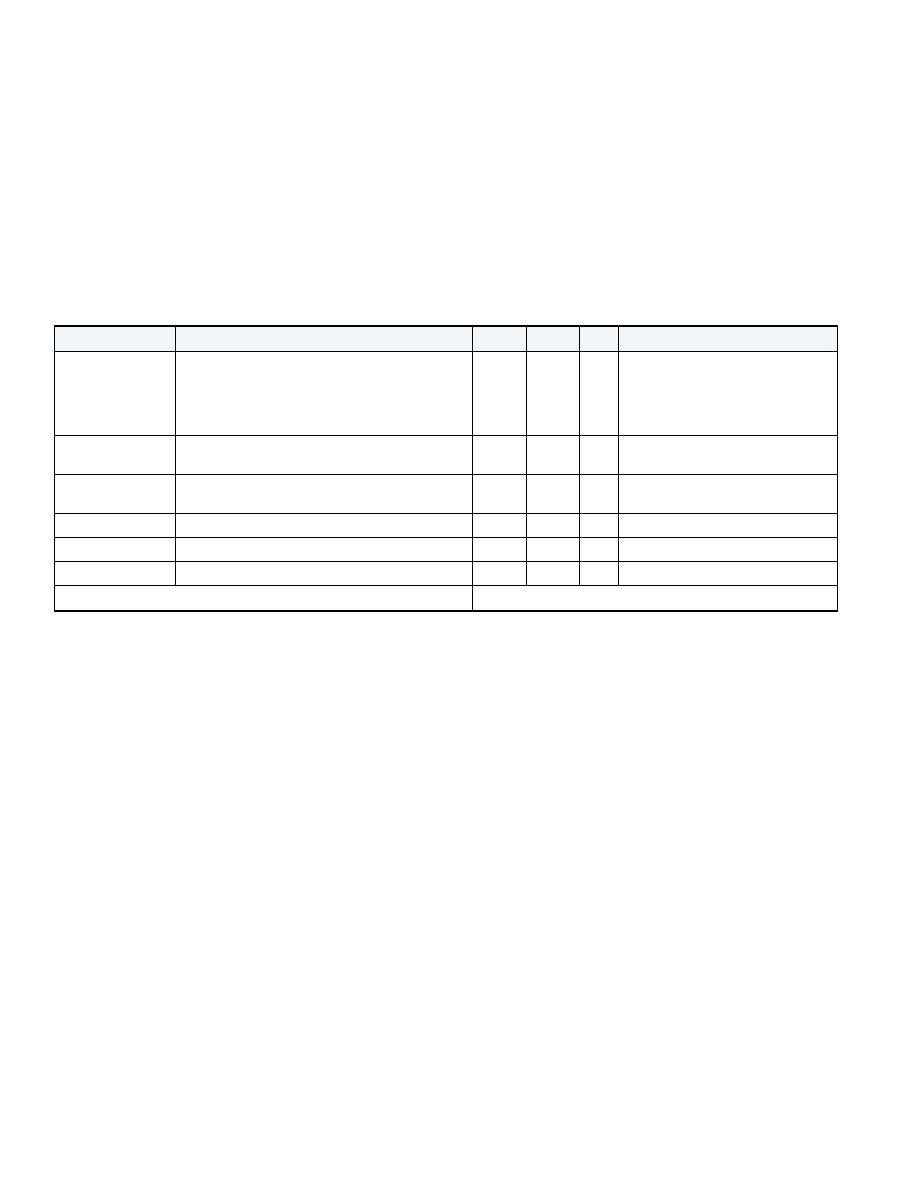

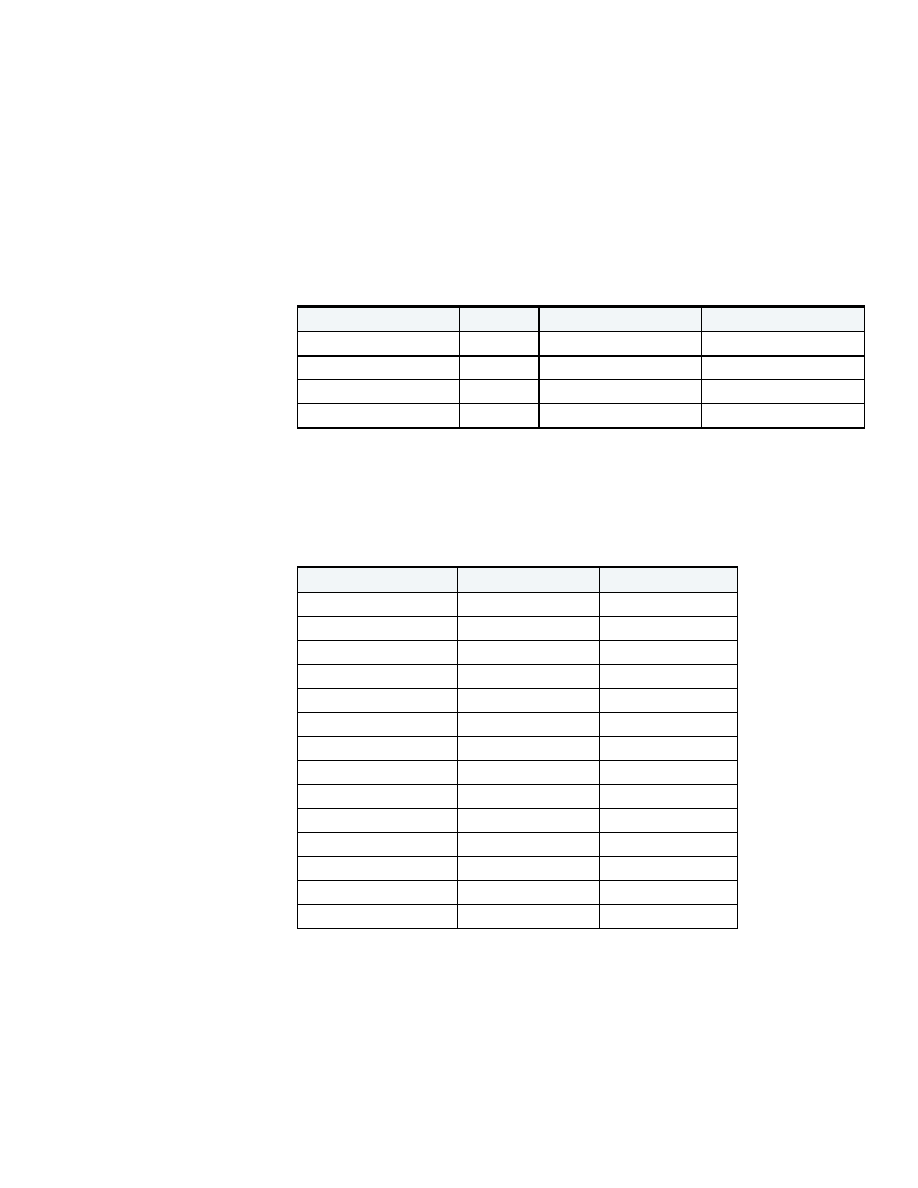

Table 2

summarizes how to navigate within an electronic document.

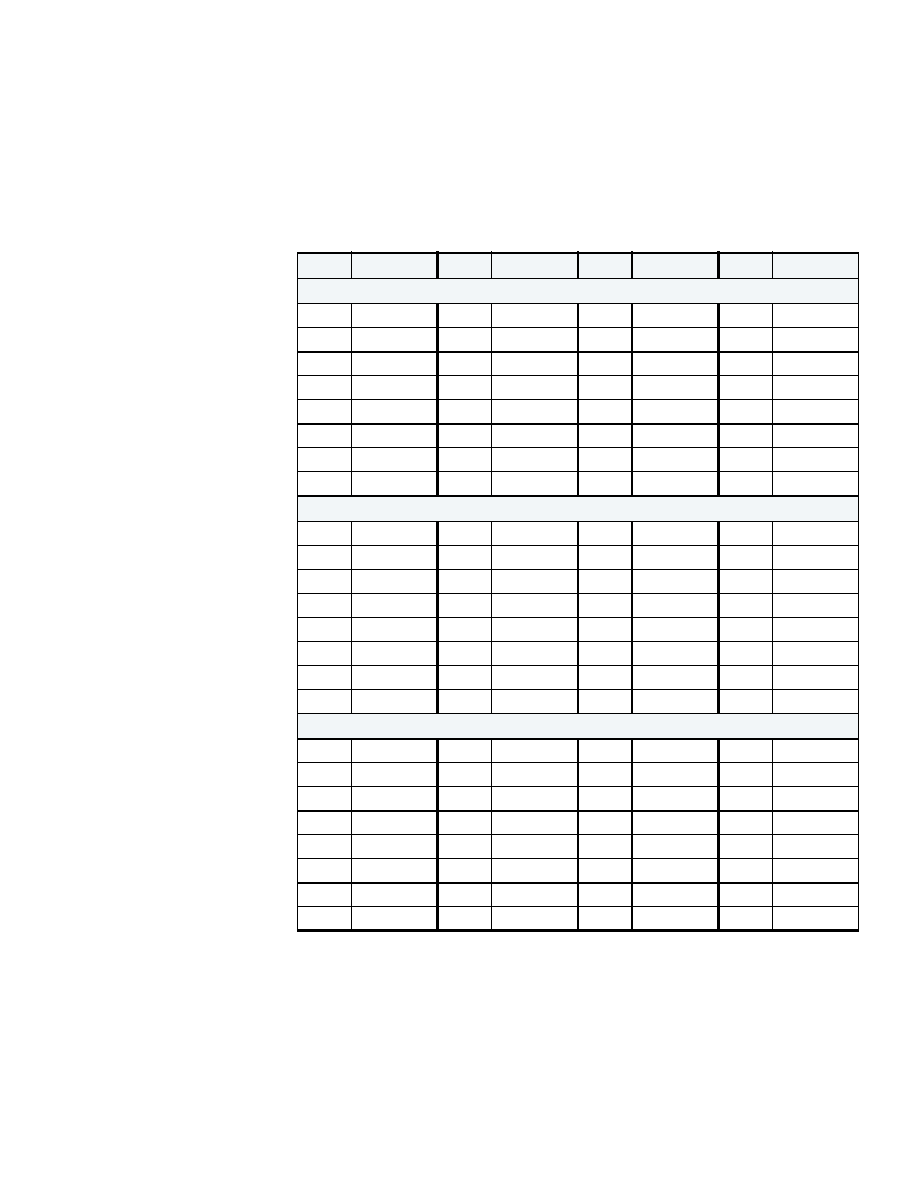

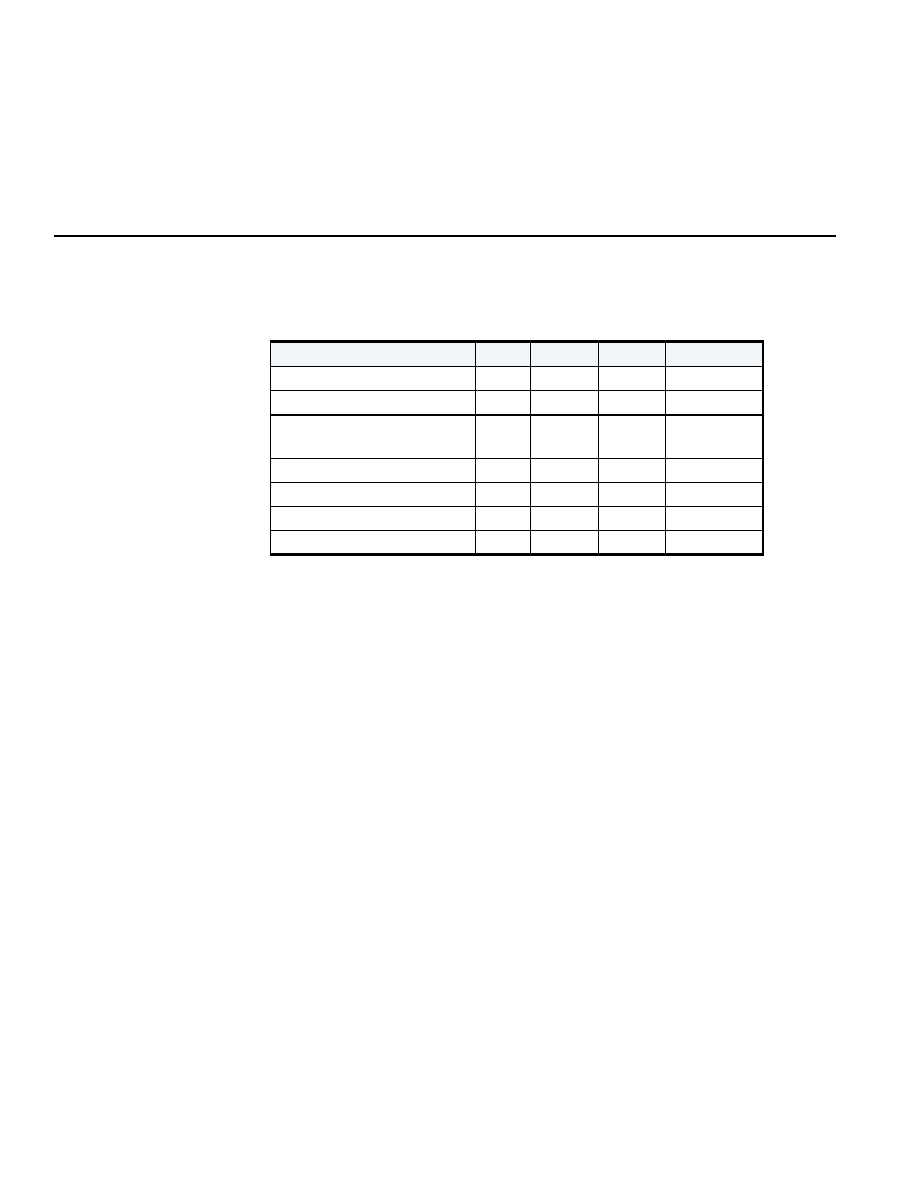

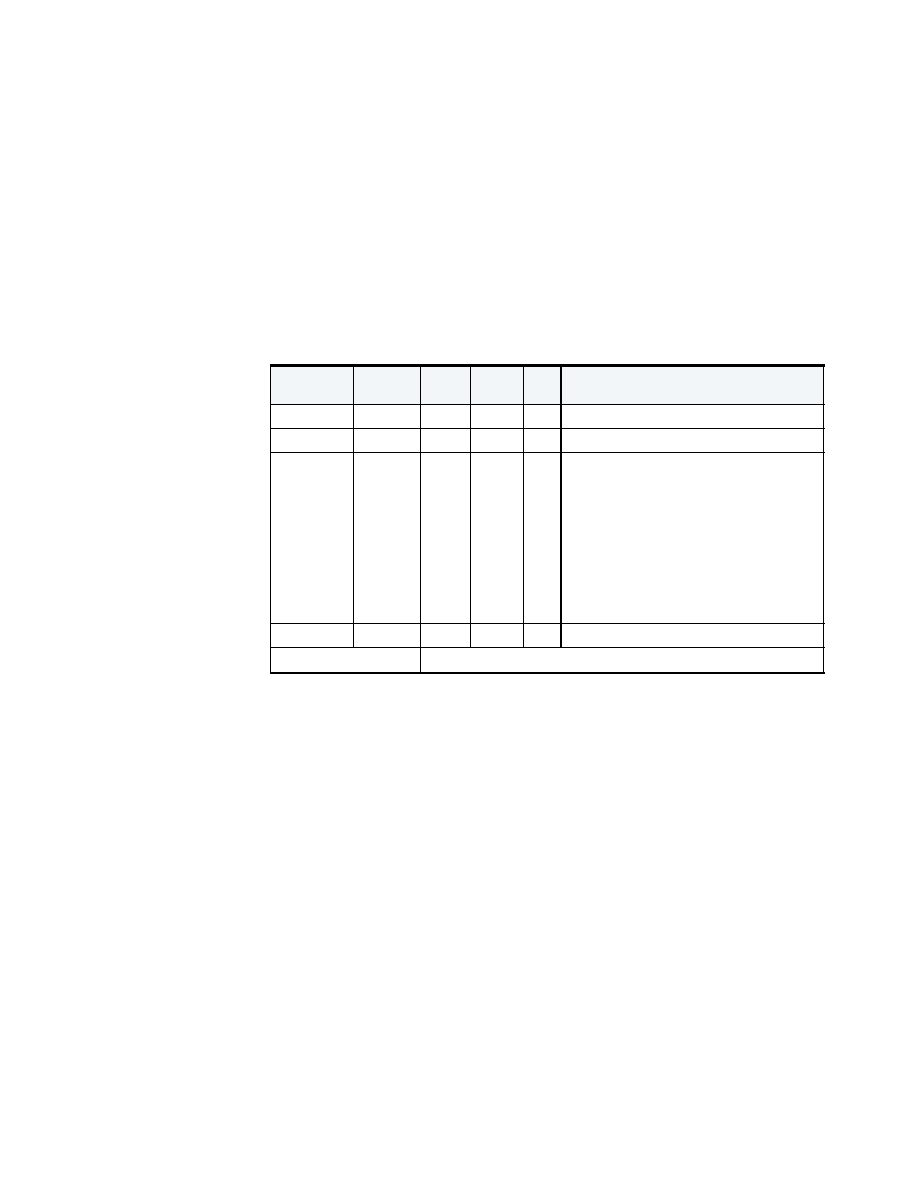

Table 2 Navigating Within a PDF Document

TO NAVIGATE THIS WAY

CLICK THIS

Move from section to section within the

document.

A bookmark on the left side of the Acrobat Reader

window

Move to an entry in the Table of Contents.

The entry itself

Move to an entry in the Index.

The page number

Move to an entry in the List of Figures or List

of Tables.

The Figure or Table number

Follow a

cross-reference

(highlighted in blue

text).

The cross-reference text

Move page by page.

The appropriate Acrobat Reader navigation

buttons

Move to the beginning or end of the

document.

The appropriate Acrobat Reader navigation

buttons

Move backward or forward among a series of

hyperlinks you have selected.

The appropriate Acrobat Reader navigation

buttons

Beginning

of document

End of

Next page

Previous

Previous or next hyperlink

16

ABOUT THIS GUIDE

C5ENPA1-DS/D REV 03

MOTOROLA GENERAL BUSINESS INFORMATION

Guide Conventions

The following visual elements are used throughout this guide, where applicable:

This icon and text designates information of special note.

Warning:

This icon and text indicate a potentially dangerous procedure. Instructions

contained in the warnings must be followed.

Warning:

This icon and text indicate a procedure where the reader must take

precautions regarding laser light.

This icon and text indicate the possibility of electrostatic discharge (ESD) in a procedure

that requires the reader to take the proper ESD precautions.

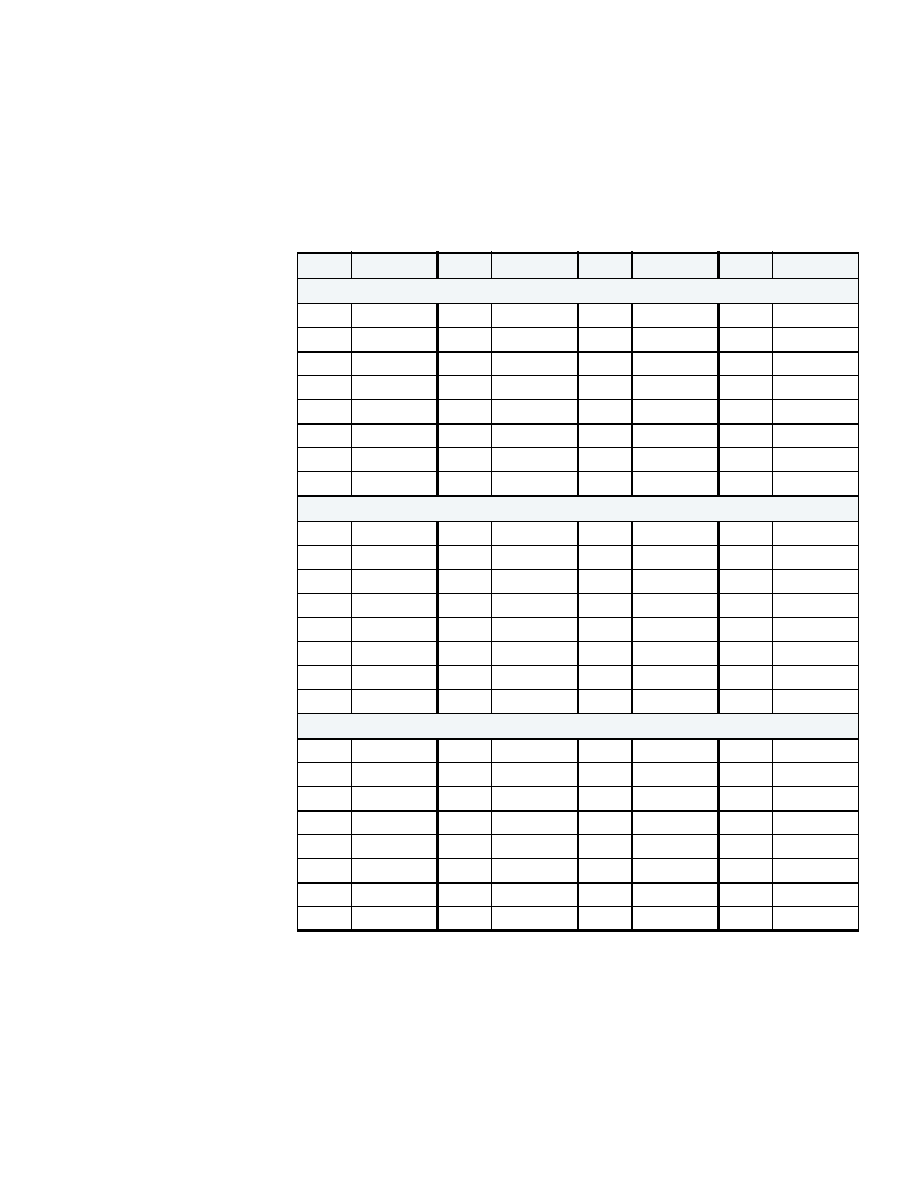

Revision History

Table 3

provides details about changes made for each revision of this guide.

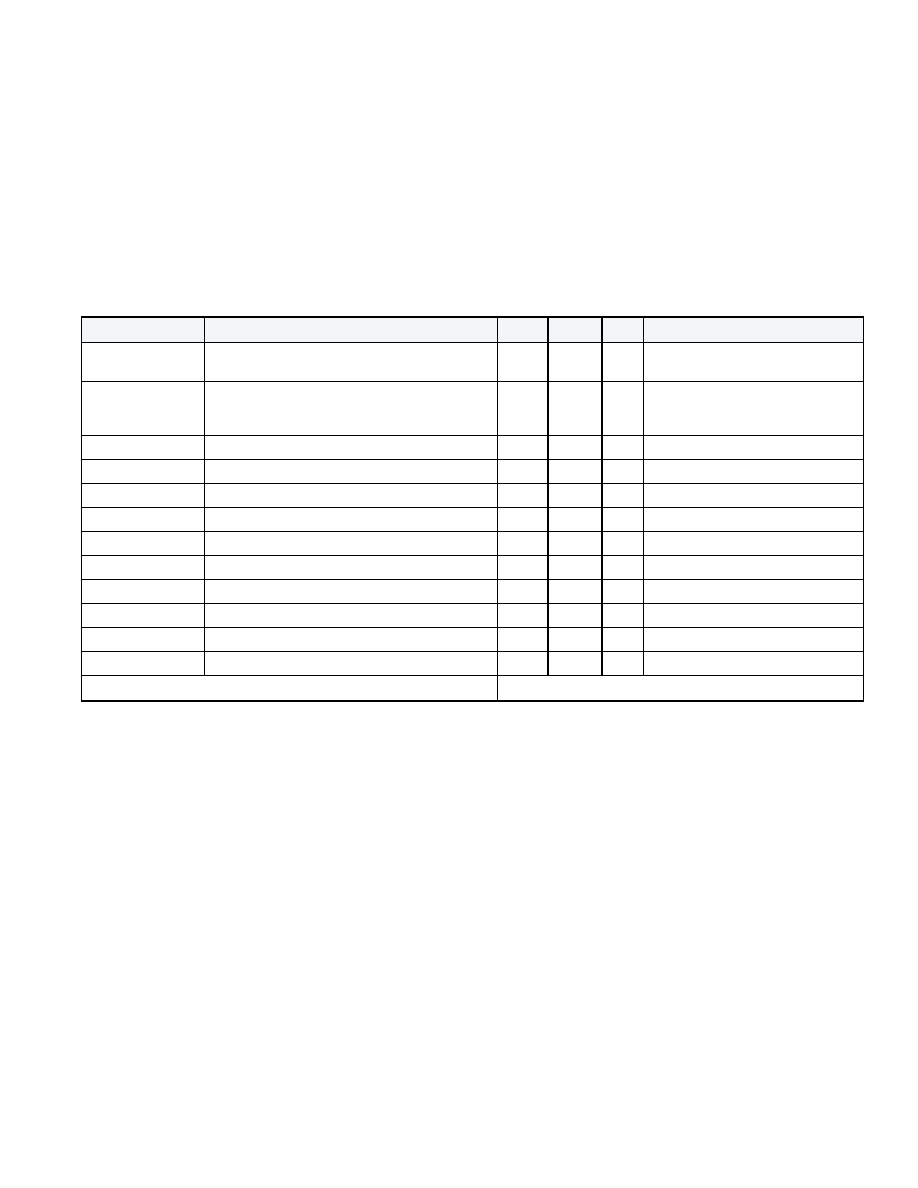

Table 3 C-5e Network Processor Data Sheet Revision History

REVISION DATE

CST REVISION

CDS REVISION

CHANGES

November 8, 2002

2.2

2.0

Added information about optional

capacitors, nominal values for

recommended operating conditions,

and updated package measurement

values.

Related Product Documentation

17

MOTOROLA GENERAL BUSINESS INFORMATION

C5ENPA1-DS/D REV 03

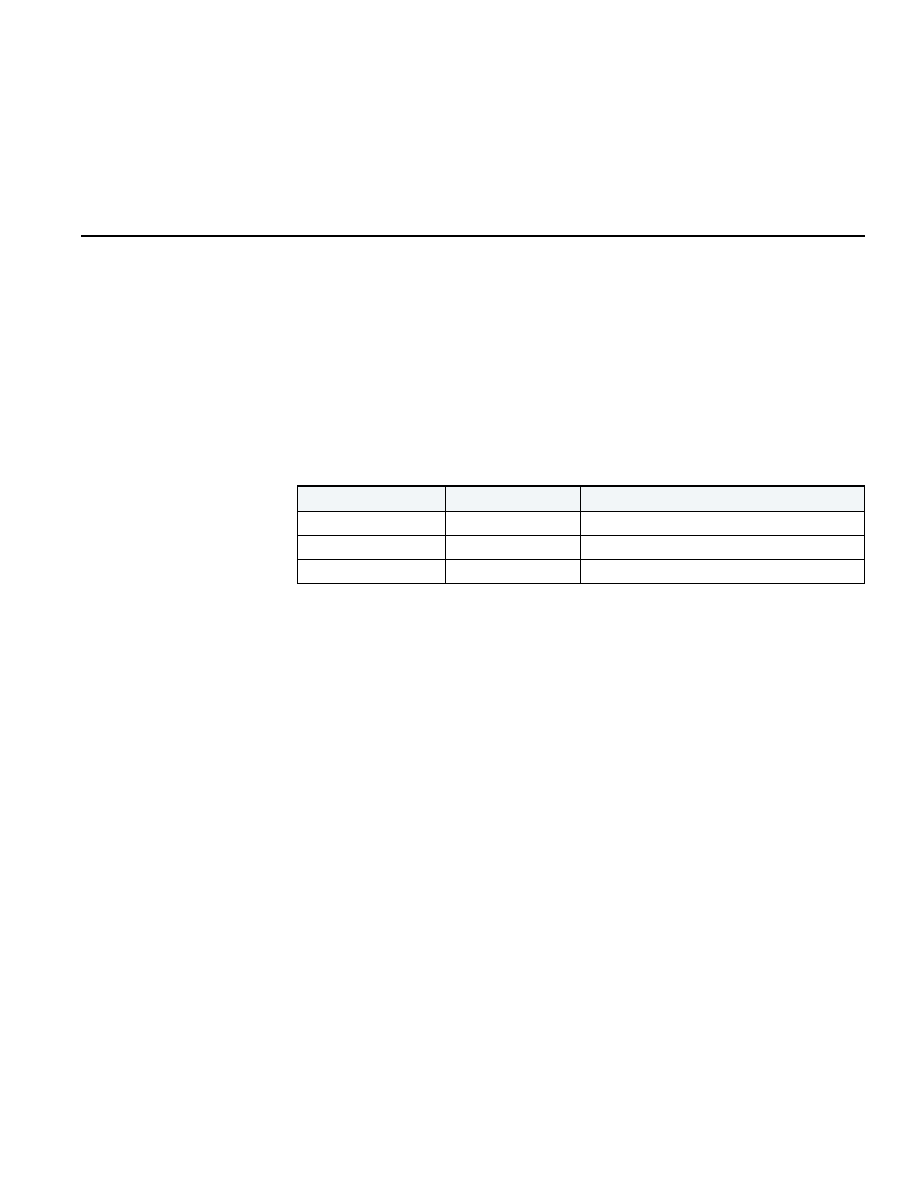

Related Product

Documentation

Table 4

lists the user and reference documentation for Motorola `s C-Port silicon

documentation set.

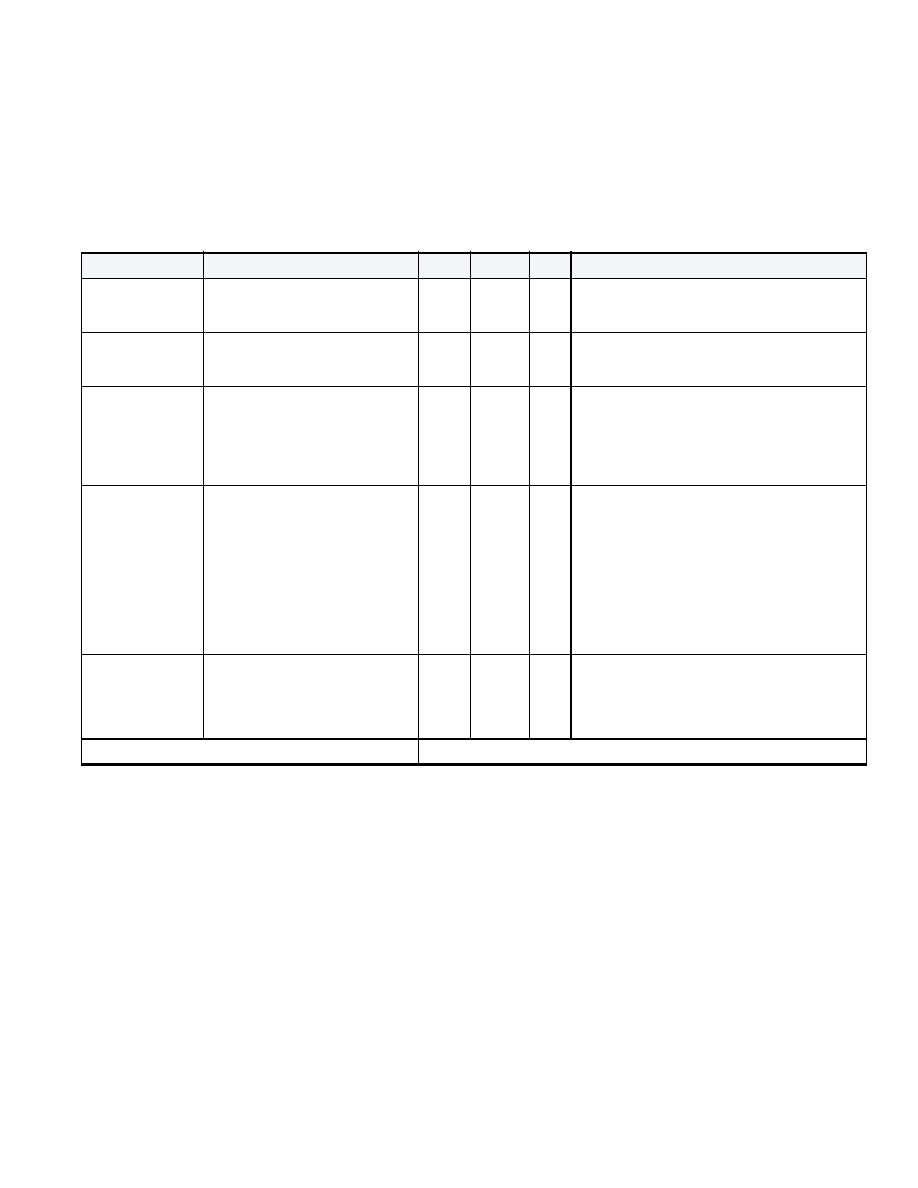

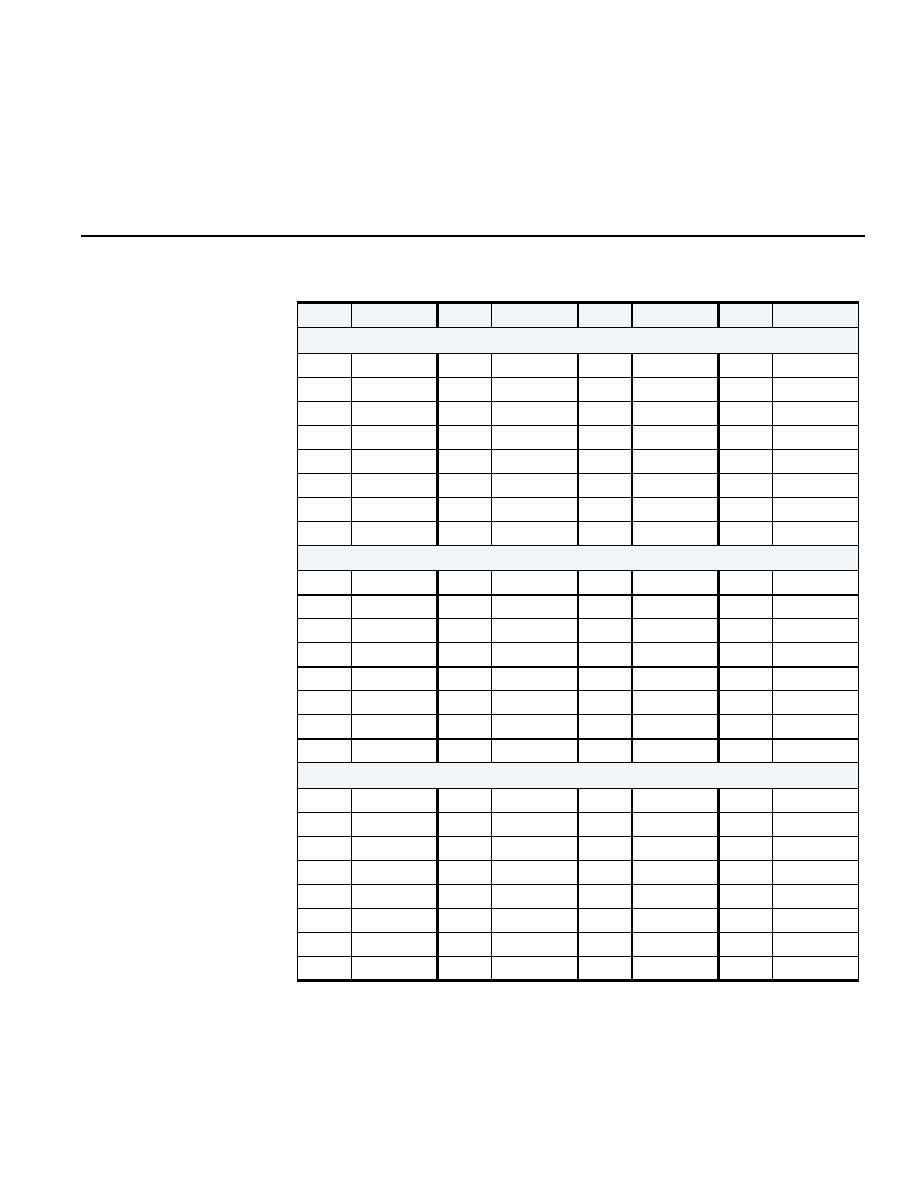

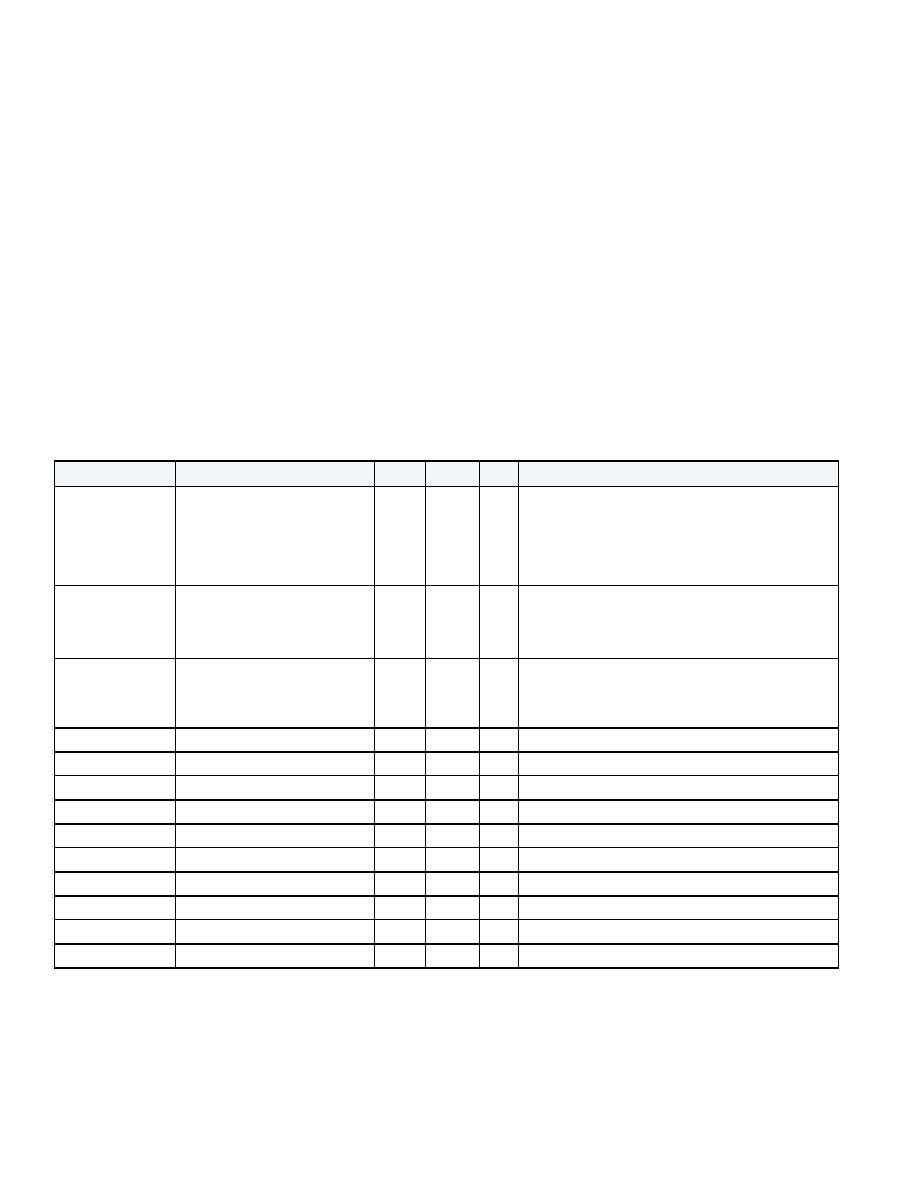

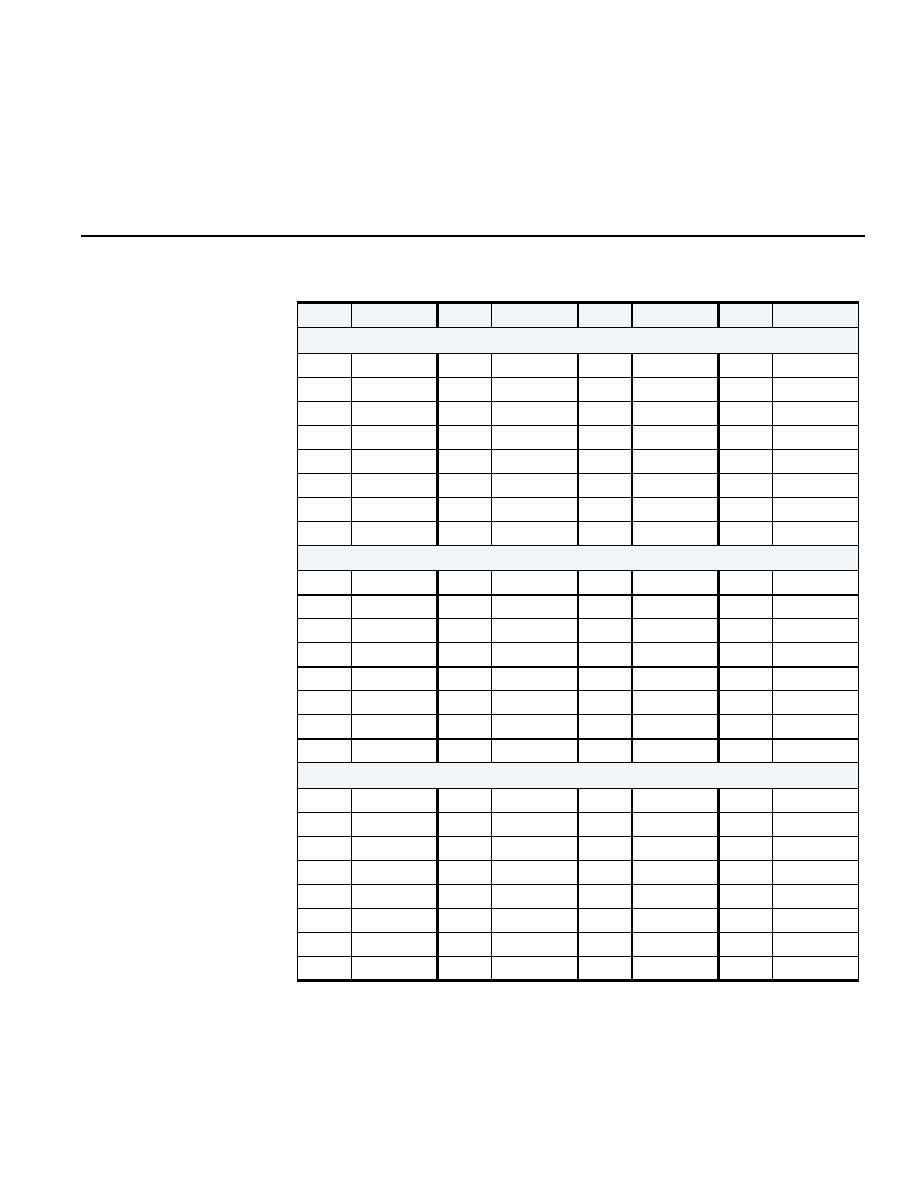

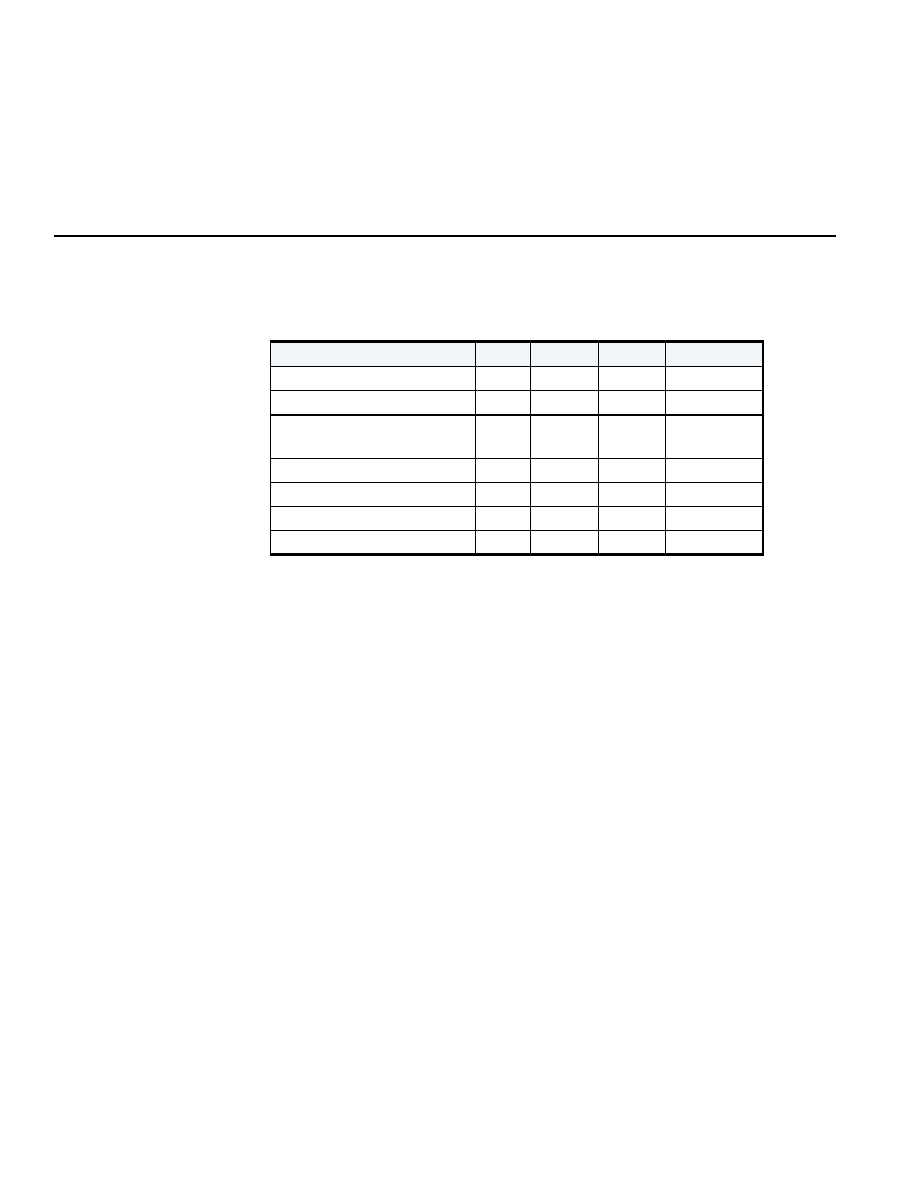

Table 4 C-Port Silicon Documentation Set

DOCUMENT

SUBJECT

DOCUMENT NAME

PURPOSE

DOCUMENT ID

Processor

Information

C-5 Network Processor Architecture Guide

Describes the full architecture of the C-5 network

processor.

C5NPARCH-RM/D

C-5 Network Processor Data Sheet

Describes hardware design specifications for the

C-5 network processor.

C5NPDATA-DS/D

C-5e/C-3e Network Processor Architecture

Guide

Describes the full architecture of the C-5e and C-3e

network processors.

C5EC3EARCH-RM/D

C-5e Network Processor Data Sheet

Describes hardware design specifications for the

C-5e network processor.

C5ENPA1-DS/D

C-3e Network Processor Data Sheet

Describes hardware design specifications for the

C-3e network processor.

C3ENPA1-DS/D

C-5 Network Processor to C-5e Network

Processor Comparison Delta Document

Describes key architectural features of the C-5e,

and highlights main differences between C-5 and

C-5e.

C5C5EDELTA-RM/D

M-5 Channel Adapter Architecture Guide

Describes the full architecture of the M-5 channel

adapter.

M5CAARCH-RM/D

M-5 Channel Adapter Data Sheet

Describes hardware design specifications for the

M-5 channel adapter.

M5CA0-DS/D

Q-5/Q-3 Traffic Management Coprocessor

Architecture Guide

Describes the full architecture of the Q-5 and Q-3

traffic management coprocessor.

Q5Q3ARCH-RM/D

Q-5 Traffic Management Coprocessor Data

Sheet

Describes hardware design specifications for the

Q-5 traffic management coprocessor.

Q5TMCA0-DS/D

18

ABOUT THIS GUIDE

C5ENPA1-DS/D REV 03

MOTOROLA GENERAL BUSINESS INFORMATION

MOTOROLA GENERAL BUSINESS INFORMATION

C5ENPA1-DS/D REV 03

C5ENPA1-DS/D

Rev 03

Chapter 1

FUNCTIONAL DESCRIPTION

Features

Key features of the C-5e

TM

Network Processor (NP) are its massive processing capabilities

and its high level of functional integration on one chip.

Massive Processing

Power

�

Operating frequencies: up to 266MHz

�

5Gbps of bandwidth (for non-blocking throughput)

�

More than 4,500MIPS of computing power (for adding services throughout the

protocol stack)

�

Up to 15 million packets per second transmitted at wire speed

�

17 programmable RISC Cores (for cell/packet forwarding)

�

32 programmable Serial Data Processors (for processing bit streams)

�

Up to 133 million table lookups per second

�

Three internal buses for 68Gbs of aggregate bandwidth

High Functional

Integration

�

840 pin Ball Grid Array (BGA) package

�

16 Channel Processors including:

� Embedded OC-3c , OC-12 , OC-12c SONET framers

� Programmable MAC interface

� RISC Cores

� Programmable pin PHY interfaces

�

Embedded coprocessors for table lookup (classification), buffer management (payload

control), and queue management (CoS/QoS implementation)

�

Dedicated Fabric Processor and port

20

CHAPTER 1: FUNCTIONAL DESCRIPTION

C5ENPA1-DS/D REV 03

MOTOROLA GENERAL BUSINESS INFORMATION

�

Embedded RISC Executive Processor

�

Integrated 32bit 33/66MHz PCI bus interface

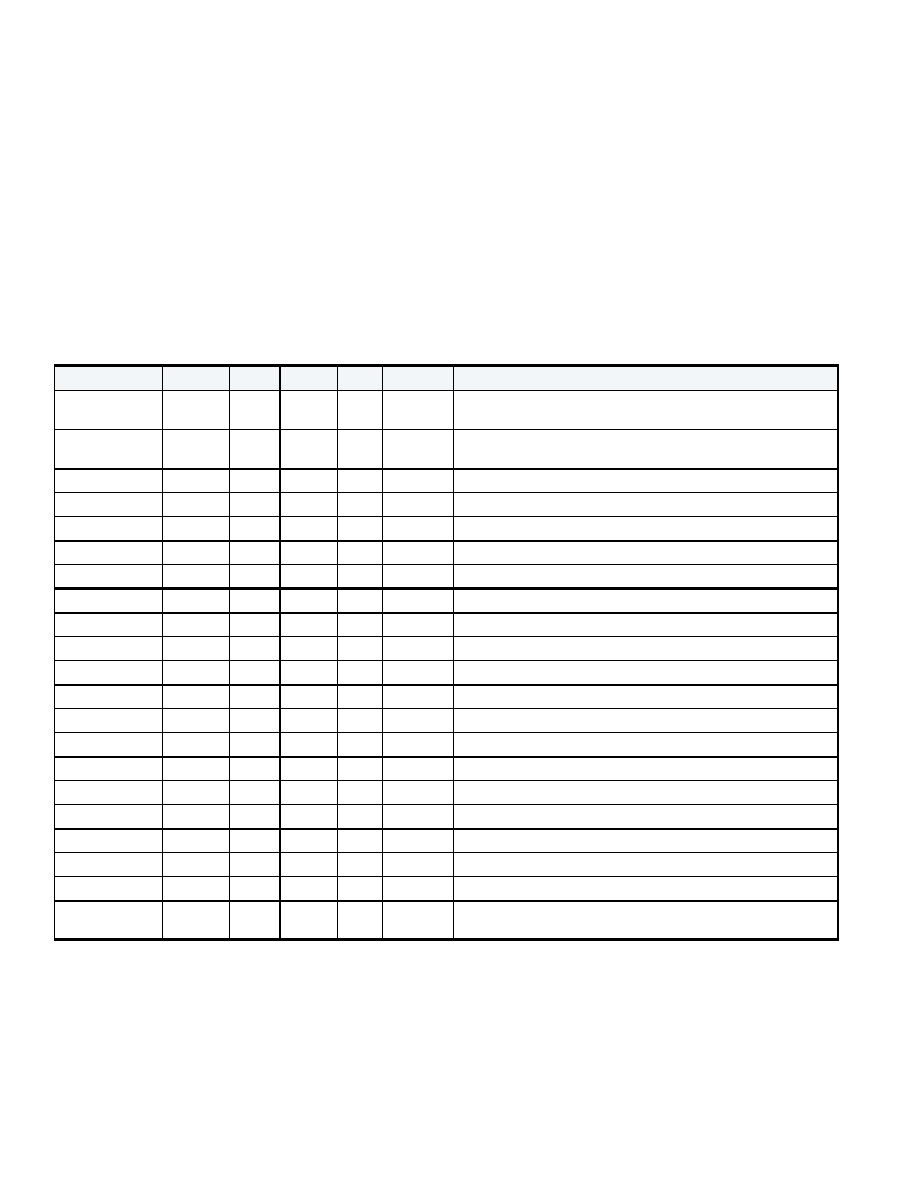

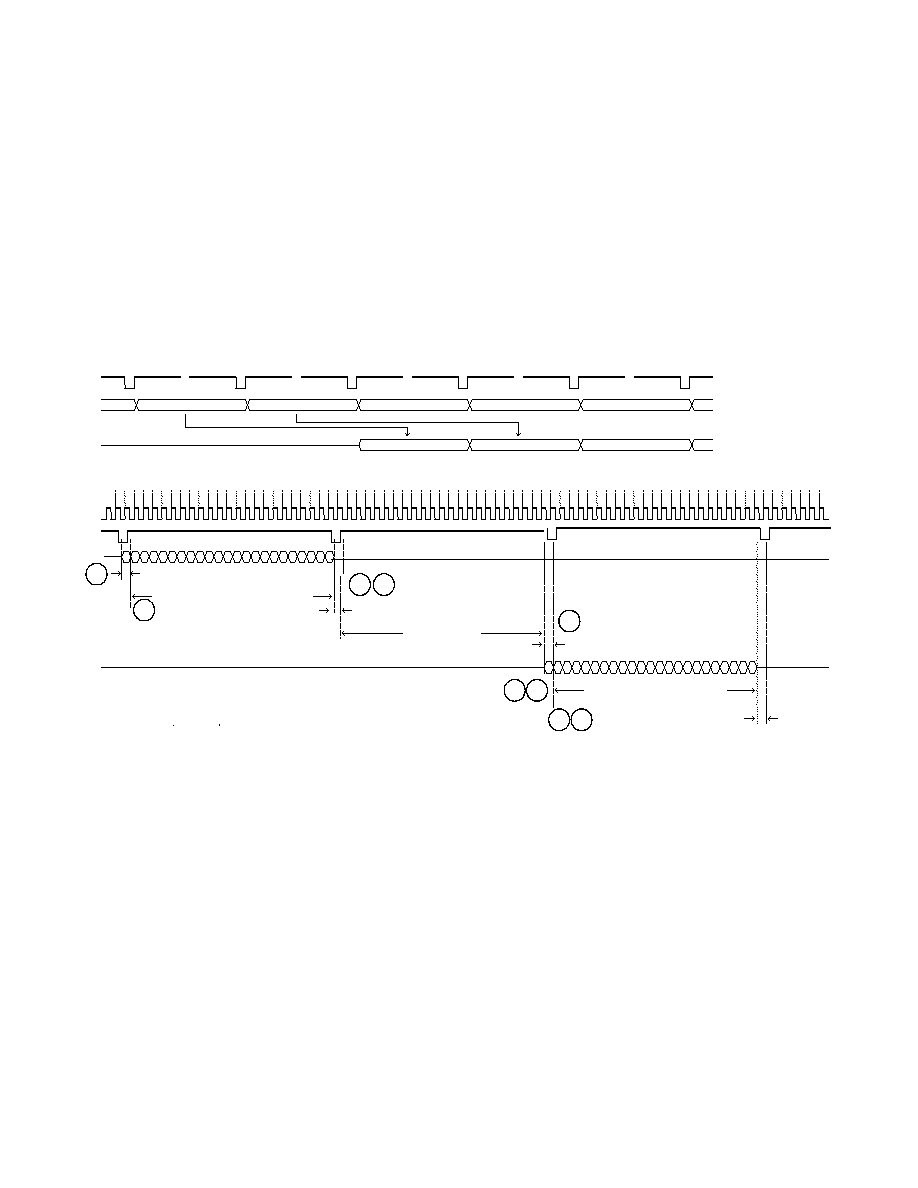

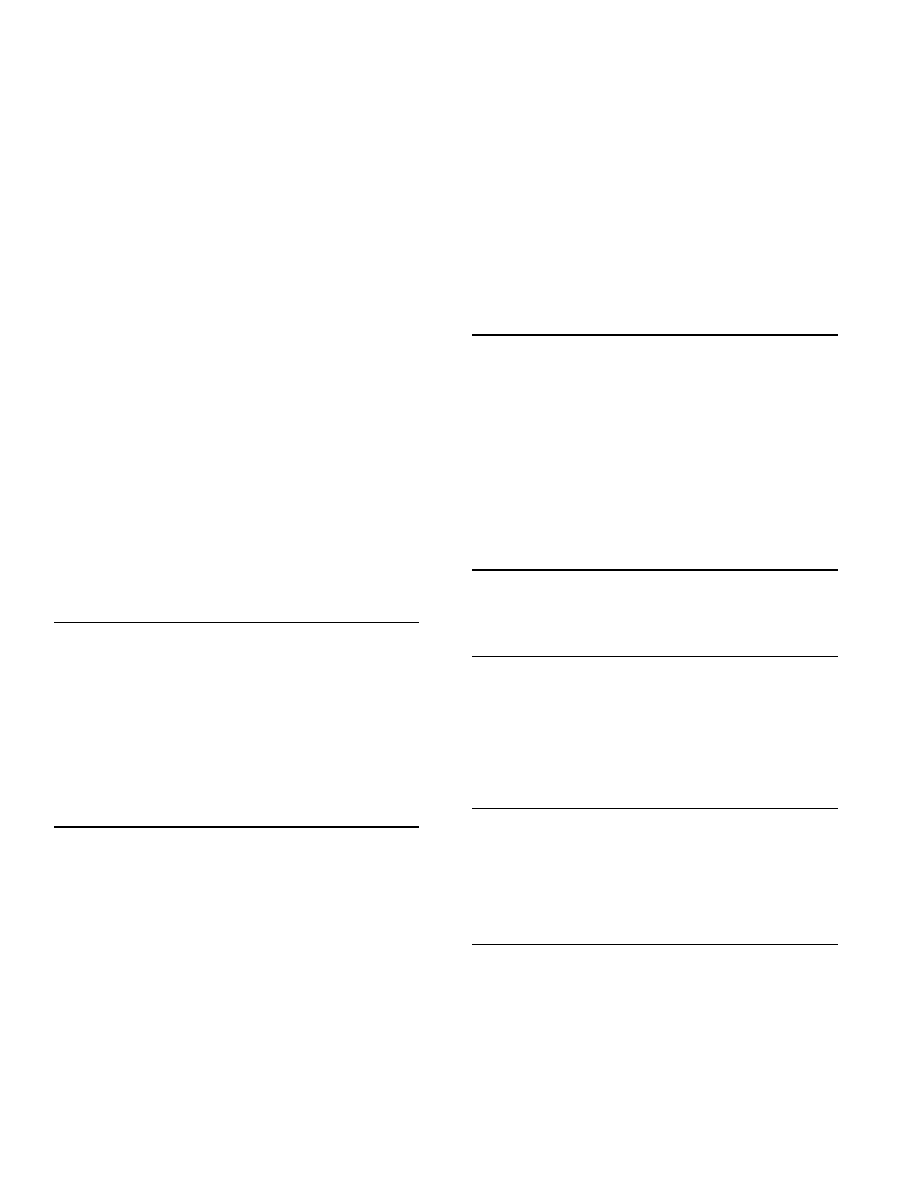

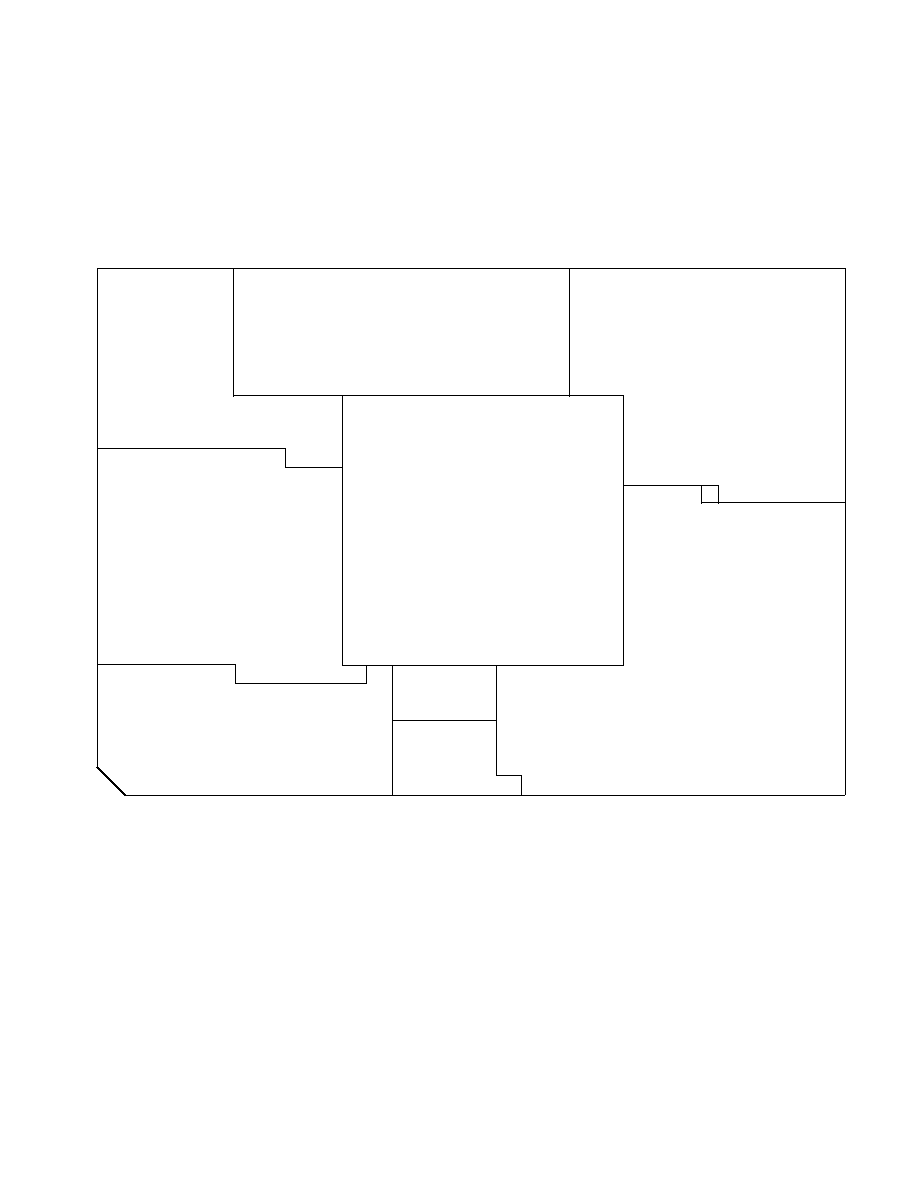

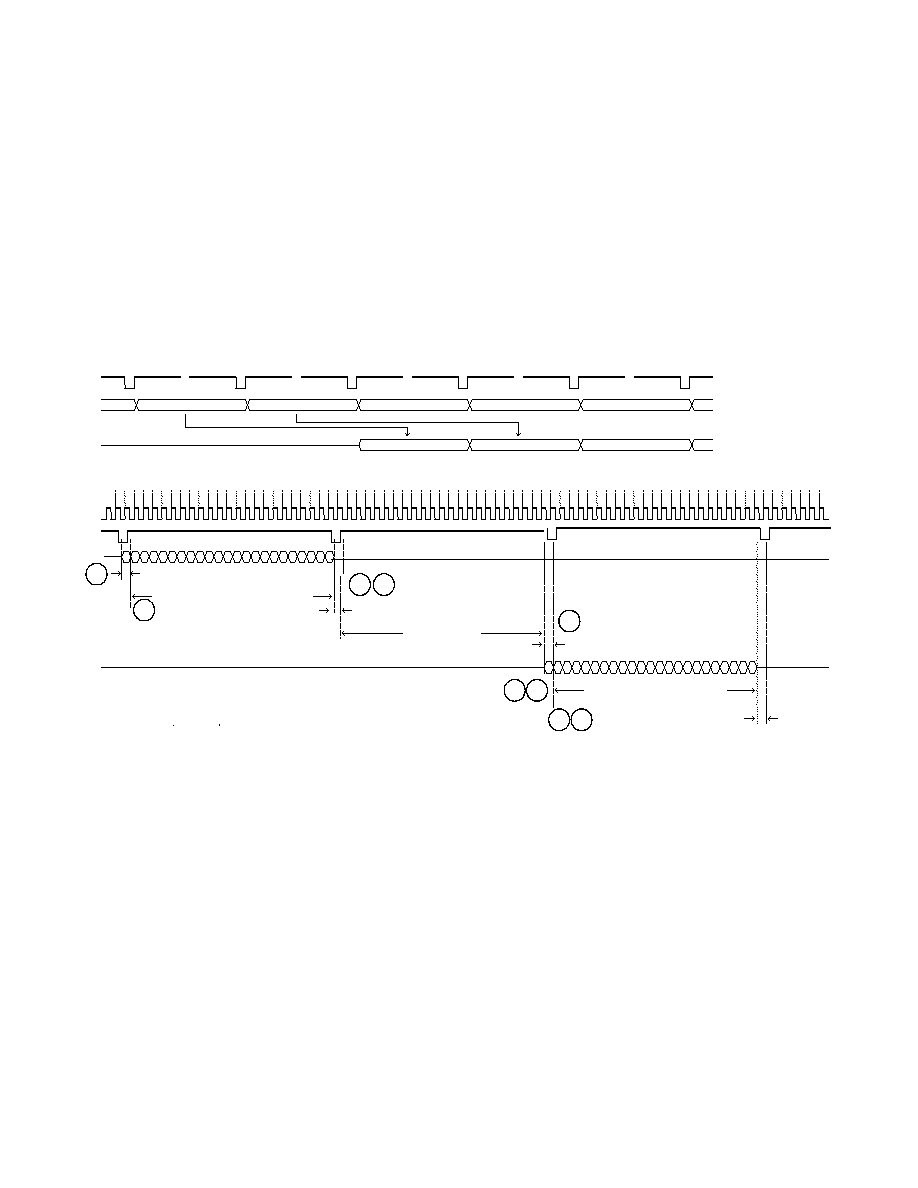

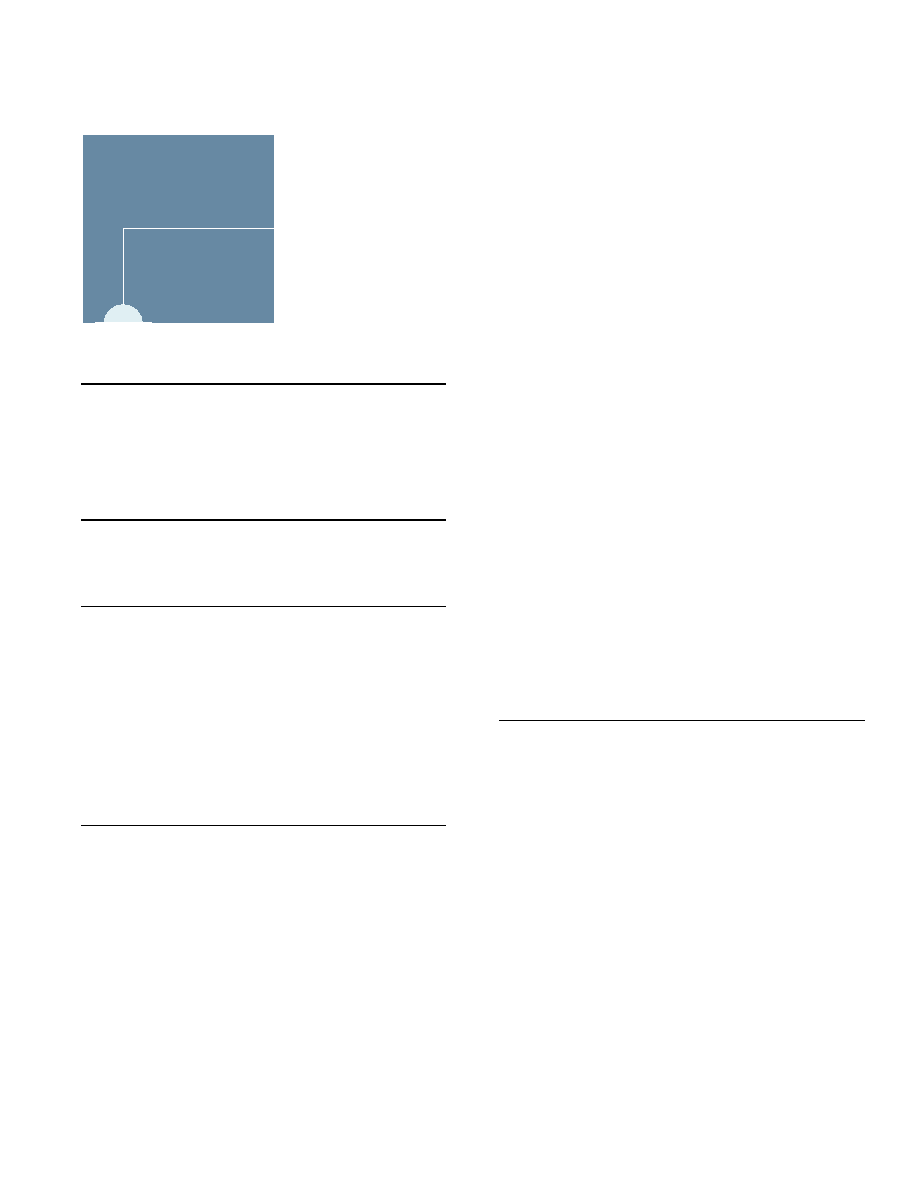

Block Diagram

The C-5e

TM

NP, has an architecture specifically designed for networking applications. The

following sections describe each component of the C-5e NP.

The main components of the C-5e NP are:

�

Channel Processors

�

Executive Processor

�

Fabric Processor

�

Buffer Management Unit

�

Table Lookup Unit

�

Queue Management Unit

The C-5e NP conforms with both SONET and SDH. Therefore, OC-3(STS-3/STM-1), OC-12

(STS-12/STM-4, and OC48 (STS-48/STM-16).

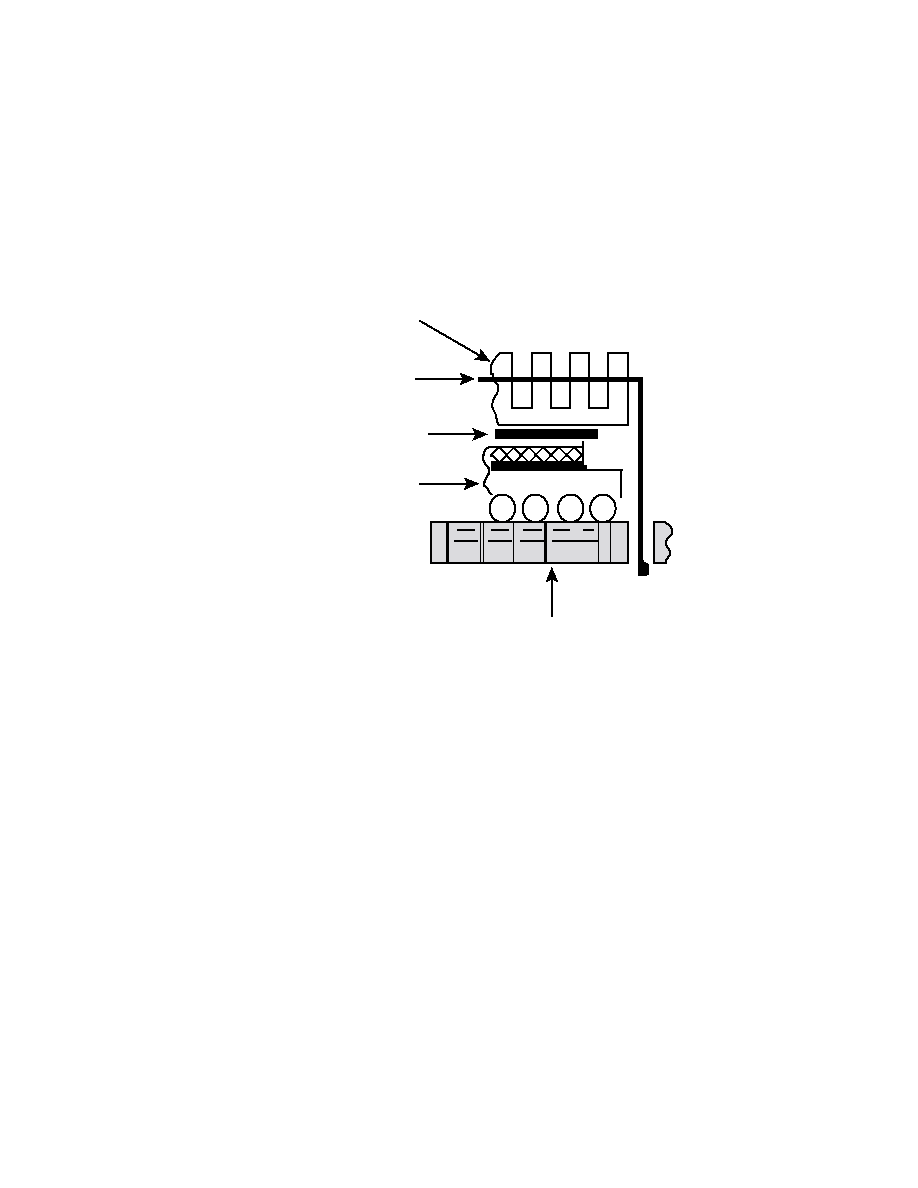

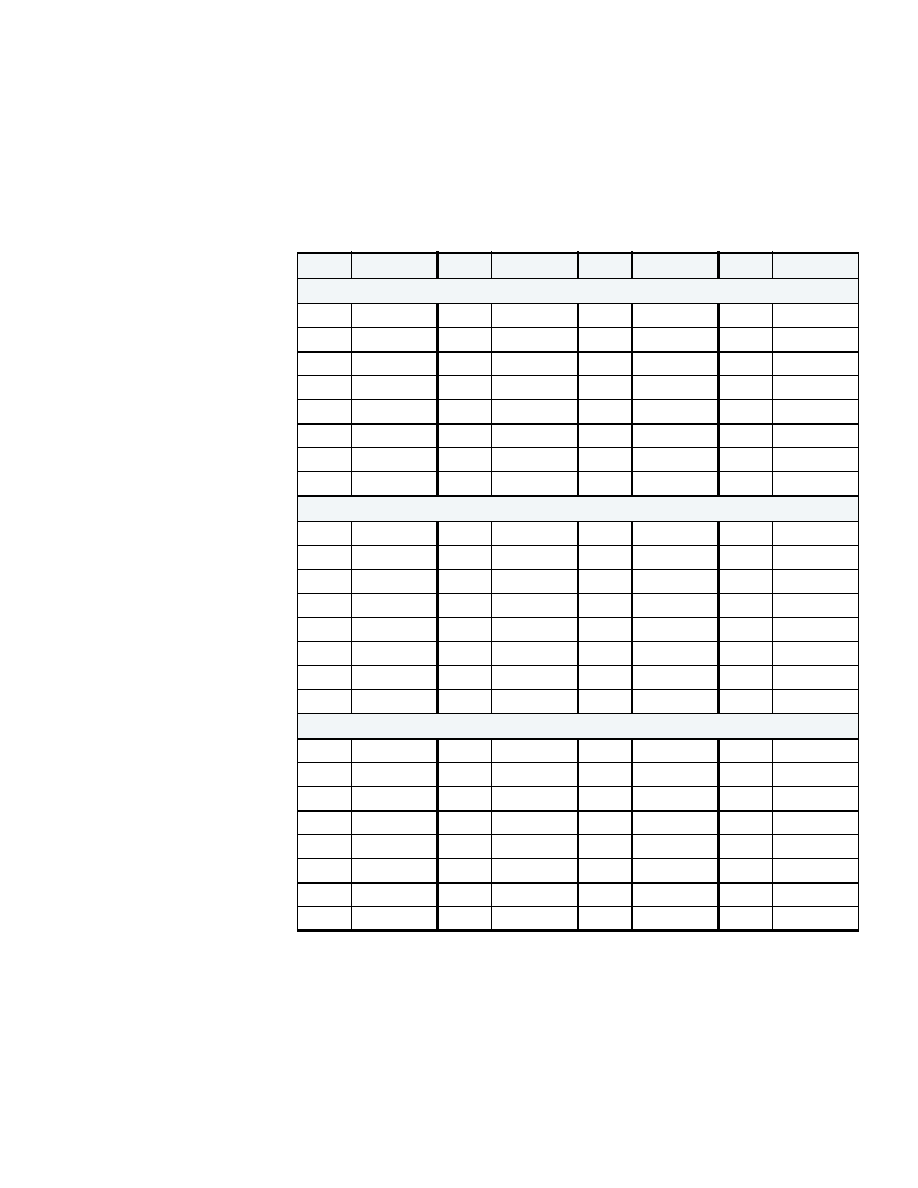

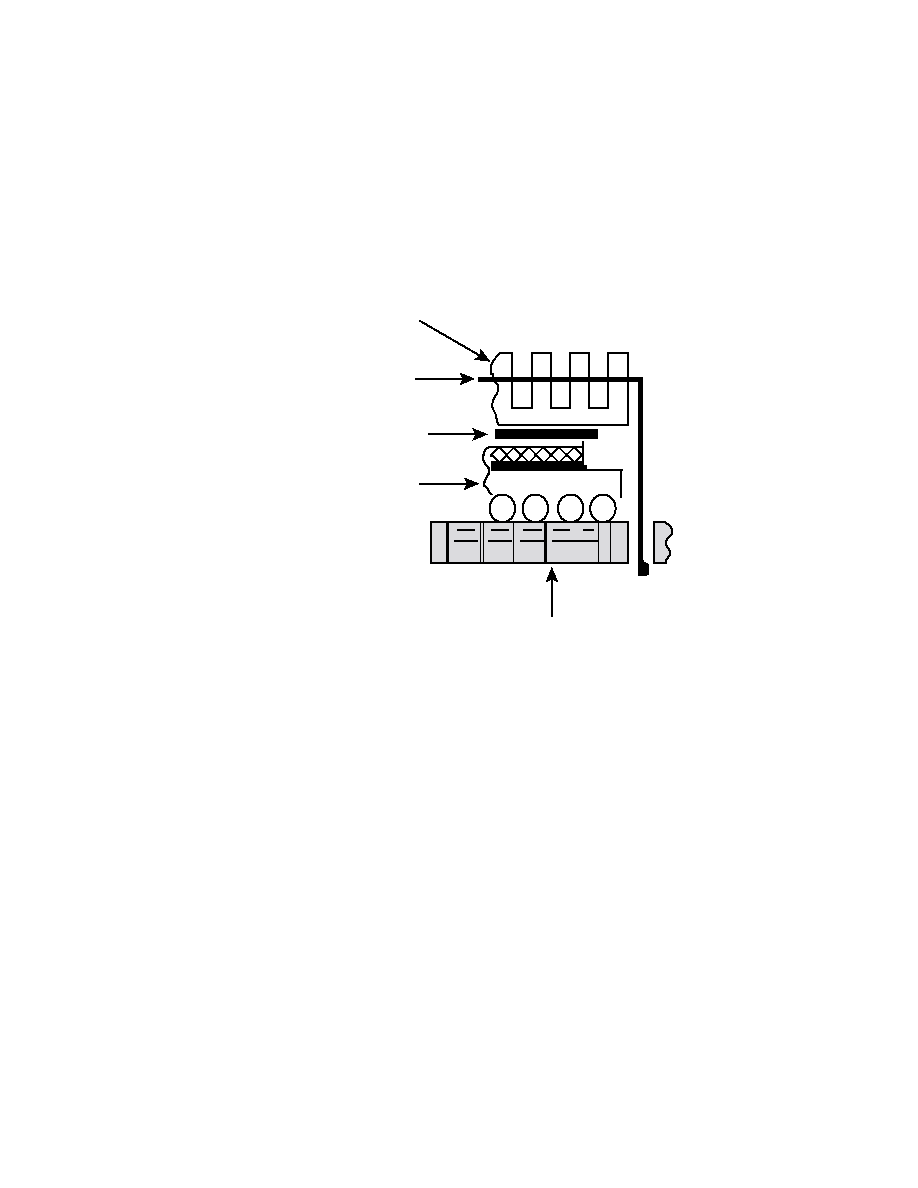

Figure 1

shows a block diagram of the C-5e NP, including its potential external interfaces.

For more information about the architecture of the C-5e NP, see the C-5e/C-3e Network

Processor Architecture Guide (part number C5EC3EARCH-RM/D).

Block Diagram

21

MOTOROLA GENERAL BUSINESS INFORMATION

C5ENPA1-DS/D REV 03

Figure 1 C-5e Network Processor Block Diagram

PHY

PHY

PHY

PHY

PHY

PHY

PHY

PHY

Buses (68Gbps Bandwidth)

Cluster

Cluster

CP-1

CP-0

CP-2

CP-3

CP-12 CP-13 CP-14 CP-15

External

Host CPU

(optional)

OC-3

PHY Interface Examples:

OC-12

Gigabit Ethernet - Aggregated

10/100 Ethernet

External

PROM

(optional)

Control

Logic

(optional)

Fabric

Processor Boundary

Buffer

Mgmt

Unit

Channel

Processors

SDRAM

C-5e

NP

SRAM

SRAM

Table

Lookup

Unit

Fabric

Processor

Executive Processor

Queue

Mgmt

Unit

PCI

Serial

PROM

1xOC-48c or 48x STS-1 with M-5 Companion Device

Q-5

(optional)

22

CHAPTER 1: FUNCTIONAL DESCRIPTION

C5ENPA1-DS/D REV 03

MOTOROLA GENERAL BUSINESS INFORMATION

Channel Processors

The C-5e NP contains sixteen programmable Channel Processors (CPs) that receive,

process, and transmit network data. The number of CPs per port is configurable,

depending on the line interface. Typically one CP is assigned to each port for medium

bandwidth applications (Fast Ethernet to OC-3). Multiple CPs can be assigned to a port in

a configuration called channel aggregation in high bandwidth applications (greater than

OC-3). Multiple logical ports can be assigned to a single CP, with the addition of an

external multiplexor, for low bandwidth applications, such as DS1 to DS3.

The C-5e NP's architecture supports a variety of industry-standard serial and parallel

protocols and individual port data rates including:

�

10/100Mb Ethernet (RMII)

�

1Gb Ethernet (GMII and TBI)

�

OC-3c

�

OC-12

�

OC-48c (using various configurations with M-5 Channel Adapter)

�

OC-48 (using various configurations with M-5 Channel Adapter)

�

100Mbit FibreChannel

�

DS1/DS3, supported through the use of external framers/multiplexors

The C-5e NP's programmability can also support a variety of special interfaces, such as

various xDSL encapsulations and proprietary protocols.

Key components of each CP are a RISC Core (CPRC) that orchestrates cell/packet

processing and a set of microprogrammable, special-purpose processors, called Serial

Data Processors (SDPs), that provide features such as Ethernet MAC and SONET/SDH

framing, multichannel HDLC, and ATM cell delineation. This means you usually only need

to include PHYs to complete the system.

Executive Processor

23

MOTOROLA GENERAL BUSINESS INFORMATION

C5ENPA1-DS/D REV 03

Executive Processor

The Executive Processor (XP) serves as a centralized computing resource for the C-5e NP

and manages the system interfaces.

The XP performs conventional supervisory tasks in the C-5e NP, including:

�

Reset and initialization of the C-5e NP

�

Program loading and control of CPs

�

Centralized exception handling

�

Management of a host interface through the PCI

�

Management of system interfaces (PCI, Serial Bus, PROM)

System Interfaces

The system interfaces to the XP are:

�

PCI -- Provides an industry standard 32bit 33/66MHz PCI channel used for chip-level

shared resources. The PCI has both initiator and target capabilities. The PCI interface is

typically connected to a host processor.

�

Serial Bus Interface -- Provides a general purpose bi-directional, two-wire serial bus

and I/O port that allows the C-5e NP to control external logic with either of two

standard protocols:

� The MDIO (high-speed) protocol: uses a 16bit data format with 10bits of

addressing and supports transfers up to 25MHz.

� The low-speed protocol: uses an 8bit data format followed by an acknowledge bit

and supports transfers up to 400kbps.

Software is used to select which protocol to use, by setting the appropriate bits in the

Serial Bus Configuration Register. When a serial bus transfer is active, an external pin is

driven by the C-5e NP to indicate which protocol is being used (SPLD=0 indicates

MDIO protocol; SPLD=1 indicates low-speed protocol).

Both SIDA and SICL are bi-directional lines that are connected, via an external pull-up

resistor, to a positive supply voltage. When the bus is free, both lines are HIGH because

of the pull-up resistor. The output stages of the devices connected to the bus must

have either an open-drain or open-collector in order to perform the wired-AND

function required for its arbitration mechanism.

24

CHAPTER 1: FUNCTIONAL DESCRIPTION

C5ENPA1-DS/D REV 03

MOTOROLA GENERAL BUSINESS INFORMATION

�

PROM Interface -- Allows the XP to boot from nonvolatile, flash memory. The PROM

interface is a low-speed, serial I/O port that runs at

1

/

2

to

1

/

16

the core clock rate. The

maximum PROM size addressable is 4MBytes, and must use a "by 16" part. External

board logic is required to perform serial-to-parallel conversion for PROM address

outputs and parallel-to-serial conversion for PROM data inputs.

Fabric Processor

The Fabric Processor (FP) acts as a high-speed network interface port with advanced

functionality. It allows the C-5e NP to interface to an application-specific switching

solution internal to your design. The FP port supports the bidirectional transfer of

segments from the C-5e NP to a hardware interface that provides connectivity to other

network processors or other similar line processing hardware. There are numerous

parameters that can be configured within the FP to allow the interface to be adapted to

different fabric protocols. The FP can be configured to conform to seven (7) different

fabric interfaces that include: CSIX-L1, UTOPIA-1, -2, -3, PRIZMA, Power X(CSIX-L0), and

UTOPIA3 like to M-5.

The FP can be configured to run at any frequency up to 125MHz, with the receive and

transmit data buses up to 32 bits wide. This allows a wide range of supported bandwidths

to and from the switching fabric, all the way up to 4000 Mbps full duplex bandwidth.

Buffer Management Unit

The Buffer Management Unit (BMU) interfaces the C-5e NP to external pipeline

architecture, Single Data Rate Synchronous DRAM. The external memory is partitioned

and used as buffers for receiving and transmitting data between CPs, the FP, and the XP. It

is also used as second level storage in the XP memory hierarchy.

The interface to an array of SDRAM chips is 139bits wide, composed of 128 data bits, two

internal control bits, and nine SECDED (single error correction-double error detection) ECC

(error correction code) bits. The interface is compliant with the PC100 standard and

operates at up to 133MHz with 3.3V LVTTL-compatible inputs and outputs. The refresh

period, Trcd, Tcas, Trp, Tmrd, and Trc are configurable via boot time configuration (see the

C-5e/C-3e Network Processor Architecture Guide (part number C5EC3EARCH-RM/D) for more

details).

The C-5e NP non-configurable interface transfers four beats of data for each read and

write using a sequential burst type. In addition, the C-5e NP uses an auto-refresh mode for

the RAM's.

Table Lookup Unit

25

MOTOROLA GENERAL BUSINESS INFORMATION

C5ENPA1-DS/D REV 03

Some of these parameters are programmed into the SDRAMs' mode register and can be

applied only once per power cycle. The ECC functionality can be enabled or disabled via

configuration register writes.

If needed, the interface can narrowed to 128bits by disabling ECC and providing board

pull-ups for the two control bits and nine ECC bits. This is useful if DIMMs are used in the

board design. If individual SDRAM parts are used, x16 and x32 are supported. The BMU

supports SDRAM devices that use 12 address lines. Internal address calculation paths limit

the maximum memory size to 128MBytes. Only one physical bank of SDRAM is supported.

Table Lookup Unit

The Table Lookup Unit (TLU) performs table lookups in external SRAM. It can also be used

for statistics accumulation and retrieval and as general data storage. The TLU

simultaneously supports multiple application-defined tables and multiple search

strategies, such as those needed for routing, circuit switching, and QoS lookup tasks.

The C-5e NP uses external 64bit wide ZBT Pipelined Bursting Static RAM (SRAM) modules

(at frequencies up to 133MHz) for storage of its tables. These modules allow

implementation of tables with 2

25

x 64bit entries using 8Mbit SRAM technology. The

maximum amount of memory supported by the TLU is 128MBytes in four banks, when

SRAM technology supports 4M x 18pins parts.

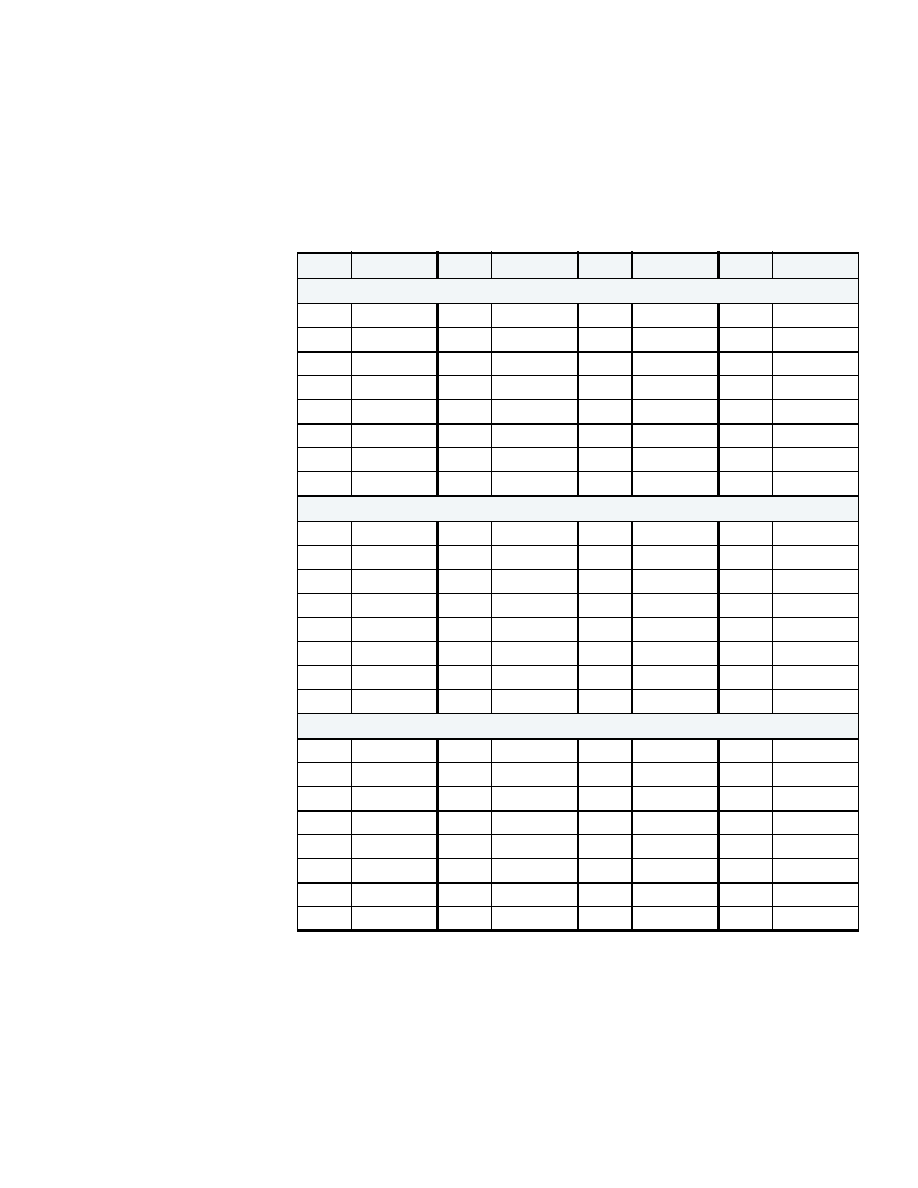

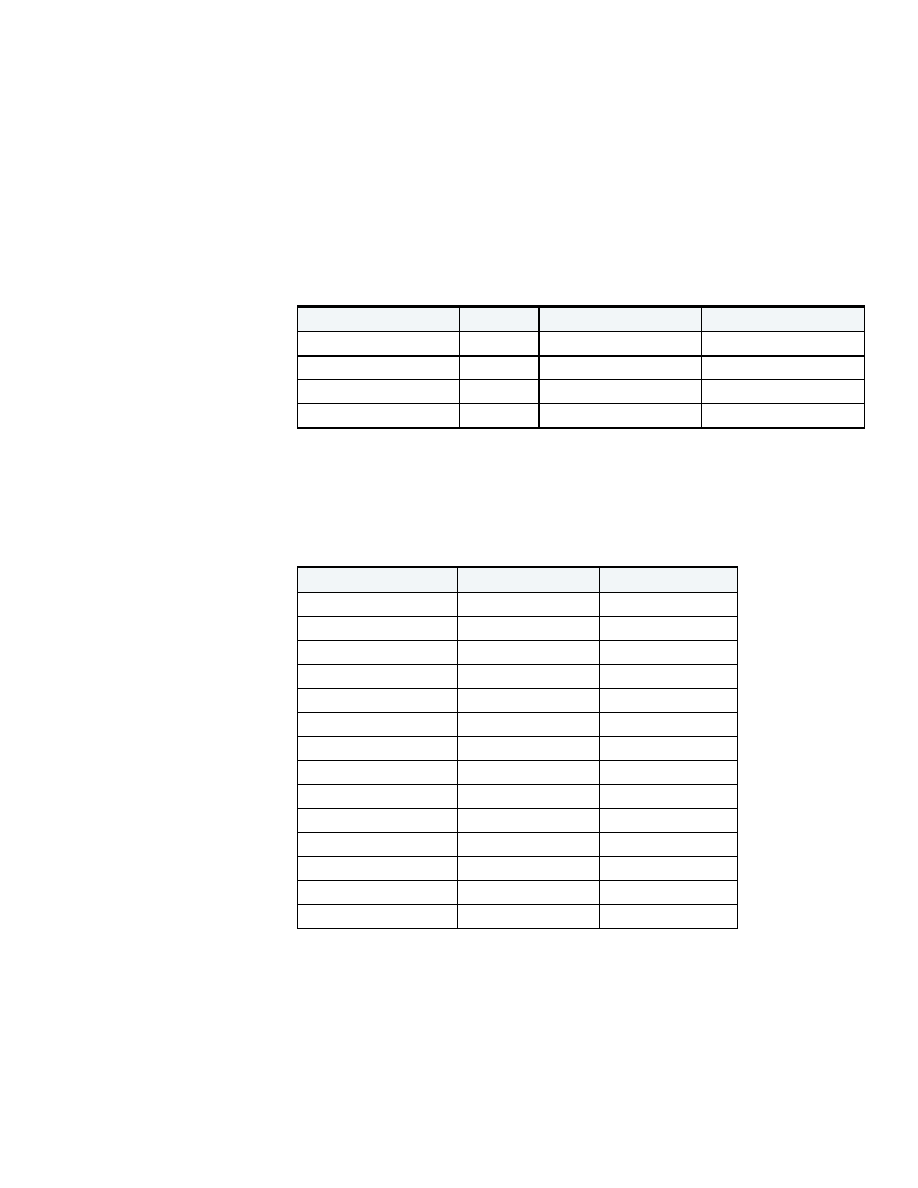

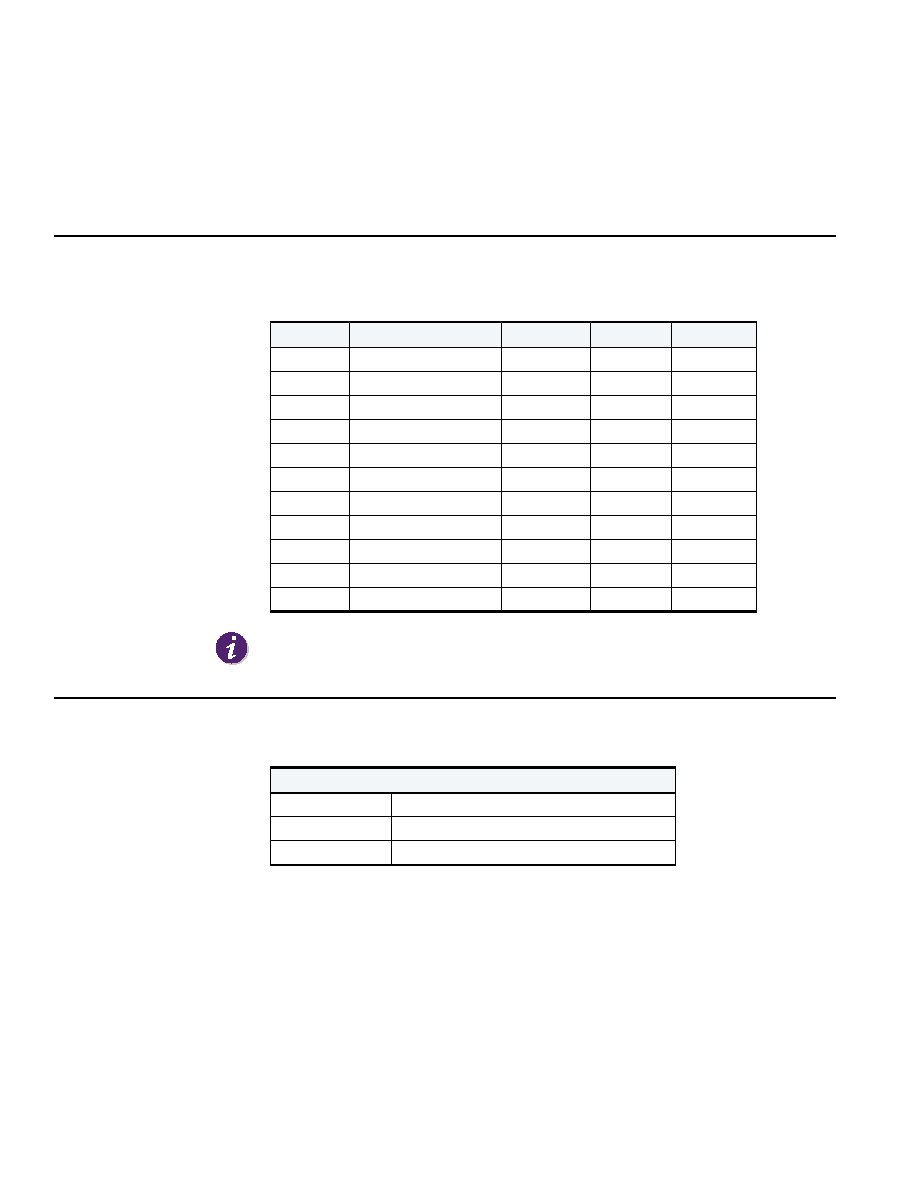

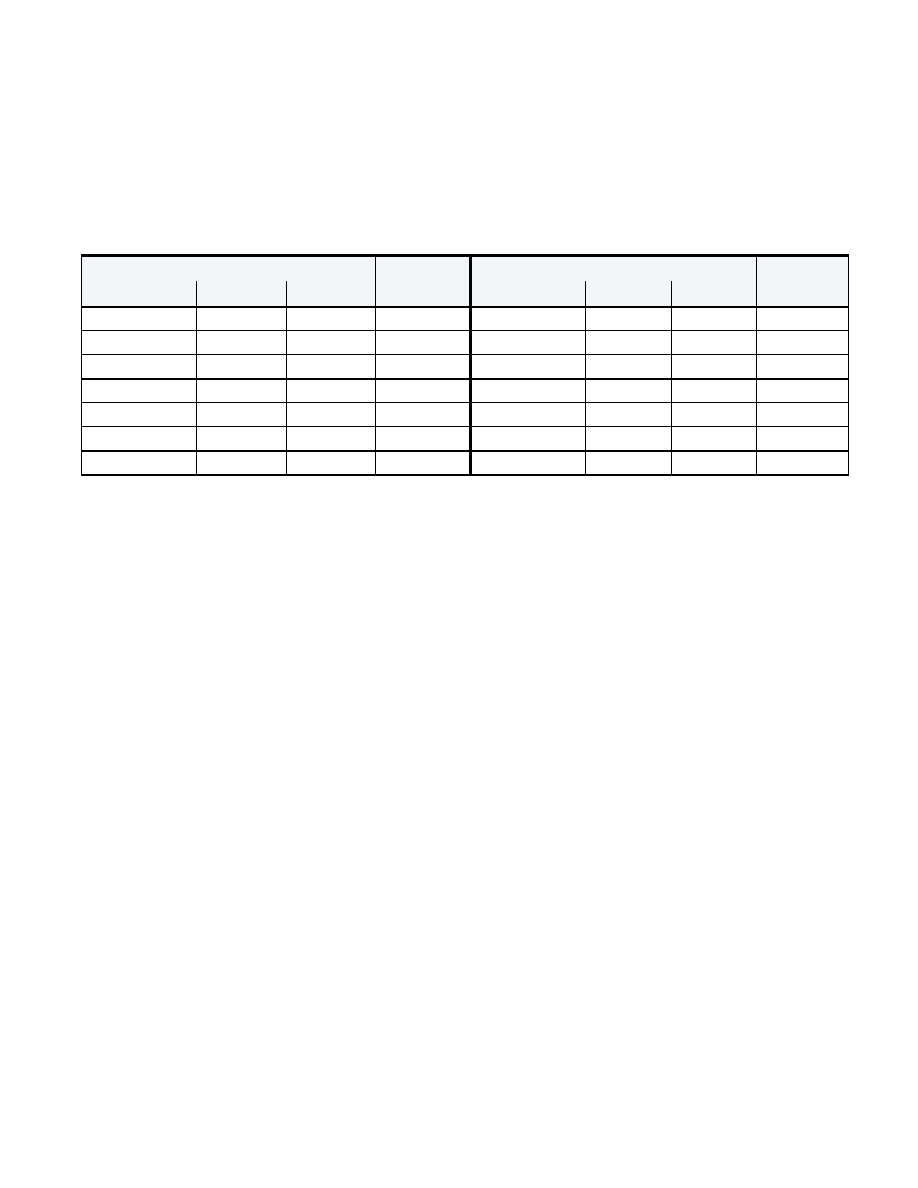

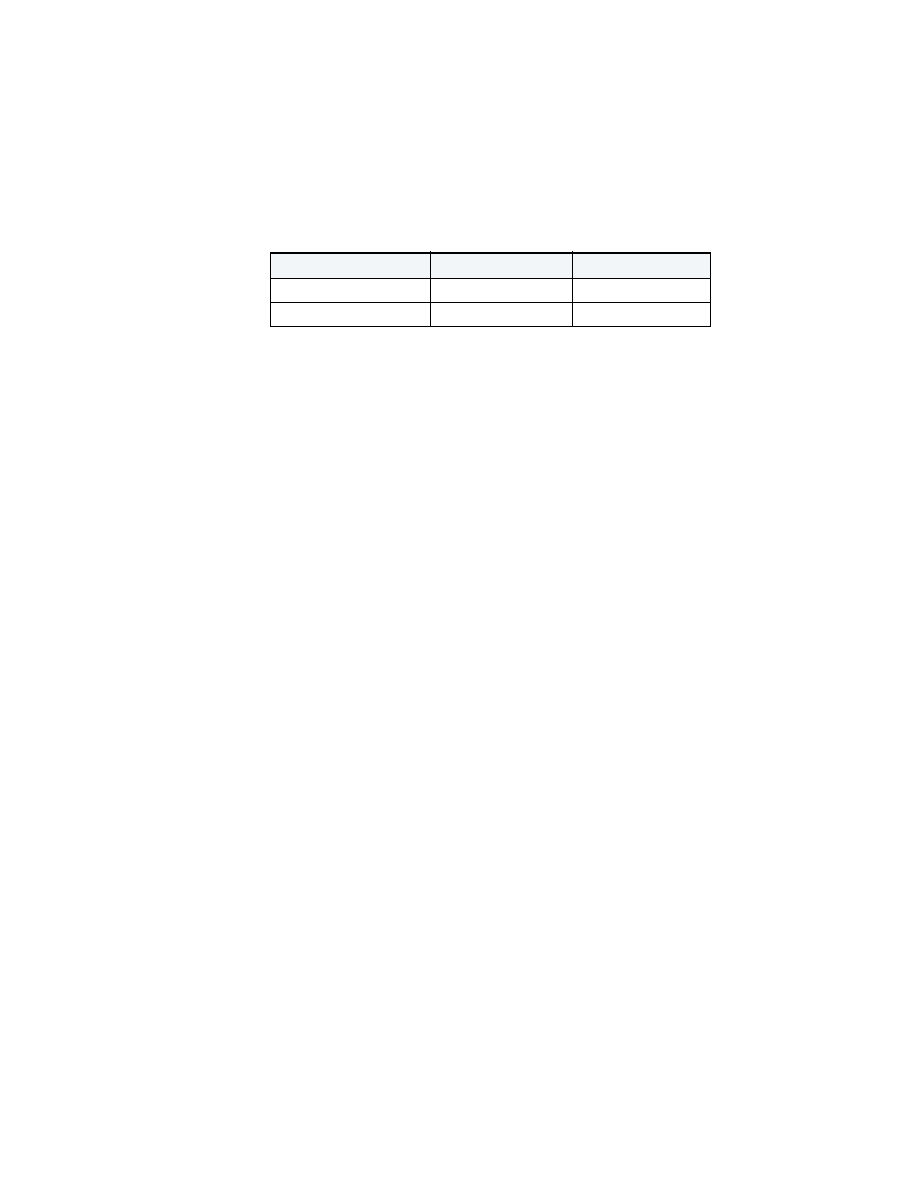

Table 5 TLU SRAM Configurations

SRAM TECHNOLOGY

MIN TABLE SIZE

(ONE BANK)

MAXIMUM TABLE SIZE

(FOUR BANKS)

1Mbit (32k x 32pins)

256kBytes

1MBytes

2Mbit (64k x 32pins)

512kBytes

2MBytes

4Mbit (256k x 18pins)

2MBytes

8MBytes

8Mbit (512k x 18pins)

4MBytes

16MBytes

16Mbit (1M x 18pins)

8MBytes

32MBytes

32Mbit (2M x 18pins)

16MBytes

64MBytes

64Mbit (4M x 18pins)

32MBytes

128MBytes

26

CHAPTER 1: FUNCTIONAL DESCRIPTION

C5ENPA1-DS/D REV 03

MOTOROLA GENERAL BUSINESS INFORMATION

Queue Management Unit

The Queue Management Unit (QMU) autonomously manages a number of

application-defined descriptor queues. It handles inter-CP and inter-C-5e NP descriptor

flows by providing switching and buffering. It also performs descriptor replication for

multicast applications. A number of up to 128 queues can be assigned to each CPRC for

QoS-based services.

The QMU provides a queuing engine internal to the chip and uses external SRAM to store

the descriptors. Scheduling is done by the CPs. The QMU supports up to 512 queues and

16, 384 descriptor buffers. A descriptor buffer holds an application-defined "descriptor",

which is a structure that defines the payload buffer handle and other attributes of the

forwarded cell or packet.

The QMU's external SRAM interface uses ZBT synchronous SRAMs organized in a single

bank of up to 128k, 32bit words. This interface runs at up to 175MHz frequency.

The C-5e provides two modes for managing queues. They consist of:

�

Internal Mode (using the internal QMU only)

�

External Mode (using the internal QMU and the external Q-5 Traffic Management

Coprocessor)

See the C-5e/C-3e Network Processor Architecture Guide (part number C5EC3EARCH-RM/D),

as well as, the Q-5/Q-3 Traffic Management Coprocessor Architecture Guide (part number

Q5Q3ARCH-RM/D)

for more details.

MOTOROLA GENERAL BUSINESS INFORMATION

C5ENPA1-DS/D REV 03

C5ENPA1-DS/D

Rev 03

Chapter 2

SIGNAL DESCRIPTIONS

Signal Summary

There are ten (10) functional groupings of signals in the C-5e Network Processor:

�

Clock -- 11 pins

�

Channel Processors (CP0 - CP15) -- 16x7 = 112 pins

�

Executive Processor (XP) -- 57 pins

� PCI Interface -- 50 pins

� PROM Interface -- 4 pins

� Serial Bus Interface -- 2 pins

� General System Interface -- 1 pin

�

Fabric Processor (FP) -- 80 pins

�

Buffer Management Unit (BMU) -- 160 pins

�

Table Lookup Unit (TLU) -- 99 pins

�

Queue Management Unit (QMU) -- 59 pins

�

Power -- 245 pins

�

Test -- 14 pins

�

No connection (NC) -- 3 pins

Two (2) of the sections (CPs and FP) are configurable, depending on the type of device

being implemented.

28

CHAPTER 2: SIGNAL DESCRIPTIONS

C5ENPA1-DS/D REV 03

MOTOROLA GENERAL BUSINESS INFORMATION

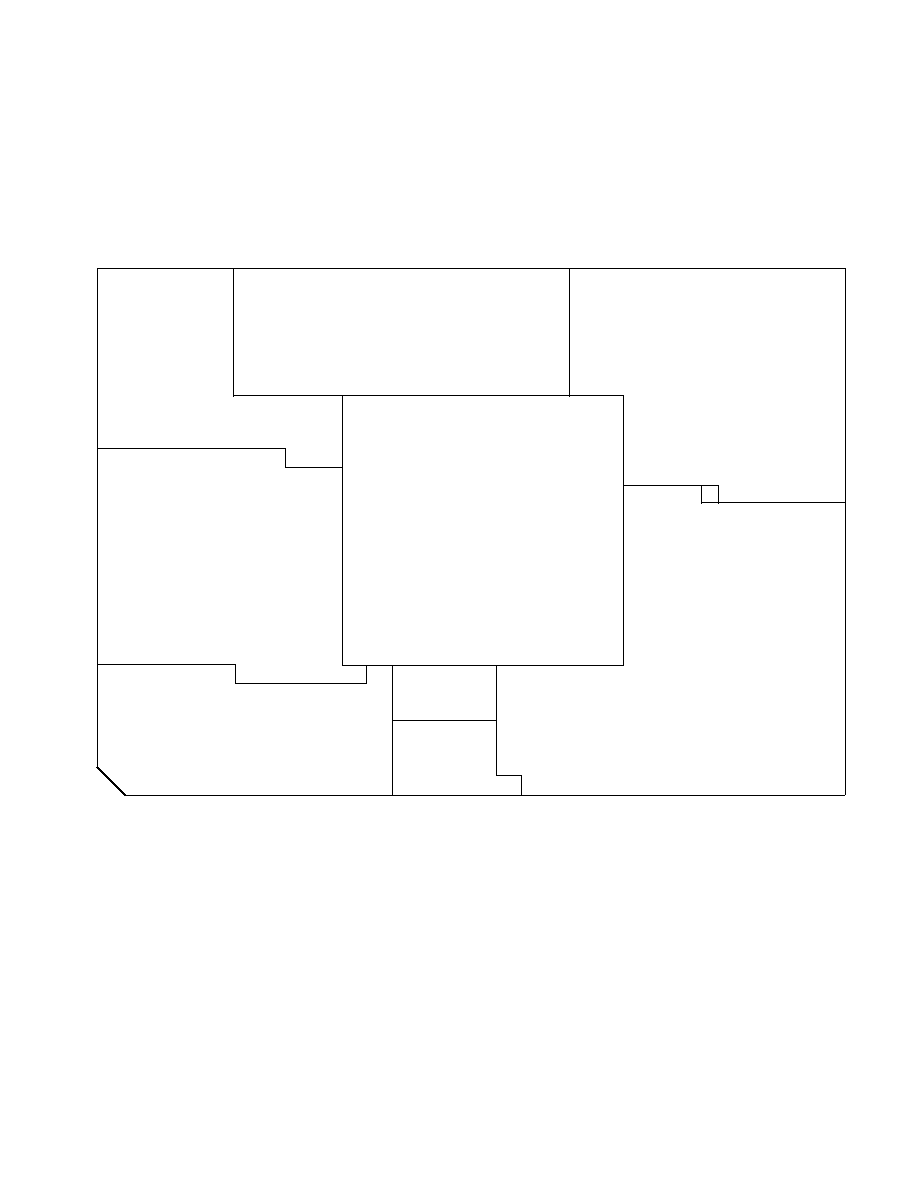

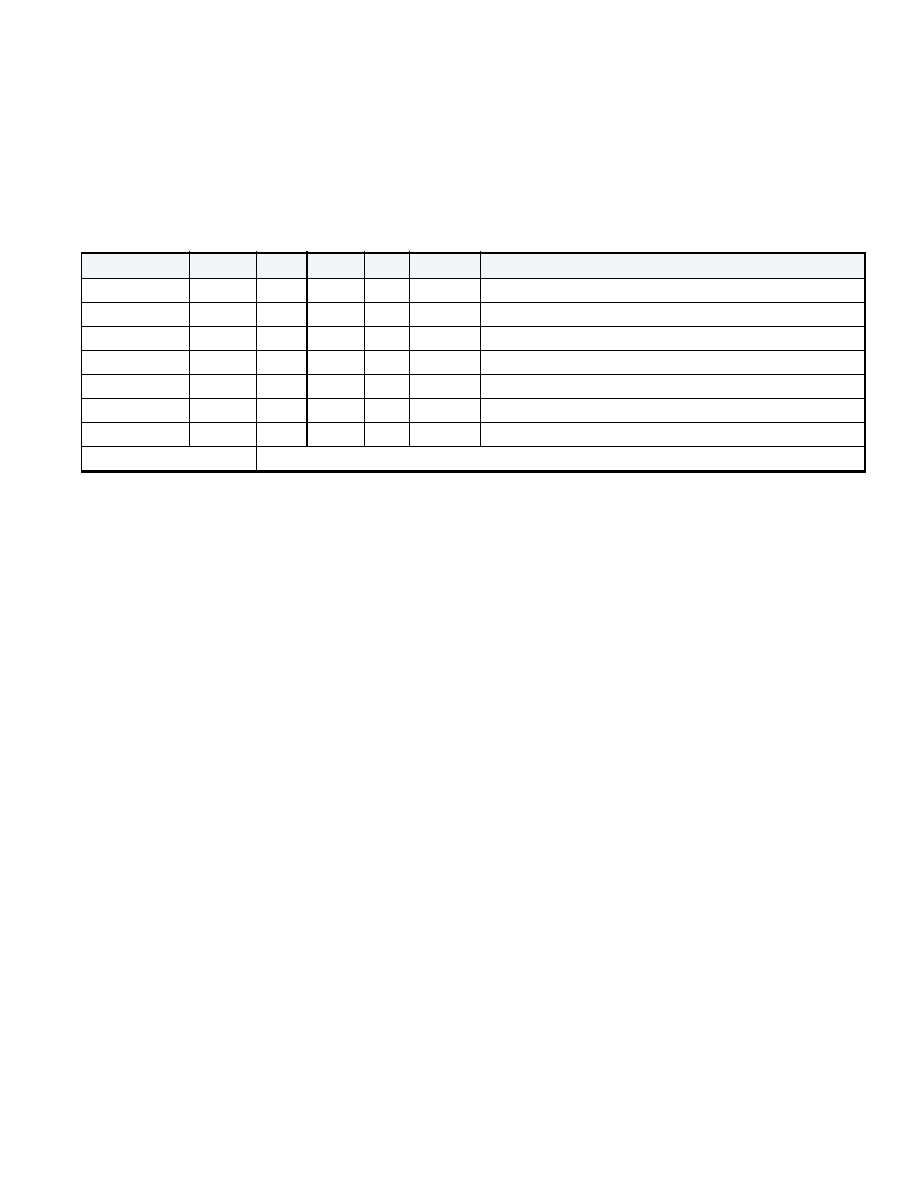

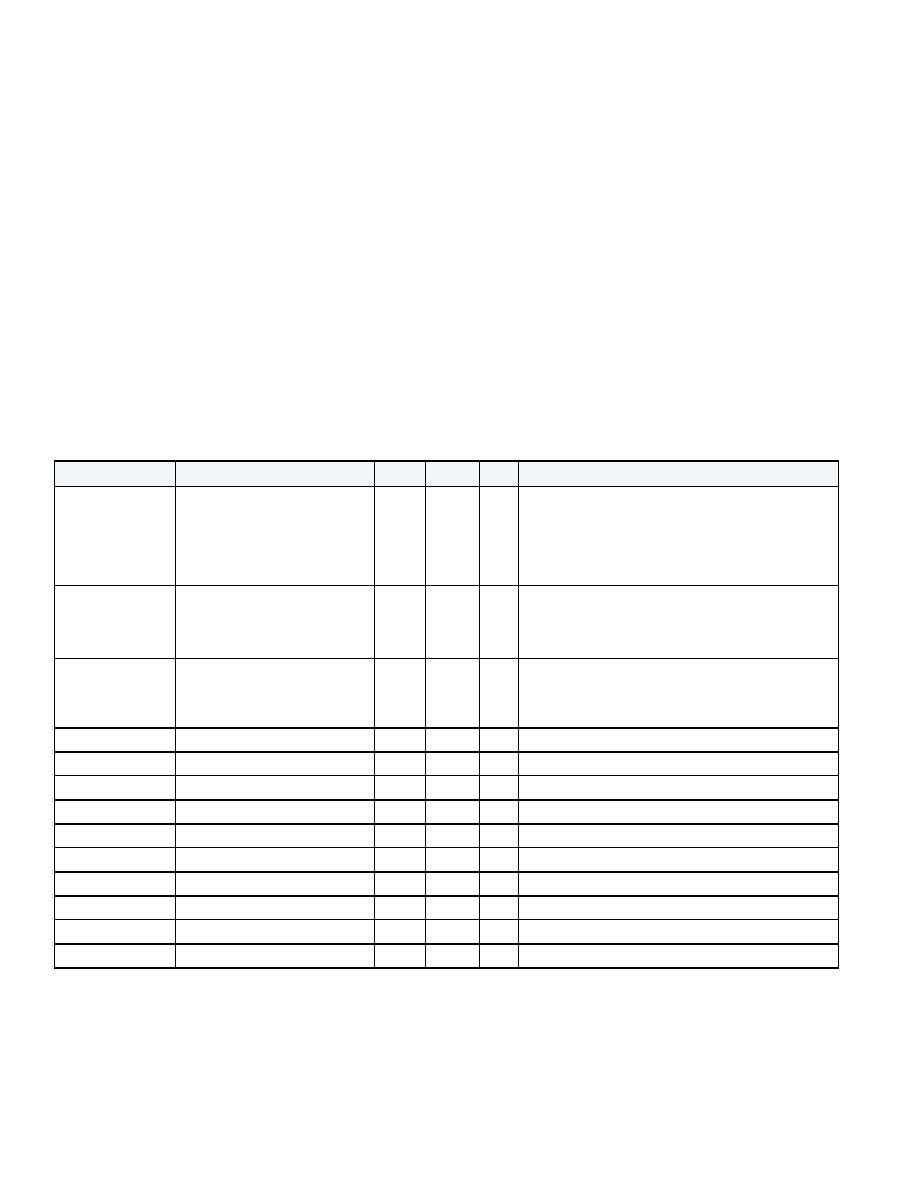

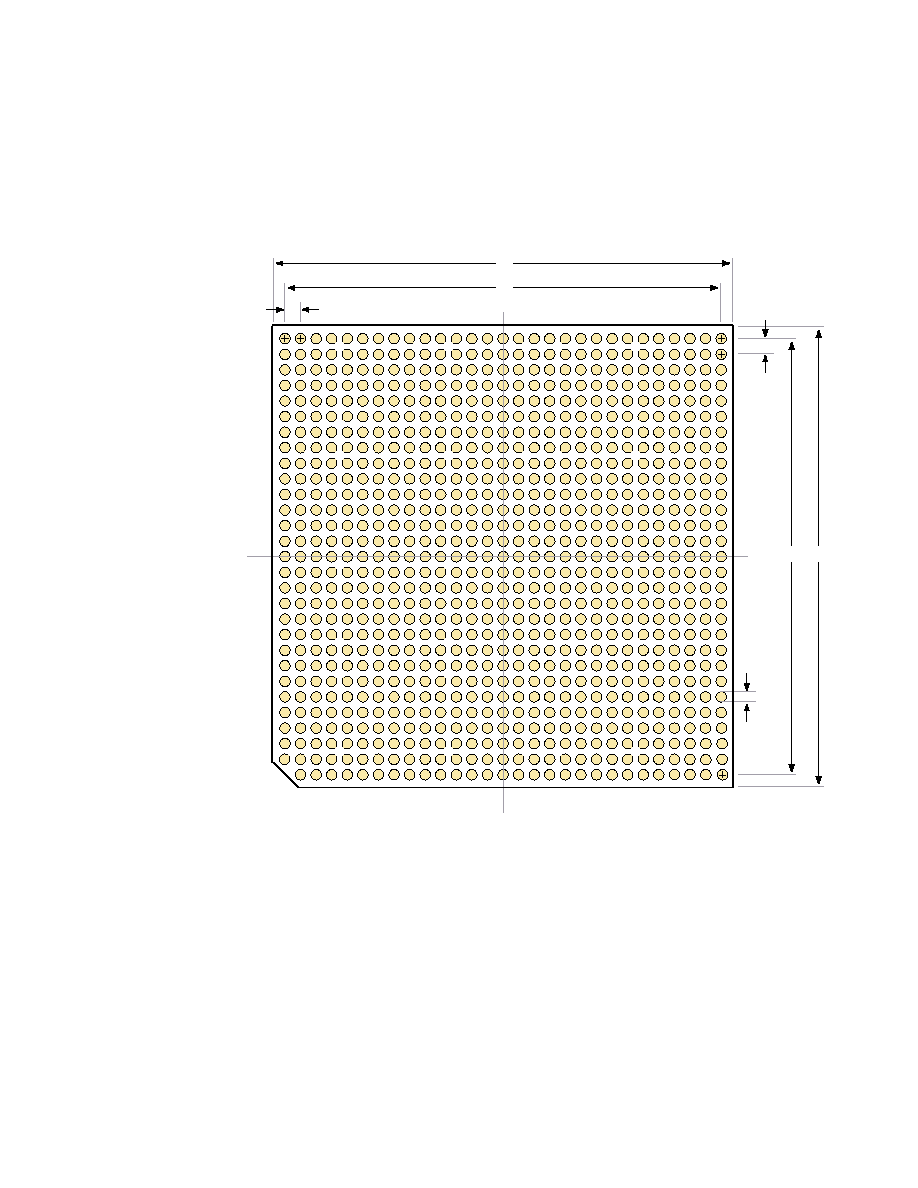

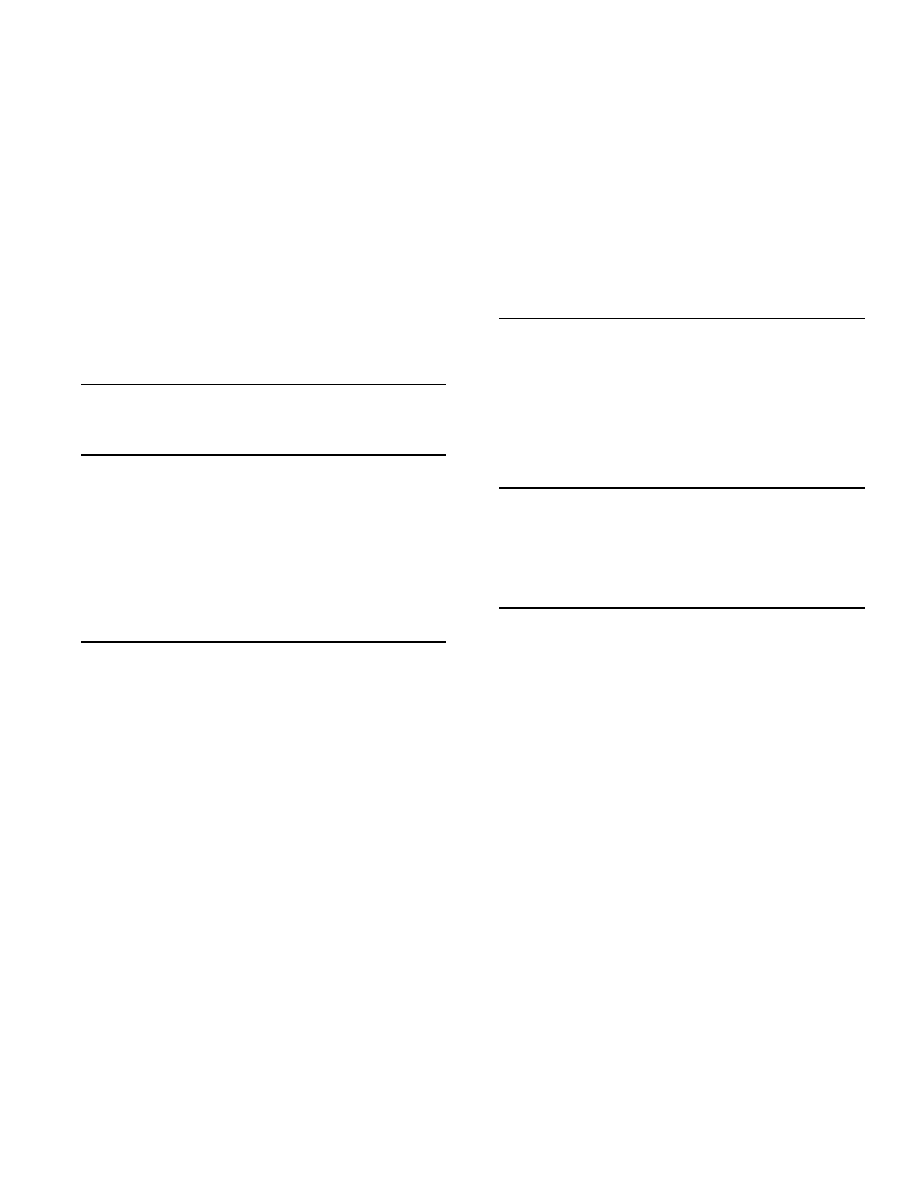

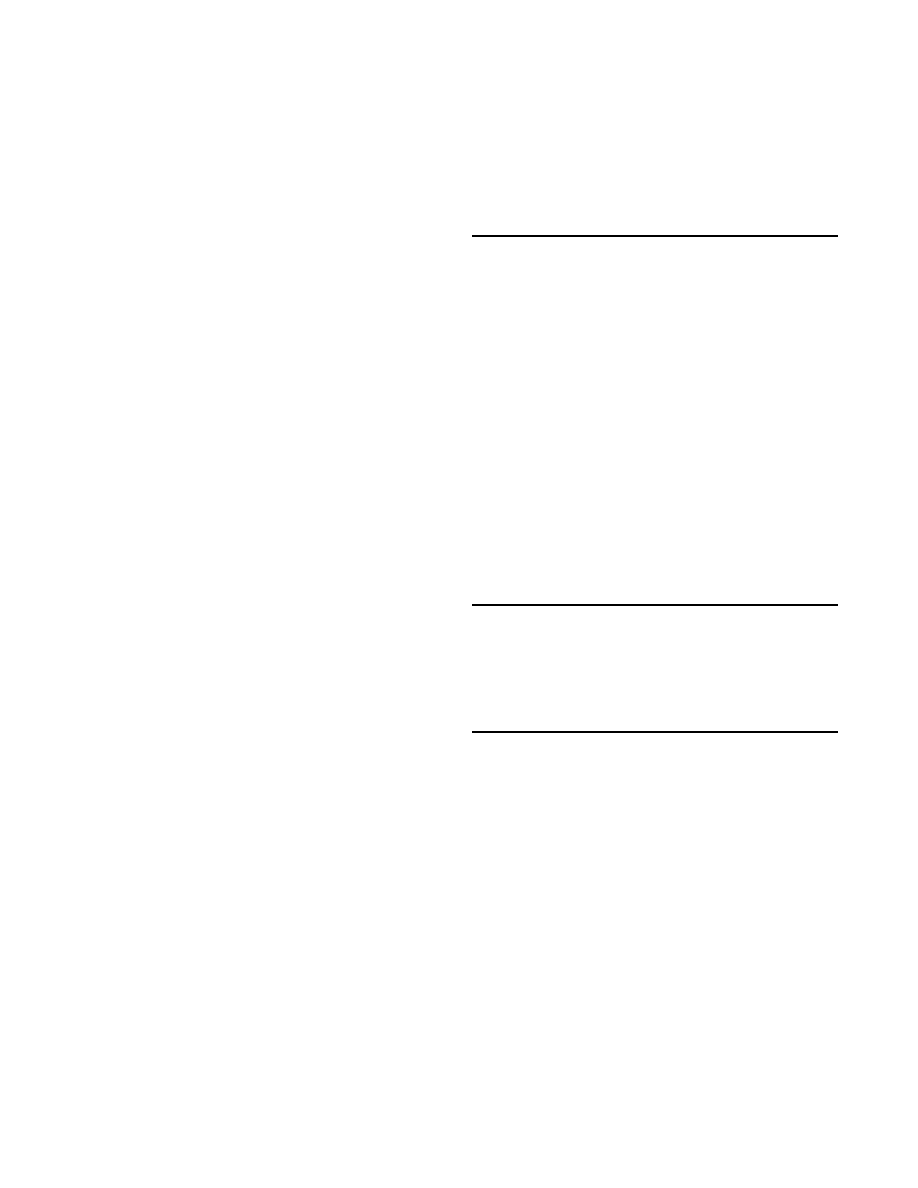

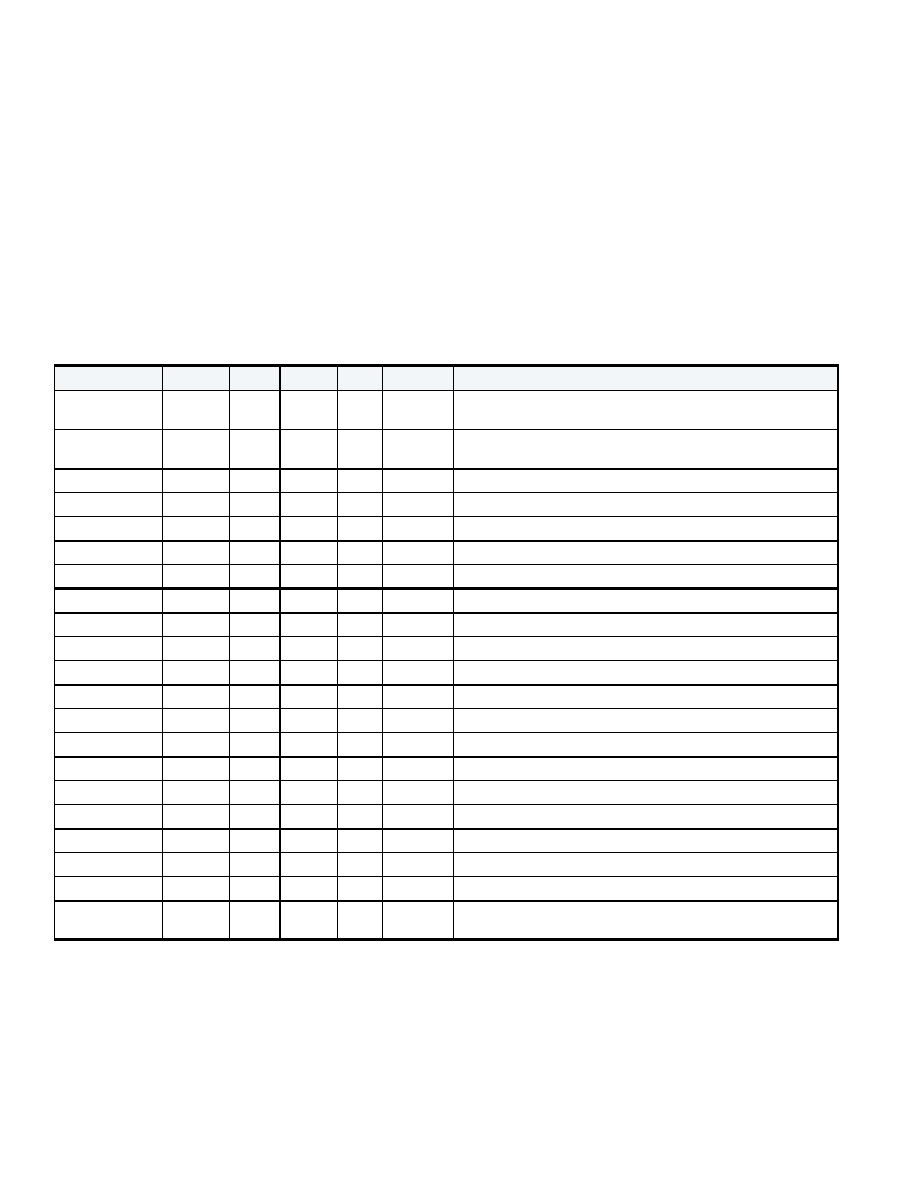

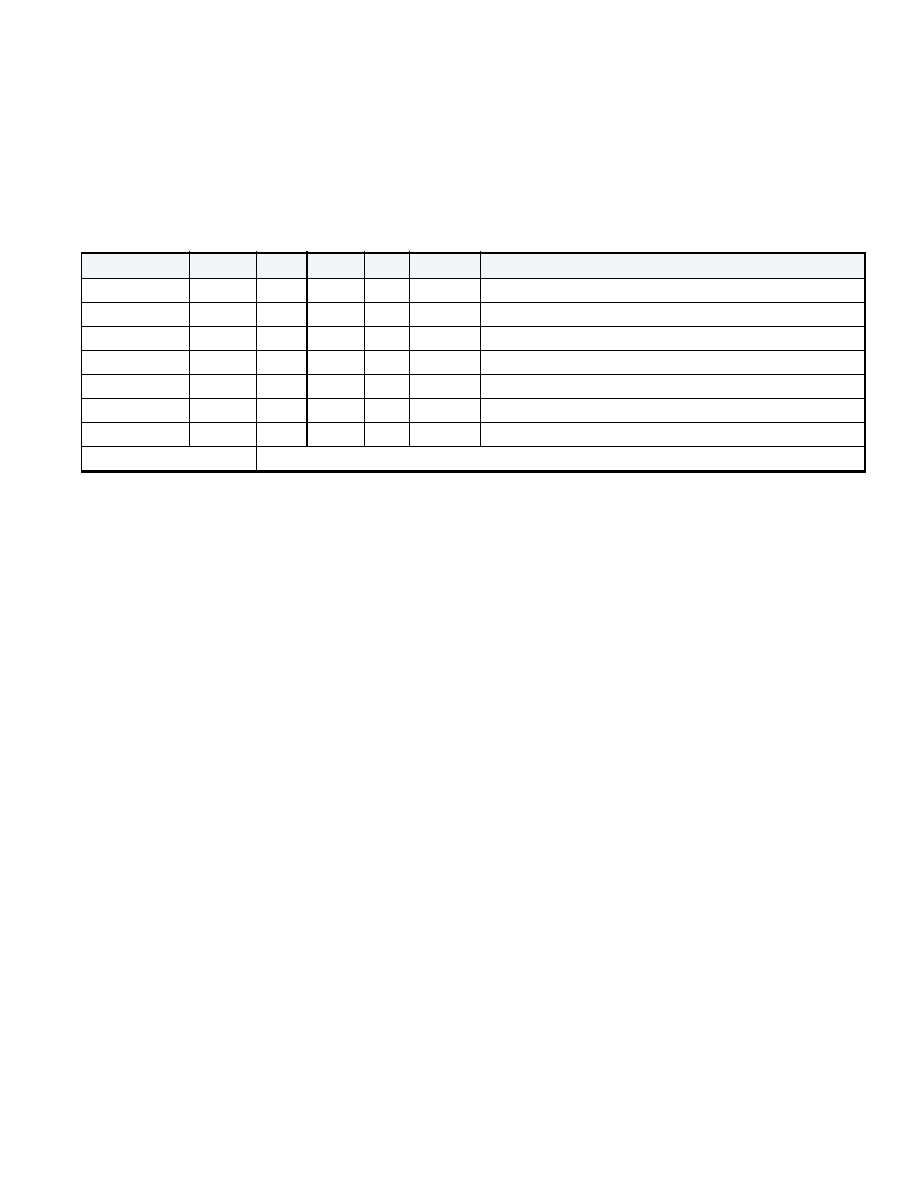

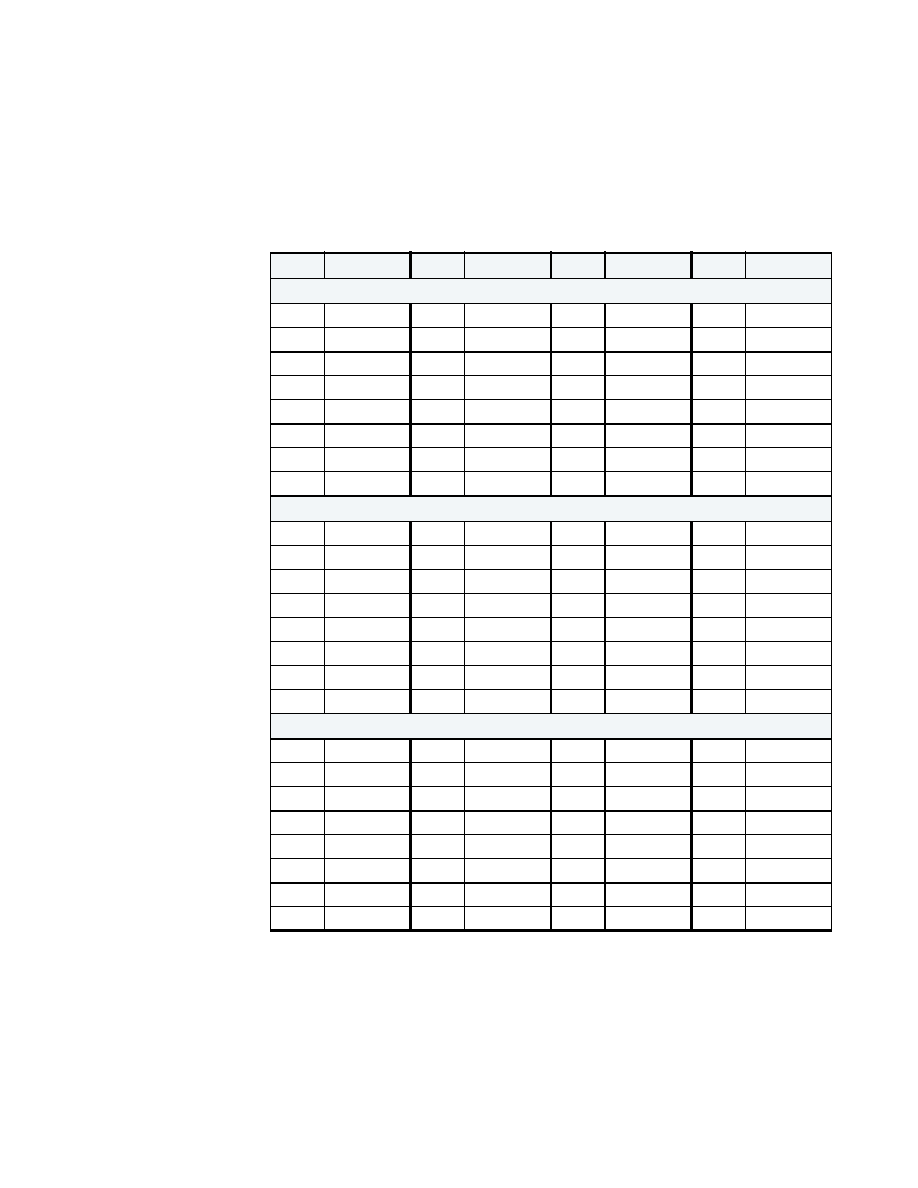

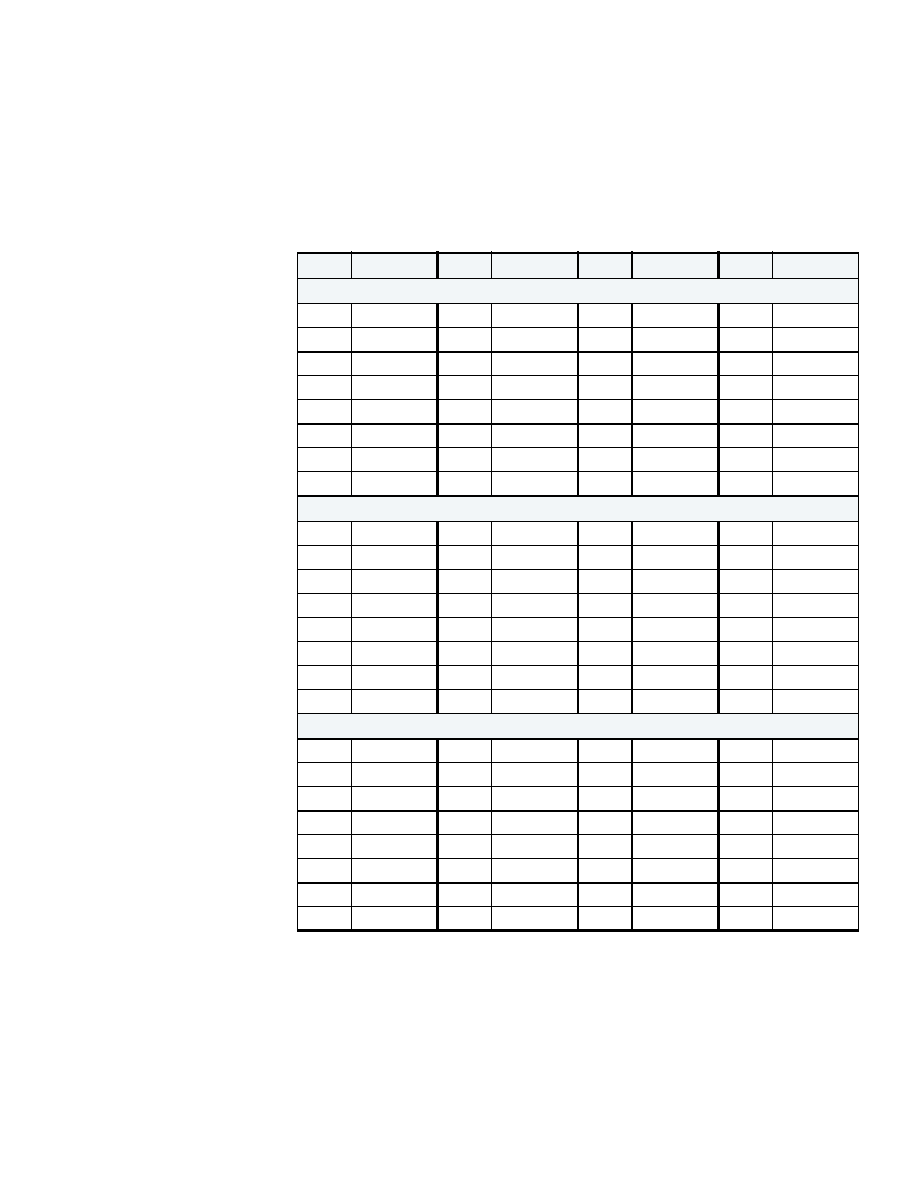

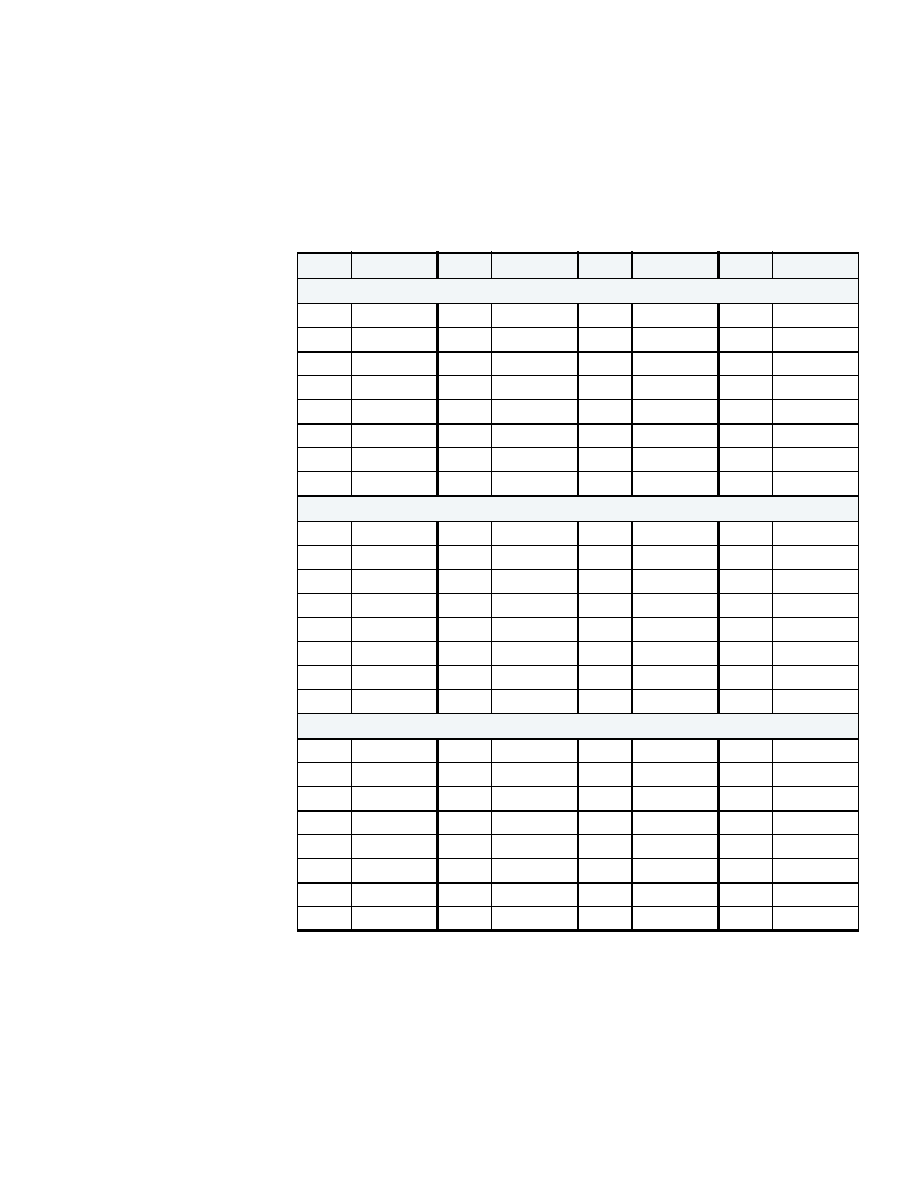

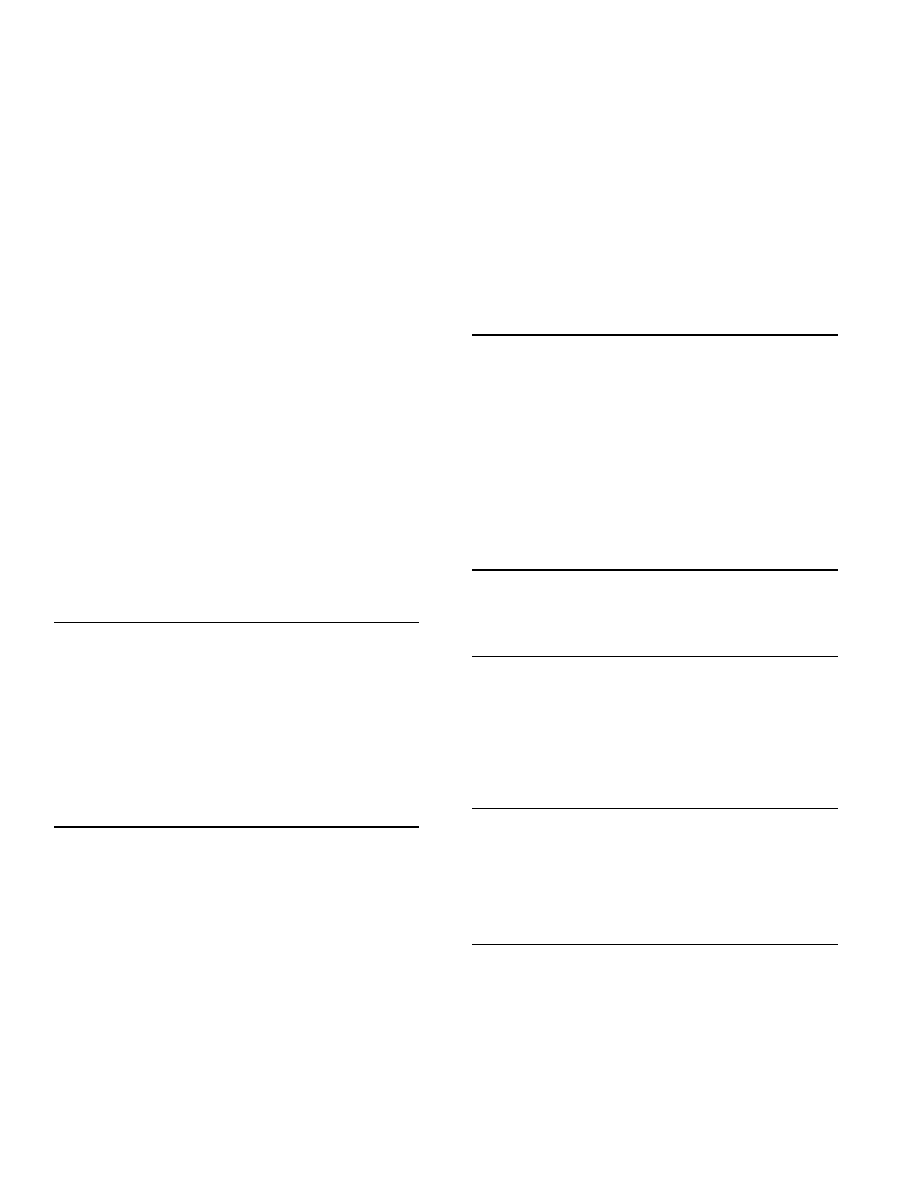

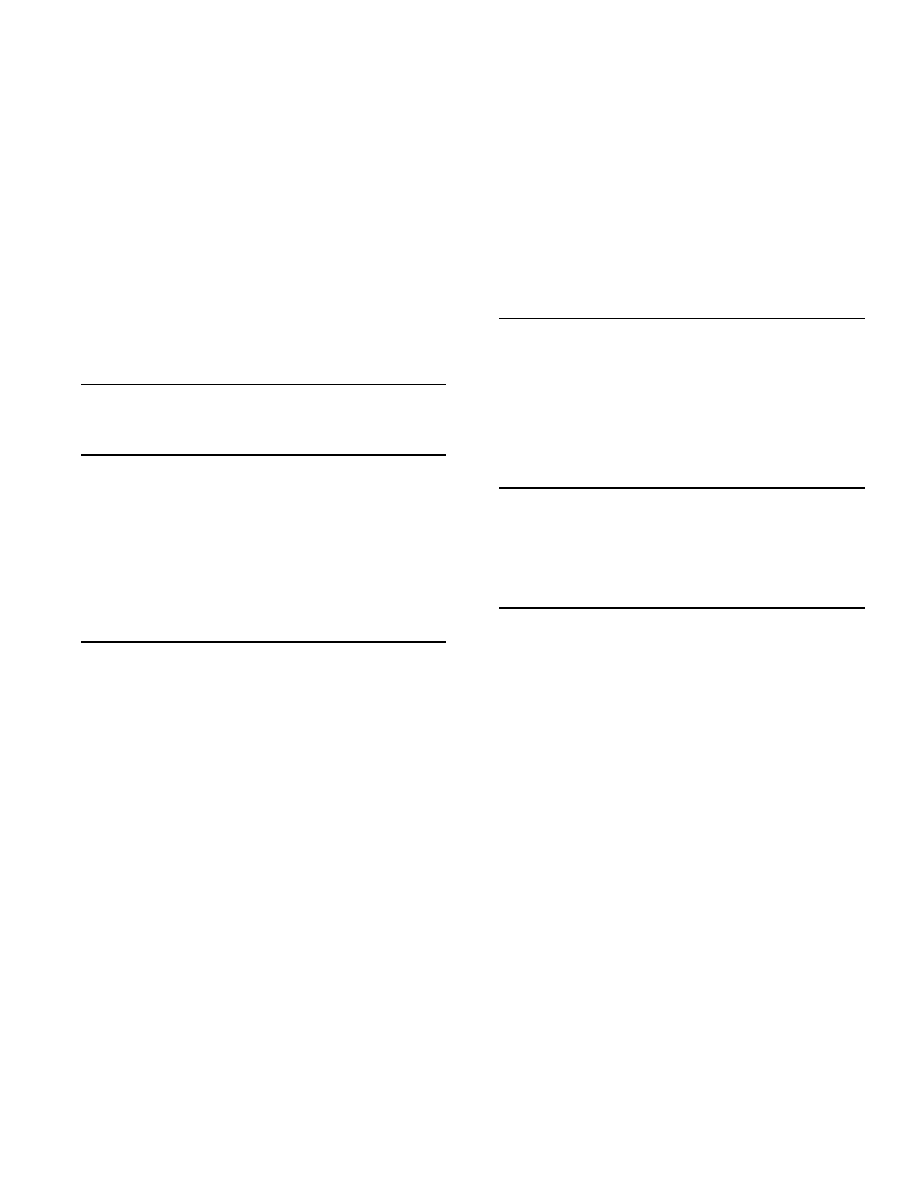

Pinout Diagram

The C-5e NP contains 840 pins. These pin numbers are referenced throughout the

remaining chapter.

Figure 2

shows the pin locations from the top view. In contrast,

Figure 3

shows the pin locations from the bottom view.

Figure 2 Pin Locations (Top View)

29

28

27

26

25

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

AJ

CP0_0

CP1_0

CP1_5 CP2_4

CP3_4

CP5_2 CP6_1

CP7_1

CP8_1

CP8_6

FOUT0 FOUT6 FOUT12 FOUT19 FOUT24

FOUT31 FTXCTL5

FIN3

FIN10

FIN15

FIN22

FIN29

FRXCTL3

PAD0

PAD1

PAD2

PAD3

PAD4

AJ

AH

CP0_1

VDD33

CP1_6 CP2_5

CP3_5

CP5_3 CP6_2

CP7_2

VDD33

CP9_0

FOUT1 FOUT7 FOUT13

GND

FOUT25

FTXCTL0 FTXCTL6

FIN4

VDDF

FIN16

FIN23

FIN30

GND

PAD5

PAD6

PAD7

VDD33

PAD8

AH

AG

CP0_2

CP1_1

CP2_0 CP2_6

CP3_6

CP5_4 CP6_3

CP7_3

CP8_2

CP9_1

FOUT2

VDDF

FOUT14 FOUT20 FOUT26

VDDF

FTXCLK

FIN5

FIN11

FIN17

FIN24

FIN31

FRXCTL4

PAD9

PAD10

PAD11

PAD12

PAD13

AG

AF

CP0_3

CP1_2

VDD33 CP3_0

CP4_0

GND

CP6_4

CP7_4

CP8_3

CP9_2

GND

FOUT8 FOUT15 FOUT21 FOUT27

FTXCTL1

GND

FIN6

FIN12

FIN18

FIN25

GND

FRXCTL5

PAD14

PAD15

VDD33

PAD16

PAD17

AF

AE

CP0_4

GND

CP2_1 CP3_1

CP4_1

CP5_5 CP6_5

CP7_5

GND

CP9_3

FOUT3 FOUT9 FOUT16

VDDF

FOUT28

FTXCTL2

FIN0

FIN7

GND

FIN19

FIN26

FRXCTL0

VDDF

PAD18

PAD19

PAD20

GND

PAD21

AE

AD

CP0_5

CP1_3

CP2_2 CP3_2

CP4_2

CP5_6 CP6_6

CP7_6

CP8_4

CP9_4

FOUT4 FOUT10 FOUT17 FOUT22 FOUT29

FTXCTL3

FIN1

FIN8

FIN13

FIN20

FIN27

FRXCTL1 FRXCTL6

PAD22

PAD23

PAD24

PAD25

PAD26

AD

AC

CP0_6

CP1_4

CP2_3 CP3_3

CP4_3

CP6_0 CP7_0

CP8_0

CP8_5

CP9_5

FOUT5 FOUT11 FOUT18 FOUT23 FOUT30

FTXCTL4

FIN2

FIN9

FIN14

FIN21

FIN28

FRXCTL2 FRXCLK

PAD27

PAD28

PAD29

PAD30

PAD31

AC

AB

CP9_6

CPA_0 VDD33 CPA_1 CPA_2

GND

CPA_4

CPA_5

VDD33

GND

VDD33

GND

VDDF

GND

VDDF

GND

VDDF

GND

VDD33 PTRDYX

PIRDYX

GND

PCBEX0 PCBEX1

PCBEX2

VDD33 PCBEX3

PPAR

AB

AA

CPA_6

GND

CPB_0 CPB_1 CPB_2

CPB_3 CPB_4

CPB_5

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

PREQX

PRSTX

PCLK

VDD33

PSTOPX PDEVSELX PPERRX

GND

PSERRX

AA

Y

CPB_6 CPC_0 CPC_1 CPC_2 CPC_3

CPC_5 CPC_6

CPD_0

VDD33

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDDT

PINTA

PIDSEL

PGNTX

SIDA

SICL

SPCK

SPLD

SPDI

SPDO

Y

W

CPD_1 CPD_2 CPD_3 CPD_4 CPD_5

CPE_0 CPE_1

CPE_2

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

PFRAMEX XPUHOT

TA21

TA20

TA19

TA18

TA17

TA16

TA15

W

V

CPE_3

CPE_4

GND

CPE_5 CPE_6

VDD33 CPF_1

CPF_2

VDD33

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDDT

TA14

TA13

VDDT

TA12

TA11

TA10

GND

TA9

TA8

V

U

CPF_3

VDD33

CPF_4 CPF_5 CPF_6

MD0

MD1

MD2

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

TA7

TA6

TA5

GND

TA4

TA3

TA2

VDDT

TA1

U

T

MD3

MD4

MD5

MD6

MD7

MD9

MD10

MD11

VDD33

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDDT

TWE3X

TWE2X

TWE1X

TWE0X

TCE3X

TCE2X

TCE1X

TCE0X

TA0

T

R

MD12

MD13

MD14

MD15

MD16

MD18

MD19

MD20

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

TD63

TD62

TD61

TD60

TPAR3

TPAR2

TPAR1

TPAR0

TCLKI

R

P

MD21

MD22

VDD33

MD23

MD24

GND

MD26

MD27

VDD33

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDDT

TD59

TD58

GND

TD57

TD56

TD55

VDDT

TD54

TD53

P

N

MD28

GND

MD29

MD30

MD31

MD32

MD33

MD34

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDDT

GND

TD52

TD51

TD50

VDDT

TD49

TD48

TD47

GND

TD46

N

M

MD35

MD36

MD37

MD38

MD39

MD41

MD42

MD43

VDD33

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDDT

TD45

TD44

TD43

TD42

TD41

TD40

TD39

TD38

TD37

M

L

MD44

MD45

MD46

MD47

MD48

MD50

MD51

MD52

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

TD36

TD35

TD34

TD33

TD32

TD31

TD30

TD29

TD28

L

K

MD53

MD54

GND

MD55

MD56

VDD33 MD58

MD59

VDD33

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDDT

TD27

TD26

VDDT

TD25

TD24

TD23

GND

TD22

TD21

K

J

MD60

VDD33

MD61

MD62

MD63

MD64

MD65

MD66

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDDT

GND

TD20

TD19

TD18

GND

TD17

TD16

TD15

VDDT

TD14

J

H

MD67

MD68

MD69

MD70

MD71

MD73

MD74

MD75

VDD33

GND

VDD33

GND

VDD33

GND

VDD33

GND

VDD33

GND

VDDT

TD13

TD12

TD11

TD10

TD9

TD8

TD7

TD6

TD5

H

G

MD76

MD77

MD78

MD79

MD80

MD82

MD83

MD84

MDECC7 MDECC2

MDQM

MA11

MA5

SCLK

CCLK0

CCLK3

CPREF

QA13

TD4

TD3

TD2

TD1

TD0

QD23

QD16

QD11

QD6

QD0

G

F

MD85

MD86

VDD33

MD87

MD88

VDD33 MD90

MD91

MDECC6 MDECC1 MDQML MA10

MA4

SCLKX

CCLK1

CCLK4

CCLK6

QA14

QA9

QA3

QDPH

VDDT

QD30

QD24

QD17

VDDT

QD7

QD1

F

E

MD92

GND

MD93

MD94

MD95

MD96

MD97

MD98

GND

MDECC0

MBA0

MA9

MA3

VDD33

CCLK2

CCLK5

CCLK7

QA15

GND

QA4

QARDY

QBCLKI

GND

QD25

QD18

QD12

GND

QD2

E

D

MD99

MD100 MD101 MD102 MD103

MD105 MD106

MD107 MDECC5

MCASX

GND

MA8

MA2

JSE

JSO0

JSO2

GND

QA16

QA10

QA5

QNQRDY QACLKO

QD31

QD26

QD19

QD13

QD8

QD3

D

C

MD108 MD109

GND

MD110 MD111

VDD33 MD113

MD114 MDECC4

MRASX

MBA1

VDD33

MA1

JTCK JCLKBYP

VDD33

JSO3

QDQPAR QA11

QA6

QA0

VDDT

QWEX

QD27

QD20

GND

QD9

QD4

C

B

MD115 VDD33 MD116 MD117 MD118

MD119 MD120

MD121

VDD33

MWEX

MDCLK

MA7

MA0

GND

JTDI

JHIGHZ

JSO5

NC3

VDDT

QA7

QA1

QACLKI

GND

QD28

QD21

QD14

VDDT

QD5

B

A

MD122 MD123 MD124 MD125 MD126

MD128 MD129 MDECC8 MDECC3

MCSX

NC5

MA6

JSO1

JSO4

JTMS

JTDO

JTRSTX

NC4

QA12

QA8

QA2

QDPL

QBCLKO

QD29

QD22

QD15

QD10

A

29

28

27

26

25

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

24

CP4_4

GND

CP4_5

CP4_6

VDD33

CP5_0

CP5_1

CPA_3

VDD33

CPC_4

CPD_6

CPF_0

GND

MD8

MD17

MD25

VDD33

MD40

MD49

MD57

GND

MD72

MD81

MD89

GND

MD104

MD112

GND

MD127

24

Pinout Diagram

29

MOTOROLA GENERAL BUSINESS INFORMATION

C5ENPA1-DS/D REV 03

Figure 3 Pin Locations (Bottom View)

29

28

27

26

25

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

AJ

CP0_0

CP1_0

CP1_5

CP2_4

CP3_4

CP5_2

CP6_1

CP7_1

CP8_1

CP8_6

FOUT0

FOUT6

FOUT12

FOUT19

FOUT24

FOUT31

FTXCTL5

FIN3

FIN10

FIN15

FIN22

FIN29

FRXCTL3

PAD0

PAD1

PAD2

PAD3

PAD4

AJ

AH

CP0_1

VDD33

CP1_6

CP2_5

CP3_5

CP5_3

CP6_2

CP7_2

VDD33

CP9_0

FOUT1

FOUT7

FOUT13

GND

FOUT25

FTXCTL0

FTXCTL6

FIN4

VDDF

FIN16

FIN23

FIN30

GND

PAD5

PAD6

PAD7

VDD33

PAD8

AH

AG

CP0_2

CP1_1

CP2_0

CP2_6

CP3_6

CP5_4

CP6_3

CP7_3

CP8_2

CP9_1

FOUT2

VDDF

FOUT14

FOUT20

FOUT26

VDDF

FTXCLK

FIN5

FIN11

FIN17

FIN24

FIN31

FRXCTL4

PAD9

PAD10

PAD11

PAD12

PAD13

AG

AF

CP0_3

CP1_2

VDD33

CP3_0

CP4_0

GND

CP6_4

CP7_4

CP8_3

CP9_2

GND

FOUT8

FOUT15

FOUT21

FOUT27

FTXCTL1

GND

FIN6

FIN12

FIN18

FIN25

GND

FRXCTL5

PAD14

PAD15

VDD33

PAD16

PAD17

AF

AE

CP0_4

GND

CP2_1

CP3_1

CP4_1

CP5_5

CP6_5

CP7_5

GND

CP9_3

FOUT3

FOUT9

FOUT16

VDDF

FOUT28

FTXCTL2

FIN0

FIN7

GND

FIN19

FIN26

FRXCTL0

VDDF

PAD18

PAD19

PAD20

GND

PAD21

AE

AD

CP0_5

CP1_3

CP2_2

CP3_2

CP4_2

CP5_6

CP6_6

CP7_6

CP8_4

CP9_4

FOUT4

FOUT10

FOUT17

FOUT22

FOUT29

FTXCTL3

FIN1

FIN8

FIN13

FIN20

FIN27

FRXCTL1

FRXCTL6

PAD22

PAD23

PAD24

PAD25

PAD26

AD

AC

CP0_6

CP1_4

CP2_3

CP3_3

CP4_3

CP6_0

CP7_0

CP8_0

CP8_5

CP9_5

FOUT5

FOUT11

FOUT18

FOUT23

FOUT30

FTXCTL4

FIN2

FIN9

FIN14

FIN21

FIN28

FRXCTL2

FRXCLK

PAD27

PAD28

PAD29

PAD30

PAD31

AC

AB

CP9_6

CPA_0

VDD33

CPA_1

CPA_2

GND

CPA_4

CPA_5

VDD33

GND

VDD33

GND

VDDF

GND

VDDF

GND

VDDF

GND

VDD33

PTRDYX

PIRDYX

GND

PCBEX0

PCBEX1

PCBEX2

VDD33

PCBEX3

PPAR

AB

AA

CPA_6

GND

CPB_0

CPB_1

CPB_2

CPB_3

CPB_4

CPB_5

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

PREQX

PRSTX

PCLK

VDD33

PSTOPX

PDEVSELX

PPERRX

GND

PSERRX

AA

Y

CPB_6

CPC_0

CPC_1

CPC_2

CPC_3

CPC_5

CPC_6

CPD_0

VDD33

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDDT

PINTA

PIDSEL

PGNTX

SIDA

SICL

SPCK

SPLD

SPDI

SPDO

Y

W

CPD_1

CPD_2

CPD_3

CPD_4

CPD_5

CPE_0

CPE_1

CPE_2

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

PFRAMEX

XPUHOT

TA21

TA20

TA19

TA18

TA17

TA16

TA15

W

V

CPE_3

CPE_4

GND

CPE_5

CPE_6

VDD33

CPF_1

CPF_2

VDD33

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDDT

TA14

TA13

VDDT

TA12

TA11

TA10

GND

TA9

TA8

V

U

CPF_3

VDD33

CPF_4

CPF_5

CPF_6

MD0

MD1

MD2

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

TA7

TA6

TA5

GND

TA4

TA3

TA2

VDDT

TA1

U

T

MD3

MD4

MD5

MD6

MD7

MD9

MD10

MD11

VDD33

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDDT

TWE3X

TWE2X

TWE1X

TWE0X

TCE3X

TCE2X

TCE1X

TCE0X

TA0

T

R

MD12

MD13

MD14

MD15

MD16

MD18

MD19

MD20

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

TD63

TD62

TD61

TD60

TPAR3

TPAR2

TPAR1

TPAR0

TCLKI

R

P

MD21

MD22

VDD33

MD23

MD24

GND

MD26

MD27

VDD33

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDDT

TD59

TD58

GND

TD57

TD56

TD55

VDDT

TD54

TD53

P

N

MD28

GND

MD29

MD30

MD31

MD32

MD33

MD34

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDDT

GND

TD52

TD51

TD50

VDDT

TD49

TD48

TD47

GND

TD46

N

M

MD35

MD36

MD37

MD38

MD39

MD41

MD42

MD43

VDD33

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDDT

TD45

TD44

TD43

TD42

TD41

TD40

TD39

TD38

TD37

M

L

MD44

MD45

MD46

MD47

MD48

MD50

MD51

MD52

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

TD36

TD35

TD34

TD33

TD32

TD31

TD30

TD29

TD28

L

K

MD53

MD54

GND

MD55

MD56

VDD33

MD58

MD59

VDD33

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDDT

TD27

TD26

VDDT

TD25

TD24

TD23

GND

TD22

TD21

K

J

MD60

VDD33

MD61

MD62

MD63

MD64

MD65

MD66

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDDT

GND

TD20

TD19

TD18

GND

TD17

TD16

TD15

VDDT

TD14

J

H

MD67

MD68

MD69

MD70

MD71

MD73

MD74

MD75

VDD33

GND

VDD33

GND

VDD33

GND

VDD33

GND

VDD33

GND

VDDT

TD13

TD12

TD11

TD10

TD9

TD8

TD7

TD6

TD5

H

G

MD76

MD77

MD78

MD79

MD80

MD82

MD83

MD84

MDECC7

MDECC2

MDQM

MA11

MA5

SCLK

CCLK0

CCLK3

CPREF

QA13

TD4

TD3

TD2

TD1

TD0

QD23

QD16

QD11

QD6

QD0

G

F

MD85

MD86

VDD33

MD87

MD88

VDD33

MD90

MD91

MDECC6

MDECC1

MDQML

MA10

MA4

SCLKX

CCLK1

CCLK4

CCLK6

QA14

QA9

QA3

QDPH

VDDT

QD30

QD24

QD17

VDDT

QD7

QD1

F

E

MD92

GND

MD93

MD94

MD95

MD96

MD97

MD98

GND

MDECC0

MBA0

MA9

MA3

VDD33

CCLK2

CCLK5

CCLK7

QA15

GND

QA4

QARDY

QBCLKI

GND

QD25

QD18

QD12

GND

QD2

E

D

MD99

MD100

MD101

MD102

MD103

MD105

MD106

MD107

MDECC5

MCASX

GND

MA8

MA2

JSE

JSO0

JSO2

GND

QA16

QA10

QA5

QNQRDY

QACLKO

QD31

QD26

QD19

QD13

QD8

QD3

D

C

MD108

MD109

GND

MD110

MD111

VDD33

MD113

MD114

MDECC4

MRASX

MBA1

VDD33

MA1

JTCK

JCLKBYP

VDD33

JSO3

QDQPAR

QA11

QA6

QA0

VDDT

QWEX

QD27

QD20

GND

QD9

QD4

C

B

MD115

VDD33

MD116

MD117

MD118

MD119

MD120

MD121

VDD33

MWEX

MDCLK

MA7

MA0

GND

JTDI

JHIGHZ

JSO5

NC3

VDDT

QA7

QA1

QACLKI

GND

QD28

QD21

QD14

VDDT

QD5

B

A

MD122

MD123

MD124

MD125

MD126

MD128

MD129

MDECC8

MDECC3

MCSX

NC5

MA6

JSO1

JSO4

JTMS

JTDO

JTRSTX

NC4

QA12

QA8

QA2

QDPL

QBCLKO

QD29

QD22

QD15

QD10

A

29

28

27

26

25

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

24

CP4_4

GND

CP4_5

CP4_6

VDD33

CP5_0

CP5_1

CPA_3

VDD33

CPC_4

CPD_6

CPF_0

GND

MD8

MD17

MD25

VDD33

MD40

MD49

MD57

GND

MD72

MD81

MD89

GND

MD104

MD112

GND

MD127

24

30

CHAPTER 2: SIGNAL DESCRIPTIONS

C5ENPA1-DS/D REV 03

MOTOROLA GENERAL BUSINESS INFORMATION

Pin Descriptions Grouped

by Function

The C-5e NP pins are categorized in groups, reflecting interfaces to the chip:

�

Clock Signals

�

CP Interface Signals

�

Executive Processor System Interface Signals

�

Fabric Processor Interface Signals

�

BMU SDRAM Interface Signals

�

TLU SRAM Interface Signals

�

QMU SRAM (Internal Mode) Interface Signals

�

QMU to Q-5 TMC (External Mode) Interface Signals

�

Power Supply Signals

�

Test Signals

�

No Connection Pins

Pins conform to Joint Electronic Devices Engineering Council (JEDEC) standards.

LVTTL and LVPECL

Specifications

C-5e NP pins are the following types:

�

Low Voltage TTL-Compatible (LVTTL). The C-5e NP's LVTTL pins conform to the JEDEC

JESD8-B specification.

�

Low Voltage Positive Emitter Coupled Logic (LVPECL).

All of the signals in the following tables in this chapter denote whether the individual

signal is an Input (I), Output (O), both Input and Output (I/O), or power (P). In addition, a

PU, PD, and nc are used. The PU indicates that an internal resistor will pullup the pad if

left unconnected. PD indicates an internal pulldown resistor. NC means the pad is to be

left unconnected.

Pin Descriptions Grouped by Function

31

MOTOROLA GENERAL BUSINESS INFORMATION

C5ENPA1-DS/D REV 03

Clock Signals

Table 6

describes the C-5e NP clock signals.

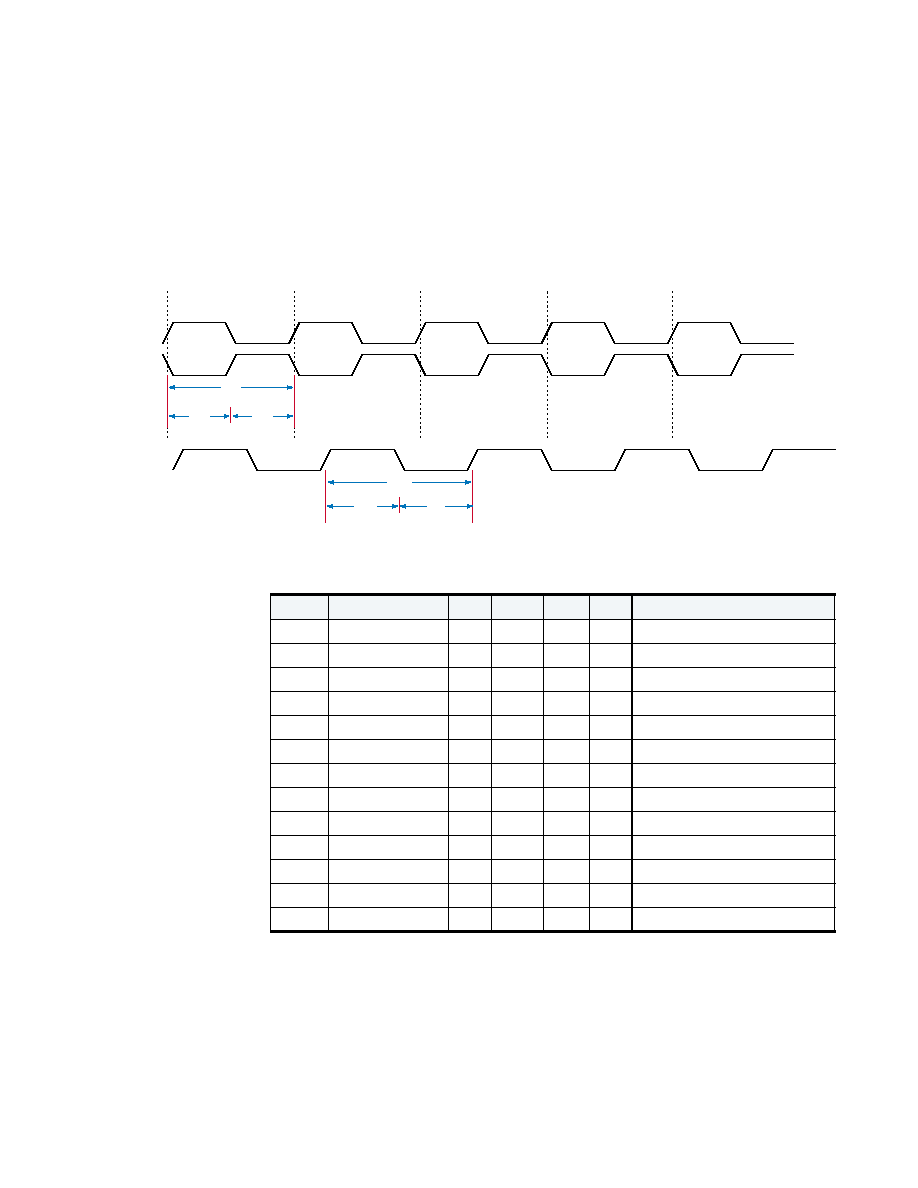

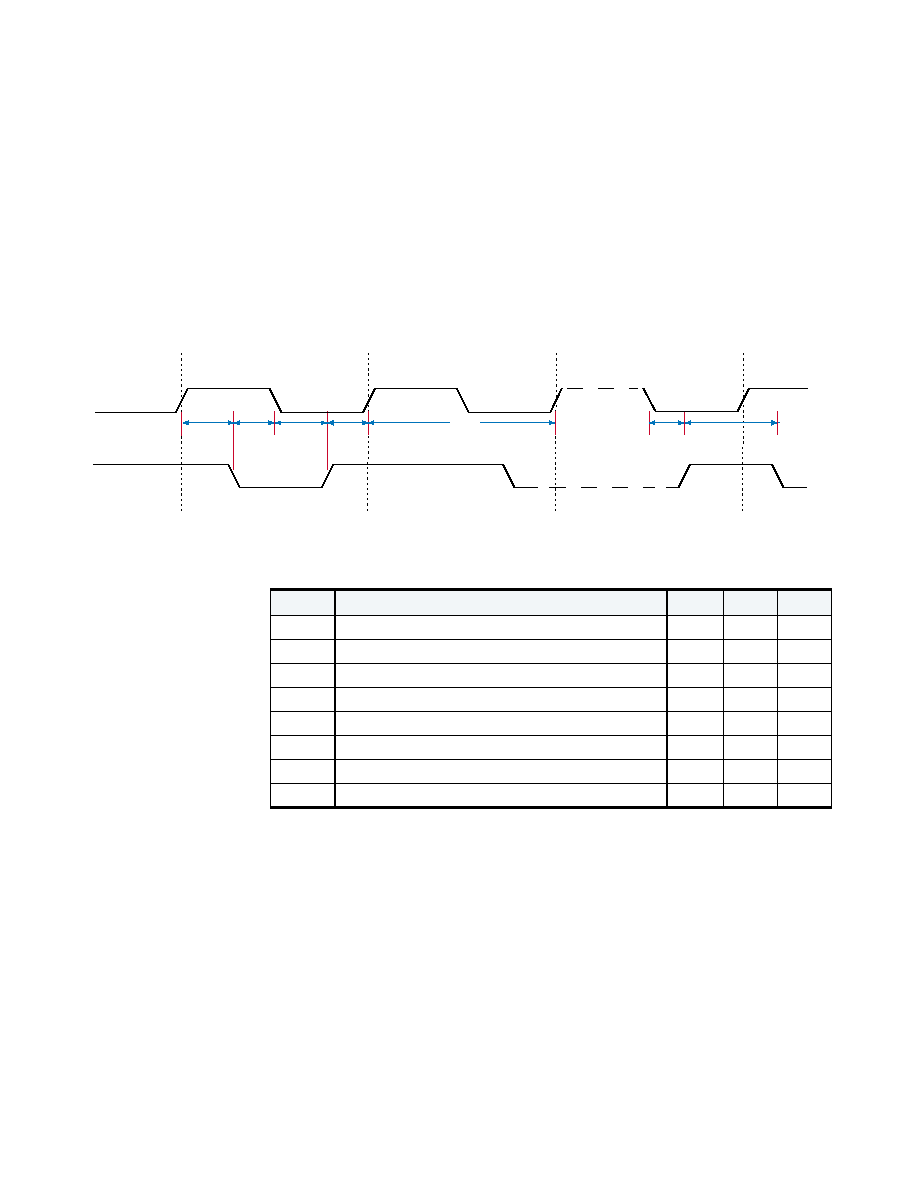

Table 6 Clock and Reference Signals

SIGNAL NAME

PIN #

TOTAL

TYPE

I/O

SIGNAL DESCRIPTION

SCLK*

SCLKX*

*

SCLK and SCLKX must not be AC-coupled.

G15

F15

1

1

LVPECL

LVPECL

I

I

Core Clock Rate (Differential)

CCLK0

G14

1

LVTTL

I

PD

1_544MHZ_CLK (T1)

The frequencies specified for CCLK0 - CCLK7 allow full flexibility for the C-5e NP. It is also possible to use one

or more CCLKn inputs for other frequencies. Contact your Motorola representative for more information.

CCLK1

F14

1

LVTTL

I

PD

2_048MHZ_CLK (E1)

CCLK2

E14

1

LVTTL

I

PD

34_368MHZ_CLK (E3)

CCLK3

G13

1

LVTTL

I

PD

44_736MHZ_CLK (T3)

CCLK4

F13

1

LVTTL

I

PD

50MHZ_CLK (100Mbit Ethernet)

CCLK5

E13

1

LVTTL

I

PD

106_25MHZ_CLK (Fibre Channel)

CCLK6

F12

1

LVTTL

I

PD

125MHZ_CLK (Gigabit Ethernet)

CCLK7

E12

1

LVTTL

I

PD

155_52MHZ_CLK (OC-3)

CPREF

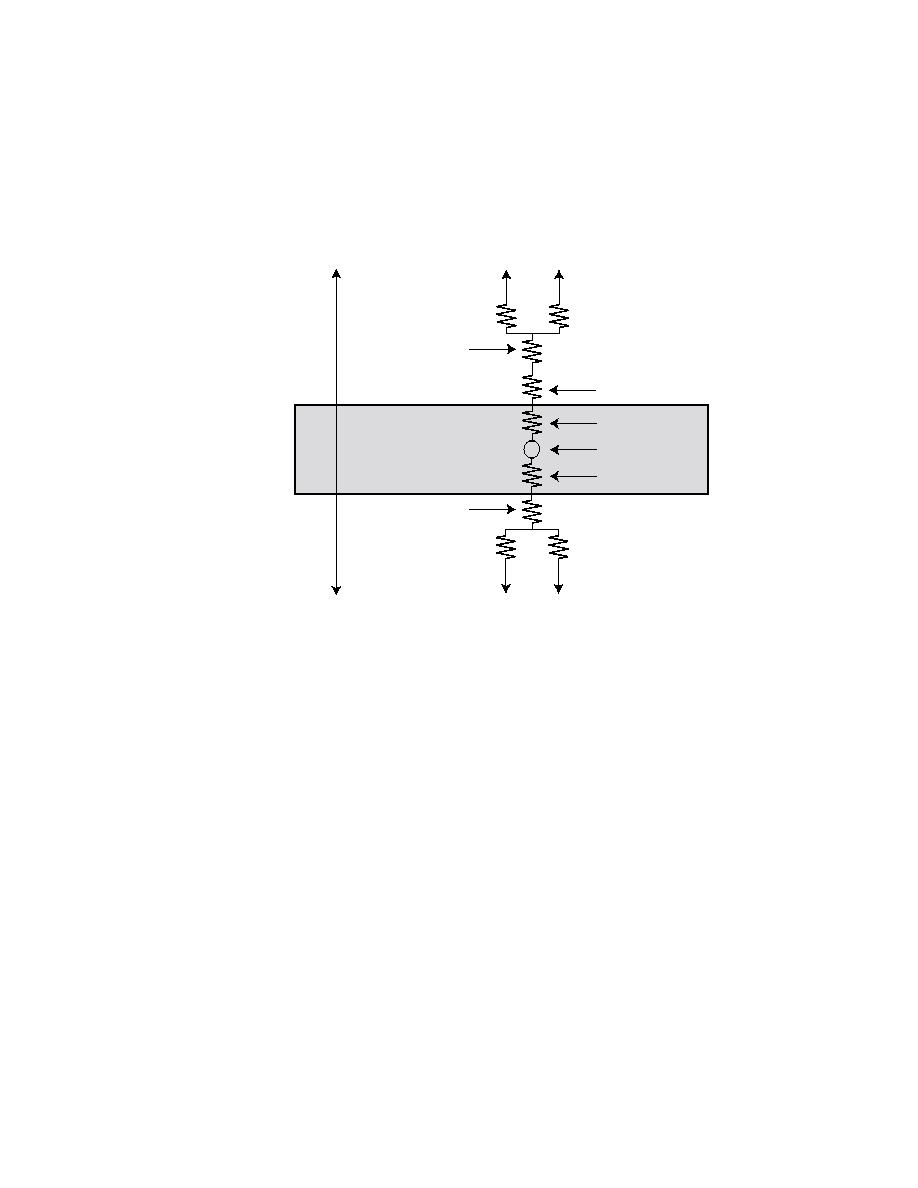

If any of the CPs are configured for LVPECL operation (OC3) using the pin mode registers, then CPREF must

be wired to an external reference, as specified in

Table 38

on page 75. If none of the CPs are configured for

LVPECL operation, then the CPREF pin can be left unconnected.

G12

1

LVPECL

I

PD

Reference

TOTAL

11

32

CHAPTER 2: SIGNAL DESCRIPTIONS

C5ENPA1-DS/D REV 03

MOTOROLA GENERAL BUSINESS INFORMATION

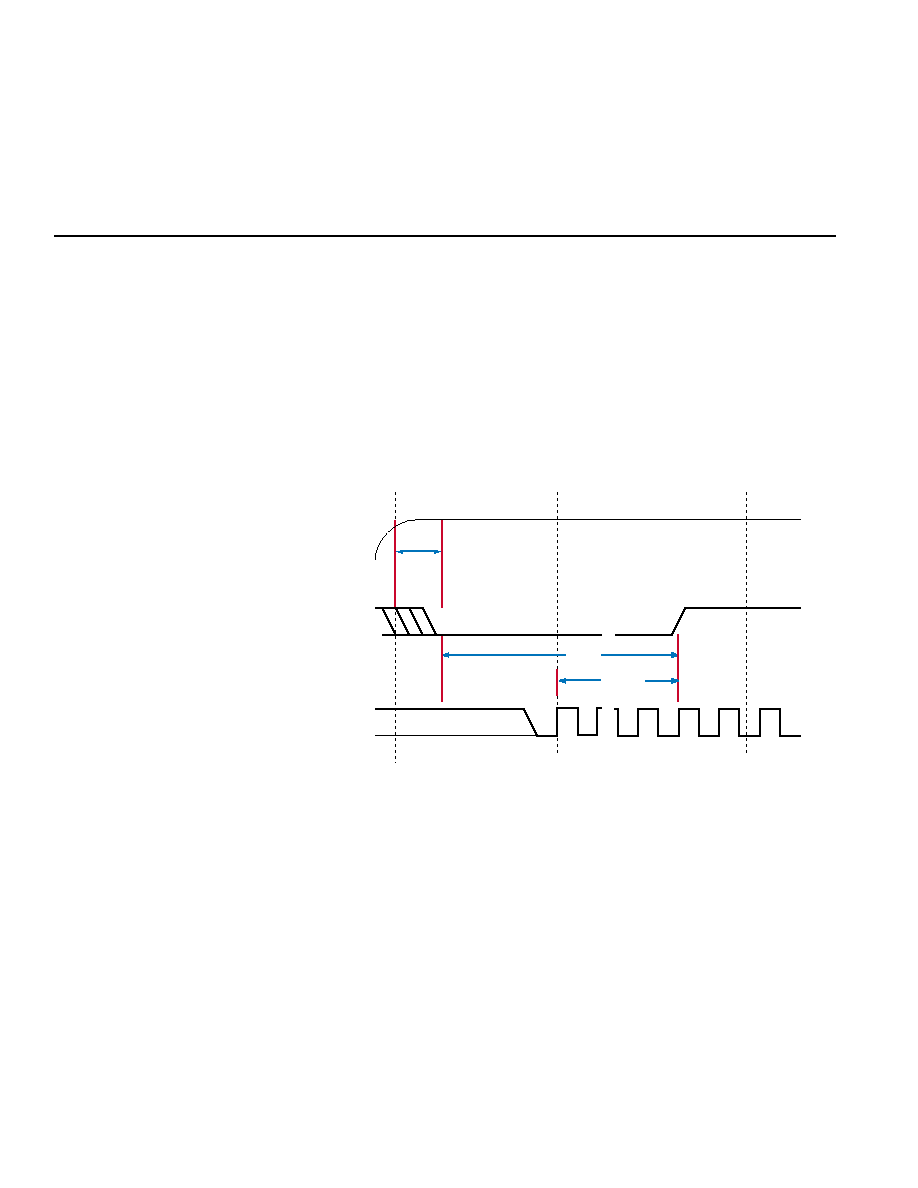

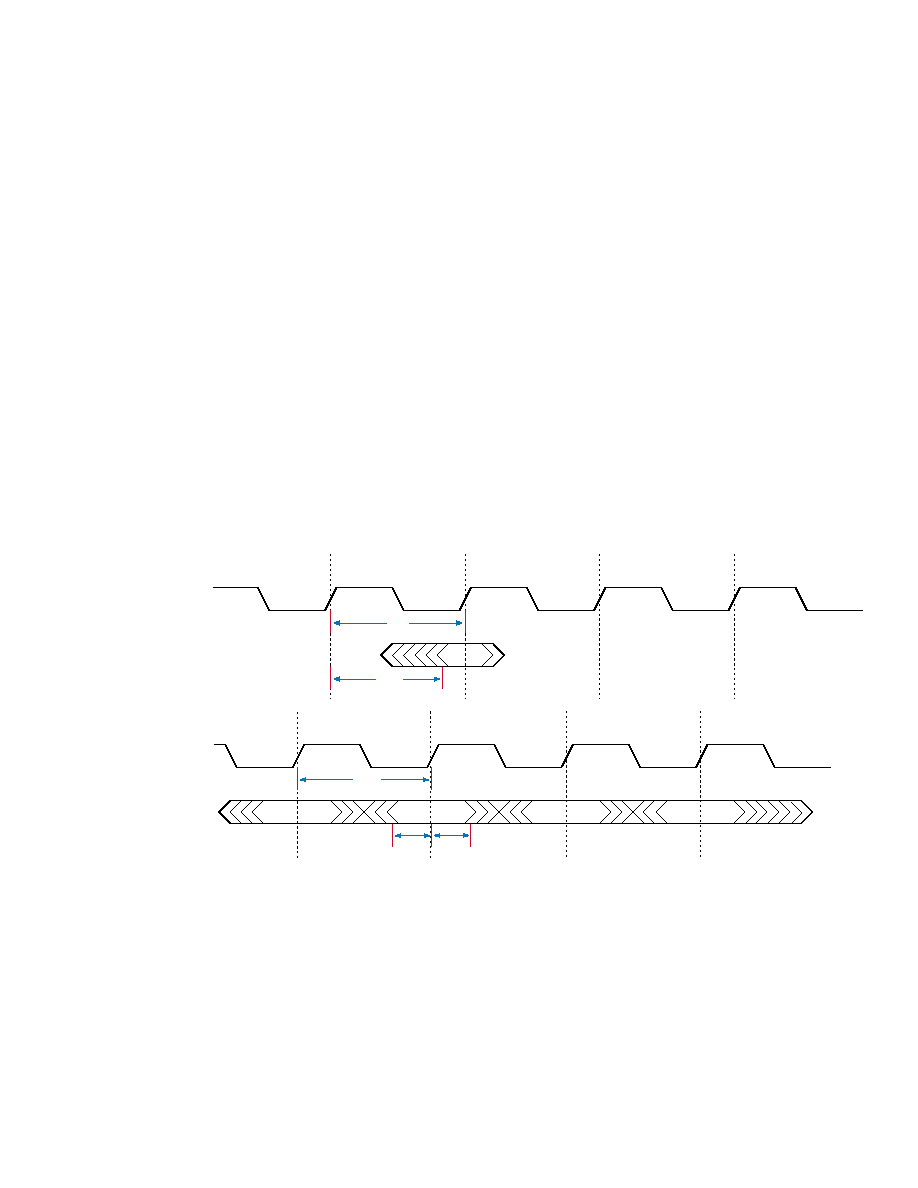

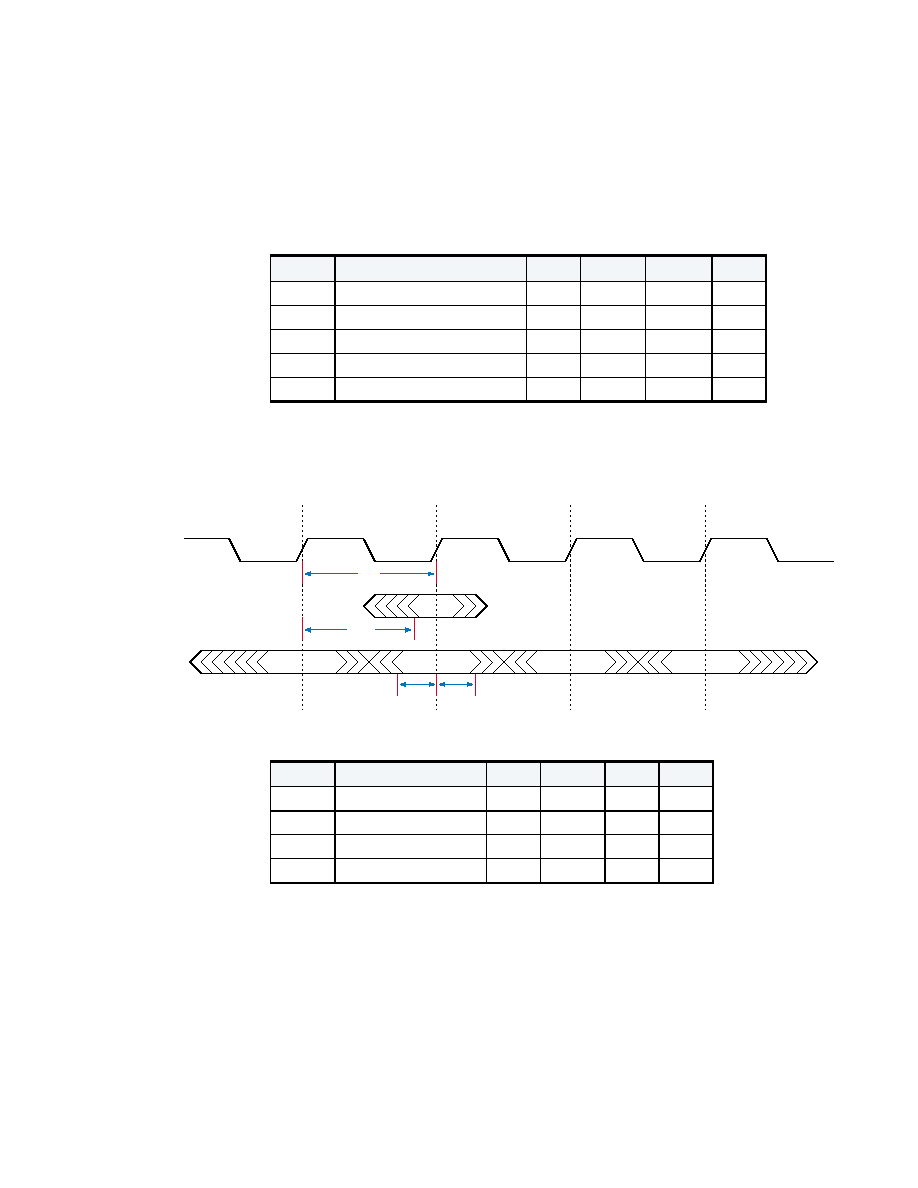

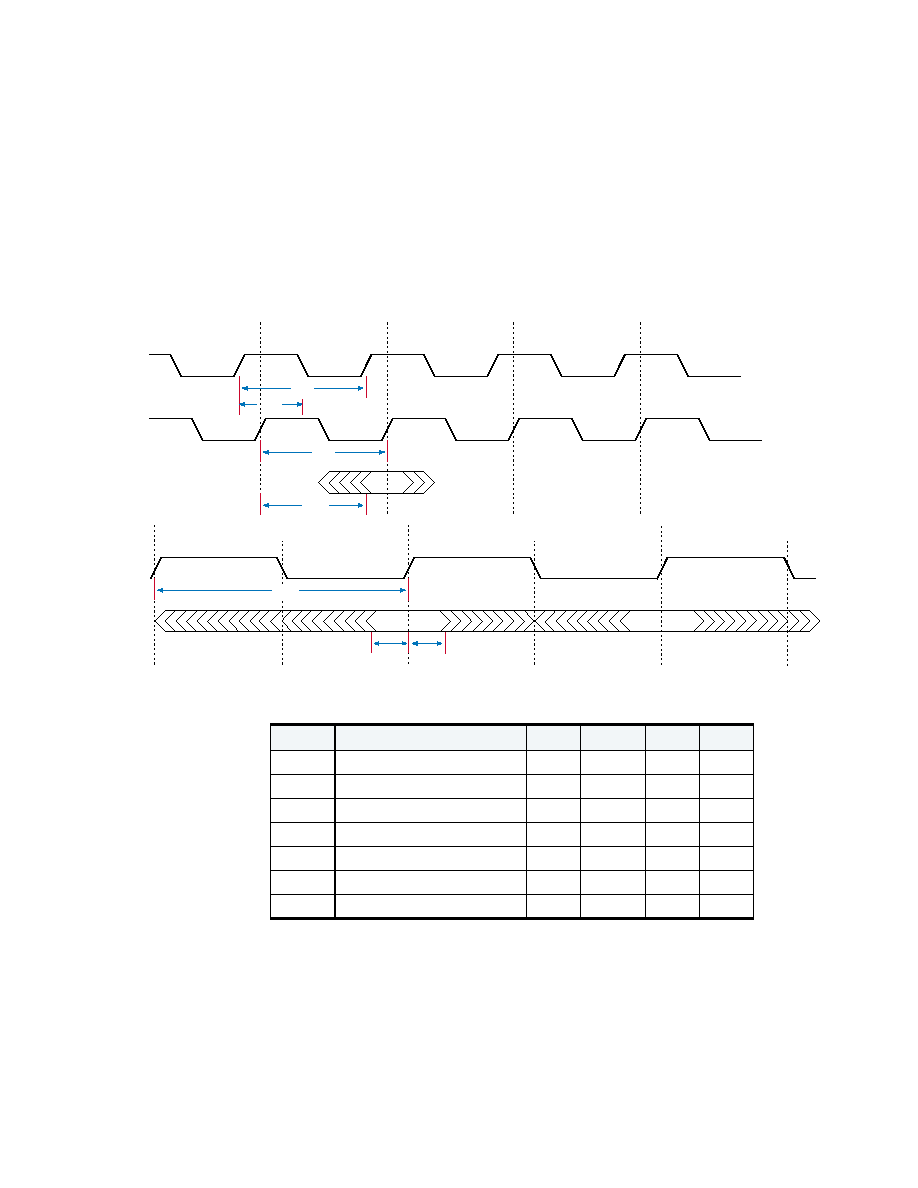

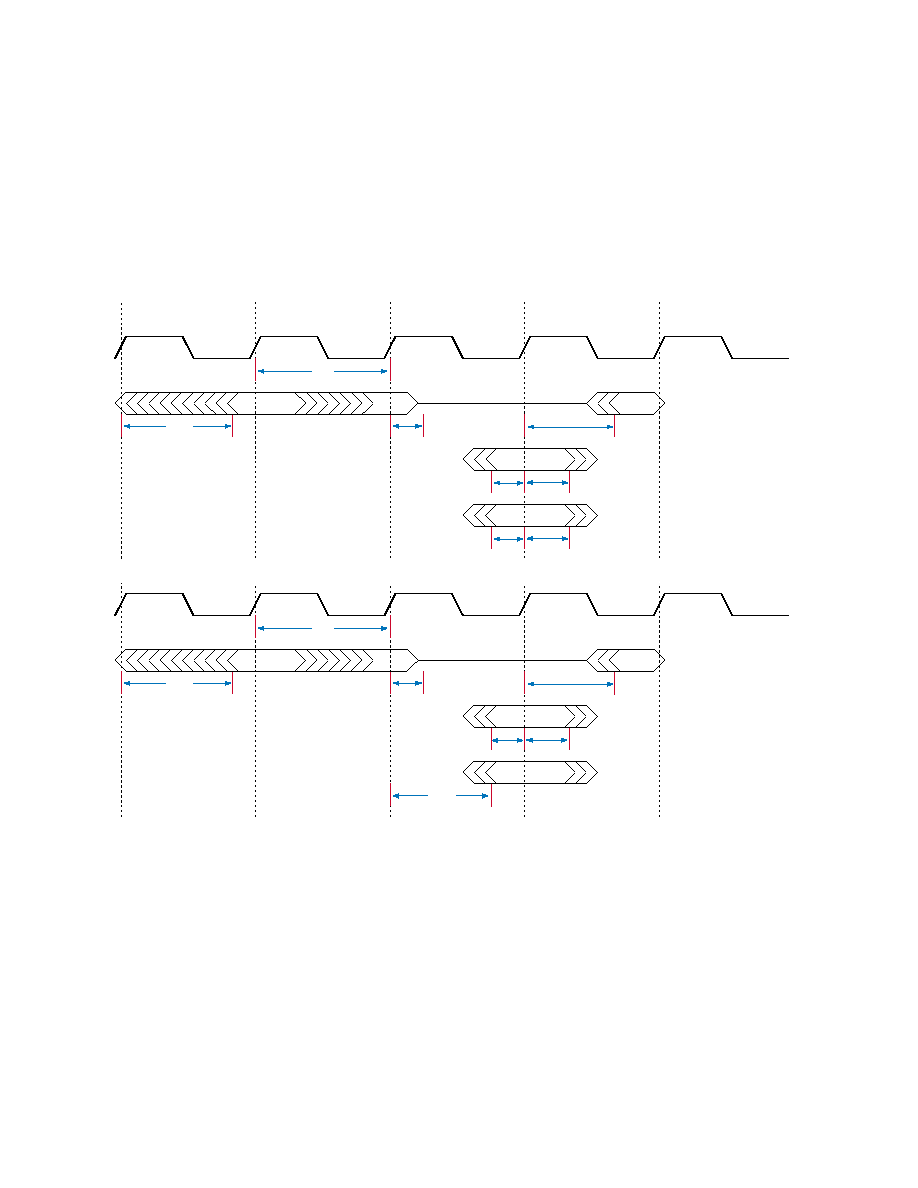

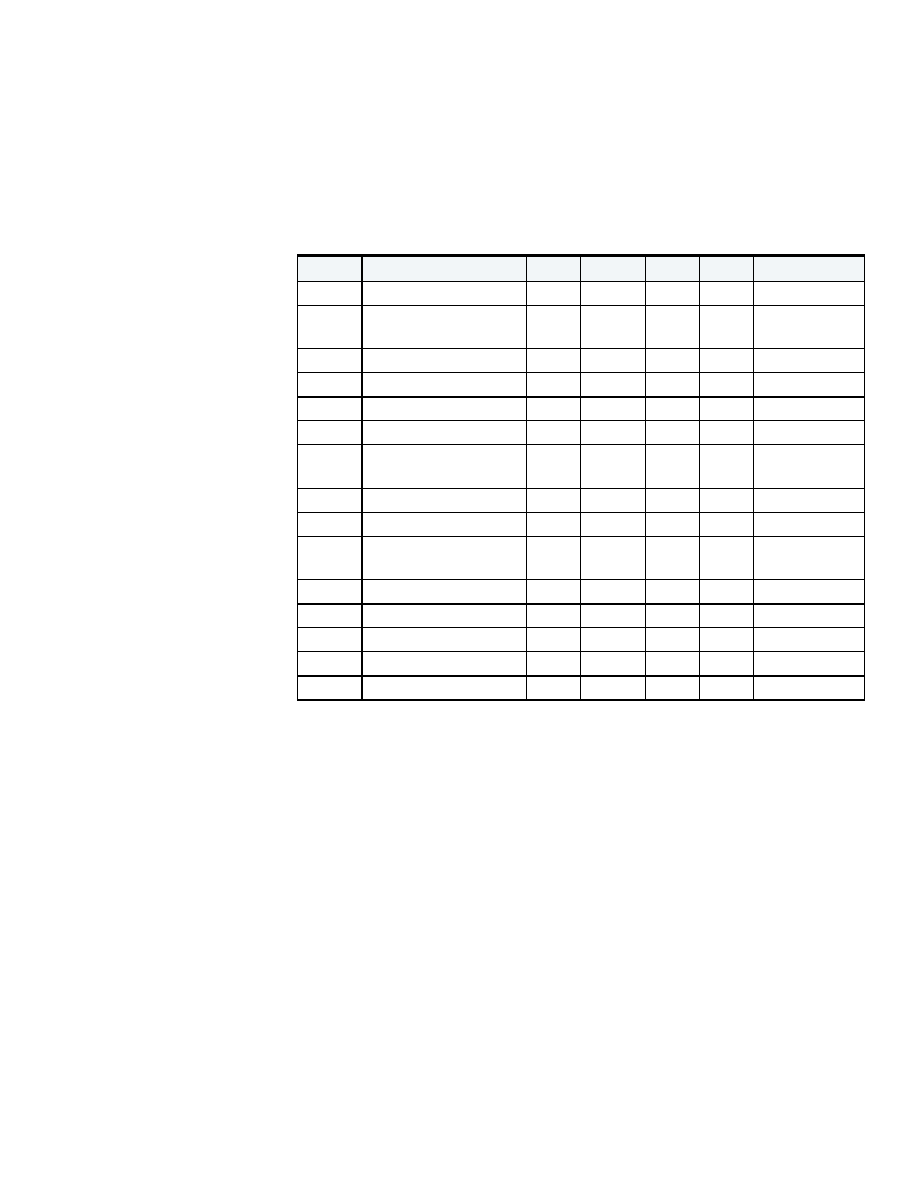

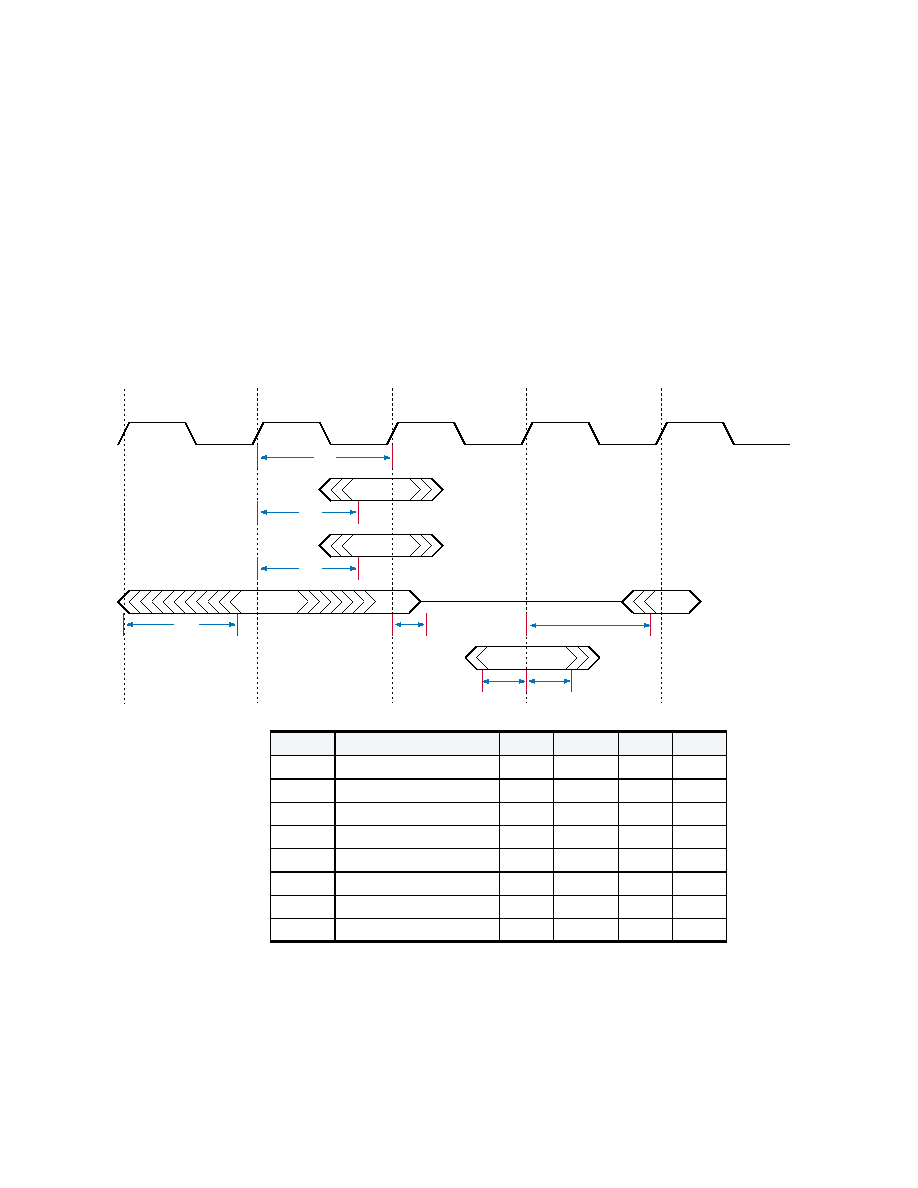

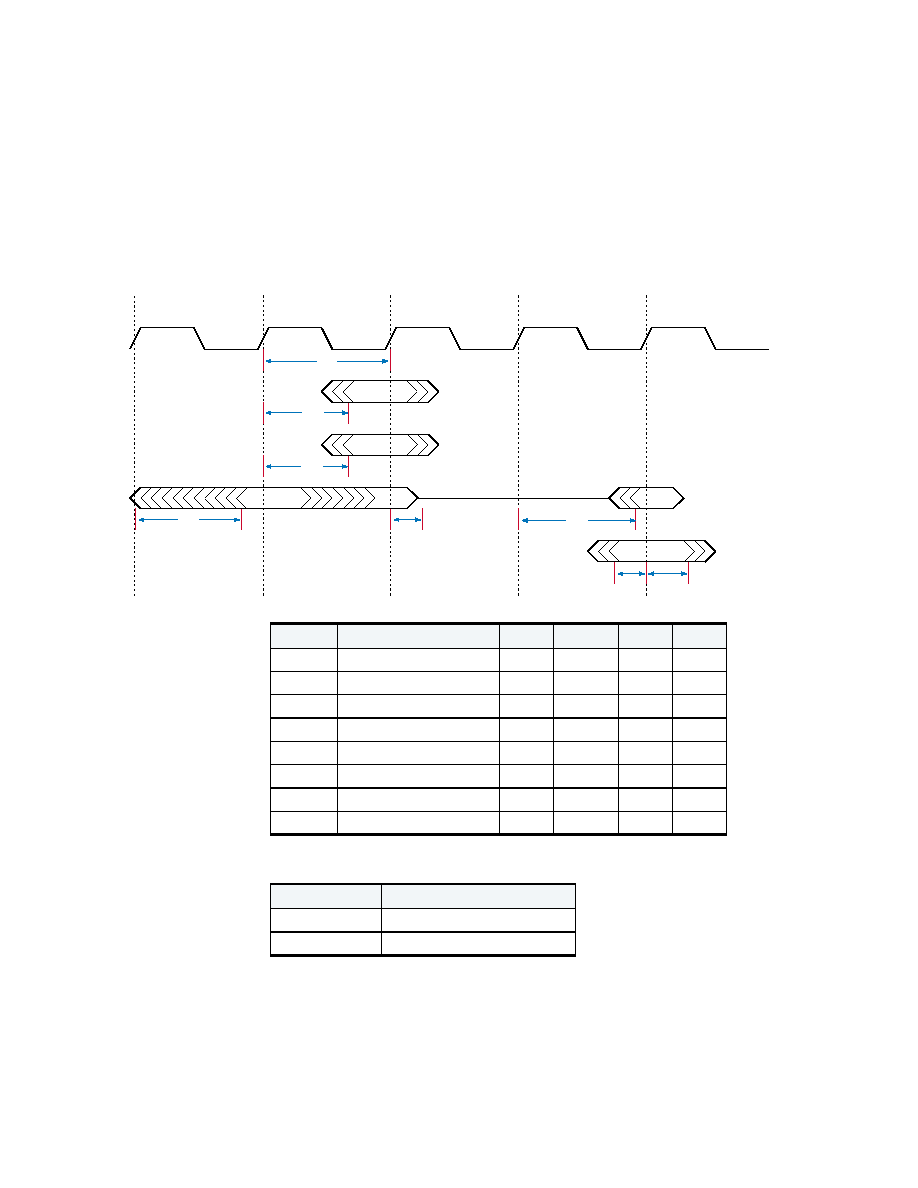

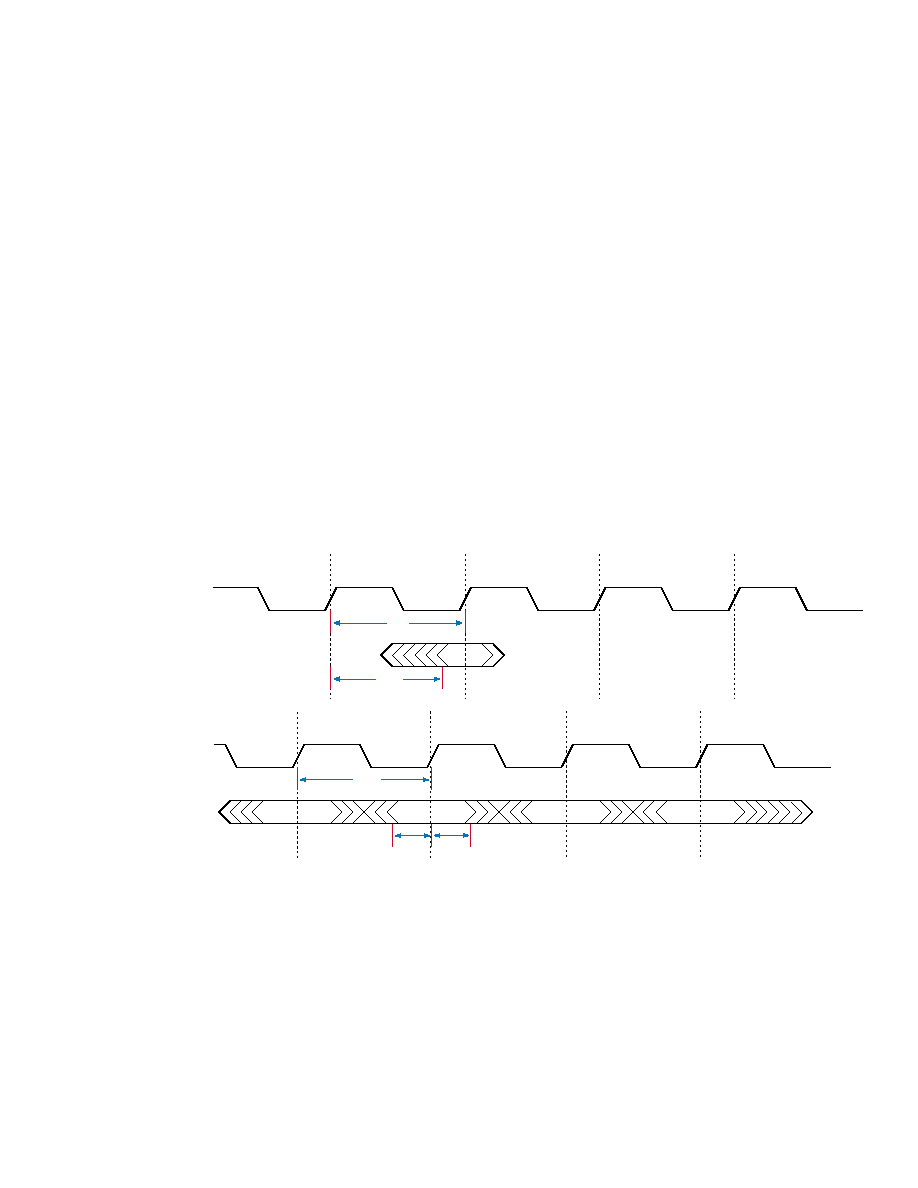

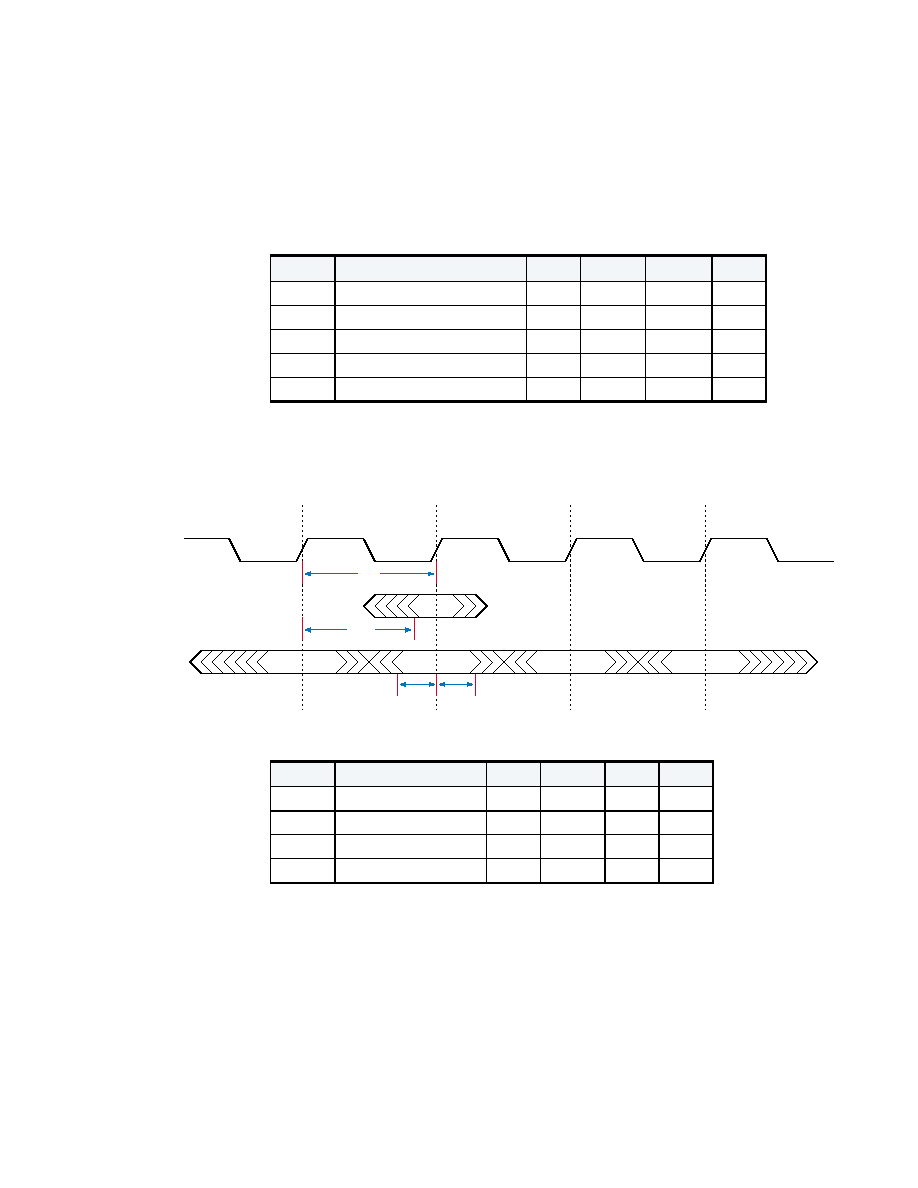

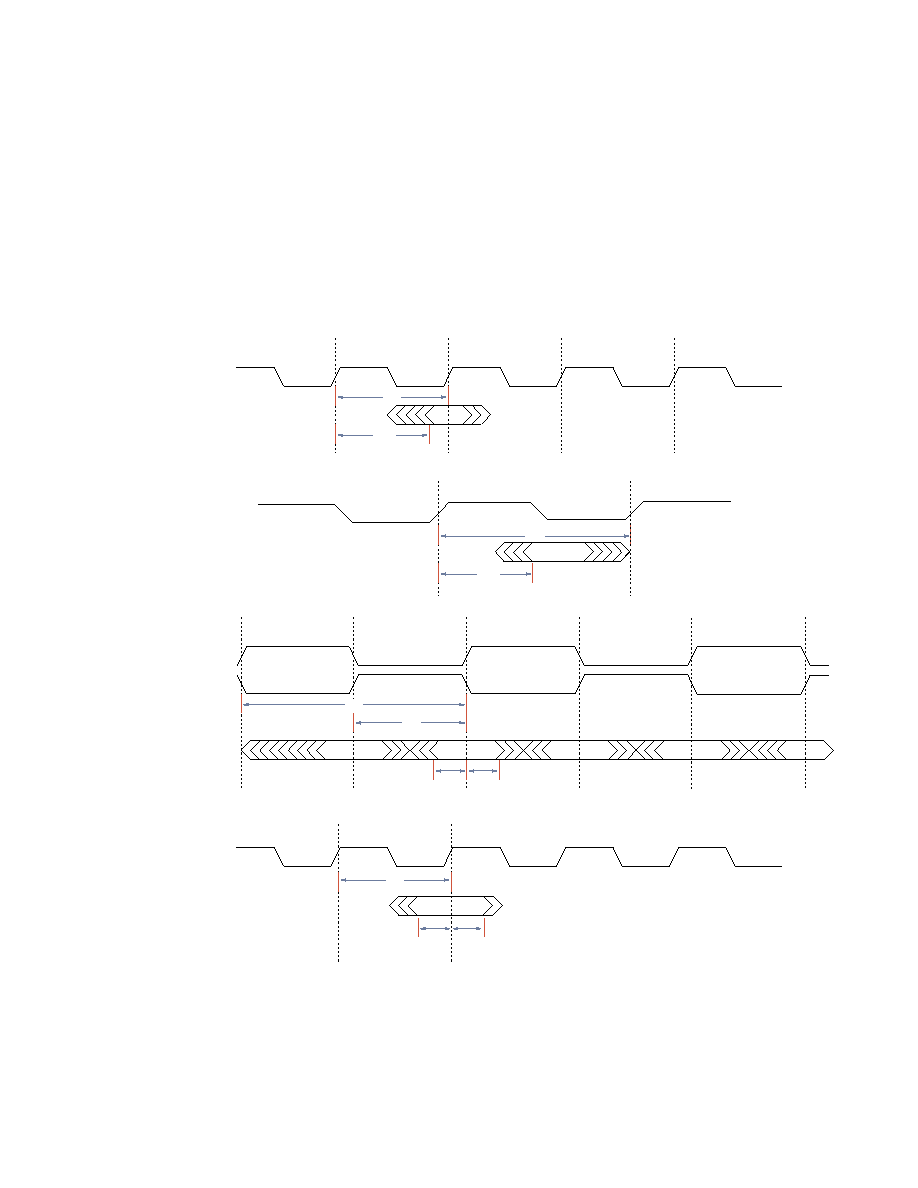

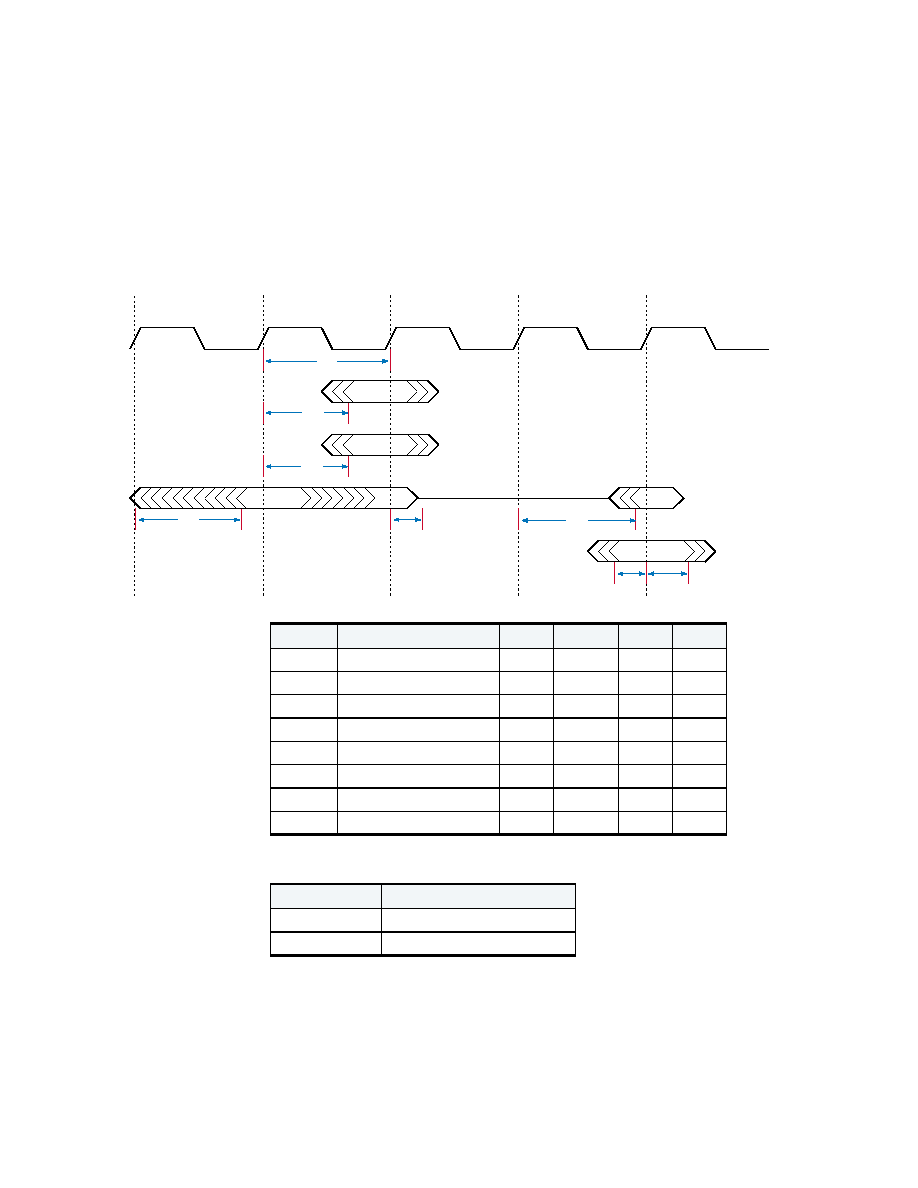

CP Interface Signals

The C-5e NP's 16 CPs support various network physical interfaces, providing a serial

interface to the PHY layer. Interfaces are configured via bits in the C-5e NP register set.

Many interfaces are possible by programming the configuration registers. CPs can be

used individually or in a cluster (four CPs) to implement the various interfaces.

Table 7

provides a quick reference of all the CP pins organized by clusters. There are seven

physical I/O pins associated with each CP. All pins are capable of receiving data, with some

configurable to be input clocks, output clocks, or data drivers. In addition, pairs of pins can

be configured as differential pairs for LVPECL compatibility.

In the case of RMII, OC-3, DS1, and DS3, the drivers and receivers at the pin are locally

configured to match the relevant PHY or Framer chip. OC-12 uses the aggregation of four

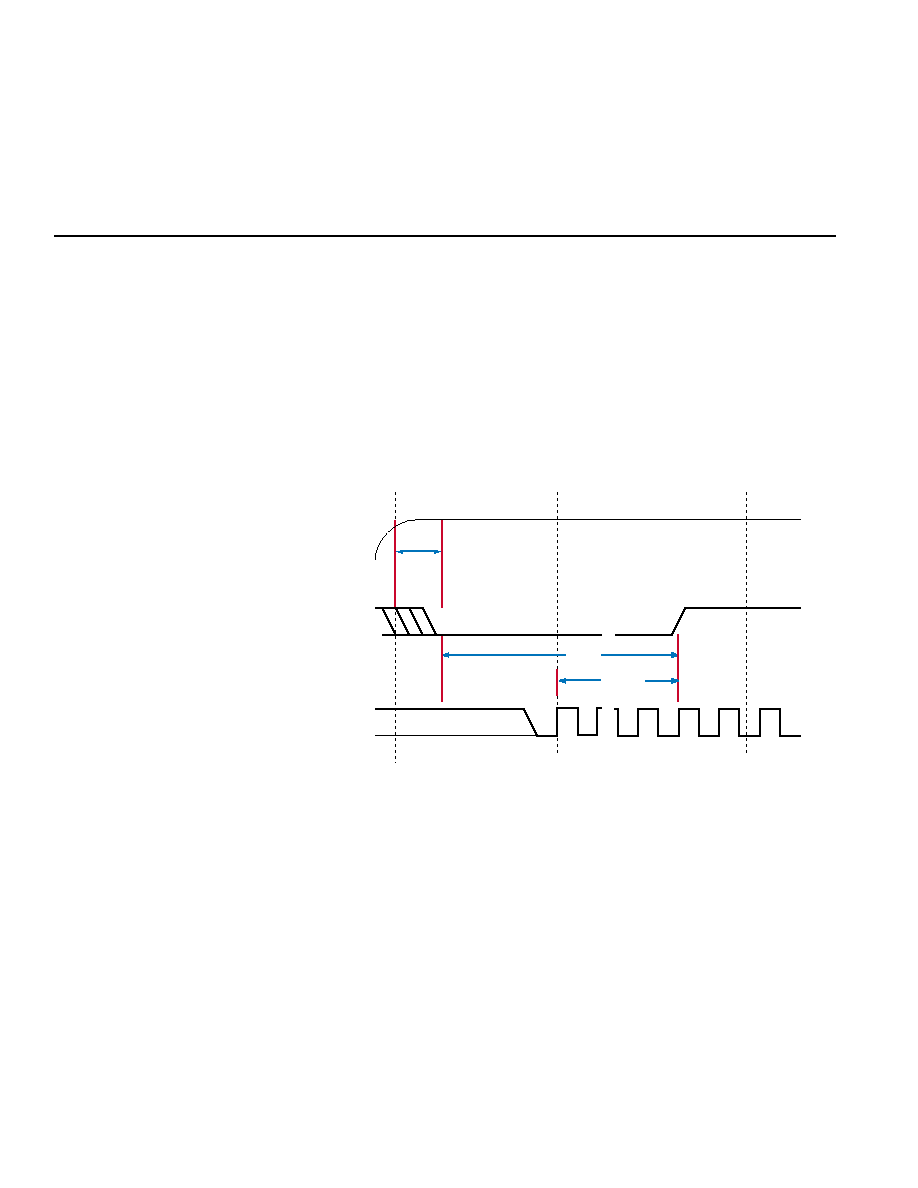

CPs (one cluster), while GMII and Ten Bit Interface (TBI) can use either eight CPs (four for

receive and four for transmit) or four CPs that share the transmit and receive functions for

non-wire speed applications.