Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or

design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein;

neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended,

or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to

support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where

personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized

application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless

against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of

personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was

negligent regarding the design or manufacture of the part.

DOCUMENT NUMBER

9S12DT128DGV2/D

1

MC9S12DT128

Device User Guide

V02.09

Covers also

MC9S12DT128E, MC9S12DG128E,

MC9S12DJ128E, MC9S12DG128,

MC9S12DJ128, MC9S12DB128

Original Release Date: 18 June 2001

Revised: 15 October 2003

Motorola, Inc

MC9S12DT128 Device User Guide -- V02.09

2

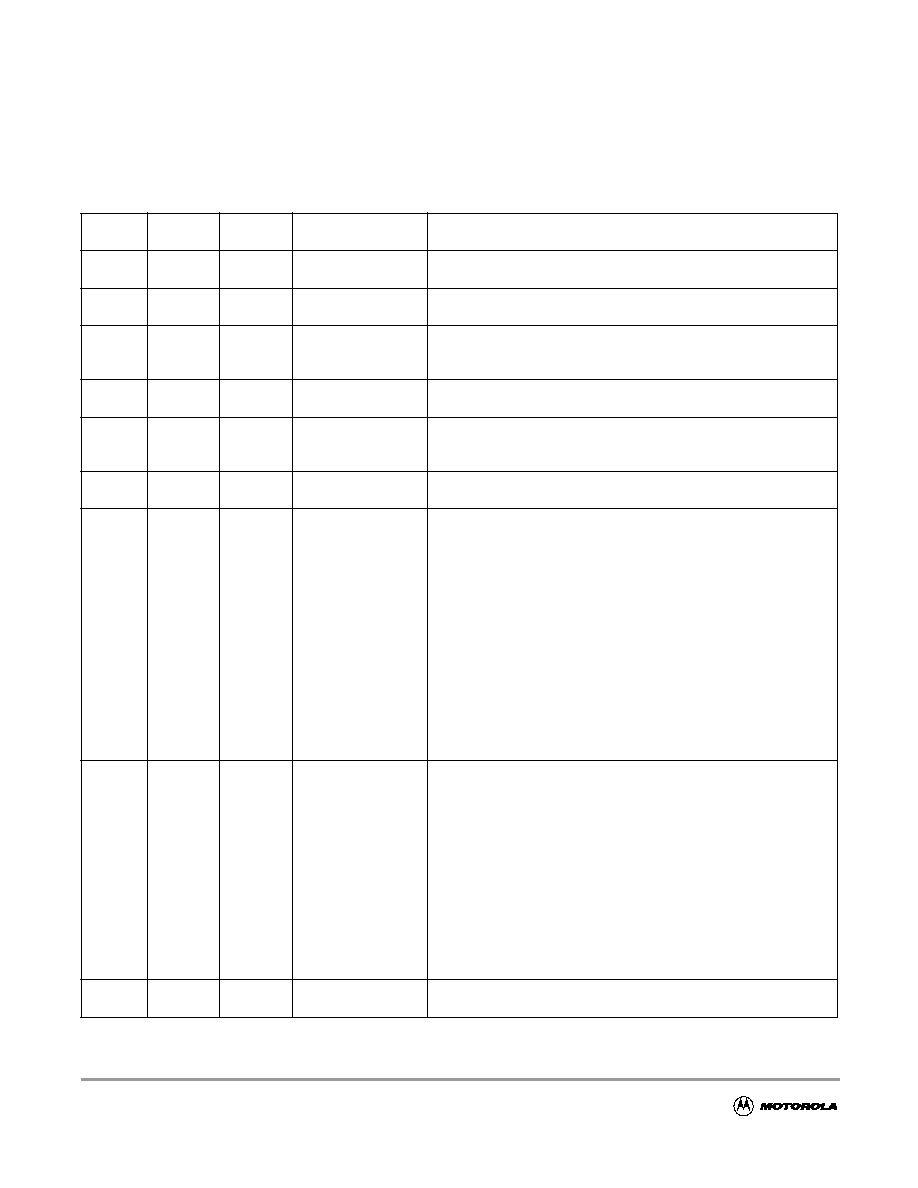

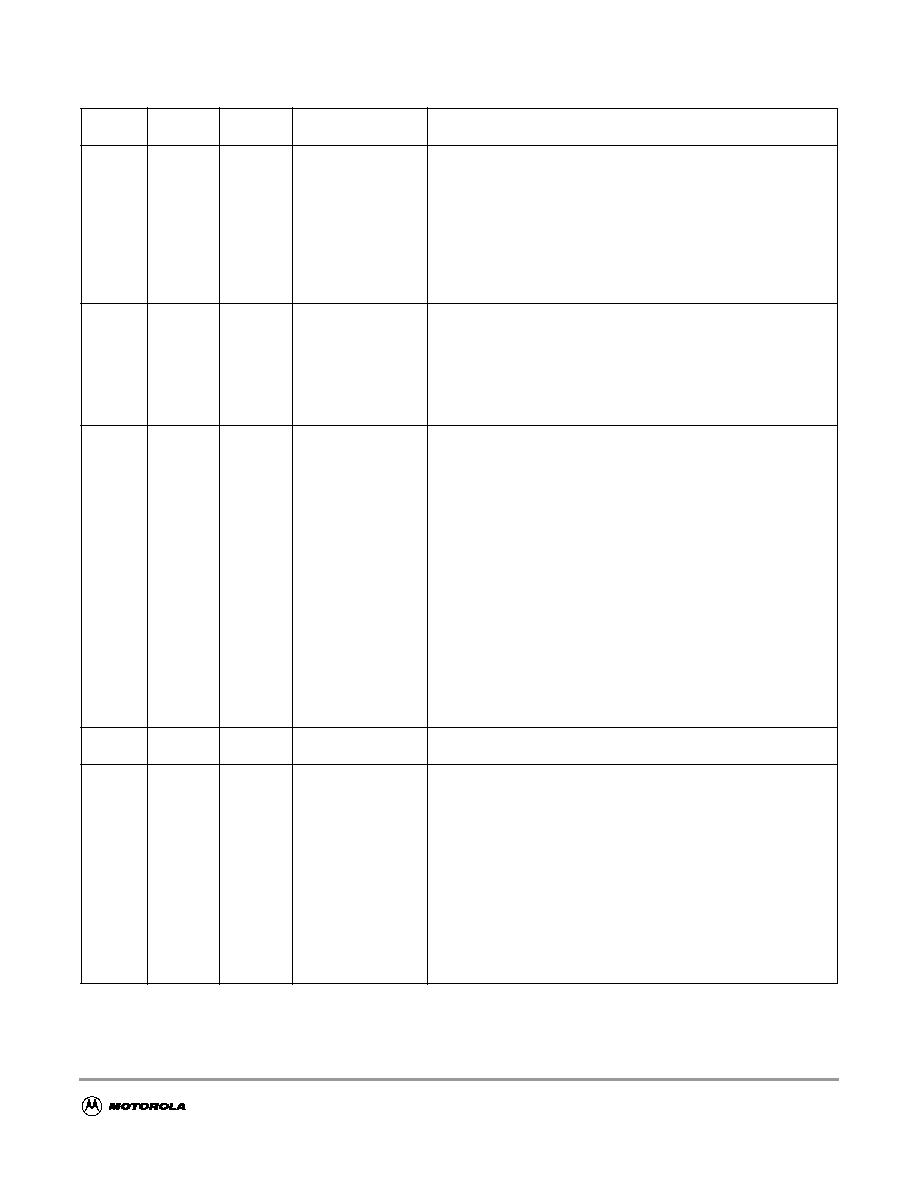

Revision History

Version

Number

Revision

Date

Effective

Date

Author

Description of Changes

V01.00

18 Jun

2001

18 June

2001

Initial version (parent doc v2.03 dug for dp256).

V01.01

23 July

2001

23 July

2001

Updated version after review

V01.02

23 Sep

2001

23 Sep

2001

Changed Partname, added pierce mode, updated electrical

characteristics

some minor corrections

V01.03

12 Oct

2001

12 Oct

2001

Replaced Star12 by HCS12

V01.04

27 Feb

2002

27 Feb

2002

Updated electrical spec after MC-Qualification (IOL/IOH), Data for

Pierce, NVM reliability

New document numbering. Corrected Typos

V01.05

4 Mar

2002

4 Mar

2002

Increased VDD to 2.35V, removed min. oscillator startup

Removed Document order number except from Cover Sheet

V01.06

8 July

2002

22 July

2002

Added:

Pull-up columns to signal table,

example for PLL Filter calculation,

Thermal values for junction to board and package,

BGND pin pull-up

Part Order Information

Global Register Table

Chip Configuration Summary

Modified:

Reduced Wait and Run IDD values

Mode of Operation chapter

changed leakage current for ADC inputs down to +-1uA

Corrected:

Interrupt vector table enable register inconsistencies

PCB layout for 80QFP VREGEN position

V02.00

11 Jan

2002

11 Jan

2002

NEW MASKSET

Changed part number from DTB128 to DT128

Functional Changes:

ROMCTL changes in Emulation Mode

80 Pin Byteflight package Option available

Flash with 2 Bit Backdoor Key Enable

Additional CAN0 routing to PJ7,6

Improved BDM with sync and acknowledge capabilities

New Part ID number

Improvements:

Significantly improved NVM reliability data

Corrections:

Interrupt vector Table

V02.01

01 Feb

2002

01 Feb

2002

Updated Block User Guide versions in preface

Updated Appendix A Electrical Characteristics

MC9S12DT128 Device User Guide -- V02.09

3

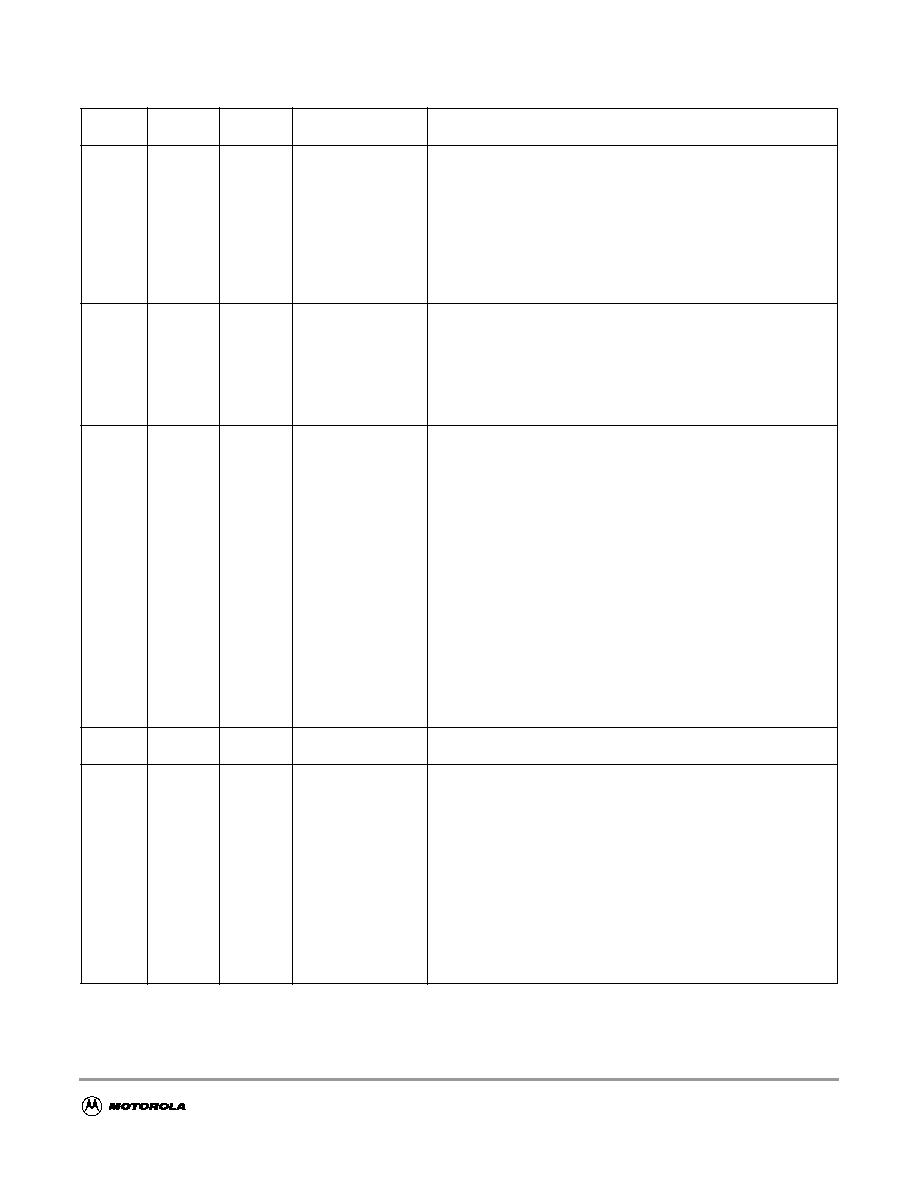

V02.02

08 Mar

2002

08 Mar

2002

Changed XCLKS to PE7 in Table 2-2

Updated device part numbers in Figure 2-1

Updated BDM clock in Figure 3-1

Removed SIM description in overview & n

UPOSC

spec in Table A-15

Updated electrical spec of VDD & VDDPLL (Table A-4), IOL/IOH

(Table A-6), C

INS

(Table A-9), C

IN

(Table A-6 & A-15),

Updated interrupt pulse timing variables in Table A-6

Updated device part numbers in Figure 2-1

Added document numbers on cover page and Table 0-2

V02.03

14 Mar

2002

14 Mar

2002

Cleaned up Fig. 1-1, 2-1

Updated Section 1.5 descriptions

Corrected PE assignment in Table 2-2, Fig. 2-5,6,7.

Corrected NVM sizes in Sections 16, 17

Added I

REF

spec for 1ATD in Table A-8

Added Blank Check in A.3.1.5 and Table A-11

Updated CRG spec in Table A-15

V02.04

16 Aug

2002

16 Aug

2002

Added:

Pull-up columns to signal table,

Example for PLL Filter calculation,

Thermal values for junction to board and package,

BGND pin pull-up

Part Order Information

Global Register Table

Chip Configuration Summary

Device specific info on CRG

Modified:

Reduced Wait and Run IDD values

Mode of Operation chapter

Changed leakage current for ADC inputs down to +-1uA

Minor modification of PLL frequency/ voltage gain values

Corrected:

Pin names/functions on 80 pin packages

Interrupt vector table enable register inconsistencies

PCB layout for 80QFP VREGEN position

V02.05

12 Sep

2002

12 Sep

2002

Corrected:

Register address mismatches in 1.5.1

V02.06

06 Nov

2002

06 Nov

2002

Removed document order no. from Revision History pages

Renamed "Preface" section to "Derivative Differences and

Document references". Added details for derivatives missing

CAN0/1/4, BDLC, IIC and/or Byteflight

Added 2L40K mask set in section 1.6

Added OSC User Guide in Preface, "Document References"

Added oscillator clock connection to BDM in S12_CORE in fig 3-1

Corrected several register and bit names in "Local Enable" column

of Table 5.1 Interrupt Vector Locations

Section HCS12 Core Block Description: mentioned alternate clock

of BDM to be equivalent to oscillator clock

Added new section: "Oscillator (OSC) Block Description"

Corrected in footnote of Table "PLL Characteristics": fOSC = 4MHz

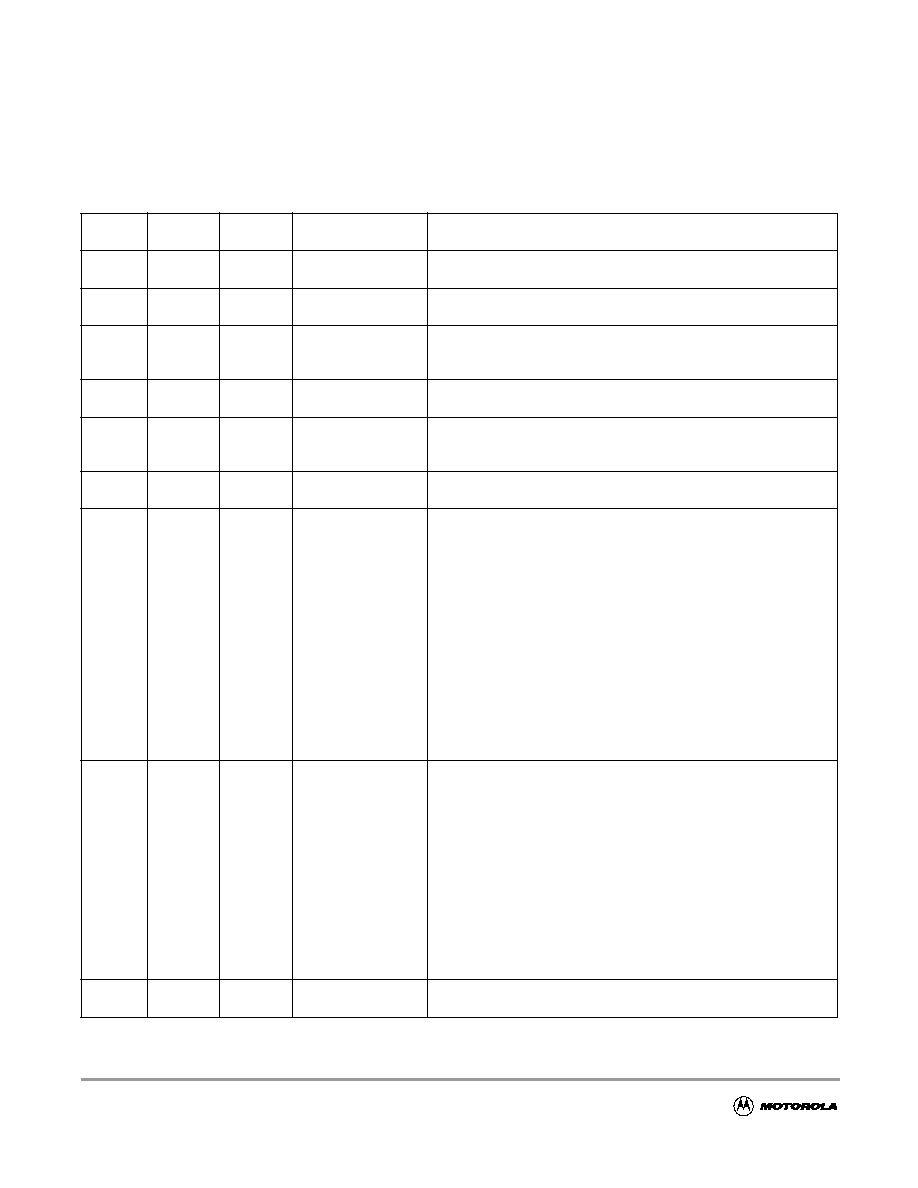

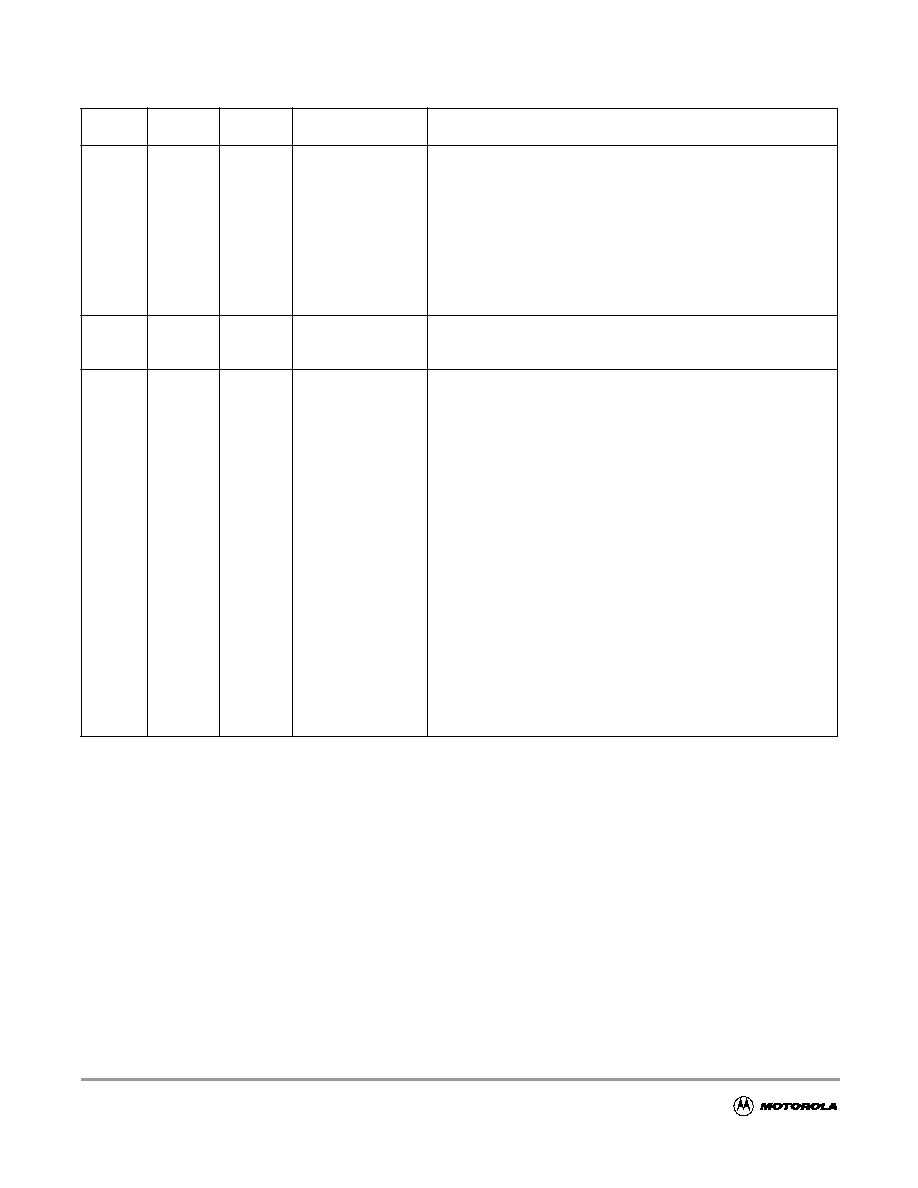

Version

Number

Revision

Date

Effective

Date

Author

Description of Changes

MC9S12DT128 Device User Guide -- V02.09

4

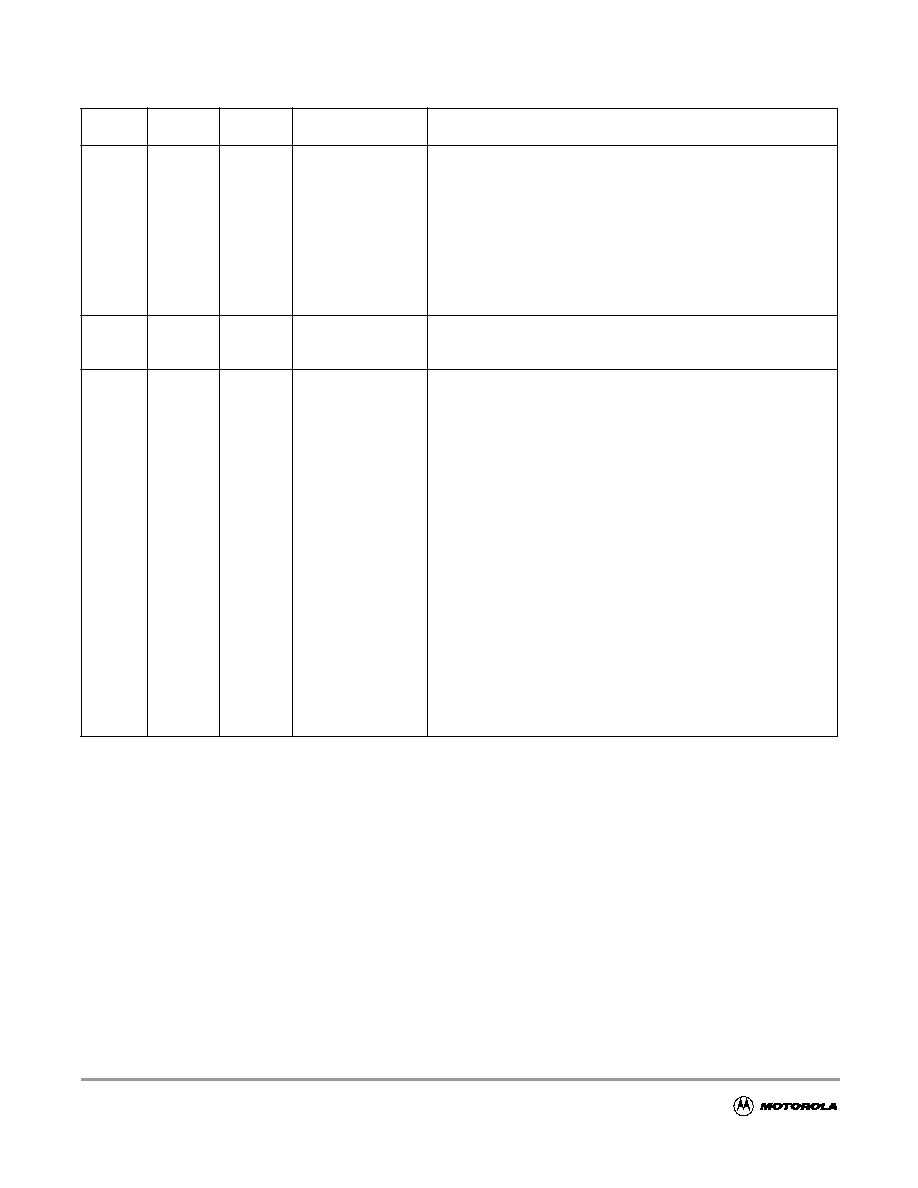

V02.07

29 Jan

2003

29 Jan

2003

Added 3L40K mask set in section 1.6

Corrected register entries in section 1.5.1 "Detailed Memory Map"

Updated description for ROMCTL in section 2.3.31

Updated section 4.3.3 "Unsecuring the Microcontroller"

Corrected and updated device-specific information for OSC

(section 8.1) & Byteflight (section 15.1)

Updated footnote in Table A-4 "Operating Conditions"

Changed reference of VDDM to VDDR in section A.1.8

Removed footnote on input leakage current in Table A-6 "5V I/O

Characteristics"

V02.08

26 Feb

2003

26 Feb

2003

Added part numbers MC9S12DT128E, MC9S12DG128E, and

MC9S12DJ128E in "Preface" and related part number references

Removed mask sets 0L40K and 2L40K from Table 1-3

V02.09

15 Oct

2003

15 Oct

2003

Replaced references to HCS12 Core Guide by the individual

HCS12 Block guides in Table 0-2, section 1.5.1, and section 6;

updated Fig.3-1 "Clock Connections" to show the individual HCS12

blocks

Corrected PIM module name and document order number in Table

0-2 "Document References"

Corrected ECT pulse accumulators description in section 1.2

"Features"

Corrected KWP5 pin name in Fig 2-1 112LQFP pin assignments

Corrected pull resistor CTRL/reset states for PE7 and PE4-PE0 in

Table 2.1 "Signal Properties"

Mentioned "S12LRAE" bootloader in Flash section 17

Corrected footnote on clamp of TEST pin under Table A-1

"Absolute Maximum Ratings"

Corrected minimum bus frequency to 0.25MHz in Table A-4

"Operating Conditions"

Replaced "burst programming" by "row programming" in A.3 "NVM,

Flash and EEPROM"

Corrected blank check time for EEPROM in Table A-11 "NVM

Timing Characteristics"

Corrected operating frequency in Table A-18 "SPI Master/Slave

Mode Timing Characteristics

Version

Number

Revision

Date

Effective

Date

Author

Description of Changes