| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: SN54LS181 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

5-332

FAST AND LS TTL DATA

4-BIT ARITHMETIC

LOGIC UNIT

The SN54 / 74LS181 is a 4-bit Arithmetic Logic Unit (ALU) which can

perform all the possible 16 logic, operations on two variables and a variety of

arithmetic operations.

∑

Provides 16 Arithmetic Operations Add, Subtract, Compare, Double,

Plus Twelve Other Arithmetic Operations

∑

Provides all 16 Logic Operations of Two Variables Exclusive -- OR,

Compare, AND, NAND, OR, NOR, Plus Ten other Logic Operations

∑

Full Lookahead for High Speed Arithmetic Operation on Long Words

∑

Input Clamp Diodes

NOTE:

The Flatpak version

has the same pinouts

(Connection Diagram) as

the Dual In-Line Package.

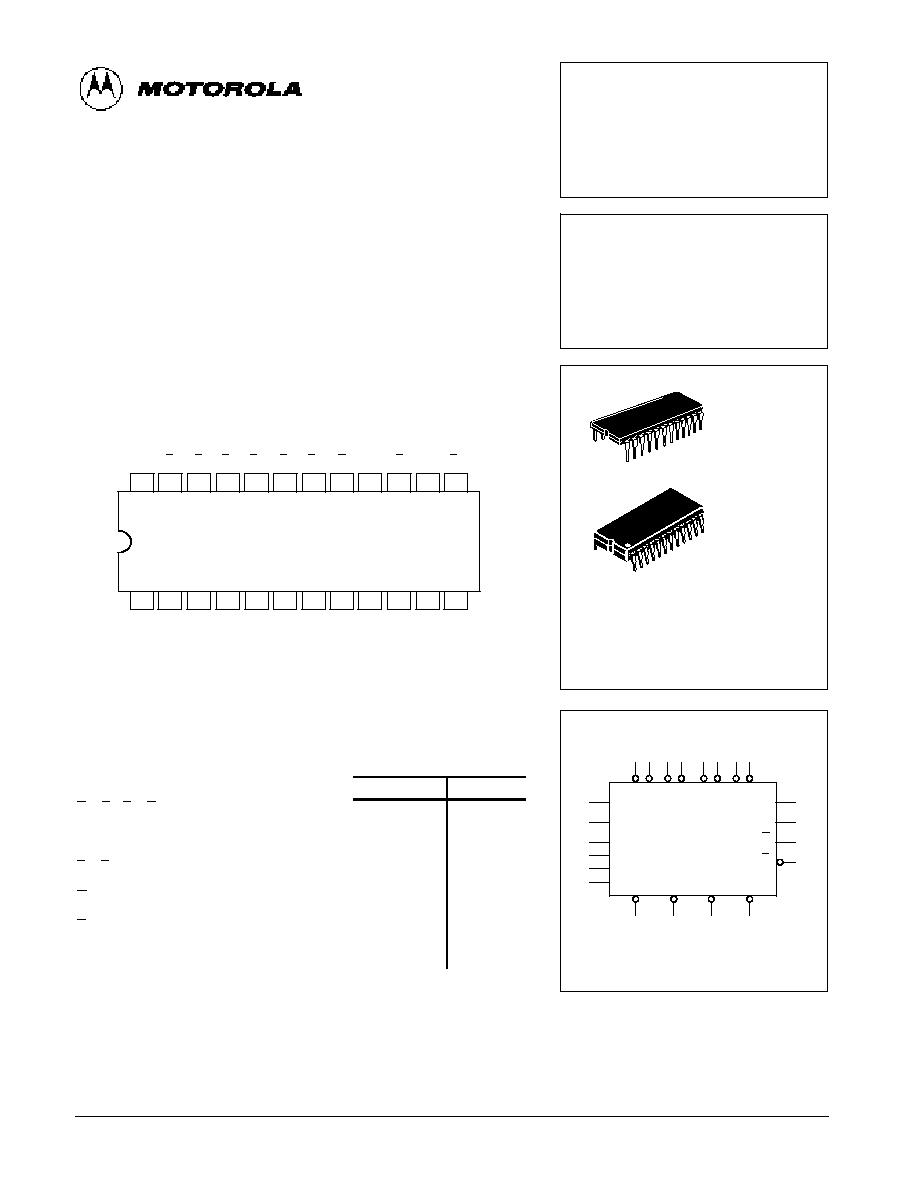

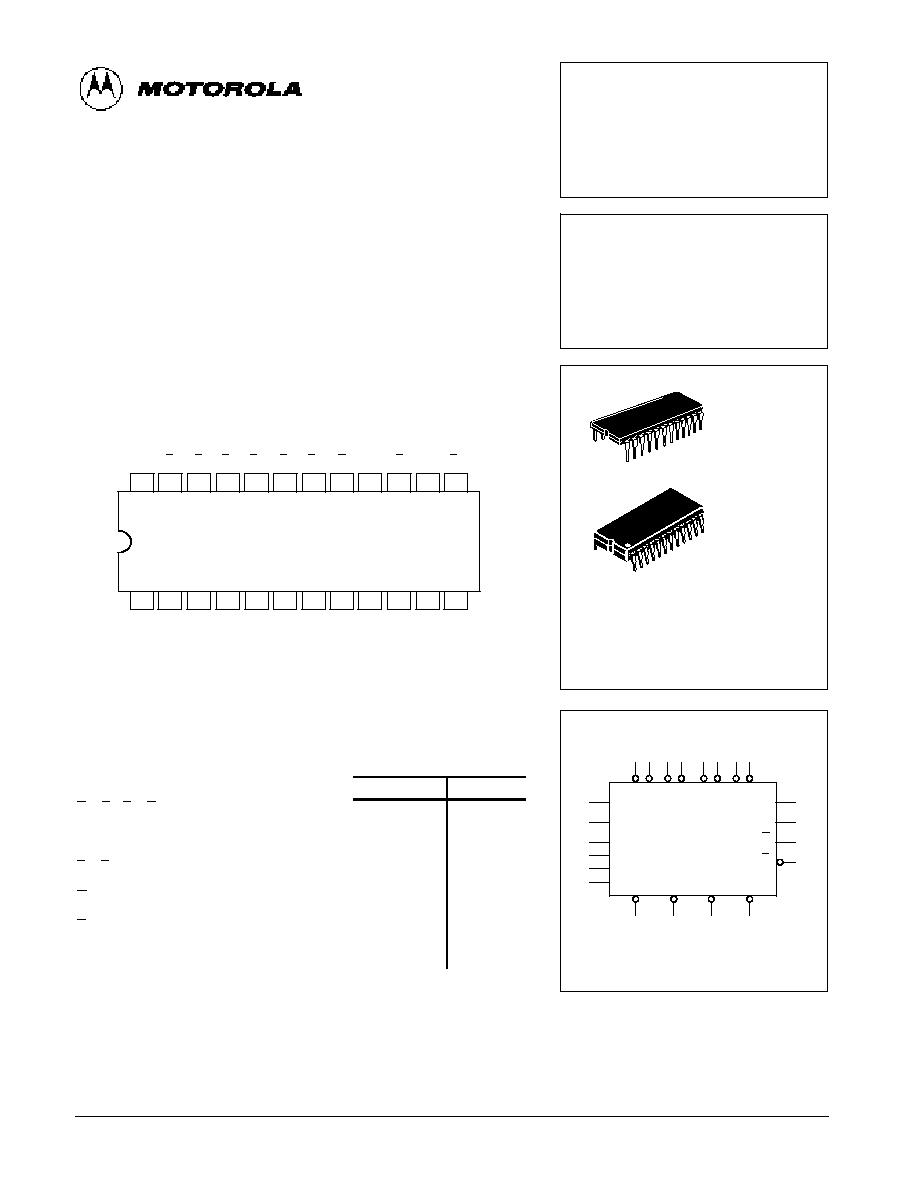

CONNECTION DIAGRAM DIP (TOP VIEW)

22

21

20

19

18

17

1

2

3

4

5

6

7

24

23

8

VCC

B0

A1 B1 A2 B2

B3

A3

G

A0 S3 S2 S1 S0 Cn M

9

10

11

12

F0 F1 F2 GND

16

15

14

13

Cn+4

A=B

P

F3

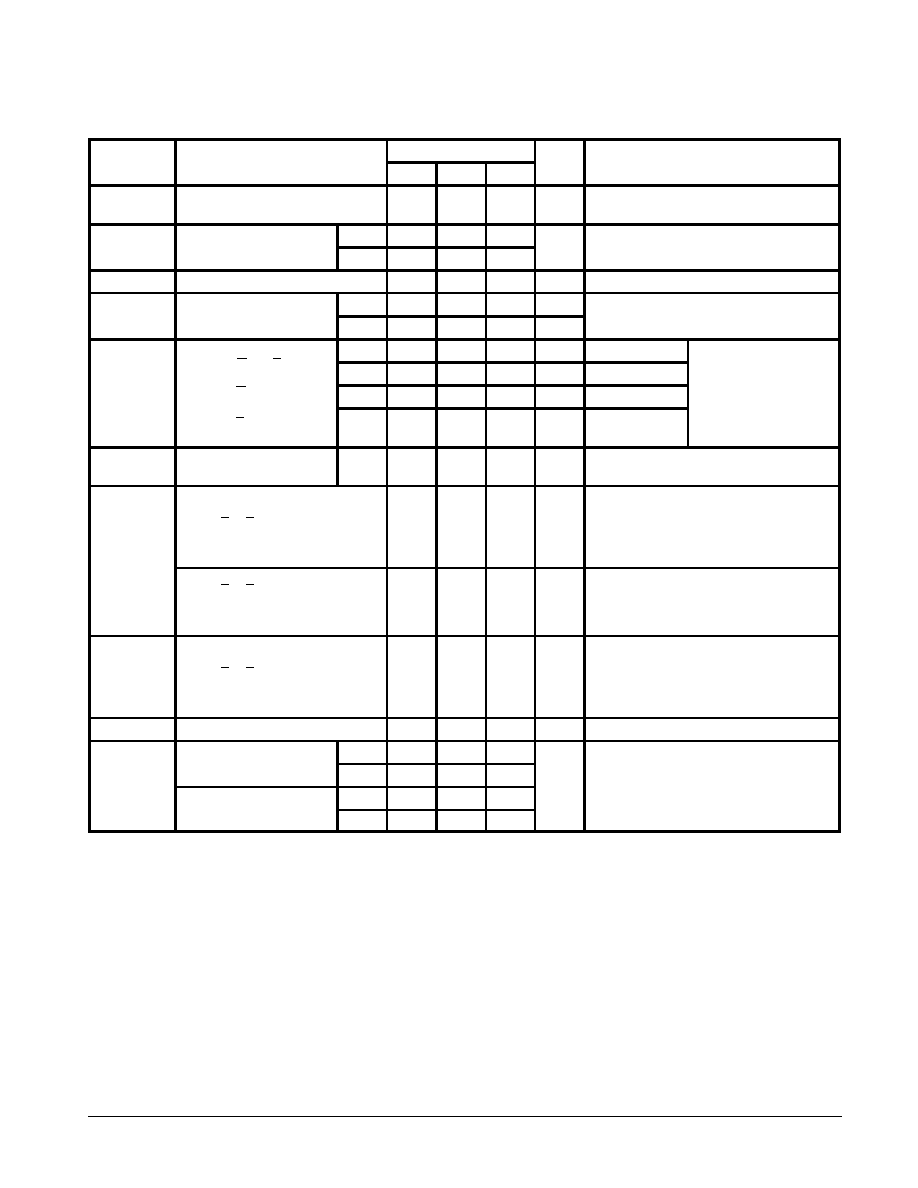

PIN NAMES

LOADING (Note a)

HIGH

LOW

A0 ≠ A3, B0 ≠ B3

S0 ≠ S3

M

Cn

F0 ≠ F3

A = B

G

P

Cn+4

Operand (Active LOW) Inputs

Function -- Select Inputs

Mode Control Input

Carry Input

Function (Active LOW) Outputs

Comparator Output

Carry Generator (Active LOW)

Output

Carry Propagate (Active LOW)

Output

Carry Output

1.5 U.L.

2.0 U.L.

0.5 U.L.

2.5 U.L.

10 U.L.

Open Collector

10 U.L.

10 U.L.

10 U.L.

0.75 U.L.

1.0 U.L.

0.25 U.L.

1.25 U.L.

5 (2.5) U.L.

5 (2.5) U.L.

10 U.L.

5 U.L.

5 (2.5) U.L.

NOTES:

a. 1 TTL Unit Load (U.L.) = 40

µ

A HIGH/1.6 mA LOW.

b. The Output LOW drive factor is 2.5 U.L. for Military (54) and 5 U.L. for Commercial (74)

b.

Temperature Ranges.

SN54/74LS181

4-BIT ARITHMETIC

LOGIC UNIT

LOW POWER SCHOTTKY

ORDERING INFORMATION

SN54LSXXXJ

Ceramic

SN74LSXXXN

Plastic

LOGIC SYMBOL

VCC = PIN 24

GND = PIN 12

7

8

6

5

4

3

9

10

11

13

15

17

14

16

2 1 23 22 21 20 19 18

Cn

M

S0

S1

S2

S3

A0B0 A1 B1 A2 B2 A3 B3

F0

F1

F2

F3

Cn+4

A = B

G

P

24

1

J SUFFIX

CERAMIC

CASE 623-05

24

1

N SUFFIX

PLASTIC

CASE 649-03

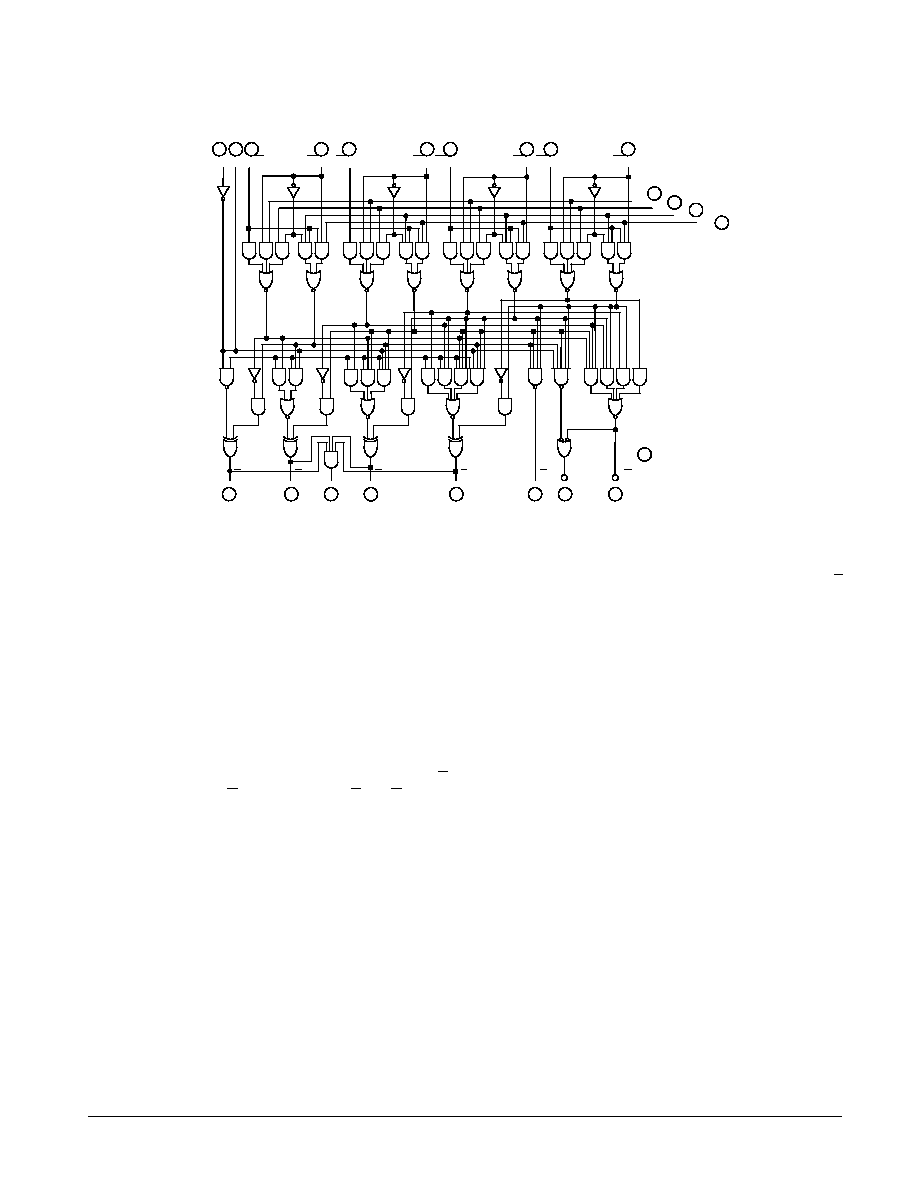

5-333

FAST AND LS TTL DATA

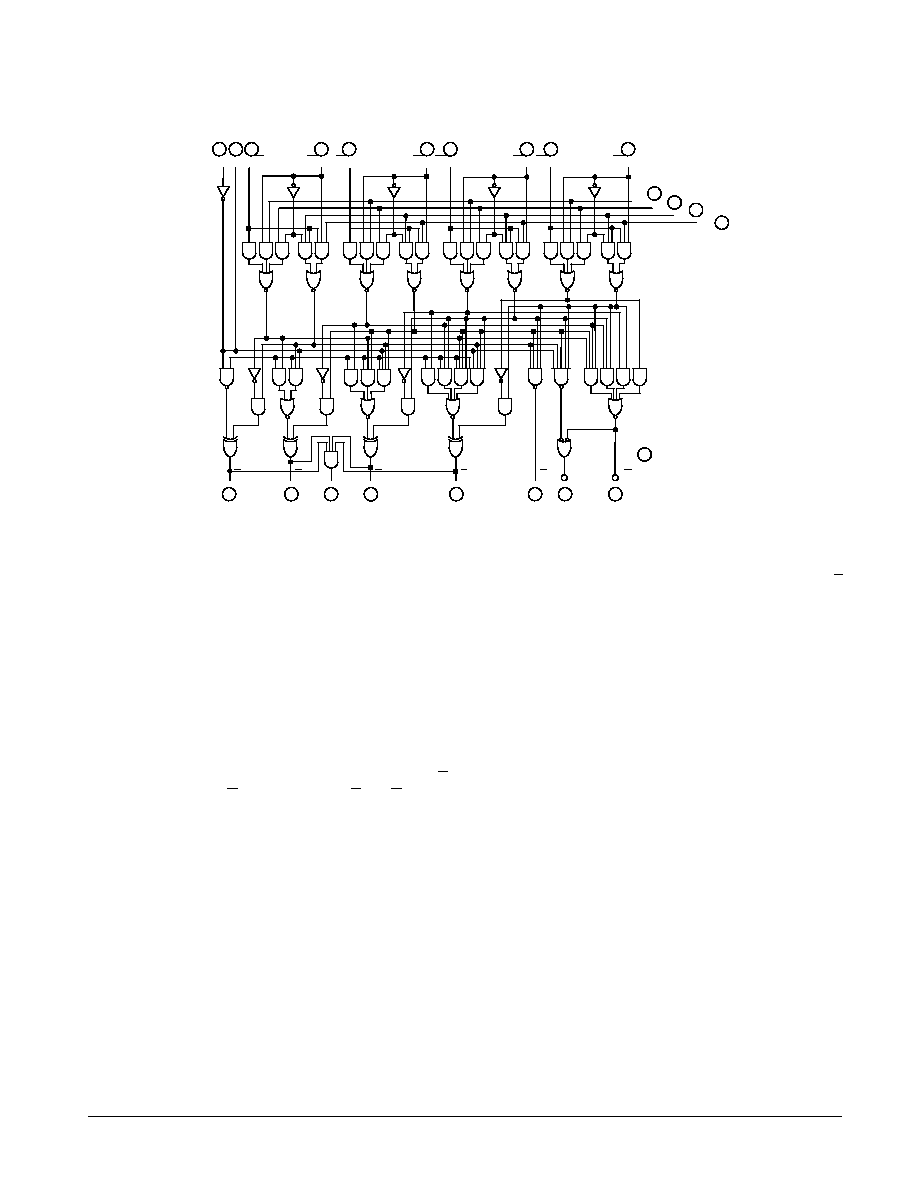

SN54/74LS181

2

LOGIC DIAGRAM

S0 S1

S2 S3

Cn M

A = B

Cn+4

A0

B0 A1

A2

A3

B1

B2

B3

F0

F1

F2

F3

P

G

14

1

6

7

3

8

4

5

9

11

16

10

13

15

VCC = PIN 24

GND = PIN 12

= PIN NUMBERS

21

22

23

20

18

19

17

FUNCTIONAL DESCRIPTION

The SN54 / 74LS181 is a 4-bit high speed parallel Arithmetic

Logic Unit (ALU). Controlled by the four Function Select Inputs

(S0 . . . S3) and the Mode Control Input (M), it can perform all

the 16 possible logic operations or 16 different arithmetic

operations on active HIGH or active LOW operands. The

Function Table lists these operations.

When the Mode Control Input (M) is HIGH, all internal

carries are inhibited and the device performs logic operations

on the individual bits as listed. When the Mode Control Input is

LOW, the carries are enabled and the device performs

arithmetic operations on the two 4-bit words. The device

incorporates full internal carry lookahead and provides for

either ripple carry between devices using the Cn+4 output, or

for carry lookahead between packages using the signals P

(Carry Propagate) and G (Carry Generate), P and G are not

affected by carry in. When speed requirements are not

stringent, the LS181 can be used in a simple ripple carry mode

by connecting the Carry Output (Cn+4) signal to the Carry Input

(Cn) of the next unit. For high speed operation the LS181 is

used in conjunction with the 9342 or 93S42 carry lookahead

circuit. One carry lookahead package is required for each

group of the four LS181 devices. Carry lookahead can be

provided at various levels and offers high speed capability

over extremely long word lengths.

The A = B output from the LS181 goes HIGH when all four F

outputs are HIGH and can be used to indicate logic

equivalence over four bits when the unit is in the subtract

mode. The A = B output is open collector and can be

wired-AND with other A = B outputs to give a comparison for

more then four bits. The A = B signal can also be used with the

Cn+4 signal to indicate A>B and A<B.

The Function Table lists the arithmetic operations that are

performed without a carry in. An incoming carry adds a one to

each operation. Thus, select code LHHL generates A minus B

minus 1 (2s complement notation) without a carry in and

generates A minus B when a carry is applied. Because

subtraction is actually performed by complementary addition

(1s complement), a carry out means borrow; thus a carry is

generated when there is no underflow and no carry is

generated when there is underflow.

As indicated, the LS181 can be used with either active LOW

inputs producing active LOW outputs or with active HIGH

inputs producing active HIGH outputs. For either case the

table lists the operations that are performed to the operands

labeled inside the logic symbol.

5-334

FAST AND LS TTL DATA

SN54/74LS181

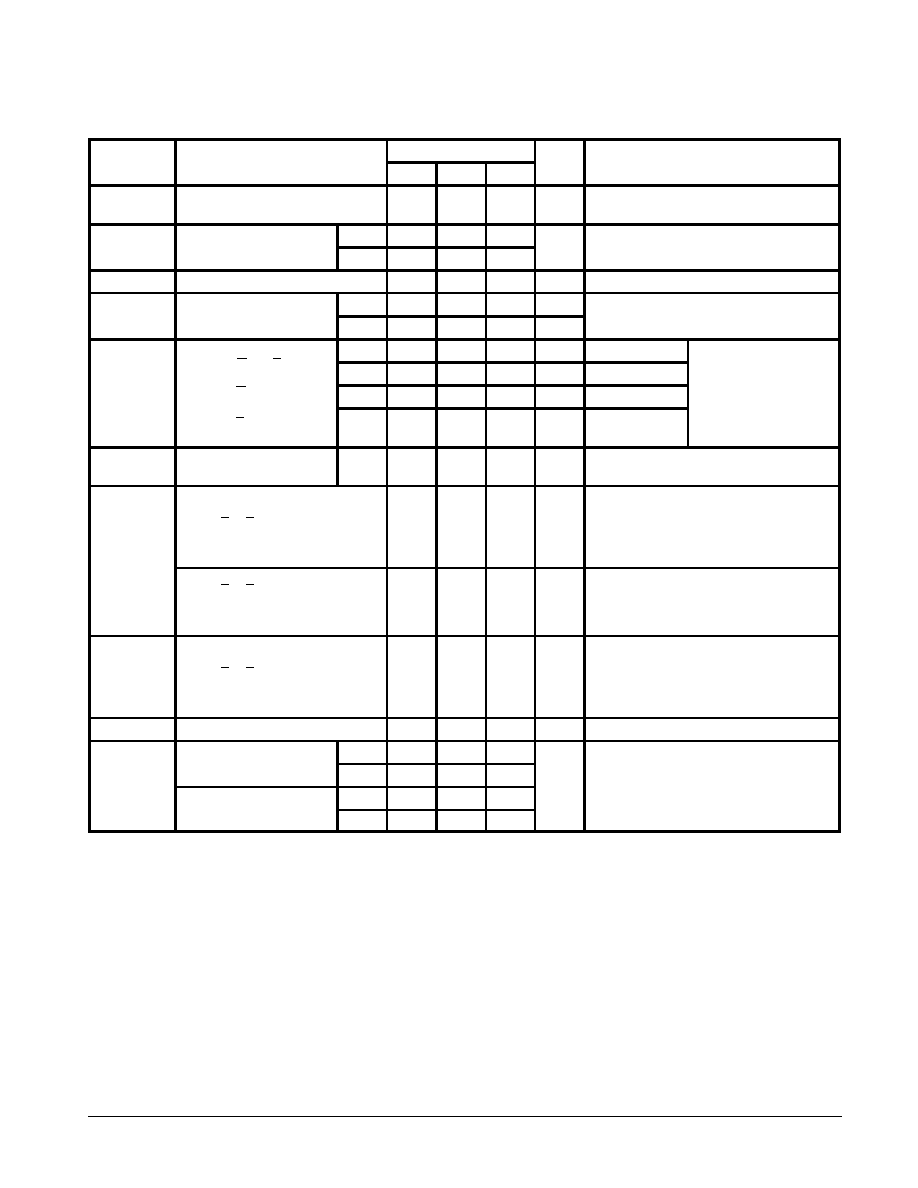

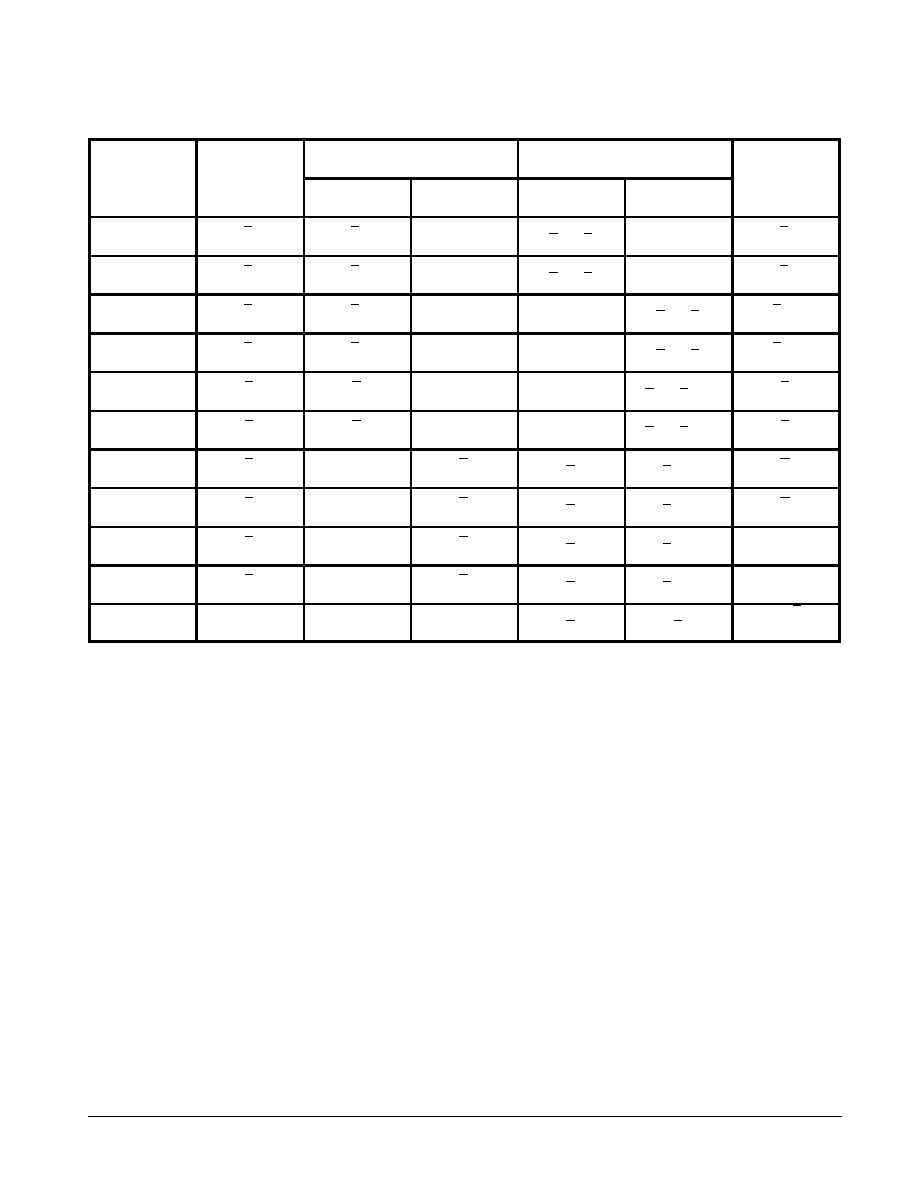

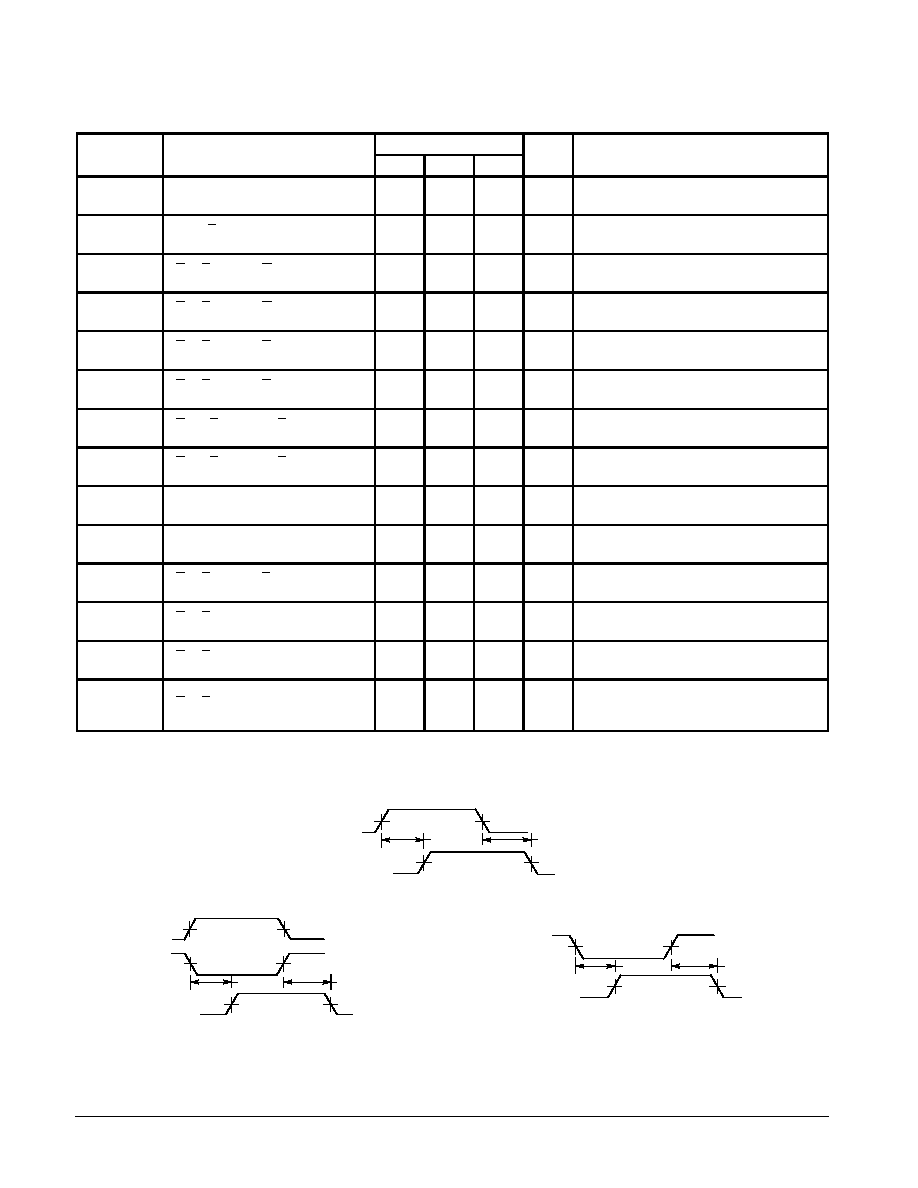

FUNCTION TABLE

MODE SELECT

INPUTS

ACTIVE LOW INPUTS

& OUTPUTS

ACTIVE HIGH INPUTS

& OUTPUTS

S3

S2

S1

S0

LOGIC

(M = H)

ARITHMETIC**

(M = L) (Cn = L)

LOGIC

(M = H)

ARITHMETIC**

(M = L) (Cn = H)

L

L

L

L

A

A minus 1

A

A

L

L

L

H

AB

AB minus 1

A + B

A + B

L

L

H

L

A + B

AB minus 1

AB

A + B

L

L

H

H

Logical 1 minus 1

Logical 0 minus 1

L

H

L

L

A + B

A plus (A + B)

AB

A plus AB

L

H

L

H

B

AB plus (A + B)

B

(A + B) plus AB

L

H

H

L

A

B

A minus B minus 1

A

B

A minus B minus 1

L

H

H

H

A + B

A + B

AB

AB minus 1

H

L

L

L

AB

A plus (A + B)

A + B

A plus AB

H

L

L

H

A

B

A plus B

A

B

A plus B

H

L

H

L

B

AB plus (A + B)

B

(A + B) plus AB

H

L

H

H

A + B

A + B

AB

AB minus 1

H

H

L

L

Logical 0 A plus A*

Logical 1 A plus A*

H

H

L

H

AB

AB plus A

A + B

(A + B) plus A

H

H

H

L

AB

AB plus A

A + B

(A + B) Plus A

H

H

H

H

A

A

A

A minus 1

L = LOW Voltage Level

H = HIGH Voltage Level

*

*Each bit is shifted to the next more significant position

**Arithmetic operations expressed in 2s complement notation

LOGIC SYMBOLS

ACTIVE LOW OPERANDS

ACTIVE HIGH OPERANDS

7

8

6

5

4

3

9

10

11

13

15

17

14

16

2 1 23 22 21 20 19 18

Cn

M

S0

S1

S2

S3

A0B0 A1 B1 A2 B2 A3 B3

F0

F1

F2

F3

Cn+4

A = B

G

P

LS181

4 BIT ARITHMETIC

LOGIC UNIT

7

8

6

5

4

3

9

10

11

13

15

17

14

16

2 1 23 22 21 20 19 18

Cn

M

S0

S1

S2

S3

A0B0 A1 B1 A2 B2 A3 B3

F0

F1

F2

F3

Cn+4

A = B

G

P

LS181

4 BIT ARITHMETIC

LOGIC UNIT

GUARANTEED OPERATING RANGES

Symbol

Parameter

Min

Typ

Max

Unit

VCC

Supply Voltage

54

74

4.5

4.75

5.0

5.0

5.5

5.25

V

TA

Operating Ambient Temperature Range

54

74

≠ 55

0

25

25

125

70

∞

C

IOH

Output Current -- High

54, 74

≠ 0.4

mA

IOL

Output Current -- Low

54

74

4.0

8.0

mA

VOH

Output Voltage -- High (A = B only)

54, 74

5.5

V

5-335

FAST AND LS TTL DATA

SN54/74LS181

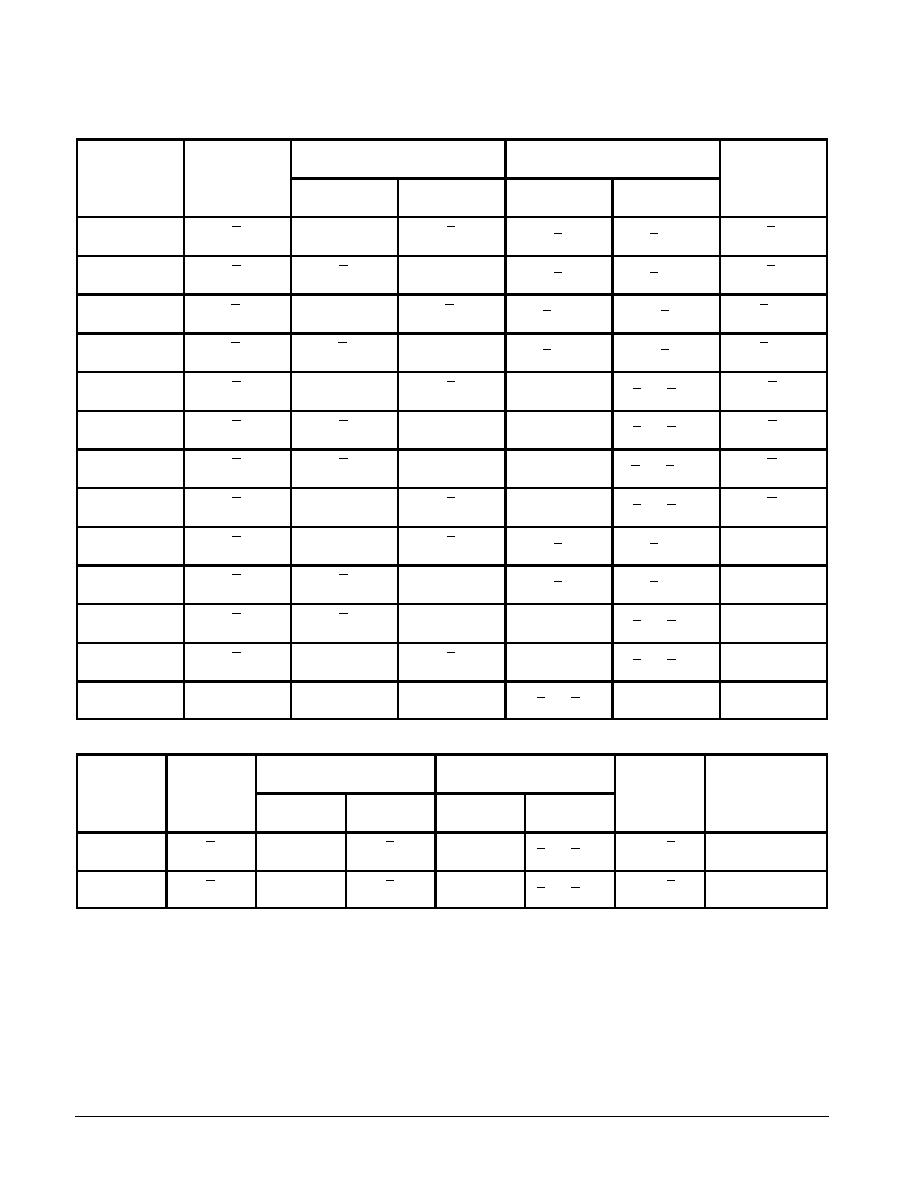

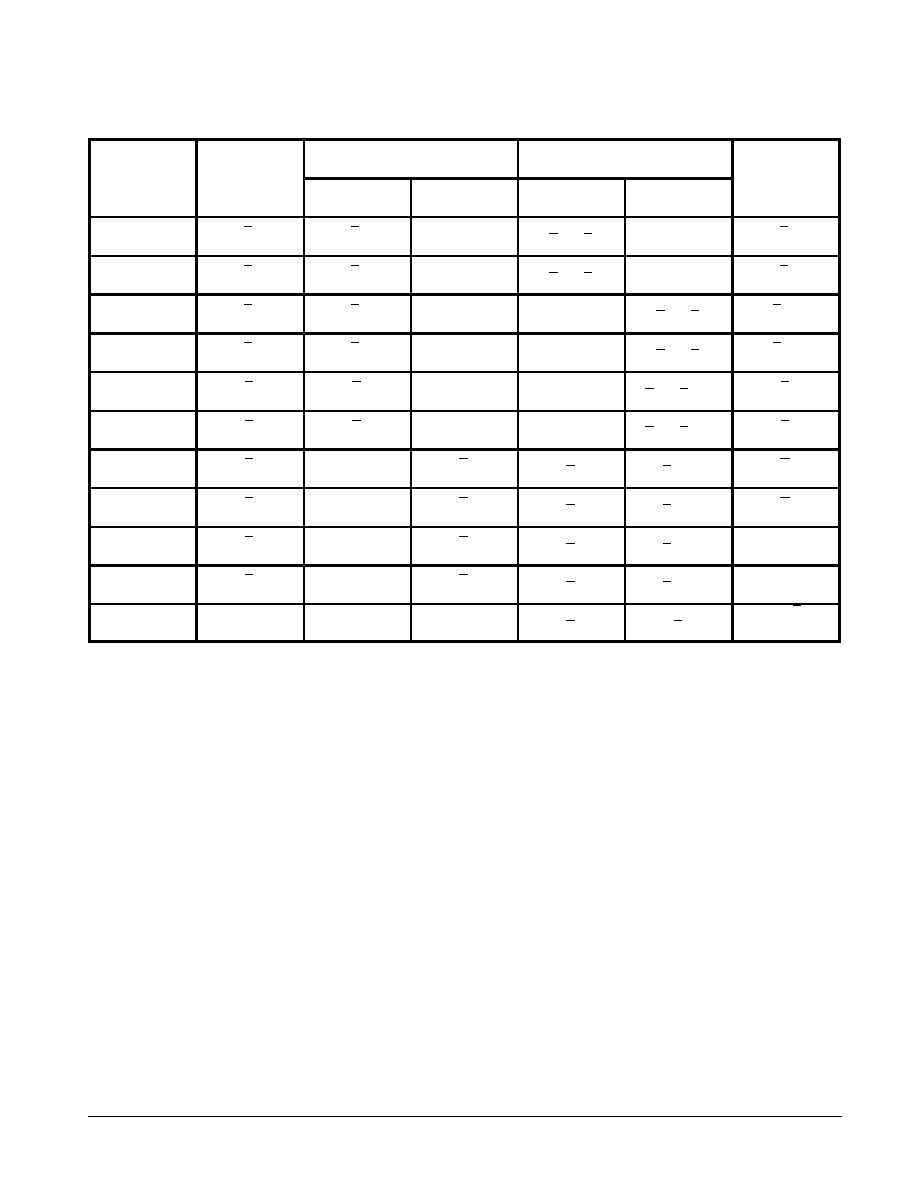

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE

(unless otherwise specified)

Symbol

Parameter

Limits

Unit

Test Conditions

Symbol

Parameter

Min

Typ

Max

Unit

Test Conditions

VIH

Input HIGH Voltage

2.0

V

Guaranteed Input HIGH Voltage for

All Inputs

VIL

Input LOW Voltage

54

0.7

V

Guaranteed Input LOW Voltage for

All Inputs

VIL

Input LOW Voltage

74

0.8

V

Guaranteed Input LOW Voltage for

All Inputs

VIK

Input Clamp Diode Voltage

≠ 0.65

≠ 1.5

V

VCC = MIN, IIN = ≠ 18 mA

VOH

Output HIGH Voltage

54

2.5

3.5

V

VCC = MIN, IOH = MAX, VIN = VIH

or VIL per Truth Table

VOH

Output HIGH Voltage

74

2.7

3.5

V

VCC = MIN, IOH = MAX, VIN = VIH

or VIL per Truth Table

VOL

Output LOW Voltage

Except G and P

54, 74

0.25

0.4

V

IOL = 4.0 mA

VCC = VCC MIN,

VIN = VIL or VIH

per Truth Table

VOL

Output LOW Voltage

Except G and P

74

0.35

0.5

V

IOL = 8.0 mA

VCC = VCC MIN,

VIN = VIL or VIH

per Truth Table

VOL

Output G

54, 74

0.7

V

IOL = 16 mA

VCC = VCC MIN,

VIN = VIL or VIH

per Truth Table

Output P

54

74

0.6

0.5

V

IOL = 8.0 mA

per Truth Table

IOH

Output HIGH Current

54, 74

100

µ

A

VCC = MIN, IOH = MAX, VIN = VIH

or VIL per Truth Table

IIH

Input HIGH Current

Mode Input

Any A or B Input

Any S Input

Cn Input

20

60

80

100

µ

A

VCC = MAX, VIN = 2.7 V

IIH

Mode Input

Any A or B Input

Any S Input

Cn Input

0.1

0.3

0.4

0.5

mA

VCC = MAX, VIN = 7.0 V

IIL

Input LOW Current

Mode Input

Any A or B Input

Any S Input

Cn Input

≠ 0.4

≠ 1.2

≠ 1.6

≠ 2.0

mA

VCC = MAX, VIN = 0.4 V

IOS

Short Circuit Current (Note 2)

≠ 20

≠ 100

mA

VCC = MAX

ICC

Power Supply Current

See Note 1A

54

32

mA

VCC = MAX

ICC

Power Supply Current

See Note 1A

74

34

mA

VCC = MAX

ICC

See Note 1B

54

35

mA

VCC = MAX

See Note 1B

74

37

Note 1.

With outputs open, ICC is measured for the following conditions:

A. S0 through S3, M, and A inputs are at 4.5 V, all other inputs are grounded.

B. S0 through S3 and M are at 4.5 V, all other inputs are grounded.

Note 2: Not more than one output should be shorted at a time, nor for more than 1 second.

5-336

FAST AND LS TTL DATA

SN54/74LS181

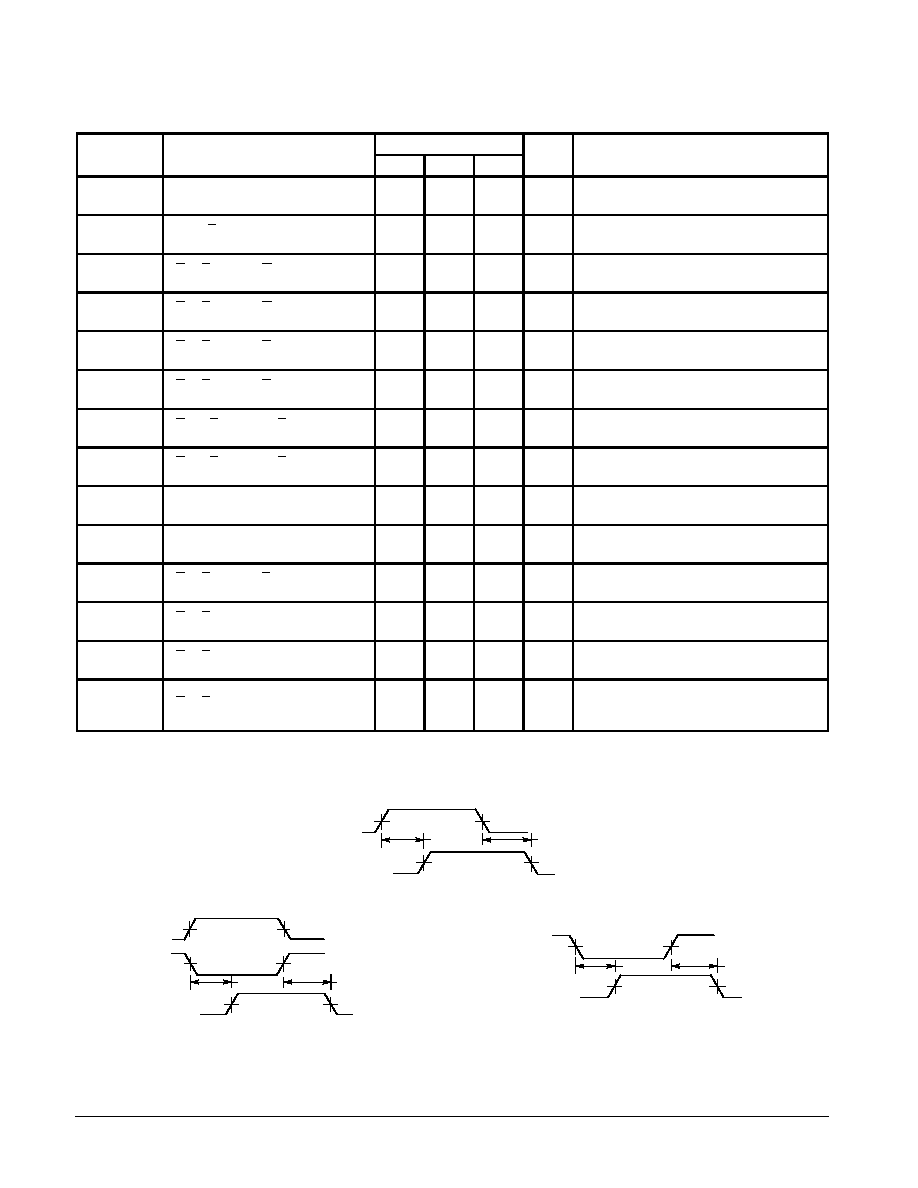

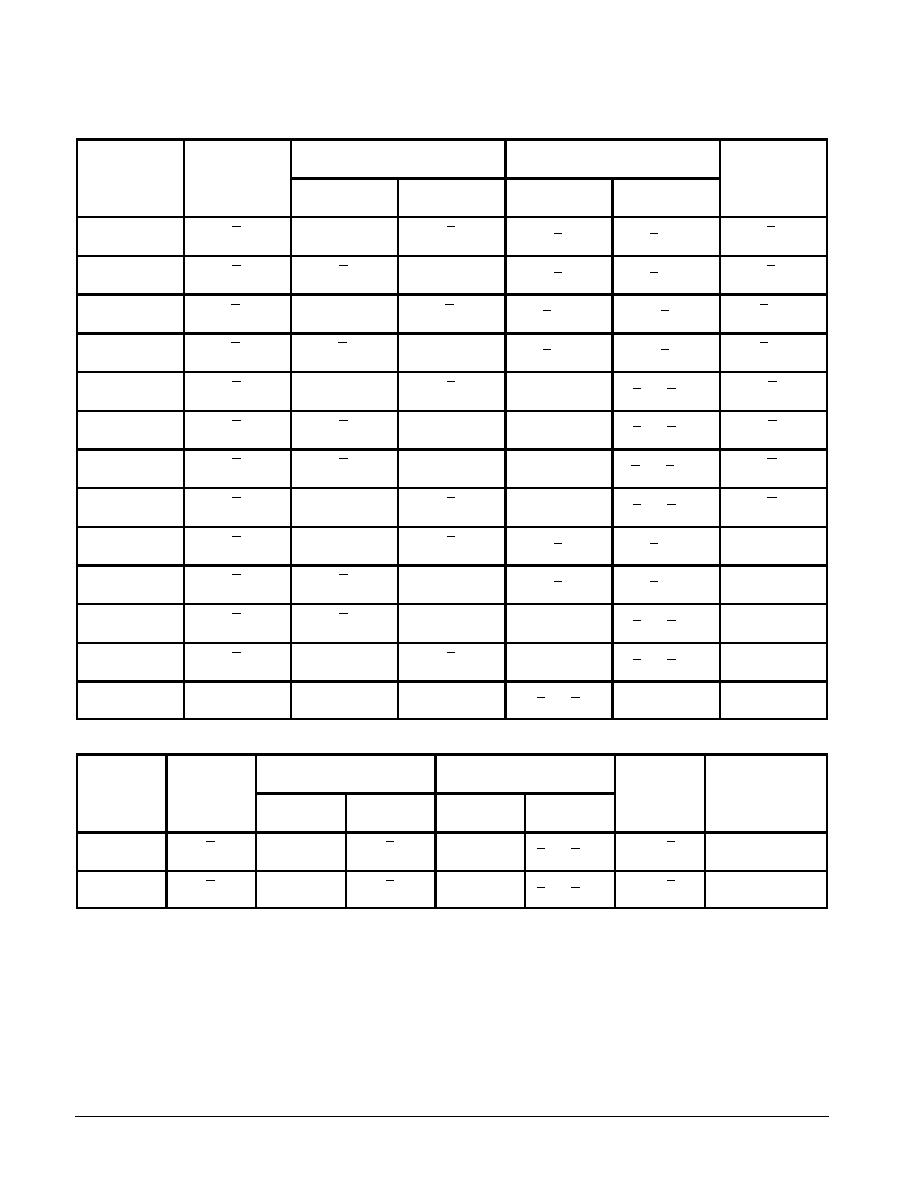

AC CHARACTERISTICS

(TA = 25

∞

C, VCC = 5.0 V, Pin 12 = GND, CL = 15 pF)

Symbol

Parameter

Limits

Unit

Test Conditions

Symbol

Parameter

Min

Typ

Max

Unit

Test Conditions

tPLH

tPHL

Propagation Delay,

(Cn to Cn+4)

18

13

27

20

ns

M = 0 V, (Sum or Diff Mode)

See Fig. 4 and Tables I and II

tPLH

tPHL

(Cn to F Outputs)

17

13

26

20

ns

M = 0 V, (Sum Mode)

See Fig. 4 and Table I

tPLH

tPHL

(A or B Inputs to G Output)

19

15

29

23

ns

M = S1 = S2 = 0 V, S0 = S3 = 4.5 V

(Sum Mode) See Fig. 4 and Table I

tPLH

tPHL

(A or B Inputs to G Output)

21

21

32

32

ns

M = S0 = S3 = 0 V, S1 = S2 = 4.5 V

(Diff Mode) See Fig. 5 and Table II

tPLH

tPHL

(A or B Inputs to P Output)

20

20

30

30

ns

M = S1 = S2 = 0 V, S0 = S3 = 4.5 V

(Sum Mode) See Fig. 4 and Table I

tPLH

tPHL

(A or B Inputs to P Output)

20

22

30

33

ns

M = S0 = S3 = 0 V, S1 = S2 = 4.5 V

(Diff Mode) See Fig. 5 and Table II

tPLH

tPHL

(AX or BX Inputs to FX Output)

21

13

32

20

ns

M = S1 = S2 = 0 V, S0 = S3 = 4.5 V

(Sum Mode) See Fig. 4 and Table I

tPLH

tPHL

(AX or BX Inputs to FX Output)

21

21

32

32

ns

M = S0 = S3 = 0 V, S1 = S2 = 4.5 V

(Diff Mode) See Fig. 5 and Table II

tPLH

tPHL

(AX or BX Inputs to FXH Outputs)

38

26

ns

M = S1 = S2 = 0 V, S0 = S3 = 4.5 V

(Sum Mode) See Fig. 4 and Table I

tPLH

tPHL

(AX or BX Inputs to FXH Outputs)

38

38

ns

M = S0 = S3 = 0 V, S1 = S2 = 4.5 V

(Diff Mode) See Fig. 5 and Table II

tPLH

tPHL

(A or B Inputs to F Outputs)

22

26

33

38

ns

M = 4.5 V (Logic Mode)

See Fig. 4 and Table III

tPLH

tPHL

(A or B Inputs to Cn+4 Output)

25

25

38

38

ns

M = 0 V, S0 = S3 = 4.5 V, S1 = S2 = 0 V

(Sum Mode) See Fig. 6 and Table I

tPLH

tPHL

(A or B Inputs to Cn+4 Output)

27

27

41

41

ns

M = 0 V, S0 = S3 = 0 V, S1 = S2 = 4.5 V

(Diff Mode)

tPLH

tPHL

(A or B Inputs to A = B Output)

33

41

50

62

ns

M = S0 = S3 = 0 V, S1 = S2 = 4.5 V

RL = 2.0 k

(Diff Mode) See Fig. 5 and Table II

AC WAVEFORMS

Figure 5

Figure 6

Figure 4

1.3 V

1.3 V

1.3 V

1.3 V

1.3 V

1.3 V

1.3 V

1.3 V

1.3 V

1.3 V

1.3 V

1.3 V

1.3 V

1.3 V

INPUT

INPUT

A INPUT

B INPUT

tPLH

tPLH

tPLH

tPHL

tPHL

tPHL

OUTPUT

OUTPUT

OUTPUT

5-337

FAST AND LS TTL DATA

SN54/74LS181

SUM MODE TEST TABLE I

FUNCTION INPUTS:

S0 = S3 = 4.5 V, S1 = S2 = M = 0 V

Parameter

Input

Under

Test

Other Input

Same Bit

Other Data Inputs

Output

Under

Test

Parameter

Input

Under

Test

Apply

4.5 V

Apply

GND

Apply

4.5 V

Apply

GND

Output

Under

Test

tPLH

tPHL

Al

Bl

None

Remaining

A and B

Cn

Fl

tPLH

tPHL

Bl

Al

None

Remaining

A and B

Cn

Fl

tPLH

tPHL

Al

Bl

None

Cn

Remaining

A and B

Fl+1

tPLH

tPHL

Bl

Al

None

Cn

Remaining

A and B

Fl+1

tPLH

tPHL

A

B

None

None

Remaining

A and B, Cn

P

tPLH

tPHL

B

A

None

None

Remaining

A and B, Cn

P

tPLH

tPHL

A

None

B

Remaining

B

Remaining

A, Cn

G

tPLH

tPHL

B

None

A

Remaining

B

Remaining

A, Cn

G

tPLH

tPHL

A

None

B

Remaining

B

Remaining

A, Cn

Cn+4

tPLH

tPHL

B

None

A

Remaining

B

Remaining

A, Cn

Cn+4

tPLH

tPHL

Cn

None

None

All

A

All

B

Any F

or Cn+4

5-338

FAST AND LS TTL DATA

SN54/74LS181

DIFF MODE TEST TABLE II

FUNCTION INPUTS:

S1 = S2 = 4.5 V, S0 = S3 = M = 0 V

Parameter

Input

Under

Test

Other Input

Same Bit

Other Data Inputs

Output

Under

Test

Parameter

Input

Under

Test

Apply

4.5 V

Apply

GND

Apply

4.5 V

Apply

GND

Output

Under

Test

tPLH

tPHL

A

None

B

Remaining

A

Remaining

B, Cn

Fl

tPLH

tPHL

B

A

None

Remaining

A

Remaining

B, Cn

Fl

tPLH

tPHL

Al

None

Bl

Remaining

B, Cn

Remaining

A

Fl+1

tPLH

tPHL

Bl

Al

None

Remaining

B, Cn

Remaining

A

Fl+1

tPLH

tPHL

A

None

B

None

Remaining

A and B, Cn

P

tPLH

tPHL

B

A

None

None

Remaining

A and B, Cn

P

tPLH

tPHL

A

B

None

None

Remaining

A and Bl, Cn

G

tPLH

tPHL

B

None

A

None

Remaining

A and B, Cn

G

tPLH

tPHL

A

None

B

Remaining

A

Remaining

B, Cn

A = B

tPLH

tPHL

B

A

None

Remaining

A

Remaining

B, Cn

A = B

tPLH

tPHL

A

B

None

None

Remaining

A and B, Cn

cn+4

tPLH

tPHL

B

None

A

None

Remaining

A and B, Cn

Cn+4

tPLH

tPHL

Cn

None

None

All

A and B

None

Cn+4

LOGIC MODE TEST TABLE III

Parameter

Input

Under

Test

Other Input

Same Bit

Other Data Inputs

Output

Under

Test

Function Inputs

Parameter

Input

Under

Test

Apply

4.5 V

Apply

GND

Apply

4.5 V

Apply

GND

Output

Under

Test

Function Inputs

tPLH

tPHL

A

None

B

None

Remaining

A and B, Cn

Any F

S1 = S2 = M = 4.5 V

S0 = S3 = 0 V

tPLH

tPHL

B

None

A

None

Remaining

A and B, Cn

Any F

S1 = S2 = M = 4.5 V

S0 = S3 = 0 V

5-339

FAST AND LS TTL DATA

Case 623-05 J Suffix

24-Pin Ceramic Dual In-Line

(WIDE BODY)

MIN

MIN

MAX

MAX

MILLIMETERS

INCHES

DIM

31.24

12.70

4.06

0.41

1.27

0.20

3.18

32.77

15.49

5.59

0.51

1.52

0.30

4.06

0

∞

0.51

1.230

0.500

0.160

0.016

0.050

0.008

0.125

1.290

0.610

0.220

0.020

0.060

0.012

0.160

15

∞

1.27

2.54 BSC

15.24 BSC

0.100 BSC

0.600 BSC

0

∞

0.020

15

∞

0.050

A

B

C

D

F

G

J

K

L

M

N

NOTES:

1. DIM L" TO CENTER OF LEADS WHEN

FORMED PARALLEL.

2. LEADS WITHIN 0.13 mm (0.005) RADIUS OF

TRUE POSITION AT SEATING PLANE AT

MAXIMUM MATERIAL CONDITION. (WHEN

FORMED PARALLEL).

SEATING PLANE

24

13

1

12

A

L

D

F

G

J

K

M

N

B

C

Case 649-03 N Suffix

24-Pin Plastic

Wide Body

M

SEATING

PLANE

G

J

L

B

A

P

H

F

K

C

D

N

Q

NOTES:

1. LEADS WITHIN 0.13 mm (0.005) RADIUS OF TRUE

POSITION AT SEATING PLANE AT MAXIMUM

MATERIAL CONDITION.

2. DIMENSION L" TO CENTER OF LEADS WHEN

FORMED PARALLEL.

3. 649 02 OBSOLETE, NEW STD 649 03 SEE ISSUE

C" FOR REFERENCE.

MIN

MIN

MAX

MAX

MILLIMETERS

INCHES

DIM

A

B

C

D

F

G

H

J

K

L

M

N

P

Q

31.50

13.21

4.70

0.38

1.02

1.65

0.20

2.92

14.99

0.51

0.13

0.51

32.13

13.72

5.21

0.51

1.52

2.16

0.30

3.43

15.49

10

∞

1.02

0.38

0.76

1.240

0.520

0.185

0.015

0.040

0.065

0.008

0.115

0.590

0.020

0.005

0.020

1.265

0.540

0.205

0.020

0.060

0.085

0.012

0.135

0.610

10

∞

0.040

0.015

0.030

2.54 BSC

0.100 BSC

1

12

13

24

5-340

FAST AND LS TTL DATA

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding

the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit,

and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different

applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does

not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in

systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of

the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such

unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless

against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death

associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

Motorola and

are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Literature Distribution Centers:

USA: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036.

EUROPE: Motorola Ltd.; European Literature Centre; 88 Tanners Drive, Blakelands, Milton Keynes, MK14 5BP, England.

JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141, Japan.

ASIA PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.