22

MPV5 Series

9x14 mm, 5.0 Volt, PECL, VCXO

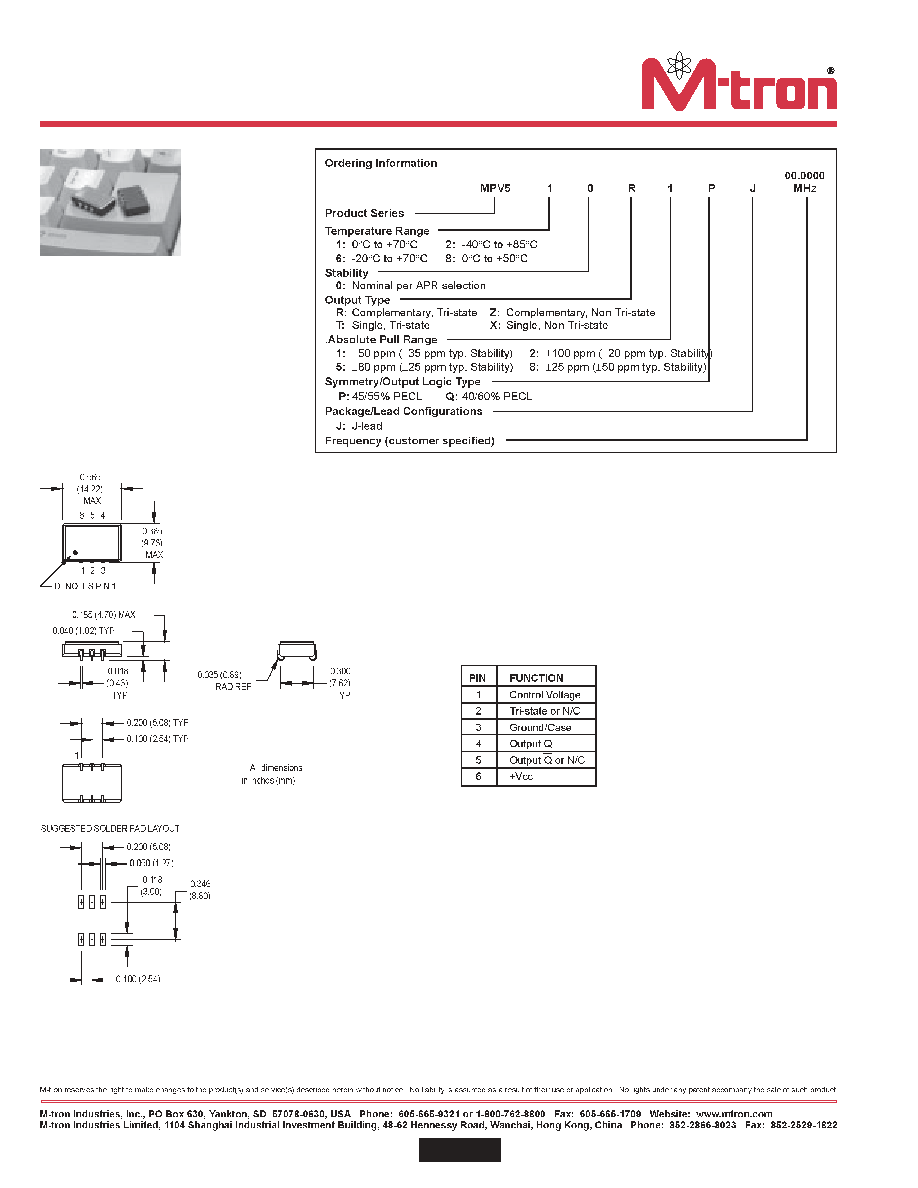

Pin Connections

∑

LVDS and PECL Output Logic With

Good Integrated Jitter Performance

(5 ps)

∑

Phase-Locked Loops (PLL's), Clock

Recovery, Reference Signal Tracking,

Synthesizers, Frequency Modulation/

Demodulation

23

V

C

X

O

1. Frequencies above 70 MHz utilize a PLL design. Fundamental and PLL designs are available for other frequencies. Contact factory.

2. Stability is given for deviation over temperature.

3. PECL load - see load circuit diagram #3 on page 148.

4. APR specification inclusive of initial tolerance, deviation over temperature, shock, vibration, supply voltage, and aging.

MPV5 Series

9x14 mm, 5.0 Volt, PECL, VCXO