| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CS5842 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

LCD Panel Timing Controller (15")

CS5842

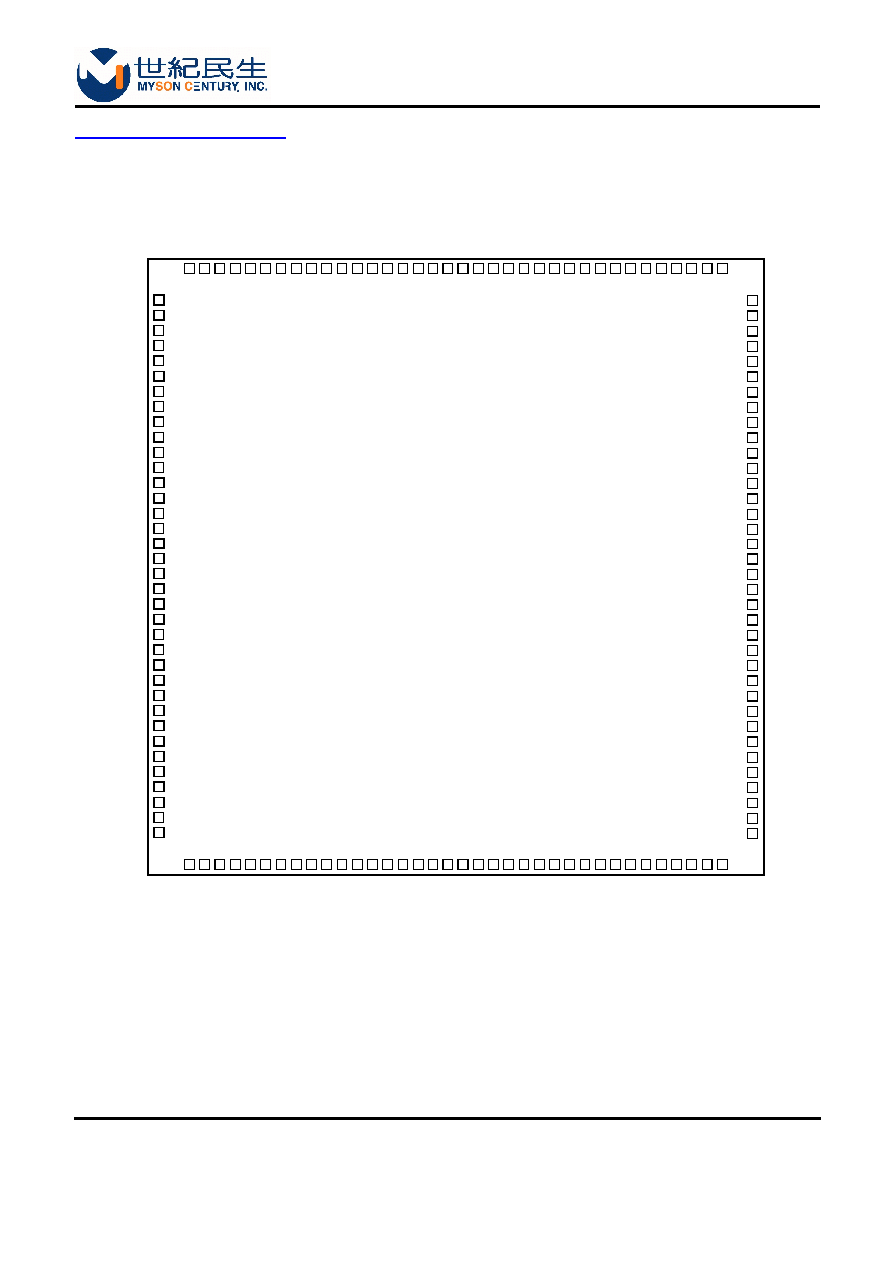

BLOCK DIAGRAM

GENERAL DESCRIPTION

FEATURES (continued)

FEATURES

USA:

4020 Moorpark Avenue Suite 115

San Jose, CA, 95117

Tel: 408-243-8388 Fax: 408-243-3188

Sales@myson.com.tw

www.myson.com.tw

Rev.1.1 June 2002

page 1 of 25

Myson Century, Inc.

Taiwan:

No. 2, Industry East Rd. III,

Science-Based Industrial Park, Hsin-Chu, Taiwan

Tel: 886-3-5784866 Fax: 886-3-5784349

∑ Interface (5V/3.3V[CMOS] input, 3.3V[CMOS] out-

put)

∑ Single (XGA2: 65MHz)/dual (XGA: 32.5MHz) 8-bit

Data input; dual port 8-bit output; SXGA auto

detective

∑ Timing adjustable for horizontal clock output

∑ Correspondent to control timing & specific resolu-

tion for different Driver IC by changing a Mask:

1. can vary the pulse width & starting position

of LP signal and POL signal polarity

position changed along with LP signal

2. can vary the pulse width & starting position

of CLKV signal and tgs time

∑ Control ASIC output timing design is based on

Data Enable signals

∑ Embedded Power On Reset circuits, Vth=2.1V, tol-

erance ± 0.3V

∑ ESD spec. 4KV

∑

Power On Latch Up 200mA/6.6V

∑ Single 3.3V supply

∑ 144-pin LQFP package

CS5842 is a TFT-LCD timing controller, which is

applicable to 8-bit data XGA (1024*768), SXGA

(1280*1024).

CS5842 can update the response timing for

display mode of XGA and SXGA automatically.

CS5842 provides a selectable polarity check

function to inverse output data for EMI reducing,

when the toggle number of ODD/EVEN RGB outputs

is larger than 13.

DENA

VD

HD

DCLK1

INV

PNDCLK

PNVD

POLIN

DATAHT

SXMD

PNHMS

PLMD

SET

HITAENB

CLKHT

GT(2~1)

ODDRI(7~0)

ODDGI(7~0)

ODDBI(7~0)

PNHD

ICMD(2~1)

SCMD

EVENRI(7~0)

EVENGI(7~0)

EVENBI(7~0)

CLKV

STV1

STV2

CLKH

STH8

POL

RLSC

LP

SHC

STH1

POWER ON RESET

POL/SHC

GENERATOR

CLKV

GENERATOR

LP

GENERATOR

CLKH

GENERATOR

DELAY

SAMPLE

POLARITY

OUTPUT

SELECTOR

DATA-PATH

ODDGO(7~0)

EVENGO(7~0)

ODDRO(7~0)

EVENRO(7~0)

ODDBO(7~0)

EVENBO(7~0)

HMS1

STH1/STH8

GENERATOR

STV1/STV3

GENERATOR

RGBD

INPUT

SELECTOR

HMS2

CS5842

CS5842

page 2 of 25

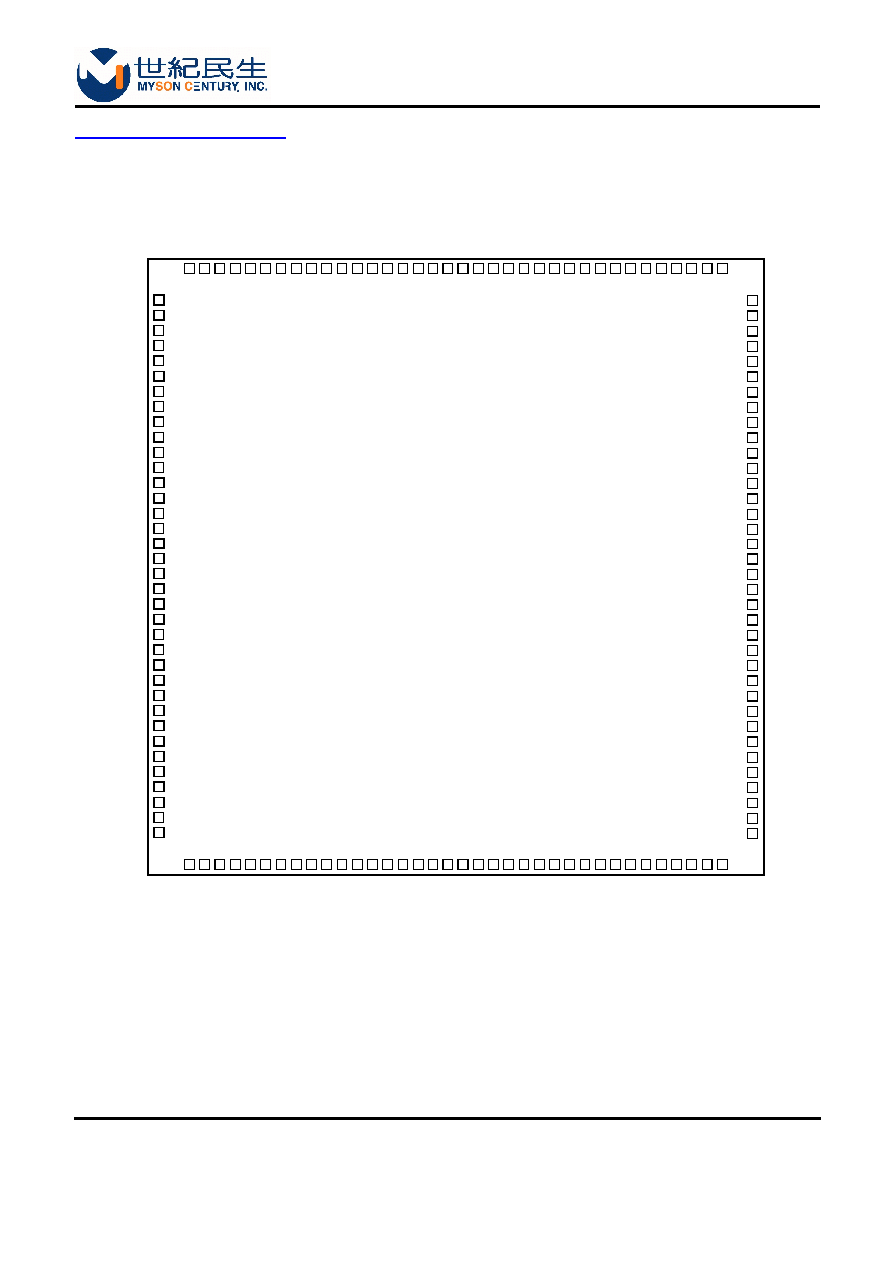

PIN CONNECTION DIAGRAM

Figure-1 144-pin LQFP

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

VDD

HITAENB

EVENGI7

EVENGI6

EVENGI5

EVENGI4

EVENGI3

EVENGI2

EVENGI1

EVENGI0

EVENRI7

EVENRI6

EVENRI5

EVENRI4

EVENRI3

EVENRI2

EVENRI1

EVENRI0

CLKHT

ICMD1

ICMD2

PLMD

PNDCLK

PNHMS

SCMD

EVENBO7

EVENBO6

EVENBO5

EVENBO4

EVENBO3

EVENBO2

EVENBO1

EVENBO0

EVENGO7

EVENGO6

VDD

VDD

INV

HD

VD

DENA

DATAHT

DCLK1

GND

PNHD

PNVD

SXMD

GT1

GT2

SET

RLSC

STV1

STV3

CLKV

STH1

LP

HMS1

HMS2

POL

SHC

STH8

ODDRO0

ODDRO1

ODDRO2

ODDRO3

ODDRO4

ODDRO5

ODDRO6

ODDRO7

ODDGO0

ODDGO1

VDD

GND

GND

EVE

NG

O

5

EVE

NG

O

4

EVE

NG

O

3

EVE

NG

O

2

EVE

NG

O

1

EVE

NG

O

0

EVENRO

7

EVENRO

0

EVENRO

5

EVENRO

2

EVENRO

3

EVENRO

4

EVENRO

1

EVENRO

6

PO

L

I

N

GND

CL

K

H

GND

ODDBO7

ODDBO6

ODDBO5

ODDBO4

ODDBO3

ODDBO2

ODDBO1

ODDBO0

ODDG

O7

ODDG

O6

ODDG

O5

ODDG

O4

ODDG

O3

ODDG

O2

GND

GND

GND

GND

EV

ENBI

0

EV

ENBI

1

EV

ENBI

2

EV

ENBI

3

EV

ENBI

4

EV

ENBI

5

EV

ENBI

6

EV

ENBI

7

ODDRI0

ODDRI1

ODDRI2

ODDRI3

ODDRI4

ODDRI5

ODDRI6

ODDRI7

ODDGI

0

ODDGI

1

ODDGI

2

ODDGI

3

ODDGI

4

ODDGI

5

ODDGI

6

ODDGI

7

ODDBI0

ODDBI1

ODDBI2

ODDBI3

ODDBI4

ODDBI5

ODDBI6

ODDBI7

GND

GND

CS5842

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

11

9

11

8

11

7

11

6

11

5

11

4

11

3

11

2

111

11

0

109

CS5842

page 3 of 25

PIN DESCRIPTION

Name

I/O

Pin

Block

Type

Description

Note

VDD

1

Supply 3.3V ± 10%

HITAENB

I

2

P5INPHU Enable signal of Hitachi mode, as ICMD2~1="10"

OPEN= disable; LOW=enable

Open

EVENGI(7-0)

I

3-10

P5INPMN EVEN green pixel data input.

(EVENGI0: LSB, EVENGI7:MSB)

(DCLK1 synchronized; low as XGA2 mode.)

XGA:16.25MHz

5V tolerant

EVENRI(7-0)

I

11-18

P5INPMN EVEN red pixel data input.

(EVENRI0: LSB, EVENRI7: MSB)

(DCLK1 synchronized; low as XGA2 mode.)

XGA:16.25MHz

5V tolerant

CLKHT

I

19

P5INPHU Adjust CLKH TIMING output.

1. CLKHT=LOW, 0.0ns delay

2. CLKHT=OPEN, 3.3ns delay

20k

pull up

(CLKHT:0

)

ICMD(1-2)

I

20-21

P5INPHU Source Driver IC selection (ICMD:LSB, ICMD2:MSB)

1. ICMD2 = OPEN, ICMD1 = LOW, (10): IC1

(NEC

µ

PD16750, Hitachi HD66350T)

2. ICMD2 = OPEN, ICMD1 = OPEN, (11): IC2

(Toshiba T6L64C, Sharp LH168R)

3. ICMD2 = LOW, ICMD1 = LOW, (00): IC3

(Winbond WFP6815)

4. ICMD2 = LOW, ICMD1 = OPEN, (01): IC4

(T.I.TMS57571)

20k

pull up

(ICMD1:0

ICMD2:OPEN)

PLMD

I

22

P5INPHU Polarity invert signal.

1. PLMD = OPEN: TWO LINE inverted

2. PLMD = LOW: ONE LINE inverted

20k

pull up

(0

)

PNDCLK

I

23

P5INPHU Input CLOCK signal polarity switch input.

LOW = inverted OPEN = non-inverted

20k

pull up

(OPEN)

PNHMS

I

24

P5INPHU HMS input invert switch output.

OPEN = non-inverted

LOW = invert output signal of HMS1 and HMS2.

20k

pull up

(0

)

SCMD

I

25

P5INPHD Controlling PIN of DRIVER IC R/L PIN

OPEN: RLSC = HIGH

output STV1, STH1; STV3,

STH8: no output (low)

HIGH: RLSC = LOW

output STV3, STH8; STV1,

STH1: no output (low)

EVENBO(7-0)

O

26-33

P3OUTRB EVEN blue pixel output

(EVENBO0:LSB, EVENBO7:MSB)

XGA:16.25MHz

EVENGO(7-6)

O

34-35

P3OUTRB EVEN green pixel output

(EVENGO0:LSB, EVENGO7:MSB)

XGA:16.25MHz

VDD

36

Power 3.3V ± 10%

GND

37

Ground.

CS5842

page 4 of 25

GND

38

Ground.

EVENGO(5-0)

O

39-44

P3OUTRB EVEN green pixel output

(EVENGO0:LSB, EVENGO7:MSB)

XGA:16.25MHz

EVENRO7

O

45

P3OUTRB EVEN red pixel output

(EVENRO7:MSB)

XGA:16.25MHz

EVENRO0

O

46

P3OUTRB EVEN red pixel output

(EVENRO0:LSB)

XGA:16.25MHz

EVENRO5

O

47

P3OUTRB EVEN red pixel output

XGA:16.25MHz

EVENRO2

O

48

P3OUTRB EVEN red pixel output

XGA:16.25MHz

EVENRO3

O

49

P3OUTRB EVEN red pixel output

XGA:16.25MHz

EVENRO4

O

50

P3OUTRB EVEN red pixel output

XGA:16.25MHz

EVENRO1

O

51

P3OUTRB EVEN red pixel output

XGA:16.25MHz

EVENRO6

O

52

P3OUTRB EVEN red pixel output

XGA:16.25MHz

POLIN

I

53

P5INPHU HMS polarity function calculation switch set.

1. POLIN = OPEN: calculated; HMS1, HMS2 calculated

separately.

2. POLIN = LOW: un-calculated; HMS1 = HMS2 = INV

20k

pull up

(OPEN)

GND

54

Ground

CLKH

O

55

P3OUTRD SHIFT clock output used by Source driver IC.

XGA:32.25MHz

GND

56

Ground

ODDBO(7-0)

O

57-64

P3OUTRB ODD blue pixel output.

(ODDBO0: LSB, ODDBO7: MSB)

XGA:16.25MHz

ODDGO(7-2)

O

65-70

P3OUTRB ODD green pixel output.

(ODDGO0: LSB, ODDGO7: MSB)

XGA:16.25MHz

GND

71

Ground

GND

72

Ground

VDD

73

Supply 3.3V± 10%

ODDGO(1-0)

O

74-75

P3OUTRB ODD green pixel output.

(ODDGO0: LSB; ODDGO7: MSB)

XGA:16.25MHz

ODDRO(7-0)

O

76-83

P3OUTRB ODD red pixel output.

(ODDRO0: LSB; ODDRO7: MSB)

XGA:16.25MHz

STH8

O

84

P3OUTRB START PULSE (S8

S1) of Source Driver IC

SHC

O

85

P3OUTRB Signal for T.I.

POL

O

86

P3OUTRB Polarity invert signal of Source Driver IC

HMS(2-1)

O

87-88

P3OUTRB Data polarity invert control signal output.

Output is based on POLIN set.

Name

I/O

Pin

Block

Type

Description

Note

CS5842

page 5 of 25

LP

O

89

P3OUTRB Latch Pulse of Source Driver IC.

STH1

O

90

P3OUTRB START PULSE (S1

S8) of Source Driver IC.

CLKV

O

91

P3OUTRB SHIFT CLOCK output for Gate Driver IC.

STV3

O

92

P3OUTRB START PULSE (G3

G1

)

of Gate Driver IC.

STV1

O

93

P3OUTRB START PULSE (G1

G3

)

of Gate Driver IC.

RLSC

O

94

P3OUTRB R/L Output for Source Driver IC.

SET

I

95

P5INPHU ASIC internal reset setting.

LOW = initialization, is usually OPEN.

20k

pull up

(OPEN)

GT(2-1)

I

96-97

P5INPHU Adjust CLKV Clock Timing (GT1: LSB; GT2: MSB).

20k

pull up

(GT1:OPEN

GT2:0

default:

01

3

µ

s)

1. ICMD2 = OPEN, ICMD1 = LOW: IC1

CLKV rising edge generated before LP falling edge.

4 steps: 0.5

µ

s (i.e. 17CLKH) each step, 2.5~4.0

µ

s

2. ICMD2 = OPEN, ICMD1 = OPEN: IC2

CLKV rising edge generated before LP rising edge.

4 steps: 0.5

µ

s (i.e. 17CLKH) each step, 2.5~4.0

µ

s

3. ICMD2 = LOW, ICMD1 = LOW: IC3

CLKV rising edge generated before LP falling edge.

4 steps: 0.5

µ

s (i.e. 17CLKH) each step, 2.5~4.0

µ

s

4. ICMD2 = LOW, ICMD1 = OPEN: IC4

CLKV rising edge generated before LP falling edge.

4 steps: 0.5

µ

s (i.e. 17CLKH) each step, 2.5~4.0

µ

s

SXMD

I

98

P5INPHU XGA/XGA2 switch selection

SXMD = OPEN; XGA(32.5MHz)

SXMD = LOW; XGA2(65MHz)

20k

pull up

(OPEN)

PNVD

I

99

P5INPHU Vertical sync signal polarity setting.

Low = inverted; Open = non-inverted.

20k

pull up

(OPEN)

PNHD

I

100

P5INPHU Horizontal sync signal polarity setting.

Low = inverted; Open = non-inverted.

20k

pull up

(OPEN)

GND

101

Ground

DCLK1

I

102

P5INPMN Dot Clock input.

XGA: 32.5MHz

5V tolerant

DATAHT

I

103

P5INPHU Adjust Data output Timing

1. DATAHT = OPEN 0.0ns/2.2ns/3.2ns delay

2. DATAHT = LOW 0.0ns/2.2ns/4.4ns delay

20k

pull up

(OPEN)

DENA

I

104

P5INPMN Data Enable signal input. DCLK1 synchronized. 5V tolerant

VD

I

105

P5INPMN Vertical sync signal input. DCLK1 synchronized. 5V tolerant

HD

I

106

P5INPMN Horizontal sync signal input. DCLK1 synchronized. 5V tolerant

Name

I/O

Pin

Block

Type

Description

Note