| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CS8553 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

BLOCK DIAGRAM

GENERAL DESCRIPTION

FEATURES

CS8553

TV Encoder

USA:

1485 Saratoga Ave. #200

San Jose, CA, 95129

Tel: 408-973-8388 Fax: 408-973-9388

Sales@myson.com.tw

www.myson.com.tw

Rev. 1.3 January 2003

page 1 of 21

Myson Century, Inc.

Taiwan:

No. 2, Industry East Rd. III,

Science-Based Industrial Park, Hsin-Chu, Taiwan

Tel: 886-3-5784866 Fax: 886-3-5784349

The CS8553 provides full conversion from digital

video format YCbCr into NTSC/PAL composite. It

can be used in VCD, DVD, and digital VCR

applications.

Two times oversampling reduces the output filter

requirements and guarantees no alias interference

by internal UV filters and Y filter.

A 9-bit DAC provides a composite video output

with high quality image.

32-pin package and pin assignment make the

CS8553 compatible with major vendors.

∑ Especially designed for VCD, Karaoke, digital

VCR, DVD, DIGITAL set-top box.

∑ Supports the following 4 modes:

NTSC, PAL-M, PAL-BDGHI, PAL-Nc.

∑ 8-bit 4:2:2 YCbCr inputs for glueless interface to

MPEG decoders.

∑ CVBS (composite YC) outputs.

∑ Supports CCIR-601 format, non-square pixel

∑ 2x oversampling simplifying external filtering.

∑ 6MHz and 1.3MHz anti-alias filters for Y and U/V

channels each.

∑ 1 channel of 9-bit DAC.

∑ Supports master and slave modes.

∑ Supports interlace operation only.

∑ Automatic mode detection/switching in slave

mode.

∑ 3.3V supply voltage; 5V tolerant for all digital I/O

pins.

VIDEO-TIMING

CONTROLLER

SUB-CARRIER

GENERATION

SINE-TABLE

SERIAL

TO

PARALLEL

4:2:2 to

4:4:4

INTER-

u-FILTER

v-FILTER

y-FILTER

POLATION

H, V-SYNC

CLK_27

SLEEP

P[7:0]

MODE[3:0]

SVIDEO

MASTER

CBSWAP

COLOR-BURST

&

MODULATION

&

MIXER

CVBS/Y

DAC-

MAPPING

VREF_O

FSADJUST

COMP

DAC

CS8553

page 2 of 21

PIN CONNECTION DIAGRAM

Figure-1 32-pin TQFP

P7

P6

P5

P4

P3

P2

P1

P0

FADJI

COMPI

VAA

VREFO

VREFI

NC

NC

VSS

CVBS/Y

VSS

VSS

HSYNC

VSYNC

VDD

VSS

CLK_27

SLEEP

SVIDEOI

CBSWA

P

I

MAS

T

ER

I

MD3

MD2

MD1

MD0

1

2

3

4

5

6

7

8

24

23

22

21

20

19

18

17

32

31

30

29

28

27

26

25

9

10

11

12

13

14

15

16

CS8553T

CS8553

page 3 of 21

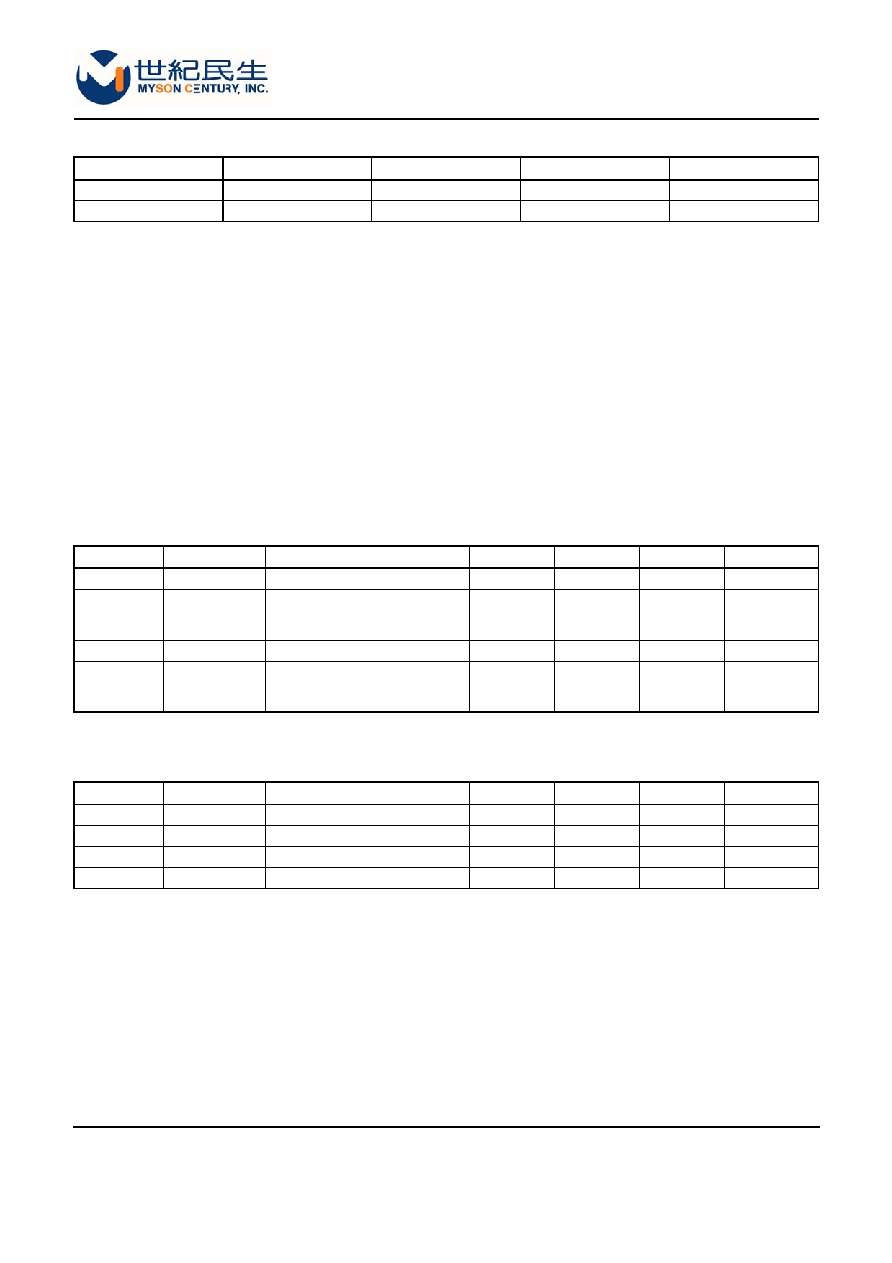

PIN DESCRIPTION

Name I/O

TQFP

Pin No.

Description

CLK_27

I

25

Pixel clock, 27MHz, twice the Y sample rate

VSYNC

I/O

28

Vertical sync, output in master mode or input in slave mode, is synchronized

by CLK.

HSYNC

I/O

29

Horizontal sync, output in master mode or input in slave mode, is

synchronized by CLK too.

P[7:0]

I

24-17

YCbCr pixel inputs (TTL compatible). Also, synchronized by CLK with

respect to the incoming HSYNC timing, the higher index corresponds to a

greater significance.

MD[3:0]

I

13-16

Configuration inputs

MASTER

I

12

in 0: slave mode, h and v sync are inputs. 1: master mode, h and v sync are

outputs.

CBSWAP

I

11

0: normal Cr, Cb sequence. 1: swaps Cr, Cb sequence

SVIDEO

I

10

Connected to VSS.

SLEEP

I

9

1: power down, reset 0: normal operation

FSADJUST

I

1

Full scale adjust control pin. A resistor RSET is connected to GND. Used to

control the full-scale output current on analog outputs.

COMP

I

2

Compensation pin. A 0.1

µF capacitor is used to bypass this pin to VCC.

VREFO

I

4

Voltage reference output, typically 1.2V, may be used to connect to VREFI

input.

VREFI/VRDAC

I

5

Voltage reference input, typically 1.235V. A 0.11

µF capacitor must be used

to decouple this input to GND. DAC current switch reference input, connect

to VREFO output.

NC

O

6

No connection

NC

O

7

No connection

CVBS/Y

O

32

Composite output or luminance (with blanking and sync)

VAA

3

Analog power

VDD

27

Digital power

GND

26

Digital ground

AGND

31,8

Analog ground

VSS

30

Analog ground

CS8553

page 4 of 21

FUNCTIONAL DESCRIPTION

MODE configuration

SeeTable 1 to Table 3 for details.

master = 1: master mode

Horizontal sync and vertical sync are generated from internal timing and are output at the rising edge of

clk_27.

md[3]: Defines EFIELD function

0: vsync is output pin

1: vsync is even/odd field indicator, vsync=0 even, vsync=1 odd.

md[2]: Defines PAL625 function

0: 525-line operation is set.

1: 626-line operation is set.

master = 0: slave mode

Horizontal sync and vertical sync are inputs that are synchronized by clk_27.

A falling edge of VSYNC* occurring within ±1/4 of a scan line from the falling edge of HSYNC* cycle time

indicates the beginning of Field-1. A falling edge of VSYNC* occurring within ±1/4 of a scan line from the

middle point of the line indicates the beginning of Field-2. See Figure 2.

Figure-2

md[3]: Defines YCSWAP

0: normal operation.

1: Swap the luma and chroma samples.

md[2]: Defines SETUP function

0: 7.5 IRE setup is enabled for NTSC and PAL-M, with scaling for 92.5% black-to-white range,

other PALs with normal 100% black-to-white range.

1: 7.5 IRE setup is disabled for NTSC and PAL-M, with scaling for 100% black-to-white range.

md[1]: Defines PALSA function, South America.

0: Normal operation.

1: PAL-M used for Brazil 525 lines operation. PAL-Nc used for Argentina 625 lines

operation.

Field-1

Field-2

CS8553

page 5 of 21

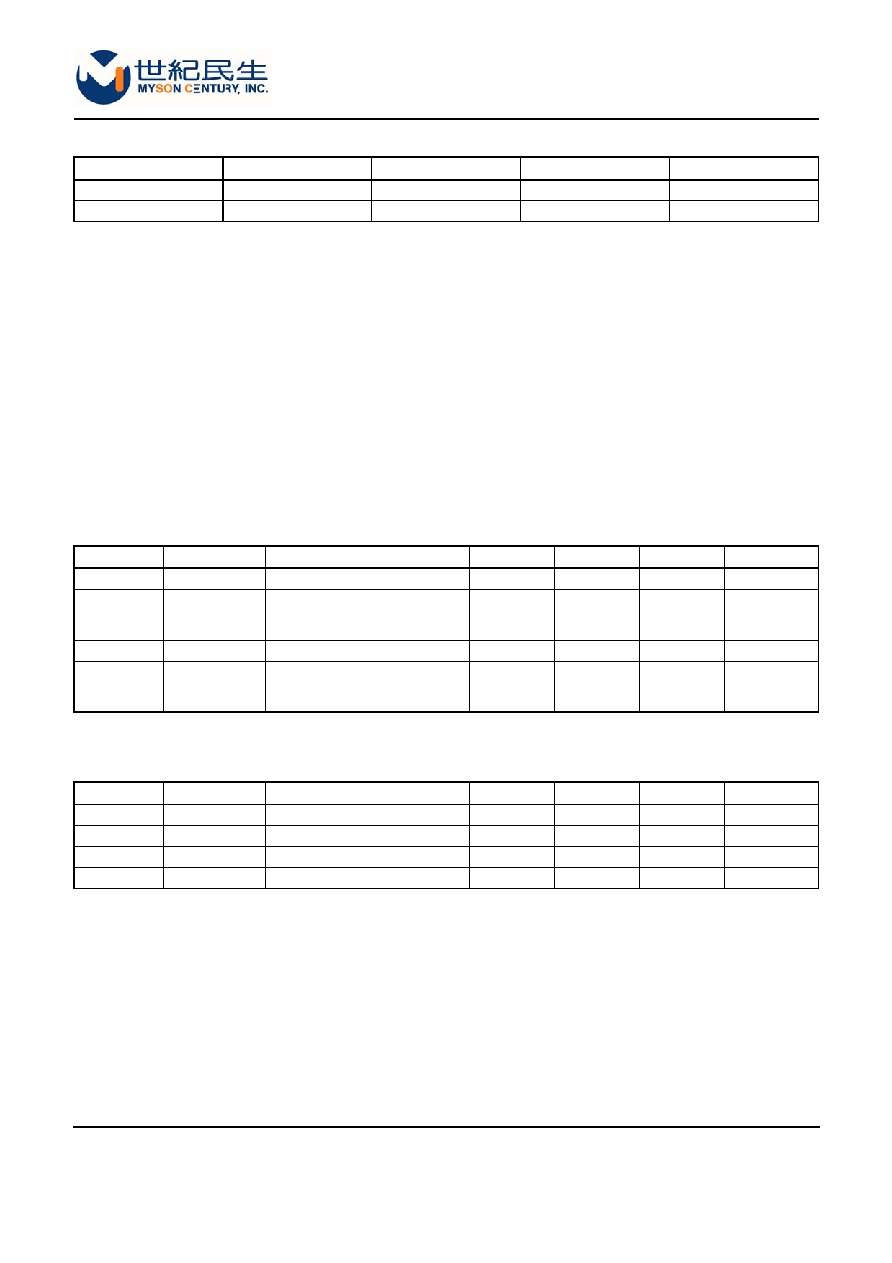

Table-1

EFIELD

EFIELD is used when configured as a master. When EFIELD is set low, the Normal vsync* signal is

output on the VSYNC* pin. When EFIELD is set high, field ID information is output on the VSYNC*

pin (VSYNC* low for Field-1 and high for Field-2)

PAL625

PAL625 is used when configured as a master. When PAL625 is set low, 525-line operation is

selected. When PAL625 is set high, 625-line operation is selected. This mode is set by automatic

detection when configured as a slave.

YCSWAP

YCSWAP should normally be set to zero. When configured as a slave, this bit can be set high to

swap the luma and chroma samples, thus altering the pixel sequence with respect to the incoming

HSYNC* timing reference.

SETUP

SETUP is normally low for the common video modes. The setup and scaling function is toggled

when this bit is high. When SETUP is low, the 7.5IRE setup is enabled for NTSC and PAL-M with

scaling amplified for a 92.5% black-to-white range. When SETUP is high, the 7.5 IRE setup is

disabled for NTSC and PAL-M with 100% black-to-white range scaling. Other PAL formats have

setup disabled with normal 100% scaling.

PALSA

PALSA is normally low for the common video modes. South American video Standards can be

enabled by setting this bit high. For 525-line operation, the PALSA enables PAL-M for Brazil; in 625-

line operation, the PALSA enables PAL-Nc for Argentina.

Table-2

Master mode:

Table-3

Slave mode:

Mode

Mode[3]

Mode[2]

Mode[1]

Mode[0]

Slave

YCSWAP

SETUP

PALSA

RESERVED

Master

EFIELD

PAL625

RESERVED

RESERVED

master

Mode[3:0]

System

PAL-625

PALSA

Fv Hz

Fh Hz

1

X000

(Normal setup) NTSC

0

0

59.94

15734.26

0

1

X010

X010

X010

PAL-M

0

1

59.94

15734.26

1

X100

PAL-BDGHI

1

0

50.00

15625

0

1

X010

X010

X110

PAL-Nc

1

1

50.00

15625

Master

Mode[3:0]

System

PAL-625

PALSA

Fv hz

Fh Hz

0

X000

NTSC

0

0

59.94

15734.26

0

X010

PAL-M

0

1

59.94

15734.26

0

X000

PAL-BDGHI

1

0

50.00

15625

0

X010

PAL-Nc

1

1

50.00

15625