3UHOLPLQDU\

3UHOLPLQDU\

GENERAL DESCRIPTION

FEATURES

CS9883/CS9883A

110 MSPS/140 MSPS Analog Flat Panel Interface

USA:

4020 Moorpark Avenue Suite 115

San Jose, CA, 95117

Tel: 408-243-8388 Fax: 408-243-3188

Sales@myson.com.tw

www.myson.com.tw

Rev. 0.92 November2002

page 1 of 41

Myson Century, Inc.

Taiwan:

No. 2, Industry East Rd. III,

Science-Based Industrial Park, Hsin-Chu, Taiwan

Tel: 886-3-5784866 Fax: 886-3-5784349

APPLICATIONS

∑ 140 Msps maximum conversion rate.

∑ 350MHz analog bandwidth.

∑ 0.5V to 1.0V analog input range.

∑ 500ps p-p PLL clock jitter.

∑ Power-Down Mode.

∑ 3.3V power supply.

∑ Midscale clamping.

∑ Sync detect for "Hot Plugging".

∑ Full sync processing.

∑ Low power: 1W typical at 140MHz.

∑ Internal PLL generates CLOCK from HSYNC.

∑ Serial port interface.

∑ Fully Programmable.

∑ 4:2:2 output format mode.

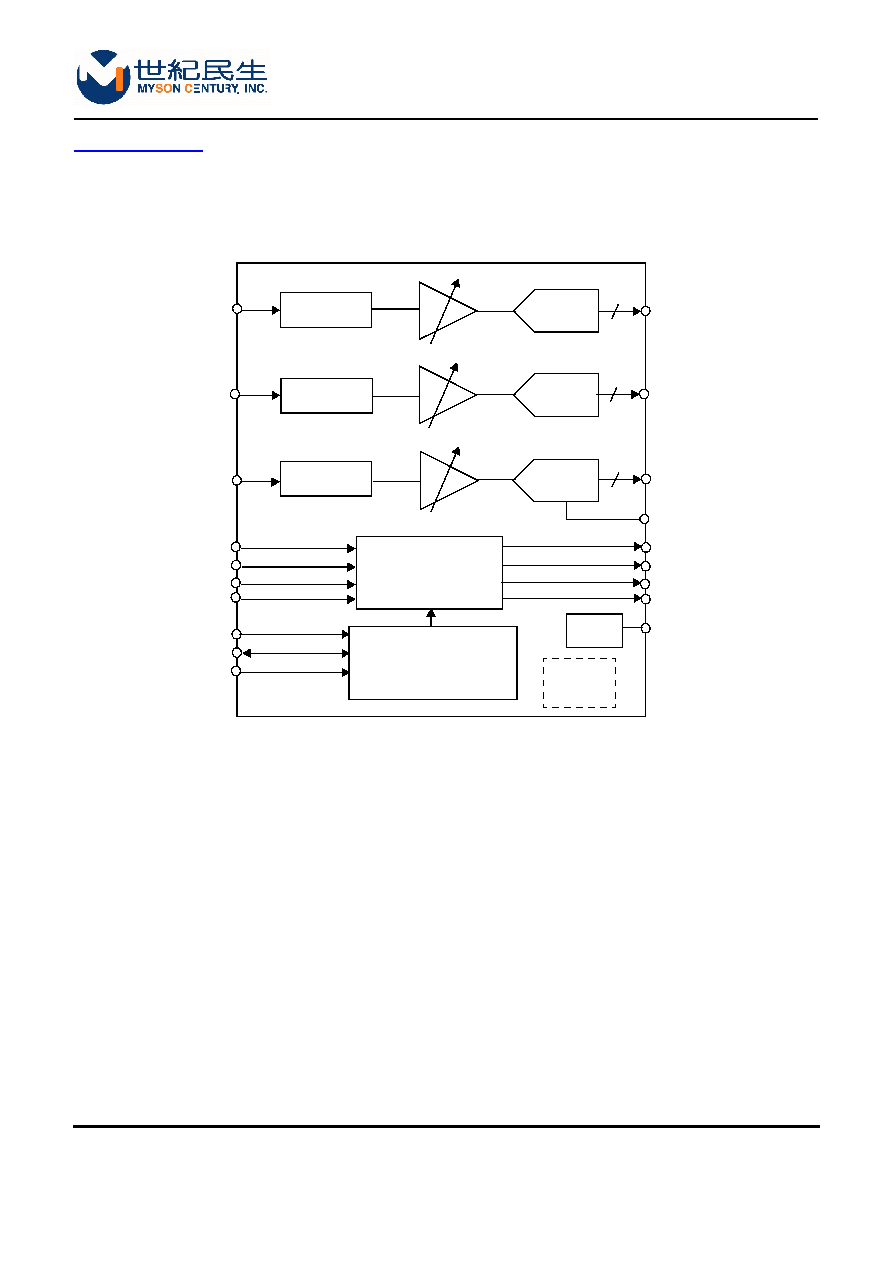

The CS9883 is a complete 8-bit 140 Msps

monolithic analog interface optimized for capturing

RGB graphics signals from personal computers and

workstations. Its 140 Msps encode rate capability

and full-power analog bandwidth of 350MHz

supports display resolutions of up to 1280x1024

(SXGA) at 85Hz with sufficient input bandwidth to

accurately acquire and digitize each pixel.

To minimize system cost and power dissipation,

the CS9883 includes an internal +1.25V reference,

PLL to generate a pixel clock from HSYNC, and

programmable gain, offset and clamp circuits. The

users provide only a +3.3V power supply, analog

input, and HSYNC and COAST signals.

The CS9883 is on-chip PLL generates a pixel

clock from the HSYNC and COAST inputs. Pixel

clock output frequencies range from 20MHz to

140MHz. PLL clock jitter is typically 500ps p-p. When

the COAST signal is presented, the PLL maintains its

output frequency in the absence of HSYNC. A 32-

step sampling phase adjustment is provided. Data,

HSYNC and data clock output phase relationships

are always maintained. The CS9883 also offers full

sync processing for composite sync and sync-on-

green applications.

A clamp signal is generated internally or may be

provided by the user through the CLAMP input pin.

This device is fully programmable via two-wire serial

port.

Fabricated in an advanced CMOS process, the

CS9883 is provided in a space-saving 80-lead LQFP

surface mount plastic package and is specified over

a 0

∞

C to +70

∞

C temperature range.

∑ RGB graphics processing

∑ LCD monitors and projectors.

∑ Plasma display panels.

∑ Scan converters.