©

1997,1999

DATA SHEET

©

1997

MIPS Technologies Inc.

MOS INTEGRATED CIRCUIT

µ

PD30500, 30500A, 30500B

Document No. U12031EJ4V0DS00 (4th edition)

Date Published May 2000 N CP(K)

Printed in Japan

DESCRIPTION

The

µ

PD30500 (V

R

5000),

µ

PD30500A (V

R

5000A), and

µ

PD30500B

Note

(V

R

5000B) are a high-performance, 64-

bit RISC (Reduced Instruction Set Computer) type microprocessors employing the RISC architecture developed by

MIPS

TM

Technologies Inc.

The instructions of the V

R

5000, V

R

5000A, and V

R

5000B are compatible with those of the V

R

3000

TM

Series and

V

R

4000

TM

Series and higher, and completely compatible with those of the V

R

10000

TM

. Therefore, present

applications can be used as they are.

Note

Under development

Detailed functions are described in the following manual. Be sure to read the manual when

designing your system.

∑ V

R

5000, V

R

5000A, V

R

5000B User's Manual (U11761E)

FEATURES

∑

Employs 64-bit MIPS-based RISC architecture

∑

High-speed processing

∑

2-way super scalar 5-stage pipeline

∑

5.5 SPECint95, 5.5 SPECfp95, 278 MIPS (

µ

PD30500)

6.6 SPECint95, 6.6 SPECfp95, 353 MIPS (

µ

PD30500A)

8 SPECint95, 8 SPECfp95, 423 MIPS (

µ

PD30500B)

∑

High-speed translation buffer mechanism (TLB) (48 entries)

∑

Address space

Physical: 36 bits, Virtual: 40 bits

∑

Floating-point unit (FPU)

∑

Sum-of-products operation instruction supported

∑

Primary cache memory (instruction/data: 32 Kbytes each)

∑

Secondary cache controller

∑

Maximum operating frequency Internal: 200 MHz (

µ

PD30500), 250 MHz (

µ

PD30500A), 300 MHz (

µ

PD30500B)

External: 100 MHz

∑

Selectable external/internal multiple rate from twice to eight times

∑

Instruction set compatible with V

R

3000 and V

R

4000 Series and higher (conforms to MIPS I, II, III, and IV)

∑

Supply voltage: 3.3 V

±

5% (

µ

PD30500)

Core: 2.5 V

±

5%, I/O: 3.3 V

±

5% (

µ

PD30500A)

Core: 1.8 V

±

0.1 V, I/O: 3.3 V

±

5% (

µ

PD30500B)

Unless otherwise specified, the V

R

5000 (

µ

PD30500) is treated as the representative model throughout this

document.

V

R

5000

TM

, V

R

5000A

TM

, V

R

5000B

TM

64-BIT MICROPROCESSOR

The mark shows major revised points.

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for availability

and additional information.

µ

PD30500, 30500A, 30500B

2

Data Sheet U12031EJ4V0DS00

APPLICATIONS

∑

High-performance embedded systems

∑

Multimedia systems

∑

Entry-class computers

∑

Image processing systems

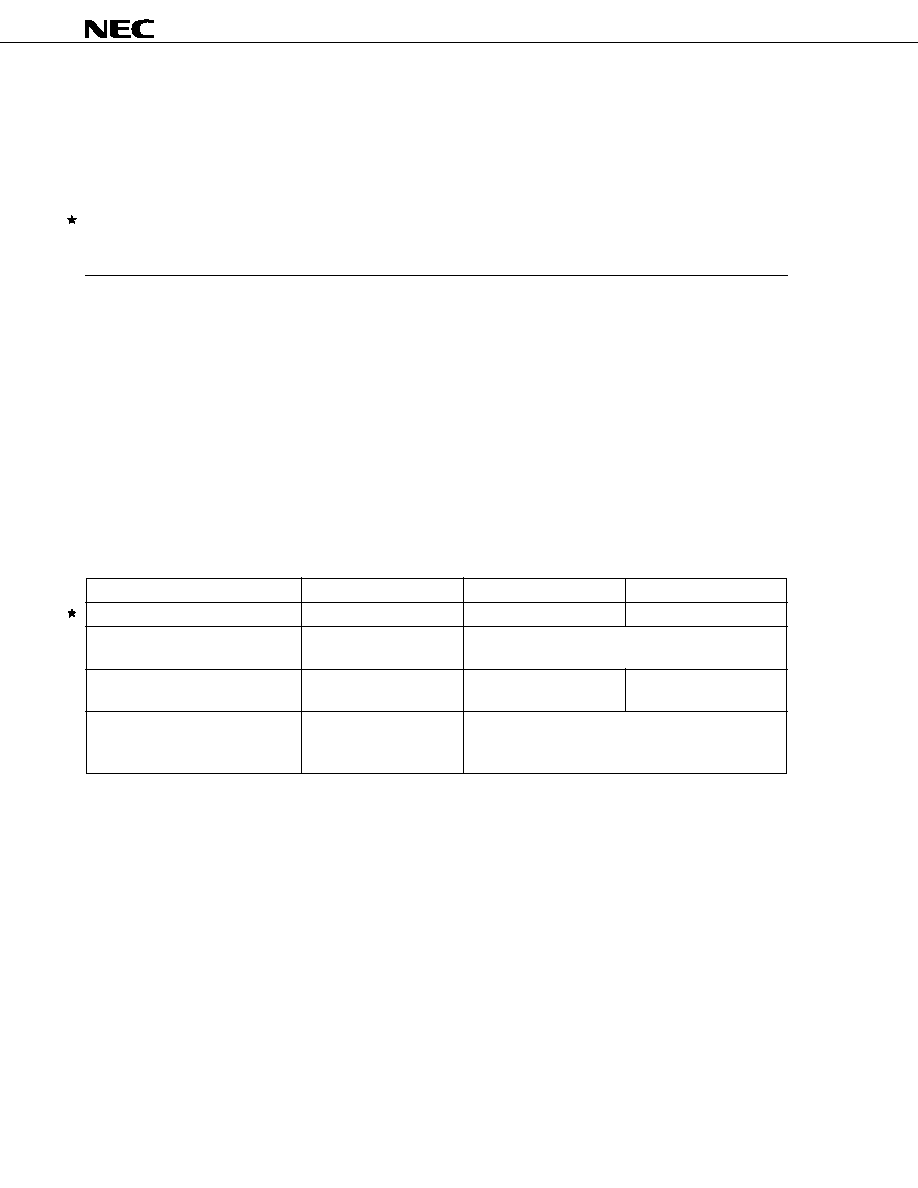

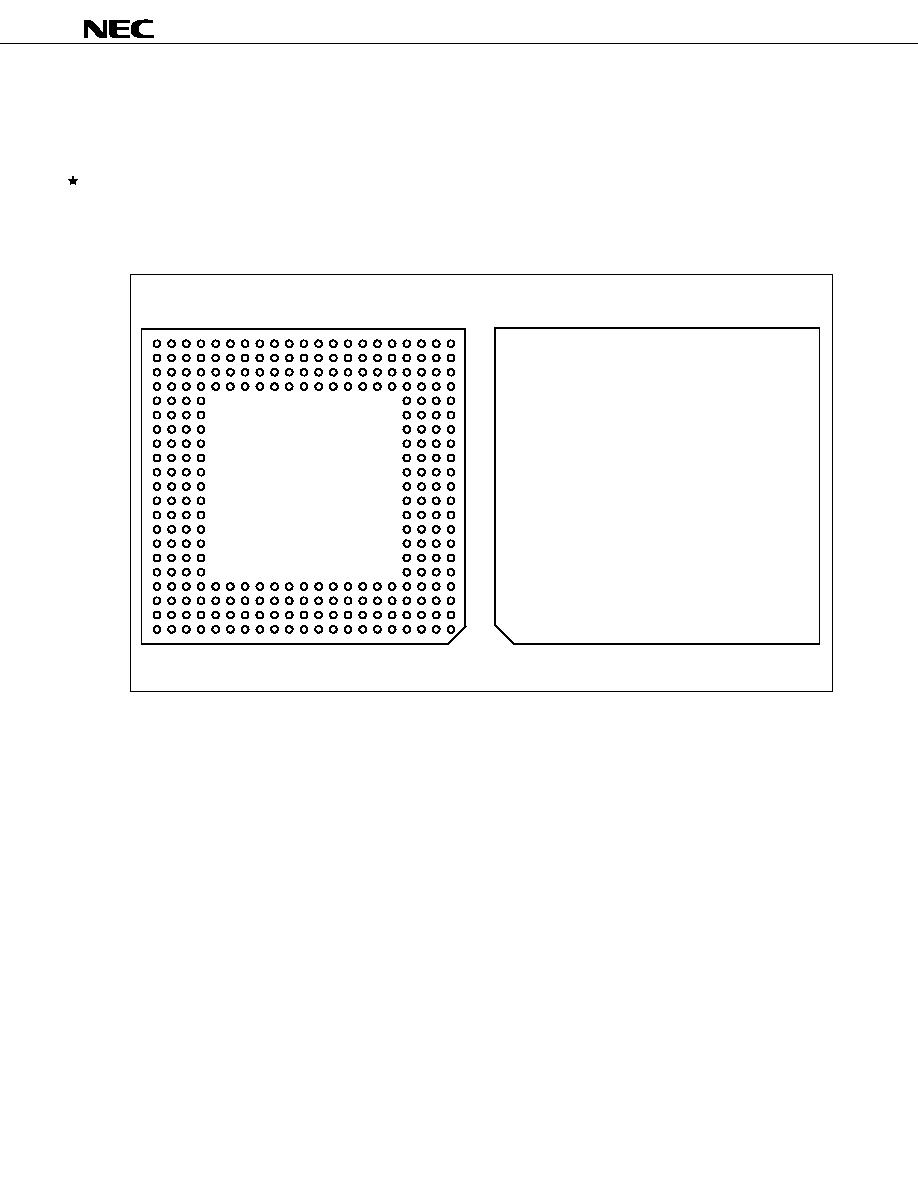

ORDERING INFORMATION

Part number

Package

Maximum operating frequency (MHz)

µ

PD30500RJ-150

223-pin ceramic PGA (48

◊

48)

150

µ

PD30500RJ-180

223-pin ceramic PGA (48

◊

48)

180

µ

PD30500RJ-200

223-pin ceramic PGA (48

◊

48)

200

µ

PD30500S2-150

272-pin plastic BGA (C/D advanced type) (29

◊

29)

150

µ

PD30500S2-180

272-pin plastic BGA (C/D advanced type) (29

◊

29)

180

µ

PD30500S2-200

272-pin plastic BGA (C/D advanced type) (29

◊

29)

200

µ

PD30500AS2-250

272-pin plastic BGA (C/D advanced type) (29

◊

29)

250

µ

PD30500BS2-300

Note

272-pin plastic BGA (C/D advanced type) (29

◊

29)

300

Note

Under development

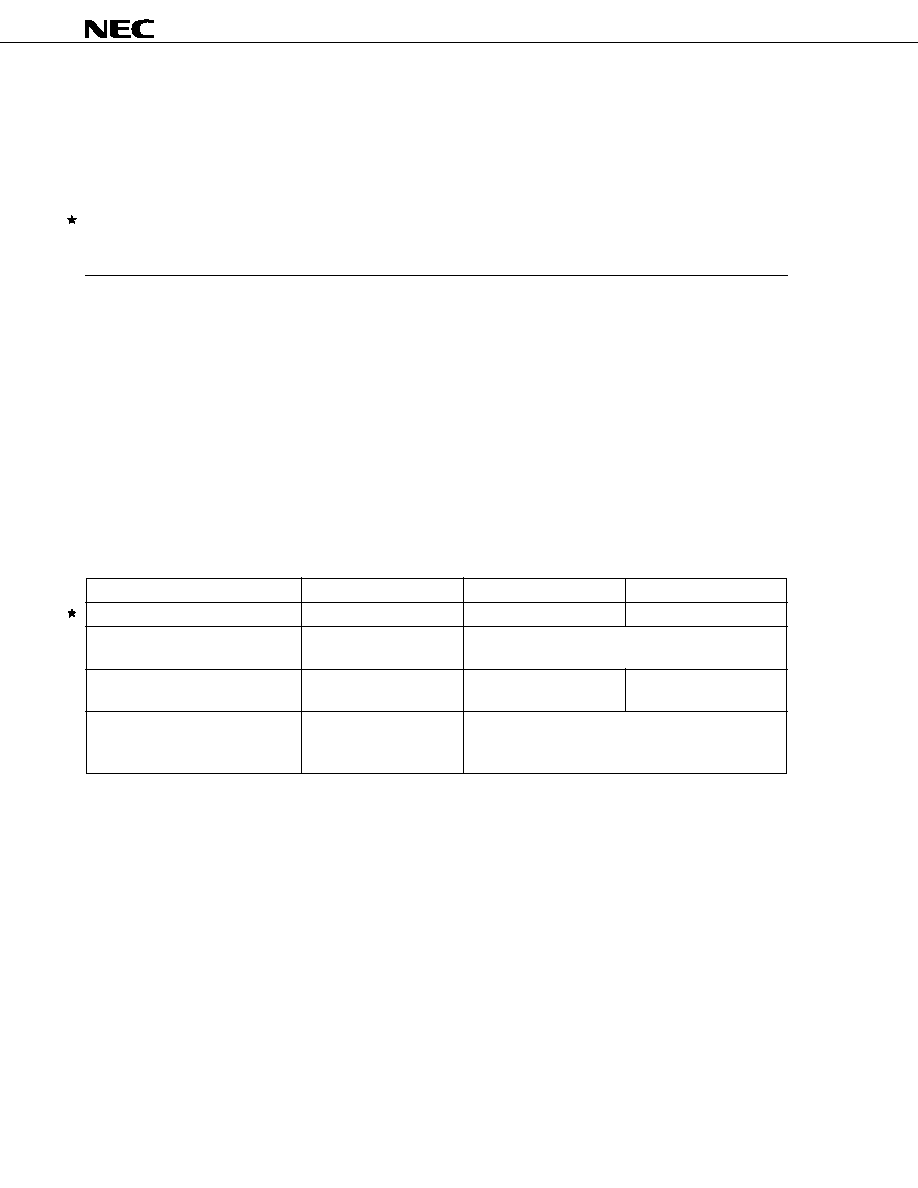

MAIN DIFFERENCES BETWEEN V

R

5000, V

R

5000A, AND V

R

5000B

Parameter

V

R

5000

V

R

5000A

V

R

5000B

Note 1

Maximum internal operating frequency

150/180/200 MHz

250 MHz

300 MHz

Internal multiplication ratio for clock

2, 3, 4, 5, 6, 7, 8

2, 2.5

Note 2

, 3, 4, 5, 6, 7, 8

interface input

Supply voltage

3.3 V

±

5%

Core: 2.5 V

±

5%

Core: 1.8 V

±

0.1 V

I/O: 3.3 V

±

5%

I/O: 3.3 V

±

5%

Package

∑ 223-pin ceramic PGA

∑ 272-pin plastic BGA (C/D advanced type)

∑ 272-pin plastic BGA

(C/D advanced type)

Notes 1. Under development

2. Selectable only when SysClock = 100 MHz