Document Outline

- COVER

- FEATURES

- APPLICATIONS

- ORDERING INFORMATION

- PIN CONFIGURATION

- PIN NAMES

- INTERNAL BLOCK DIAGRAM

- 1. DIFFERENCES AMONG PRODUCTS

- 2. LIST OF PIN FUNCTIONS

- 2.1 Port Pins

- 2.2 Non-port Pins

- 2.3 I/O Circuits of Pins and Processing of Unused Pins

- 3. FUNCTION BLOCKS

- 4. CPU FUNCTIONS

- 5. BUS CONTROL FUNCTIONS

- 6. INTERRUPT/EXCEPTION HANDLING FUNCTIONS

- 7. CLOCK GENERATION FUNCTIONS

- 8. TIMER/COUNTER FUNCTIONS (REAL-TIME PULSE UNIT)

- 9. SERIAL INTERFACE FUNCTIONS (SIO)

- 9.1 Asynchronous Serial Interfaces 0, 1 (UART0, UART1)

- 9.2 Clock-synchronized Serial Interfaces 0 to 3 (CSI0 to CSI3)

- 9.3 Baud Rate Generators 0 to 2 (BRG0 to BRG2)

- 10. PWM UNIT

- 11. A/D CONVERTER

- 12. D/A CONVERTER

- 13. PORT FUNCTIONS

- 14. RESET FUNCTIONS

- 15. INSTRUCTION SET

- 16. ELECTRICAL SPECIFICATIONS

- 17. PACKAGE DRAWINGS

- 18. RECOMMENDED SOLDERING CONDITIONS

©

1997

DATA SHEET

µ

PD703003

MOS INTEGRATED CIRCUIT

The

µ

PD703003 is a member of the V850 Family

TM

of 32-bit single-chip microcontrollers designed for real-time

control operations. This microcontroller provides on-chip features, including a 32-bit CPU core, ROM, RAM, interrupt

controller, real-time pulse unit, a serial interface, an A/D converter, a D/A converter, and PWM signal units.

See the following manuals for a detailed description of this product's functions. Be sure to use these

manuals as a reference for design.

V853 USER'S MANUAL, HARDWARE:

U10913E

V850 FAMILY USER'S MANUAL, ARCHITECTURE:

U10243E

FEATURES

∑ Number of instructions: 74

∑ Minimum instruction execution time

30 ns (during 33-MHz operation)

∑ General registers

32 bits

◊

32 registers

∑ Instruction set optimized for control applications

∑

On-chip memory

ROM: 128 Kbytes

RAM:

4 Kbytes

∑ Advanced on-chip interrupt controller

∑ Real-time pulse unit suitable for control operations

∑ Powerful serial interface (on-chip dedicated baud rate generator)

∑ On-chip clock generator

∑ 10-bit resolution A/D converter: 8 channels

∑ 8-bit resolution D/A converter: 2 channels

∑ 8/9/10/12-bit resolution PWM: 2 channels

∑ Power saving functions

APPLICATIONS

∑ AV: Video cameras, VCRs, etc.

∑ Office equipment: PPCs, LBPs, printers, etc.

∑ Industrial equipment: motor controllers, NC machine tools, etc.

∑ Communications equipment: Mobile telephones, etc.

V853

TM

32/16-BIT SINGLE-CHIP MICROCONTROLLER

The mark shows major revised points.

Document No. U12261EJ2V1DS00 (2nd edition)

Date Published April 1999 N CP(K)

Printed in Japan

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for availability

and additional information.

µ

PD703003

2

Data Sheet U12261EJ2V1DS00

ORDERING INFORMATION

Part Number

Package

Maximum operating frequency (MHz)

µ

PD703003GC-25-xxx-7EA 100-pin plastic QFP (fine pitch) (14

◊

14 mm)

25

µ

PD703003GC-33-xxx-7EA 100-pin plastic QFP (fine pitch) (14

◊

14 mm)

33

Remark "xxx" indicates ROM code suffix.

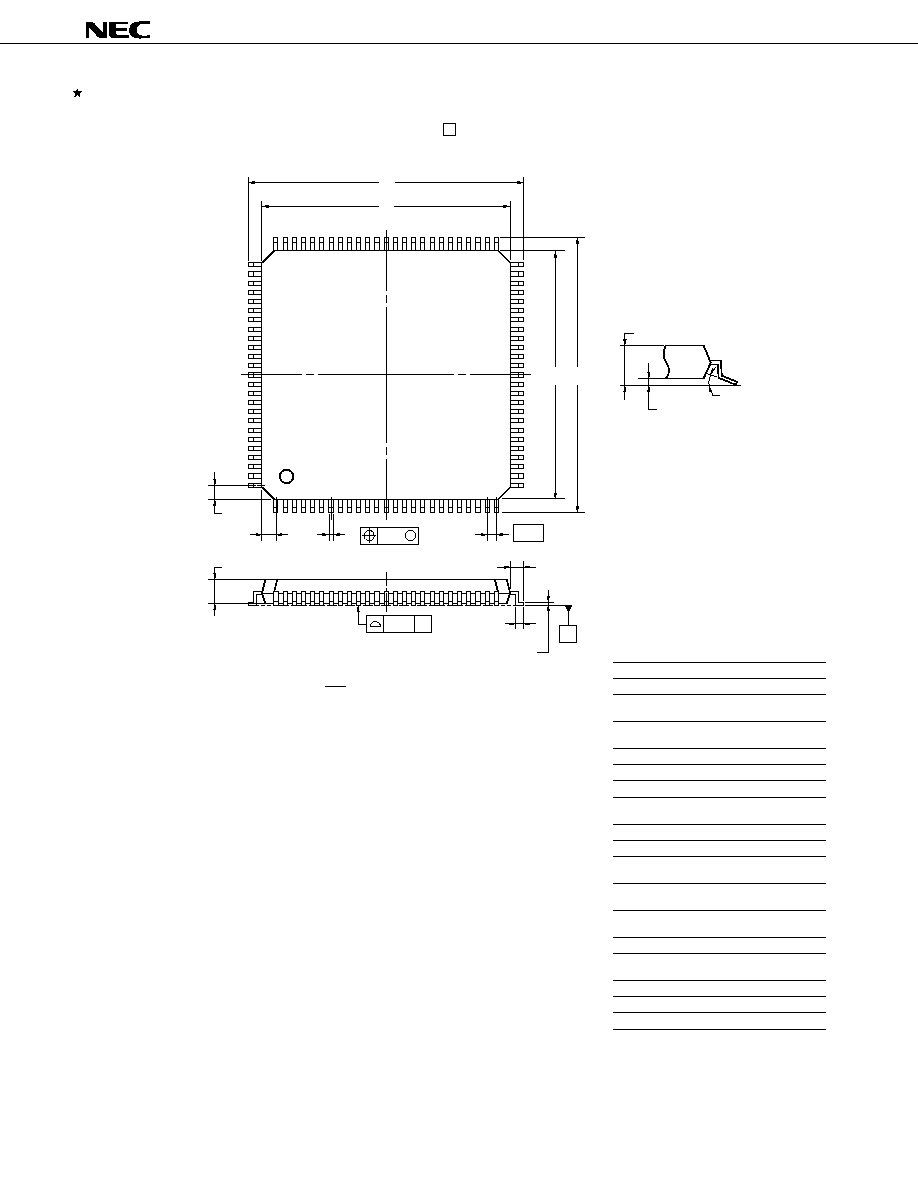

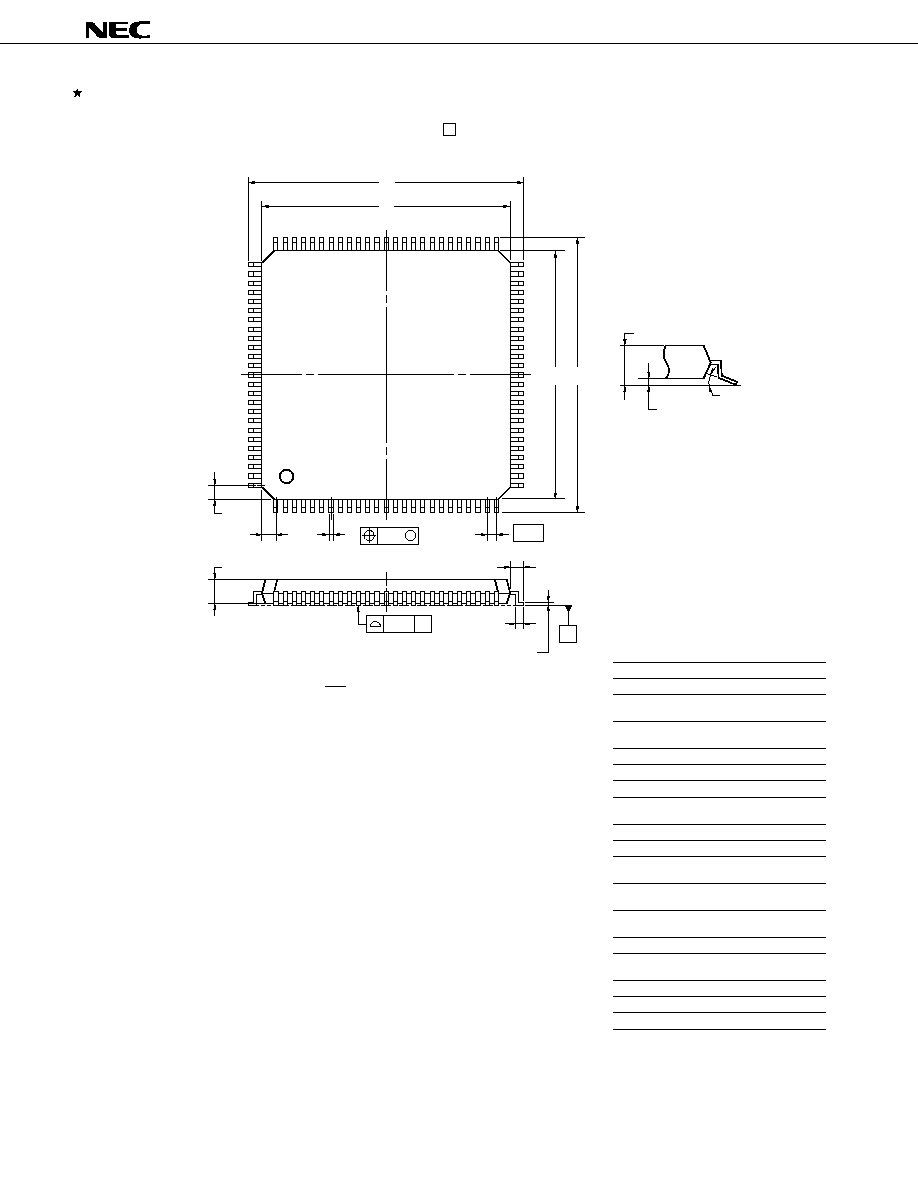

PIN CONFIGURATION

∑ 100-Pin Plastic QFP (fine pitch) (14

◊

14 mm)

µ

PD703003GC-25-xxx-7EA

µ

PD703003GC-33-xxx-7EA

Caution

Connect the IC pin directly to V

SS

.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

P75/ANI5

P74/ANI4

P73/ANI3

P72/ANI2

P71/ANI1

P70/ANI0

ANO0

ANO1

AV

REF2

AV

REF3

P07/INTP113/ADTRG

P06/INTP112

P05/INTP111

P04/INTP110

P03/TI11

P02/TCLR11

P01/TO111

P00/TO110

P117/INTP143

P116/INTP142

P115/INTP141

P114/INTP140

P113/TI14

P112/TCLR14

P111/TO141

P31/TO131

P32/TCLR13

P33/TI13

P34/INTP130

P35/INTP131/SO3

P36/INTP132/SI3

P37/INTP133/SCK3

P63/A19

P62/A18

P61/A17

P60/A16

V

SS

V

DD

P57/AD15

P56/AD14

P55/AD13

P54/AD12

P53/AD11

P52/AD10

P51/AD9

P50/AD8

P47/AD7

P46/AD6

P45/AD5

P44/AD4

P43/AD3

P42/AD2

V

SS

V

DD

P41/AD1

P40/AD0

P90/LBEN

P91/UBEN

P92/R/W

P93/DSTB

P94/ASTB

P95/HLDAK

P96/HLDRQ

WAIT

IC

MODE

RESET

CV

DD

/CKSEL

X2

X1

CV

SS

CLKOUT

V

SS

V

DD

P110/TO140

P30/TO130

P27/SCK1

P26/RXD1/SI1

P25/TXD1/SO1

P24/SCK0

P23/RXD0/SI0

P22/TXD0/SO0

P21/PWM1

P20/PWM0

NMI

V

DD

V

SS

P17/INTP123/SCK2

P16/INTP122/SI2

P15/INTP121/SO2

P14/INTP120

P13/TI12

P12/TCLR12

P11/TO121

P10/TO120

AV

DD

AV

SS

AV

REF1

P77/ANI7

P76/ANI6

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

3

µ

PD703003

Data Sheet U12261EJ2V1DS00

PIN NAMES

A16 to A19

: Address Bus

P30 to P37

: Port3

AD0 to AD15

: Address/Data Bus

P40 to P47

: Port4

ADTRG

: AD Trigger Input

P50 to P57

: Port5

ANI0 to ANI7

: Analog Input

P60 to P63

: Port6

ANO0, ANO1

: Analog Output

P70 to P77

: Port7

ASTB

: Address Strobe

P90 to P96

: Port9

AV

DD

: Analog V

DD

P110 to P117

: Port11

AV

REF1

to AV

REF3

: Analog Reference Voltage

PWM0, PWM1

: Pulse Width Modulation

AV

SS

: Analog V

SS

RESET

: Reset

CV

DD

: Power Supply for Clock Generator

R/W

: Read/Write Status

CV

SS

: Ground for Clock Generator

RXD0, RXD1

: Receive Data

CKSEL

: Clock Select

SCK0 to SCK3

: Serial Clock

CLKOUT

: Clock Output

SI0 to SI3

: Serial Input

DSTB

: Data Strobe

SO0 to SO3

: Serial Output

HLDAK

: Hold Acknowledge

TO110, TO111,

: Timer Output

HLDRQ

: Hold Request

TO120, TO121,

IC

: Internally Connected

TO130, TO131,

INTP110 to INTP113, : Interrupt Request from Peripherals

TO140, TO141

INTP120 to INTP123,

TCLR11 to TCLR14 : Timer Clear

INTP130 to INTP133,

TI11 to TI14

: Timer Input

INTP140 to INTP143

TXD0, TXD1

: Transmit Data

LBEN

: Lower Byte Enable

UBEN

: Upper Byte Enable

MODE

: Mode

WAIT

: Wait

NMI

: Non-maskable Interrupt Request

X1, X2

: Crystal

P00 to P07

: Port0

V

DD

: Power Supply

P10 to P17

: Port1

V

SS

: Ground

P20 to P27

: Port2

µ

PD703003

4

Data Sheet U12261EJ2V1DS00

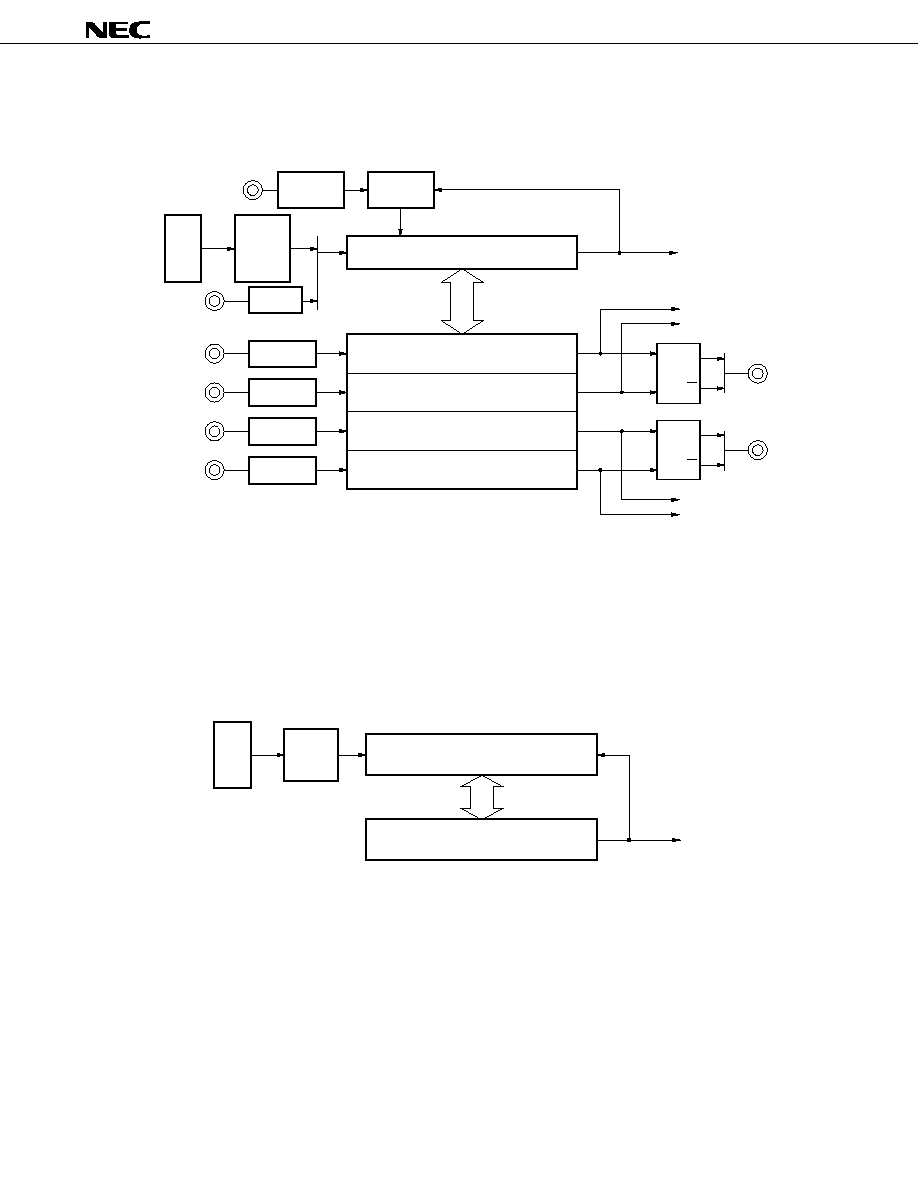

INTERNAL BLOCK DIAGRAM

NMI

TO110, TO111

TO120, TO121

TO130, TO131

TO140, TO141

INTP110 to INTP113

INTP120 to INTP123

INTP130 to INTP133

INTP140 to INTP143

TCLR11 to TCLR14

TI11 to TI14

INTC

RPU

SIO

Mask ROM

RAM

4

Kbytes

128

Kbytes

CPU

PC

32-bit

barrel shifter

System

register

General

register

32 bits

◊

32

ALU

Multiplier

16

◊

16

32

Port

P110 to P117

P90 to P96

P70 to P77

P60 to P63

P50 to P57

P40 to P47

P30 to P37

P20 to P27

P10 to P17

P00 to P07

CG

BCU

Instruction

queue

ASTB

DSTB

R/W

UBEN

LBEN

WAIT

A16 to A19

AD0 to AD15

HLDRQ

HLDAK

CLKOUT

X1

X2

MODE

RESET

UART0/CSI0

BRG0

UART1/CSI1

BRG1

CSI2

BRG2

CSI3

PWM

SO0/TXD0

SI0/RXD0

SCK0

SO1/TXD1

SI1/RXD1

SCK1

SO2

SI2

SCK2

SO3

SI3

SCK3

PWM0, PWM1

A/D

converter

ANI0 to ANI7

AV

REF1

AV

SS

AV

DD

ADTRG

D/A

converter

ANO0, ANO1

AV

REF2

, AV

REF3

V

DD

V

SS

CV

DD

CV

SS

CKSEL

5

µ

PD703003

Data Sheet U12261EJ2V1DS00

CONTENTS

1.

DIFFERENCES AMONG PRODUCTS ...........................................................................................

6

2.

LIST OF PIN FUNCTIONS ...............................................................................................................

7

2.1

Port Pins ................................................................................................................................................

7

2.2

Non-port Pins ........................................................................................................................................

9

2.3

I/O Circuits of Pins and Processing of Unused Pins .........................................................................

11

3.

FUNCTION BLOCKS .......................................................................................................................

14

3.1

Internal Units .........................................................................................................................................

14

4.

CPU FUNCTIONS ............................................................................................................................

16

5.

BUS CONTROL FUNCTIONS .........................................................................................................

17

6.

INTERRUPT/EXCEPTION HANDLING FUNCTIONS .....................................................................

18

7.

CLOCK GENERATION FUNCTIONS ..............................................................................................

21

8.

TIMER/COUNTER FUNCTIONS (REAL-TIME PULSE UNIT) ........................................................

22

9.

SERIAL INTERFACE FUNCTIONS (SIO) .......................................................................................

24

9.1

Asynchronous Serial Interface 0, 1 (UART0, UART1) ........................................................................

24

9.2

Clock-synchronized Serial Interface 0 to 3 (CSI0 to CSI3) ................................................................

26

9.3

Baud Rate Generator 0 to 2 (BRG0 to BRG2) .....................................................................................

28

10. PWM UNIT .......................................................................................................................................

29

11. A/D CONVERTER ............................................................................................................................

30

12. D/A CONVERTER ............................................................................................................................

31

13. PORT FUNCTIONS ..........................................................................................................................

32

14. RESET FUNCTIONS ........................................................................................................................

45

15. INSTRUCTION SET .........................................................................................................................

46

16. ELECTRICAL SPECIFICATIONS ....................................................................................................

53

17. PACKAGE DRAWINGS ...................................................................................................................

77

18. RECOMMENDED SOLDERING CONDITIONS ...............................................................................

78

µ

PD703003

6

Data Sheet U12261EJ2V1DS00

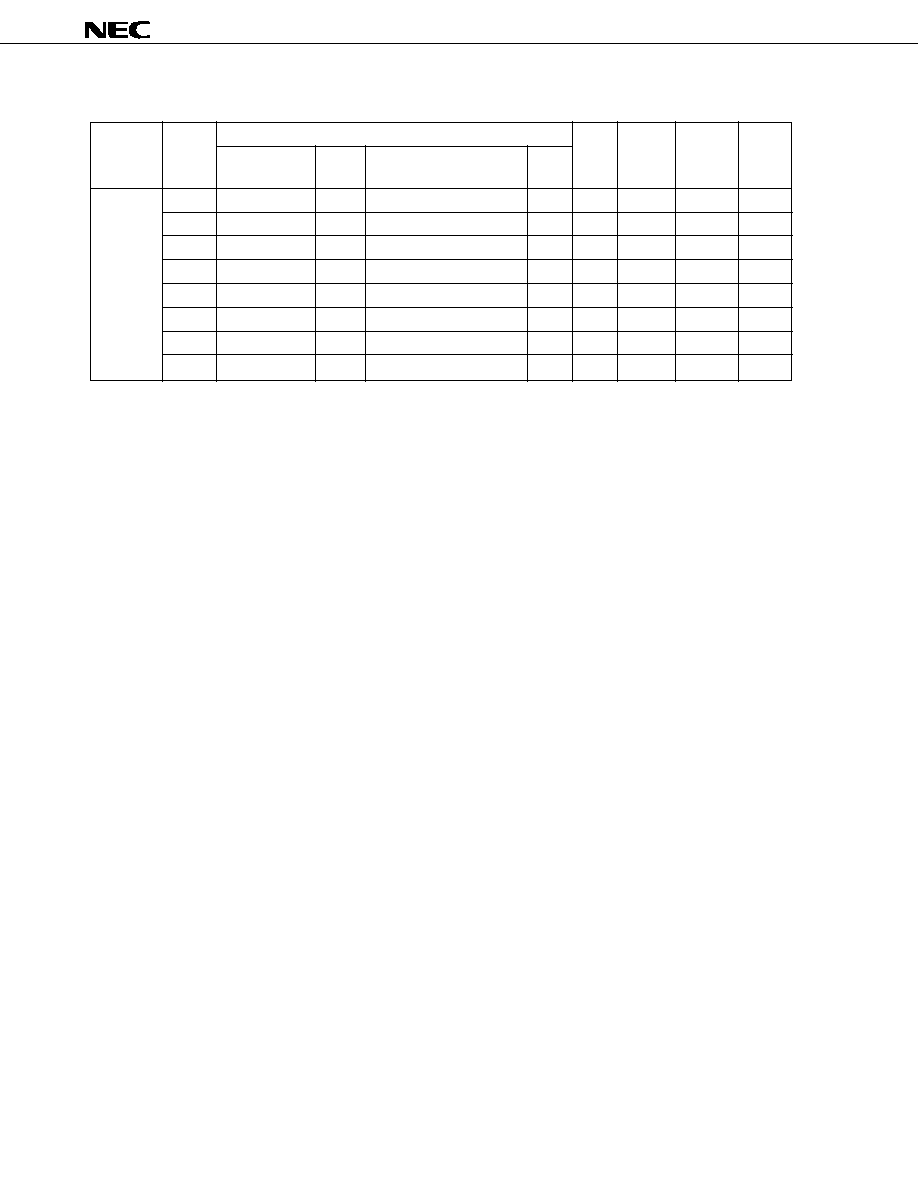

1. DIFFERENCES AMONG PRODUCTS

Item

µ

PD703003

µ

PD703003A

µ

PD703004A

µ

PD703025A

µ

PD70F3003

µ

PD70F3003A

µ

PD70F3025A

Internal ROM

Mask ROM

Flash memory

128 Kbytes

96 Kbytes

256 Kbytes 128 Kbytes

256 Kbytes

Internal RAM

4 Kbytes

8 Kbytes

4 Kbytes

8 Kbytes

Operation Normal

Single-chip Implemented

mode

operation

mode

mode

ROM-less

Implemented Not implemented

Implemented Not implemented

mode

Flash memory

Not implemented

Implemented

programming mode

V

PP

pin

Not implemented

Implemented

Value of CKC register when reset 00H

MODE = 0 : 03H

00H

MODE = 0 : 03H

MODE = 1 : 00H

MODE = 1 : 00H

Electrical specifications

Power consumption levels vary (see specific product's data sheet).

Others

Noise tolerance and noise emission vary, depending on the circuit scale and mask layout.

7

µ

PD703003

Data Sheet U12261EJ2V1DS00

2. LIST OF PIN FUNCTIONS

2.1 Port Pins

(1/2)

Pin Name

I/O

Function

Alternate Function Pin

P00

I/O

Port 0

TO110

P01

8-bit I/O port

TO111

P02

Input/output mode can be specified bitwise

TCLR11

P03

TI11

P04

INTP110

P05

INTP111

P06

INTP112

P07

INTP113/ADTRG

P10

I/O

Port 1

TO120

P11

8-bit I/O port

TO121

P12

Input/output mode can be specified bitwise

TCLR12

P13

TI12

P14

INTP120

P15

INTP121/SO2

P16

INTP122/SI2

P17

INTP123/SCK2

P20

I/O

Port 2

PWM0

P21

8-bit I/O port

PWM1

P22

Input/output mode can be specified bitwise

TXD0/SO0

P23

RXD0/SI0

P24

SCK0

P25

TXD1/SO1

P26

RXD1/SI1

P27

SCK1

P30

I/O

Port 3

TO130

P31

8-bit I/O port

TO131

P32

Input/output mode can be specified bitwise

TCLR13

P33

TI13

P34

INTP130

P35

INTP131/SO3

P36

INTP132/SI3

P37

INTP133/SCK3

P40 to P47

I/O

Port 4

AD0 to AD7

8-bit I/O port

Input/output mode can be specified bitwise

P50 to P57

I/O

Port 5

AD8 to AD15

8-bit I/O port

Input/output mode can be specified bitwise

µ

PD703003

8

Data Sheet U12261EJ2V1DS00

(2/2)

Pin Name

I/O

Function

Alternate Function Pin

P60 to P63

I/O

Port 6

A16 to A19

4-bit I/O port

Input/output mode can be specified bitwise

P70 to P77

Input

Port 7

ANI0 to ANI7

8-bit input port

P90

I/O

Port 9

LBEN

P91

7-bit I/O port

UBEN

P92

Input/output mode can be specified bitwise

R/W

P93

DSTB

P94

ASTB

P95

HLDAK

P96

HLDRQ

P110

I/O

Port 11

TO140

P111

8-bit I/O port

TO141

P112

Input/output mode can be specified bitwise

TCLR14

P113

TI14

P114

INTP140

P115

INTP141

P116

INTP142

P117

INTP143

9

µ

PD703003

Data Sheet U12261EJ2V1DS00

2.2 Non-port Pins

(1/2)

Pin Name

I/O

Function

Alternate Function Pin

TO110

Output

Pulse signal output from timers 11 to 14

P00

TO111

P01

TO120

P10

TO121

P11

TO130

P30

TO131

P31

TO140

P110

TO141

P111

TCLR11

Input

External clear signal input for timers 11 to 14

P02

TCLR12

P12

TCLR13

P32

TCLR14

P112

TI11

Input

External count clock input for timers 11 to 14

P03

TI12

P13

TI13

P33

TI14

P113

INTP110

Input

External maskable interrupt request input,

P04

INTP111

shared as external capture trigger input for timer 11

P05

INTP112

P06

INTP113

P07/ADTRG

INTP120

Input

External maskable interrupt request input,

P14

INTP121

shared as external capture trigger input for timer 12

P15/SO2

INTP122

P16/SI2

INTP123

P17/SCK2

INTP130

Input

External maskable interrupt request input,

P34

INTP131

shared as external capture trigger input for timer 13

P35/SO3

INTP132

P36/SI3

INTP133

P37/SCK3

INTP140

Input

External maskable interrupt request input,

P114

INTP141

shared as external capture trigger input for timer 14

P115

INTP142

P116

INTP143

P117

SO0

Output

Serial transmit data output (3-wire) for CSI0 to CSI3

P22/TXD0

SO1

P25/TXD1

SO2

P15/INTP121

SO3

P35/INTP131

SI0

Input

Serial receive data input (3-wire) for CSI0 to CSI3

P23/RXD0

SI1

P26/RXD1

SI2

P16/INTP122

SI3

P36/INTP132

µ

PD703003

10

Data Sheet U12261EJ2V1DS00

(2/2)

Pin Name

I/O

Function

Alternate Function Pin

SCK0

I/O

Serial clock I/O (3-wire) for CSI0 to CSI3

P24

SCK1

P27

SCK2

P17/INTP123

SCK3

P37/INTP133

TXD0

Output

Serial transmit data output for UART0 and UART1

P22/SO0

TXD1

P25/SO1

RXD0

Input

Serial receive data input for UART0 and UART1

P23/SI0

RXD1

P26/SI1

PWM0

Output

PWM pulse signal output

P20

PWM1

P21

AD0 to AD7

I/O

16-bit multiplexed address/data bus for external memory expansion

P40 to P47

AD8 to AD15

P50 to P57

A16 to A19

Output

High-order address bus used for external memory expansion

P60 to P63

LBEN

Output

External data bus's low-order byte enable signal output

P90

UBEN

External data bus's high-order byte enable signal output

P91

R/W

Output

External read/write status output

P92

DSTB

External data strobe signal output

P93

ASTB

External address strobe signal output

P94

HLDAK

Output

Bus hold acknowledge output

P95

HLDRQ

Input

Bus hold request input

P96

ANI0 to ANI7

Input

Analog input to A/D converter

P70 to P77

ANO0, ANO1

Output

Analog output to D/A converter

--

NMI

Input

Nonmaskable interrupt request input

--

CLKOUT

Output

System clock output

--

CKSEL

Input

Input for specifying clock generator's operation mode

CV

DD

WAIT

Input

Control signal input for inserting wait in bus cycle

--

MODE

Input

Operation mode select

--

RESET

Input

System reset input

--

X1

Input

Oscillator connection for system clock. Input is via X1 when using an

--

X2

--

external clock.

--

ADTRG

Input

A/D converter external trigger input

P07/INTP113

AV

REF1

Input

Reference voltage input for A/D converter

--

AV

REF2

Input

Reference voltage input for D/A converter

--

AV

REF3

--

AV

DD

--

Positive power supply for A/D converter

--

AV

SS

--

Ground potential for A/D converter

--

CV

DD

--

Positive power supply for on-chip clock generator

CKSEL

CV

SS

--

Ground potential for on-chip clock generator

--

V

DD

--

Positive power supply

--

V

SS

--

Ground potential

--

IC

--

Internally connected pin (connect directly to V

SS

)

--

11

µ

PD703003

Data Sheet U12261EJ2V1DS00

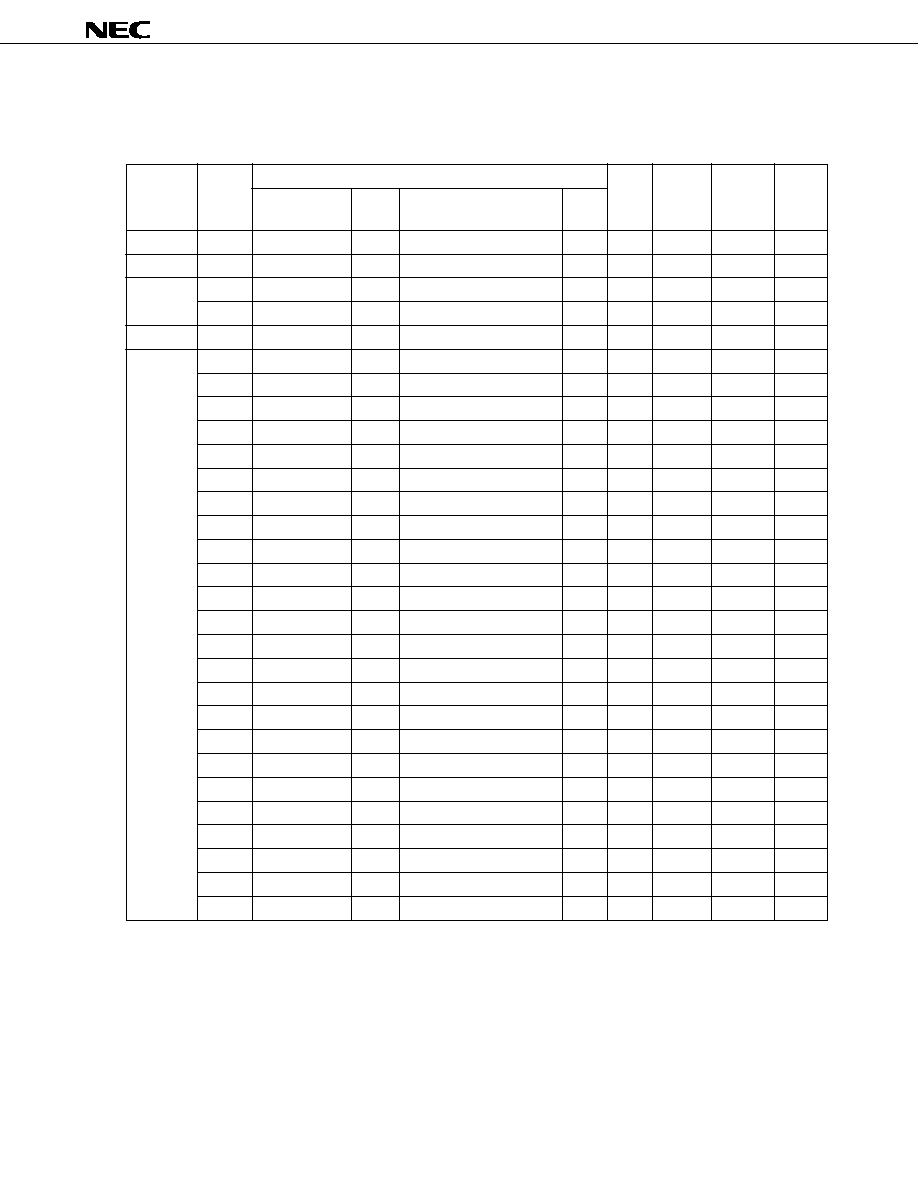

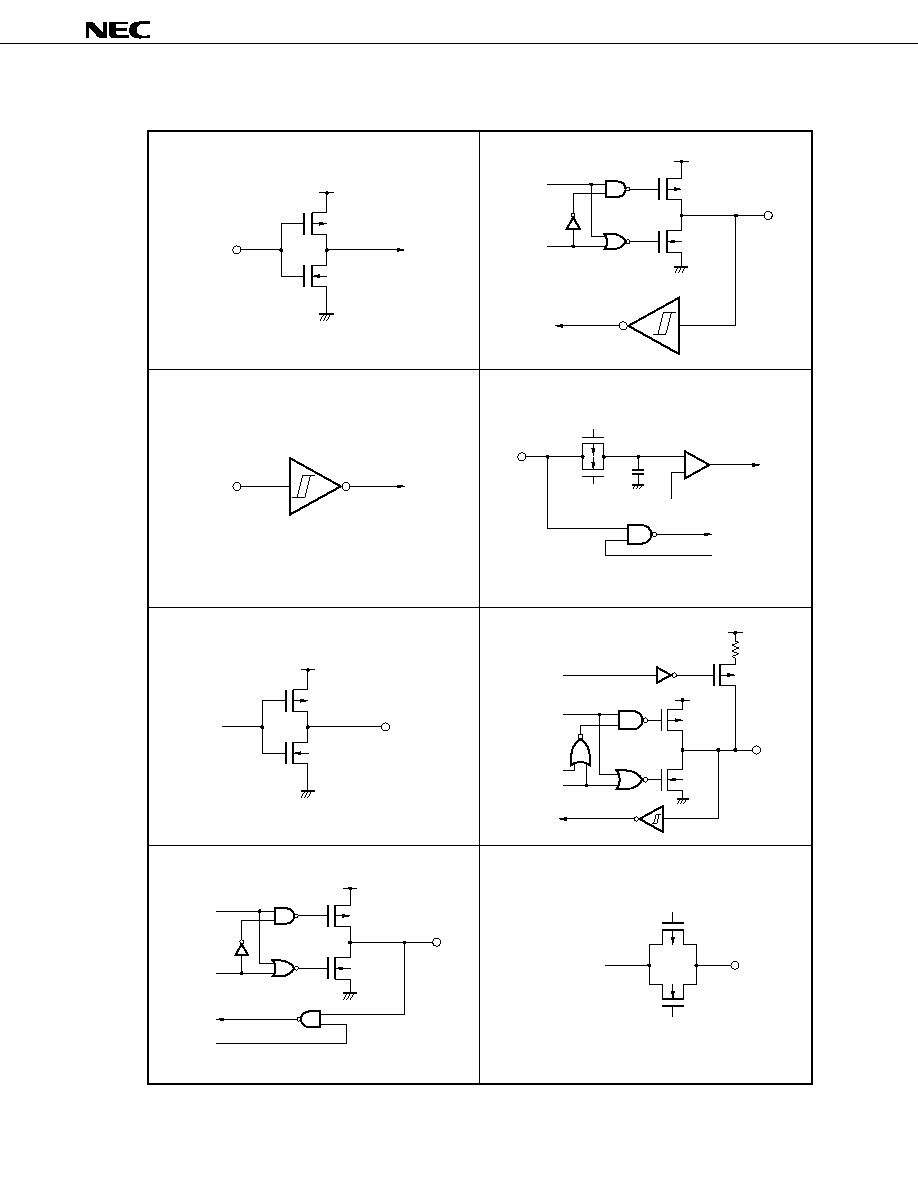

2.3 I/O Circuits of Pins and Processing of Unused Pins

Table 2-1 lists I/O circuit type of respective pins and processing method (recommended connection method) when

not used. Figure 2-1 illustrates the various circuit types using partially abridged diagrams.

When connecting to V

DD

or V

SS

via a resistor, a resistance value in the range of 1 to 10 k

is recommended.

Table 2-1. I/O Circuits of Pins and Processing of Unused Pins (1/2)

Pin

I/O Circuit Type

Recommended Connection Method

P00/TO110, P01/TO111

5

Input: Connect to V

DD

or V

SS

separately via a resistor

P02/TCLR11, P03/TI11,

8

Output: Leave open

P04/INTP110 to P07/INTP113/ADTRG

P10/TO120, P11/TO121

5

P12/TCLR12, P13/TI12

8

P14/INTP120

P15/INTP121/SO2

P16/INTP122/SI2

P17/INTP123/SCK2

P20/PWM0, P21/PWM1

5

P22/TXD0/SO0

P23/RXD0/SI0, P24/SCK0

8

P25/TXD1/SO1

5

P26/RXD1/SI1, P27/SCK1

8

P30/TO130, P31/TO131

5

P32/TCLR13, P33/TI13

8

P34/INTP130

P35/INTP131/SO3

10-A

P36/INTP132/SI3

P37/INTP133/SCK3

P40/AD0 to P47/AD7

5

P50/AD8 to P57/AD15

P60/A16 to P63/A19

P70/ANI0 to P77/ANI7

9

Connect directly to V

SS

P90/LBEN

5

Input: Connect to V

DD

or V

SS

separately via a resistor

P91/UBEN

Output: Leave open

P92/R/W

P93/DSTB

P94/ASTB

P95/HLDAK

P96/HLDRQ

P110/TO140, P111/TO141

P112/TCLR14, P113/TI14

8

P114/INTP140 to P117/INTP143

ANO0, ANO1

12

Leave open

NMI

2

Connect directly to V

SS

µ

PD703003

12

Data Sheet U12261EJ2V1DS00

Table 2-1. I/O Circuits of Pins and Processing of Unused Pins (2/2)

Pin

I/O Circuit Type

Recommended Connection Method

CLKOUT

3

Leave open

WAIT

1

Connect directly to V

DD

MODE

2

--

RESET

CV

DD

/CKSEL

AV

REF1

to AV

REF3

, AV

SS

--

Connect directly to V

SS

AV

DD

--

Connect directly to V

DD

IC

--

Connect directly to V

SS

13

µ

PD703003

Data Sheet U12261EJ2V1DS00

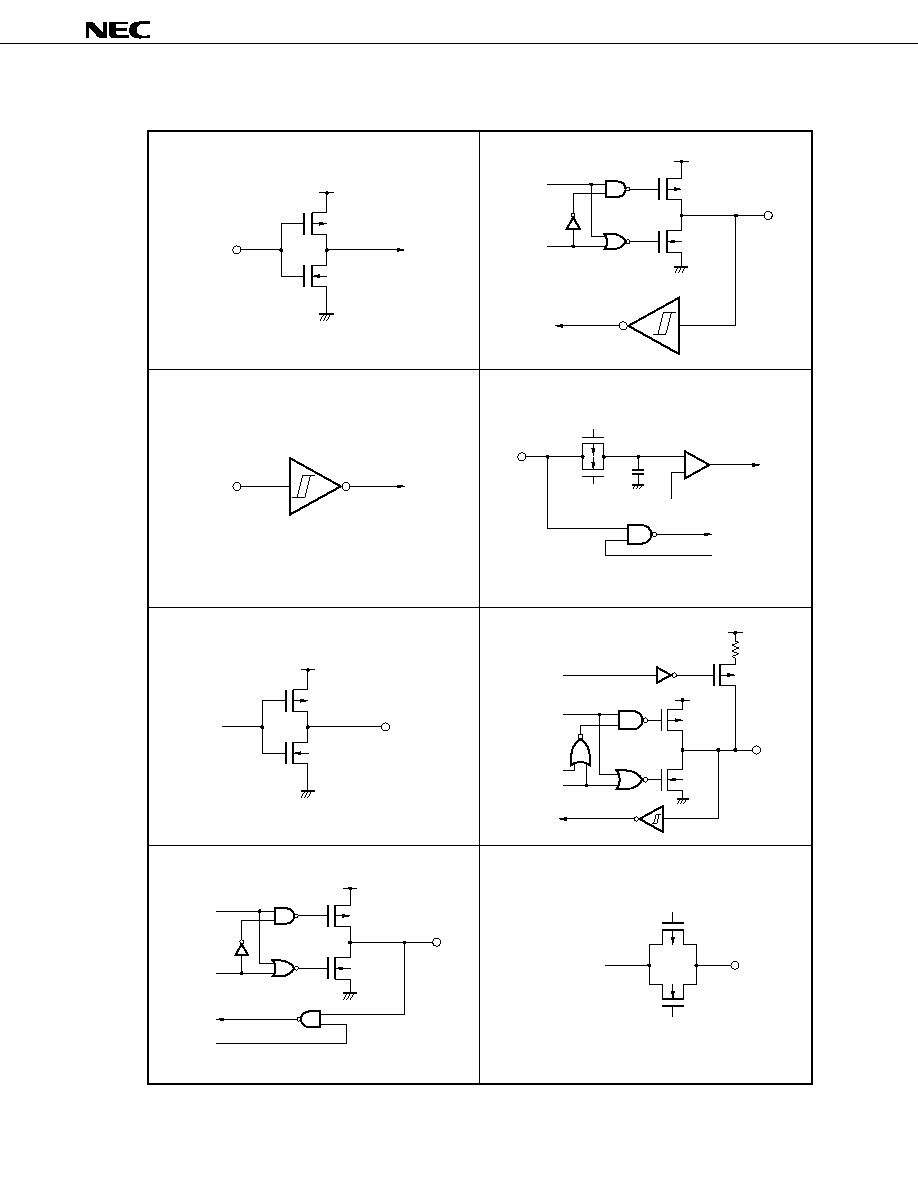

Figure 2-1. I/O Circuits of Pins

Type 1

Type 2

Type 8

Type 3

P-ch

N-ch

IN

V

DD

IN

Schmitt trigger input with hysteresis characteristics

P-ch

N-ch

V

DD

OUT

P-ch

N-ch

V

DD

IN/OUT

Data

Output

disable

Type 5

P-ch

N-ch

V

DD

IN/OUT

Data

Output

disable

Input

enable

IN

Comparator

+

≠

V

REF

(threshold voltage)

P-ch

N-ch

Input enable

Type 9

Data

output disable

P-ch

IN/OUT

V

DD

N-ch

P-ch

V

DD

Pull-up

enable

Open-drain

Type 10-A

OUT

P-ch

N-ch

Analog output voltage

Type 12

µ

PD703003

14

Data Sheet U12261EJ2V1DS00

3. FUNCTION BLOCKS

3.1 Internal Units

3.1.1 CPU

The CPU uses five-stage pipeline control to enable single-clock execution of address calculations, arithmetic logic

operations, data transfers, and almost all other instruction processing.

Other dedicated on-chip hardware, such as the multiplier (16 bits

◊

16 bits) and the barrel shifter (32 bits) help

accelerate processing of complex instructions.

3.1.2 Bus control unit (BCU)

The BCU starts a required bus cycle based on the physical address obtained by the CPU. When an instruction

is fetched from external memory space and the CPU does not send a bus cycle start request, the BCU generates a

prefetch address and prefetches the instruction code. The prefetched instruction code is stored in a prefetch queue.

3.1.3 ROM

ROM is mapped to the address space starting at 00000000H. The MODE pin can be used to select an access

enable/disable setting. ROM can be accessed by the CPU in one clock cycle when an instruction is fetched.

3.1.4 RAM

RAM is mapped to the address space starting at FFFFE000H. RAM can be accessed by the CPU in one clock

cycle when data accessed.

3.1.5 Ports

In addition to the 75 pins (port 0 to port 11) comprising I/O ports (of which eight pins comprise an input-only port),

various port pin and control pin functions can be selected for these pins.

3.1.6 Interrupt controller (INTC)

This controller handles hardware interrupt requests (NMI, INTP110 to INTP113, INTP120 to INTP123, INTP130

to INTP133, and INTP140 to INTP143) from on-chip peripheral hardware and external hardware. Eight interrupt

priority levels can be specified for these interrupt requests, and multiplexed servicing control can be performed for

interrupt sources.

3.1.7 Clock generator (CG)

An on-chip PLL enables the CPU operating clock to be supplied to resonators connected to pins X1 and X2 at 5

◊

frequency, 1

◊

frequency, and 1/2

◊

frequency. It can also be connected to an external clock instead of to the resonator.

3.1.8 Real-time pulse unit (RPU)

The RPU includes a four-channel 16-bit timer/event counter and a one-channel 16-bit interval timer, which enables

measurement of pulse intervals and frequency as well as programmable pulse output.

15

µ

PD703003

Data Sheet U12261EJ2V1DS00

3.1.9 Serial interface (SIO)

Four channels are comprised of two kinds of serial interfaces: an asynchronous serial interface (UART) and a clock-

synchronized serial interface (CSI). Two of these four channels are switchable between the UART and CSI and the

other two channels are fixed as CSI.

For UART, data is transferred via the TXD and RXD pins. The baud rate is determined by the on-chip baud rate

generator. For CSI, data is transferred via the SO, SI, and SCK pins. The baud rate can be determined by the on-

chip baud rate generator or it can be supplied from an external source.

One of the two CSI-fixed channels is used as the serial clock output, and serial output is sent via an N-ch open

drain output.

3.1.10 Pulse width modulation (PWM)

There are two channels of selectable 8/9/10/12-bit resolution PWM signal outputs. When a low pass filter is

externally connected, PWM output can be used as D/A converter output. This is suitable for actuator control

applications, such as in motors.

3.1.11 A/D converter (ADC)

This is a high-speed, high-resolution 10-bit A/D converter that includes eight analog input pins. It converts using

the sequential conversion method.

3.1.12 D/A converter (DAC)

This is an 8-bit resolution D/A converter that includes two channels. It converts using the R-2R conversion method.

µ

PD703003

16

Data Sheet U12261EJ2V1DS00

4. CPU FUNCTIONS

The CPU employs a RISC-based architecture and uses five-stage pipeline control to enable single-clock execution

of almost all instructions.

The features of the CPU functions are shown below.

∑ Minimum instruction execution time

30 ns (during internal 33-MHz operation)

∑ Address space: 16-Mbyte linear

∑ General registers: 32 bits

◊

32 registers

∑ Internal 32-bit architecture

∑ 5-stage pipeline control

∑ Multiply/divide instructions

∑ Saturated operation instructions

∑ 32-bit shift instruction: 1 clock

∑ Long/short format

∑ Four types of bit manipulation instructions

∑ Set

∑ Clear

∑ Not

∑ Test

17

µ

PD703003

Data Sheet U12261EJ2V1DS00

5. BUS CONTROL FUNCTIONS

The features of the bus control functions are shown below.

∑ Shared as port pins, connectable to external device

∑ Wait functions

∑ Programmable wait function for up to three states per two blocks

∑ External wait function using WAIT pin

∑ Idle state insertion function

∑ Bus mastering arbitration function

∑ Bus hold function

µ

PD703003

18

Data Sheet U12261EJ2V1DS00

6. INTERRUPT/EXCEPTION HANDLING FUNCTIONS

The features of the interrupt/exception handling functions are shown below.

∑ Interrupts

∑ Nonmaskable interrupt: 1 source

∑ Maskable interrupt: 32 sources

∑ 8-level programmable priority control

∑ Multiple interrupt control based on priority levels

∑ Mask specification for each maskable interrupt request

∑ Noise elimination, edge detection, and valid edge specification for external interrupt requests

∑ Exceptions

∑ Software exceptions: 32 sources

∑ Exception trap: 1 source (invalid instruction code exception)

The configuration of the interrupt/exception handling functions is shown below.

Figure 6-1. Block Diagram of Maskable Interrupt

RPU

Selector

3

210

3

210

3

2103

210

3

210

32

10

32

1032

1032

10

3

210

3

2103

210

INTM1

INTM2

INTM3

INTM4

SIO

INTCSI0

INTOV11

Internal bus

XXMKn (interrupt mask flag)

ISPR

Handler

address

generator

CPU

PSW

ID

Interrupt

request

Interrupt

request

acknowledge

HALT mode

release signal

XXPRn (priority controller)

7

0

OVIF11

OVIF12

OVIF13

OVIF14

P11IF0

P11IF1

P11IF2

P11IF3

P12IF0

P12IF1

P12IF2

P12IF3

P13IF0

P13IF1

P13IF2

P13IF3

P14IF0

P14IF1

P14IF2

P14IF3

CSIF0

CSIF1

CSIF2

CSIF3

SEIF0

SRIF0

STIF0

SEIF1

SRIF1

STIF1

ADIF

CMIF4

INTOV12

INTOV13

INTOV14

INTP110/INTCC110

INTP111/INTCC111

INTP112/INTCC112

INTP113/INTCC113

INTP120/INTCC120

INTP121/INTCC121

INTP122/INTCC122

INTP123/INTCC123

INTP130/INTCC130

INTP131/INTCC131

INTP132/INTCC132

INTP133/INTCC133

INTP140/INTCC140

INTP141/INTCC141

INTP142/INTCC142

INTP143/INTCC143

INTCM4

INTAD

INTCSI1

INTCSI2

INTCSI3

INTSER0

INTSR0

INTST0

INTSER1

INTSR1

INTST1

A/D converter

INTP110

INTP111

INTP112

INTP113

INTP120

INTP121

INTP122

INTP123

INTP130

INTP131

INTP132

INTP133

INTP140

INTP141

INTP142

INTP143

XX: Name of peripheral unit (OV, P11 to P14, CM, CS, SE, SR, ST, AD)

n: Peripheral unit number (if none exists, then 0 to 4 or 11 to 14)

19

µ

PD703003

Data Sheet U12261EJ2V1DS00

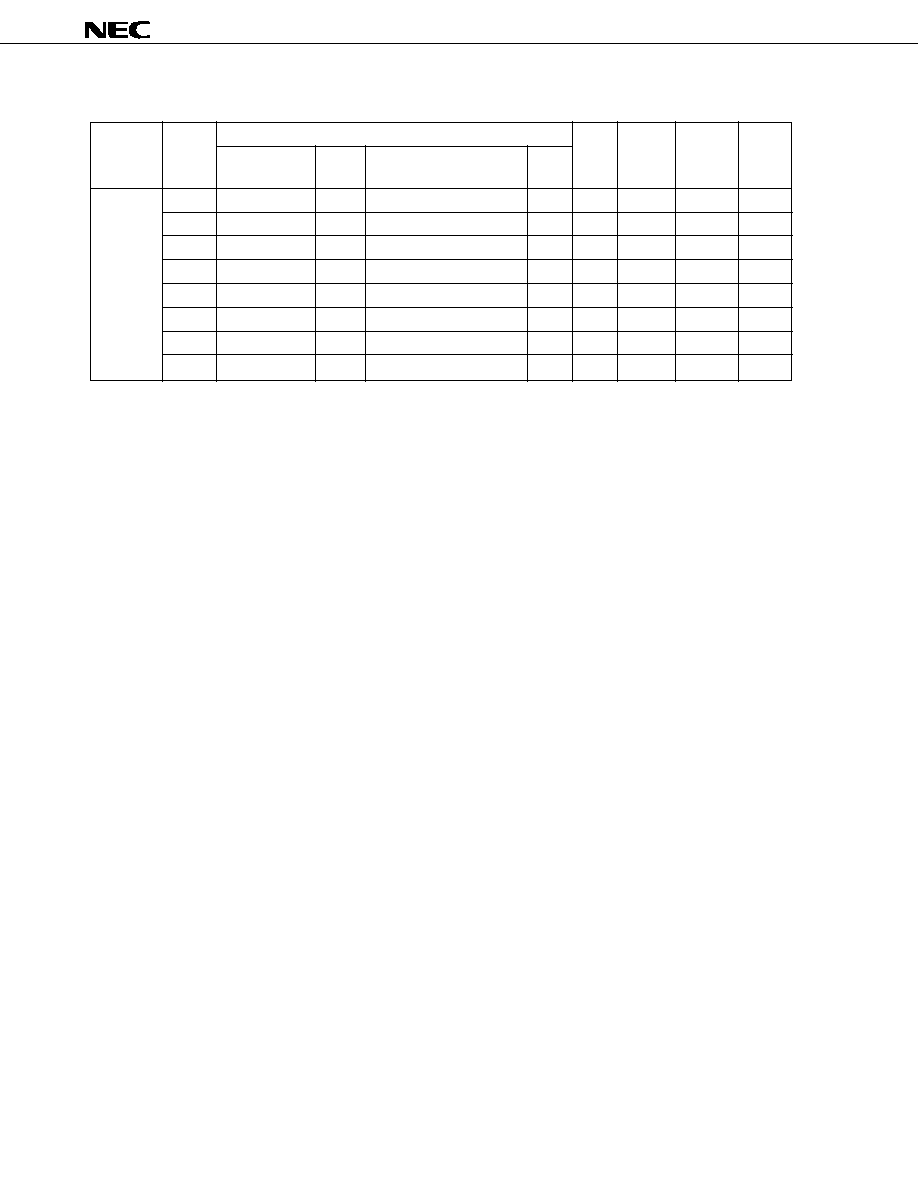

Interrupt/exception sources are shown in Table 6-1.

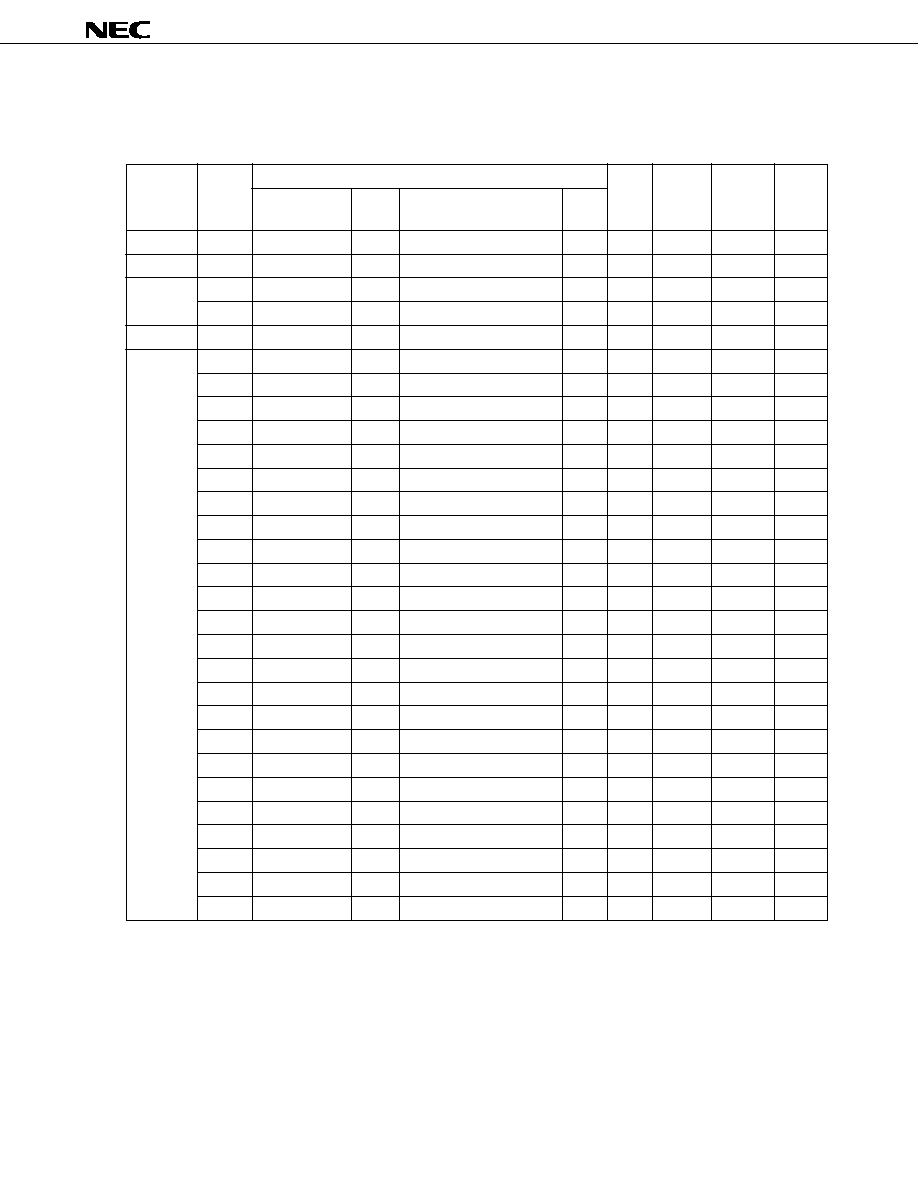

Table 6-1. List of Interrupts (1/2)

Interrupt/Exception Source

Default

Exception

Handler

Restored

Type

Category

Name

Control

Trigger Source

Unit

Priority

Register

Level

Code

Address

PC

Reset

Interrupt

RESET

--

Reset input

--

--

0000H

00000000H

Undefined

Nonmaskable

Interrupt

NMI

--

NMI input

--

--

0010H

00000010H

nextPC

Software

Exception TRAP0n

Note

--

TRAP instruction

--

--

004nH

Note

00000040H

nextPC

exception

Exception TRAP1n

Note

--

TRAP instruction

--

--

005nH

Note

00000050H

nextPC

Exception trap

Exception ILGOP

--

Undefined instruction code

--

--

0060H

00000060H

nextPC

Maskable

Interrupt

INTOV11

OVIC11 Timer 11 overflow

RPU

0

0080H

00000080H

nextPC

Interrupt

INTOV12

OVIC12 Timer 12 overflow

RPU

1

0090H

00000090H

nextPC

Interrupt

INTOV13

OVIC13 Timer 13 overflow

RPU

2

00A0H

000000A0H

nextPC

Interrupt

INTOV14

OVIC14 Timer 14 overflow

RPU

3

00B0H

000000B0H

nextPC

Interrupt

INTP110/INTCC110 P11IC0

Match between INTP110 and CC110

Pin/RPU

4

00C0H

000000C0H nextPC

Interrupt

INTP111/INTCC111 P11IC1

Match between INTP111 and CC111

Pin/RPU

5

00D0H

000000D0H nextPC

Interrupt

INTP112/INTCC112 P11IC2

Match between INTP112 and CC112

Pin/RPU

6

00E0H

000000E0H

nextPC

Interrupt

INTP113/INTCC113 P11IC3

Match between INTP113 and CC113

Pin/RPU

7

00F0H

000000F0H

nextPC

Interrupt

INTP120/INTCC120 P12IC0

Match between INTP120 and CC120

Pin/RPU

8

0100H

00000100H

nextPC

Interrupt

INTP121/INTCC121 P12IC1

Match between INTP121 and CC121

Pin/RPU

9

0110H

00000110H

nextPC

Interrupt

INTP122/INTCC122 P12IC2

Match between INTP122 and CC122

Pin/RPU

10

0120H

00000120H

nextPC

Interrupt

INTP123/INTCC123 P12IC3

Match between INTP123 and CC123

Pin/RPU

11

0130H

00000130H

nextPC

Interrupt

INTP130/INTCC130 P13IC0

Match between INTP130 and CC130

Pin/RPU

12

0140H

00000140H

nextPC

Interrupt

INTP131/INTCC131 P13IC1

Match between INTP131 and CC131

Pin/RPU

13

0150H

00000150H

nextPC

Interrupt

INTP132/INTCC132 P13IC2

Match between INTP132 and CC132

Pin/RPU

14

0160H

00000160H

nextPC

Interrupt

INTP133/INTCC133 P13IC3

Match between INTP133 and CC133

Pin/RPU

15

0170H

00000170H

nextPC

Interrupt

INTP140/INTCC140 P14IC0

Match between INTP140 and CC140

Pin/RPU

16

0180H

00000180H

nextPC

Interrupt

INTP141/INTCC141 P14IC1

Match between INTP141 and CC141

Pin/RPU

17

0190H

00000190H

nextPC

Interrupt

INTP142/INTCC142 P14IC2

Match between INTP142 and CC142

Pin/RPU

18

01A0H

000001A0H

nextPC

Interrupt

INTP143/INTCC143 P14IC3

Match between INTP143 and CC143

Pin/RPU

19

01B0H

000001B0H

nextPC

Interrupt

INTCM4

CMIC4

Signal matches CM4

RPU

20

01C0H

000001C0H nextPC

Interrupt

INTCSI0

CSIC0

CSI0 send/receive completion

SIO

21

01D0H

000001D0H nextPC

Interrupt

INTCSI1

CSIC1

CSI1 send/receive completion

SIO

22

01E0H

000001E0H

nextPC

Interrupt

INTCSI2

CSIC2

CSI2 send/receive completion

SIO

23

01F0H

000001F0H

nextPC

Note n represents a value between 0 and FH.

Remarks 1. Default priority: The default priority level is the level that takes precedence when multiple

maskable interrupt requests having the same priority level occur at the same

time. The highest priority level is level 0.

Restored PC: This is the PC value that is saved to EIPC or FEPC when interrupt or exception

handling is activated. However, if an interrupt occurs during execution of the

DIVH (divide) instruction, the recovered PC value is the PC value of the current

instruction (DIVH).

2. The invalid instruction execution address can be obtained (using restored PC-4) when an invalid

instruction code exception occurs.

µ

PD703003

20

Data Sheet U12261EJ2V1DS00

Table 6-1. List of Interrupts (2/2)

Interrupt/Exception Source

Default

Exception

Handler

Restored

Type

Category

Name

Control

Trigger Source

Unit

Priority

Register

Level

Code

Address

PC

Maskable

Interrupt

INTCSI3

CSIC3

CSI3 transmit/receive completion

SIO

24

0200H

00000200H

nextPC

Interrupt

INTSER0

SEIC0

UART0 receive error

SIO

25

0210H

00000210H

nextPC

Interrupt

INTSR0

SRIC0

UART0 receive completion

SIO

26

0220H

00000220H

nextPC

Interrupt

INTST0

STIC0

UART0 transmit completion

SIO

27

0230H

00000230H

nextPC

Interrupt

INTSER1

SEIC1

UART1 receive error

SIO

28

0240H

00000240H

nextPC

Interrupt

INTSR1

SRIC1

UART1 receive completion

SIO

29

0250H

00000250H

nextPC

Interrupt

INTST1

STIC1

UART1 transmit completion

SIO

30

0260H

00000260H

nextPC

Interrupt

INTAD

ADIC

A/D conversion completion

ADC

31

0270H

00000270H

nextPC

Remarks 1. Default priority: The default priority level is the level that takes precedence when multiple

maskable interrupt requests having the same priority level occur at the same

time. The highest priority level is level 0.

Restored PC: This is the PC value that is saved to EIPC or FEPC when interrupt or exception

handling is started. However, if an interrupt occurs during execution of the DIVH

(divide) instruction, the restored PC value is the PC value of the current instruction

(DIVH).

2. The invalid instruction execution address can be obtained using (restored PC-4) when an invalid

instruction code exception occurs.

21

µ

PD703003

Data Sheet U12261EJ2V1DS00

7. CLOCK GENERATION FUNCTIONS

The features of the clock generation functions are shown below.

∑ Multiplier function using PLL clock synthesizer

∑ Clock sources

∑ Oscillation via resonator connection (PLL mode): f

XX

=

, 2

◊

,

/5

∑ External clock (PLL mode): f

XX

=

, 2

◊

,

/5

∑ External clock (direct mode): f

XX

= 2

◊

∑ Power saving control

∑ HALT mode

∑ IDLE mode

∑ Software STOP mode

∑ Clock output inhibit mode

The configuration of the clock generation functions is shown below.

Figure 7-1. Block Diagram of Clock Generation Functions

X1

X2

CKSEL

(f

XX

)

CLKOUT

CPU, On-chip peripheral I/O

Clock generator

Remark

: internal system clock

µ

PD703003

22

Data Sheet U12261EJ2V1DS00

8. TIMER/COUNTER FUNCTIONS (REAL-TIME PULSE UNIT)

The features of the timer/counter functions are shown below.

∑ Measurement of pulse interval and frequency, programmable pulse output

∑ 16-bit measurements enabled

∑ Generates a variety of pulse patterns (interval pulse, one-shot pulse, etc.)

∑ Timer 1

∑ 16-bit timer/event counter

∑ Count clock sources: two types (selection of an internal system clock division, external pulse input)

∑ Capture/compare (shared) registers: 16

∑ Count clear pins: TCLR11 to TCLR14

∑ Interrupt sources: 20 types

∑ External pulse outputs: 8

∑ Timer 4

∑ 16-bit interval timer

∑ Count clock: selected from an internal system clock division

∑ Compare register: 1

∑ Interrupt sources: 1

23

µ

PD703003

Data Sheet U12261EJ2V1DS00

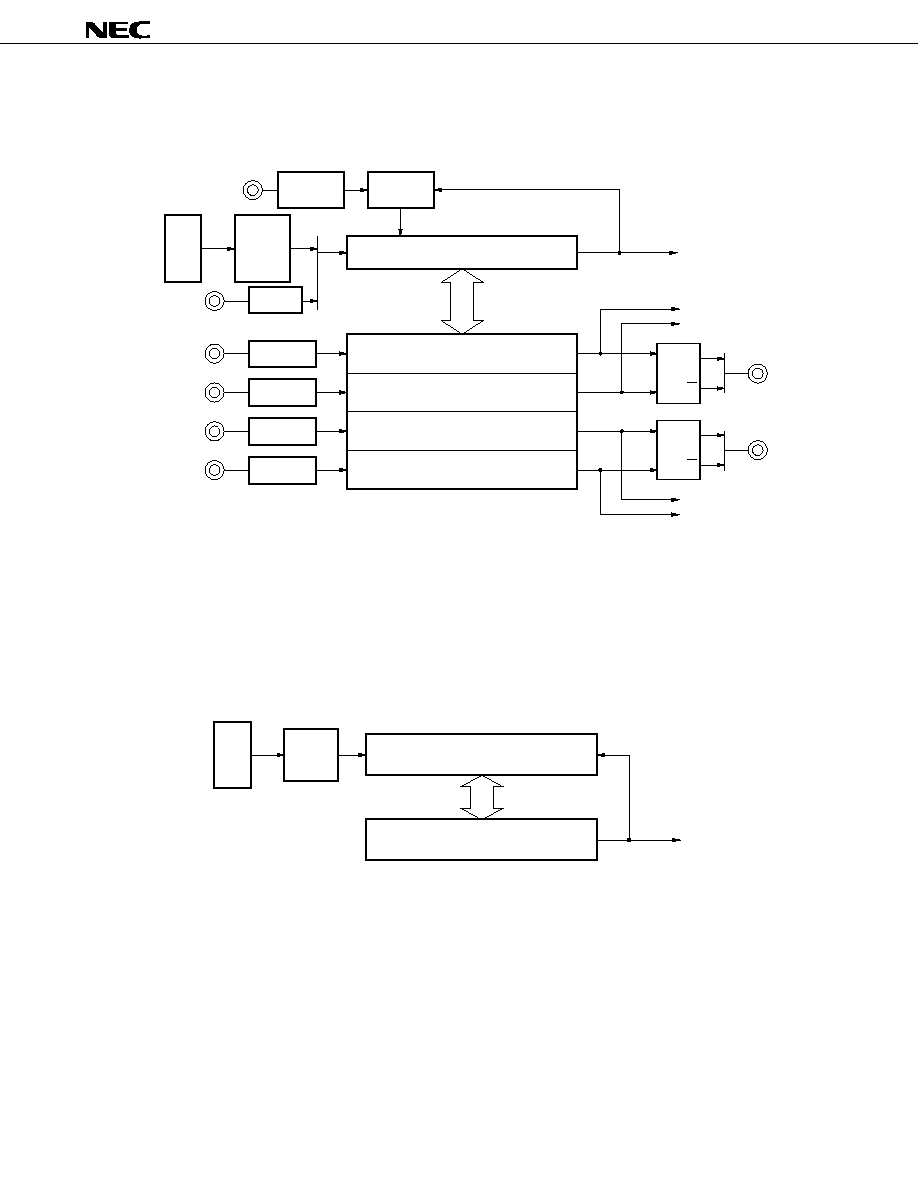

The configurations of the timer/counter functions are shown below.

Figure 8-1. Block Diagram of Timer 1 (16-bit timer/event counter)

Notes 1. Internal count clock

2. External count clock

3. Priority to reset

Remark

: internal system clock

n = 1 to 4

Figure 8-2. Block Diagram of Timer 4 (16-bit interval timer)

Note Internal count clock

Remark

: Internal system clock

m

m/4

m/8

m/32

/2

/4

m

TCLR1n

TI1n

INTP1n0

INTP1n1

INTP1n2

INTP1n3

Note 2

Note 1

Clear and start

TM1n (16 bits)

CC1n0

CC1n1

CC1n2

CC1n3

INTOV1n

INTCC1n0

INTCC1n1

S

R

Note3

Q

Q

S

Q

Q

R

Note3

INTCC1n2

INTCC1n3

TO1n0

TO1n1

Edge

detect

Clear and

start

Edge detect

Edge detect

Edge detect

Edge detect

Edge detect

TM4 (16-bit)

CM4

Clear and start

INTCM4

Note

m

m/32

m

/2

/4

/16

/32

µ

PD703003

24

Data Sheet U12261EJ2V1DS00

9. SERIAL INTERFACE FUNCTIONS (SIO)

Two types and six channels of serial interfaces are provided.

Up to four channels may be used at the same time.

(1) Asynchronous serial interfaces 0, 1 (UART0, UART1): 2 channels

(2) Clock-synchronized serial interfaces 0 to 3 (CSI0 to CSI3): 4 channels

Caution

UART0 and CSI0 are a shared pin, as are UART1 and CSI1. Either one can be selected via a

register (ASIM00, ASIM10).

9.1 Asynchronous Serial Interfaces 0, 1 (UART0, UART1)

The features of the asynchronous serial interfaces 0, 1 (UART0, UART1) are shown below.

∑ Transfer rate

150 bps to 76800 bps (@

= 33-MHz operation, using baud rate generator)

110 bps to 307200 bps (@

= 20-MHz operation, using baud rate generator)

Maximum 1031 Kbytes (@

= 33-MHz operation, using

/2)

∑ Full duplex communications: Receive buffer (RXBn) included

∑ Two-pin configuration

TXDn: output pin for transmit data

RXDn: input pin for receive data

∑ Reception error detection function

∑ Parity error

∑ Framing error

∑ Overrun error

∑ Three types of interrupt sources

∑ Reception error interrupt (INTSERn)

∑ Reception completion interrupt (INTSRn)

∑ Transmission completion interrupt (INTSTn)

∑ The character length of transmit and receive data is specified via the ASIMn0, ASIMn1 register

∑ Character lengths: 7 or 8 bits, or 9 bits (if using expansion bit)

∑ Parity function: even, odd, zero, or no parity

∑ Transmission stop bits: 1 or 2 bits

∑ On-chip baud rate generator

Remark n = 0, 1

: internal system clock

25

µ

PD703003

Data Sheet U12261EJ2V1DS00

The configuration of the asynchronous serial interfaces 0, 1 (UART0, UART1) are shown below.

Figure 9-1. Block Diagram of Asynchronous Serial Interfaces 0, 1 (UART0, UART1)

Internal bus

16/8

Receive

buffer

8

RXBn

RXBnL

Receive

shift register

Transmit

shift register

RXDn

TXDn

Reception

control

parity check

Transmission

control parity

attachment

1

16

INTSRn

INTSERn

PEn FEn OVEn SOTn

ASISn

16/8

TXSn

TXSnL

INTSTn

Selector

1

16

1

2

Baud rate generator

8

8

ASIMn0

ASIMn1

EBSn

RXEn

TXEn

PSn1 PSn0 CLn SLn SCLSn

Remark n = 0, 1

: internal system clock

µ

PD703003

26

Data Sheet U12261EJ2V1DS00

9.2 Clock-synchronized Serial Interfaces 0 to 3 (CSI0 to CSI3)

The features of the clock-synchronized serial interfaces 0 to 3 (CSI0 to CSI3) are shown below.

∑ Number of channels: 4 channels (CSIn)

∑ High-speed transfer

MAX 8.25 Mbps (@

= 33-MHz operation)

∑ Half-duplex communications

∑ Character length uses 8-bit unit

∑ Switchable byte ordering (MSB first or LSB first)

∑ Selectable external serial clock input/internal serial clock output

∑ 3-wire type

SOn: Serial data output

SIn:

Serial data input

SCKn: Serial clock I/O

∑ Interrupt source: 1 type

∑

Transmission/reception completion interrupt (INTCSIn)

Remark n = 0 to 3

: internal system clock

27

µ

PD703003

Data Sheet U12261EJ2V1DS00

The configuration of the clock-synchronized serial interfaces 0 to 3 (CSI0 to CSI3) is shown below.

Figure 9-2. Block Diagram of Clock-synchronized Serial Interfaces 0 to 3 (CSI0 to CSI3)

Note

SO0 to SO2, SCK0 to SCK2: CMOS outputs

SO3, SCK3:

N-ch open-drain outputs

Remark n = 0 to 3

: internal system clock

Internal bus

CTXEn CRXEn CSOTn MODn

CLSn1 CLSn0

CSIMn

SIn

SOn

SCKn

Shift register (SIOn)

SO latch

D

Q

2

1

Serial clock

control circuit

Serial clock

counter

Interrupt

control circuit

INTCSIn

Baud rate generator

/2

Note

Note

Selector

Selector

µ

PD703003

28

Data Sheet U12261EJ2V1DS00

9.3 Baud Rate Generators 0 to 2 (BRG0 to BRG2)

The features of the baud rate generators 0 to 2 (BRG0 to BRG2) are shown below.

∑ Serial clock can be selected via baud rate generator output and

(internal system clock)

∑ Identical baud rates during transmission and reception

The configuration of the baud rate generators 0 to 2 (BRG0 to BRG2) is shown below.

Figure 9-3. Block Diagram of Baud Rate Generators 0 to 2 (BRG0 to BRG2)

Baud rate generator 0

Baud rate generator 1

Baud rate generator 2

Internal bus

1

2

Prescaler

TMBRG0

Clear

BRG0

Match

BPRM0

BRCE0

BPR02

BPR01

BPR00

UART0

CSI0

UART1

CSI1

CSI2

CSI3

29

µ

PD703003

Data Sheet U12261EJ2V1DS00

10. PWM UNIT

The features of the PWM unit are shown below.

∑ PWMn: 2 channels

∑ Selectable active level for PWMn output pulse

∑ Operating clock selectable as

,

/2,

/4,

/8, or

/16 (

: internal system clock)

∑ PWMn output resolution selectable as 8, 9, 10, or 12 bits

Remark n = 0, 1

The configuration of the PWM unit is shown below.

Figure 10-1. Block Diagram of PWM Unit

Note Priority to reset

Remark n = 0, 1

: internal system clock

TMPn (12 bits)

Comparator

CMPn (12 bits)

PWMn (12 bits)

/2

/4

/8

/16

Overflow

Match

7

8

9

11

0-7

0-8

0-9

0-11

S

Q

R

Note

ALVn

PWMn

µ

PD703003

30

Data Sheet U12261EJ2V1DS00

11. A/D CONVERTER

The features of the A/D converter are shown below.

∑ Analog inputs: 8 channels

∑ On-chip 10-bit A/D converter

∑ On-chip A/D conversion result registers (ADCR0 to ADCR7)

10 bits

◊

8 registers

∑ A/D conversion trigger modes

A/D trigger mode

Timer trigger mode

External trigger mode

∑ Sequential conversion method

The configuration of the A/D converter is shown below.

Figure 11-1. Block Diagram of A/D Converter

Internal bus

ANI0

ANI1

ANI2

ANI3

ANI4

ANI5

ANI6

ANI7

INTAD

Controller

ADM0 (8)

ADM1 (8)

7

8

8

10

10

10

ADCR0

SAR (10)

Voltage comparator

Tap selector

ADCR1

ADCR2

ADCR3

ADCR4

ADCR5

ADCR6

ADCR7

7

0

0

0

9

0

R/2

Series resistor string

Sample & hold circuit

AV

REF1

AV

SS

AV

DD

R

R/2

9

INTCC110

INTCC111

INTCC112

Noise

elimination

Edge

detection

INTCC113

ADTRG

Input circuit

31

µ

PD703003

Data Sheet U12261EJ2V1DS00

12. D/A CONVERTER

The features of the D/A converter are shown below.

∑ 8-bit resolution D/A converter: 2 channels

∑ R-2R conversion method

The configuration of the D/A converter is shown below.

Figure 12-1. Block Diagram of D/A Converter

Remark n = 0, 1

DACSn

Selector

DACEn

2R

2R

2R

2R

R

R

ANOn

AV

REF2

AV

REF3

Internal bus

µ

PD703003

32

Data Sheet U12261EJ2V1DS00

13. PORT FUNCTIONS

The features of the port functions are shown below.

∑

Number of ports

Input-only ports:

8

I/O ports:

67

∑ Alternated as I/O pins for other peripheral functions

∑ I/O setting can be specified bitwise

∑ Noise elimination

∑ Edge detection

The configurations of the port functions are shown below.

Figure 13-1. Block Diagram of P00 and P01 (Port 0)

Remark

n = 0, 1

WR

PMC

WR

PM

WR

PORT

RD

IN

PMC0n

Internal bus

PM0n

P0n

Selector

Selector

Selector

TO11n

P0n

Address

33

µ

PD703003

Data Sheet U12261EJ2V1DS00

Figure 13-2. Block Diagram of P02 to P07 (Port 0)

Remark

n = 2 to 7

Figure 13-3. Block Diagram of P10 and P11 (Port 1)

Remark

n = 0, 1

WR

PMC

WR

PM

WR

PORT

RD

IN

PMC0n

Internal bus

PM0n

P0n

Noise elimination

Edge detection

P0n

INTP110-INTP112,

INTP113/ADTRG,

TCLR11, TI11

Address

Selector

Selector

WR

PM

WR

PORT

RD

IN

PM1n

TO12n

WR

PMC

PMC1n

P1n

P1n

Internal bus

Address

Selector

Selector

Selector

µ

PD703003

34

Data Sheet U12261EJ2V1DS00

Figure 13-4. Block Diagram of P12 to P14 (Port 1)

Remark

n = 2 to 4

Figure 13-5. Block Diagram of P15 (Port 1)

PMC1n

PM1n

P1n

RD

IN

WR

PORT

WR

PM

WR

PMC

P1n

TCLR12, TI12

INTP120

Internal bus

Noise elimination

Edge detection

Address

Selector

Selector

PMC15

PM15

P15

RD

IN

WR

PORT

WR

PM

WR

PMC

P15

INTP121

SO2

PCM1

PCM1

Internal bus

Noise elimination

Edge detection

Address

Selector

Selector

Selector

35

µ

PD703003

Data Sheet U12261EJ2V1DS00

Figure 13-6. Block Diagram of P16 (Port 1)

Figure 13-7. Block Diagram of P17 (Port 1)

PMC16

PM16

P16

RD

IN

WR

PORT

WR

PM

WR

PMC

P16

INTP122

SI2

PCM1

Internal bus

Noise elimination

Edge detection

Address

Selector

Selector

PMC17

PM17

P17

RD

IN

WR

PORT

WR

PM

WR

PMC

P17

INTP123

SCK2 output

PCM1

SCK2 output

SCK2 I/O

switch

PCM1

Internal bus

Noise elimination

Edge detection

Address

Selector

Selector

Selector

µ

PD703003

36

Data Sheet U12261EJ2V1DS00

Figure 13-8. Block Diagram of P20 and P21 (Port 2)

Remark

n = 0, 1

Figure 13-9. Block Diagram of P22 and P25 (Port 2)

Remark

n = 2, 5

PMC2n

PM2n

P2n

RD

IN

WR

PORT

WR

PM

WR

PMC

PWM0, PWM1

P2n

Internal bus

Address

Selector

Selector

Selector

PMC2n

PM2n

P2n

RD

IN

WR

PORT

WR

PM

WR

PMC

TXD0/SO0

TXD1/SO1

P2n

SO0, SO1 output

enable

Internal bus

Address

Selector

Selector

Selector

37

µ

PD703003

Data Sheet U12261EJ2V1DS00

Figure 13-10. Block Diagram of P23 and P26 (Port 2)

Remark

n = 3, 6

Figure 13-11. Block Diagram of P24 and P27 (Port 2)

Remark

n = 4, 7

PMC2n

PM2n

P2n

RD

IN

WR

PORT

WR

PM

WR

PMC

P2n

RXD0/SI0

RXD1/SI1

Internal bus

Address

Selector

Selector

PMC2n

PM2n

P2n

RD

IN

WR

PORT

WR

PM

WR

PMC

P2n

SCK0 input

SCK1 input

SCK0 output

SCK1 output

SCK0, SCK1

I/O switch

Internal bus

Address

Selector

Selector

Selector

µ

PD703003

38

Data Sheet U12261EJ2V1DS00

Figure 13-12. Block Diagram of P30 and P31 (Port 3)

Remark

n = 0, 1

Figure 13-13. Block Diagram of P32 to P34 (Port 3)

Remark

n = 2 to 4

WR

PMC

WR

PM

WR

PORT

RD

IN

PMC3n

PM3n

P3n

TO13n

P3n

Internal bus

Address

Selector

Selector

Selector

PMC3n

PM3n

P3n

RD

IN

WR

PORT

WR

PM

WR

PMC

P3n

TCLR13, TI13

INTP130

Internal bus

Noise elimination

Edge detection

Address

Selector

Selector

39

µ

PD703003

Data Sheet U12261EJ2V1DS00

Figure 13-14. Block Diagram of P35 (Port 3)

Figure 13-15. Block Diagram of P36 (Port 3)

PMC35

PM35

P35

RD

IN

WR

PORT

WR

PM

WR

PMC

P35

INTP131

PCM3

SO3

SO3 output

enable

PCM3

PUO3

V

DD

P

N

P

Internal bus

Noise elimination

Edge detection

Address

Selector

Selector

Selector

PMC36

PM36

P36

RD

IN

WR

PORT

WR

PM

WR

PMC

P36

INTP132

PCM3

PUO3

V

DD

P

N

SI3

P

Internal bus

Noise elimination

Edge detection

Address

Selector

Selector

µ

PD703003

40

Data Sheet U12261EJ2V1DS00

Figure 13-16. Block Diagram of P37 (Port 3)

Figure 13-17. Block Diagram of P40 to P47 (Port 4)

Remark

n = 0 to 7

PMC37

PM37

P37

RD

IN

WR

PORT

WR

PM

WR

PMC

P37

INTP133

PCM3

PUO3

V

DD

P

N

SCK3 input

SCK3 output

P

SCK3 I/O

switch

PCM3

Internal bus

Noise elimination

Edge detection

Address

Selector

Selector

Selector

PM4n

P4n

RD

IN

WR

PORT

WR

PM

AD0 to AD7 output

P4n

AD0 to AD7 input

I/O control circuit

MODE

MM0 to MM2

Internal bus

Address

Selector

Selector

Selector

41

µ

PD703003

Data Sheet U12261EJ2V1DS00

Figure 13-18. Block Diagram of P50 to P57 (Port 5)

Remark

n = 0 to 7

Figure 13-19. Block Diagram of P60 to P63 (Port 6)

Remark

n = 0 to 3

PM5n

P5n

RD

IN

WR

PORT

WR

PM

P5n

I/O control circuit

MODE

MM0 to MM2

AD8 to AD15 output

AD8 to AD15 input

Internal bus

Address

Selector

Selector

Selector

PM6n

P6n

RD

IN

WR

PORT

WR

PM

A16 to A19 output

P6n

MODE

MM0 to MM2

I/O control circuit

Internal bus

Address

Selector

Selector

Selector

µ

PD703003

42

Data Sheet U12261EJ2V1DS00

Figure 13-20. Block Diagram of P70 to P77 (Port 7)

Remark

n = 0 to 7

Figure 13-21. Block Diagram of P90 to P95 (Port 9)

Remark

n = 0 to 5

RD

IN

P7n

ANI0 to ANI7

Sample & hold

circuit

Internal bus

PM9n

P9n

RD

IN

WR

PORT

WR

PM

LBEN, UBEN, R/W,

DSTB, ASTB, HLDAK

P9n

MODE

MM0 to MM3

Internal bus

Address

Selector

Selector

Selector

I/O control circuit

43

µ

PD703003

Data Sheet U12261EJ2V1DS00

Figure 13-22. Block Diagram of P96 (Port 9)

Figure 13-23. Block Diagram of P110 and P111 (Port 11)

Remark

n = 0, 1

PM96

P96

RD

IN

WR

PORT

WR

PM

P96

MM3

HLDRQ

I/O control circuit

Internal bus

Address

Selector

Selector

WR

PMC

WR

PM

WR

PORT

RD

IN

PMC11n

PM11n

P11n

TO14n

P11n

Internal bus

Address

Selector

Selector

Selector

µ

PD703003

44

Data Sheet U12261EJ2V1DS00

Figure 13-24. Block Diagram of P112 to P117 (Port 11)

Remark

n = 2 to 7

PMC11n

PM11n

P11n

RD

IN

WR

PORT

WR

PM

WR

PMC

P11n

TCLR14, TI14

INTP140 to INTP143

Internal bus

Noise elimination

Edge detection

Selector

Selector

Address

45

µ

PD703003

Data Sheet U12261EJ2V1DS00

14. RESET FUNCTIONS

When low-level input occurs at the RESET pin, a system reset is performed and the various on-chip hardware

devices are reset to their initial settings.

When the input at the RESET pin changes from low level to high level, the reset status is canceled and the CPU

resumes program execution. The contents of the various registers should be initialized within the program as

necessary.

The feature of the reset functions is shown below.

∑ On-chip noise elimination circuit which uses analog delay (

60 ns) for the RESET pin

µ

PD703003

46

Data Sheet U12261EJ2V1DS00

15. INSTRUCTION SET

∑ How to read instruction set tables

Table 15-1. Symbols Used to Indicate Operands

Symbol

Description

reg1

General registers (r0 to r31): used as source registers

reg2

General registers (r0 to r31): mainly used as destination registers

ep

Element pointer (r30)

bit#3

3-bit data used to specify bit number

immX

X bits immediate

dispX

X bits displaced

regID

System register number

vector

5-bit data used to specify trap vector (00H to 1FH)

cccc

4-bit data used to indicate condition code

Indicates the instruction group. Instructions are listed in these table according to their respective groups.

Indicates the mnemonic abbreviation for the instruction.

Indicates the instruction's operands (see Table 15-1).

Indicates the instruction binary code. The binary codes for 32-bit

instructions are shown in two levels (see Table 15-2).

Indicates instruction operation (see Table 15-3).

Indicates flag operations

(see Table 15-4).

Mnemonic

Operand

Opcode

Operation

Flags

CY

OV

S

Z

SAT

Instruction

group

47

µ

PD703003

Data Sheet U12261EJ2V1DS00

Table 15-2. Symbols Used to Indicate Opcodes

Symbol

Description

R

1-bit data of code specifying reg1 or regID

r

1-bit data of code specifying reg2

d

1 bit of displaced data

i

1 bit of immediate data

cccc

4-bit data used to indicate condition code

bbb

3-bit data used to specify bit number

Table 15-3. Symbols Used to Indicate Operations

Symbol

Description

Assign

GR [ ]

General register

SR [ ]

System register

zero-extend (n)

Zero-extend n up until word length

sign-extend (n)

Sign-extend n up until word length

load-memory (a, b)

Read data having size b from address a

store-memory (a, b, c)

Replace data b at address a with data having size c

load-memory-bit (a, b)

Read bit b from address a

store-memory-bit (a, b, c)

Write c to bit b from address a

saturated (n)

Execute saturation processing for n (n = complement to 2)

Calculation of n:

When n

7FFFFFFFH, result is 7FFFFFFFH.

When n

80000000H, result is 80000000H.

result

Result is indicated by flag operations

Byte

Byte (8 bits)

Halfword

Half word (16 bits)

Word

Word (32 bits)

+

Add

≠

Subtract

||

Bit linkage

◊

Multiply

˜

Divide

AND

Logical AND

OR

Logical OR

XOR

Exclusive OR

NOT

Logical NOT

logically shift left by

Logical shift left

logically shift right by

Logical shift right

arithmetically shift right by

Arithmetic shift right

µ

PD703003

48

Data Sheet U12261EJ2V1DS00

Table 15-4. Flag Operations

Identifier

Description

(Blank)

No change

0

Clear to zero

◊

Set or clear according to result

R

Restore previously saved value(s)

Table 15-5. Condition Codes

Condition name (cond)

Condition code (cccc)

Conditional expression

Description

V

0000

OV = 1

Overflow

NV

1000

OV = 0

No overflow

C/L

0001

CY = 1

Carry

Lower (Less than)

NC/NL

1001

CY = 0

No carry

No lower (Greater than or equal)

Z/E

0010

Z = 1

Zero

Equal

NZ/NE

1010

Z = 0

Not zero

Not equal

NH

0011

(CY OR Z) = 1

Not higher (Less than or equal)

H

1011

(CY OR Z) = 0

Higher (Greater than)

N

0100

S = 1

Negative

P

1100

S = 0

Positive

T

0101

≠

Always (unconditional)

SA

1101

SAT = 1

Saturated

LT

0110

(S XOR OV) = 1

Less than signed

GE

1110

(S XOR OV) = 0

Greater than or equal signed

LE

0111

((S XOR OV) OR Z) = 1

Less than or equal signed

GT

1111

((S XOR OV) OR Z) = 0

Greater than signed

49

µ

PD703003

Data Sheet U12261EJ2V1DS00

Instruction Set List

Instruction Mnemonic

Operand

Opcode

Operation

Flags

group

CY OV S

Z

SAT

Load/store

SLD.B

disp7[ep], reg2

r r r r r 0 1 1 0 d d d d d d d adr

ep + zero-extend (disp7)

instructions

GR[reg2]

sign-extend (Load-memory (adr, Byte))

SLD.H

disp8[ep], reg2

r r r r r 1 0 0 0 d d d d d d d adr

ep + zero-extend (disp8)

Note 1 GR[reg2]

sign-extend (Load-memory (adr, Halfword))

SLD.W

disp8[ep], reg2

r r r r r 1 0 1 0 d d d d d d 0 adr

ep + zero-extend (disp8)

Note 2 GR[reg2]

Load-memory (adr, Word)

LD.B

disp16[reg1], reg2

r r r r r 1 1 1 0 0 0 RRRRR adr

GR[reg1] + sign-extend (disp16)

d d d d d d d d d d d d d d d d GR[reg2]

sign-extend (Load-memory (adr, Byte))

LD.H

disp16[reg1], reg2

r r r r r 1 1 1 0 0 1 RRRRR adr

GR[reg1] + sign-extend (disp16)

d d d d d d d d d d d d d d d 0 GR[reg2]

sign-extend (Load-memory (adr, Halfword))

Note 3

LD.W

disp16[reg1], reg2

r r r r r 1 1 1 0 0 1 RRRRR adr

GR[reg1] + sign-extend (disp16)

d d d d d d d d d d d d d d d 1 GR[reg2]

Load-memory (adr, Word)

Note 3

SST.B

reg2, disp7[ep]

r r r r r 0 1 1 1 d d d d d d d adr

ep + zero-extend (disp7)

Store-memory (adr, GR[reg2], Byte)

SST.H

reg2, disp8[ep]

r r r r r 1 0 0 1 d d d d d d d adr

ep + zero-extend (disp8)

Note 1 Store-memory (adr, GR[reg2], Halfword)

SST.W

reg2, disp8[ep]

r r r r r 1 0 1 0 d d d d d d 1 adr

ep + zero-extend (disp8)

Note 2 Store-memory (adr, GR[reg2], Word)

ST.B

reg2, disp16[reg1]

r r r r r 1 1 1 0 1 0 RRRRR adr

GR[reg1] + sign-extend (disp16)

d d d d d d d d d d d d d d d d Store-memory (adr, GR[reg2], Byte)

ST.H

reg2, disp16[reg1]

r r r r r 1 1 1 0 1 1 RRRRR adr

GR[reg1] + sign-extend (disp16)

d d d d d d d d d d d d d d d 0 Store-memory (adr, GR[reg2], Halfword)

Note 3

ST.W

reg2, disp16[reg1]

r r r r r 1 1 1 0 1 1 RRRRR adr

GR[reg1] + sign-extend (disp16)

d d d d d d d d d d d d d d d 1 Store-memory (adr, GR[reg2], Word)

Note 3

Arithmetic MOV

reg1, reg2

r r r r r 0 0 0 0 0 0 RRRRR GR[reg2]

GR[reg1]

operation

MOV

imm5, reg2

r r r r r 0 1 0 0 0 0 i i i i i

GR[reg2]

sign-extend (imm5)

instructions

MOVHI

imm16, reg1, reg2

r r r r r 1 1 0 0 1 0 RRRRR GR[reg2]

GR[reg1] + (imm16 || 0

16

)

i i i i i i i i i i i i i i i i

MOVEA

imm16, reg1, reg2

r r r r r 1 1 0 0 0 1 RRRRR GR[reg2]

GR[reg1] + sign-extend (imm16)

i i i i i i i i i i i i i i i i

ADD

reg1, reg2

r r r r r 0 0 1 1 1 0 RRRRR GR[reg2]

GR[reg2] + GR[reg1]

◊ ◊ ◊ ◊

ADD

imm5, reg2

r r r r r 0 1 0 0 1 0 i i i i i

GR[reg2]

GR[reg2] + sign-extend (imm5)

◊ ◊ ◊ ◊

ADDI

imm16, reg1, reg2

r r r r r 1 1 0 0 0 0 RRRRR GR[reg2]

GR[reg1] + sign-extend (imm16)

◊ ◊ ◊ ◊

i i i i i i i i i i i i i i i i

SUB

reg1, reg2

r r r r r 0 0 1 1 0 1 RRRRR GR[reg2]

GR[reg2] ≠ GR[reg1]

◊ ◊ ◊ ◊

SUBR

reg1, reg2

r r r r r 0 0 1 1 0 0 RRRRR GR[reg2]

GR[reg1] ≠ GR[reg2]

◊ ◊ ◊ ◊

Notes 1. ddddddd = high-order 7 bits of disp8

2. dddddd = high-order 6 bits of disp8

3. ddddddddddddddd = high-order 15 bits of disp16

µ

PD703003

50

Data Sheet U12261EJ2V1DS00

Instruction Mnemonic

Operand

Opcode

Operation

Flags

group

CY OV S Z

SAT

Arithmetic MULH

reg1, reg2

r r r r r 0 0 0 1 1 1 RRRRR GR[reg2]

GR[reg2]

Note

◊

GR[reg1]

Note

operation

(signed multiplication)

instructions

MULH

imm5, reg2

r r r r r 0 1 0 1 1 1 i i i i i

GR[reg2]

GR[reg2]

Note

◊

sign-extend (imm5)

(signed multiplication)

MULHI

imm16, reg1, reg2

r r r r r 1 1 0 1 1 1 RRRRR GR[reg2]

GR[reg1]

Note

◊

imm16

i i i i i i i i i i i i i i i i

(signed multiplication)

DIVH

reg1, reg2

r r r r r 0 0 0 0 1 0 RRRRR GR[reg2]

GR[reg2]

˜

GR[reg1]

Note

(signed division)

◊ ◊ ◊

CMP

reg1, reg2

r r r r r 0 0 1 1 1 1 RRRRR result

GR[reg2] ≠ GR[reg1]

◊ ◊ ◊ ◊

CMP

imm5, reg2

r r r r r 0 1 0 0 1 1 i i i i i

result

GR[reg2] ≠ sign-extend (imm5)

◊ ◊ ◊ ◊

SETF

cccc, reg2

r r r r r 1 1 1 1 1 1 0 c c c c if conditions are satisfied

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 then GR[reg2]

00000001H

else GR[reg2]

00000000H

Saturated SATADD reg1, reg2

r r r r r 0 0 0 1 1 0 RRRRR GR[reg2]

saturated (GR[reg2] + GR[reg1])

◊ ◊ ◊ ◊ ◊

operation

SATADD imm5, reg2

r r r r r 0 1 0 0 0 1 i i i i i

GR[reg2]

saturated (GR[reg2] + sign-extend (imm5))

◊ ◊ ◊ ◊ ◊

instructions

SATSUB reg1, reg2

r r r r r 0 0 0 1 0 1 RRRRR GR[reg2]

saturated (GR[reg2] ≠ GR[reg1])

◊ ◊ ◊ ◊ ◊

SATSUBI imm16, reg1, reg2

r r r r r 1 1 0 0 1 1 RRRRR GR[reg2]

saturated (GR[reg1] ≠ sign-extend (imm16))

◊ ◊ ◊ ◊ ◊

i i i i i i i i i i i i i i i i

SATSUBR reg1, reg2

r r r r r 0 0 0 1 0 0 RRRRR GR[reg2]

saturated (GR[reg1] ≠ GR[reg2])

◊ ◊ ◊ ◊ ◊

Logical

TST

reg1, reg2

r r r r r 0 0 1 0 1 1 RRRRR result

GR[reg2]AND GR[reg1]

0

◊ ◊

operation

OR

reg1, reg2

r r r r r 0 0 1 0 0 0 RRRRR GR[reg2]

GR[reg2]OR GR[reg1]

0

◊ ◊

instruction

ORI

imm16, reg1, reg2

r r r r r 1 1 0 1 0 0 RRRRR GR[reg2]

GR[reg1]OR zero-extend (imm16)

0

◊ ◊

i i i i i i i i i i i i i i i i

AND

reg1, reg2

r r r r r 0 0 1 0 1 0 RRRRR GR[reg2]

GR[reg2]AND GR[reg1]

0

◊ ◊

ANDI

imm16, reg1, reg2

r r r r r 1 1 0 1 1 0 RRRRR GR[reg2]

GR[reg1]AND zero-extend (imm16)

0 0

◊

i i i i i i i i i i i i i i i i

XOR

reg1, reg2

r r r r r 0 0 1 0 0 1 RRRRR GR[reg2]

GR[reg2]XOR GR[reg1]

0

◊ ◊

XORI

imm16, reg1, reg2

r r r r r 1 1 0 1 0 1 RRRRR GR[reg2]

GR[reg1]XOR zero-extend (imm16)

0

◊ ◊

i i i i i i i i i i i i i i i i

NOT

reg1, reg2

r r r r r 0 0 0 0 1 RRRRR

GR[reg2]

NOT (GR[reg1])

0

◊ ◊

SHL

reg1, reg2

r r r r r 1 1 1 1 1 1 RRRRR GR[reg2]

GR[reg2]logically shift left by GR[reg1]

◊

0

◊ ◊

0 0 0 0 0 0 0 0 1 1 0 0 0 0 0 0

SHL

imm5, reg2

r r r r r 0 1 0 1 1 0 i i i i i

GR[reg2]

GR[reg2]logically shift left by

◊

0

◊ ◊

zero-extend (imm5)

SHR

reg1, reg2

r r r r r 1 1 1 1 1 1 RRRRR GR[reg2]

GR[reg2]logically shift right by GR[reg1]

◊

0

◊ ◊

0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0

SHR

imm5, reg2

r r r r r 0 1 0 1 0 0 i i i i i

GR[reg2]

GR[reg2]logically shift right by

◊

0

◊ ◊

zero-extend (imm5)

SAR

reg1, reg2

r r r r r 1 1 1 1 1 1 RRRRR GR[reg2]

GR[reg2]arithmetically shift right by

◊

0

◊ ◊

0 0 0 0 0 0 0 0 1 0 1 0 0 0 0 0

GR[reg1]

SAR

imm5, reg2

r r r r r 0 1 0 1 0 1 i i i i i

GR[reg2]

GR[reg2]arithmetically shift right by

◊

0

◊ ◊

zero-extend (imm5)

Note Only the low-order half word is valid.

51

µ

PD703003

Data Sheet U12261EJ2V1DS00

Instruction Mnemonic

Operand

Opcode

Operation

Flags

group

CY OV S

Z

SAT

Branch

JMP

[reg1]

0 0 0 0 0 0 0 0 0 1 1 RRRRR PC

GR[reg1]

instructions

JR

disp22

0 0 0 0 0 1 1 1 1 0 d d d d d d PC

PC + sign-extend (disp22)

d d d d d d d d d d d d d d d 0

Note 1

JARL

disp22, reg2

r r r r r 1 1 1 1 0 d d d d d d GR[reg2]

PC + 4

d d d d d d d d d d d d d d d 0 PC

PC + sign-extend (disp22)

Note 1

Bcond

disp9

d d d d d 1 0 1 1 d d d c c c c if conditions are satisfied

Note 2 then PC

PC + sign-extend (disp9)

Bit

SET1

bit#3, disp16[reg1] 0 0 b b b 1 1 1 1 1 0 RRRRR adr

GR[reg1] + sign-extend (disp16)

◊

manipulation

d d d d d d d d d d d d d d d d Z flag

Not (Load-memory-bit (adr, bit#3))

instructions

Store-memory-bit (adr, bit#3, 1)

CLR1

bit#3, disp16[reg1] 1 0 b b b 1 1 1 1 1 0 RRRRR adr

GR[reg1] + sign-extend (disp16)

◊

d d d d d d d d d d d d d d d d Z flag

Not (Load-memory-bit (adr, bit#3))

Store-memory-bit (adr, bit#3, 0)

NOT1

bit#3, disp16[reg1] 0 1 b b b 1 1 1 1 1 0 RRRRR adr

GR[reg1] + sign-extend (disp16)

◊

d d d d d d d d d d d d d d d d Z flag

Not (Load-memory-bit (adr, bit#3))

Store-memory-bit (adr, bit#3, Z flag)

TST1

bit#3, disp16[reg1] 1 1 b b b 1 1 1 1 1 0 RRRRR adr

GR[reg1] + sign-extend (disp16)

◊

d d d d d d d d d d d d d d d d Z flag

Not (Load-memory-bit (adr, bit#3))

Notes 1. ddddddddddddddddddddd = high-order 21 bits of disp22

2. dddddddd = high-order 8 bits of disp9

µ

PD703003

52

Data Sheet U12261EJ2V1DS00

Instruction Mnemonic

Operand

Opcode

Operation

Flags

group

CY OV S Z

SAT

Special

LDSR

reg2, regID

r r r r r 1 1 1 1 1 1 RRRRR SR[regID]

GR[reg2]

regID = EIPC, FEPC

instructions

0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0

regID = EIPSW, FEPSW

Note

regID = PSW

◊ ◊ ◊ ◊ ◊

STSR

regID, reg2

r r r r r 1 1 1 1 1 1 RRRRR GR[reg2]

SR[regID]

0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0