Document Outline

- COVER

- INTRODUCTION

- CHAPTER 1 OVERVIEW OF EACH PRODUCT

- 1.1 Outline

- 1.2 Features

- 1.3 Ordering Information

- 1.4 Pin Configuration

- 1.5 Internal Block Diagram

- CHAPTER 2 OVERVIEW OF PCI HOST BRIDGE MACRO

- CHAPTER 3 SPECIFICATIONS OF PCI HOST BRIDGE MACRO

- 3.1 Internal Blocks of PCI Host Bridge Macro

- 3.2 Relationship Between Internal Blocks and Signals

- 3.3 Pin Functions

- 3.3.1 External bus slave interface pins

- 3.3.2 SDRAM bus interface pins

- 3.3.3 PCI bus interface pins

- 3.4 Registers

- 3.4.1 PCI_CONFIG_DATA register

- 3.4.2 PCI_CONFIG_ADD register

- 3.4.3 PCI_CONTROL register

- 3.4.4 PCI_IO_BASE register

- 3.4.5 PCI_MEM_BASE register

- 3.4.6 PCI_INT_CTL register

- 3.4.7 PCI_ERR_ADD register

- 3.4.8 SYSTEM_MEM_BASE register

- 3.4.9 SYSTEM_MEM_RANGE register

- 3.4.10 SDRAM_CTL register

- 3.5 Address Map

- 3.6 Initializing PCI Host Bridge Macro

- 3.7 Bus Width of External Bus Interface

- 3.8 Timing

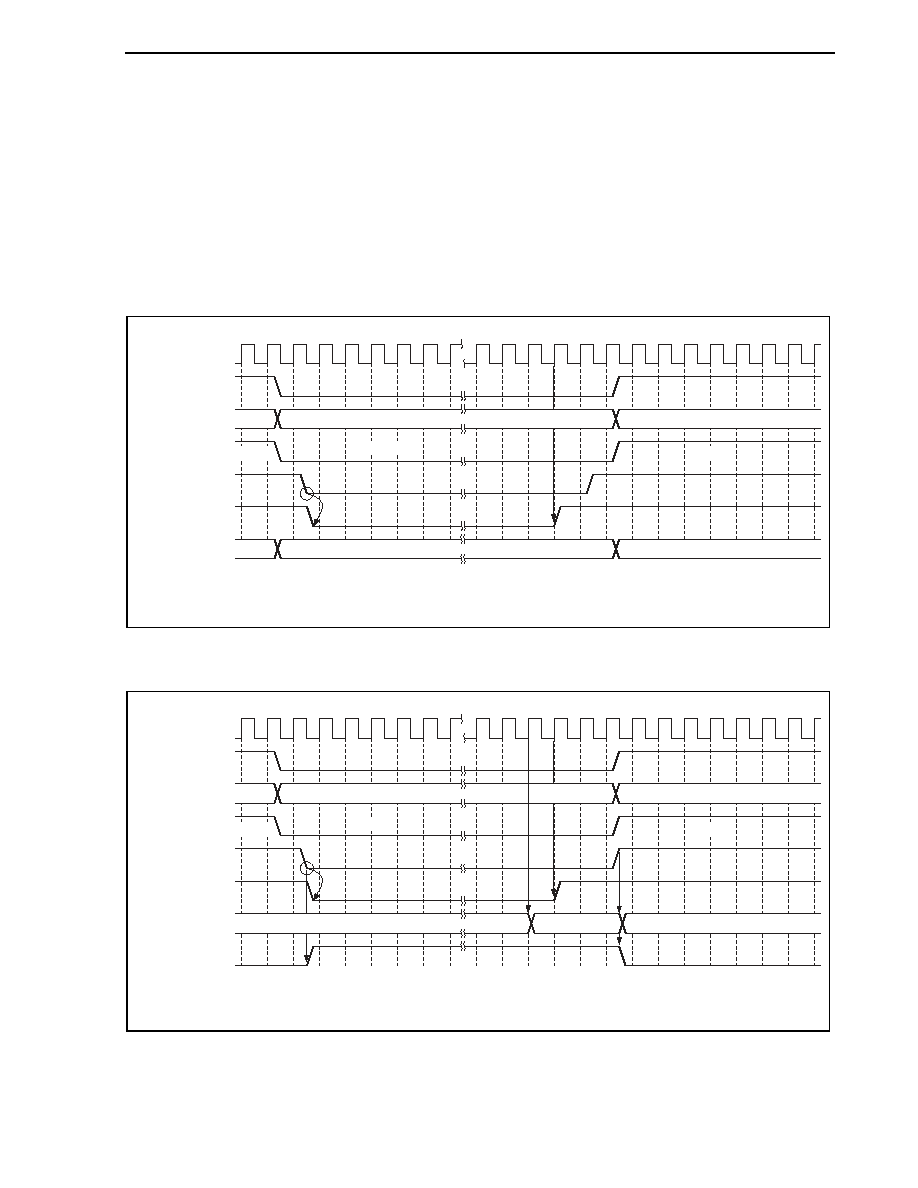

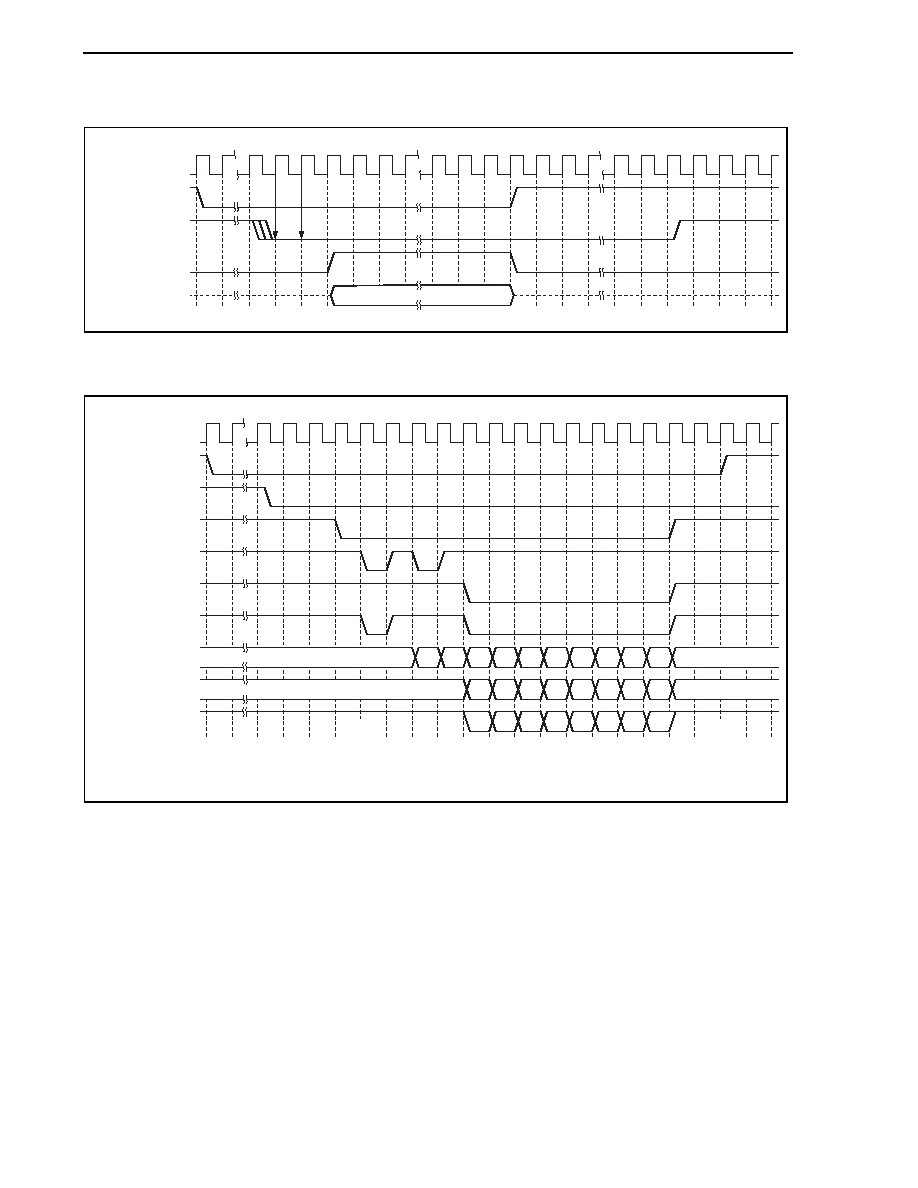

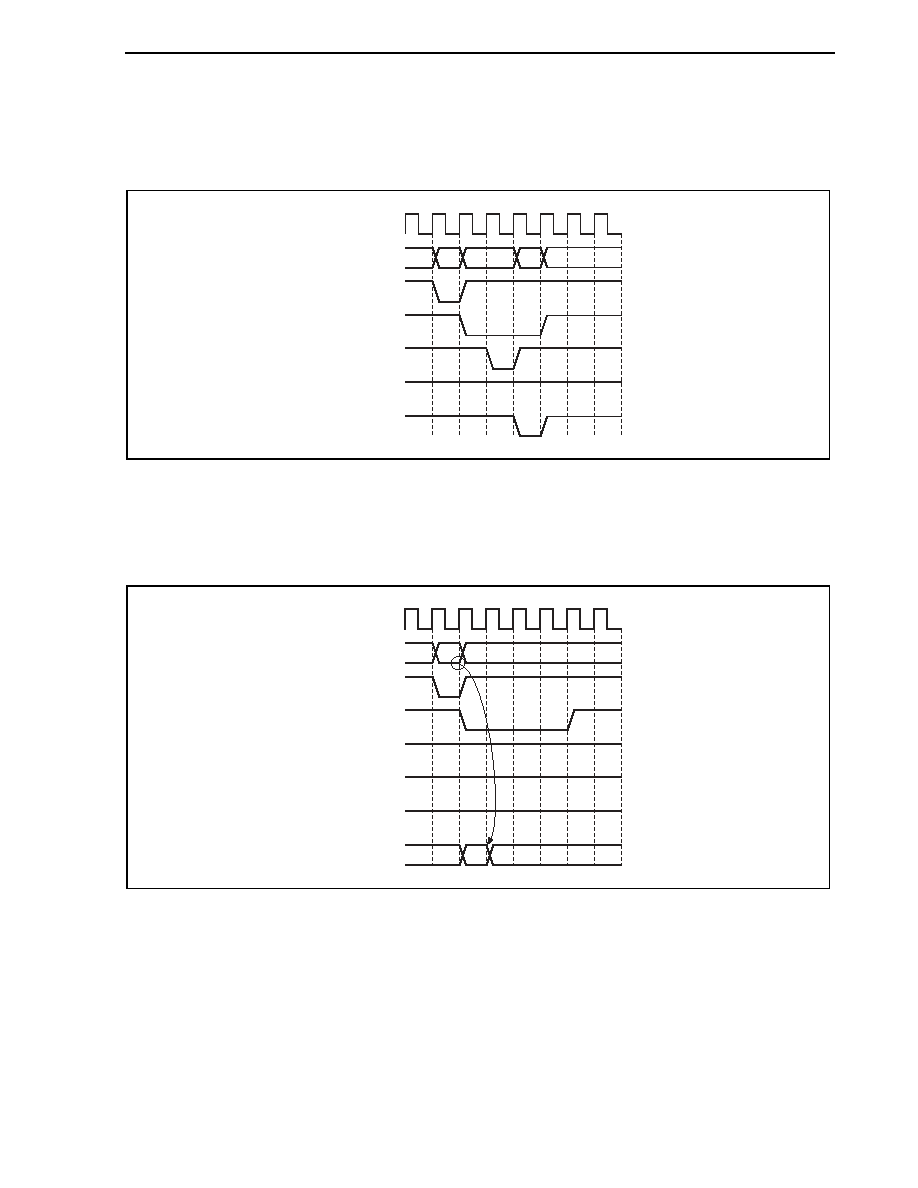

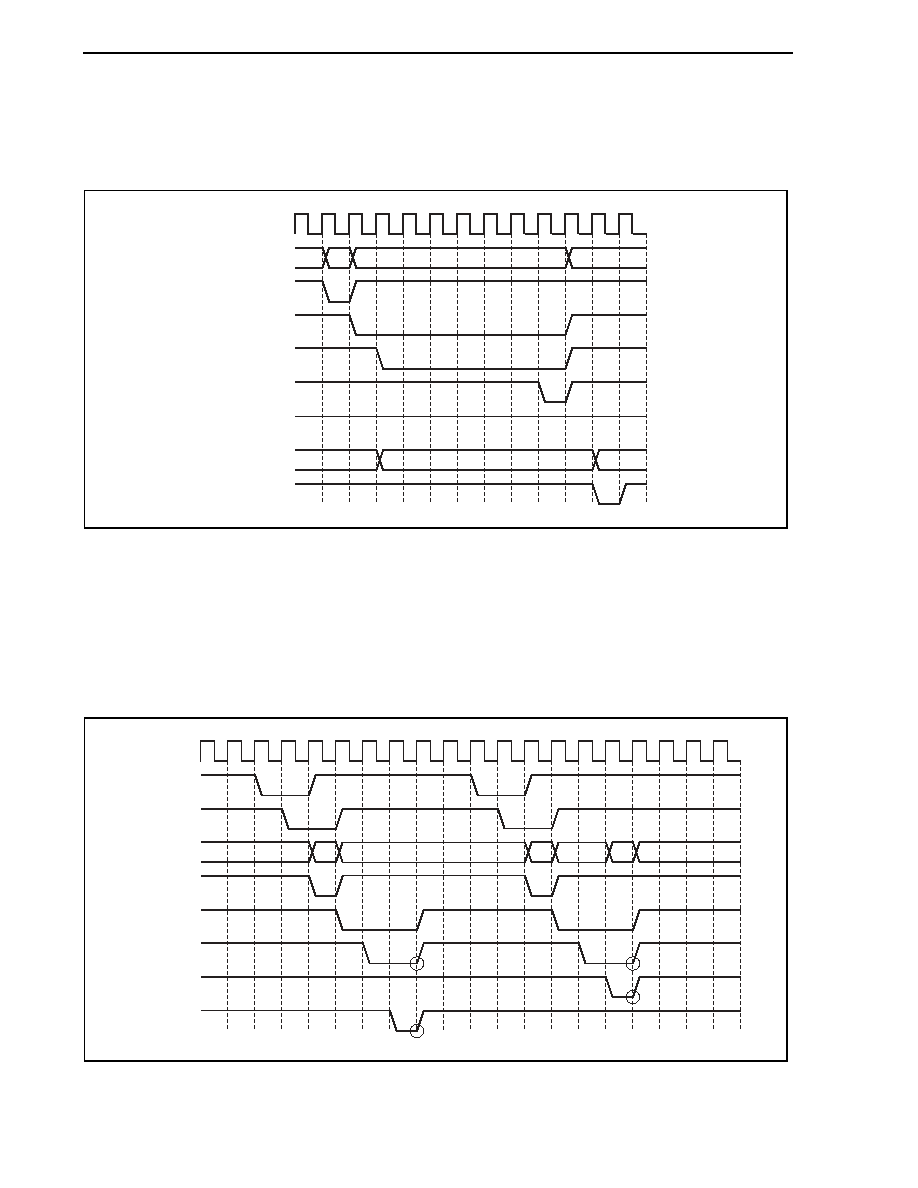

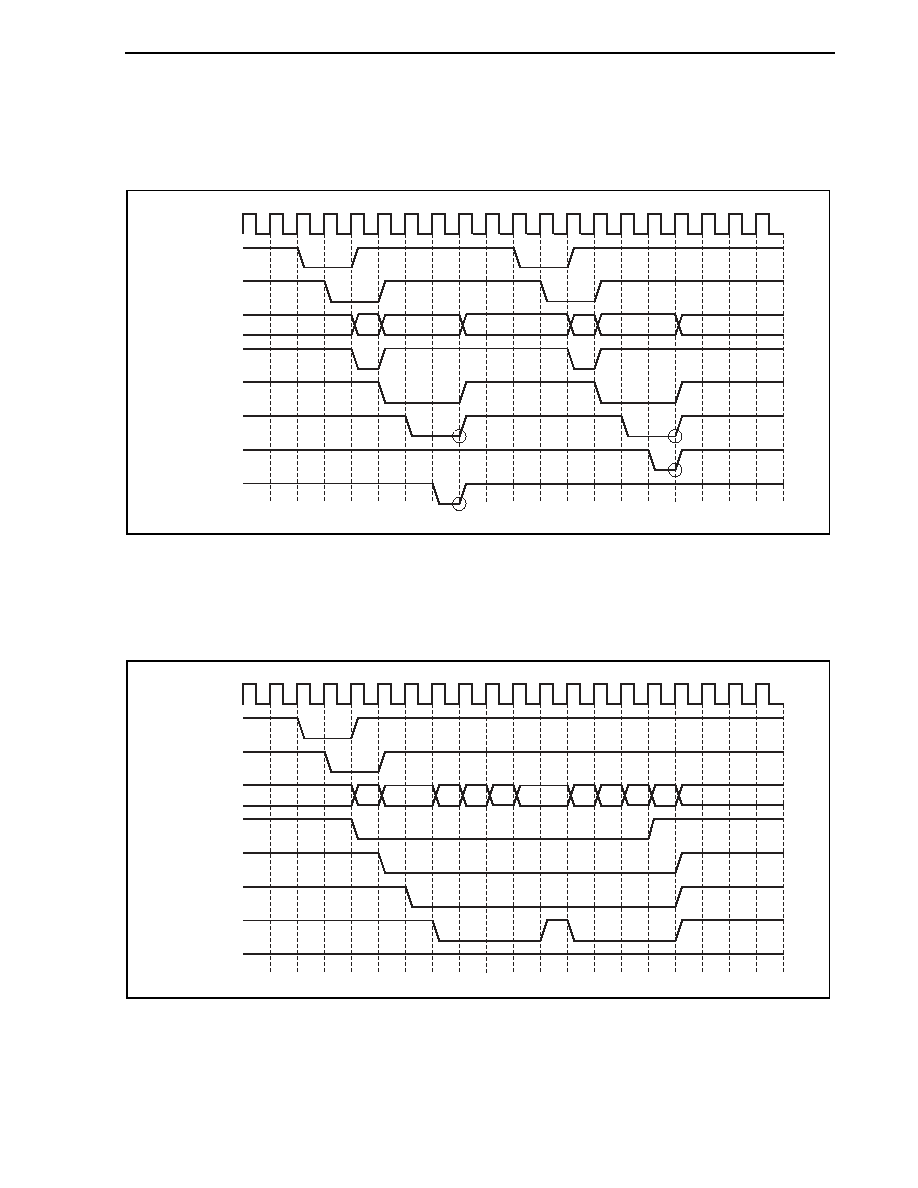

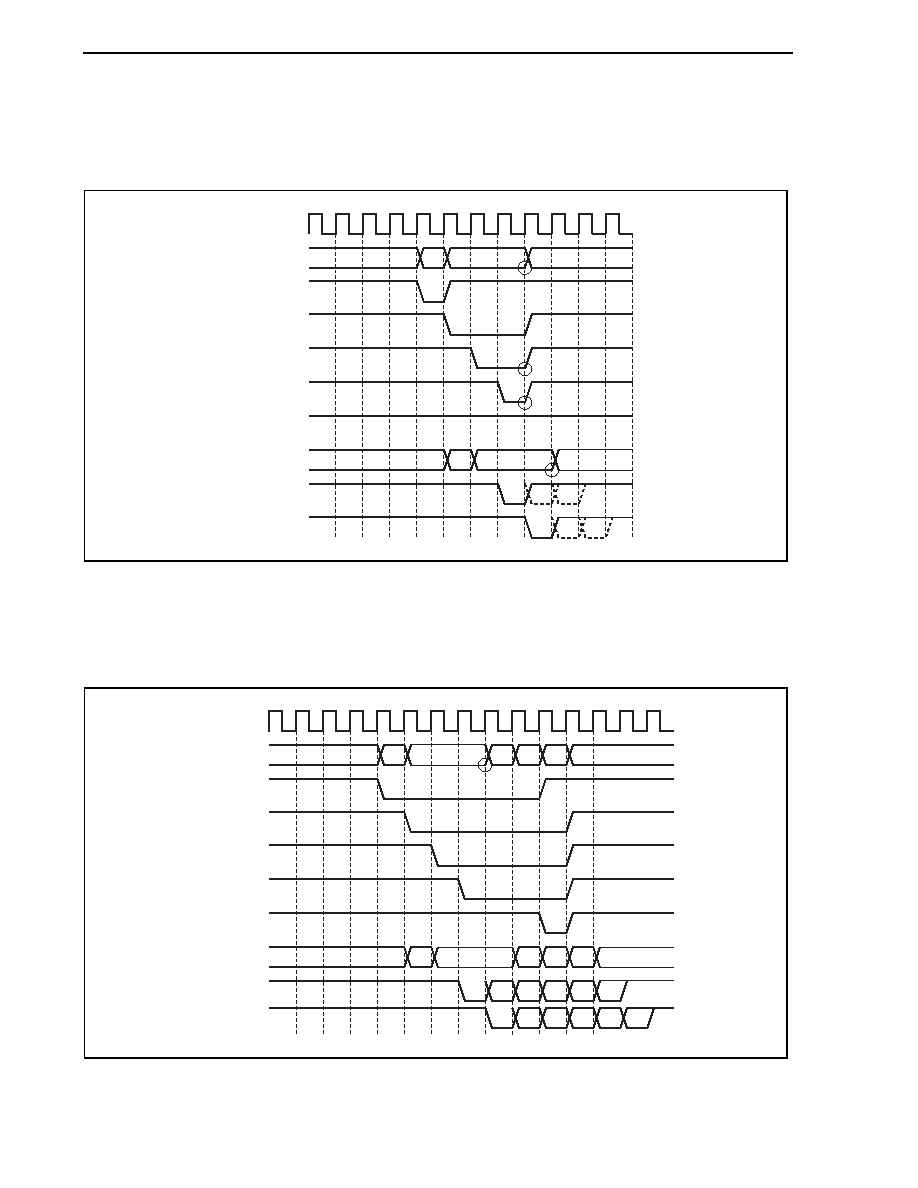

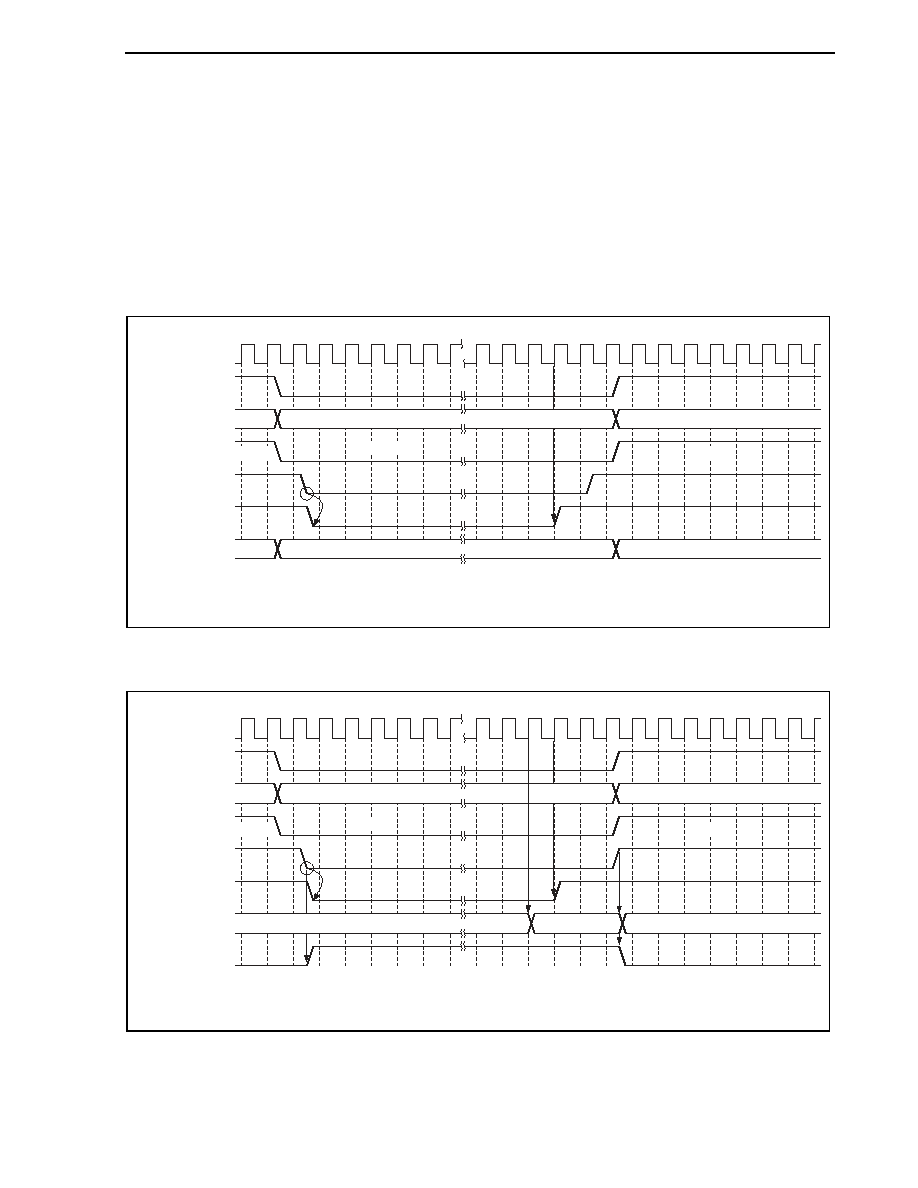

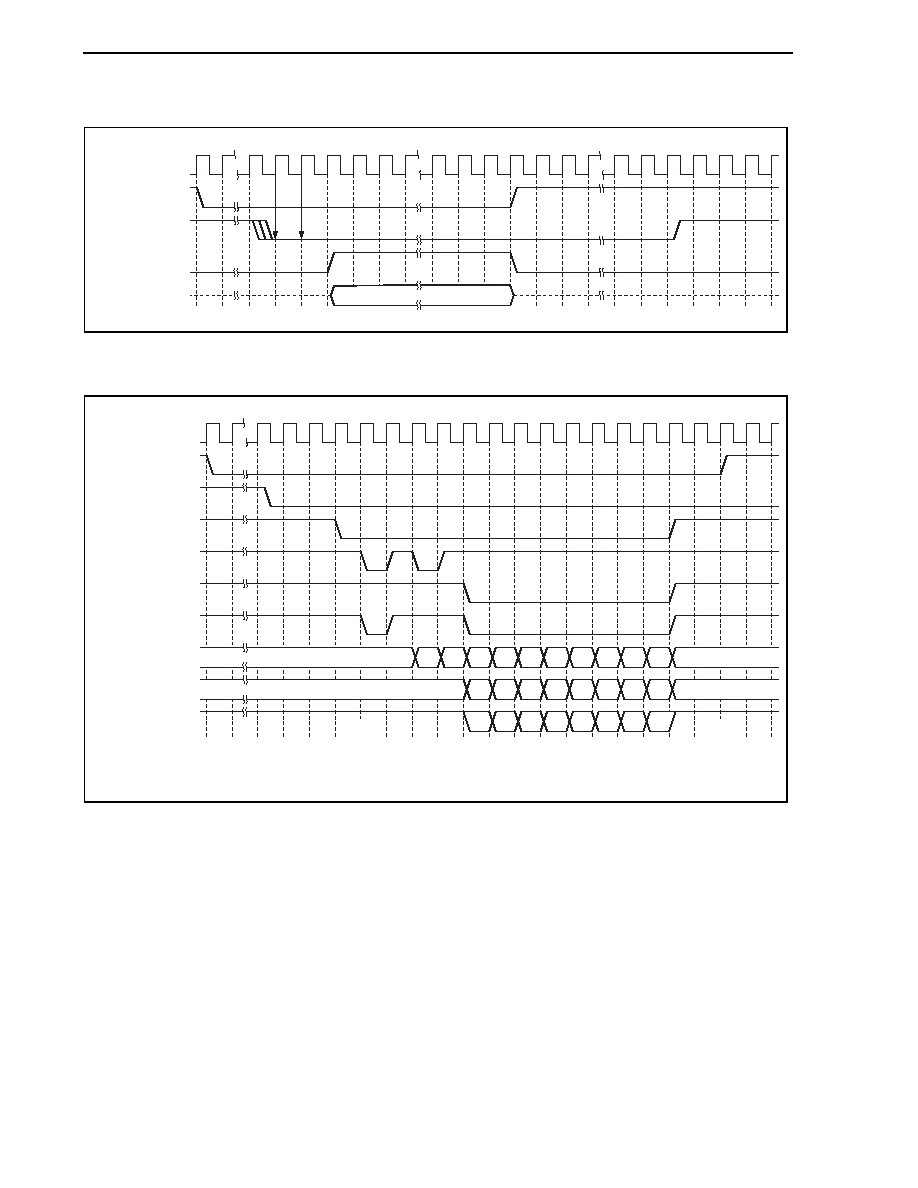

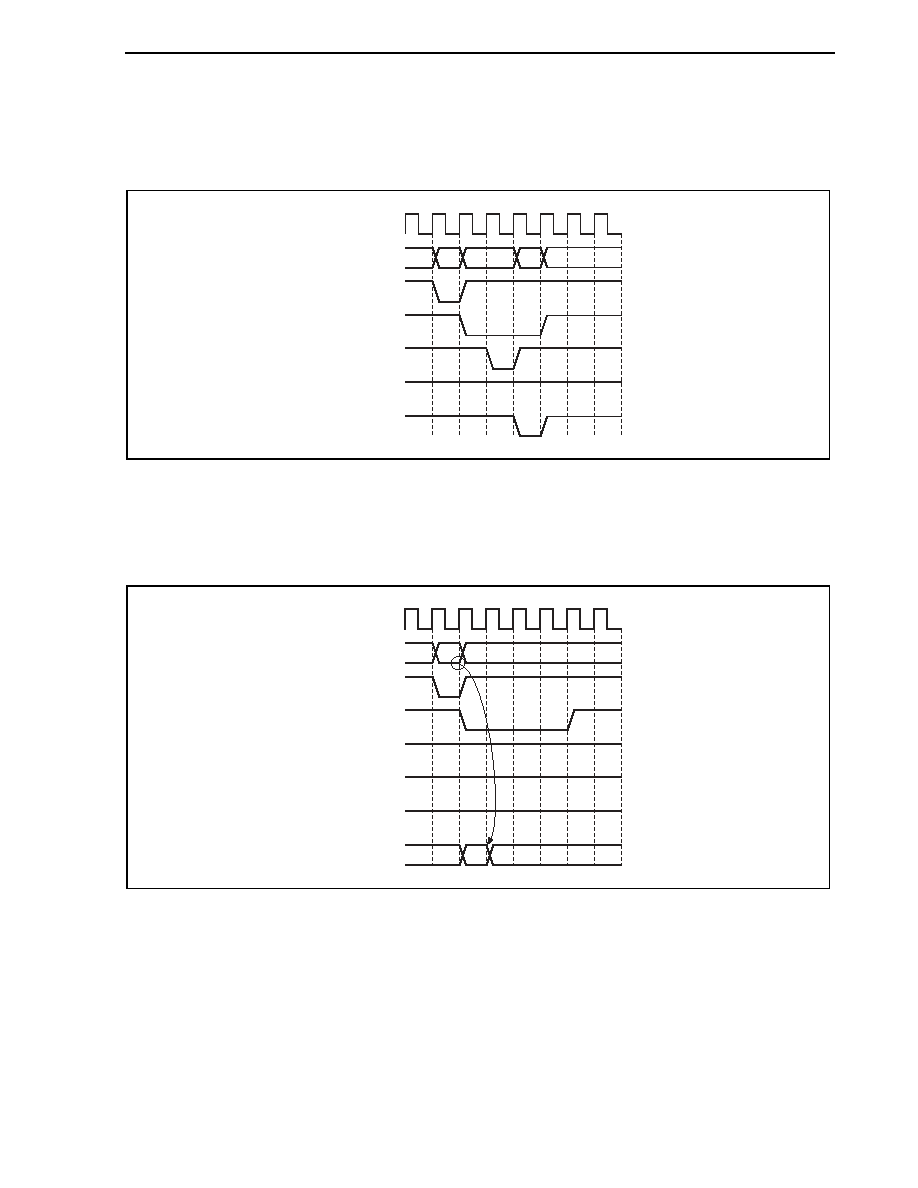

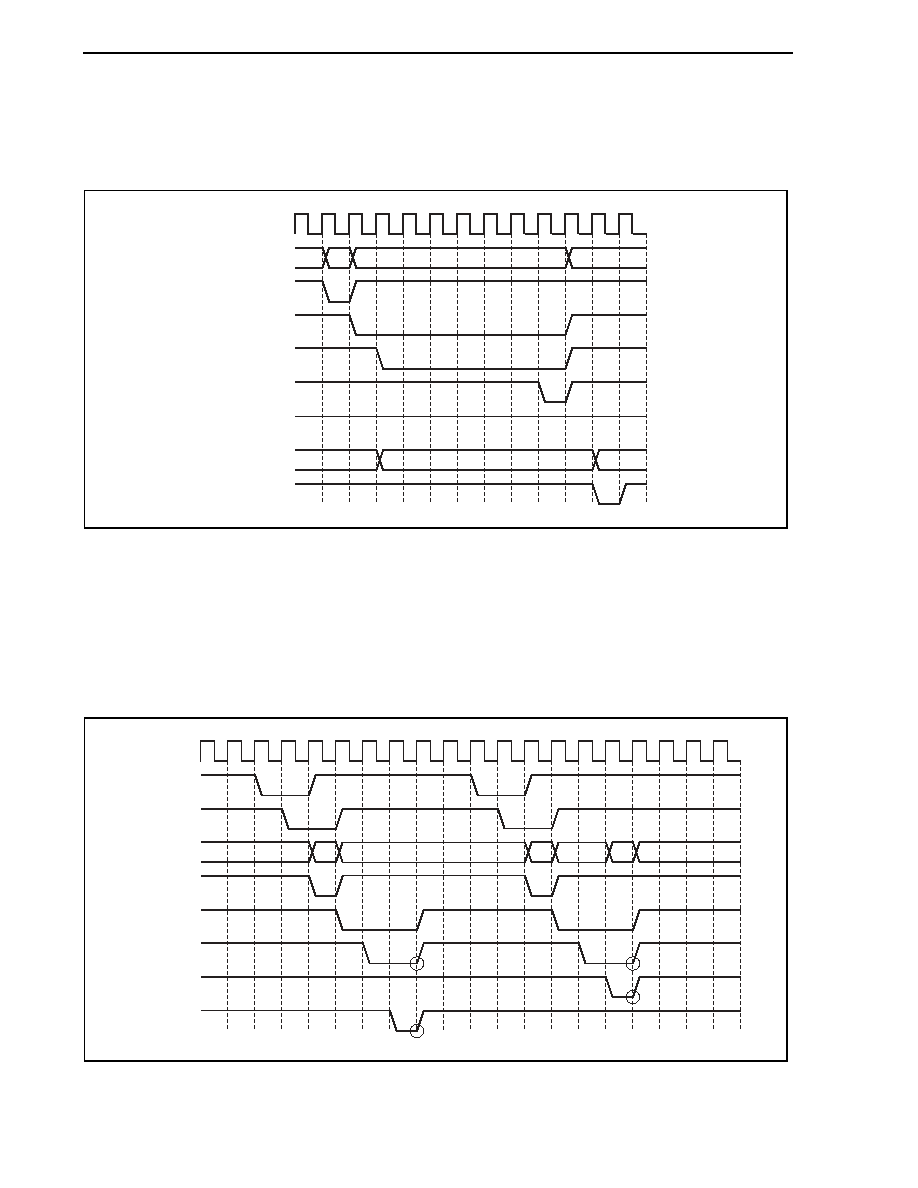

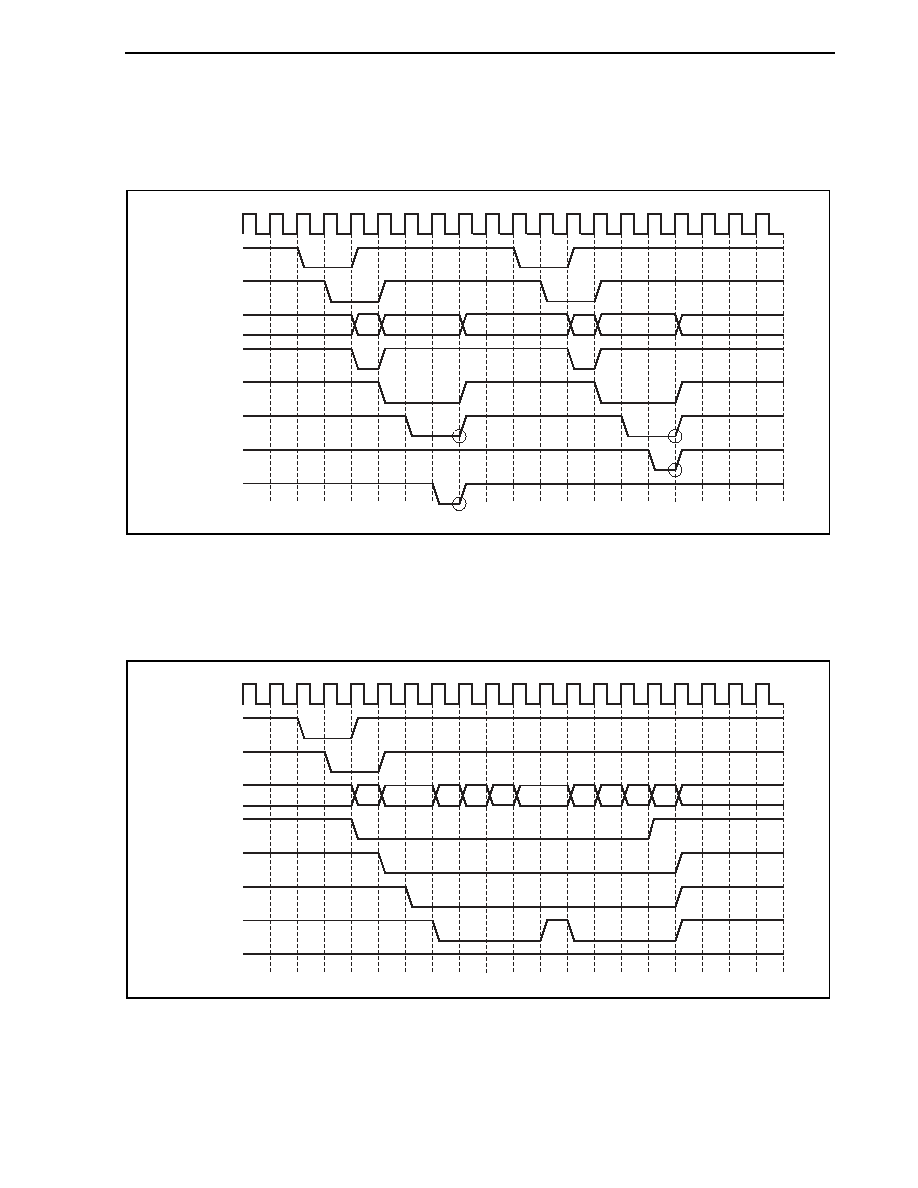

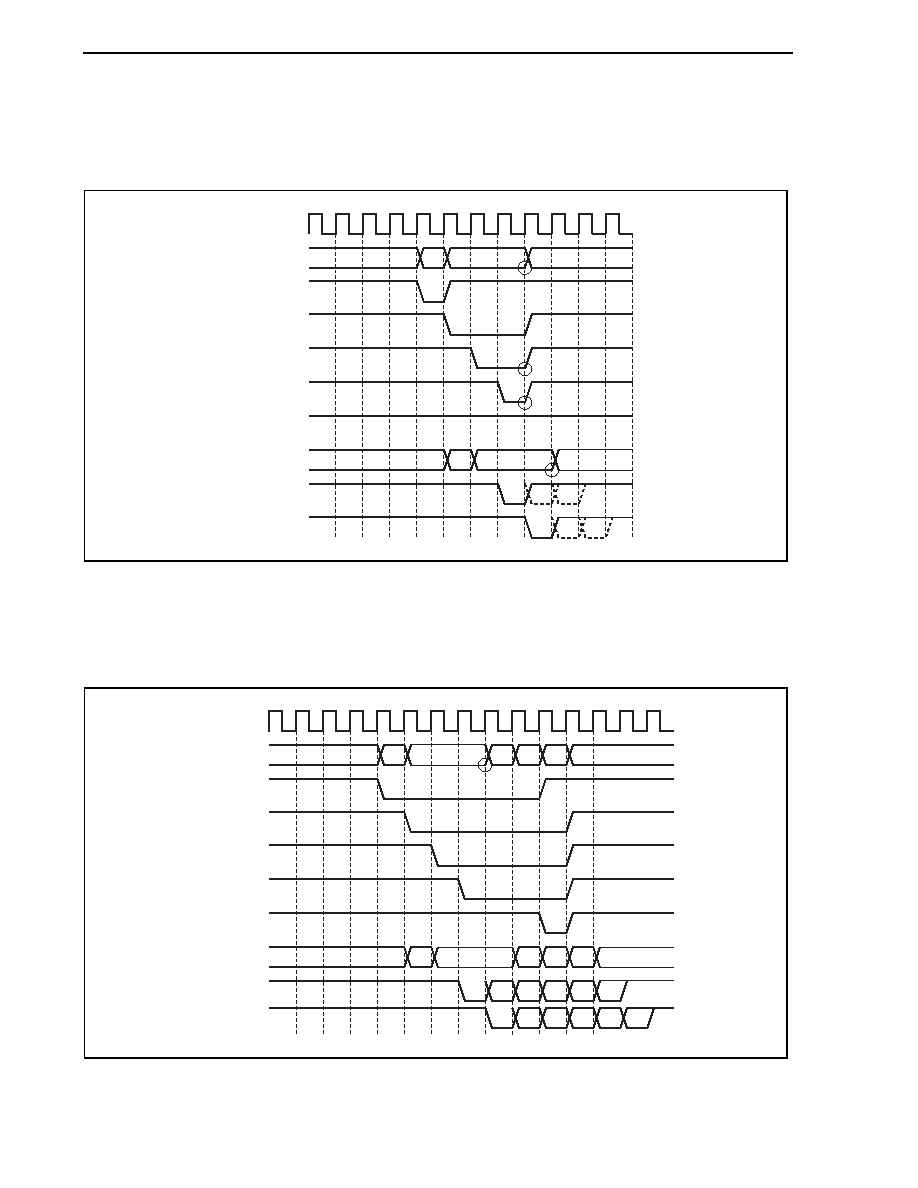

- 3.8.1 External bus interface timing

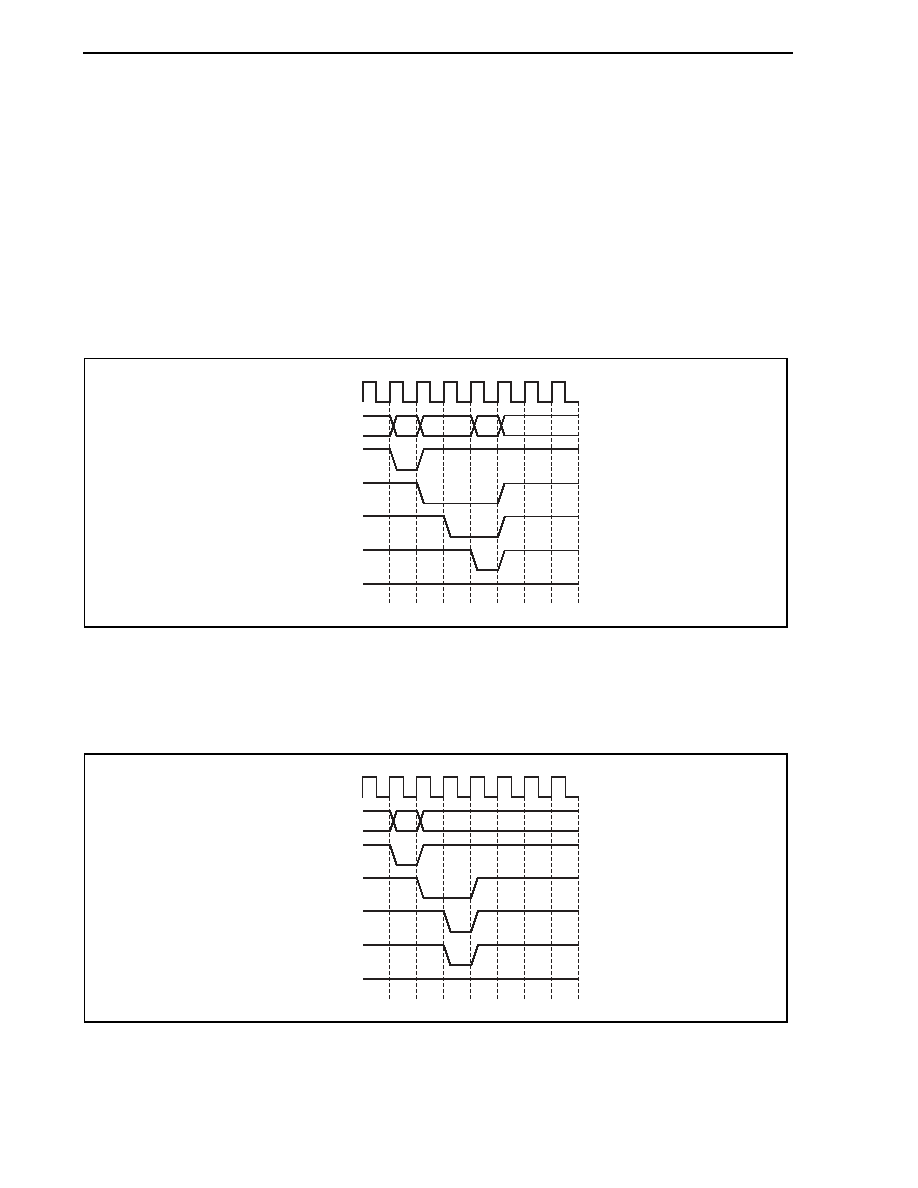

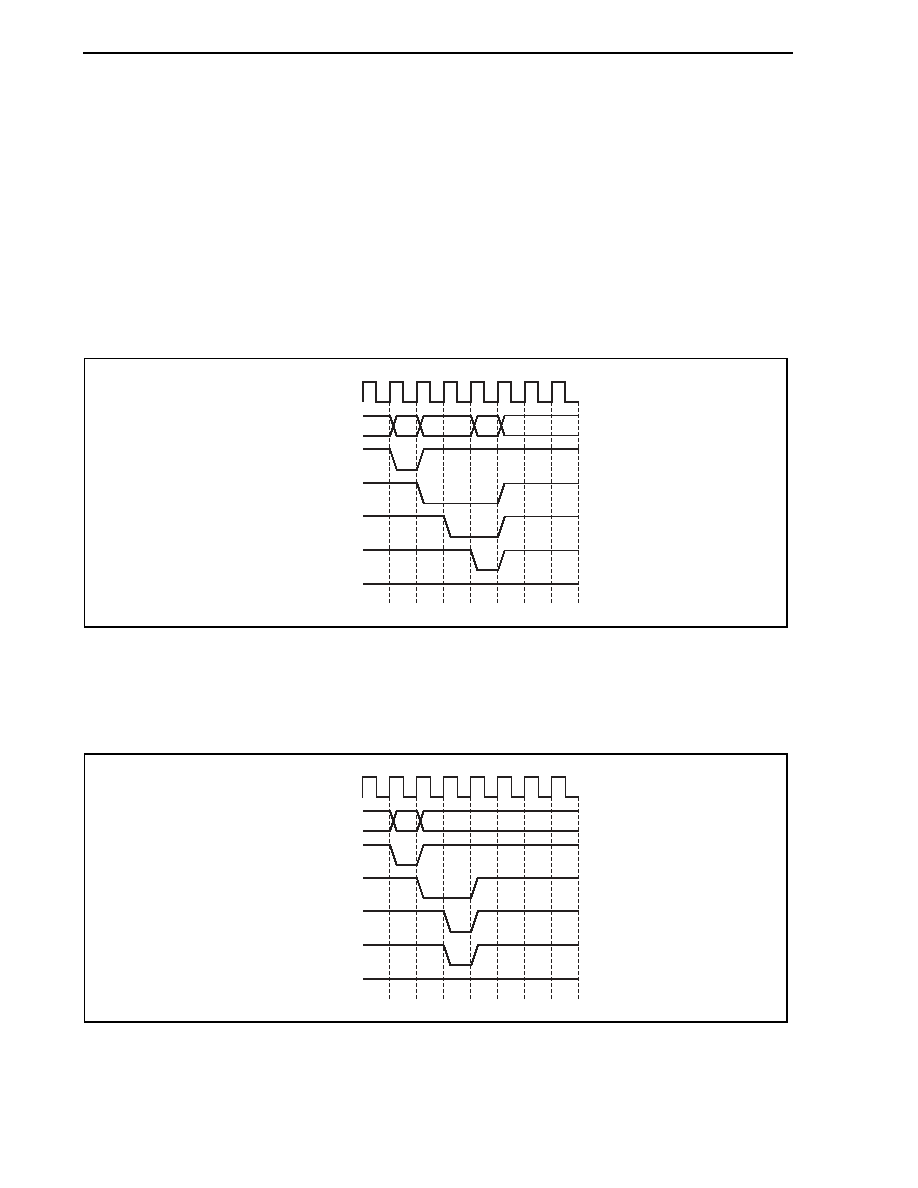

- 3.8.2 PCI bus interface timing

- CHAPTER 4 CONFIGURATION EXAMPLES OF FPGA INTEGRATION

- 4.1 Conditions for Configuration Examples of FPGA Integration

- 4.2 Points to Remember When Creating Top Layer of FPGA

- 4.3 Reference Diagram for FPGA Top Connection

- 4.4 FPGA Top Pin Functions

- 4.4.1 CPU bus slave interface pins

- 4.4.2 SDRAM bus interface pins

- 4.4.3 PCI bus interface pins

- 4.5 FPGA Top Pin Configuration

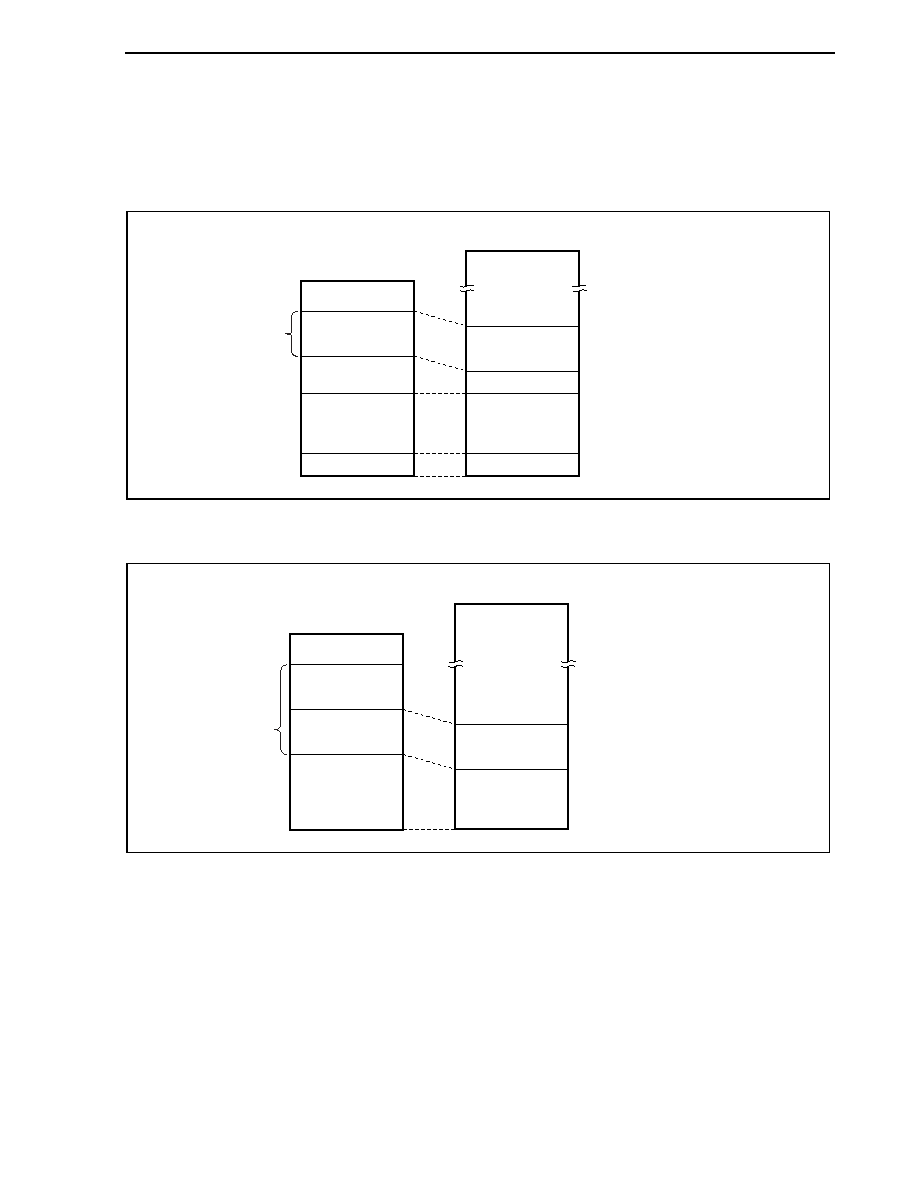

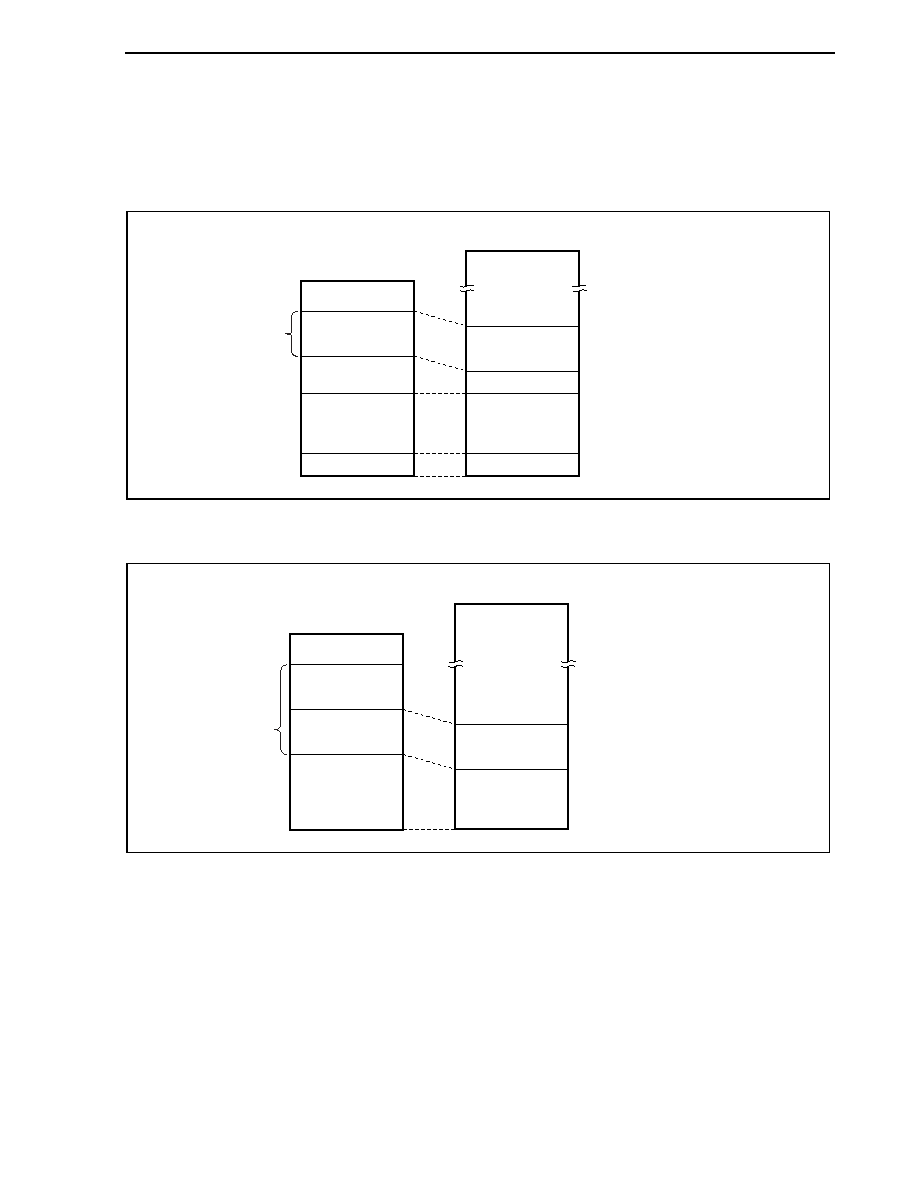

- 4.5.1 Internal connection diagram of external bus interface

- 4.5.2 Internal connection diagram of PCI bus interface

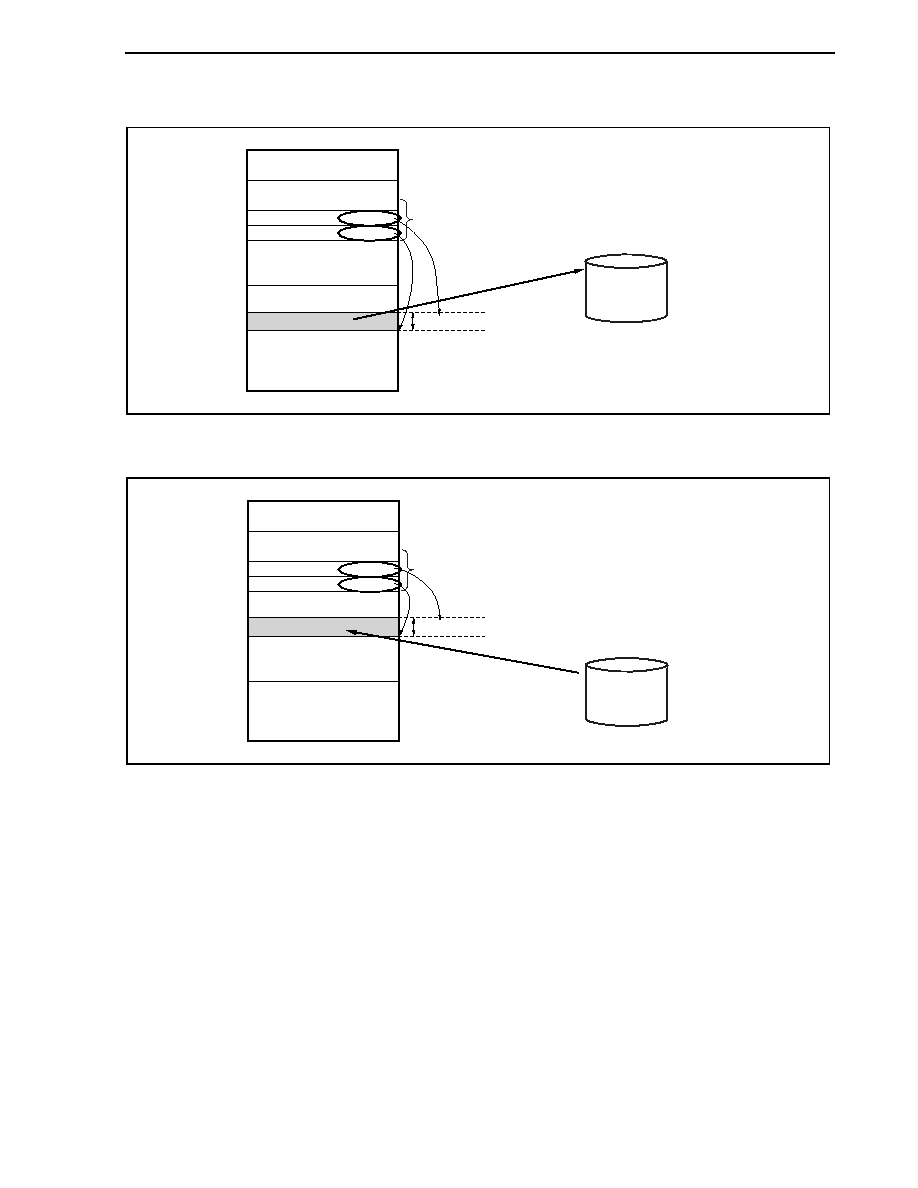

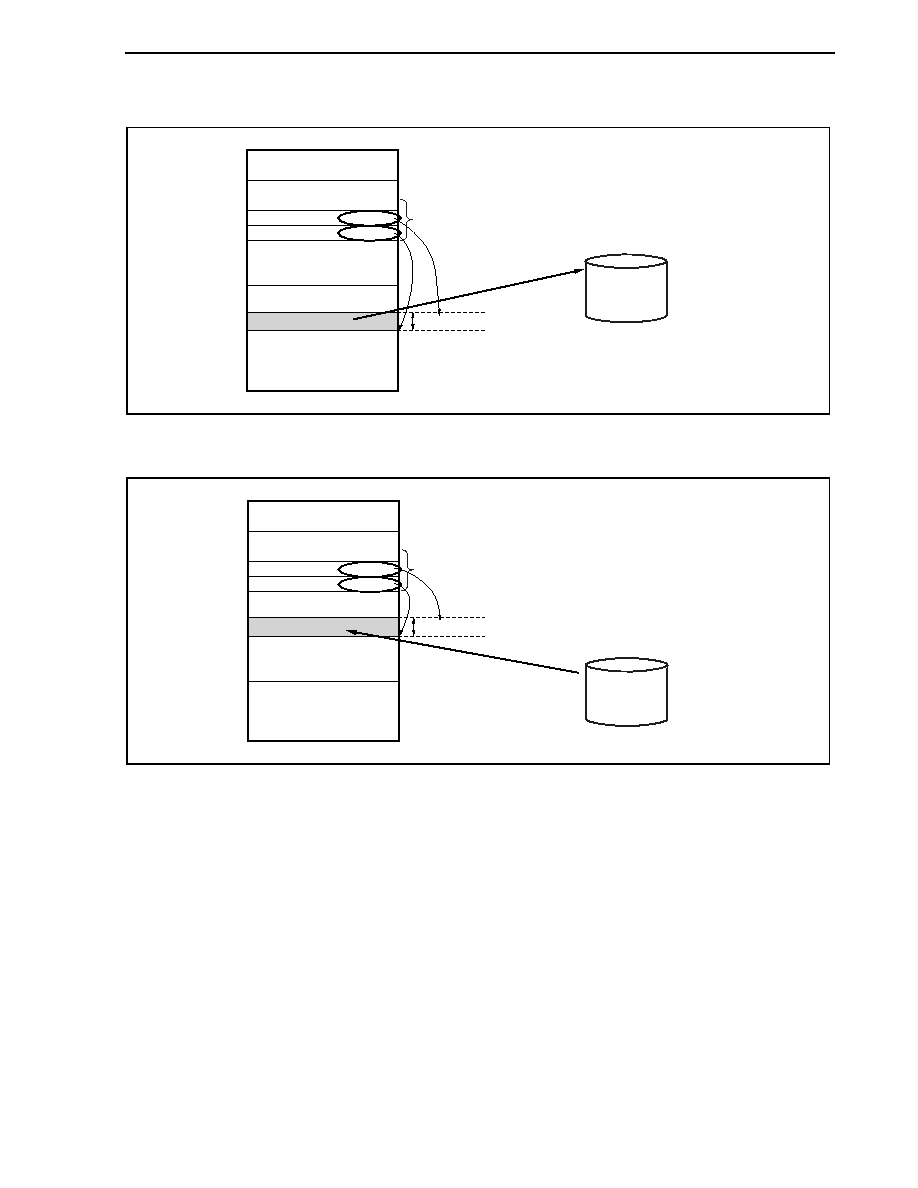

- 4.5.3 External connection diagram of external bus interface (example of connection with V850E/ME2)

- 4.5.4 External connection diagram of PCI bus interface

- 4.6 Cautions on Designing FPGA

- 4.6.1 FPGA fitting design

- 4.6.2 PCI bus interface timing parameters (as constraint of PCI CLK = 33 MHz)

- 4.6.3 SDRAM interface timing

- CHAPTER 5 APPLICATION EXAMPLES

- 5.1 Block Diagram of Evaluation Board

- 5.2 Specifications of Evaluation Board

- 5.3 Example of Evaluation Board Connection Circuit

- 5.4 Evaluation Board Memory Space

- 5.5 Sample Program Examples

- 5.5.1 Development tools

- 5.5.2 Program configuration

- 5.5.3 V850E/ME2 PCI host bridge macro initialization sample program list

- 5.5.4 PCI configuration space access sample program list

- 5.5.5 IDE HDD access sample program list

Application Note

V850E/MA1, V850E/MA2, V850E/MA3, V850E/ME2

32-Bit Single-Chip Microcontrollers

PCI Host Bridge Macro

Document No. U17121EJ1V1AN00 (1st edition)

Date Published September 2004 N CP(K)

Printed in Japan

2004

V850E/MA1: V850E/MA2: V850E/MA3: V850E/ME2:

�

PD703103A

�

PD703108

�

PD703131A

�

PD703111A

�

PD703105A

�

PD703131AY

�

PD703106A

�

PD703132A

�

PD703106A(A)

�

PD703132AY

�

PD703107A

�

PD703133A

�

PD703107A(A)

�

PD703133AY

�

PD70F3107A

�

PD703134A

�

PD70F3107A(A)

�

PD703134AY

�

PD70F3134A

�

PD70F3134AY

Application Note U17121EJ1V1AN

2

[MEMO]

Application Note U17121EJ1V1AN

3

1

2

3

4

VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the

CMOS device stays in the area between V

IL

(MAX) and V

IH

(MIN) due to noise, etc., the device may

malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed,

and also in the transition period when the input level passes through the area between V

IL

(MAX) and

V

IH

(MIN).

HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is

possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS

devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed

high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to V

DD

or GND

via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must

be judged separately for each device and according to related specifications governing the device.

PRECAUTION AGAINST ESD

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and

ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as

much as possible, and quickly dissipate it when it has occurred. Environmental control must be

adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that

easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static

container, static shielding bag or conductive material. All test and measurement tools including work

benches and floors should be grounded. The operator should be grounded using a wrist strap.

Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for

PW boards with mounted semiconductor devices.

STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power

source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does

not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the

reset signal is received. A reset operation must be executed immediately after power-on for devices

with reset functions.

POWER ON/OFF SEQUENCE

In the case of a device that uses different power supplies for the internal operation and external

interface, as a rule, switch on the external power supply after switching on the internal power supply.

When switching the power supply off, as a rule, switch off the external power supply and then the

internal power supply. Use of the reverse power on/off sequences may result in the application of an

overvoltage to the internal elements of the device, causing malfunction and degradation of internal

elements due to the passage of an abnormal current.

The correct power on/off sequence must be judged separately for each device and according to related

specifications governing the device.

INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current

injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and

the abnormal current that passes in the device at this time may cause degradation of internal elements.

Input of signals during the power off state must be judged separately for each device and according to

related specifications governing the device.

NOTES FOR CMOS DEVICES

5

6

Application Note U17121EJ1V1AN

4

The copyright of the PCI host bridge macro described in this document is held by the System Interface Module

Development Department, Device Solutions Division, NEC Engineering, Ltd.

Green Hills Software and MULTI are trademarks of Green Hills Software, Inc.

These commodities, technology or software, must be exported in accordance

with the export administration regulations of the exporting country.

Diversion contrary to the law of that country is prohibited.

The information in this document is current as of March, 2004. The information is subject to change

without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or

data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all

products and/or types are available in every country. Please check with an NEC Electronics sales

representative for availability and additional information.

No part of this document may be copied or reproduced in any form or by any means without the prior

written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may

appear in this document.

NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual

property rights of third parties by or arising from the use of NEC Electronics products listed in this document

or any other liability arising from the use of such products. No license, express, implied or otherwise, is

granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

Descriptions of circuits, software and other related information in this document are provided for illustrative

purposes in semiconductor product operation and application examples. The incorporation of these

circuits, software and information in the design of a customer's equipment shall be done under the full

responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by

customers or third parties arising from the use of these circuits, software and information.

While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products,

customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To

minimize risks of damage to property or injury (including death) to persons arising from defects in NEC

Electronics products, customers must incorporate sufficient safety measures in their design, such as

redundancy, fire-containment and anti-failure features.

NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and

"Specific".

The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-

designated "quality assurance program" for a specific application. The recommended applications of an NEC

Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of

each NEC Electronics product before using it in a particular application.

"Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio

and visual equipment, home electronic appliances, machine tools, personal electronic equipment

and industrial robots.

"Special":

Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster

systems, anti-crime systems, safety equipment and medical equipment (not specifically designed

for life support).

"Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life

support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC

Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications

not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to

determine NEC Electronics' willingness to support a given application.

(Note)

(1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its

majority-owned subsidiaries.

(2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics

(as defined above).

�

�

�

�

�

�

M8E 02. 11-1

Application Note U17121EJ1V1AN

5

Regional Information

�

Device availability

�

Ordering information

�

Product release schedule

�

Availability of related technical literature

�

Development environment specifications (for example, specifications for third-party tools and

components, host computers, power plugs, AC supply voltages, and so forth)

�

Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary

from country to country.

[GLOBAL SUPPORT]

http://www.necel.com/en/support/support.html

NEC Electronics America, Inc. (U.S.)

Santa Clara, California

Tel: 408-588-6000

800-366-9782

NEC Electronics Hong Kong Ltd.

Hong Kong

Tel: 2886-9318

NEC Electronics Hong Kong Ltd.

Seoul Branch

Seoul, Korea

Tel: 02-558-3737

NEC Electronics Shanghai Ltd.

Shanghai, P.R. China

Tel: 021-5888-5400

NEC Electronics Taiwan Ltd.

Taipei, Taiwan

Tel: 02-2719-2377

NEC Electronics Singapore Pte. Ltd.

Novena Square, Singapore

Tel: 6253-8311

J04.1

NEC Electronics (Europe) GmbH

Duesseldorf, Germany

Tel: 0211-65030

�

Sucursal en Espa�a

Madrid, Spain

Tel: 091-504 27 87

V�lizy-Villacoublay, France

Tel: 01-30-67 58 00

�

Succursale Fran�aise

�

Filiale Italiana

Milano, Italy

Tel: 02-66 75 41

�

Branch The Netherlands

Eindhoven, The Netherlands

Tel: 040-244 58 45

�

Tyskland Filial

Taeby, Sweden

Tel: 08-63 80 820

�

United Kingdom Branch

Milton Keynes, UK

Tel: 01908-691-133

Some information contained in this document may vary from country to country. Before using any NEC

Electronics product in your application, pIease contact the NEC Electronics office in your country to

obtain a list of authorized representatives and distributors. They will verify:

Application Note U17121EJ1V1AN

6

INTRODUCTION

Readers

This application note is intended for users who wish to understand the functions of the

V850E/MA1, V850E/MA2, V850E/MA3, V850E/ME2, and PCI bus to design application

systems using these products.

Purpose

The purpose of this application note is to help the user understand the PCI host bridge

macro and its composition using the V850E/MA1, V850E/MA2, V850E/MA3,

V850E/ME2, and PCI host bridge macro as a system example.

Organization

This application note is broadly divided into the following sections.

�

Overview of each product

�

Overview of PCI host bridge macro

�

Specifications of PCI host bridge macro

�

Configuration examples of FPGA integration

�

Application examples

How to Read This Manual It is assumed that the readers of this application note have general knowledge in the

fields of electrical engineering, logic circuits, and microcontrollers.

For details of the hardware functions and electrical specifications of the V850E/MA1,

V850E/MA2, V850E/MA3, and V850E/ME2

Refer to the Hardware User's Manual of each product.

For details of the instruction functions of the V850E/MA1, V850E/MA2, V850E/MA3, and

V850E/ME2

Refer to the V850E1 Architecture User's Manual.

Conventions

Data significance:

Higher digits on the left and lower digits on the right

Active low representation: xxx (overscore over pin or signal name) or /xxx ("/" before

signal

name)

Memory map address:

Higher addresses on the top and lower addresses on the

bottom

Note:

Footnote for item marked with Note in the text

Caution:

Information requiring particular attention

Remark: Supplementary

information

Numeric representation:

Binary ... xxxx or xxxxB

Decimal ... xxxx

Hexadecimal ... xxxxH

Prefix indicating power of 2 (address space, memory capacity):

K (kilo) ... 2

10

= 1,024

M (mega) ... 2

20

= 1,024

2

G (giga) ... 2

30

= 1,024

3

Application Note U17121EJ1V1AN

7

Related Documents

The related documents indicated in this publication may include preliminary versions.

However, preliminary versions are not marked as such.

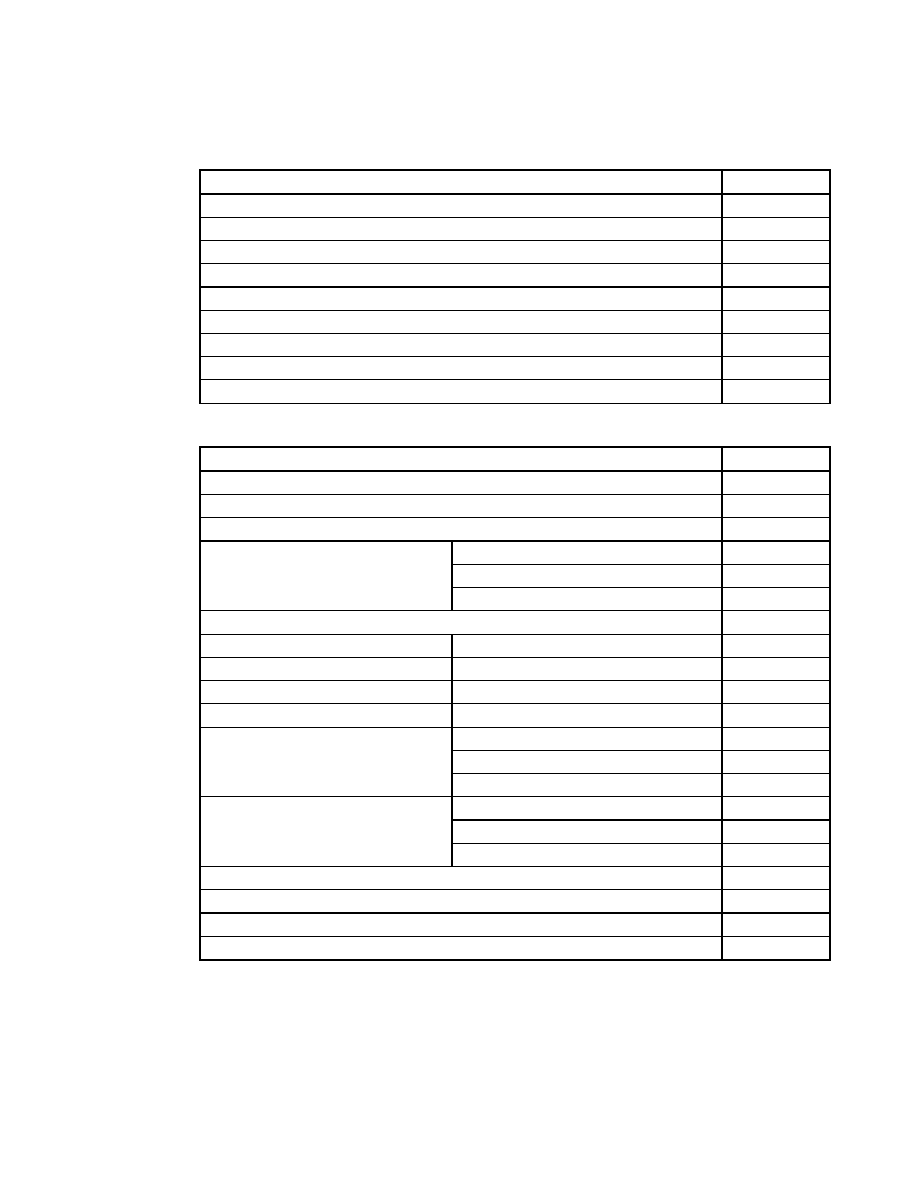

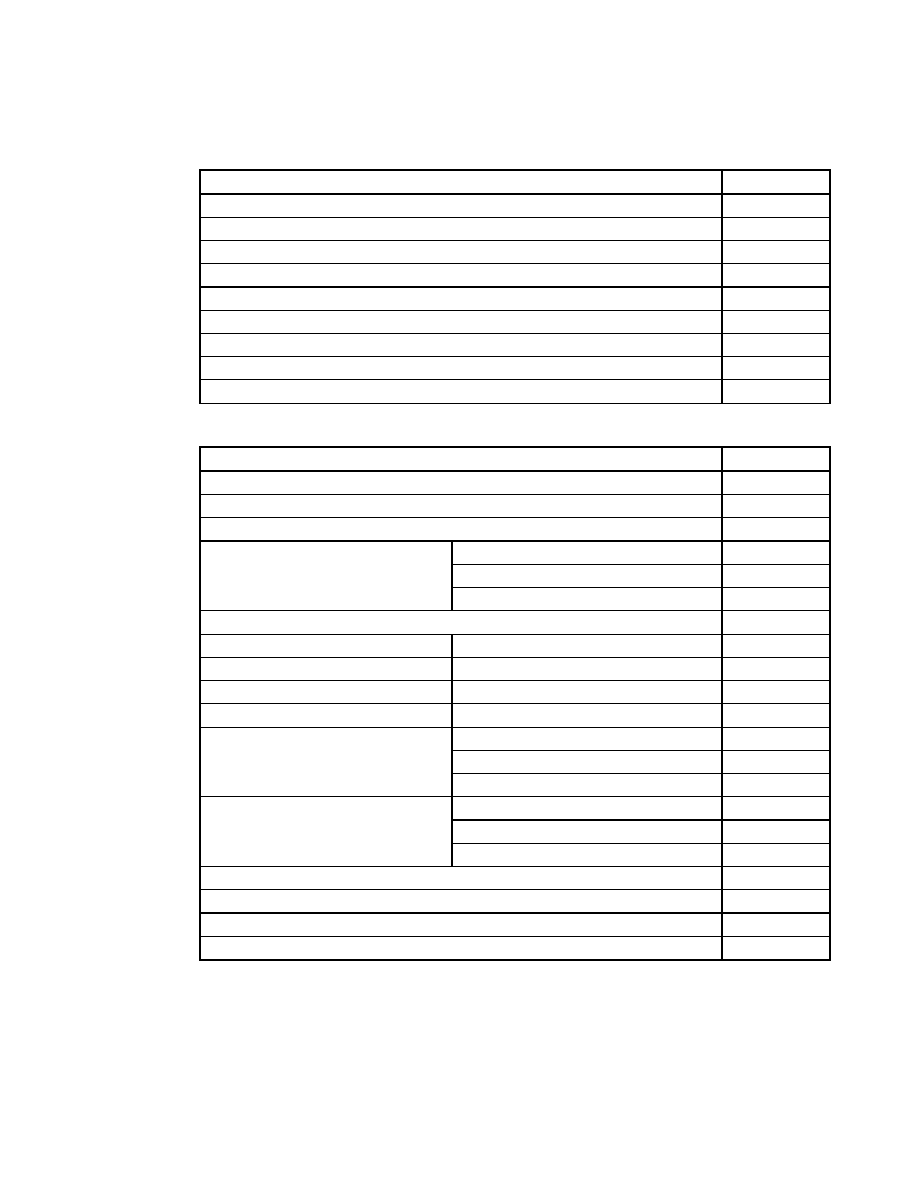

Documents related to V850E/MA1, V850E/MA2, V850E/MA3, and V850E/ME2

Document Name

Document No.

V850E1 Architecture User's Manual

U14559E

V850E/MA1 Hardware User's Manual

U14359E

V850E/MA1 Hardware Application Note

U15179E

V850E/MA2 Hardware User's Manual

U14980E

V850E/MA3 Hardware User's Manual

U16397E

V850E/ME2 Hardware User's Manual

U16031E

V850E/ME2 Hardware Application Note

U16794E

V850E/ME2 USB Function Driver Application Note

U17069E

V850E/MA1, V850E/MA2, V850E/MA3, V850E/ME2 PCI Host Bridge Macro Application Note

This manual

Documents related to development tools (user's manuals)

Document Name

Document No.

IE-V850E-MC, IE-V850E-MC-A In-Circuit Emulator

U14487E

IE-703107-MC-EM1 In-Circuit Emulator Option Board

U14481E

IE-V850E1-CD-NW PCMCIA Card Type On-Chip Debug Emulator

U16647E

Operation U16053E

C Language

U16054E

CA850 Ver.2.50 C Compiler Package

Assembly Language

U16042E

PM plus Ver.5.20

U16934E

ID850 Ver.2.50 Integrated Debugger

Operation

U16217E

ID850NW Ver.2.51 Integrated Debugger

Operation

U16454E

SM850 Ver.2.40 System Simulator

Operation

U15182E

SM850 Ver.2.00 or Later System Simulator

External Part User Open Interface Specifications U14873E

Basics U13430E

Installation U13410E

RX850 Ver.3.13 or Later Real-Time OS

Technical U13431E

Basics U13773E

Installation U13774E

RX850 Pro Ver.3.15 Real-Time OS

Technical U13772E

RD850 Ver.3.01 Task Debugger

U13737E

RD850 Pro Ver.3.01 Task Debugger

U13916E

AZ850 Ver.3.10 System Performance Analyzer

U14410E

PG-FP4 Flash Memory Programmer

U15260E

Application Note U17121EJ1V1AN

8

CONTENTS

CHAPTER 1 OVERVIEW OF EACH PRODUCT..................................................................................10

1.1 Outline ...........................................................................................................................................10

1.2 Features.........................................................................................................................................11

1.3 Ordering Information....................................................................................................................12

1.4 Pin Configuration..........................................................................................................................14

1.5 Internal Block Diagram ................................................................................................................25

CHAPTER 2 OVERVIEW OF PCI HOST BRIDGE MACRO ..............................................................29

2.1 Outline ...........................................................................................................................................29

2.2 Features.........................................................................................................................................30

CHAPTER 3 SPECIFICATIONS OF PCI HOST BRIDGE MACRO ...................................................31

3.1 Internal Blocks of PCI Host Bridge Macro .................................................................................31

3.2 Relationship Between Internal Blocks and Signals ..................................................................32

3.3 Pin Functions ................................................................................................................................33

3.3.1 External bus slave interface pins .......................................................................................................33

3.3.2 SDRAM

bus

interface pins .................................................................................................................33

3.3.3 PCI bus interface pins ........................................................................................................................34

3.4 Registers .......................................................................................................................................35

3.4.1 PCI_CONFIG_DATA register.............................................................................................................35

3.4.2 PCI_CONFIG_ADD register...............................................................................................................36

3.4.3 PCI_CONTROL register.....................................................................................................................37

3.4.4 PCI_IO_BASE register.......................................................................................................................38

3.4.5 PCI_MEM_BASE register ..................................................................................................................38

3.4.6 PCI_INT_CTL register........................................................................................................................39

3.4.7 PCI_ERR_ADD register .....................................................................................................................40

3.4.8 SYSTEM_MEM_BASE register .........................................................................................................41

3.4.9 SYSTEM_MEM_RANGE register ......................................................................................................41

3.4.10 SDRAM_CTL register ........................................................................................................................42

3.5 Address Map .................................................................................................................................44

3.6 Initializing PCI Host Bridge Macro ..............................................................................................45

3.7 Bus Width of External Bus Interface ..........................................................................................46

3.8 Timing ............................................................................................................................................47

3.8.1 External

bus

interface timing..............................................................................................................47

3.8.2 PCI bus interface timing .....................................................................................................................50

CHAPTER 4 CONFIGURATION EXAMPLES OF FPGA INTEGRATION..........................................57

4.1 Conditions for Configuration Examples of FPGA Integration .................................................57

4.2 Points to Remember When Creating Top Layer of FPGA ........................................................57

4.3 Reference Diagram for FPGA Top Connection .........................................................................58

4.4 FPGA Top Pin Functions .............................................................................................................59

4.4.1 CPU bus slave interface pins .............................................................................................................59

4.4.2 SDRAM

bus

interface pins .................................................................................................................59

4.4.3 PCI bus interface pins ........................................................................................................................60

4.5 FPGA Top Pin Configuration.......................................................................................................61

Application Note U17121EJ1V1AN

9

4.5.1 Internal

connection diagram of external bus interface ....................................................................... 61

4.5.2 Internal

connection diagram of PCI bus interface .............................................................................. 62

4.5.3 External

connection

diagram of external bus interface (example of connection with V850E/ME2).... 63

4.5.4 External

connection diagram of PCI bus interface ............................................................................. 64

4.6 Cautions on Designing FPGA .....................................................................................................65

4.6.1 FPGA

fitting design............................................................................................................................ 65

4.6.2 PCI bus interface timing parameters (as constraint of PCI CLK = 33 MHz)....................................... 65

4.6.3 SDRAM

interface timing .................................................................................................................... 66

CHAPTER 5 APPLICATION EXAMPLES..............................................................................................67

5.1 Block Diagram of Evaluation Board ...........................................................................................67

5.2 Specifications of Evaluation Board............................................................................................68

5.3 Example of Evaluation Board Connection Circuit ....................................................................69

5.4 Evaluation Board Memory Space ...............................................................................................70

5.5 Sample Program Examples .........................................................................................................72

5.5.1 Development tools ............................................................................................................................. 72

5.5.2 Program

configuration ....................................................................................................................... 72

5.5.3 V850E/ME2 PCI host bridge macro initialization sample program list ............................................... 73

5.5.4 PCI

configuration space access sample program list ........................................................................ 76

5.5.5 IDE HDD access sample program list................................................................................................ 79

Application Note U17121EJ1V1AN

10

CHAPTER 1 OVERVIEW OF EACH PRODUCT

The V850E/MA1, V850E/MA2, V850E/MA3, and V850E/ME2 are products in NEC Electronics' V850 Series of

single-chip microcontrollers. This chapter gives a simple outline of each product.

1.1 Outline

The V850E/MA1, V850E/MA2, V850E/MA3, and V850E/ME2 are 32-bit single-chip microcontrollers that integrate

the V850E1 CPU, which is a 32-bit RISC-type CPU core for ASIC, newly developed as the CPU core central to

system LSI in the current age of system-on-chip. These devices incorporate memory and various peripheral functions

such as memory controllers, a DMA controller, timer/counters, serial interfaces, and an A/D converter for realizing

high-capacity data processing and sophisticated real-time control.

CHAPTER 1 OVERVIEW OF EACH PRODUCT

Application Note U17121EJ1V1AN

11

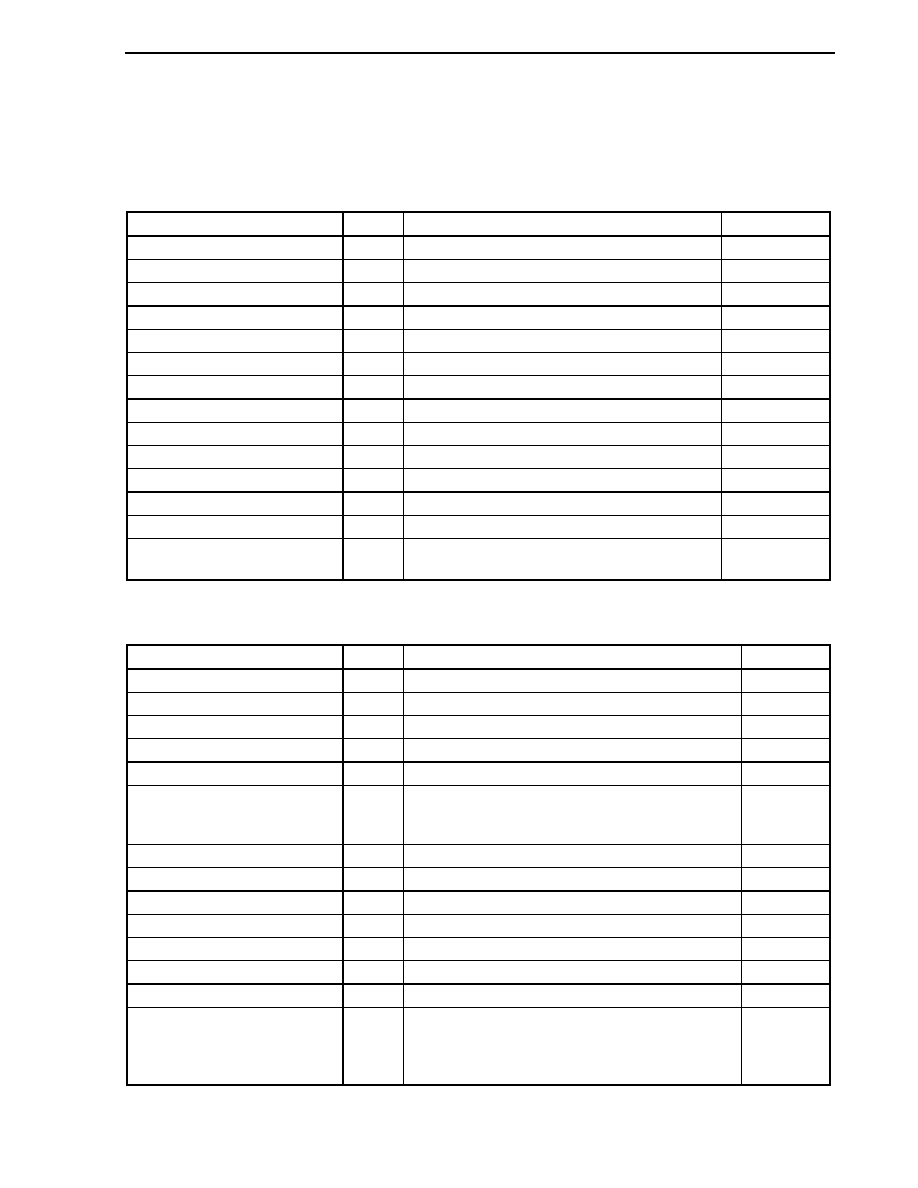

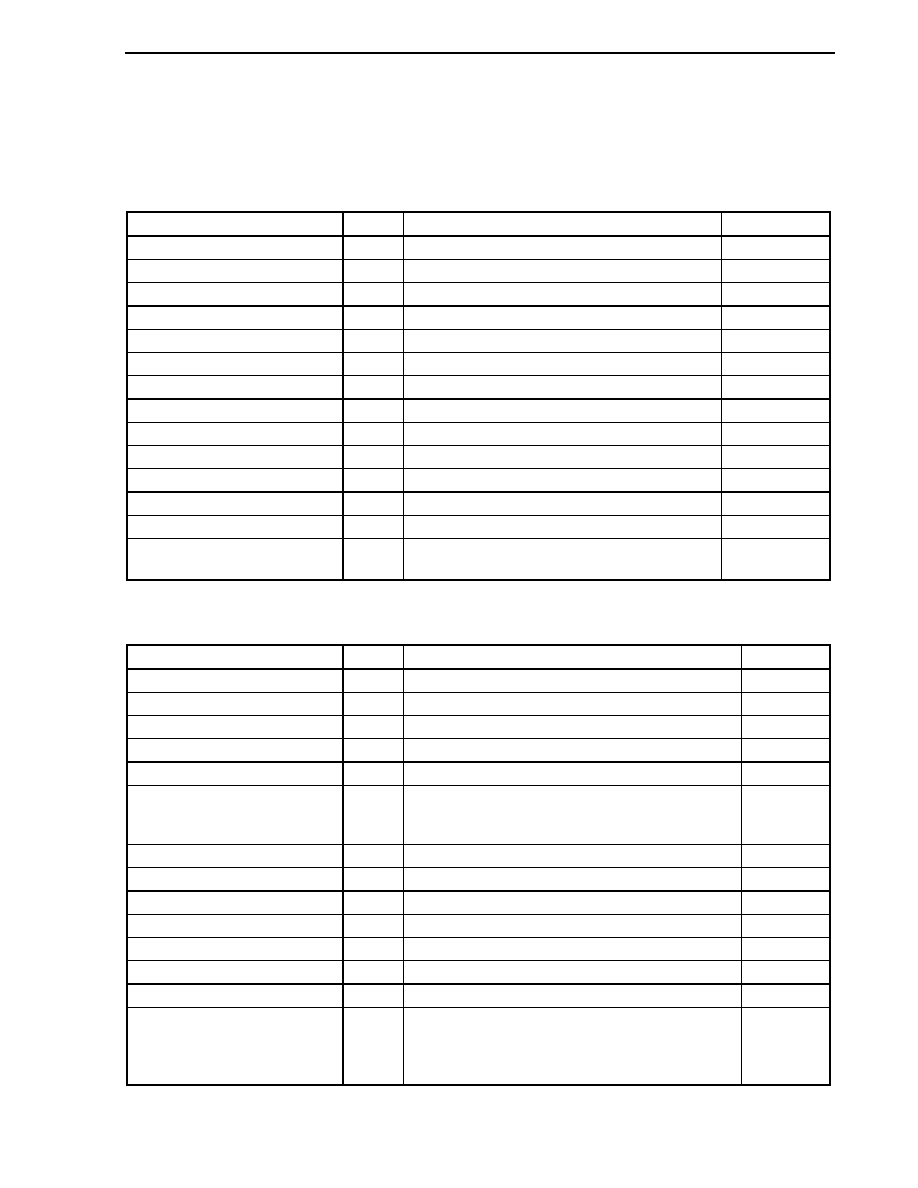

1.2 Features

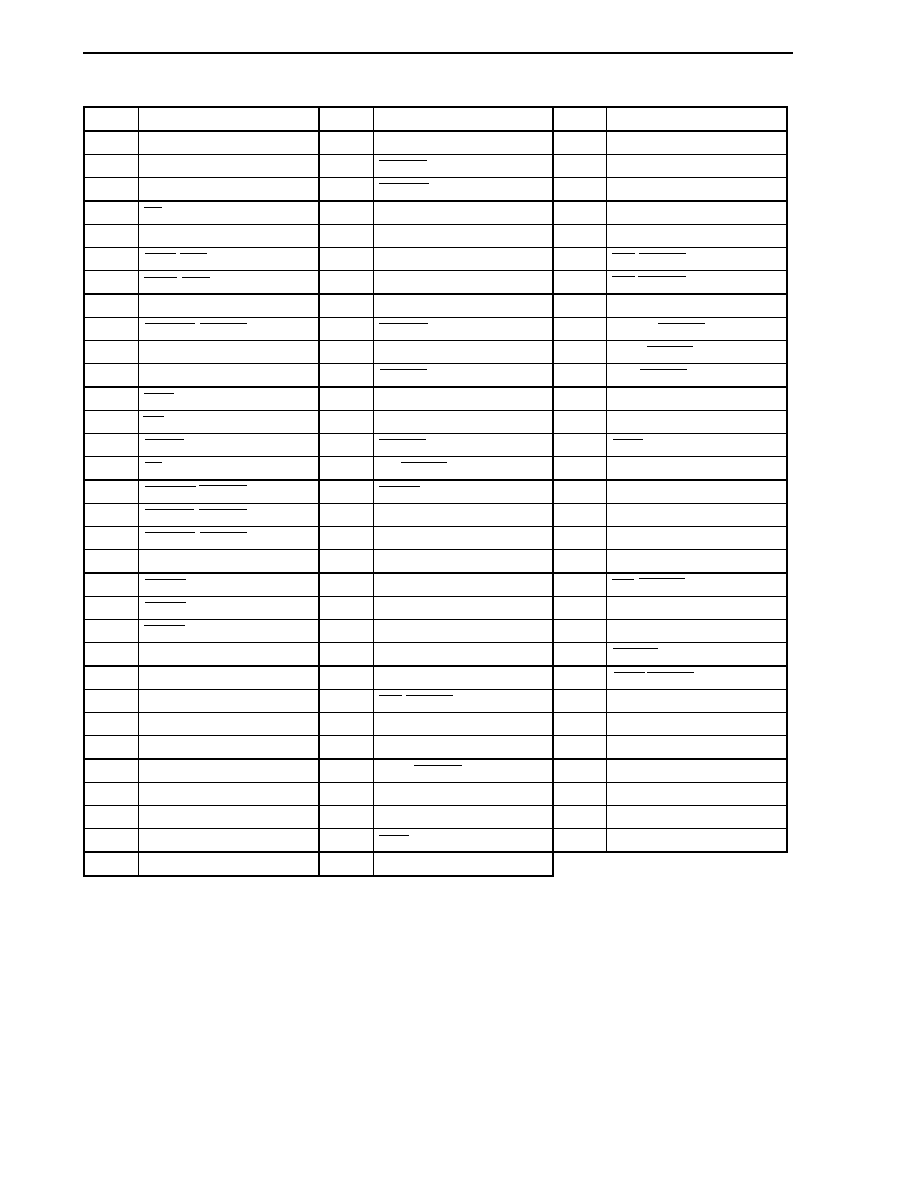

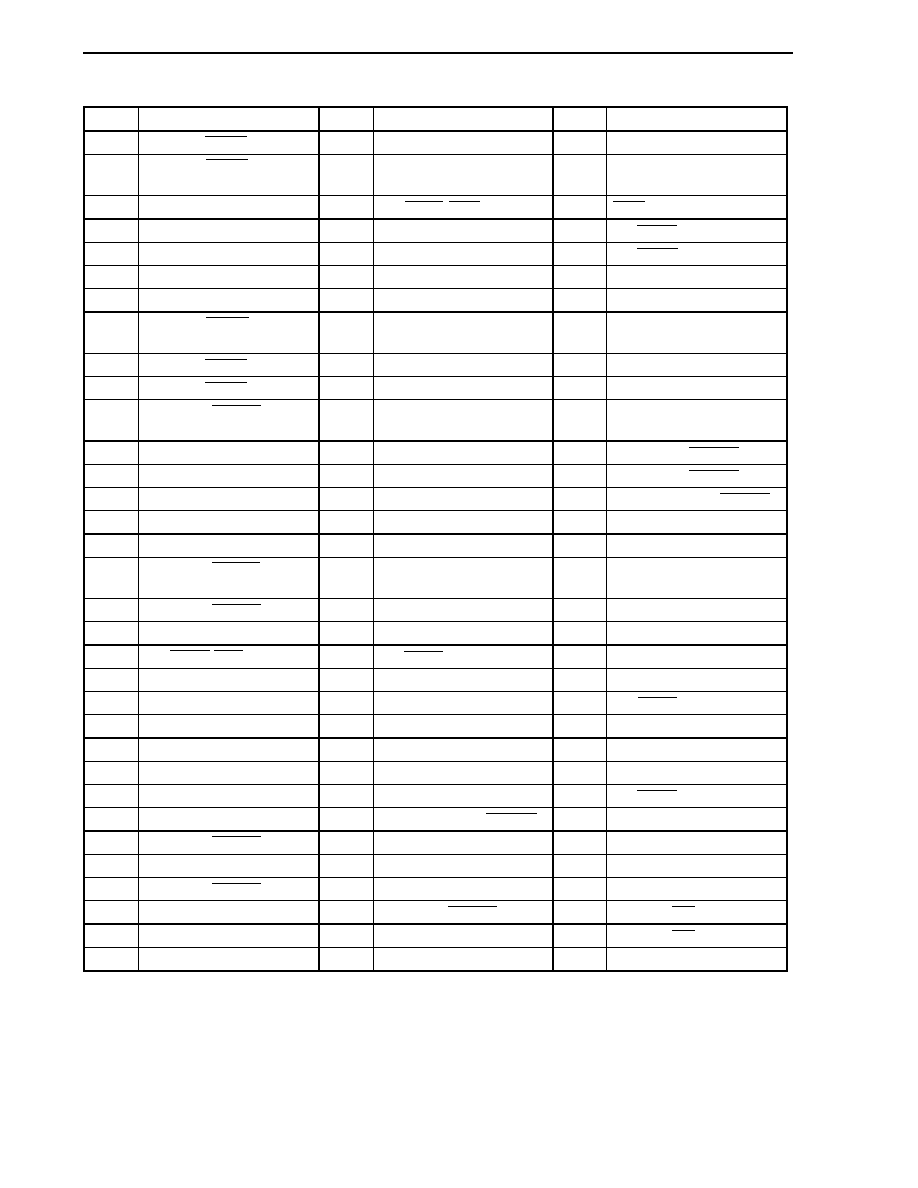

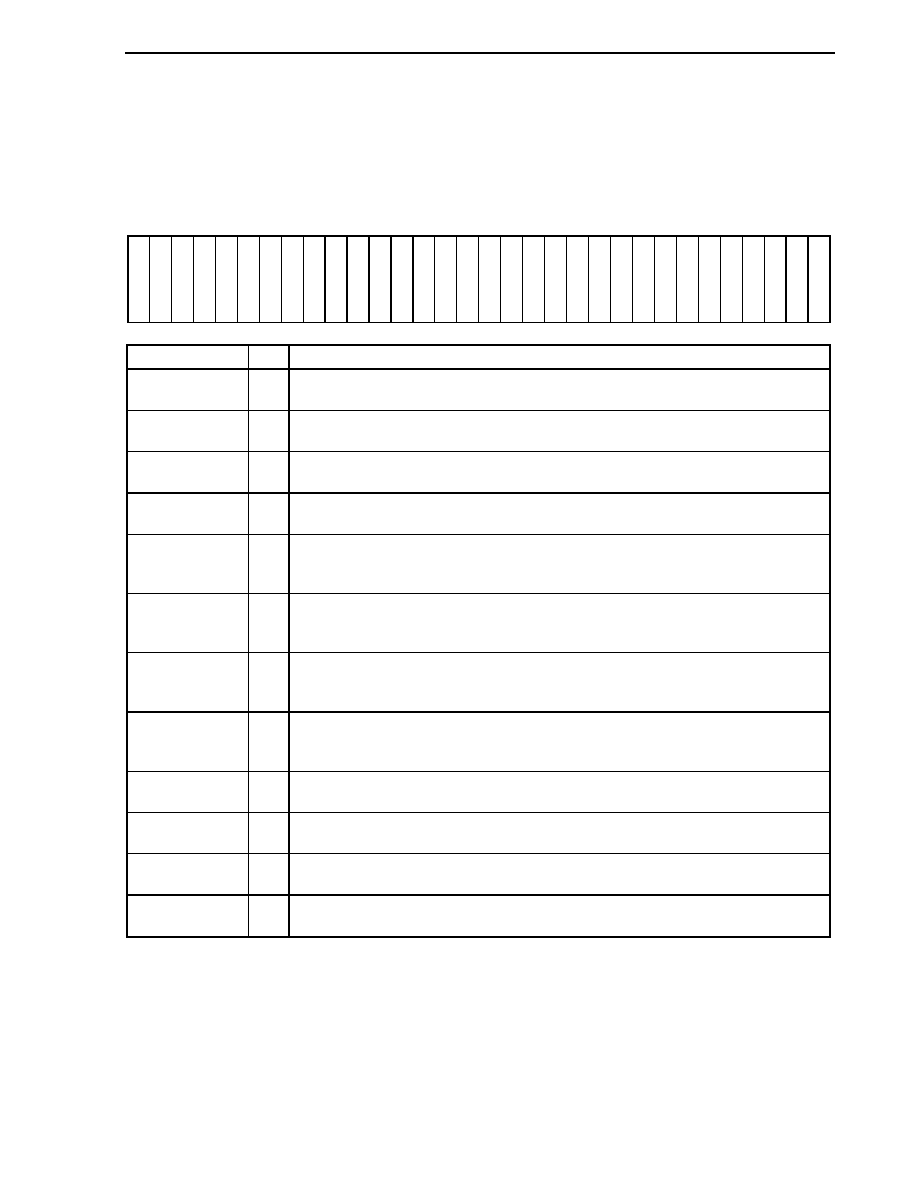

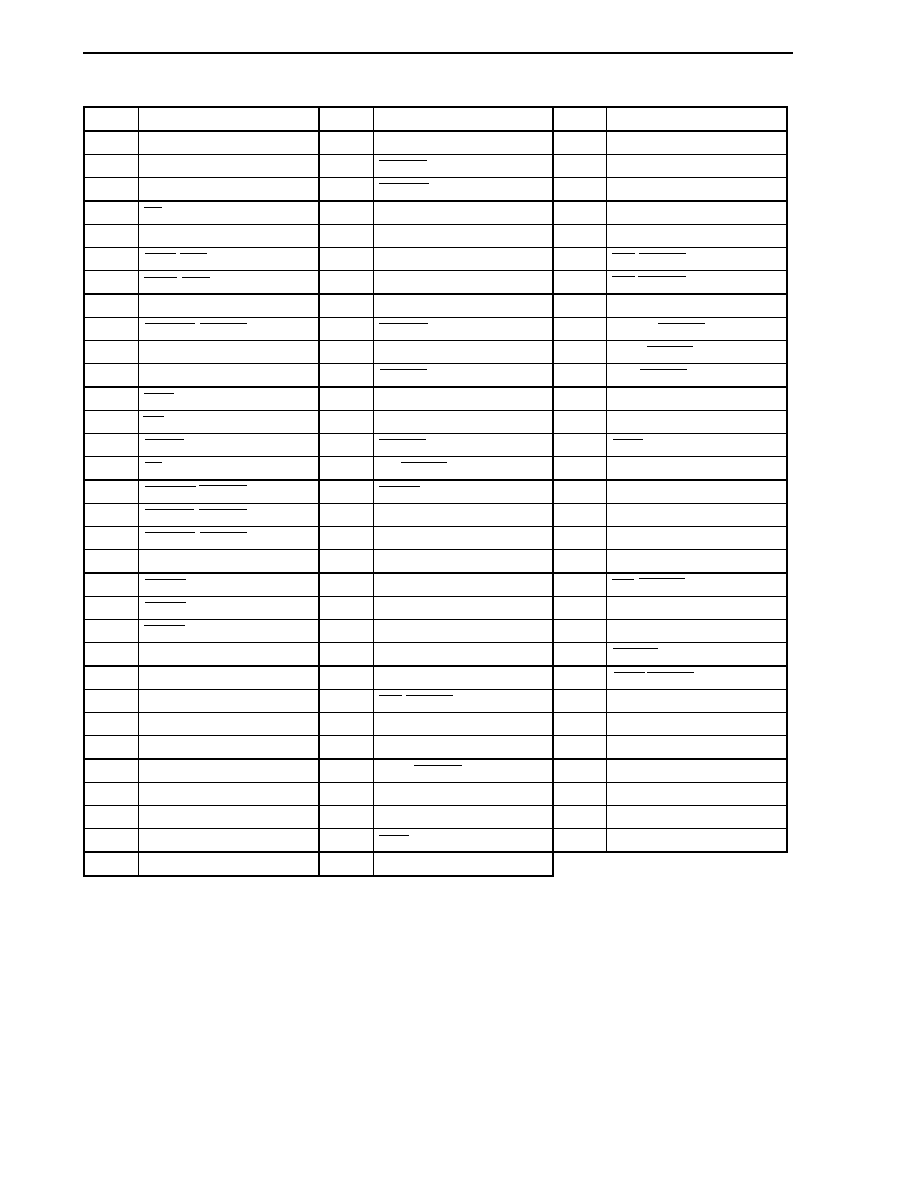

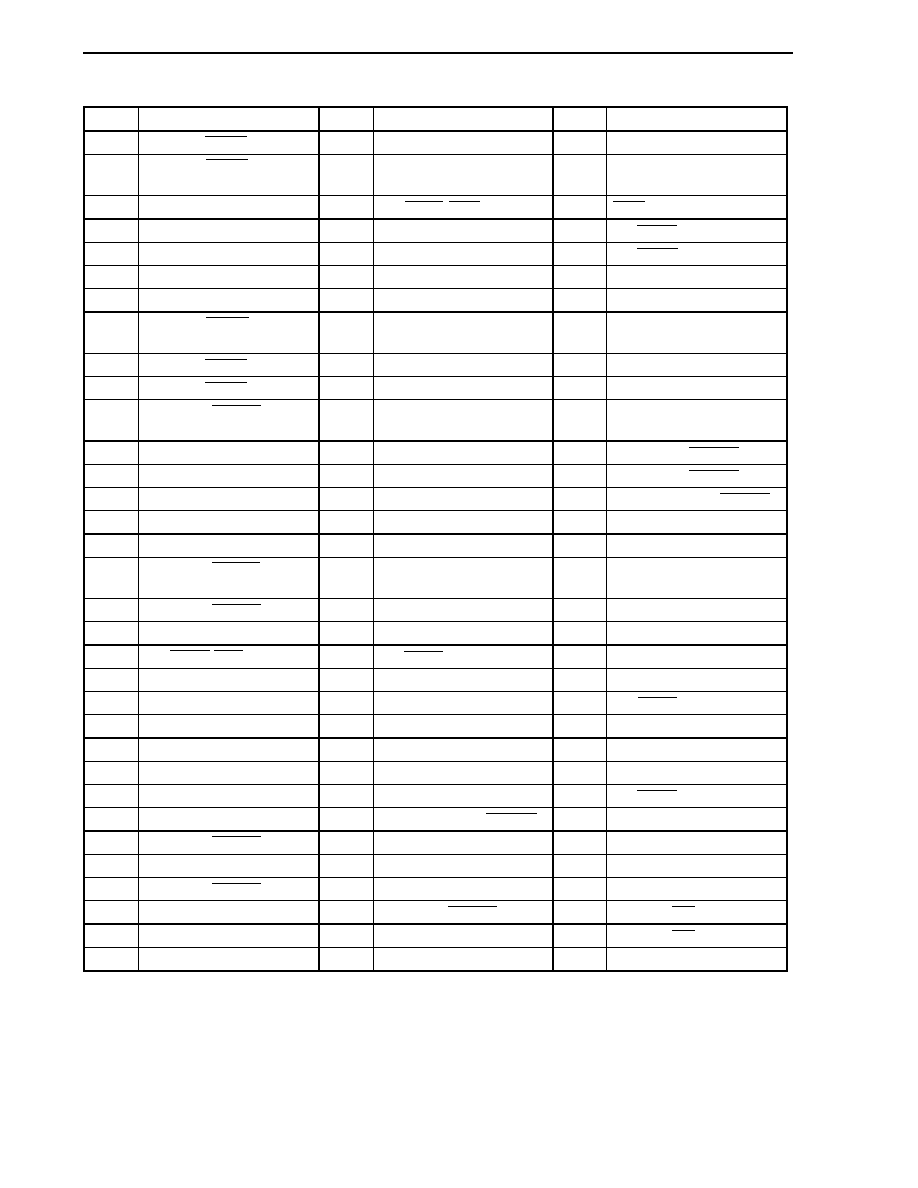

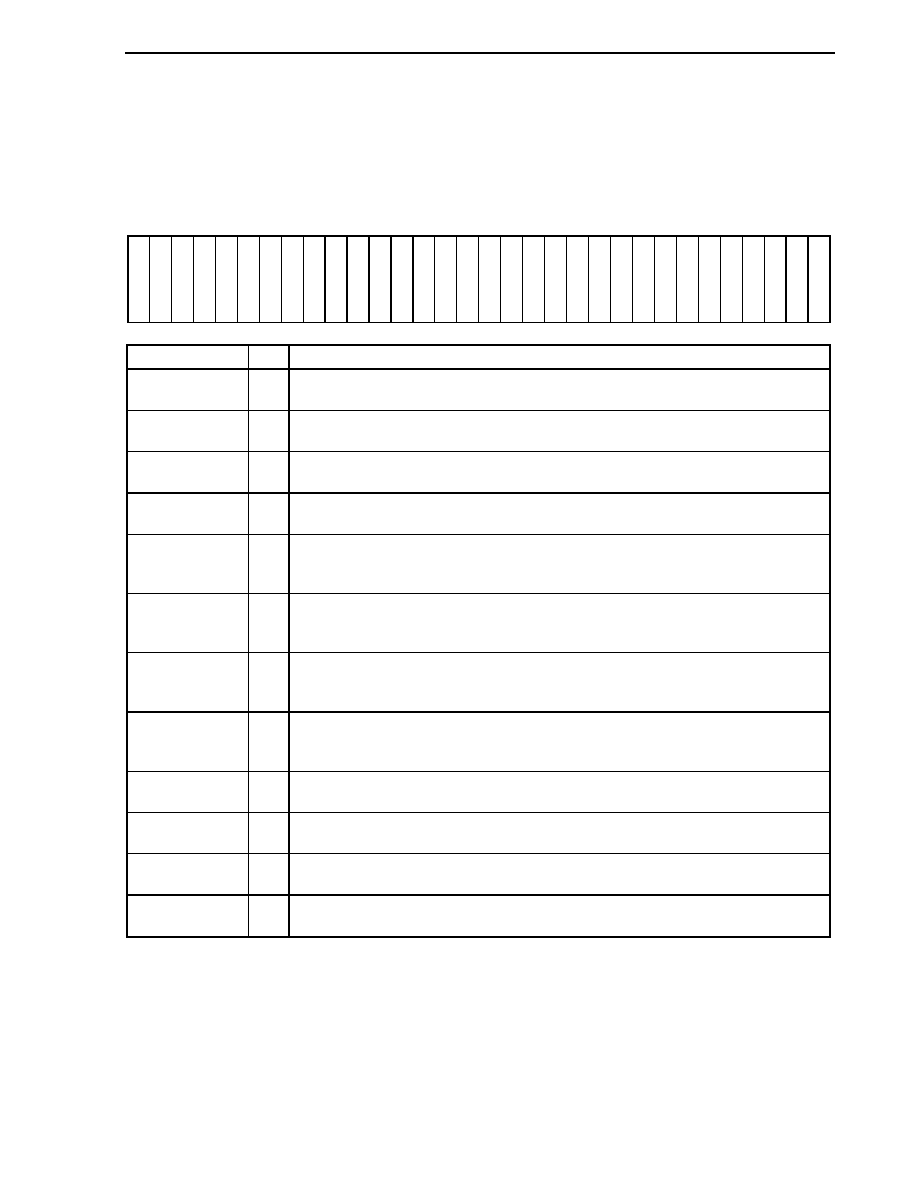

Commercial Name

V850E/MA1

V850E/MA2

V850E/MA3

V850E/ME2

Maximum operating

frequency

50 MHz

40 MHz

80 MHz

150 MHz

Mask ROM

-

128 256

-

-

256 512

-

-

Flash memory

-

256

-

-

512

-

Internal

memory

(KB)

RAM 4

10 4

16

32

16

32

Instruction

RAM:

128

Data RAM: 16

Cache (KB)

-

Instruction cache: 8

Bus type

Separate

Separate

Separate/multiplexed

Separate

Address bus

26 bits

25 bits

26 bits

26 bits

Data bus

8/16 bits

8/16 bits

8/16 bits

16/32 bits

External

bus

Chip select signals 8

4

8

8

Memory controller

SDRAM, EDO DRAM,

SRAM, etc.

SDRAM, SRAM, etc.

External

Note 1

17 (17)

4 (4)

26 (26)

40 (31)

Interrupts

Internal 41

27

49

59

32

�

32

64

20 to 40 ns (50 MHz)

25 to 50 ns (40 MHz)

12.5 to 25 ns (80 MHz) 6.7 to 13.3 ns (150 MHz)

DSP

function

32

�

32 + 32

32 60 ns (50 MHz)

75 ns (40 MHz)

37.5 ns (80 MHz)

20 ns (150 MHz)

TMC

4 ch

2 ch

-

6 ch

TMP

-

-

3 ch

-

TMQ

-

-

1 ch

-

Interval timer

4 ch

4 ch

4 ch

4 ch

16-bit

timer

Up/down counter

-

-

1 ch

2 ch

Watchdog timer

-

-

1 ch

-

CSI 1

ch

-

-

1 ch

UART 1

ch

-

-

1 ch

CSI/UART

2 ch

2 ch

3 ch

1 ch

Serial

interface

UART/I

2

C

-

-

1 ch

Note 2

-

10-bit A/D converter

8 ch

4 ch

8 ch

8 ch

8-bit D/A converter

-

-

2 ch

-

DMA controller

4 ch

4 ch

4 ch

4 ch

CMOS input

9

5

11

7

Ports

CMOS I/O

106

74

101

77

Debug functions

-

-

Provided (RUN, break)

Provided (RUN, break,

trace)

Other peripheral functions

PWM

�

2 ch

-

ROM correction function USB function, SSCG,

PWM

�

2 ch

Power supply voltage

3.0 to 3.6 V

2.3 to 2.7 V (internal)

3.0 to 3.6 V (external)

1.5 V (internal)

3.3 V (external)

Power consumption

(mask version TYP.)

528 mW

416 mW

575 mW

200 mW

Package

144-pin LQFP (20

�

20)

161-pin FBGA (13

�

13)

100-pin LQFP (14

�

14) 144-pin LQFP (20

�

20)

161-pin FBGA (13

�

13)

176-pin LQFP (20

�

20)

240-pin FBGA (16

�

16)

Operating ambient

temperature

T

A

=

-

40 to +85

�

C T

A

=

-

40 to +85

�

C

(@133 MHz)

T

A

=

-

40 to +70

�

C

(@150 MHz)

Notes 1. The figure in parentheses indicates the number of external interrupts that can release STOP mode.

2. Available only in on-chip I

2

C products (Y products).

CHAPTER 1 OVERVIEW OF EACH PRODUCT

Application Note U17121EJ1V1AN

12

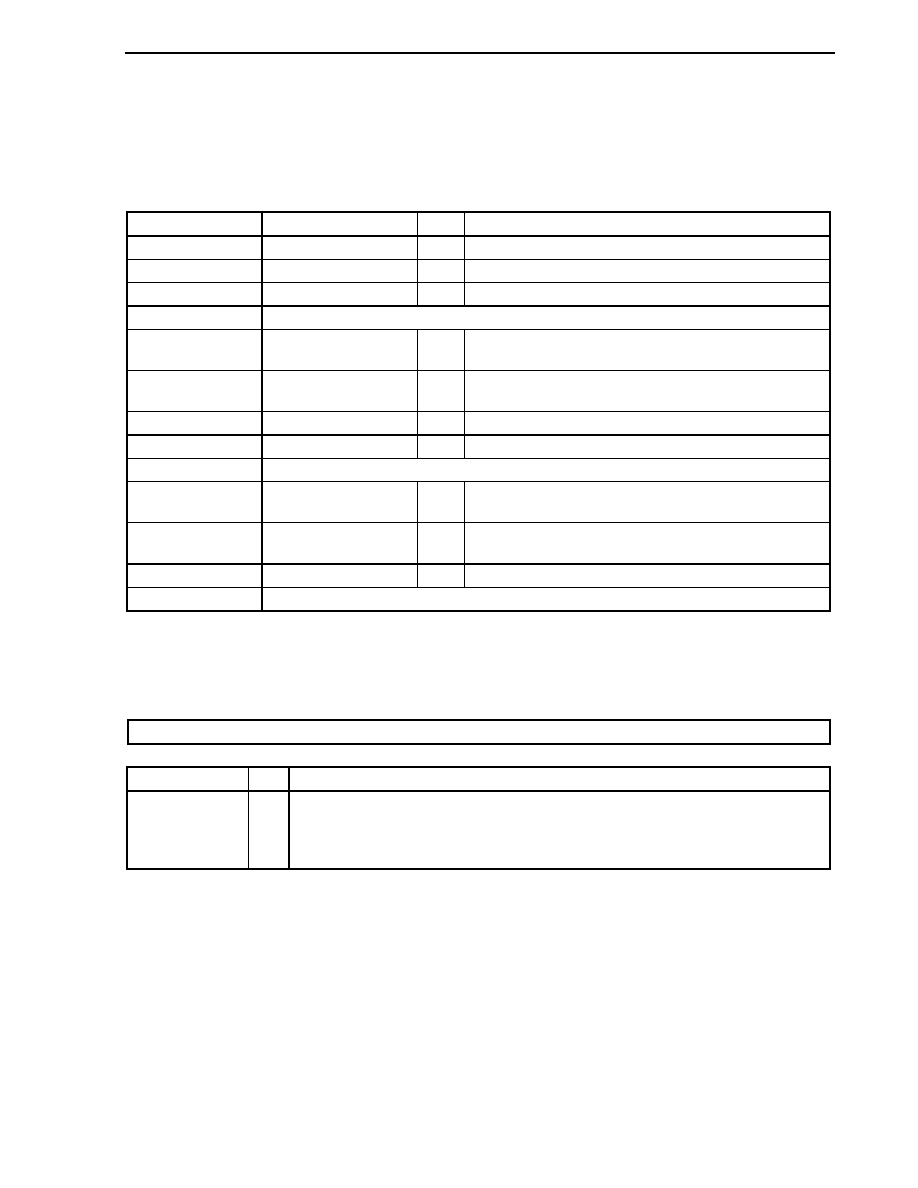

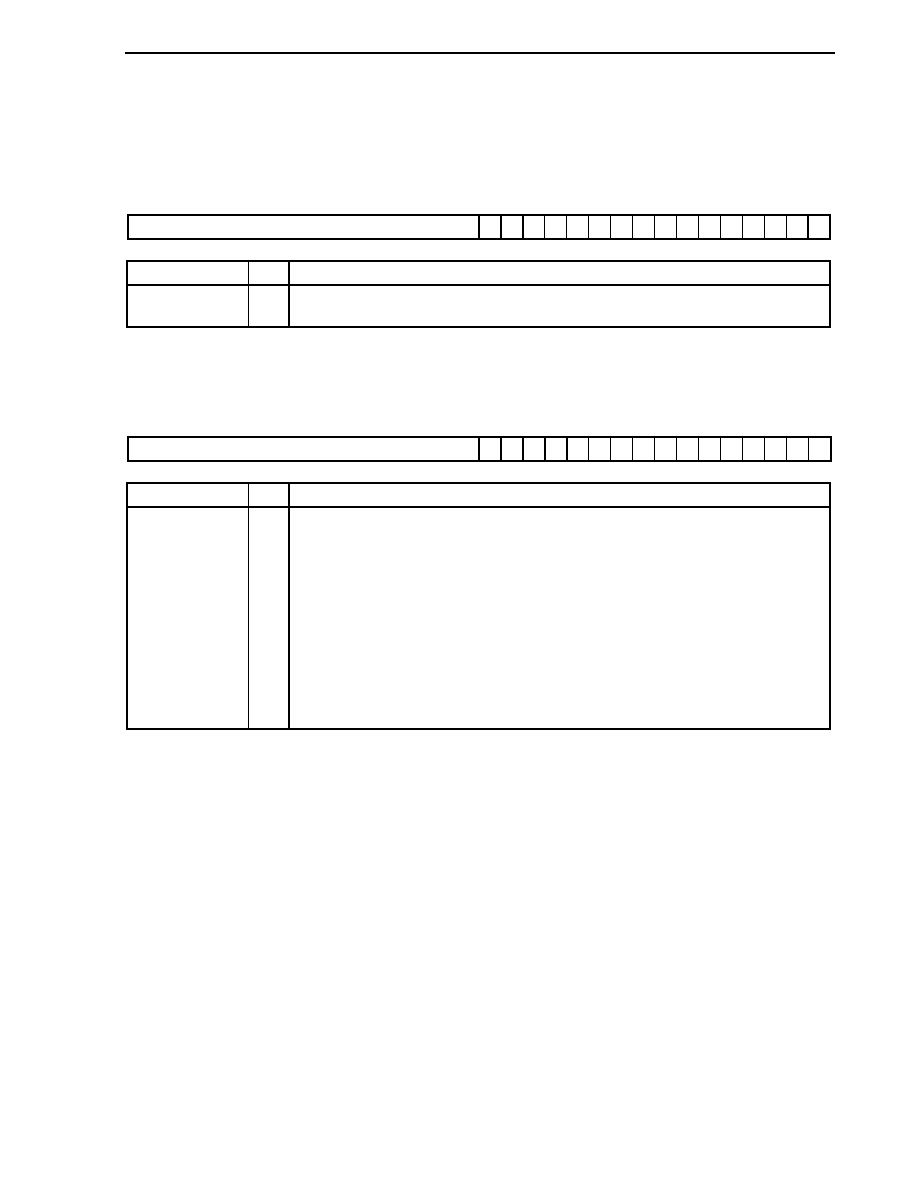

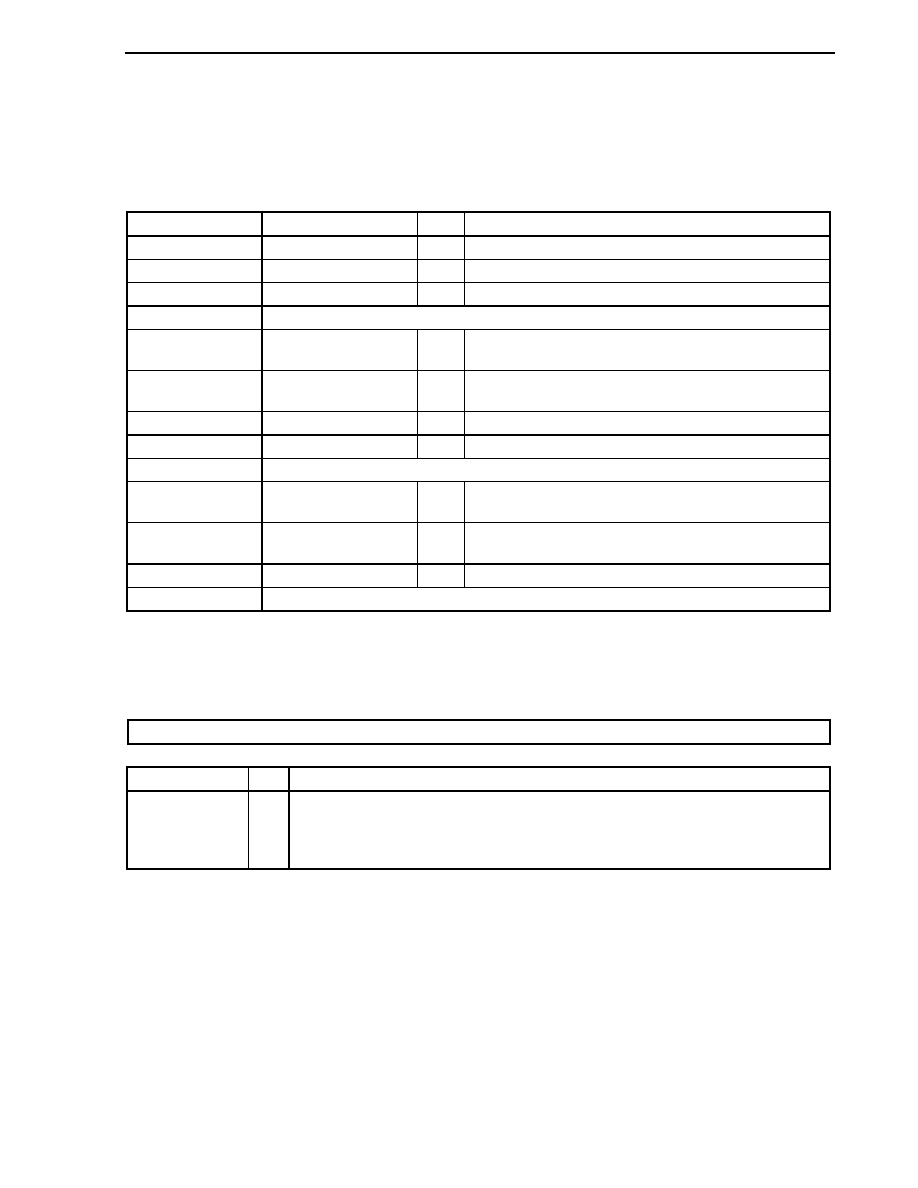

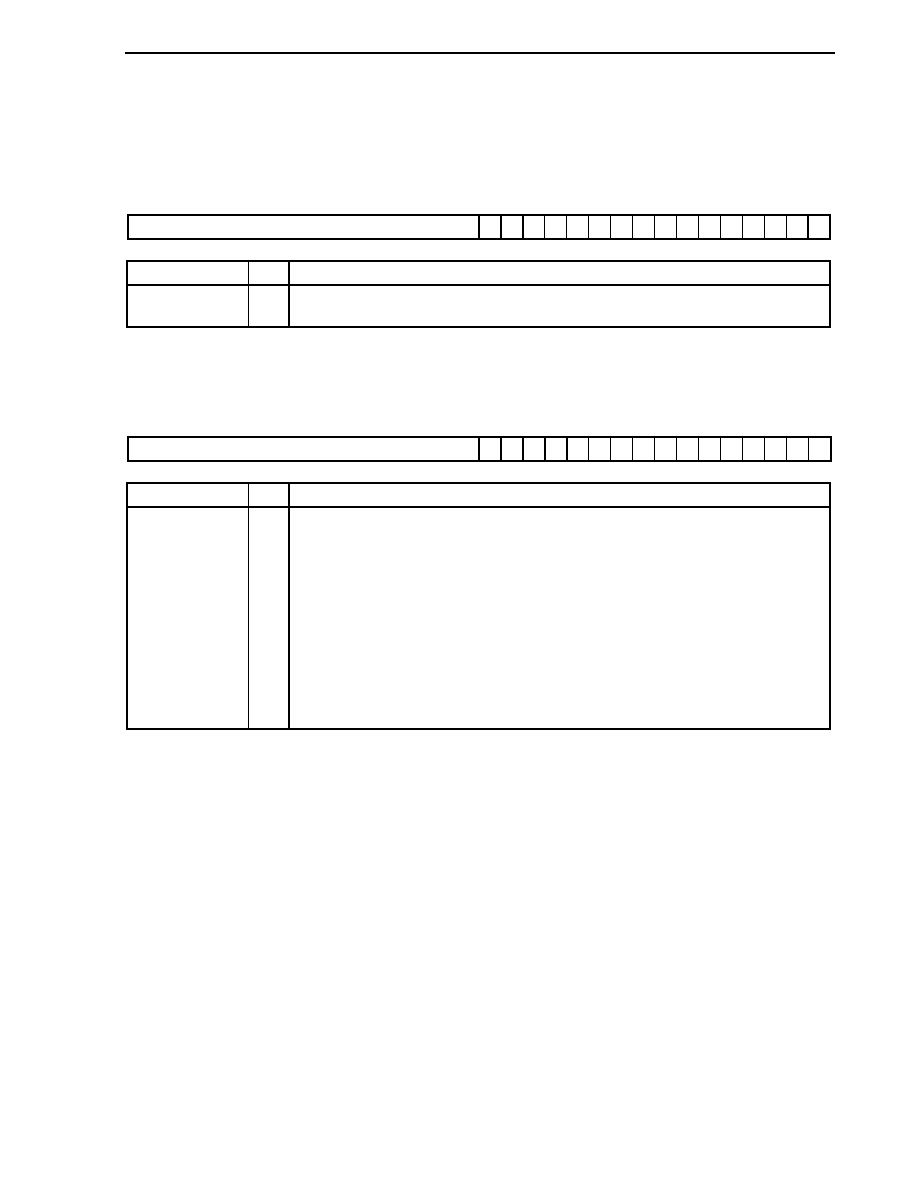

1.3 Ordering Information

(1) V850E/MA1

Part Number

Package

Internal ROM

�

PD703103AGJ-UEN

144-pin plastic LQFP (fine pitch) (20

�

20)

ROMless

�

PD703105AGJ-xxx-UEN

144-pin plastic LQFP (fine pitch) (20

�

20)

Mask ROM (128 KB)

�

PD703106AGJ-xxx-UEN

144-pin plastic LQFP (fine pitch) (20

�

20)

Mask ROM (128 KB)

�

PD703106AGJ(A)-xxx-UEN

144-pin plastic LQFP (fine pitch) (20

�

20)

Mask ROM (128 KB)

�

PD703106AF1-xxx-EN4

161-pin plastic FBGA (13

�

13)

Mask ROM (128 KB)

�

PD703107AGJ-xxx-UEN

144-pin plastic LQFP (fine pitch) (20

�

20)

Mask ROM (256 KB)

�

PD703107AGJ(A)-xxx-UEN

144-pin plastic LQFP (fine pitch) (20

�

20)

Mask ROM (256 KB)

�

PD703107AF1-xxx-EN4

161-pin plastic FBGA (13

�

13)

Mask ROM (256 KB)

�

PD70F3107AGJ-UEN

144-pin plastic LQFP (fine pitch) (20

�

20)

Flash memory (512 KB)

�

PD70F3107AGJ(A)-UEN

144-pin plastic LQFP (fine pitch) (20

�

20)

Flash memory (512 KB)

�

PD70F3107AF1-EN4

161-pin plastic FBGA (13

�

13)

Flash memory (512 KB)

(2) V850E/MA2

Part Number

Package

Internal ROM

�

PD703108GC-8EU

100-pin plastic LQFP (fine pitch) (14

�

14)

ROMless

CHAPTER 1 OVERVIEW OF EACH PRODUCT

Application Note U17121EJ1V1AN

13

(3) V850E/MA3

Part Number

Package

Internal ROM

�

PD703131AGJ-xxx-UEN

144-pin plastic LQFP (fine pitch) (20

�

20)

Mask ROM (256 KB)

�

PD703131AF1-xxx-EN4

161-pin plastic FBGA (13

�

13)

Mask ROM (256 KB)

�

PD703131AYGJ-xxx-UEN

144-pin plastic LQFP (fine pitch) (20

�

20)

Mask ROM (256 KB)

�

PD703131AYF1-xxx-EN4

161-pin plastic FBGA (13

�

13)

Mask ROM (256 KB)

�

PD703132AGJ-xxx-UEN

144-pin plastic LQFP (fine pitch) (20

�

20)

Mask ROM (256 KB)

�

PD703132AF1-xxx-EN4

161-pin plastic FBGA (13

�

13)

Mask ROM (256 KB)

�

PD703132AYGJ-xxx-UEN

144-pin plastic LQFP (fine pitch) (20

�

20)

Mask ROM (256 KB)

�

PD703132AYF1-xxx-EN4

161-pin plastic FBGA (13

�

13)

Mask ROM (256 KB)

�

PD703133AGJ-xxx-UEN

144-pin plastic LQFP (fine pitch) (20

�

20)

Mask ROM (512 KB)

�

PD703133AF1-xxx-EN4

161-pin plastic FBGA (13

�

13)

Mask ROM (512 KB)

�

PD703133AYGJ-xxx-UEN

144-pin plastic LQFP (fine pitch) (20

�

20)

Mask ROM (512 KB)

�

PD703133AYF1-xxx-EN4

161-pin plastic FBGA (13

�

13)

Mask ROM (512 KB)

�

PD703134AGJ-xxx-UEN

144-pin plastic LQFP (fine pitch) (20

�

20)

Mask ROM (512 KB)

�

PD703134AF1-xxx-EN4

161-pin plastic FBGA (13

�

13)

Mask ROM (512 KB)

�

PD703134AYGJ-xxx-UEN

144-pin plastic LQFP (fine pitch) (20

�

20)

Mask ROM (512 KB)

�

PD703134AYF1-xxx-EN4

161-pin plastic FBGA (13

�

13)

Mask ROM (512 KB)

�

PD70F3134AGJ-UEN

144-pin plastic LQFP (fine pitch) (20

�

20)

Flash memory (512 KB)

�

PD70F3134AF1-EN4

161-pin plastic FBGA (13

�

13)

Flash memory (512 KB)

�

PD70F3134AYGJ-UEN 144-pin

plastic LQFP (fine pitch) (20

�

20)

Flash memory (512 KB)

�

PD70F3134AYF1-EN4

161-pin plastic FBGA (13

�

13)

Flash memory (512 KB)

(4) V850E/ME2

Part Number

Package

Maximum Operating

Frequency

�

PD703111AGM-10-UEU

176-pin plastic LQFP (fine pitch) (24

�

24)

100 MHz

�

PD703111AGM-13-UEU

176-pin plastic LQFP (fine pitch) (24

�

24)

133 MHz

�

PD703111AGM-15-UEU

176-pin plastic LQFP (fine pitch) (24

�

24)

150 MHz

�

PD703111AF1-10-GA3

240-pin plastic FBGA (16

�

16)

100 MHz

�

PD703111AF1-13-GA3

240-pin plastic FBGA (16

�

16)

133 MHz

�

PD703111AF1-15-GA3

240-pin plastic FBGA (16

�

16)

150 MHz

CHAPTER 1 OVERVIEW OF EACH PRODUCT

Application Note U17121EJ1V1AN

14

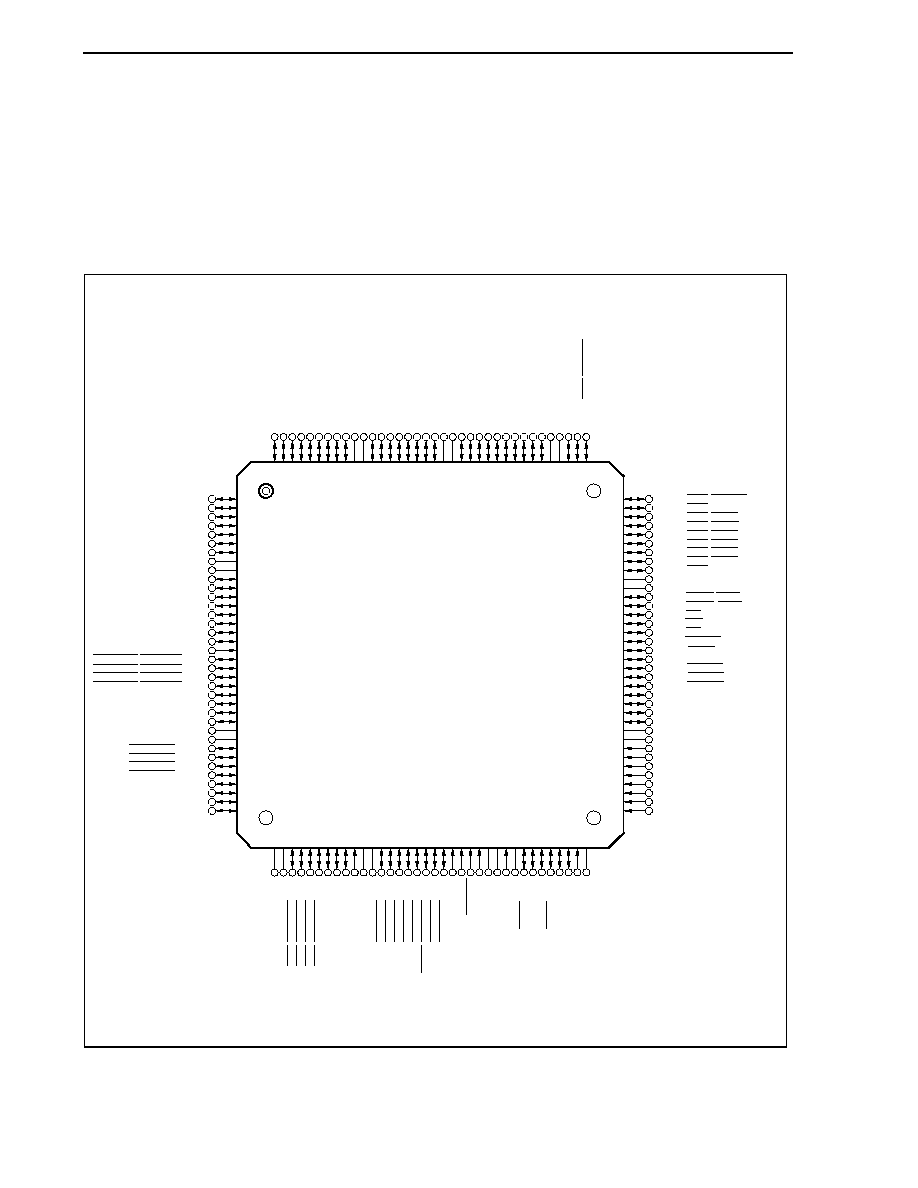

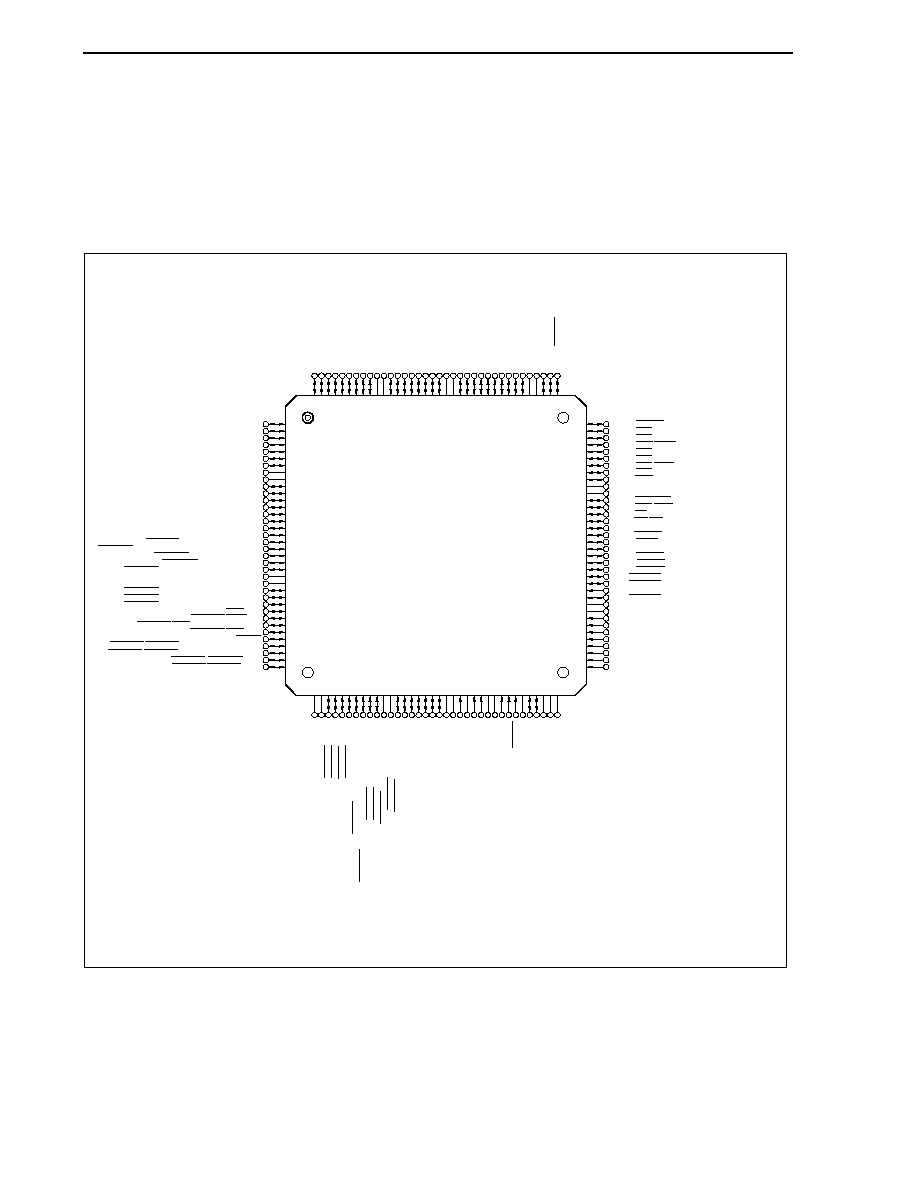

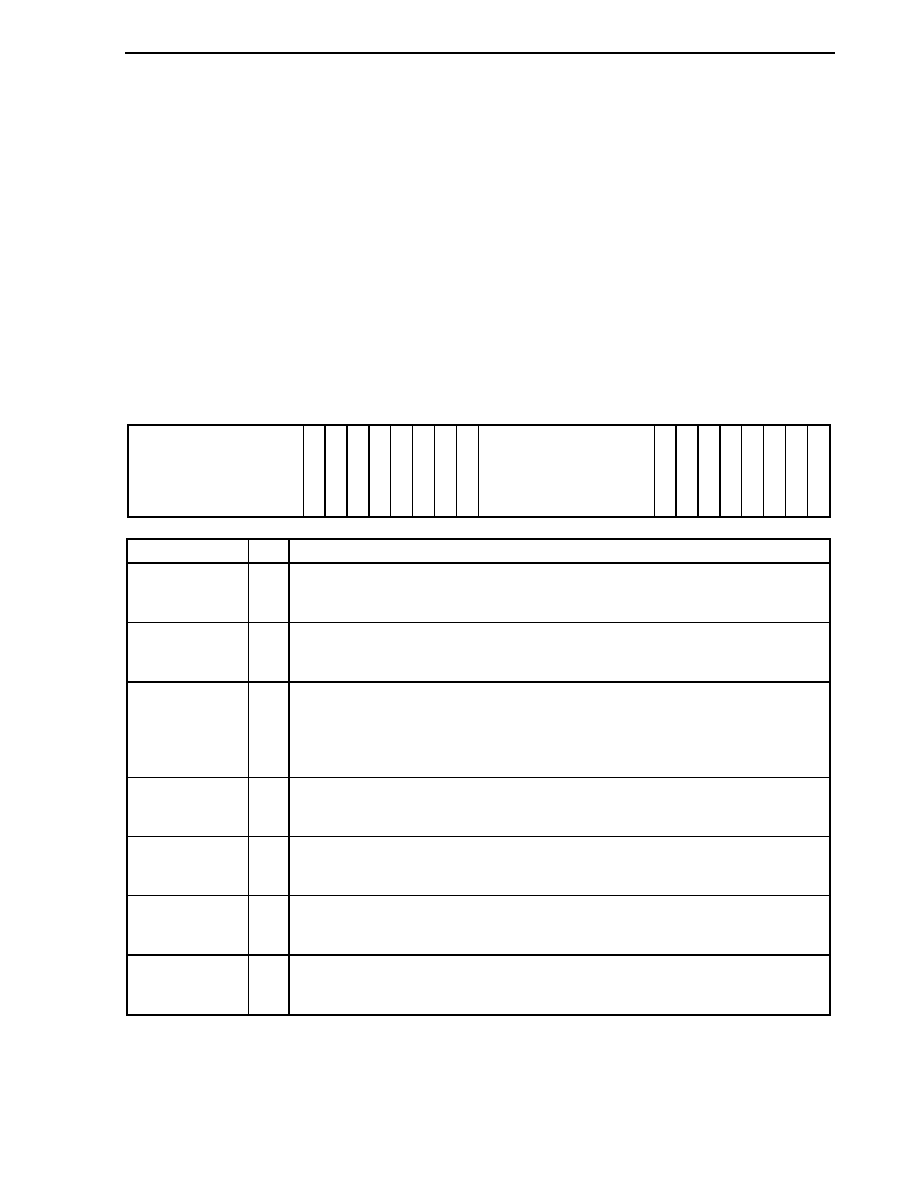

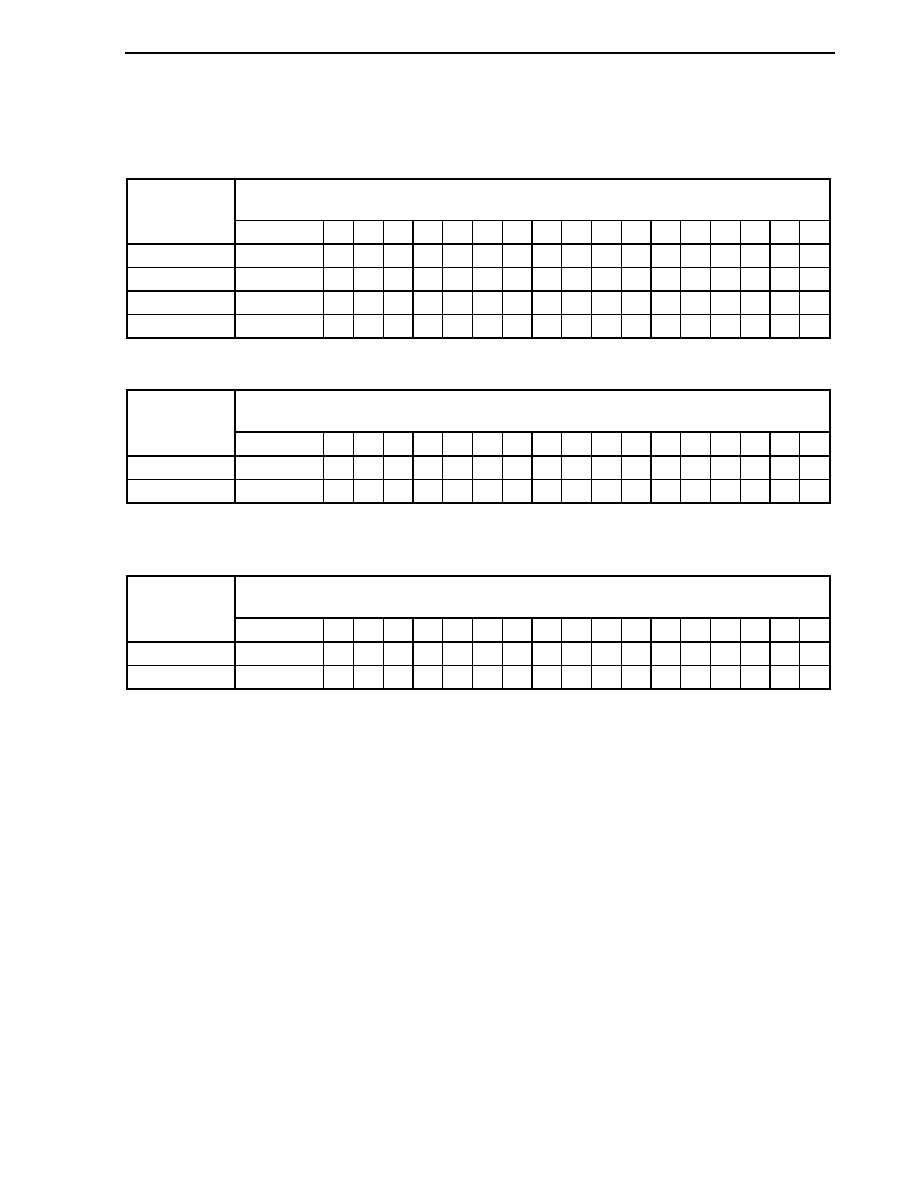

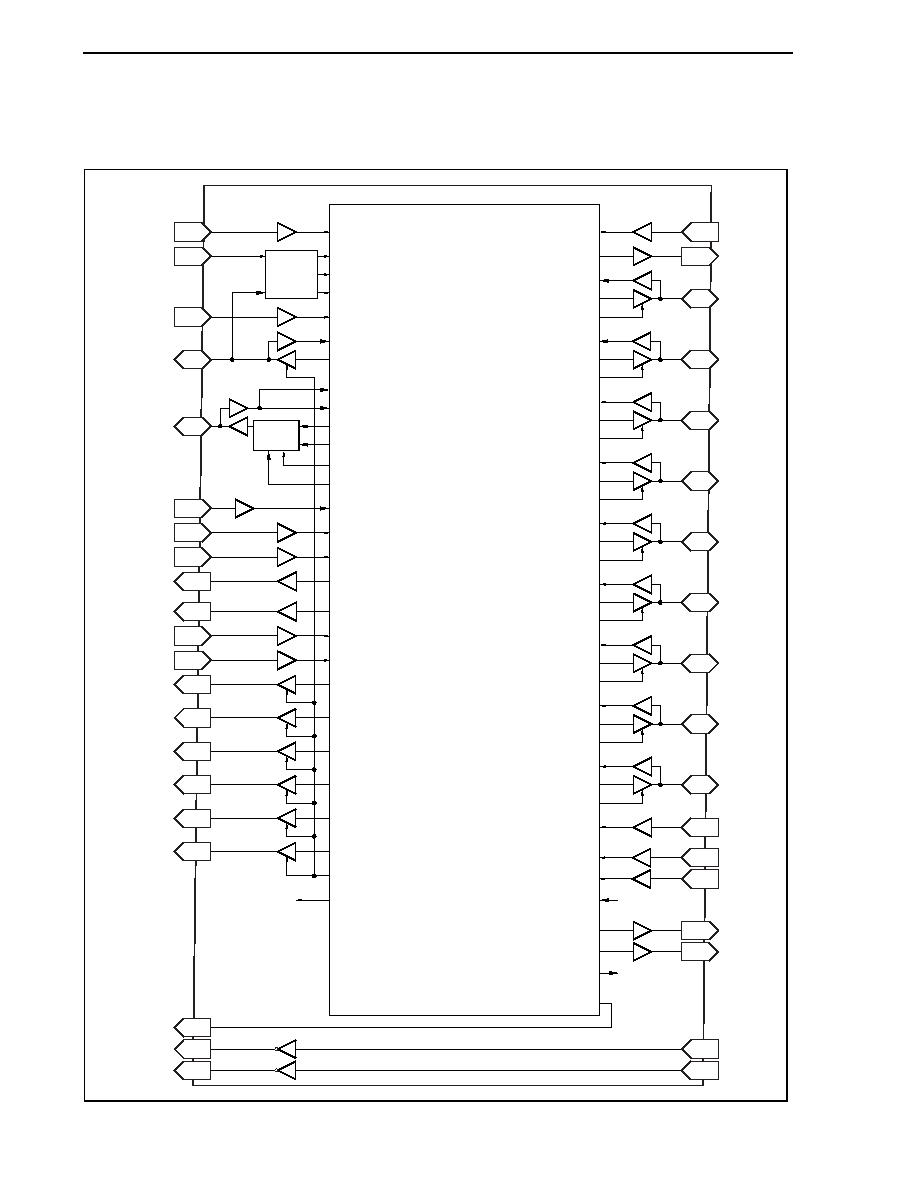

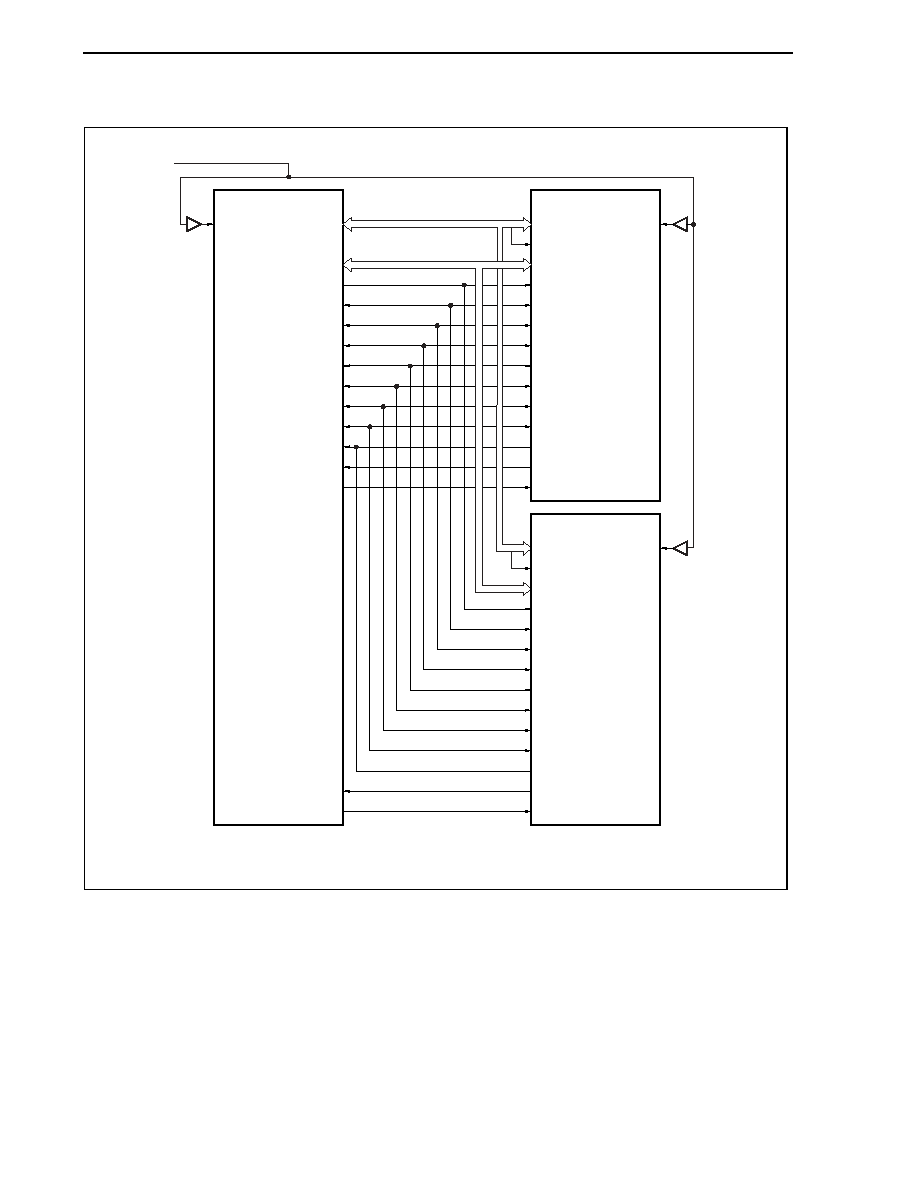

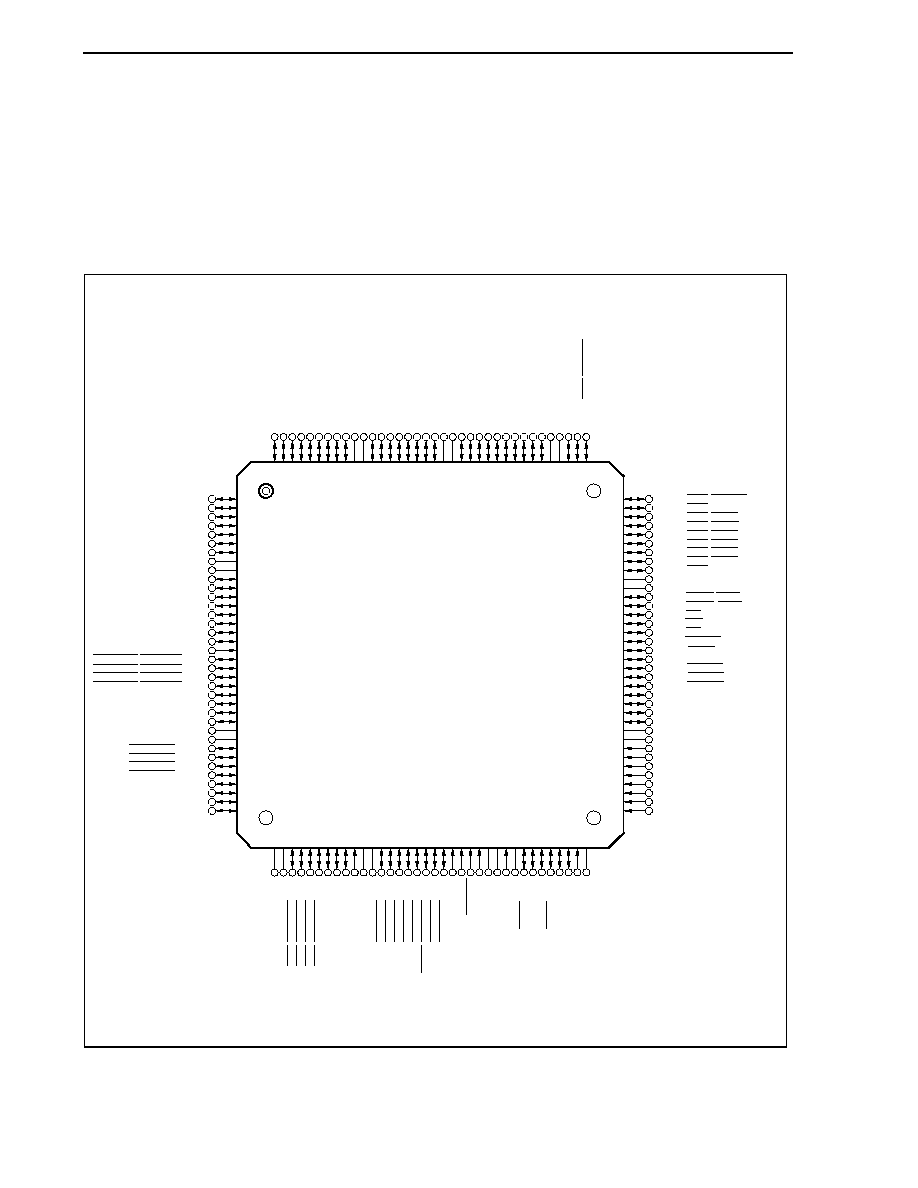

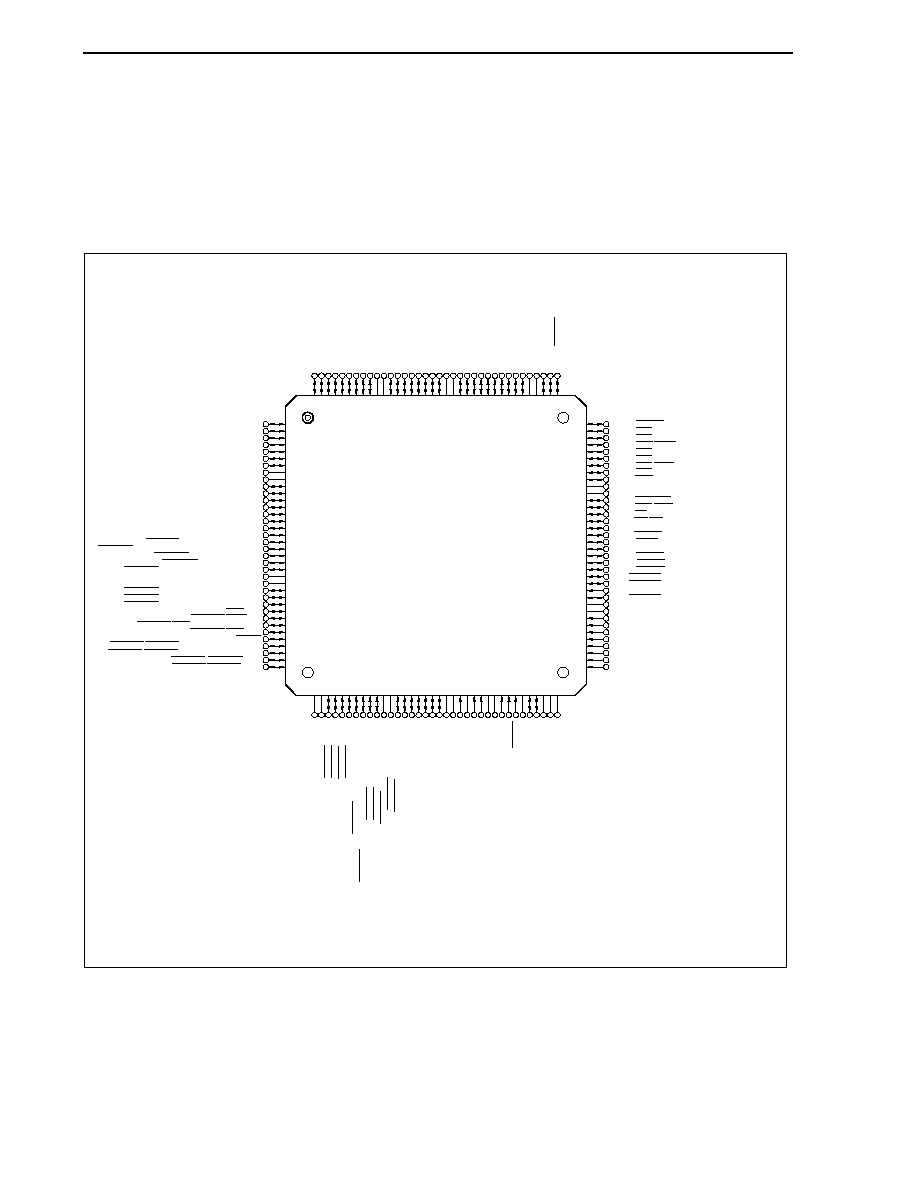

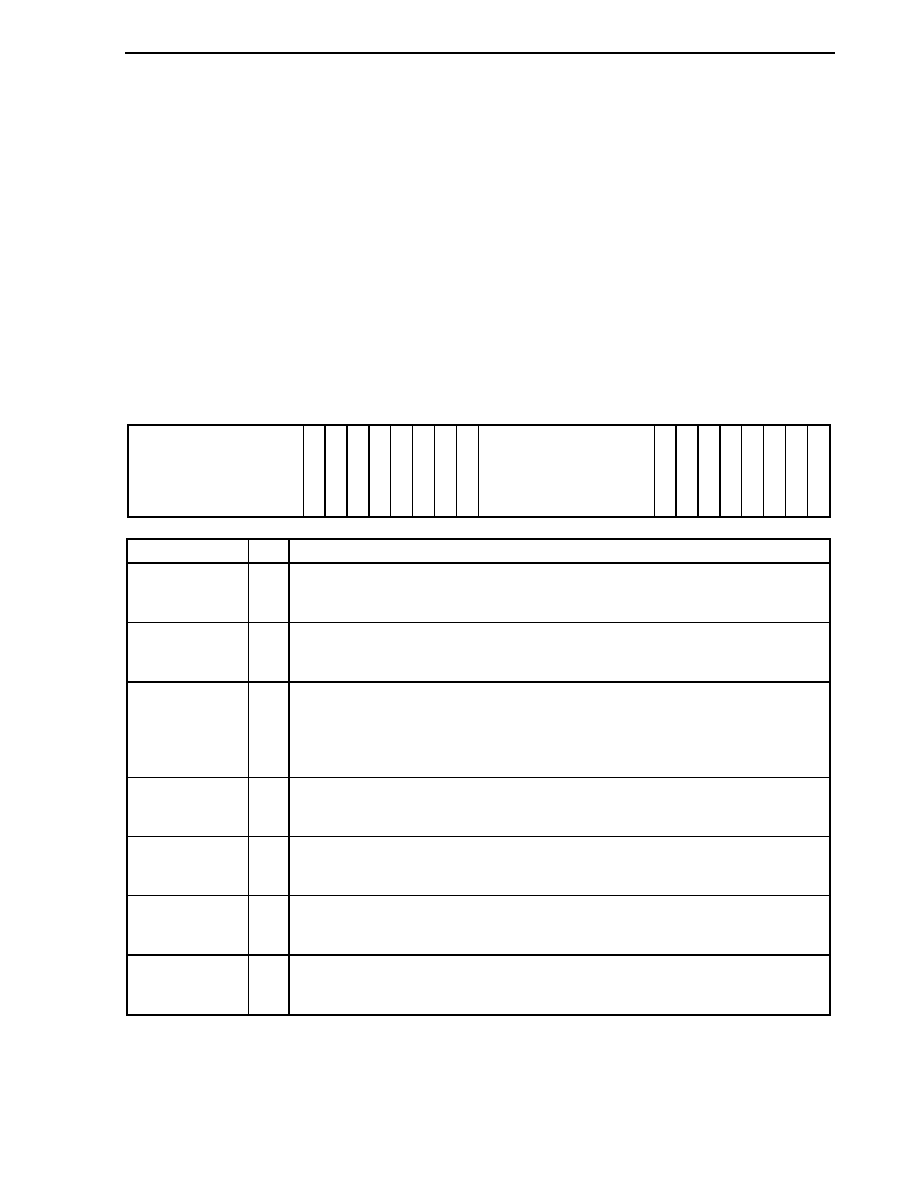

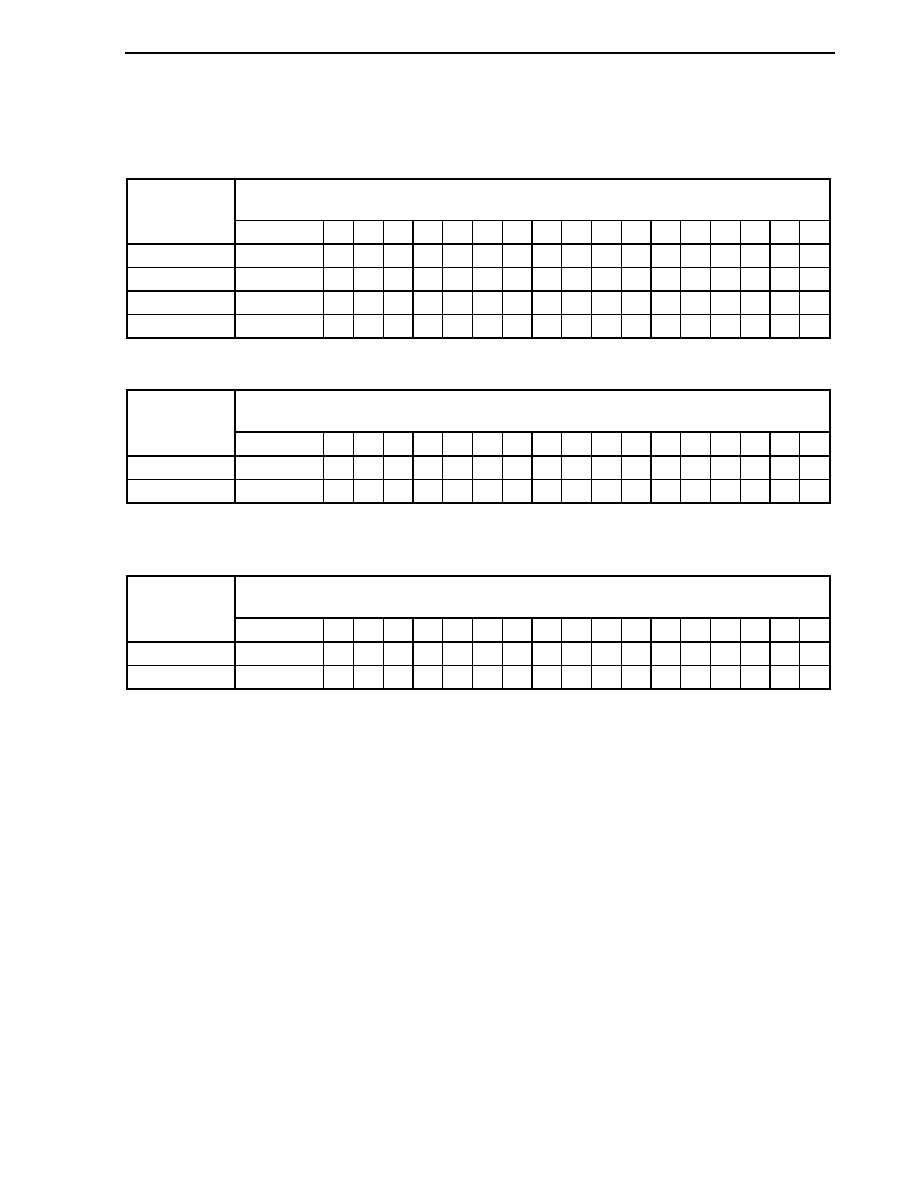

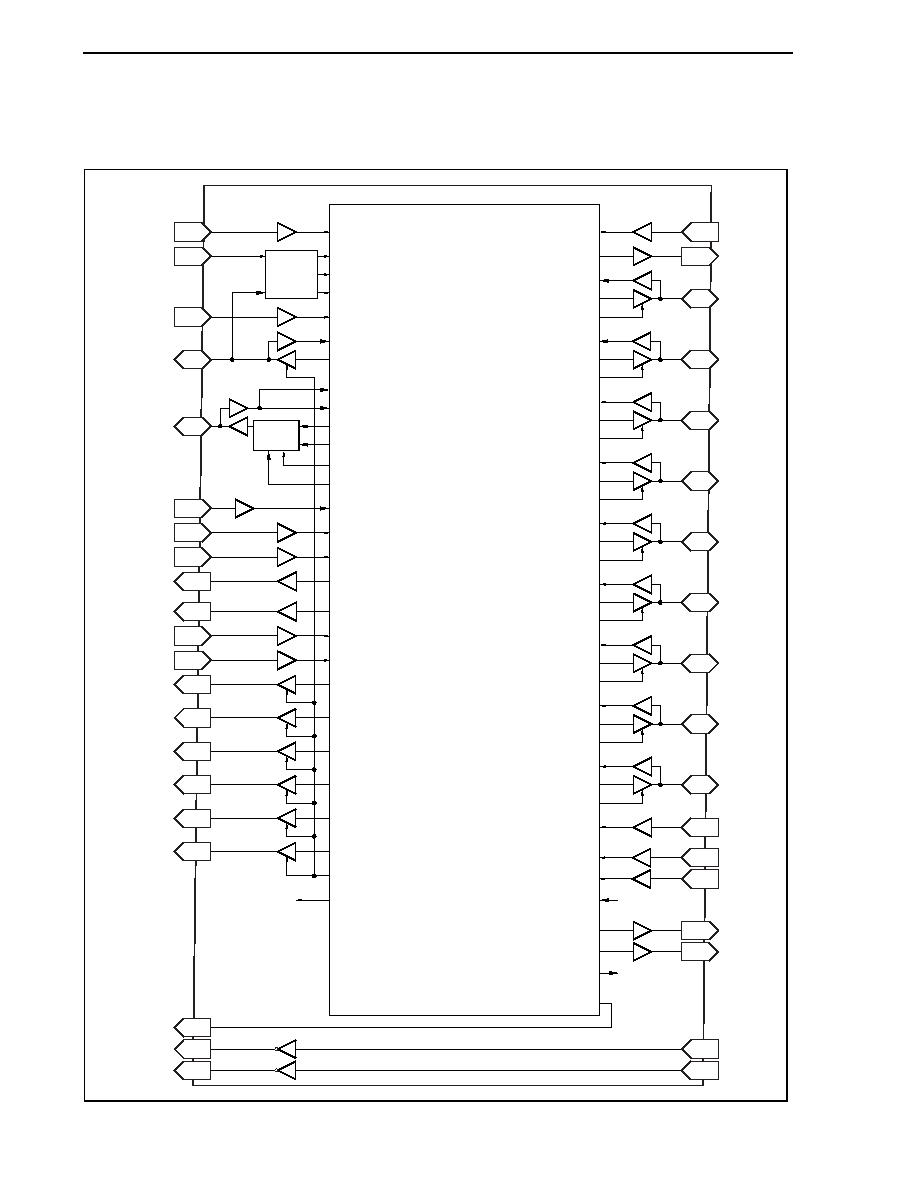

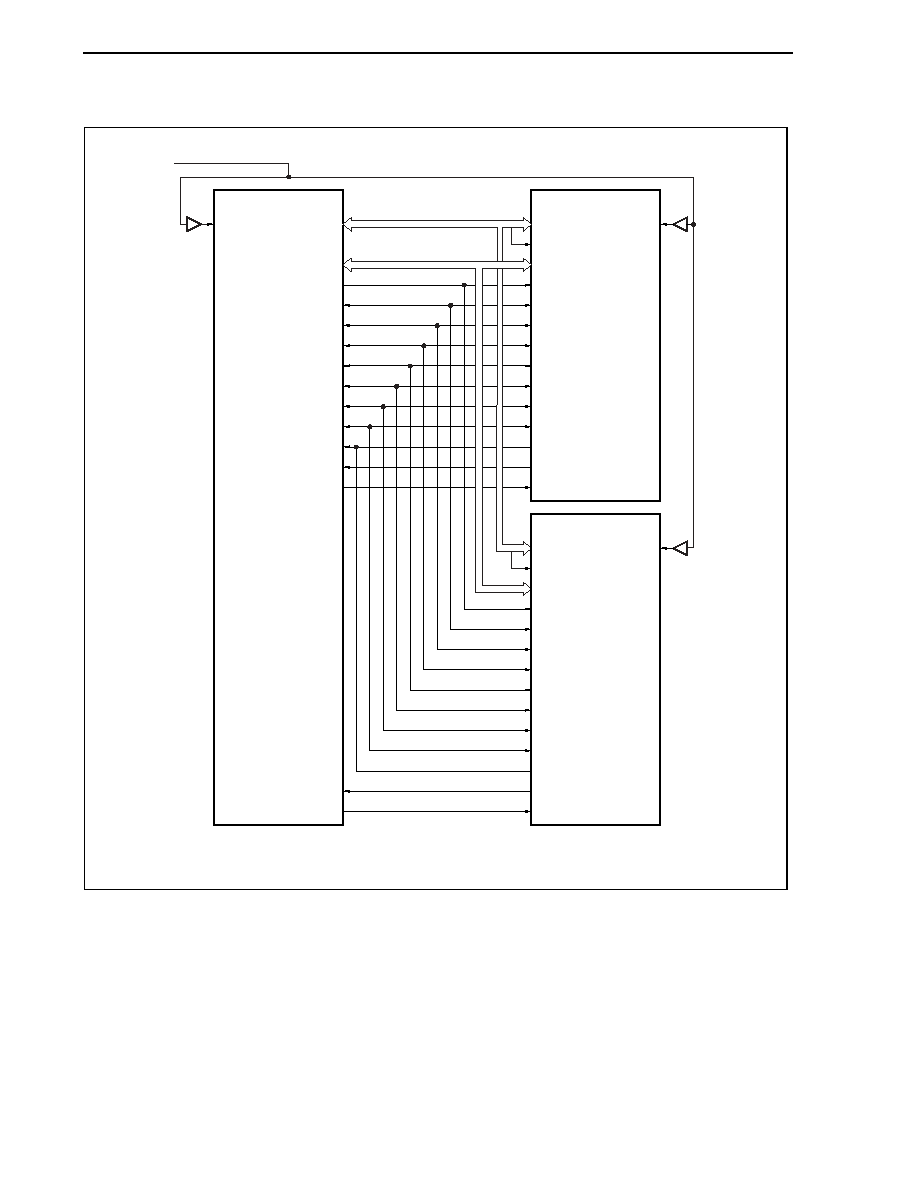

1.4 Pin Configuration

(1) V850E/MA1

�

144-pin plastic LQFP (fine pitch) (20

�

20)

�

PD703103AGJ-UEN

�

PD703106AGJ(A)-xxx-UEN

�

PD70F3107AGJ-UEN

�

PD703105AGJ-xxx-UEN

�

PD703107AGJ-xxx-UEN

�

PD70F3107AGJ(A)-UEN

�

PD703106AGJ-xxx-UEN

�

PD703107AGJ(A)-xxx-UEN

Top View

D14/PDL14

D13/PDL13

D12/PDL12

D11/PDL11

D10/PDL10

D9/PDL9

D8/PDL8

V

DD

V

SS

D7/PDL7

D6/PDL6

D5/PDL5

D4/PDL4

D3/PDL3

D2/PDL2

D1/PDL1

D0/PDL0

MODE2 (V

PP

/MODE2)

DMARQ3/INTP103/P07

DMARQ2/INTP102/P06

DMARQ1/INTP101/P05

DMARQ0/INTP100/P04

TO00/P03

INTP001/P02

TI000/INTP000/P01

PWM0/P00

V

DD

V

SS

DMAAK3/PBD3

DMAAK2/PBD2

DMAAK1/PBD1

DMAAK0/PBD0

TO01/P13

INTP011/P12

TI010/INTP010/P11

PWM1/P10

PCD3/UBE/SDRAS

PCS0/CS0

PCS1/CS1/RAS1

PCS2/CS2/IOWR

PCS3/CS3/RAS3

PCS4/CS4/RAS4

PCS5/CS5/IORD

PCS6/CS6/RAS6

PCS7/CS7

V

SS

V

DD

PCT0/LCAS/LWR/LDQM

PCT1/UCAS/UWR/UDQM

PCT4/RD

PCT5/WE

PCT6/OE

PCT7/BCYST

PCM0/WAIT

PCM1/CLKOUT/BUSCLK

PCM2/HLDAK

PCM3/HLDRQ

PCM4/REFRQ

PCM5/SELFREF

P50/INTP030/TI030

P51/INTP031

P52/TO03

V

SS

V

DD

P70/ANI0

P71/ANI1

P72/ANI2

P73/ANI3

P74/ANI4

P75/ANI5

P76/ANI6

P77/ANI7

V

DD

V

SS

TC3/INTP113/P27 TC2/INTP112/P26 TC1/INTP111/P25 TC0/INTP110/P24

TO02/P23

INTP021/P22

TI020/INTP020/P21

NMI/P20

V

DD

V

SS

ADTRG/INTP123/P37

INTP122/P36 INTP121/P35

RXD2/INTP120/P34 TXD2/INTP133/P33 SCK2/INTP132/P32

SI2/INTP131/P31

SO2/INTP130/P30

MODE1 MODE0 RESET CKSEL

CV

DD

X2 X1

CV

SS

SCK1/P45

RXD1/SI1/P44 TXD1/SO1/P43

SCK0/P42

RXD0/SI0/P41 TXD0/SO0/P40

AV

DD

/AV

REF

AV

SS

PDL15/D15 PAL0/A0 PAL1/A1 PAL2/A2 PAL3/A3 PAL4/A4 PAL5/A5 PAL6/A6 PAL7/A7 V

SS

V

DD

PAL8/A8 PAL9/A9 PAL10/A10 PAL11/A11 PAL12/A12 PAL13/A13 PAL14/A14 PAL15/A15 V

SS

V

DD

PAH0/A16 PAH1/A17 PAH2/A18 PAH3/A19 PAH4/A20 PAH5/A21 PAH6/A22 PAH7/A23 PAH8/A24 PAH9/A25 V

SS

V

DD

PCD0/SDCKE PCD1/SDCLK PCD2/LBE/SDCAS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

144 143 142 141 140 139 138 137 136 135 134 133 132 131 130 129 128 127 126 125 124 123 122 121 120 119 118 117 116 115 114 113 112 111 110 109

37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

Remark Items in parentheses are pin names in the

�

PD70F3107A.

CHAPTER 1 OVERVIEW OF EACH PRODUCT

Application Note U17121EJ1V1AN

15

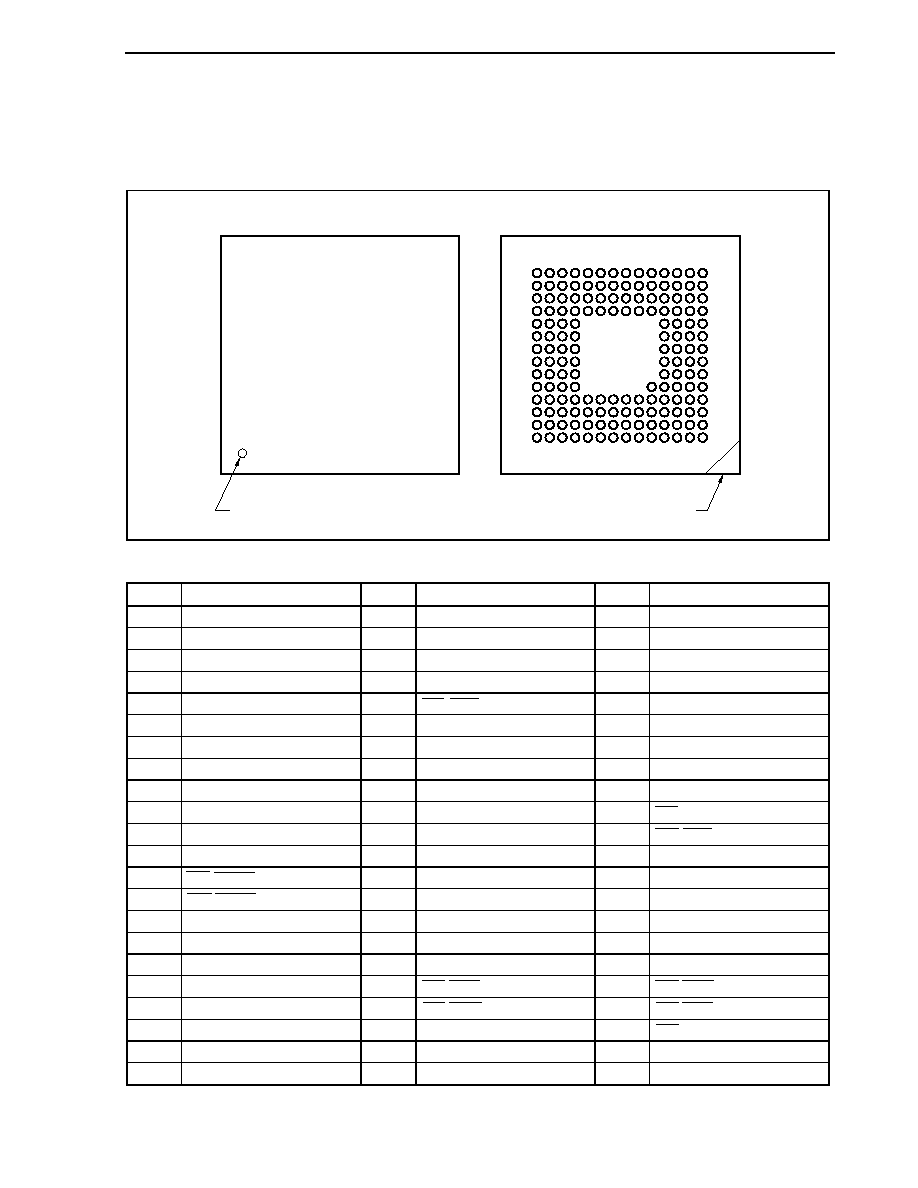

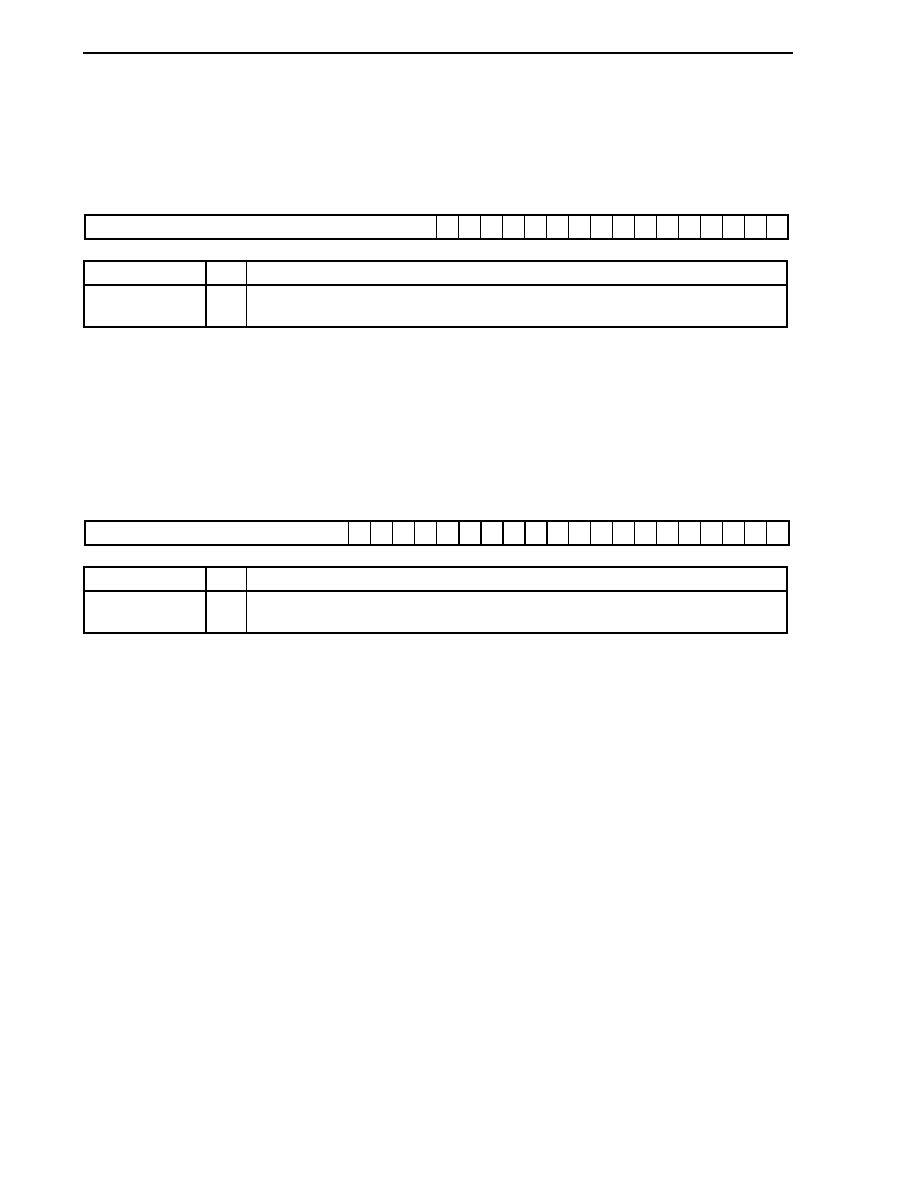

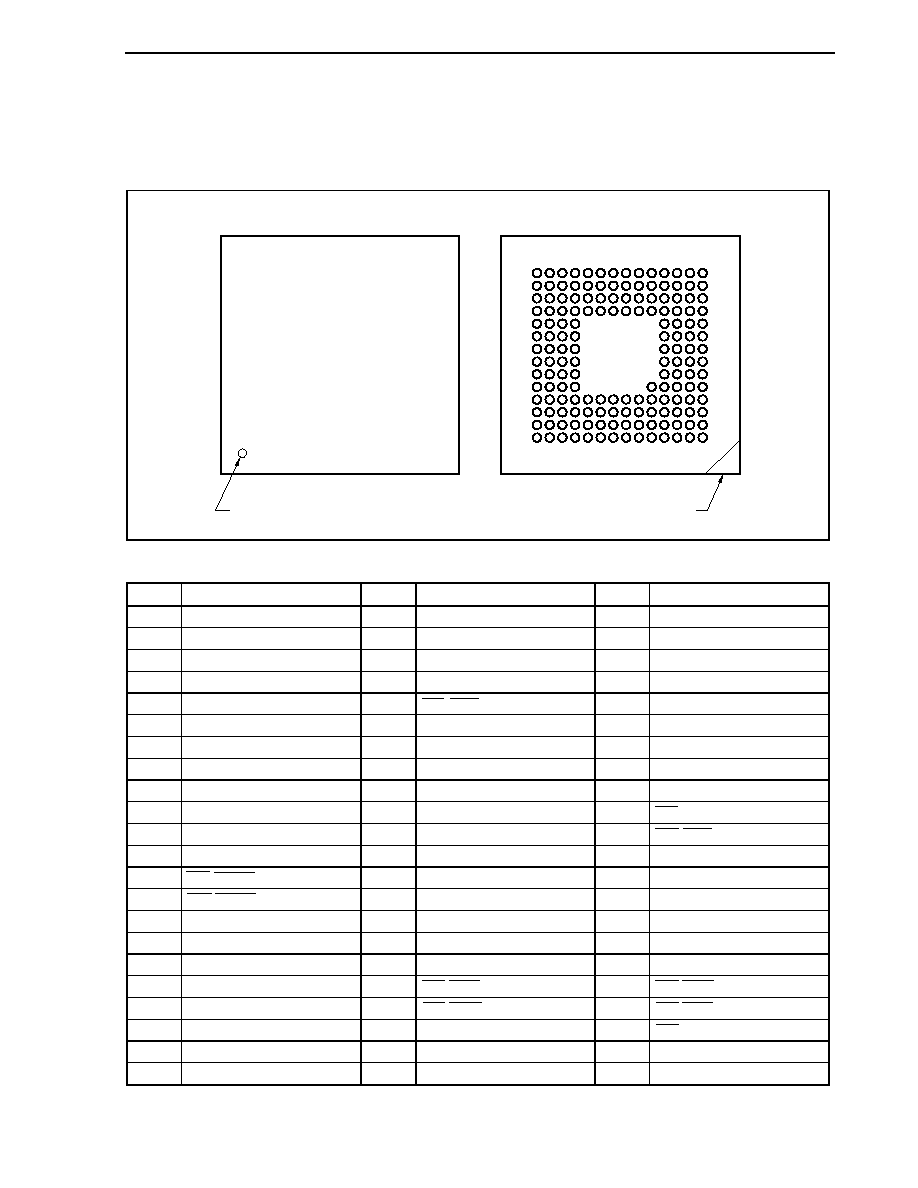

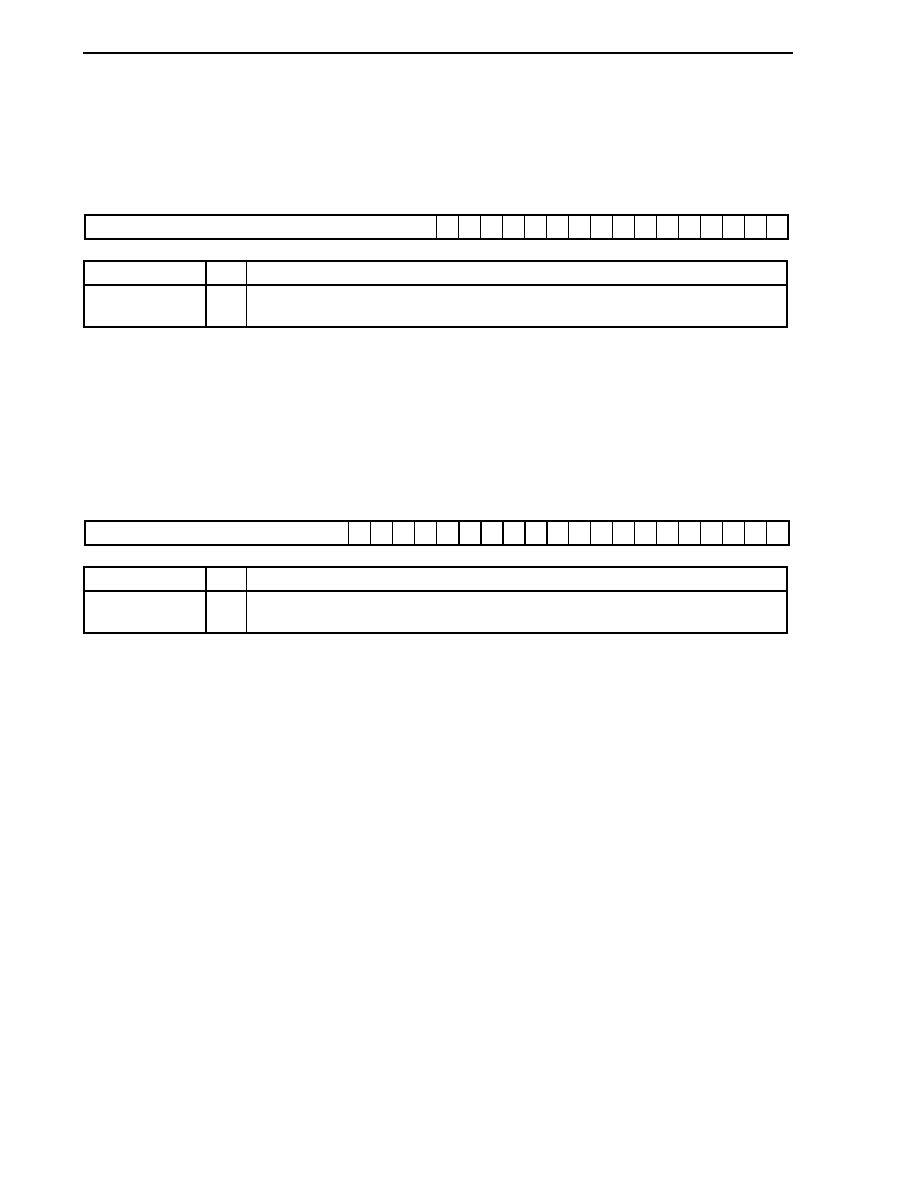

�

161-pin plastic FBGA (13

�

13)

�

PD703106AF1-xxx-EN4

�

PD703107AF1-xxx-EN4

�

PD70F3107AF1-EN4

14

13

12

11

10

9

8

7

6

5

4

3

2

1

Top View

Bottom View

P N M L K J H G F E D C B A

A B C D E F G H J K L M N P

Index mark

Index mark

(1/2)

Pin No.

Name

Pin No.

Name

Pin No.

Name

A1

-

B9 A18/PAH2

D3 D14/PDL14

A2 D15/PDL15

B10 A21/PAH5

D4 A3/PAL3

A3 A2/PAL2

B11 A25/PAH9

D5 A6/PAL6

A4 A5/PAL5

B12 SDCLK/PCD1

D6 A10/PAL10

A5

-

B13 CS1/RAS1/PCS1

D7 A14/PAL14

A6 A9/PAL9

B14

-

D8 A16/PAH0

A7 A12/PAL12

C1

-

D9 A20/PAH4

A8 A15/PAL15

C2 D9/PDL9

D10 A23/PAH7

A9 A17/PAH1

C3 D13/PDL13

D11 SDCKE/PCD0

A10

-

C4 A1/PAL1

D12 CS0/PCS0

A11 A24/PAH8

C5 A7/PAL7

D13 CS5/IORD/PCS5

A12 V

DD

C6

V

DD

D14

-

A13 LBE/SDCAS/PCD2

C7 A11/PAL11

E1 D5/PDL5

A14 UBE/SDRAS/PCD3

C8 V

DD

E2

D7/PDL7

B1

-

C9 A19/PAH3

E3 D8/PDL8

B2 D12/PDL12

C10 A22/PAH6

E4 D11/PDL11

B3 A0/PAL0

C11 V

SS

E5

-

B4 A4/PAL4

C12 CS3/RAS3/PCS3

E11 CS6/RAS6/PCS6

B5 V

SS

C13

CS2/IOWR/PCS2

E12

CS4/RAS4/PCS4

B6 A8/PAL8

C14

-

E13 CS7/PCS7

B7 A13/PAL13

D1 V

SS

E14

V

SS

B8 V

SS

D2

D10/PDL10

F1

D2/PDL2

CHAPTER 1 OVERVIEW OF EACH PRODUCT

Application Note U17121EJ1V1AN

16

(2/2)

Pin No.

Name

Pin No.

Name

Pin No.

Name

F2 D3/PDL3

K2 V

SS

M12

ANI6/P76

F3 D4/PDL4

K3 DMAAK1/PBD1

M13 ANI5/P75

F4 V

DD

K4

DMAAK3/PBD3

M14

-

F11 RD/PCT4

K11 ANI1/P71

N1

-

F12 V

DD

K12

ANI0/P70

N2

PWM1/P10

F13 LCAS/LWR/LDQM/PCT0

K13 V

SS

N3

TC3/INTP113/P27

F14 UCAS/UWR/UDQM/PCT1

K14 V

DD

N4

TC0/INTP110/P24

G1 MODE2

(MODE2/V

PP

) L1

-

N5 NMI/P20

G2 DMARQ3/INTP103/P07

L2 DMAAK2/PBD2

N6 ADTRG/INTP123/P37

G3 D0/PDL0

L3 TI010/INTP010/P11

N7 TXD2/INTP133/P33

G4 D6/PDL6

L4 DMAAK0/PBD0

N8 SO2/INTP130/P30

G11 WAIT/PCM0

L5 TO02/P23

N9 X2

G12 WE/PCT5

L6 V

DD

N10

CV

SS

G13 BCYST/PCT7

L7 INTP122/P36

N11 SCK0/P42

G14 OE/PCT6

L8 SI2/INTP131/P31

N12 AV

DD

/AV

REF

H1 DMARQ2/INTP102/P06

L9 RESET

N13 AV

SS

H2 DMARQ1/INTP101/P05

L10 TXD1/SO1/P43

N14

-

H3 DMARQ0/INTP100/P04

L11 ANI7/P77

P1 V

DD

H4 D1/PDL1

L12 ANI4/P74

P2 V

SS

H11 REFRQ/PCM4

L13 ANI3/P73

P3 TC1/INTP111/P25

H12 HLDRQ/PCM3

L14 ANI2/P72

P4 INTP021/P22

H13 HLDAK/PCM2

M1

-

P5

-

H14 CLKOUT/BUSCLK/PCM1

M2 INTP011/P12

P6 INTP121/P35

J1 TO00/P03

M3 TO01/P13

P7 SCK2/INTP132/P32

J2 TI000/INTP000/P01

M4 TC2/INTP112/P26

P8 MODE1

J3 V

DD

M5

TI020/INTP020/P21

P9

CV

DD

J4 INTP001/P02

M6 V

SS

P10

X1

J11 TO03/P52

M7 RXD2/INTP120/P34

P11

-

J12 TI030/INTP030/P50

M8 MODE0

P12 RXD1/SI1/P44

J13 SELFREF/PCM5

M9 CKSEL

P13 RXD0/SI0/P41

J14 INTP031/P51

M10 SCK1/P45

P14

-

K1 PWM0/P00

M11 TXD0/SO0/P40

Remarks 1. Leave the A1, A5, A10, B1, B14, C1, C14, D14, E5, L1, M1, M14, N1, N14, P5, P11, and P14 pins

open.

2. Items in parentheses are pin names in the

�

PD70F3107A.

CHAPTER 1 OVERVIEW OF EACH PRODUCT

Application Note U17121EJ1V1AN

17

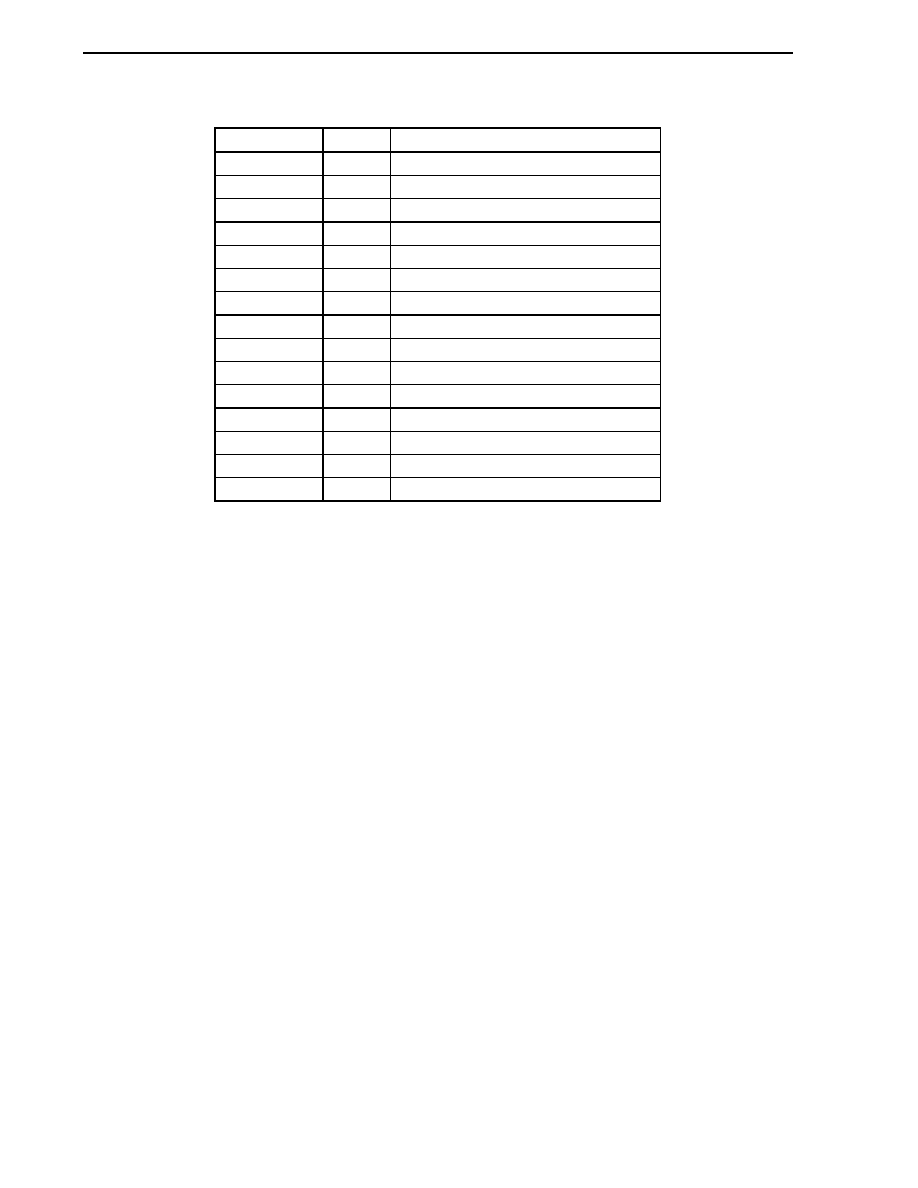

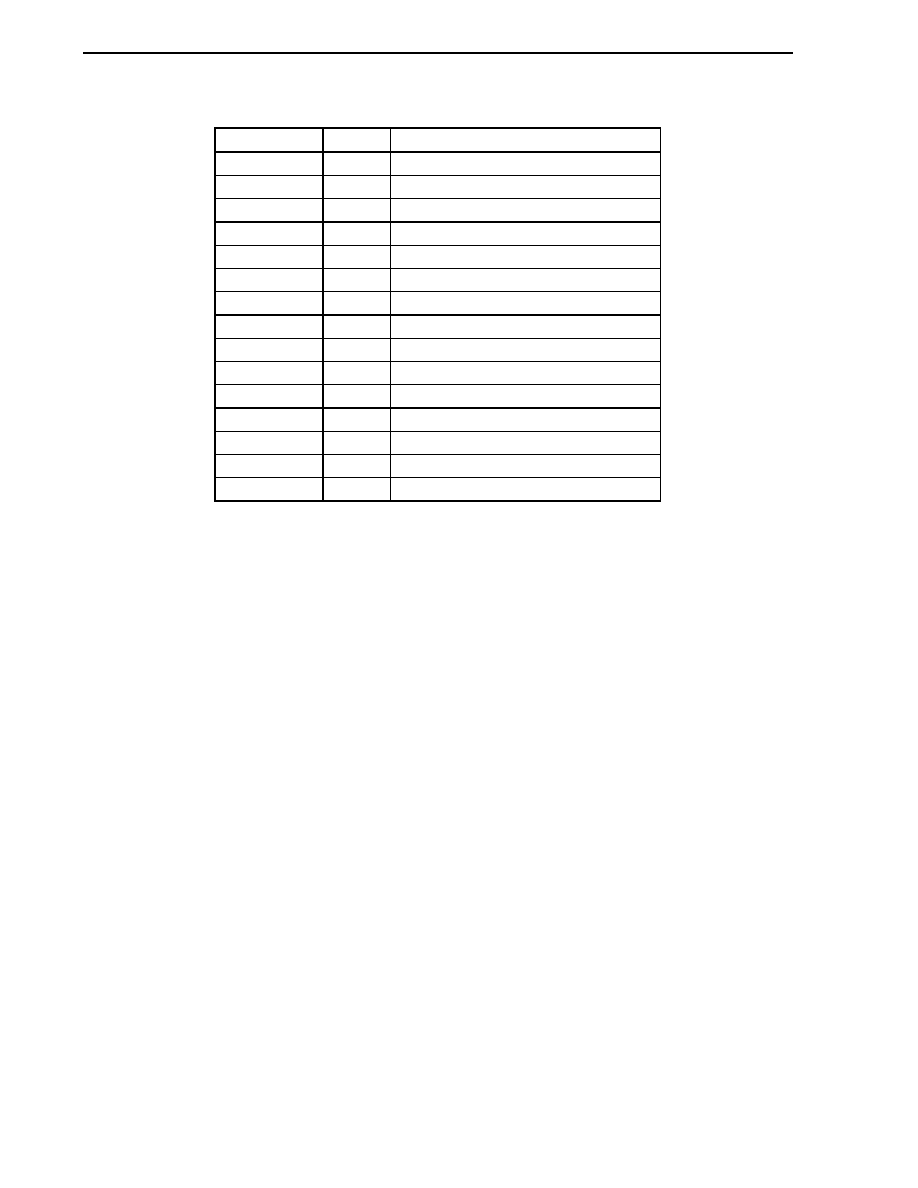

(2) V850E/MA2

�

100-pin plastic LQFP (fine pitch) (14

�

14)

�

PD703108GC-8EU

Top View

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

A1/PAL1

A0/PAL0

D15/PDL15

D14/PDL14

D13/PDL13

D12/PDL12

D11/PDL11

D10/PDL10

D9/PDL9

D8/PDL8

V

DD

V

SS

D7/PDL7

D6/PDL6

D5/PDL5

D4/PDL4

D3/PDL3

D2/PDL2

D1/PDL1

D0/PDL0

MODE2

DMARQ1/INTP101/P05

DMARQ0/INTP100/P04

TO00/P03

INTP001/P02

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

PAH7/A23

PAH8/A24

PCD0/SDCKE

PCD1/SDCLK

PCD2/LBE/SDCAS

PCD3/UBE/SDRAS

PCS0/CS0

PCS3/CS3

PCS4/CS4

PCS7/CS7

PCT0/LWR/LDQM

PCT1/UWR/UDQM

PCT4/RD

PCT5/WE

PCM0/WAIT

PCM1/CLKOUT

PCM2/HLDAK

PCM3/HLDRQ

PCM4/REFRQ

V

SS

V

DD

P70/ANI0

P71/ANI1

P72/ANI2

P73/ANI3

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

PAL2/A2

PAL3/A3

PAL4/A4

PAL5/A5

PAL6/A6

PAL7/A7

V

SS

V

DD

PAL8/A8

PAL9/A9

PAL10/A10

PAL11/A11

PAL12/A12

PAL13/A13

PAL14/A14

PAL15/A15

V

SS

V

DD

PAH0/A16

PAH1/A17

PAH2/A18

PAH3/A19

PAH4/A20

PAH5/A21

PAH6/A22

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

TI000/INTP000/P01

DMAAK1/PBD1

DMAAK0/PBD0

INTP011/P12

TI010/INTP010/P11

TC0/INTP110/P24

NMI/P20

V

DD

V

SS

MODE1

MODE0

RESET

CKSEL

CV

DD

X2

X1

CV

SS

SCK1/P45

RXD1/SI1/P44

TXD1/SO1/P43

SCK0/P42

RXD0/SI0/P41

TXD0/SO0/P40

AV

DD

/A

REF

AV

SS

CHAPTER 1 OVERVIEW OF EACH PRODUCT

Application Note U17121EJ1V1AN

18

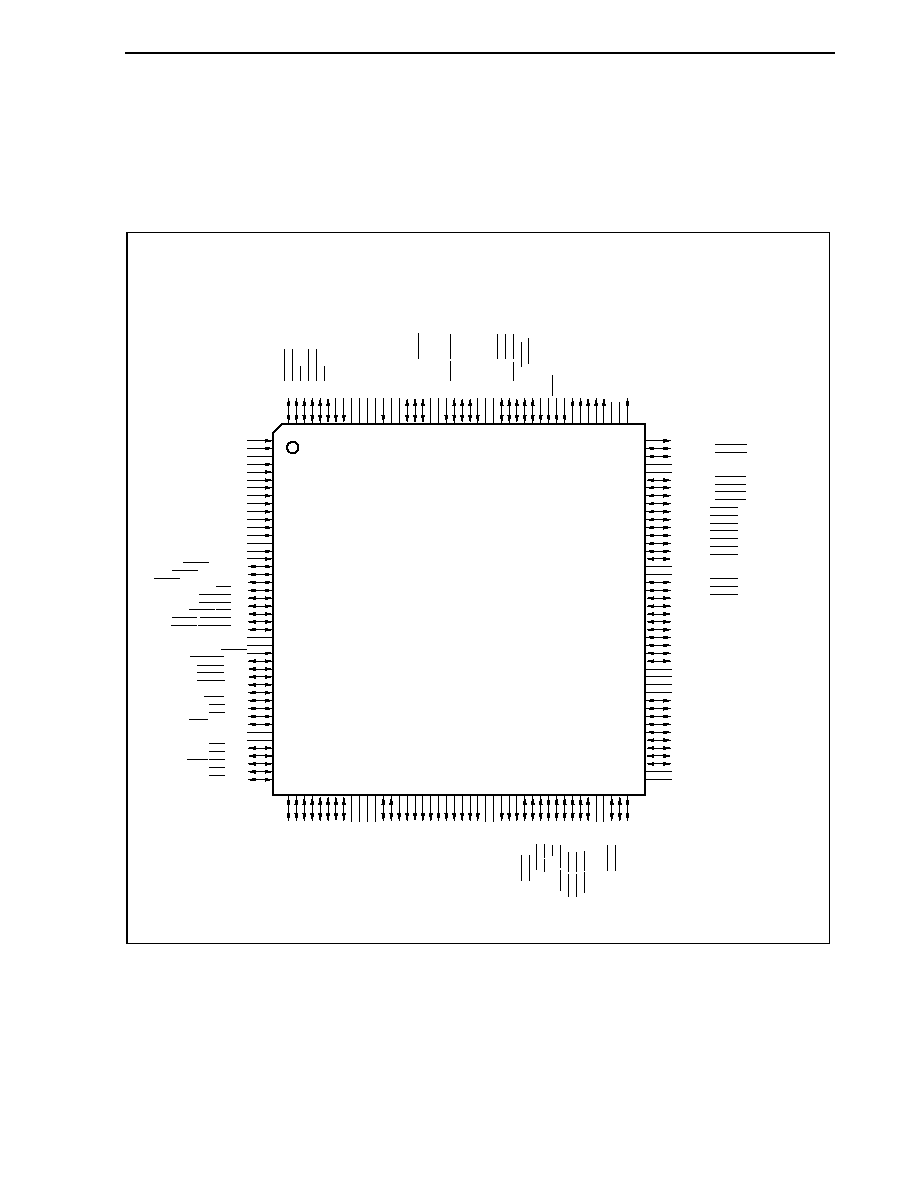

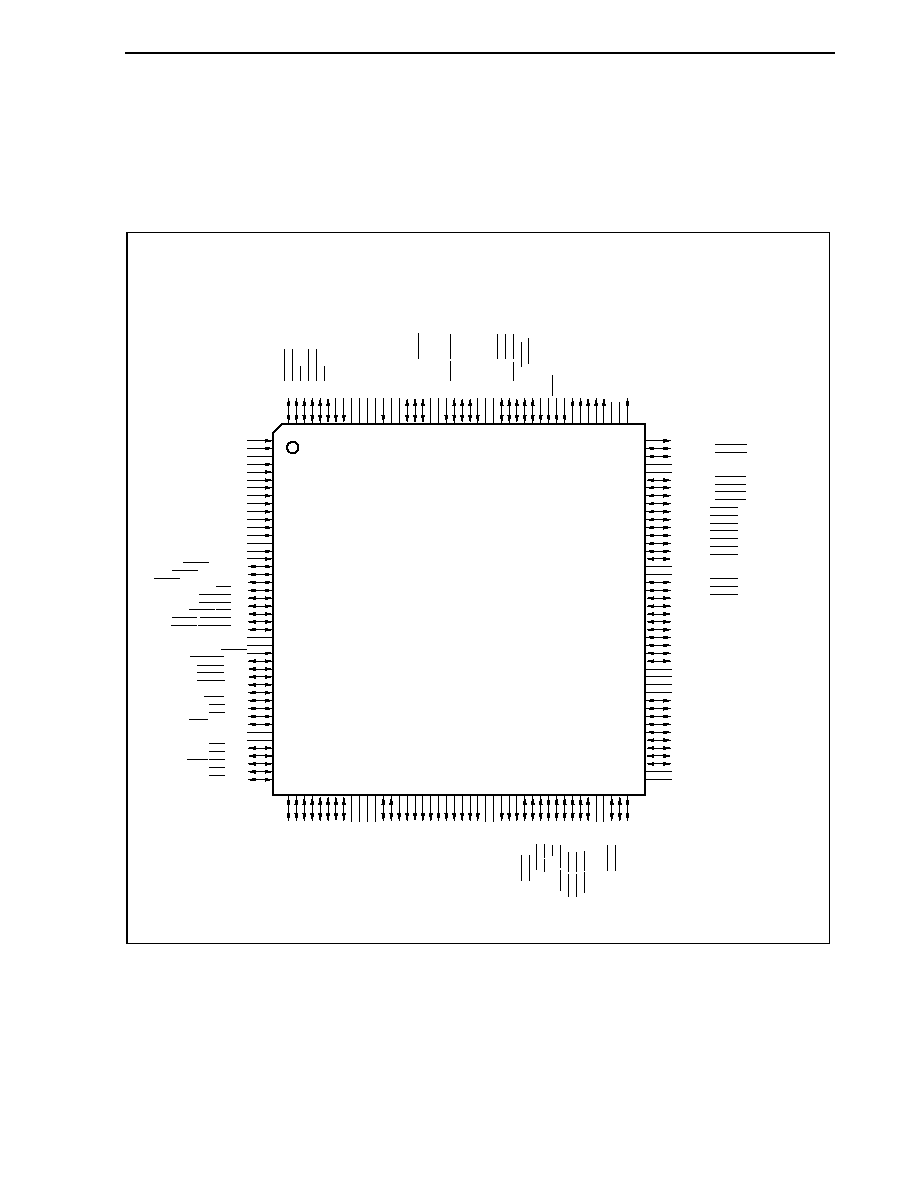

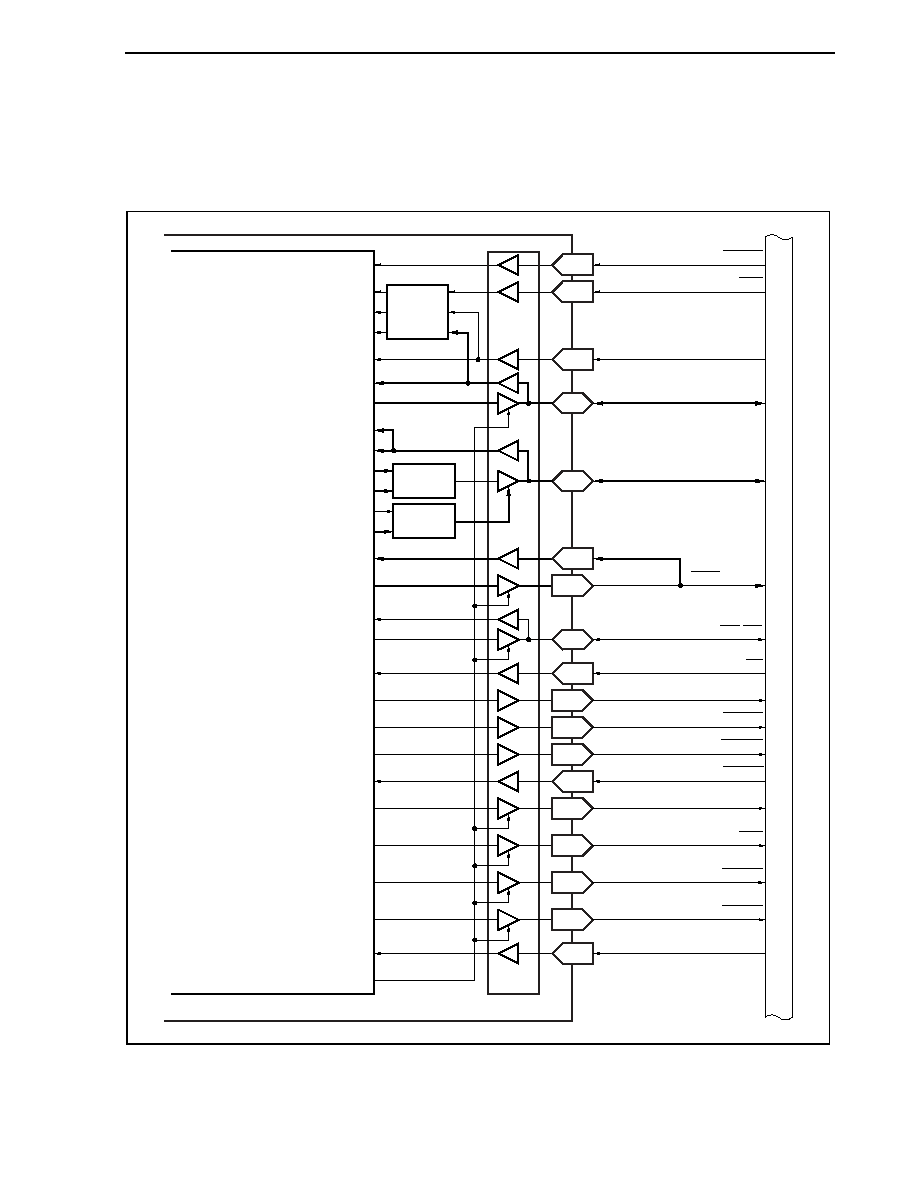

(3) V850E/MA3

�

144-pin plastic LQFP (fine pitch) (20

�

20)

�

PD703131AGJ-xxx-UEN

�

PD703133AGJ-xxx-UEN

�

PD70F3134AGJ-UEN

�

PD703131AYGJ-xxx-UEN

�

PD703133AYGJ-xxx-UEN

�

PD70F3134AYGJ-UEN

�

PD703132AGJ-xxx-UEN

�

PD703134AGJ-xxx-UEN

�

PD703132AYGJ-xxx-UEN

�

PD703134AYGJ-xxx-UEN

Top View

AD14/PDL14

AD13/PDL13

AD12/PDL12

AD11/PDL11

AD10/PDL10

AD9/PDL9

AD8/PDL8

EV

DD

EV

SS

AD7/PDL7

AD6/PDL6

AD5/PDL5

AD4/PDL4

AD3/PDL3

AD2/PDL2

AD1/PDL1

AD0/PDL0

INTP001/TOP01/INTPP01/P01

INTP000/TOP00/EVTP0/TIP0/INTPP00/P00

INTP115/TOQB3/EVTQ/P15

INTP114/TOQB2/TIQ/P14

INTP013/TOQT3/INTPQ3/TOQ3/P13

V

DD

V

SS

INTP012/TOQT2/INTPQ2/TOQ2/P12

INTP011/TOQT1/INTPQ1/TOQ1/P11

INTP010/TOQB1/INTPQ0/TOQ0/P10

TDO/TC3/P27

TDI/INTP126/TC2/P26

INTP125/TC1/TIUD10/TO10/P25

INTP124/TC0/P24

TRST

INTP004/DMARQ0/TCLR10/INTP11/P04

INTP005/DMARQ1/TCUD10/INTP10/P05

TMS/INTP106/DMARQ2/P06

TCK/INTP107/DMARQ3/P07

PCD3/SDRAS

PCS0/CS0

PCS1/CS1

PCS2/CS2/IOWR

PCS3/CS3

PCS4/CS4

PCS5/CS5/IORD

PCS6/CS6

PCS7/CS7

EV

SS

EV

DD

PCT0/LBE/LWR/LDQM

PCT1/UBE/UWR/UDQM

PCT4/RD

PCT5/WR/WE

PCT6/ASTB

PCT7/BCYST

PCM0/WAIT

PCM1/BUSCLK

PCM2/HLDAK

PCM3/HLDRQ

PCM4/REFRQ

P50/INTP050/INTPP20/TOP20/EVTP2/TIP2

P51/INTP051/INTPP21/TOP21

P20/NMI

P37/INTP137/ADTRG

V

SS

V

DD

P70/ANI0

P71/ANI1

P72/ANI2

P73/ANI3

P74/ANI4

P75/ANI5

P76/ANI6

P77/ANI7

EV

DD

EV

SS

DMAAK3/PBD3 DMAAK2/PBD2 DMAAK1/PBD1 DMAAK0/PBD0

INTP022/TOP11/INTPP11/P22

INTP021/TOP10/EVTP1/TIP1/INTPP10/P21

INTP134/RXD3/SCL

Note

/P34

INTP133/TXD3/SDA

Note

/P33

INTP132/ASCK2/SCK2/P32

INTP131/RXD2/SI2/P31 INTP130/TXD2/SO2/P30

ASCK1/SCK1/P45

RXD1/SI1/P44 TXD1/SO1/P43

ASCK0/SCK0/P42

RXD0/SI0/P41 TXD0/SO0/P40

CV

DD

X2 X1

CV

SS

CKSEL

PSEL

V

DD

V

SS

MODE0 MODE1 RESET

AV

DD1

ANO1/P81 ANO0/P80

AV

SS1

AV

SS0

AV

DD0

PDL15/AD15 PAL0/A0 PAL1/A1 PAL2/A2 PAL3/A3 PAL4/A4 PAL5/A5 PAL6/A6 PAL7/A7 EV

SS

EV

DD

PAL8/A8 PAL9/A9 PAL10/A10 PAL11/A11 PAL12/A12 PAL13/A13 PAL14/A14 PAL15/A15 V

SS

V

DD

PAH0/A16 PAH1/A17 PAH2/A18 PAH3/A19 PAH4/A20 PAH5/A21 PAH6/A22 PAH7/A23 PAH8/A24 PAH9/A25 EV

SS

EV

DD

PCD0/SDCKE PCD1/SDCLK PCD2/SDCAS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

144 143 142 141 140 139 138 137 136 135 134 133 132 131 130 129 128 127 126 125 124 123 122 121 120 119 118 117 116 115 114 113 112 111 110 109

37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

Note SCL and SDA are available only in the

�

PD703131Y, 703132Y, 703133Y, 703134Y, 703137Y, and

70F3134Y.

CHAPTER 1 OVERVIEW OF EACH PRODUCT

Application Note U17121EJ1V1AN

19

�

161-pin plastic FBGA (13

�

13)

�

PD703131AF1-EN4

�

PD703133AF1-xxx-EN4

�

PD70F3134AF1-EN4

�

PD703131AYF1-xxx-EN4

�

PD703133AYF1-xxx-EN4

�

PD70F3134AYF1-EN4

�

PD703132AF1-xxx-EN4

�

PD703134AF1-xxx-EN4

�

PD703132AYF1-xxx-EN4

�

PD703134AYF1-xxx-EN4

14

13

12

11

10

9

8

7

6

5

4

3

2

1

Top View

Bottom View

P N M L K J H G F E D C B A

A B C D E F G H J K L M N P

Index mark

Index mark

(1/2)

Pin No.

Name

Pin No.

Name

Pin No.

Name

A1 EV

SS

B8

V

SS

D1

EV

SS

A2 AD15/PDL15

B9 A18/PAH2

D2 AD10/PDL10

A3 A2/PAL2

B10 A21/PAH5

D3 AD14/PDL14

A4 A5/PAL5

B11 A25/PAH9

D4 A3/PAL3

A5 EV

SS

B12

SDCLK/PCD1

D5

A6/PAL6

A6 A9/PAL9

B13 CS1/PCS1

D6 A10/PAL10

A7 A12/PAL12

B14 EV

SS

D7

A14/PAL14

A8 A15/PAL15

C1 EV

SS

D8

A16/PAH0

A9 A17/PAH1

C2 AD9/PDL9

D9 A20/PAH4

A10

-

C3 AD13/PDL13

D10 A23/PAH7

A11 A24/PAH8

C4 A1/PAL1

D11 SDCKE/PCD0

A12 EV

DD

C5

A7/PAL7

D12

CS0/PCS0

A13 SDCAS/PCD2

C6 EV

DD

D13

CS5/IORD/PCS5

A14 SDRAS/PCD3

C7 A11/PAL11

D14 EV

SS

B1 EV

SS

C8

V

DD

E1

AD5/PDL5

B2 AD12/PDL12

C9 A19/PAH3

E2 AD7/PDL7

B3 A0/PAL0

C10 A22/PAH6

E3 AD8/PDL8

B4 A4/PAL4

C11 EV

SS

E4

AD11/PDL11

B5 EV

SS

C12

CS3/PCS3

E5

-

B6 A8/PAL8

C13 CS2/IOWR/PCS2

E11 CS6/PCS6

B7 A13/PAL13

C14 EV

SS

E12

CS4/PCS4

CHAPTER 1 OVERVIEW OF EACH PRODUCT

Application Note U17121EJ1V1AN

20

(2/2)

Pin No.

Name

Pin No.

Name

Pin No.

Name

E13 CS7/PCS7

J14 NMI/P20

M11 AV

SS0

E14 EV

SS

K1

TOQT1/INTP011/INTPQ1/TOQ1/P11

M12 ANI6/P76

F1 AD2/PDL2

K2 TC3/TDO/P27

M13 ANI5/P75

F2 AD3/PDL3

K3 TC0/INTP124/P24

M14

-

F3 AD4/PDL4

K4 TC2/TDI/INTP126/P26

N1 EV

SS

F4 EV

DD

K11

ANI1/P71

N2

DMARQ3/TCK/INTP107/P07

F11 RD/PCT4

K12 ANI0/P70

N3 DMAAK3/PBD3

F12 EV

DD

K13

V

SS

N4

DMAAK0/PBD0

F13 LBE/LWR/LDQM/PCT0

K14 V

DD

N5

TXD3/SDA

Note

/INTP133/P33

F14 UBE/UWR/UDQM/PCT1

L1 EV

SS

N6

TXD2/SO2/INTP130/P30

G1 TOP01/INTP001/INTPP01/P01 L2 TC1/TIUD10/TO10/INTP125/P25

N7 ASCK0/SCK0/P42

G2

TOP00/INTP000/EVTP0/TIP0/

INTPP00/P00

L3 DMARQ2/TMS/INTP106/P06

N8 V

SS

G3 AD0/PDL0

L4 TRST

N9 X2

G4 AD6/PDL6

L5 TOP11/INTPP11/INTP022/P22 N10 CV

SS

G11 WAIT/PCM0

L6 ASCK2/SCK2/INTP132/P32

N11 ANO1/P81

G12 WR/WE/PCT5

L7 ASCK1/SCK1/P45

N12 AV

SS1

G13 BCYST/PCT7

L8 TXD0/SO0/P40

N13 AV

DD1

G14 ASTB/PCT6

L9 MODE0

N14

-

H1 TOQB3/INTP115/EVTQ/P15

L10 AV

DD0

P1

EV

DD

H2 TOQB2/INTP114/TIQ/P14

L11 ANI7/P77

P2 EV

SS

H3

TOQT3/INTP013/INTPQ3/TOQ3/P13

L12 ANI4/P74

P3 DMAAK1/PBD1

H4 AD1/PDL1

L13 ANI3/P73

P4 TOP10/INTPP10/EVTP1/TIP1/

INTP021/P21

H11 REFRQ/PCM4

L14 ANI2/P72

P5 EV

SS

H12 HLDRQ/PCM3

M1 EV

SS

P6

RXD1/SI1/P44

H13 HLDAK/PCM2

M2 DMARQ1/TCUD10/INTP10/

INTP005/P05

P7 RXD0/SI0/P41

H14 BUSCLK/PCM1

M3 DMARQ0/INTP11/TCLR10/

INTP004/P04

P8 PSEL

J1 V

DD

M4

DMAAK2/PBD2

P9

CV

DD

J2

TOQT2/INTP012/INTPQ2/TOQ2/P12

M5 RXD3/SCL

Note

/INTP134/P34 P10

X1

J3

TOQB1/INTP010/INTPQ0/TOQ0/P10

M6 RXD2/SI2/INTP131/P31

P11

-

J4 V

SS

M7

TXD1/SO1/P43

P12

RESET

J11 ADTRG/INTP137/P37

M8 V

DD

P13

ANO0/P80

J12 TOP21/INTPP21/INTP051/P51 M9 CKSEL

P14

-

J13

TOP20/INTPP20/EVTP2/TIP2/

INTP050/P50

M10 MODE1

Note SCL and SDA are available only in the

�

PD703131AY, 703132AY, 703133AY, 703134AY, and 70F3134AY.

Remark Leave the A10, E5, M14, N14, P11, and P14 pins open.

CHAPTER 1 OVERVIEW OF EACH PRODUCT

Application Note U17121EJ1V1AN

21

(4) V850E/ME2

�

176-pin plastic LQFP (fine pitch) (24

�

24)

�

PD703111AGM-10-UEU

�

PD703111AGM-13-UEU

�

PD703111AGM-15-UEU

Top View

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

TRCDATA3

PDH15/D31/INTPD15/PWM1

PDH14/D30/INTPD14/PWM0

EV

SS

EV

DD

PDH13/D29/INTPD13/TIUD11

PDH12/D28/INTPD12/TO11

PDH11/D27/INTPD11/INTP111/TCLR11

PDH10/D26/INTPD10/INTP110/TCUD11

PDH9/D25/INTPD9/TIUD10

PDH8/D24/INTPD8/TO10

PDH7/D23/INTPD7/INTP101/TCLR10

PDH6/D22/INTPD6/INTP100/TCUD10

PDH5/D21/INTPD5/TOC5

PDH4/D20/INTPD4

PDH3/D19/INTPD3

EV

SS

EV

DD

PDH2/D18/INTPD2/TOC4

PDH1/D17/INTPD1

PDH0/D16/INTPD0

D15

D14

D13

D12

D11

D10

D9

D8

IV

SS

IV

DD

EV

SS

EV

DD

D7

D6

D5

D4

D3

D2

D1

D0

SDCKE/PCD0

EV

SS

EV

DD

176

175

174

173

172

171

170

169

168

167

166

165

164

163

162

161

160

159

158

157

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

P72/DMARQ2/INTPC20/TIC2

P73/DMAAK2/INTPC21

P74/TC2/TOC2

P75/DMARQ3/INTPC30/TIC3

P76/DMAAK3/INTPC31

P77/TC3/TOC3

SSEL0

SSEL1

PLLV

SS

PLLV

DD

OSCV

SS

X2

X1

OSCV

DD

UV

DD

UDM

UDP

P10/UCLK/INTP10

IV

SS

IV

DD

PLLSEL

P11/SCK0/INTP11

P12/RXD0/SI0

P13/TXD0/SO0

P20/NMI

EV

SS

EV

DD

P21/RXD1/INTP21

P22/TXD1/INTP22

P23/SCK1/INTP23

P24/SI1/INTP24

P25/SO1/INTP25

DCK

DMS

DRST

DDI

DDO

TRCCLK

TRCEND

TRCDATA0

TRCDATA1

IV

SS

IV

DD

TRCDATA2

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

A25/PAH9

A24/PAH8

A23/PAH7

A22/PAH6

A21/PAH5

A20/PAH4

A19/PAH3

A18/PAH2

EV

DD

EV

SS

IV

DD

IV

SS

A17/PAH1

A16/PAH0

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

EV

DD

EV

SS

A4

A3

A2

INTPL1/A1/PAL1

INTPL0/A0/PAL0

BCYST/PCT7

WE/WR/PCT5

RD/PCT4

UUDQM/UUBE/UUWR/PCT3

PCT2/ULWR/ULBE/ULDQM

PCT1/LUWR/LUBE/LUDQM

PCT0/LLWR/LLBE/LLDQM

IV

DD

IV

SS

SDRAS/PCD3

SDCAS/PCD2

BUSCLK/PCD1

JIT1

JIT0

AV

DD

AV

REFP

ANI0

ANI1

ANI2

ANI3

ANI4

ANI5

ANI6

ANI7

AV

REFM

AV

SS

MODE1

MODE0

INTP67/TOC1/P67

INTP66/INTPC11/P66

INTP65/TIC1/INTPC10/P65

TOC0/TC1/P55

INTPC01/DMAAK1/P54

INTPC00/TIC0/DMARQ1/P53

INTP52/TC0/P52

INTP51/DMAAK0/P51

INTP50/DMARQ0/P50

IV

DD

IV

SS

RESET

ADTRG/SELFREF/PCM5

REFRQ/PCM4

HLDRQ/PCM3

HLDAK/PCM2

PCM1

WAIT/PCM0

CS7/PCS7

CS6/PCS6

IORD/CS5/PCS5

EV

DD

EV

SS

CS4/PCS4

CS3/PCS3

IOWR/CS2/PCS2

CS1/PCS1

CS0/PCS0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

CHAPTER 1 OVERVIEW OF EACH PRODUCT

Application Note U17121EJ1V1AN

22

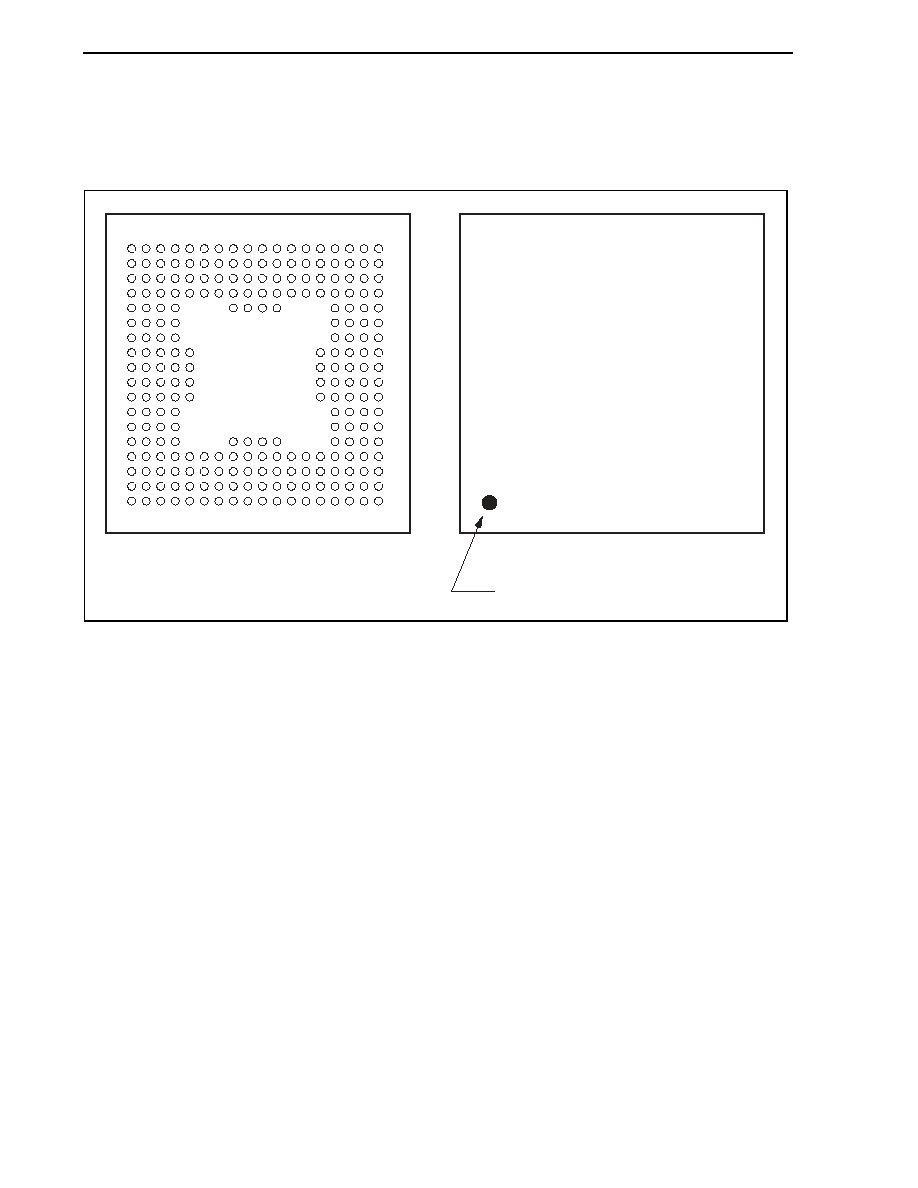

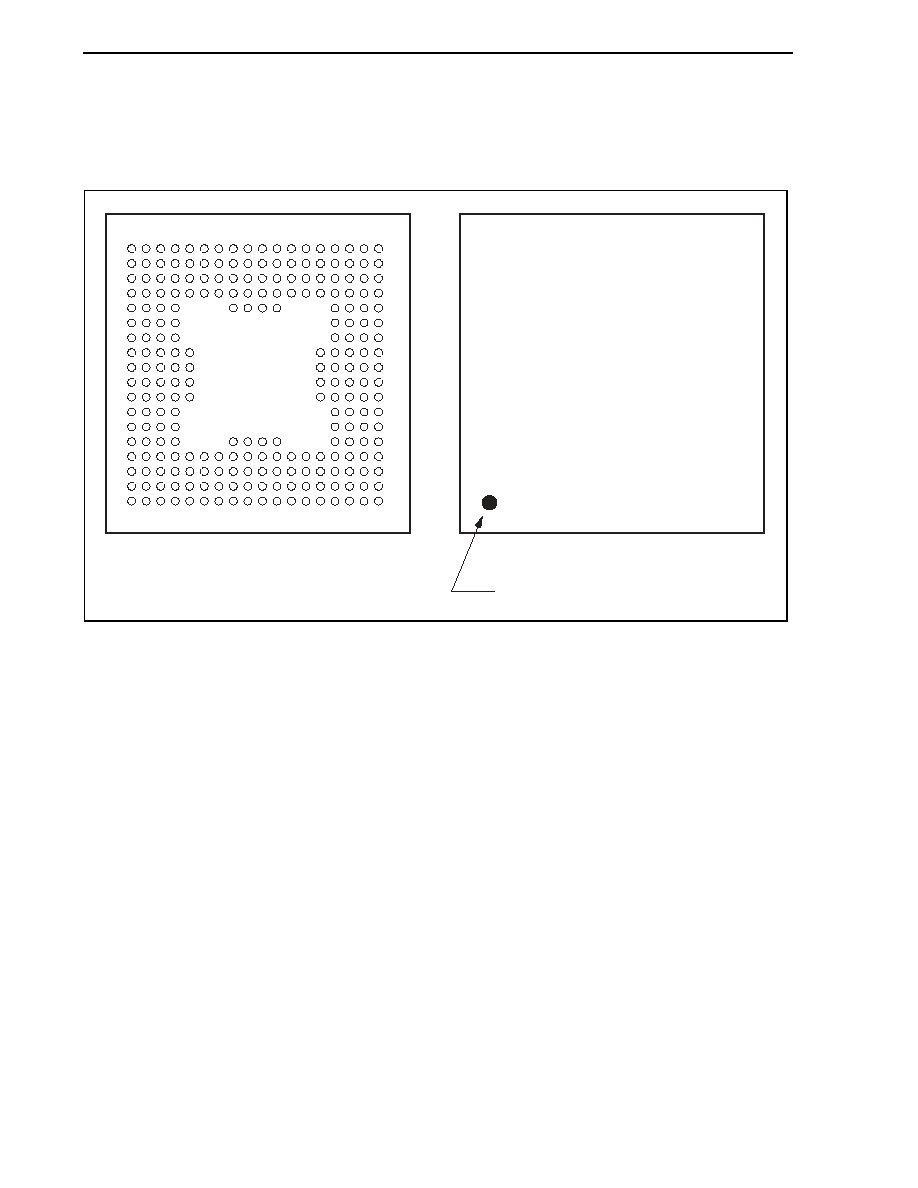

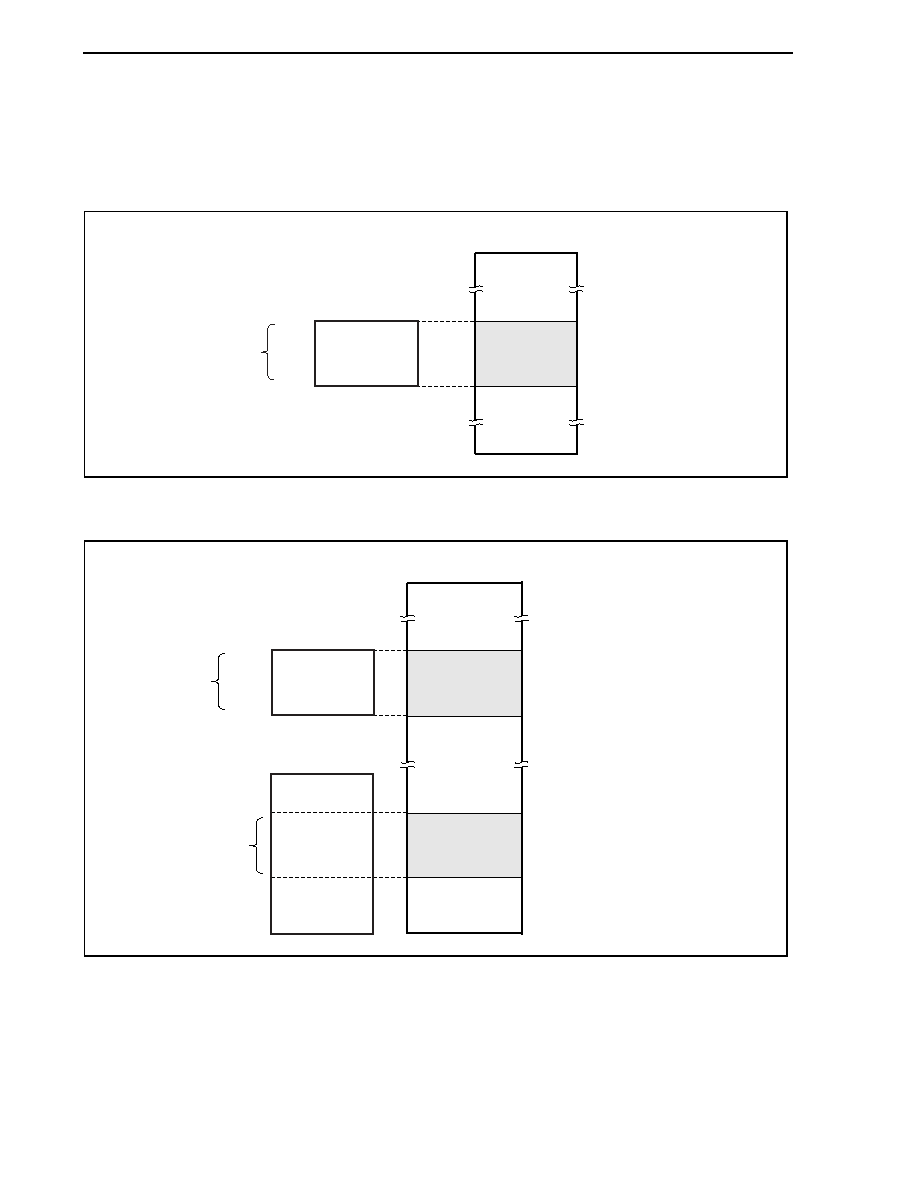

�

240-pin plastic FBGA (16

�

16)

�

PD703111AF1-10-GA3

�

PD703111AF1-13-GA3

�

PD703111AF1-15-GA3

Bottom View

Top View

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

Index mark

E F G H J K L M N P R T U V

A B C D

P N M L K J H G F E D C B A

V U T R

CHAPTER 1 OVERVIEW OF EACH PRODUCT

Application Note U17121EJ1V1AN

23

(1/2)

Pin No.

Name

Pin No.

Name

Pin No.

Name

A1

-

C12 IV

DD

G3

EV

SS

A2 IV

SS

C13

PAH2/A18

G4

D7

A3 PCT0/LLWR/LLBE/LLDQM

C14 PAH4/A20

G15 PCM1

A4

-

C15 PAH6/A22

G16 PCM3/HLDRQ

A5 PCT4/RD

C16

-

G17 PCM4/REFRQ

A6

-

C17 PCS0/CS0

G18 PCM5/ADTRG/SELFREF

A7

-

C18

-

H1

-

A8 EV

DD

D1

D0 H2

D8

A9 A9

D2 EV

SS

H3

D9

A10

-

D3 PCD0/SDCKE

H4 D10

A11 A14

D4 EV

DD

H5

IV

SS

A12 IV

SS

D5

PCT1/LUWR/LUBE/LUDQM

H14

-

A13 EV

DD

D6

-

H15 RESET

A14

-

D7 PAL0/INTPL0/A0

H16 IV

SS

A15 PAH5/A21

D8 A4

H17

-

A16 PAH7/A23

D9 A6

H18 IV

DD

A17 PAH9/A25

D10

-

J1

-

A18

-

D11 A13

J2 D11

B1

-

D12 EV

SS

J3

D12

B2 PCD1/BUSCLK

D13 PAH3/A19

J4

-

B3 PCD2/SDCAS

D14

-

J5 D13

B4

-

D15

-

J14

-

B5 PCT3/UUWR/UUBE/UUDQM D16 PCS2/CS2/IOWR

J15 P50/INTP50/DMARQ0

B6 PCT7/BCYST

D17 PCS3/CS3

J16 P51/INTP51/DMAAK0

B7 A2

D18 EV

DD

J17

P52/INTP52/TC0

B8

-

E1 D3

J18 P53/INTPC00/TIC0/DMARQ1

B9 A8

E2 D2

K1 D14

B10 A12

E3 D1

K2 D15

B11 PAH0/A16

E4

-

K3 PDH0/D16/INTPD0

B12

-

E8 A3

K4 PDH1/D17/INTPD1

B13

-

E9 A5

K5 PDH2/D18/INTPD2/TOC4

B14

-

E10 A10

K14 P55/TOC0/TC1

B15

-

E11 PAH1/A17

K15 P54/INTPC01/DMAAK1

B16 PAH8/A24

E15 PCS4/CS4

K16 P65/INTP65/INTPC10/TIC1

B17

-

E16 EV

SS

K17

P66/INTP66/INTPC11

B18 PCS1/CS1

E17 PCS5/CS5/IORD

K18

-

C1

-

E18 PCS6/CS6

L1 EV

DD

C2

-

F1 D6

L2

-

C3 PCD3/SDRAS

F2 D5

L3 EV

SS

C4 IV

DD

F3 D4

L4 PDH3/D19/INTPD3

C5 PCT2/ULWR/ULBE/ULDQM

F4

-

L5 PDH4/D20/INTPD4

C6 PCT5/WE/WR

F15

-

L14 MODE1

C7 PAL1/INTPL1/A1

F16 PCS7/CS7

L15

-

C8 EV

SS

F17 PCM0/WAIT

L16 MODE0

C9 A7

F18 PCM2/HLDAK

L17

-

C10 A11

G1 IV

DD

L18

P67/INTP67/TOC1

C11 A15

G2 EV

DD

M1

-

CHAPTER 1 OVERVIEW OF EACH PRODUCT

Application Note U17121EJ1V1AN

24

(2/2)

Pin No.

Name

Pin No.

Name

Pin No.

Name

M2 PDH5/D21/INTPD5/TOC5

R7 DCK

U4

-

M3

PDH6/D22/INTPD6/INTP100/

TCUD10

R8 EV

DD

U5

TRCCLK

M4

-

R9 P11/INTP11/SCK0

U6 DRST

M15 ANI6

R10 IV

SS

U7

P25/INTP25/SO1

M16 AV

REFM

R11

UDM

U8

P22/INTP22/TXD1

M17 ANI7

R12 X2

U9 EV

SS

M18 AV

SS

R13

PLLV

DD

U10

IV

DD

N1

PDH7/D23/INTPD7/INTP101/

TCLR10

R14 SSEL0

U11

-

N2 PDH8/D24/INTPD8/TO10

R15

-

U12 OSCV

DD

N3 PDH9/D25/INTPD9/TIUD10

R16 AV

REFP

U13

-

N4

PDH10/D26/INTPD10/

INTP110/TCUD11

R17 AV

DD

U14

-

N15 ANI2

R18

-

U15 P76/INTPC31/DMAAK3

N16 ANI3

T1 EV

DD

U16

P73/INTPC21/DMAAK2

N17 ANI4

T2 TRCDATA3

U17 P72/INTPC20/TIC2/DMARQ2

N18 ANI5

T3

-

U18

-

P1

-

T4 TRCDATA1

V1

-

P2

PDH11/D27/INTPD11/

INTP111/TCLR11

T5 TRCEND

V2 TRCDATA2

P3 PDH13/D29/INTPD13/TIUD11 T6 DDI

V3 IV

SS

P4

-

T7

-

V4 TRCDATA0

P8 P23/INTP23/SCK1

T8 P21/INTP21/RXD1

V5

-

P9 P12/SI0/RXD0

T9 P20/NMI

V6 DMS

P10

-

T10

-

V7 P24/INTP24/SI1

P11 UV

DD

T11

UDP V8

-

P15

-

T12 X1

V9 P13/SO0/TXD0

P16 ANI0

T13 OSCV

SS

V10

PLLSEL

P17 ANI1

T14 SSEL1

V11 P10/INTP10/UCLK

P18

-

T15 P75/INTPC30/TIC3/DMARQ3 V12

-

R1 PDH12/D28/INTPD12/TO11

T16

-

V13

-

R2 EV

SS

T17

JIT1 V14

-

R3 PDH14/D30/INTPD14/PWM0 T18 JIT0

V15 PLLV

SS

R4 IV

DD

U1

PDH15/D31/INTPD15/PWM1

V16

P77/TOC3/TC3

R5

-

U2

-

V17 P74/TOC2/TC2

R6 DDO

U3

-

V18

-

Remark Leave the A1, A4, A6, A7, A10, A14, A18, B1, B4, B8, B12 to B15, B17, C1, C2, C16, C18, D6, D10, D14,

D15, E4, F4, F15, H1, H14, H17, J1, J4, J14, K18, L2, L15, L17, M1, M4, P1, P4, P10, P15, P18, R5, R15,

R18, T3, T7, T10, T16, U2 to U4, U11, U13, U14, U18, V1, V5, V8, V12 to V14, and V18 pins open.

CHAPTER 1 OVERVIEW OF EACH PRODUCT

Application Note U17121EJ1V1AN

25

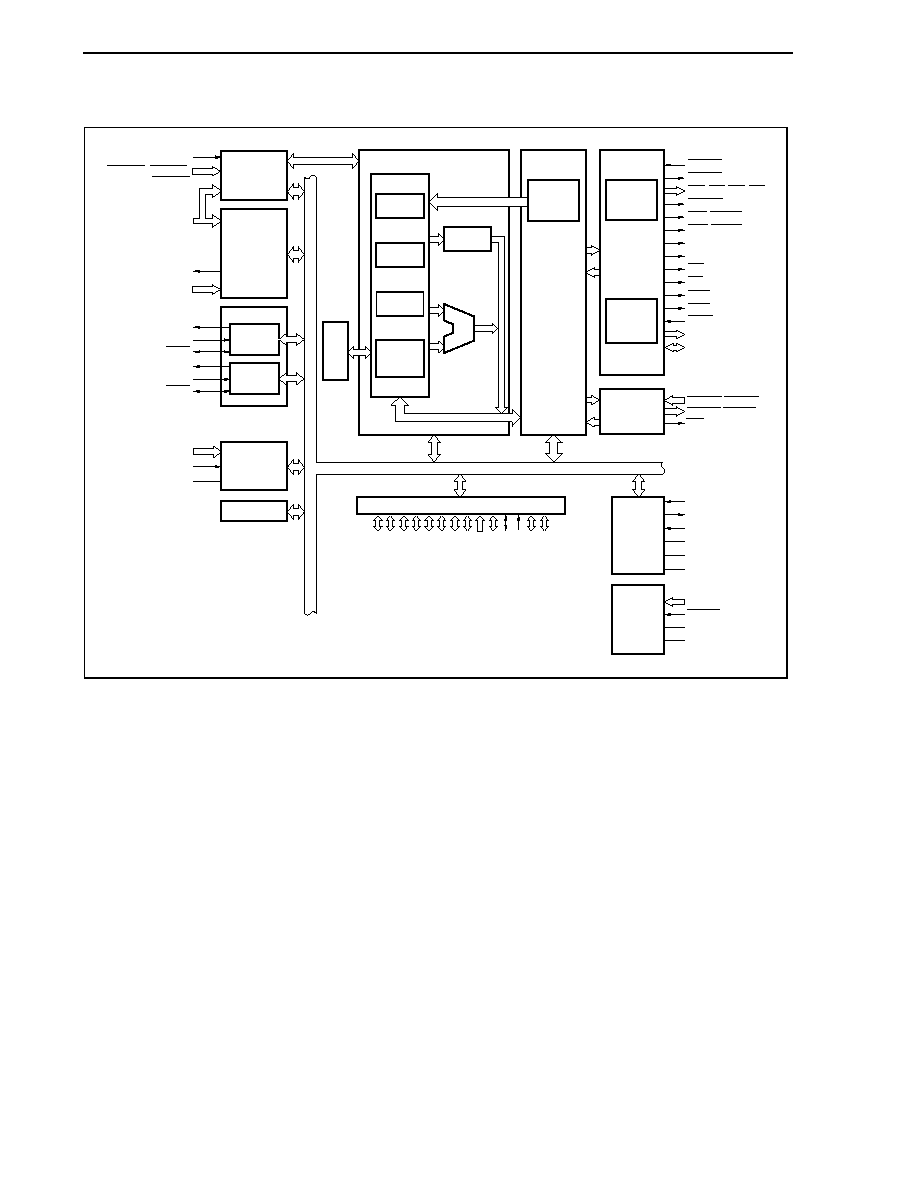

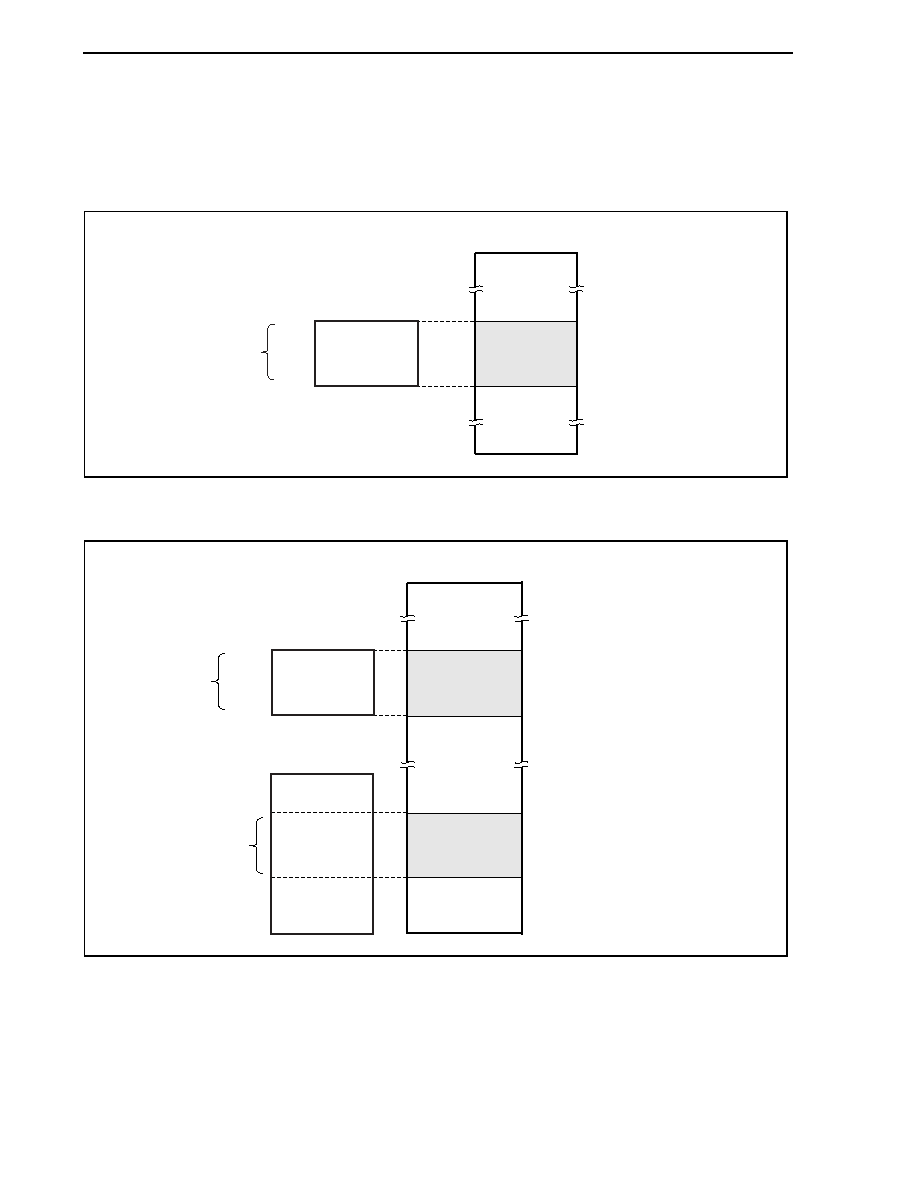

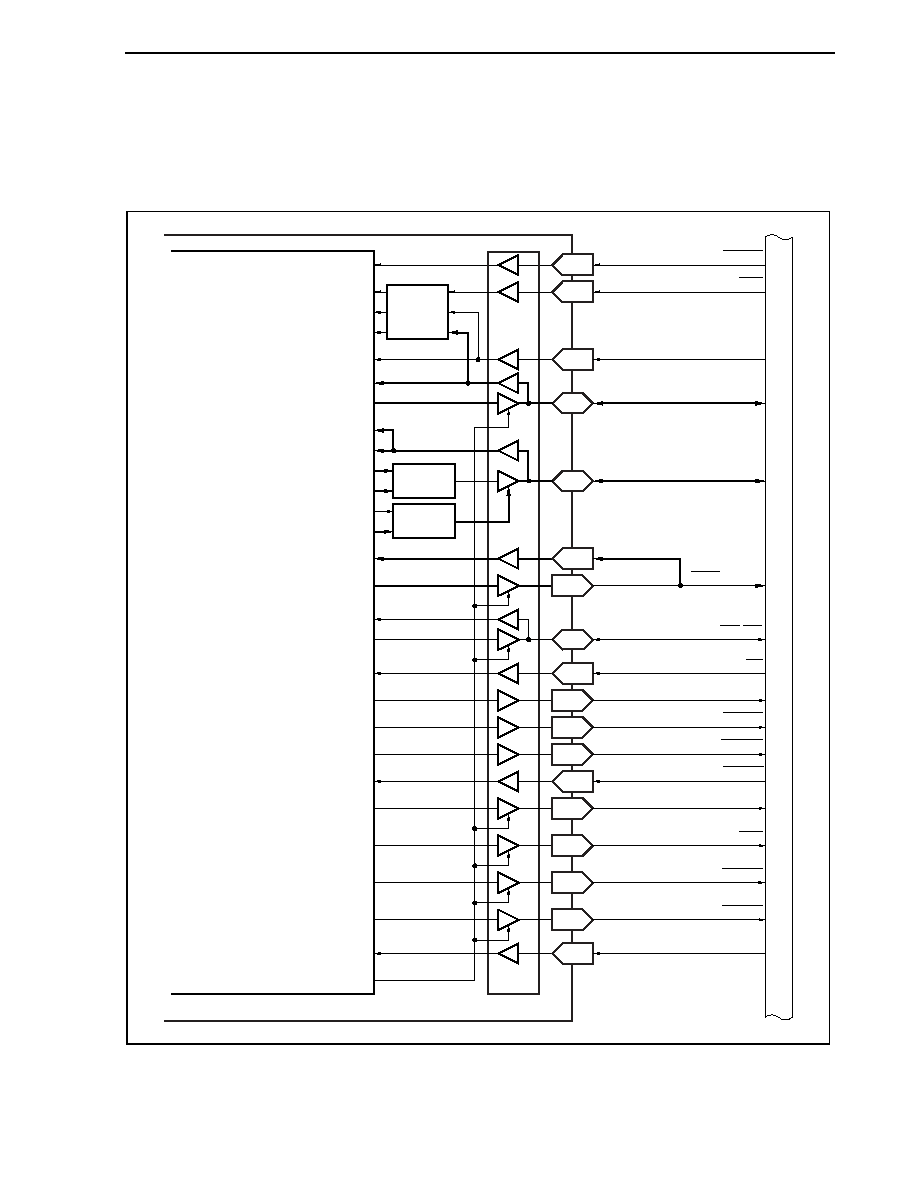

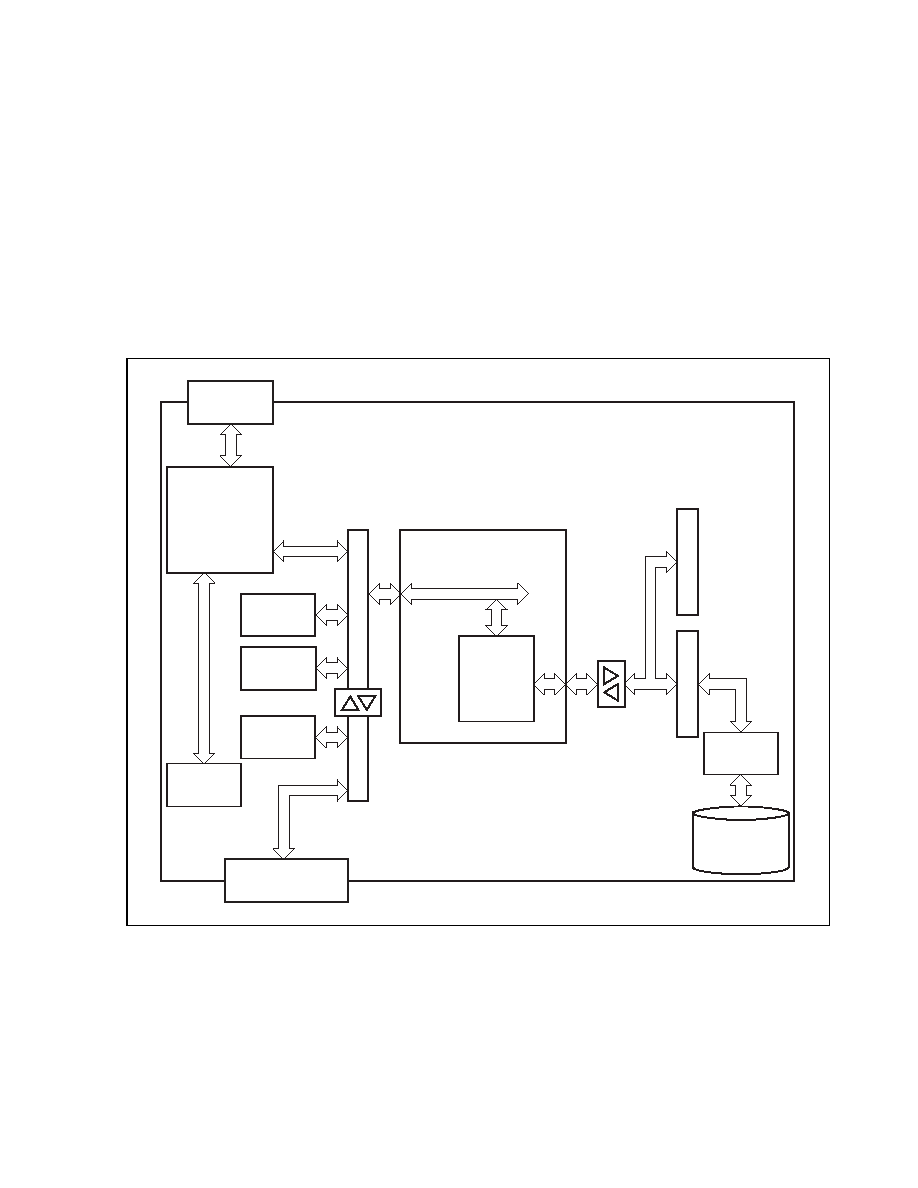

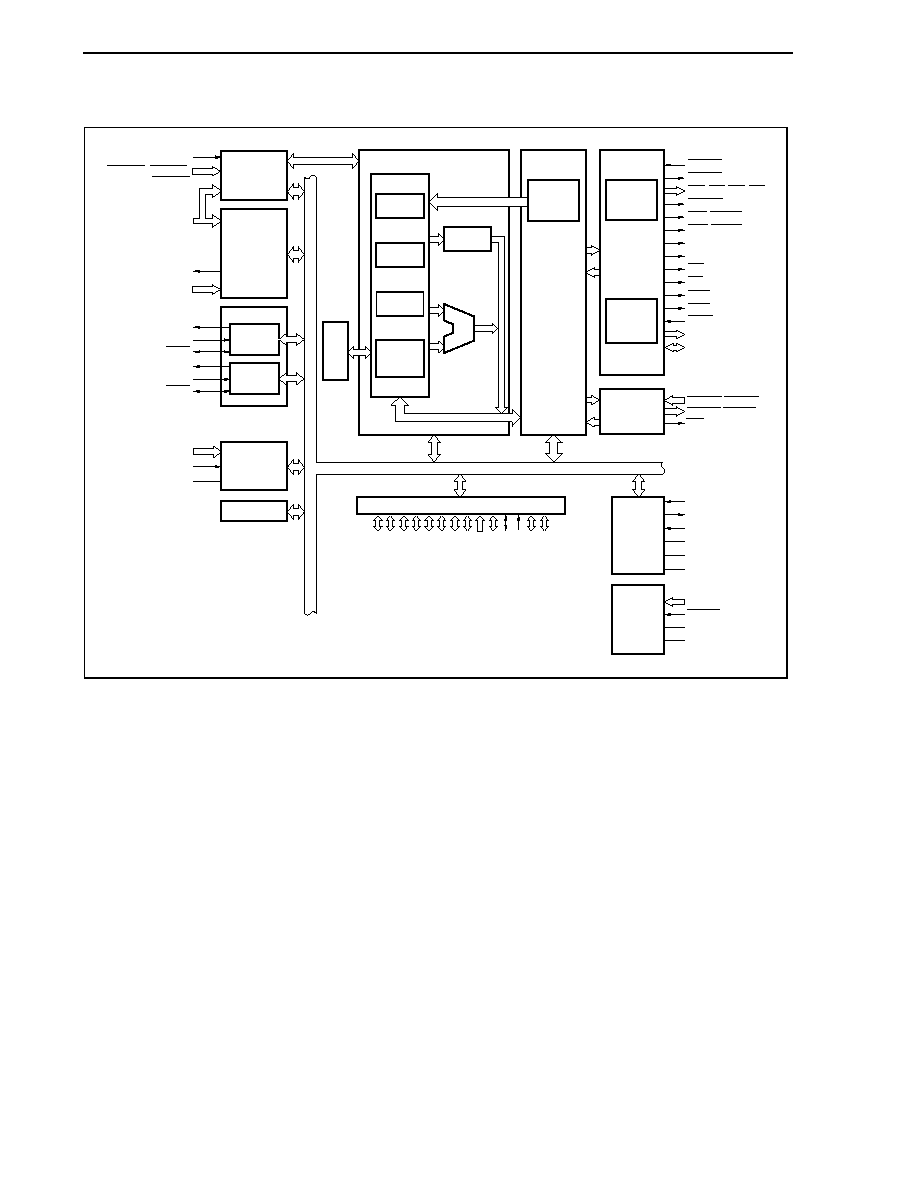

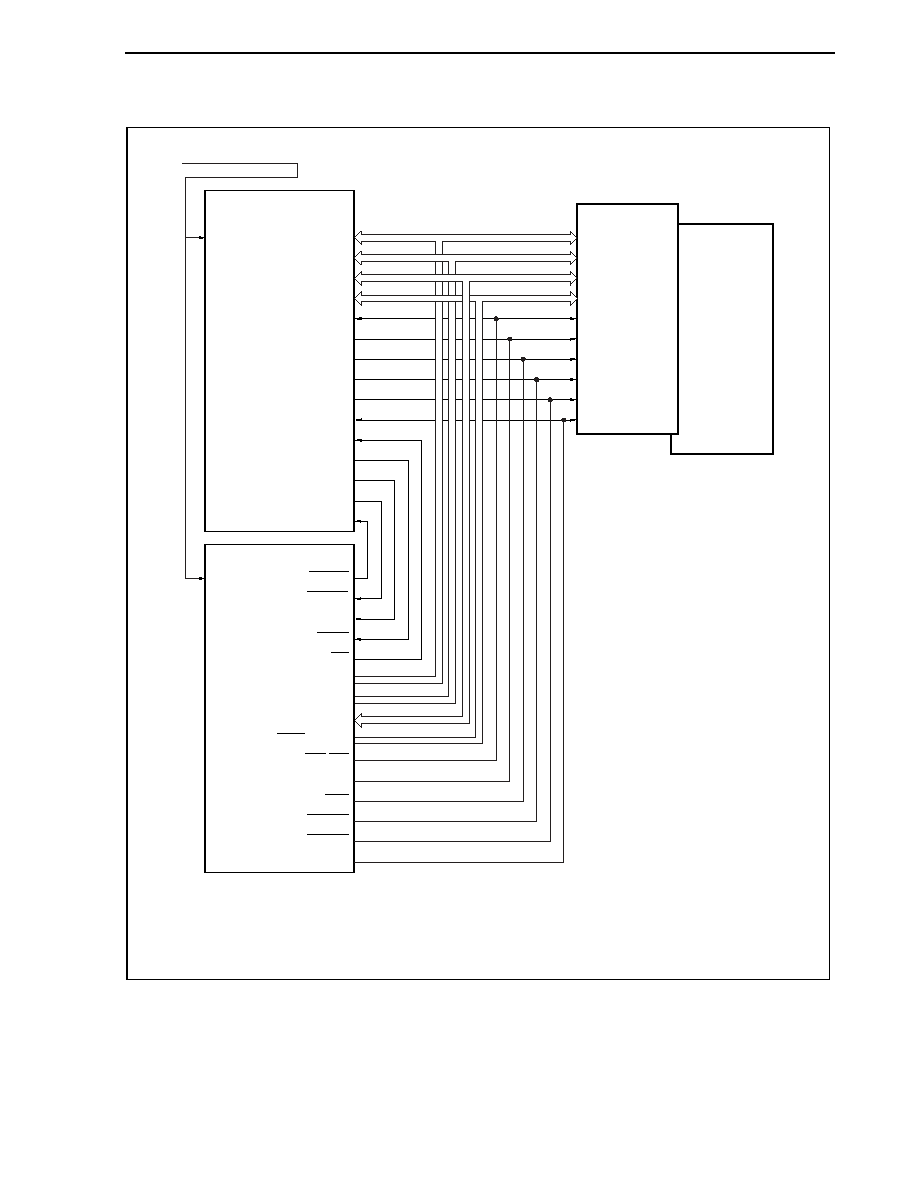

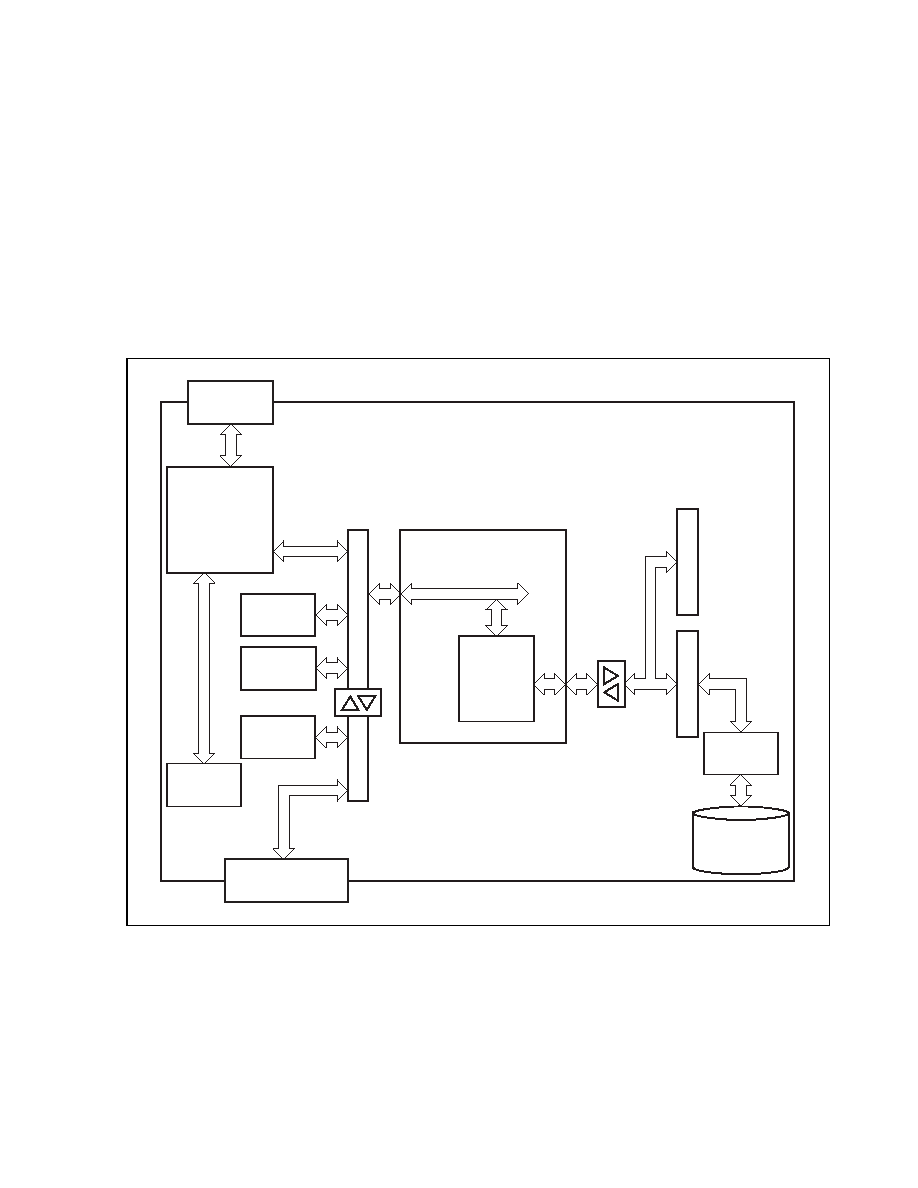

1.5 Internal Block Diagram

(1) V850E/MA1

NMI

INTP000, INTP001,

INTP010, INTP011,

INTP020, INTP021,

INTP030, INTP031

INTP100 to INTP103,

INTP110 to INTP113,

INTP120 to INTP123,

INTP130 to INTP133

TO00 to TO03

TI000, TI010,

TI020, TI030

INTC

RPU

SIO

ROM

Note 1

RAM

Note 2

CPU

32-bit

barrel shifter

PC

System

registers

General-

purpose

registers

(32 bits

�

32)

ALU

Multiplier

(32

�

32

64)

Ports

PDL0 to PDL15

PAL0 to PAL15

PAH0 to PAH9

PCS0 to PCS7

PCT0, PCT1, PCT4 to PCT7

PCM0 to PCM5

PCD0 to PCD3

PBD0 to PBD3

P70 to P77

P50 to P52

P40 to P45

P30 to P37

P21 to P27

P20

P10 to P13

P00 to P07

CG

System

controller

BCU

CLKOUT

CKSEL

X1

X2

CV

DD

CV

SS

MODE0, MODE1

MODE2/V

PP

Note 3

RESET

V

DD

V

SS

UART0/CSI0

UART1/CSI1

UART2

CSI2

ADC

SO0/TXD0

SI0/RXD0

SCK0

SO1/TXD1

SI1/RXD1

SCK1

TXD2

RXD2

PWM0

SO2

SI2

SCK2

ANI0 to ANI7

AV

REF

/AV

DD

AV

SS

ADTRG

Instruction

queue

MEMC

HLDRQ

HLDAK

CS0, CS7

CS1/RAS1, CS3/RAS3

CS4/RAS4, CS6/RAS6

CS2/IORD

CS5/IOWR

SELFREF

REFRQ

BCYST

LBE/SDCAS

UBE/SDRAS

SDCLK

SDCKE

WE

RD

OE

UWR/UCAS/UDQM

LWR/LCAS/LDQM

WAIT

A0 to A25

D0 to D15

BUSCLK

DRAMC

DMAC

ROMC

PWM0

PWM1

PWM1

DMARQ0 to DMARQ3

DMAAK0 to DMAAK3

TC0 to TC3

Notes 1.

�

PD703103A: ROMless

�

PD703105A, 703106A:

128 KB (mask ROM)

�

PD703107A:

256 KB (mask ROM)

�

PD70F3107A:

256 KB (flash memory)

2.

�

PD703103A, 703105A:

4 KB

�

PD703106A, 703107A, 70F3107A: 10 KB

3. Available only in the

�

PD70F3107A.

CHAPTER 1 OVERVIEW OF EACH PRODUCT

Application Note U17121EJ1V1AN

26

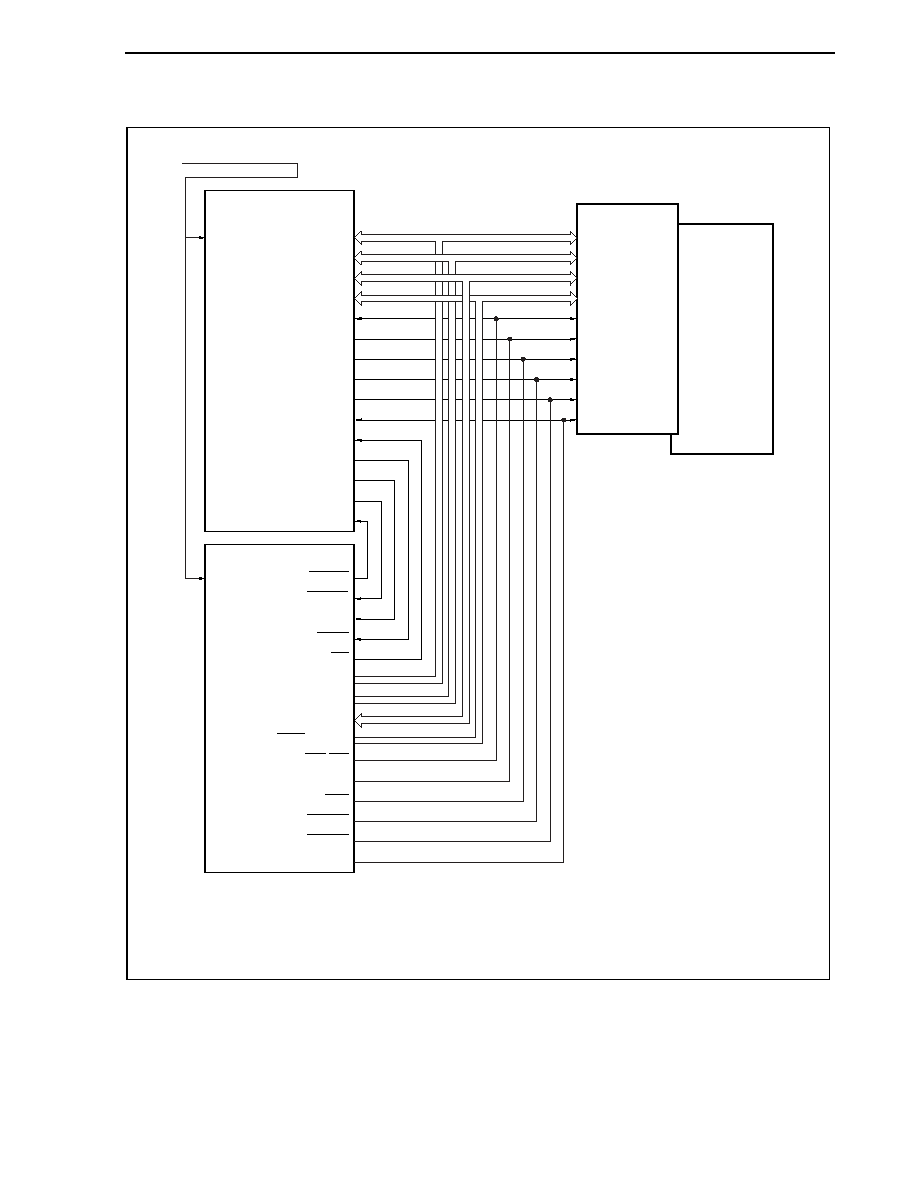

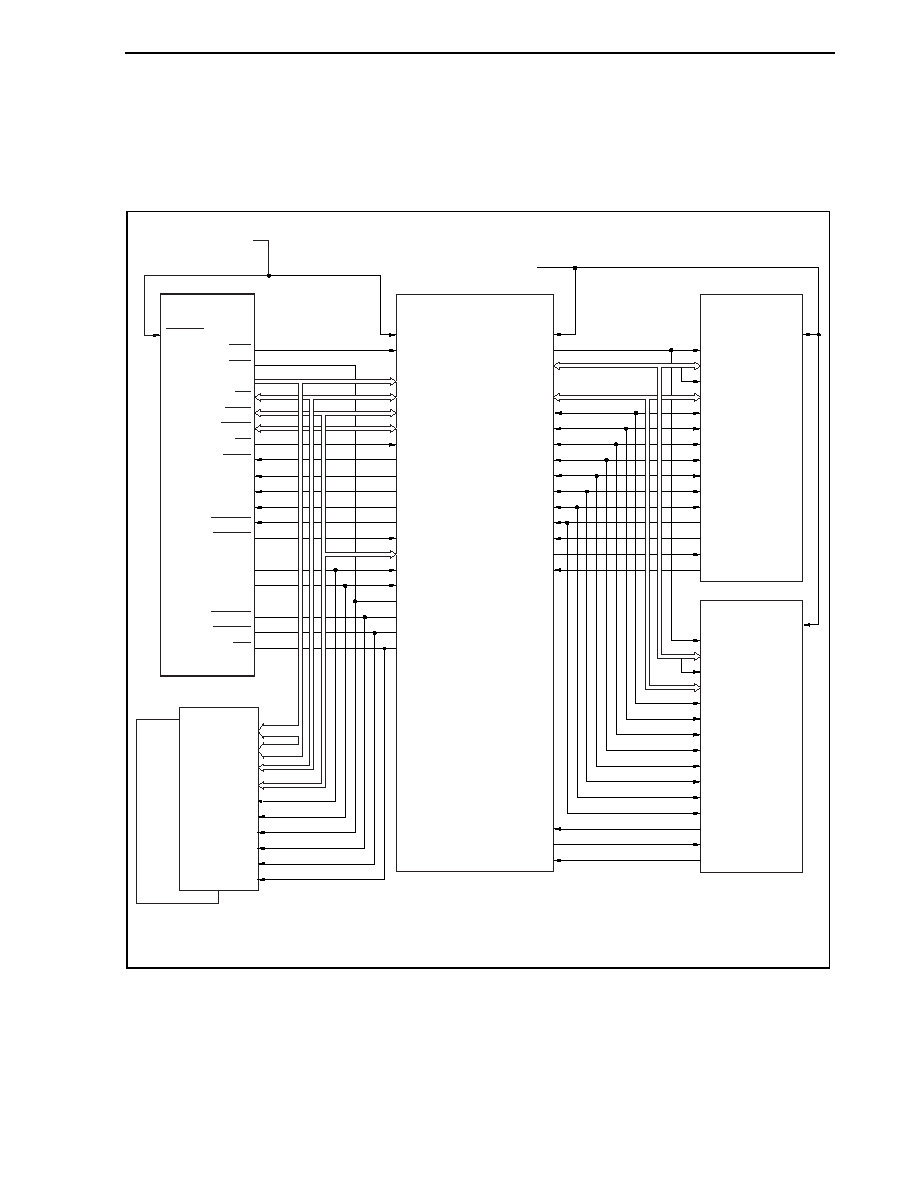

(2) V850E/MA2

NMI

INTP000, INTP001,

INTP010, INTP011

INTP100, INTP101,

INTP110

TO00

TI000, TI010

INTC

RPU

SIO

RAM

4 KB

CPU

32-bit

barrel shifter

PC

System

registers

General-

purpose

registers

(32 bits

�

32)

ALU

Multiplier

(32

�

32

64)

Ports

PDL0 to PDL15

PAL0 to PAL15

PAH0 to PAH8

PCS0, PCS3, PCS4, PCS7

PCT0, PCT1, PCT4, PCT5

PCM0 to PCM4

PCD0 to PCD3

PBD0, PBD1

P70 to P73

P40 to P45

P24

P20

P11, P12

P01 to P05

CG

System

controller

BCU

CLKOUT

CKSEL

X1

X2

CV

DD

CV

SS

MODE0 to MODE2

RESET

V

DD

V

SS

UART0/CSI0

UART1/CSI1

ADC

TXD0/SO0

RXD0/SI0

SCK0

TXD1/SO1

RXD1/SI1

SCK1

ANI0 to ANI3

AV

REF

/AV

DD

AV

SS

Instruction

queue

MEMC

HLDRQ

HLDAK

CS0, CS3, CS4, CS7

REFRQ

LBE/SDCAS

UBE/SDRAS

SDCLK

SDCKE

WE

RD

UWR/UDQM

LWR/LDQM

WAIT

A0 to A24

D0 to D15

SDRAMC

DMAC

ROMC

Prescaler

DMARQ0, DMARQ1

DMAAK0, DMAAK1

TC0

CHAPTER 1 OVERVIEW OF EACH PRODUCT

Application Note U17121EJ1V1AN

27

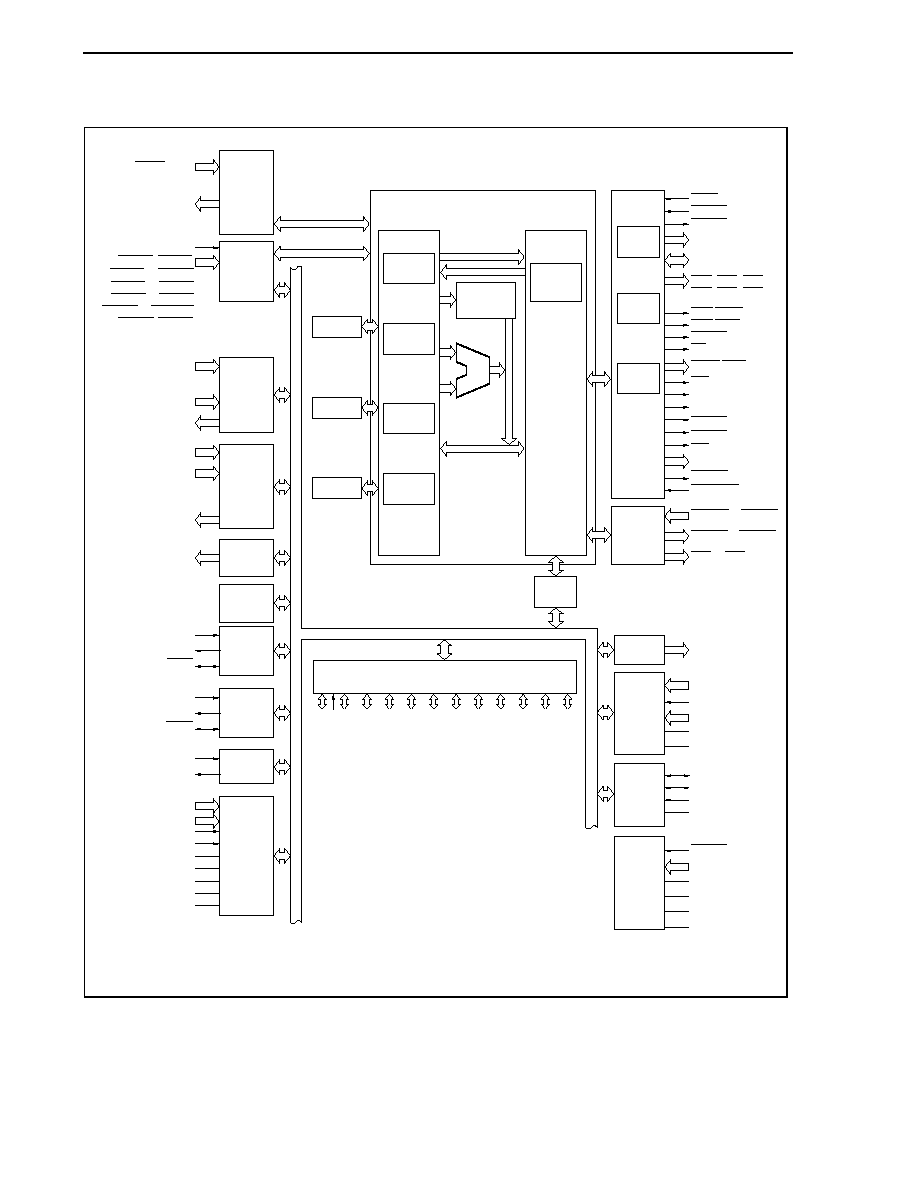

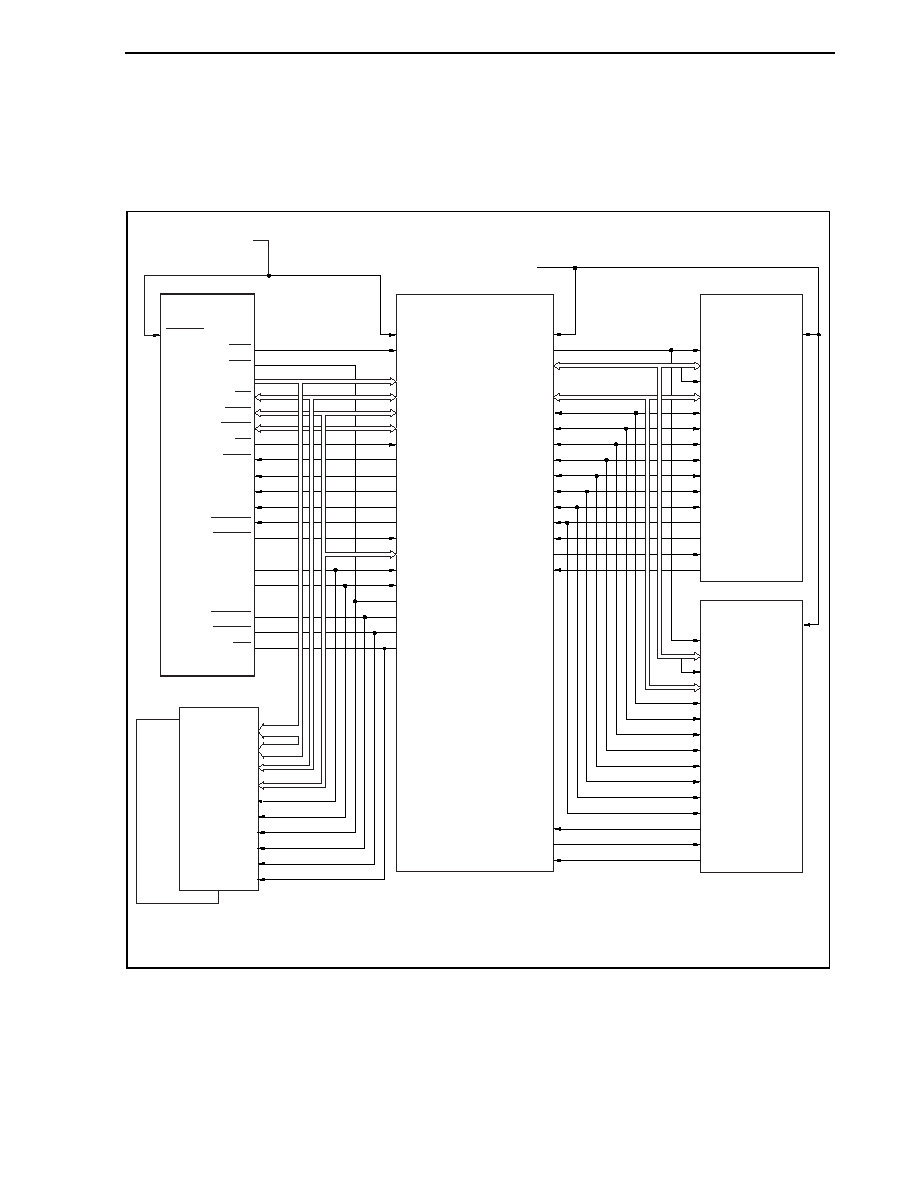

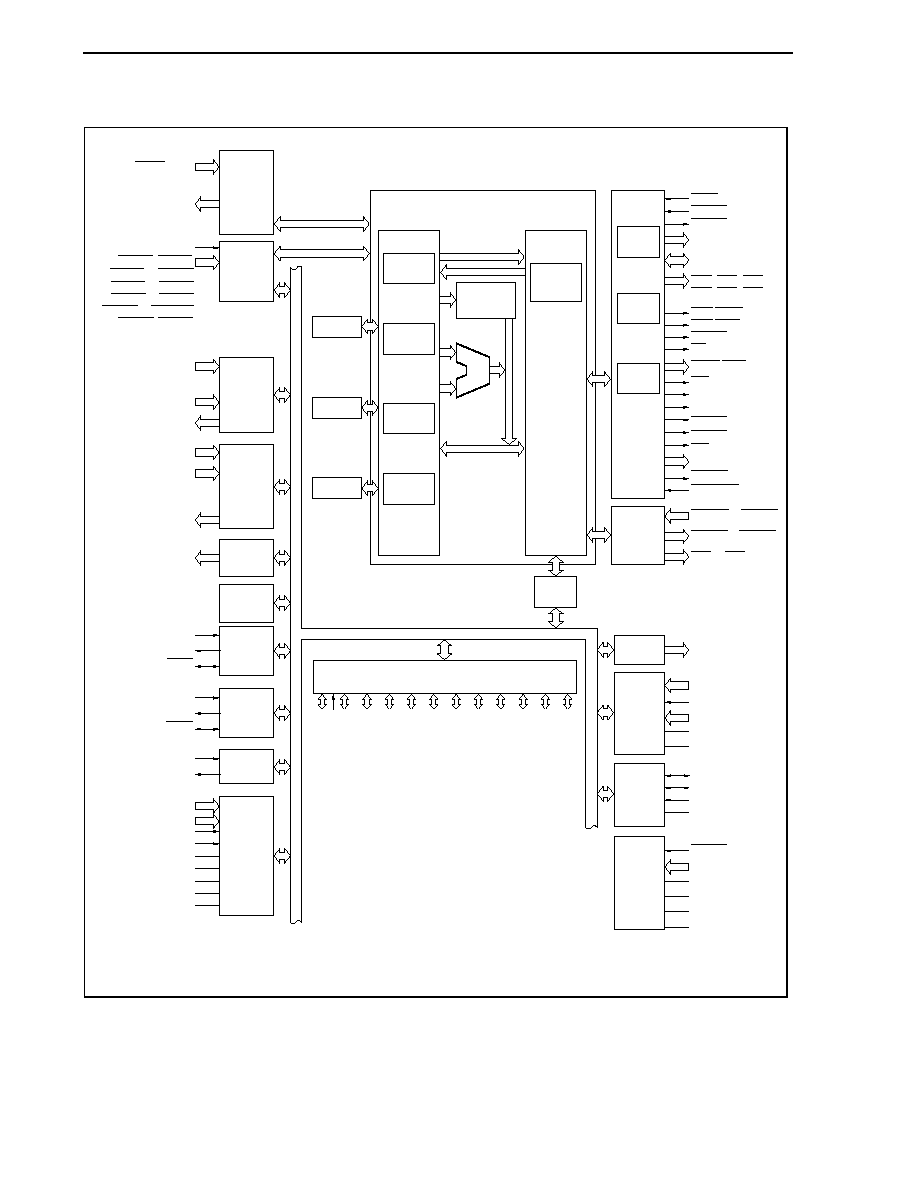

(3) V850E/MA3

NMI

TOQ0 to TOQ3,

TOQT1 to TOQT3,

TOQB1 to TOQB3

ANI0 to ANI7

ANO0, ANO1

TCLR10, TIUD10, TCUD10

INTP10, INTP11

TO10

INTP000, INTP001, INTP004, INTP005

INTP010 to INTP013, INTP114, INTP115

INTP021, INTP022, INTP124 to INTP126

INTP130 to INTP134, INTP137, INTP050,

INTP051, INTP106, INTP107

INTC

TMENC

�

1 ch

TMD

�

4 ch

TMQ0

�

1 ch

TMP

�

3 ch

UARTA0/CSIB0

UARTA1/CSIB1

ADC

�

8 ch

DAC

�

2 ch

ROM

RAM

Note 2

CPU

32-bit

barrel shifter

PC

System

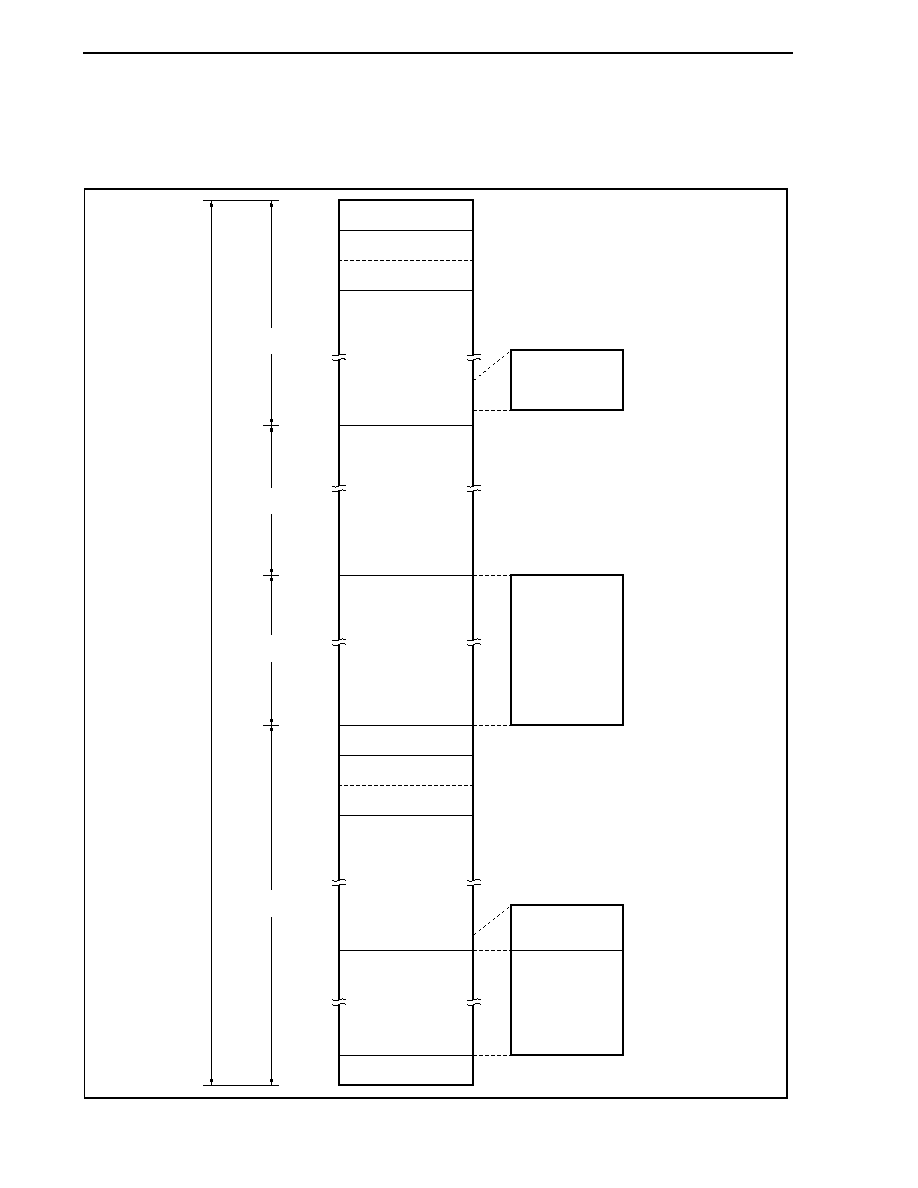

registers

General-

purpose

registers

(32 bits

�

32)

ALU

Multiplier

(32

�

32

64)

Ports

CG

DCU

System

controller

BCU

PSEL

CKSEL

X1

X2

CV

DD

CV

SS

RESET

MODE0, MODE1

V

DD

V

SS

EV

DD

EV

SS

TCK

TMS

TRST

TDO

TDI

TIQ, EVTQ, INTPQ0 to INTPQ3

EVTP0 to EVTP2, TIP0 to TIP2, INTPP00, INTPP01

INTPP10, INTPP11, INTPP20, INTPP21

TOP00, TOP01, TOP10,

TOP11, TOP20, TOP21

TXD2/SO2

RXD2/SI2

ASCK2/SCK2

UARTA2/CSIB2

ADTRG

TXD0/SO0

RXD0/SI0

ASCK0/SCK0

TXD1/SO1

RXD1/SI1

ASCK1/SCK1

AV

DD0

AV

SS

0

AV

DD1

AV

SS

1

Instruction

queue

MEMC

WAIT

HLDRQ

HLDAK

BUSCLK

A0 to A25

AD0 to AD15

CS0 to CS7

BCYST

RD

UWR, LWR/UBE, LBE

WR

ASTB

IORD

IOWR

SDCLK

SDCKE

SDRAS

SDCAS

WE

LDQM, UDQM

REFRQ

SRAM

ROM

DMAC

SDRAM

WDT

UARTA3/I

2

C

Note 3

TXD3/SDA

Note 3

RXD3/SCL

Note 3

DMARQ0 to DMARQ3

DMAAK0 to DMAAK3

TC0 to TC3

P00, P01, P04 to P07

P10 to P15

P20

P21, P22, P24 to P27

P30 to P34, P37

P40 to P45

P50, P51

P70 to P77

P80, P81

PAL0 to PAL15

PAH0 to PAH9

PDL0 to PDL15

PCS0 to PCS7

PCT0 to PCT7

PCM0 to PCM4

PCD0 to PCD3

PBD0 to PBD3

ROM

correction

Note 1

PLL

Notes 1.

�

PD703131A, 703131AY, 703132A, 703132AY: 256 KB (mask ROM)

�

PD703133A, 703133AY, 703134A, 703134AY: 512 KB (mask ROM)

�

PD70F3134A, 70F3134AY:

512 KB (flash memory)

2.

�

PD703131A, 703131AY, 703133A, 703133AY: 16 KB

�

PD703132A, 703132AY, 703134A, 703134AY,

70F3134A, 70F3134AY:

32 KB

3. Available only in the

�

PD703131AY, 703132AY, 703133AY, 703134AY, 703137AY, and 70F3134AY.

CHAPTER 1 OVERVIEW OF EACH PRODUCT

Application Note U17121EJ1V1AN

28

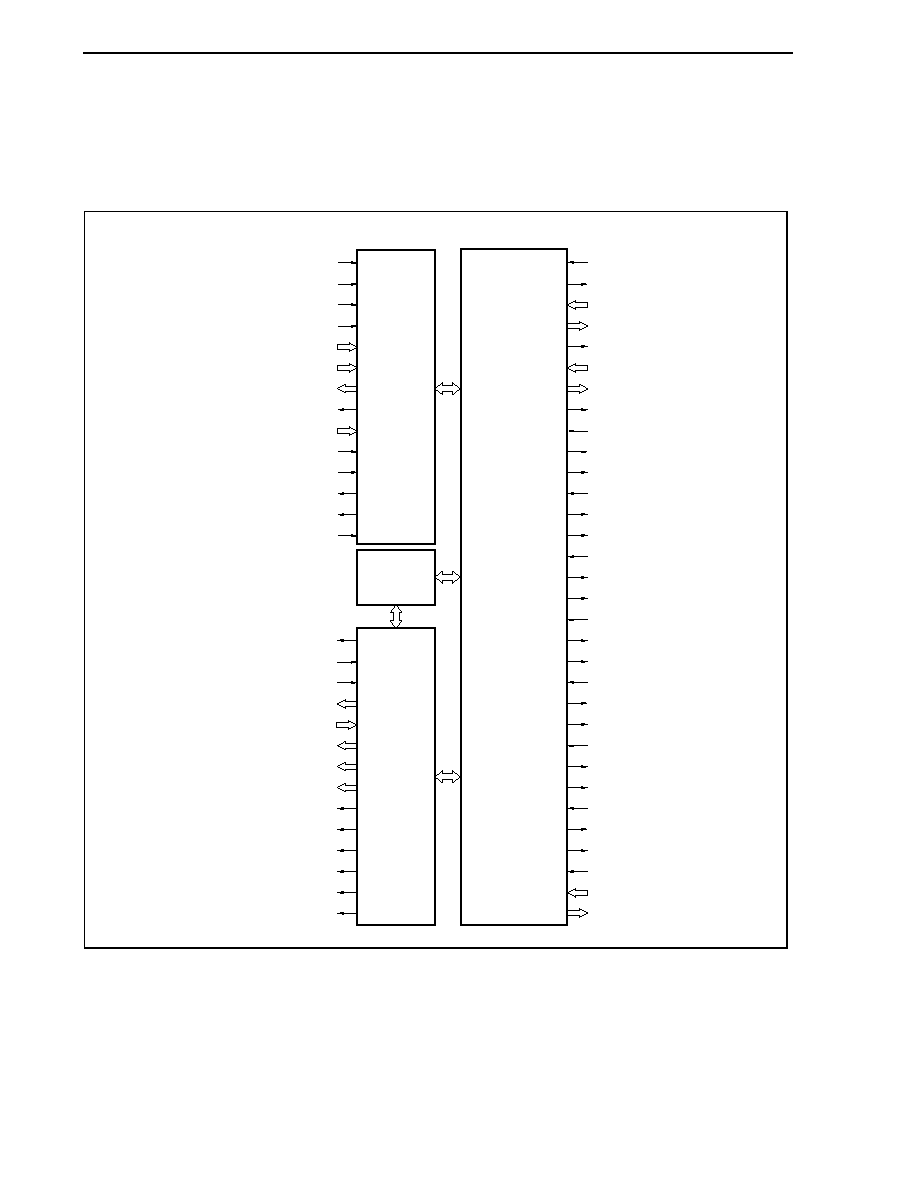

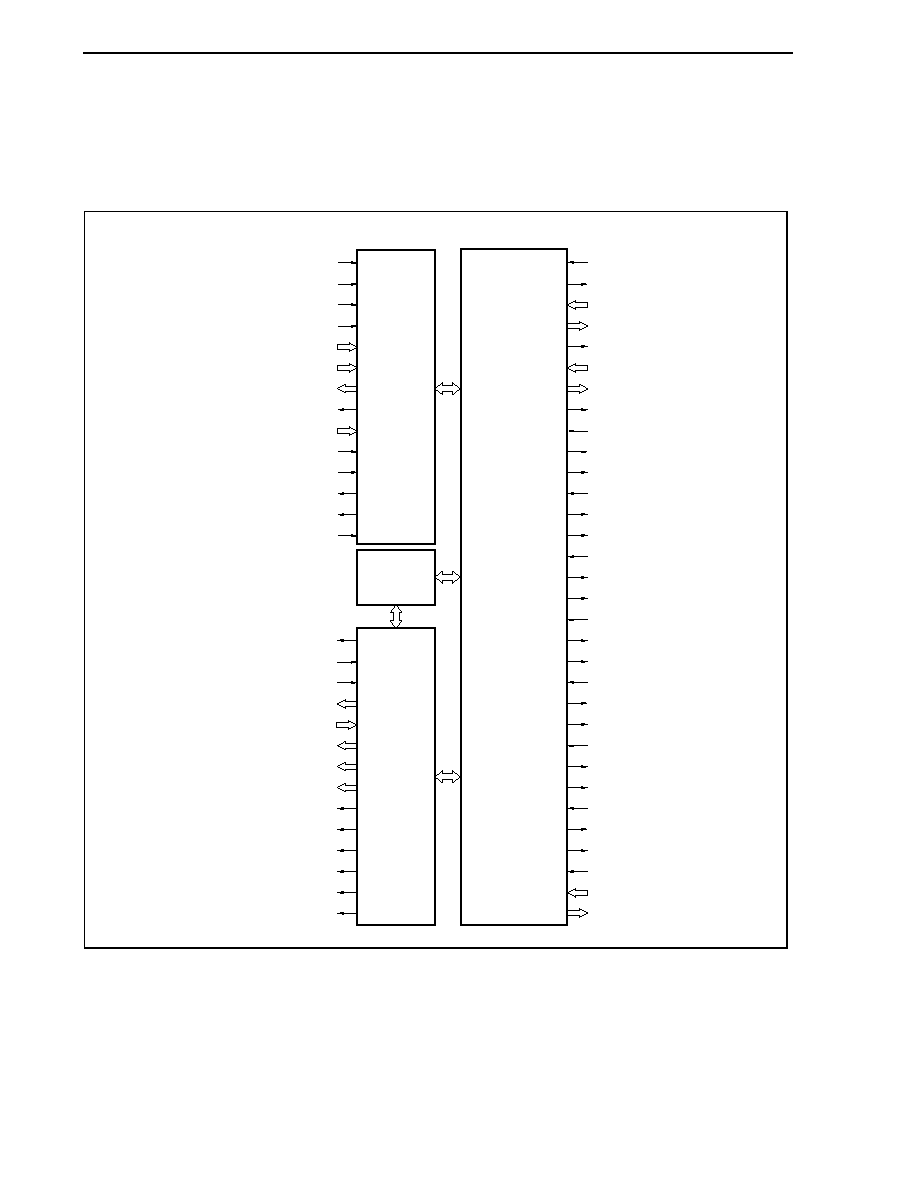

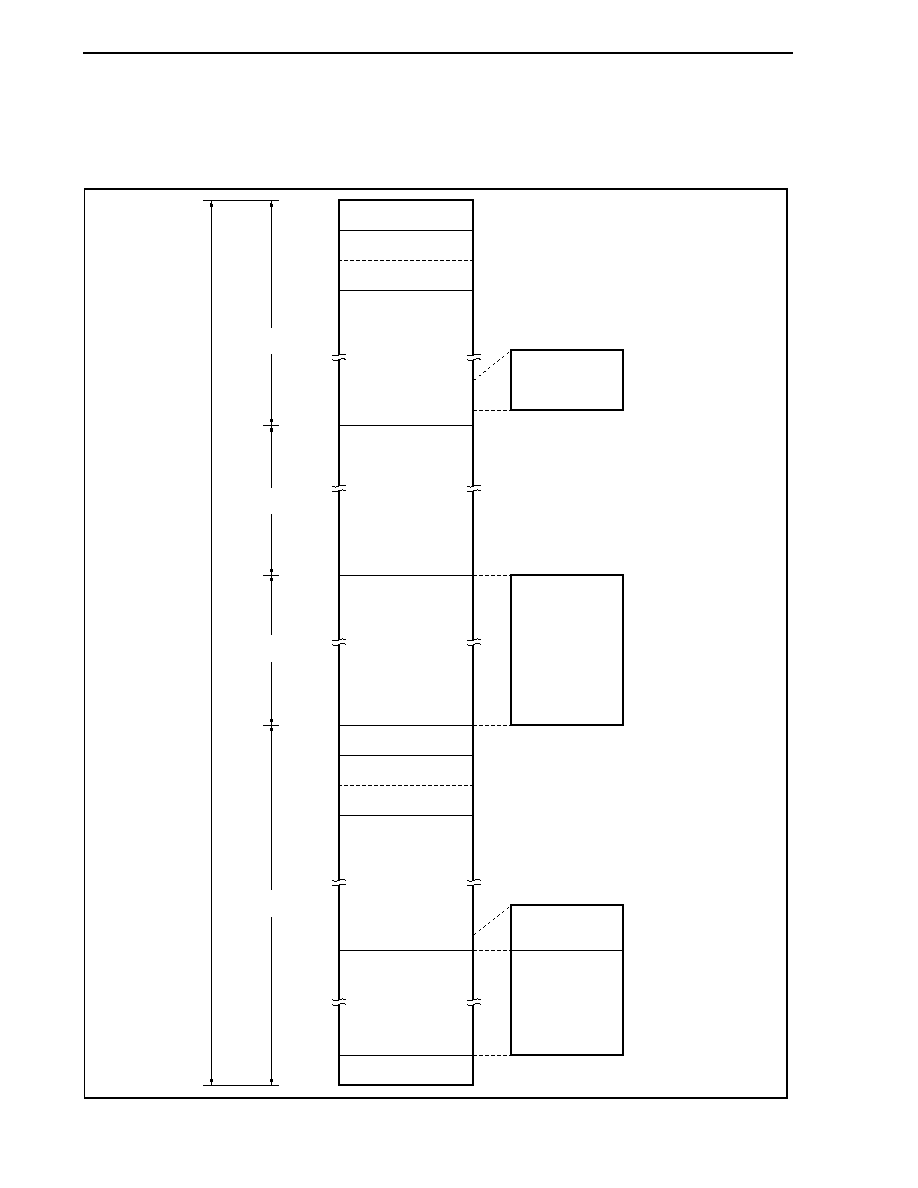

(4) V850E/ME2

CPU

32-bit

barrel shifter

PC

System

registers

General-

purpose

registers

(32 bits

�

32)

ALU

Multiplier

(32

�

32

64)

Ports

P10 to P13

P20

P21 to P25

P50 to P55

P65 to P67

P72 to P77

PAL0, PAL1

PAH0 to PAH9

PCD0 to PCD3

PCM0 to PCM5

PCS0 to PCS7

PCT0 to PCT5, PCT7

PDH0 to PDH15

ADC

USBF

PWM

System

controller

BCU

Instruction

queue

MEMC

SRAM

ROM

SDRAM

DMA

SI0/RXD0

SO0/TXD0

SCK0

TOC4, TOC5

TOC0 to TOC3

TIC0 to TIC3

TO10, TO11

NMI

DRST, DCK,

DMS, DDI,

WAIT

HLDRQ

HLDAK

A0 to A25

D0 to D31

DMARQ0 to DMARQ3

DMAAK0 to DMAAK3

TC0 to TC3

CS0, CS1, CS3,

CS4, CS6, CS7

CS2/IOWR

CS5/IORD

BCYST

RD

ANI0 to ANI7

ADTRG

AV

REFP

, AV

REFM

AV

DD

AV

SS

RESET

MODE0, MODE1

IV

DD

IV

SS

EV

DD

EV

SS

PWM0, PWM1

UDP

UDM

UCLK

UV

DD

xxWR/xxBE

WR

BUSCLK

SDCKE

SDRAS

SDCAS

WE

xxDQM

REFRQ

SELFREF

DDO, TRCCLK,

TRCDATA0 to TRCDATA3,

TRCEND

INTP100, INTP110

INTP101, INTP111

INTP10, INTP11

INTP21 to INTP25

INTP50 to INTP52

INTP65 to INTP67

INTPD0 to INTPD15

INTPL0, INTPL1

TCLR10, TCLR11

TIUD10, TIUD11

TCUD10, TCUD11

INTPC00, INTPC01,

INTPC10, INTPC11,

INTPC20, INTPC21,

INTPC30, INTPC31

SI1

SO1

SCK1

RXD1

TXD1

SSEL0, SSEL1

JIT0, JIT1

PLLSEL

X1

X2

OSCV

DD

OSCV

SS

PLLV

DD

PLLV

SS

TMC

TMC