Document Outline

- COVER

- FEATURES

- ORDERING INFORMATION

- BLOCK DIAGRAM

- PIN CONFIGURATION (TOP VIEW)

- 1. PIN INFORMATION

- 2. ELECTRICAL SPECIFICATIONS

- 2.1 Buffer List

- 2.2 Terminology

- 2.3 Electrical Specifications

- 3. PACKAGE DRAWING

- 4. RECOMMENDED SOLDERING CONDITIONS

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all products and/or types are available in every country. Please check with an NEC Electronics

sales representative for availability and additional information.

MOS INTEGRATED CIRCUIT

µ

PD720110A

USB2.0 HUB CONTROLLER

Document No. S15737EJ5V0DS00 (5th edition)

Date Published August 2004 NS CP (N)

Printed in Japan

DATA SHEET

NEC Electronics Corporation 2004

The

µ

PD720110A is an USB 2.0 hub device that comply with the Universal Serial Bus (USB) Specification Revision

2.0 and work up to 480 Mbps. USB2.0 compliant transceivers are integrated for upstream and all downstream ports.

The

µ

PD720110A works backward compatible either when any one of downstream ports is connected to an USB 1.1

compliant device, or when the upstream port is connected to a USB 1.1 compliant host.

Detailed function descriptions are provided in the following user's manual. Be sure to read the manual before designing.

µ

PD720110A User's Manual: S15738E

FEATURES

∑ Compliant with Universal Serial Bus Specification Revision 2.0 (Data Rate 1.5/12/480 Mbps)

∑ Certified by USB implementers forum and granted with USB 2.0 high-Speed Logo

∑ High-speed or full-speed packet protocol sequencer for Endpoint 0/1

∑ 4 (Max.) downstream facing ports

∑ All downstream facing ports can handle high-speed (480 Mbps), full-speed (12 Mbps), and low-speed (1.5 Mbps)

transaction.

∑ Supports split transaction to handle full-speed and low-speed transaction at downstream facing ports when Hub

controller is working at high-speed mode.

∑ One Transaction Translator per Hub and supports 4 non-periodic buffers

∑ Supports self-powered mode only

∑ Supports Over-current detection and Individual power control

∑ Supports configurable vendor ID and product ID with external Serial ROM

∑ Supports "non-removable" attribution on individual port

∑ Uses 30 MHz X'tal, 30 MHz clock input, or 48 MHz clock input

∑ Supports downstream port status with LED

∑ HS detection indicator output

∑ 3.3 V power supply

Data Sheet S15737EJ5V0DS

2

µ

PD720110A

ORDERING INFORMATION

Part Number

Package

µ

PD720110AGC-8EA

100-pin plastic LQFP (Fine pitch) (14

◊ 14)

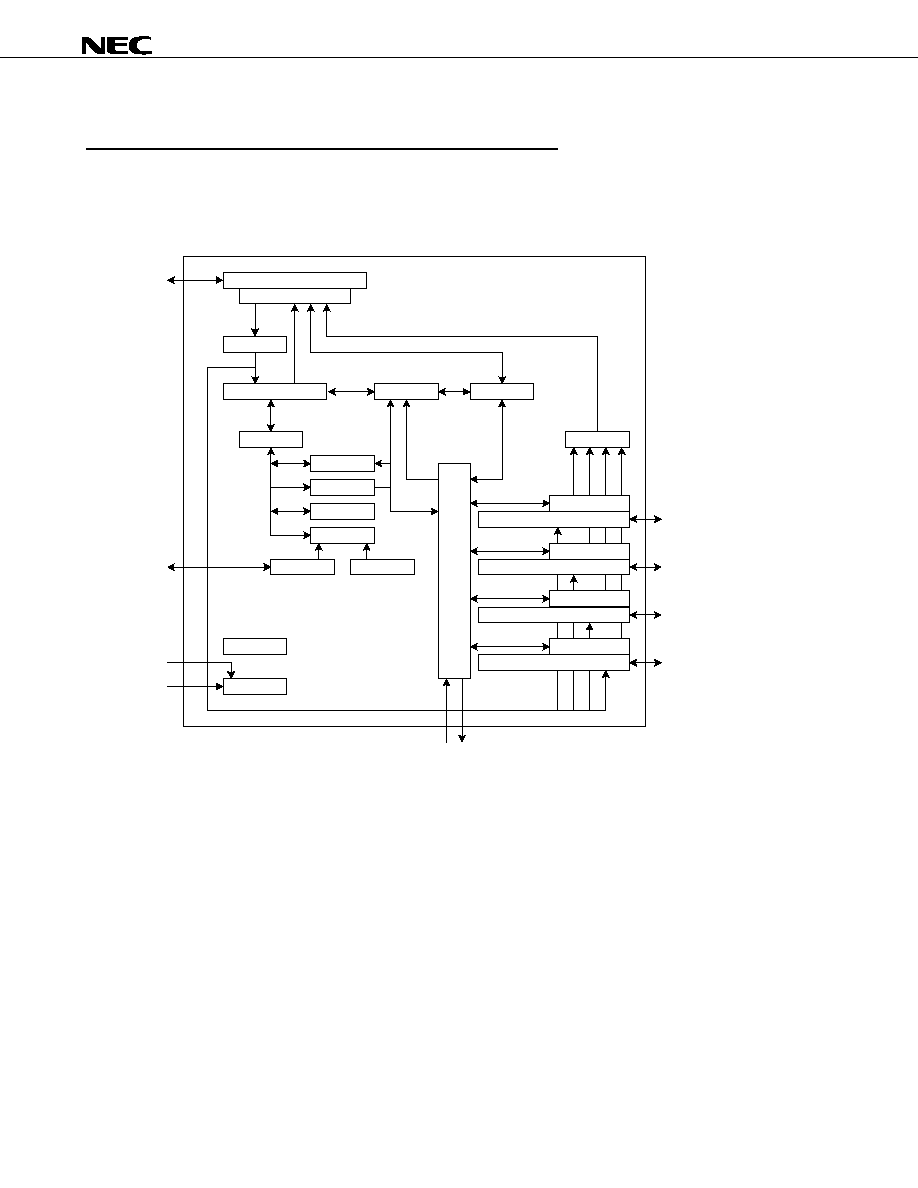

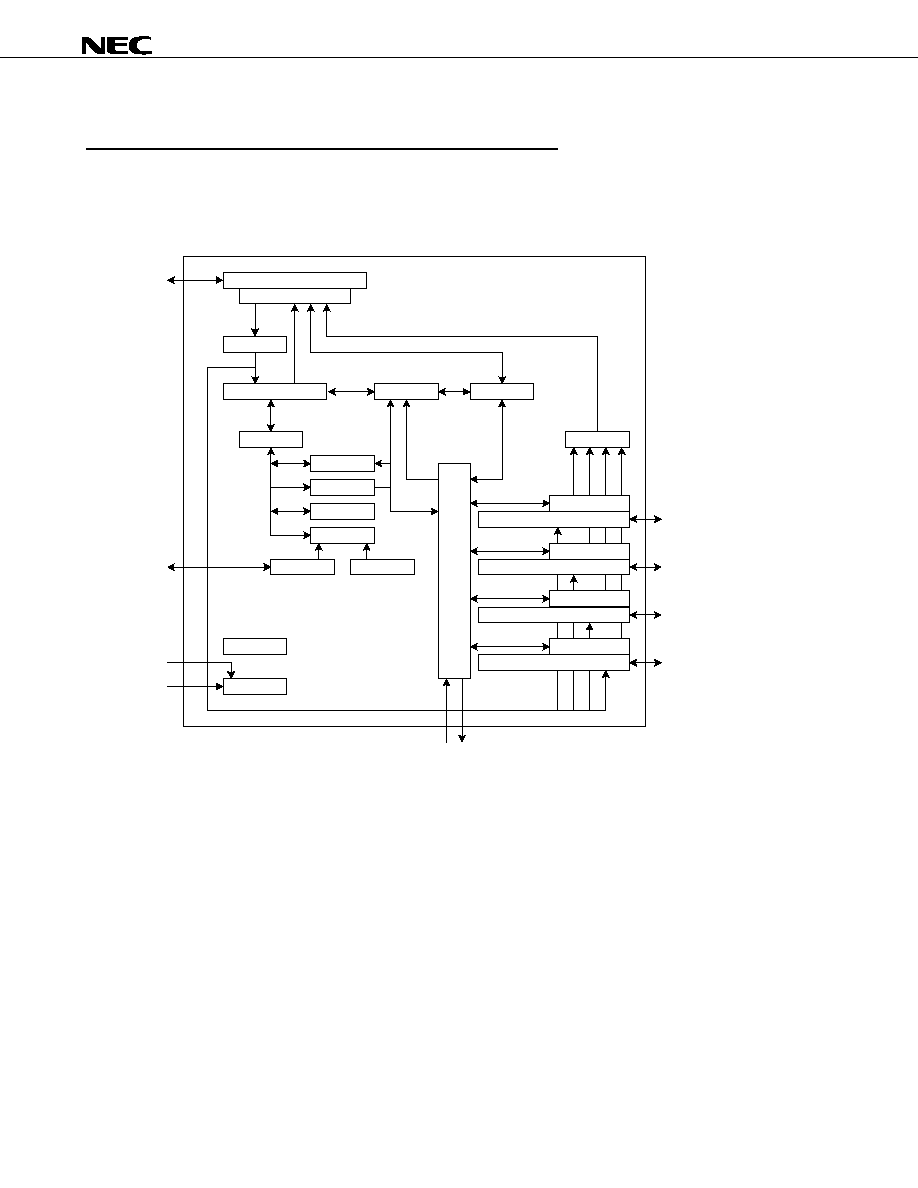

BLOCK DIAGRAM

Upstream facing port

UP_PHY

Downstream facing port #1

SERDES

SIE_2H

CDR

APLL

OSB

UPC

ROM

ROM I/F

ALL_TT

F_TIM

EP1

EP0

DP(1)_PHY

Downstream facing port #2

DP(2)_PHY

Downstream facing port #3

DP(3)_PHY

Downstream facing port #4

DP(4)_PHY

DPC

FS_REP

To Host/Hub

downstream

facing port

X1_CLK/X2

CLKSEL

PPB(4:1)

CSB(4:1)

To Hub/Function

upstream facing port

To Hub/Function

upstream facing port

To Hub/Function

upstream facing port

upstream facing port

To Hub/Function

External

Serial ROM

CDR

Data Sheet S15737EJ5V0DS

3

µ

PD720110A

APLL

: Generates all clocks of Hub.

ALL_TT

: Translates the high-speed transactions (split transactions) for full/low-speed device

to full/low-speed transactions. ALL_TT buffers the data transfer from either

upstream or downstream direction. For OUT transaction, ALL_TT buffers data from

upstream port and sends it out to the downstream facing ports after speed

conversion from high-speed to full/low-speed. For IN transaction, ALL_TT buffers

data from downstream ports and sends it out to the upstream facing ports after

speed conversion from full/low-speed to high-speed.

CDR

: Data & clock recovery circuit

DPC

: Downstream Port Controller handles Port Reset, Enable, Disable, Suspend and

Resume

DP(n)_PHY

: Downstream transceiver supports high-speed (480 Mbps), full-speed (12 Mbps), and

low-speed (1.5 Mbps) transaction

EP0

: Endpoint 0 controller

EP1

: Endpoint 1 controller

F_TIM (Frame Timer)

: Manages hub's synchronization by using micro-SOF which is received at upstream

port, and generates SOF packet when full/low-speed device is attached to

downstream facing port.

FS_REP

: Full/low-speed repeater is enabled when the

µ

PD720110A is worked at full-speed

mode

OSB :

Oscillator

Block

ROM

: Contains default Descriptors

ROM I/F

: Interface block for external Serial ROM which contains user-defined Descriptors

SERDES :

Serializer

and

Deserializer

SIE_2H

: Serial Interface Engine (SIE) controls USB2.0 and 1.1 protocol sequencer

UP_PHY

: Upstream Transceiver supports high-speed (480 Mbps), full-speed (12 Mbps)

transaction

UPC

: Upstream Port Controller handles Suspend and Resume

Data Sheet S15737EJ5V0DS

4

µ

PD720110A

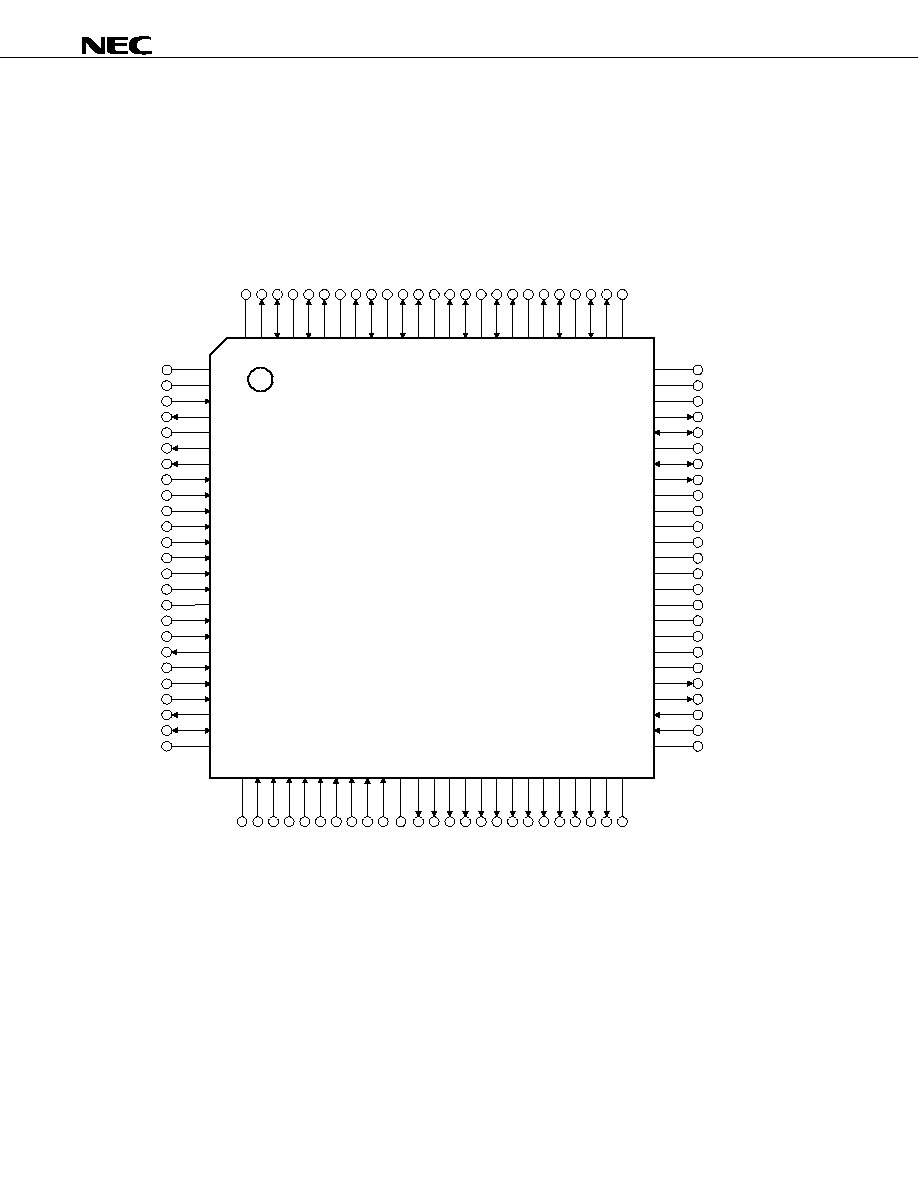

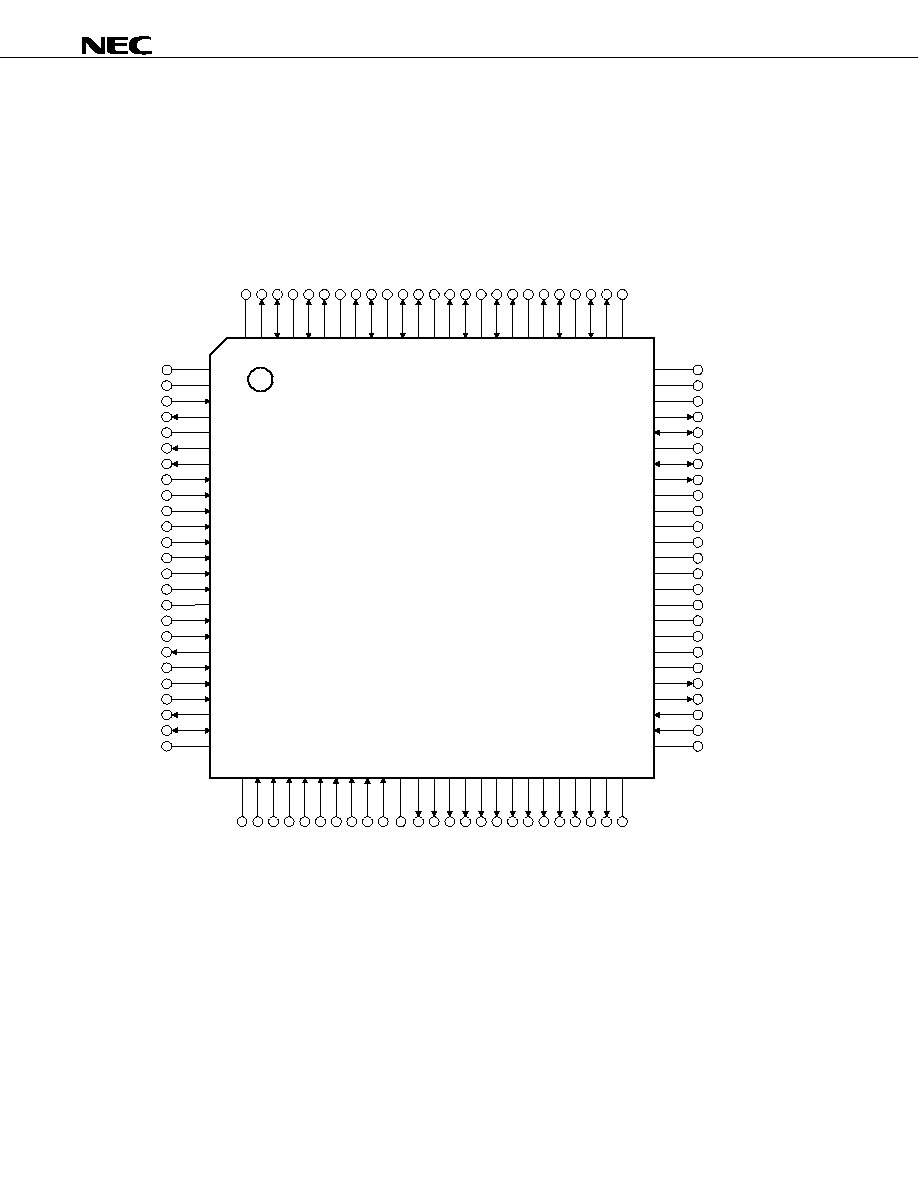

PIN CONFIGURATION (TOP VIEW)

∑ 100-pin plastic LQFP (Fine pitch) (14 ◊ 14)

µ

PD720110AGC-8EA

1

5

10

15

20

25

35

30

26

40

50

45

55

60

65

70

51

75

76

80

85

90

95

100

V

DD

V

SS

X1_CLK

X2

V

DD

PLLLOCK

OSL

TS1

CLKSEL

TS2

TS3

TS4

TS5

TS6

SYSRSTB

V

SS

TS7

TS8

TSO

SMD

TS9

TS10

SCL

SDA

V

DD

V

SS

GREENBP4

AMBERBP4

GREENBP3

AMBERBP3

GREENBP2

AMBERBP2

GREENBP1

AMBERBP1

HSMODE

PPB4

PPB3

PPB2

PPB1

V

SS

CSB4

CSB3

CSB2

CSB1

PORTRMV2

PORTRMV1

VBUSM

NUMPORT

PWMODE

V

SS

V

DD

RPU

V

SS

RSDPU

DPU

V

DD

DMU

RSDMU

V

SS

PC1

AV

SS

PC2

AV

DD

AV

SS

V

SS

N.C.

RREF

AV

SS

AV

DD

AV

SS

CLK30MO

EPERR

PORTRMV4

PORTRMV3

V

DD

V

SS

RSDMD1

DMD1

V

DD

DPD1

RSDPD1

V

SS

RSDMD2

DMD2

V

DD

DPD2

RSDPD2

V

SS

RSDMD3

DMD3

V

DD

DPD3

RSDPD3

V

SS

RSDMD4

DMD4

V

DD

DPD4

RSDPD4

V

SS

Data Sheet S15737EJ5V0DS

5

µ

PD720110A

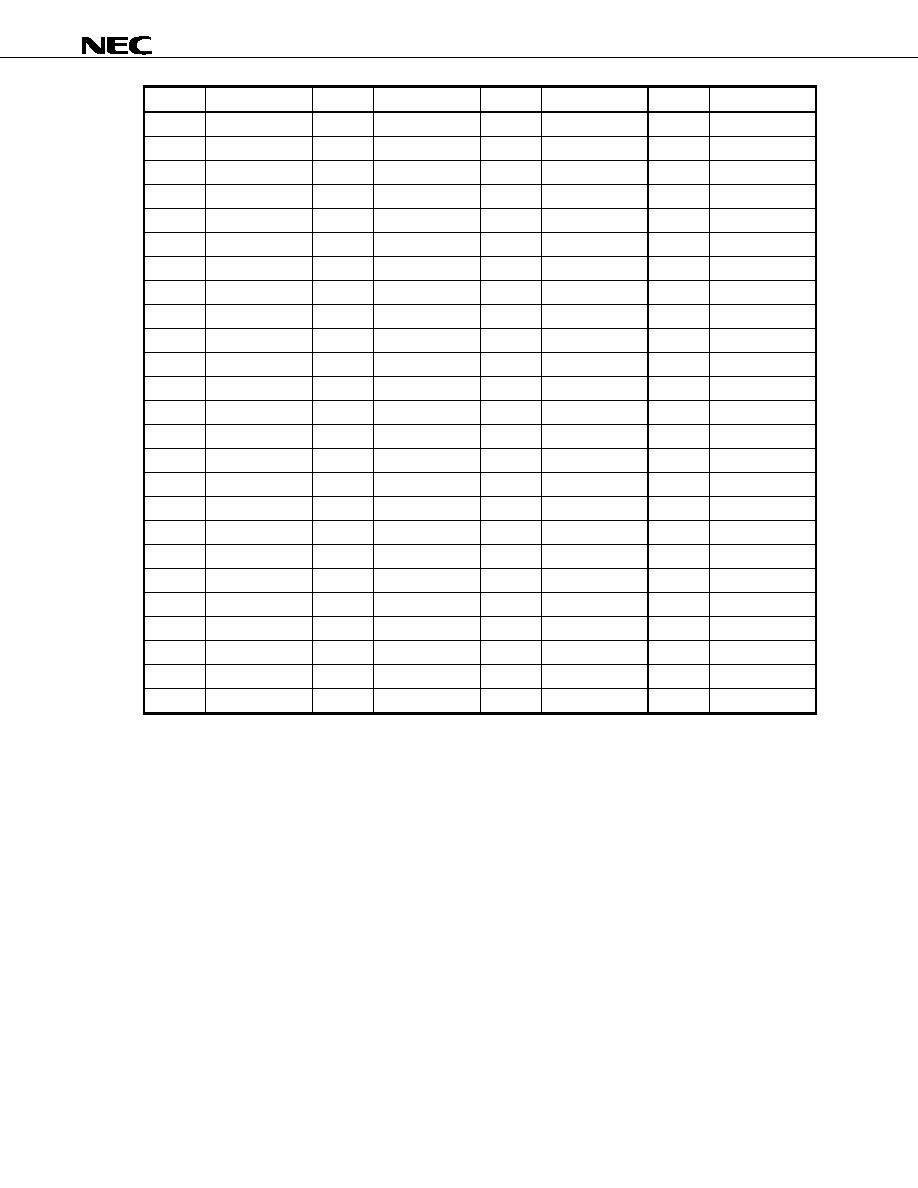

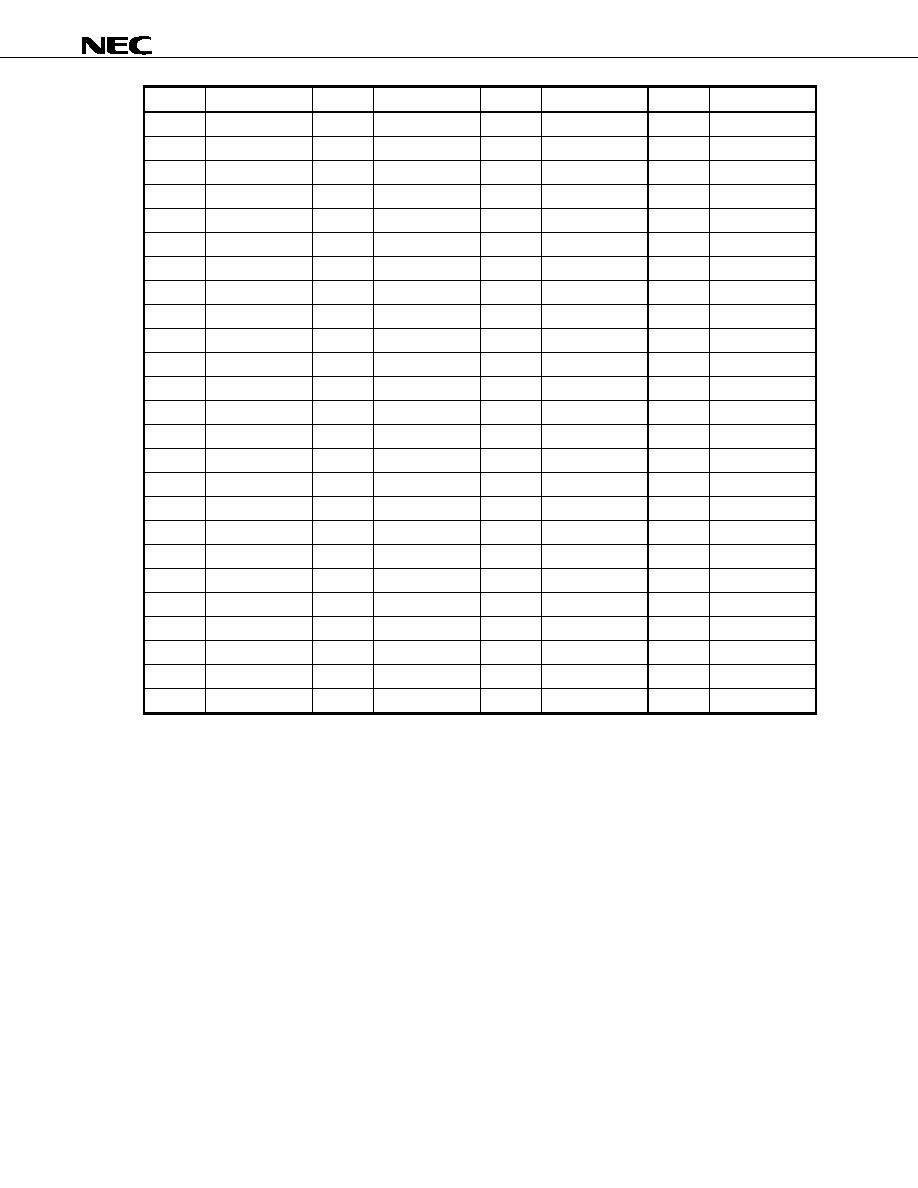

Pin No.

Pin Name

Pin No.

Pin Name

Pin No.

Pin Name

Pin No.

Pin Name

1 V

DD

26

V

SS

51

V

DD

76

V

SS

2 V

SS

27 PWMODE 52 PORTRMV3

77 RSDMD1

3 X1_CLK

28 NUMPORT 53 PORTRMV4

78 DMD1

4 X2

29 VBUSM

54 EPERR

79 V

DD

5 V

DD

30 PORTRMV1

55 CLK30MO 80 DPD1

6 PLLLOCK 31 PORTRMV2

56 AV

SS

81

RSDPD1

7 OSL

32 CSB1

57 AV

DD

82

V

SS

8 TS1

33 CSB2

58 AV

SS

83

RSDMD2

9 CLKSEL 34 CSB3

59 RREF

84 DMD2

10 TS2

35 CSB4

60 N.C.

85 V

DD

11 TS3

36 V

SS

61

V

SS

86

DPD2

12 TS4

37 PPB1

62 AV

SS

87

RSDPD2

13 TS5

38 PPB2

63 AV

DD

88

V

SS

14 TS6

39 PPB3

64 PC2

89 RSDMD3

15 SYSRSTB 40 PPB4

65 AV

SS

90

DMD3

16 V

SS

41 HSMODE 66 PC1

91 V

DD

17 TS7

42 AMBERBP1

67 V

SS

92

DPD3

18 TS8

43 GREENBP1

68 RSDMU

93 RSDPD3

19 TSO

44 AMBERBP2

69 DMU

94 V

SS

20 SMD

45 GREENBP2

70 V

DD

95

RSDMD4

21 TS9

46 AMBERBP3

71 DPU

96 DMD4

22 TS10

47 GREENBP3

72 RSDPU

97 V

DD

23 SCL

48 AMBERBP4

73 V

SS

98

DPD4

24 SDA

49 GREENBP4

74 RPU

99 RSDPD4

25 V

DD

50

V

SS

75

V

DD

100

V

SS