Document Outline

- COVER

- DESCRIPTION

- FEATURES

- APPLICATION EXAMPLES

- ORDERING INFORMATION

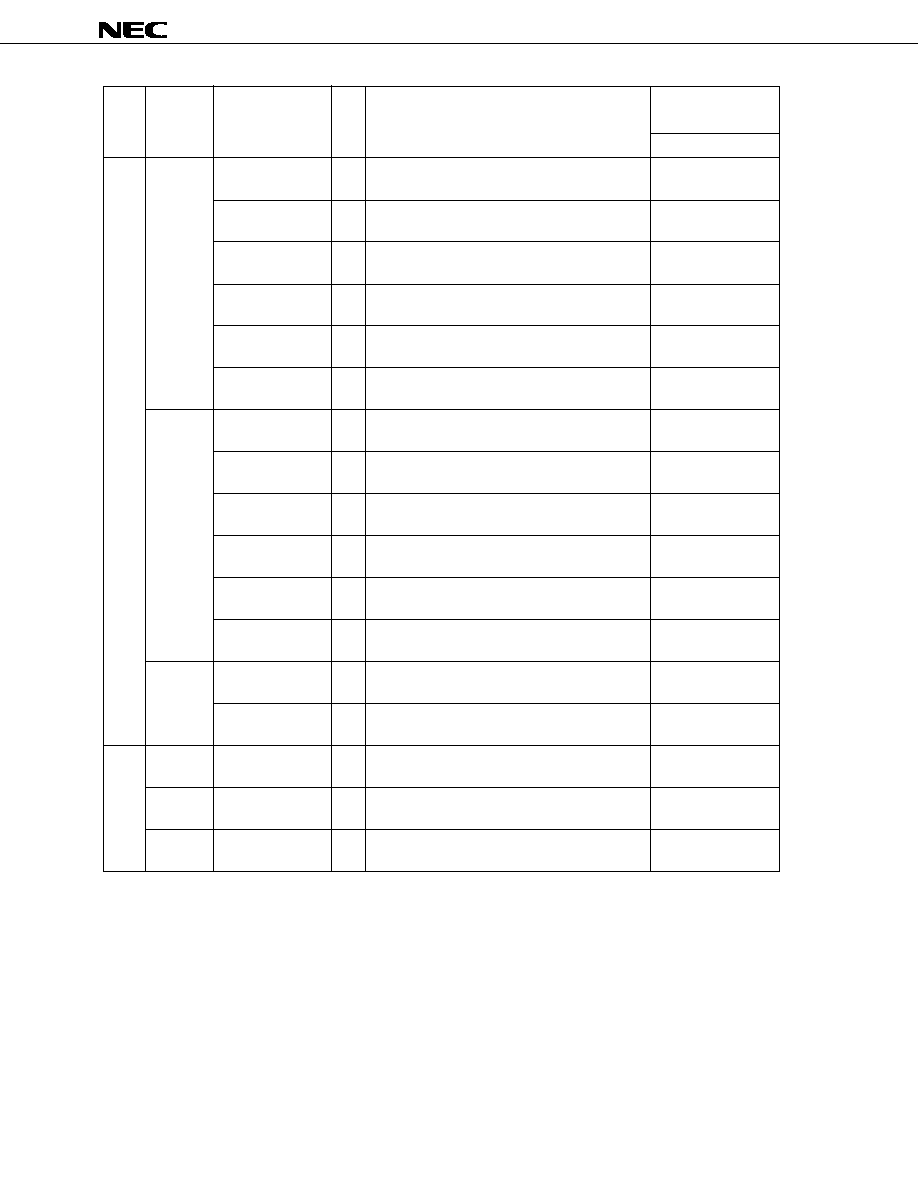

- 78K/III Series Product Development

- PIN CONFIGURATION (TOP VIEW)

- FUNCTIONAL OUTLINE

- DIFFERENCES BETWEEN uPD78362A AND uPD78366A

- BLOCK DIAGRAM

- 1. PIN FUNCTIONS

- 1.1 PORT PINS

- 1.2 PINS OTHER THAN PORT PINS

- 1.3 PIN I/O CIRCUITS AND PROCESSING OF UNUSED PINS

- 2. CPU ARCHITECTURE

- 2.1 MEMORY SPACE

- 2.2 DATA MEMORY ADDRESSING

- 2.3 PROCESSOR REGISTERS

- 2.3.1 Control Registers

- 2.3.2 General-Purpose Registers

- 2.3.3 Special Function Registers (SFR)

- 3. FUNCTIONAL BLOCKS

- 3.1 EXECUTION UNIT (EXU)

- 3.2 BUS CONTROL UNIT (BCU)

- 3.3 ROM/RAM

- 3.4 PORT FUNCTIONS

- 3.5 CLOCK GENERATOR CIRCUIT

- 3.6 REAL-TIME PULSE UNIT (RPU)

- 3.7 REAL-TIME OUTPUT PORT (RTP)

- 3.8 A/D CONVERTER

- 3.9 SERIAL INTERFACE

- 3.10 PWM UNIT

- 3.11 WATCHDOG TIMER (WDT)

- 4. INTERRUPT FUNCTIONS

- 4.1 OUTLINE

- 4.2 MACRO SERVICE

- 4.3 CONTEXT SWITCHING

- 4.3.1 Context Switching Function by Interrupt Request

- 4.3.2 Context Switching Function by BRKCS Instruction

- 4.3.3 Restoration from Context Switching

- 5. STANDBY FUNCTIONS

- 6. RESET FUNCTION

- 7. INSTRUCTION SET

- 8. EXAMPLE OF SYSTEM CONFIGURATION

- 9. ELECTRICAL SPECIFICATIONS

- 10. PACKAGE DRAWING

- 11. RECOMMENDED SOLDERING CONDITIONS

- APPENDIX A. DIFFERENCES BETWEEN uPD78362A AND uPD78328

- APPENDIX B. TOOLS

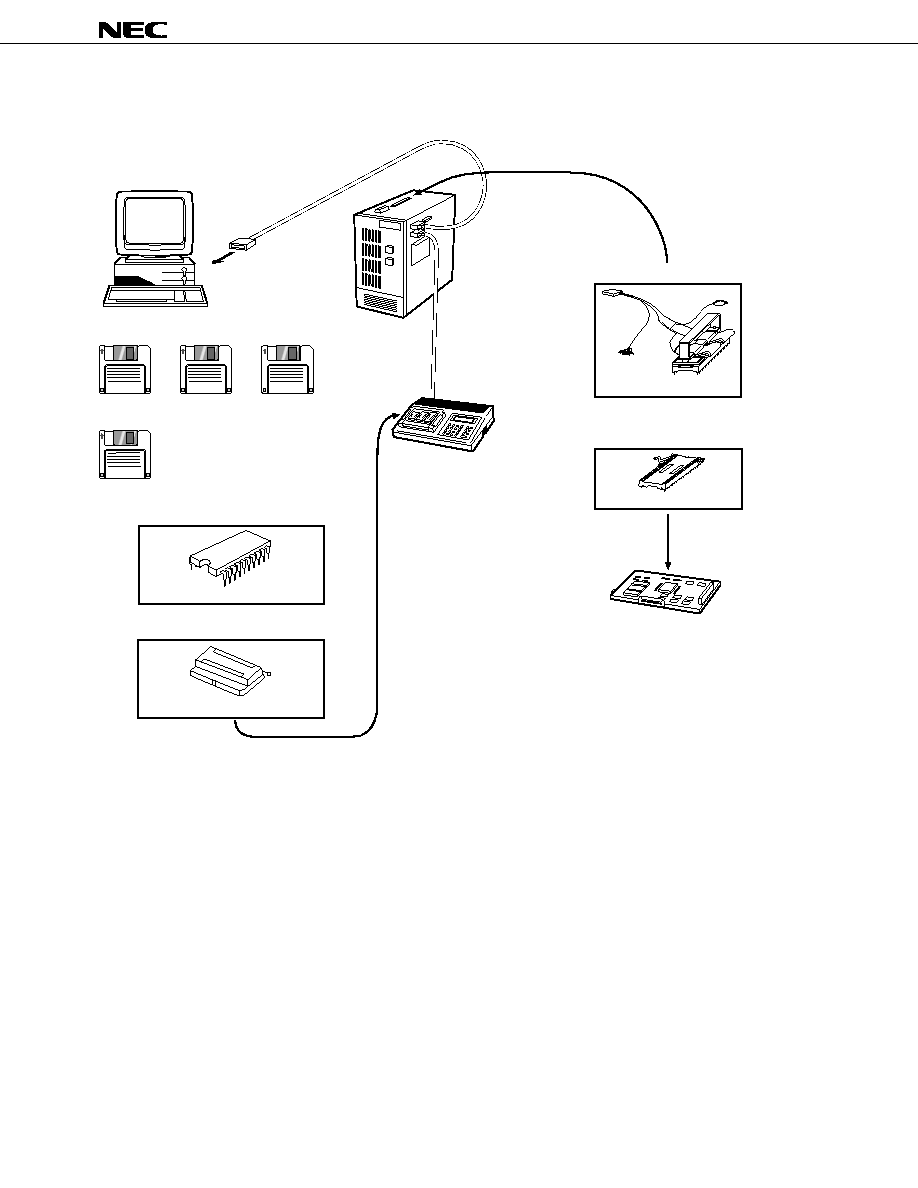

- B.1 DEVELOPMENT TOOLS

- B.2 EMBEDDED SOFTWARE

MOS INTEGRATED CIRCUIT

µ

PD78361A, 78362A

16/8-BIT SINGLE-CHIP MICROCONTROLLER

DESCRIPTION

µ

PD78362A is provided with a high-speed, high-performance CPU and powerful operation functions. Unlike the

existing

µ

PD78328,

µ

PD78362A is also provided with a high-resolution PWM signal output function which

substantially contributes to improving the performance of the inverter control.

A PROM model,

µ

PD78P364A, is also available.

Detailed functions, etc. are described in the following user's manual. Be sure to read the manual to design

systems.

µ

PD78362A User's Manual Hardware : U10745E

µ

PD78356 User's Manual Instruction

: U12117E

FEATURES

∑

Internal 16-bit architecture, external 8-bit data bus

∑

High-speed processing by pipeline control method and high- speed operating clock

Minimum instruction execution time: 125 ns (internal clock: at 16 MHz, external clock: 8MHz)

∑

Real-time pulse unit for inverter control

∑

10-bit resolution A/D converter: 8 channels

∑

8-/9-/10-/12-bit resolution variable PWM signal output function: 2 channels

∑

Powerful serial interface: 2 channels

∑

Internal memory : ROM

32K bytes (

µ

PD78361A)

24K bytes (

µ

PD78362A)

RAM

2K bytes

(

µ

PD78361A)

768 bytes (

µ

PD78362A)

APPLICATION EXAMPLES

∑

Inverter air conditioner

∑

Factory automation fields, such as industrial robots and machine tools.

ORDERING INFORMATION

Part Number

Package

Internal ROM

µ

PD78361ACW-

◊◊◊

64-pin plastic shrink DIP (750 mil)

Mask ROM

µ

PD78362ACW-

◊◊◊

64-pin plastic shrink DIP (750 mil)

Mask ROM

Remark

◊◊◊

indicates a ROM code suffix.

Unless otherwise specified, the

µ

PD78362A is treated as the representative model throughout this document.

The mark

shows major revised points.

Document No. U10098EJ2V0DS00 (2nd edition)

Date Published August 1997 N

Printed in Japan

©

1996

DATA SHEET

The information in this document is subject to change without notice.

2

µ

PD78361A, 78362A

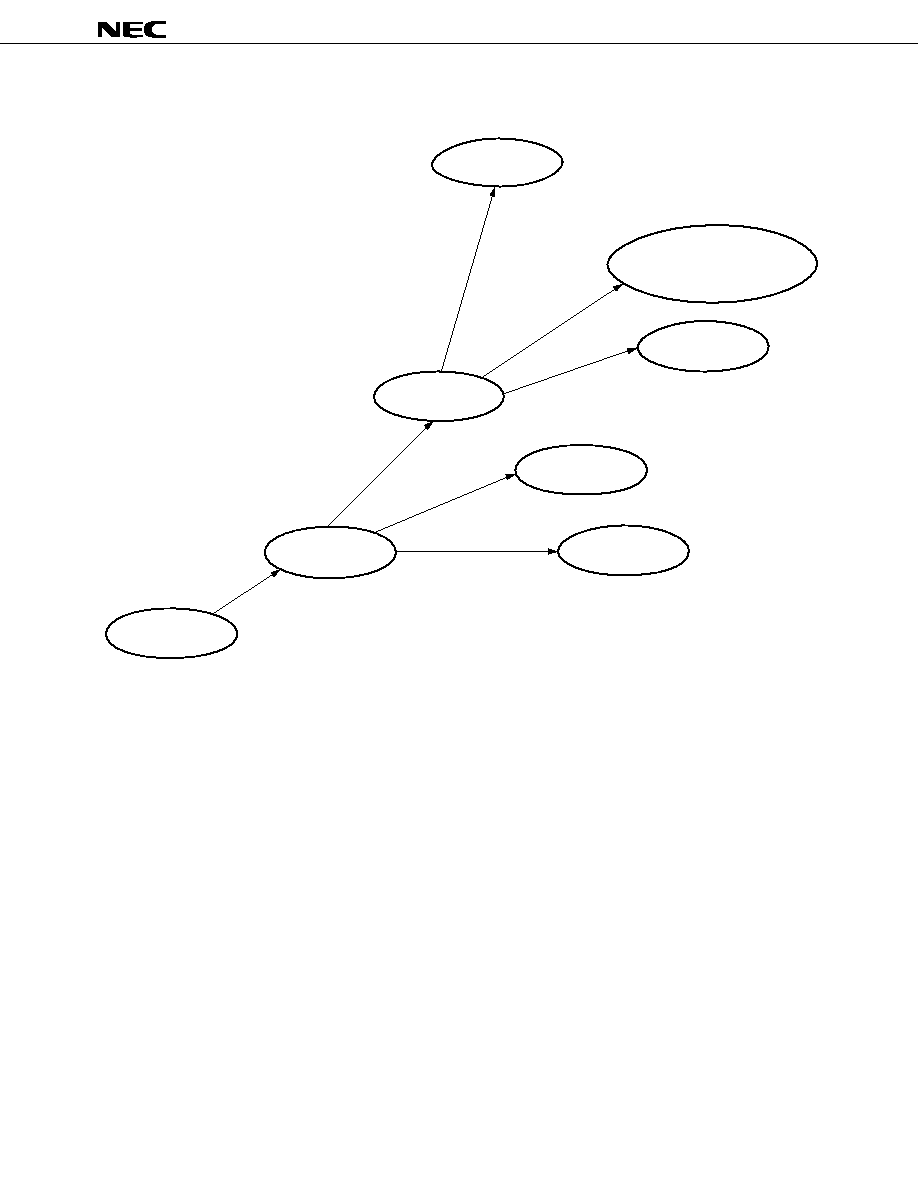

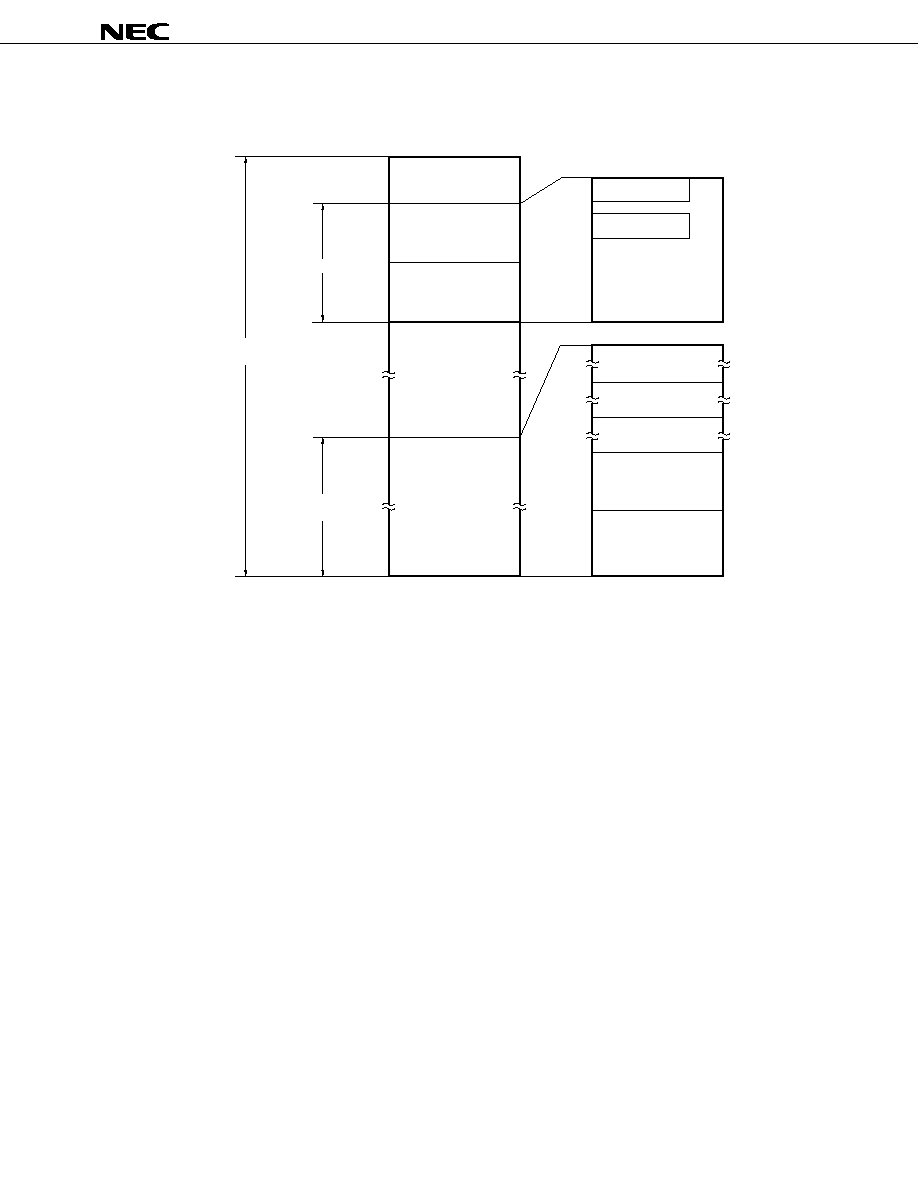

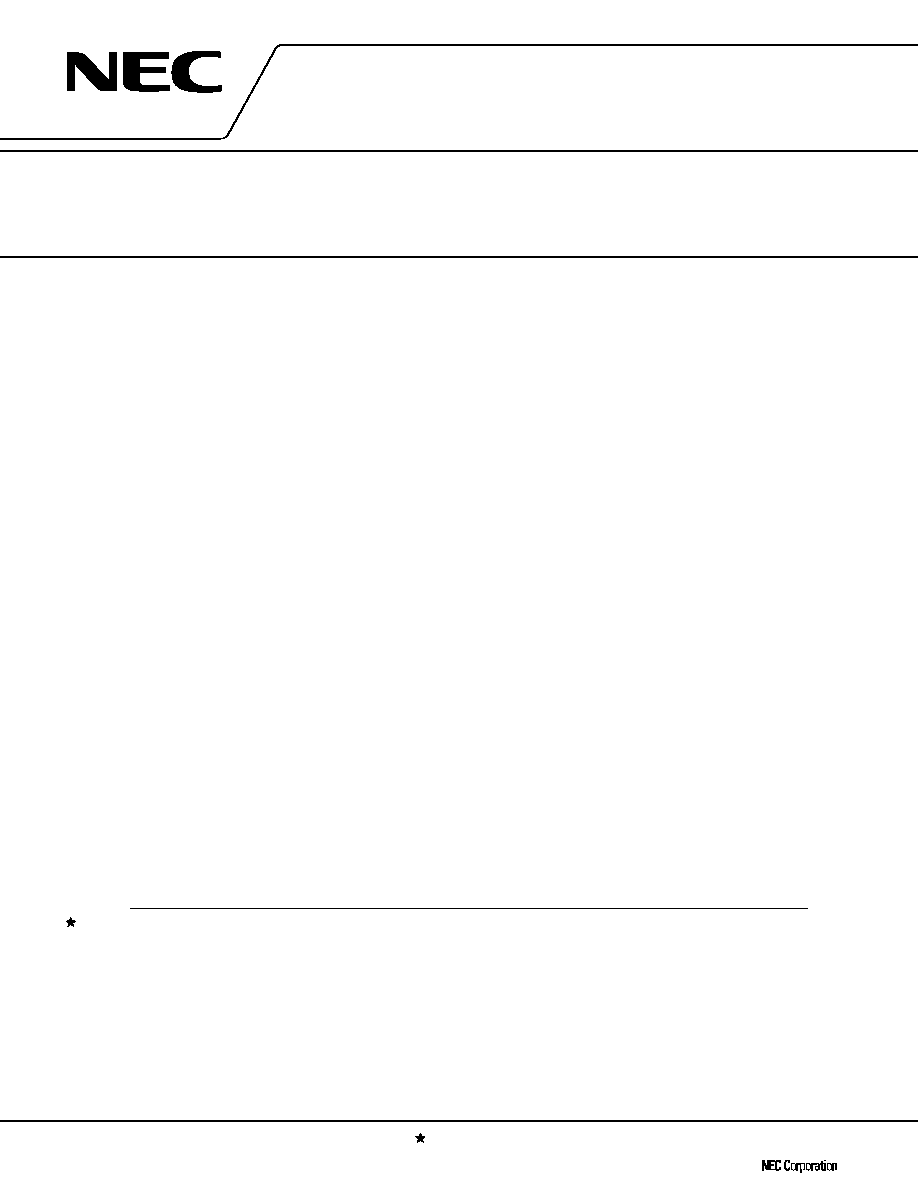

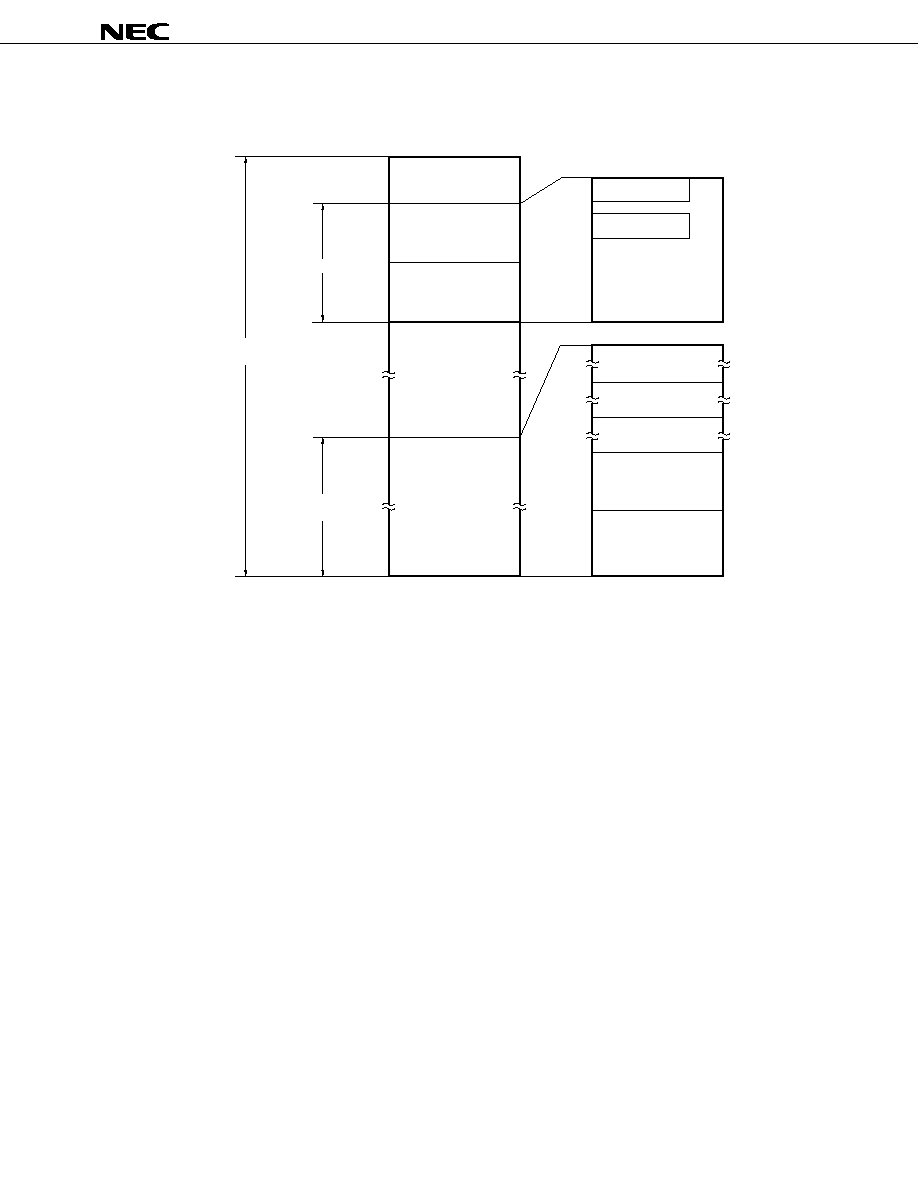

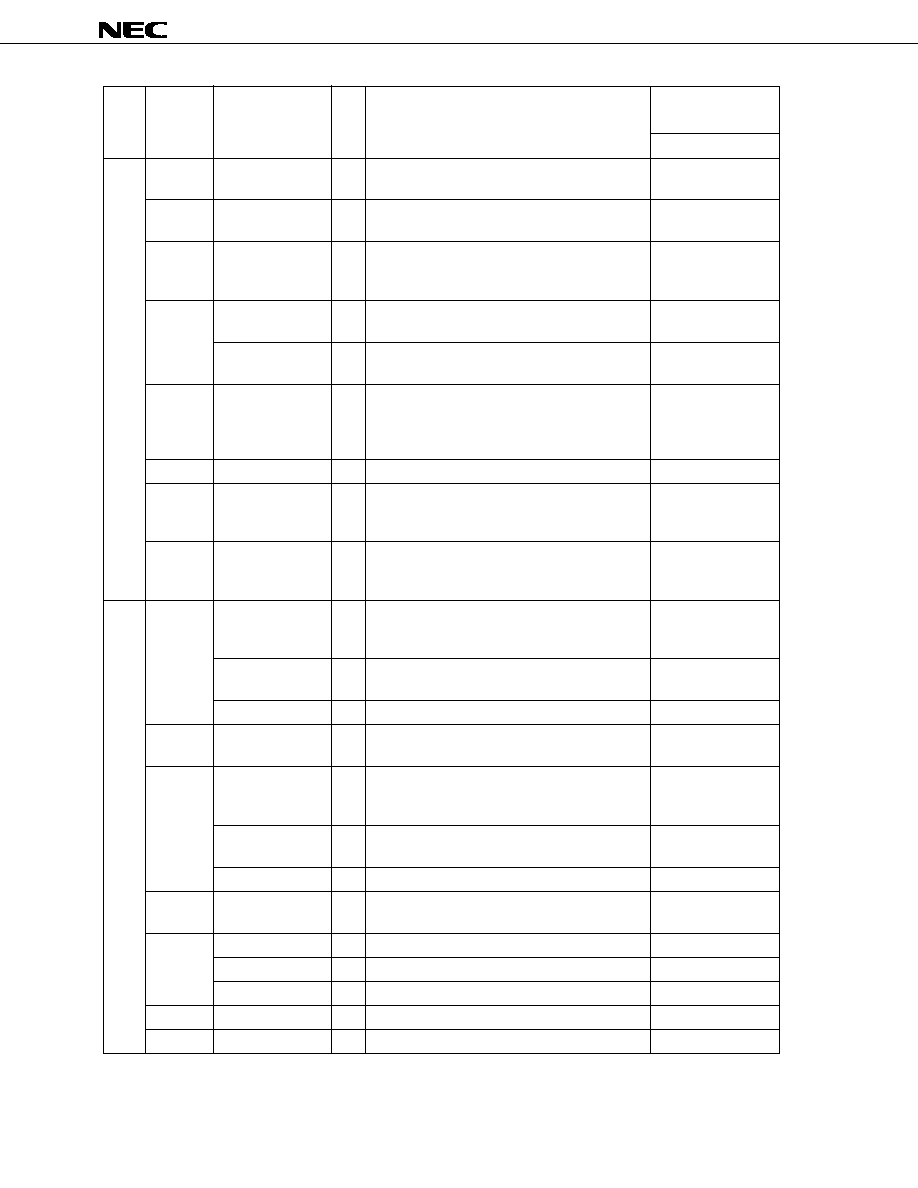

78K/III Series Product Development

High-speed, multi-function,

reinforced interrupt,

10-bit A/D

(for control application in OA and FA fields)

High-performance CPU,

sum-of-products instruction added

Reinforced timer and

A/D, expanded ROM

and RAM

Pulse output function

for inverter control

(for HDD)

(for control application in OA and FA fields)

(for control application in OA and FA fields)

(for inverter)

A/D, D/A relative instruction

added, expanded ROM, RAM

Pulse output function

for inverter control,

expanded ROM, RAM

Reinforced timer,

A/D added

(for control unit of automotive appliances)

(for inverter)

(for camera, HDD)

PD78372 subseries

PD78356 subseries

PD78334 subseries

PD78328 subseries

PD78352A subseries

PD78322 subseries

PD78312A subseries

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

PD78366A subseries

µ

PD78361A

PD78362A

PD78P364A

PD78363A

PD78365A

PD78366A

PD78368A

PD78P368A

µ

µ

3

µ

PD78361A, 78362A

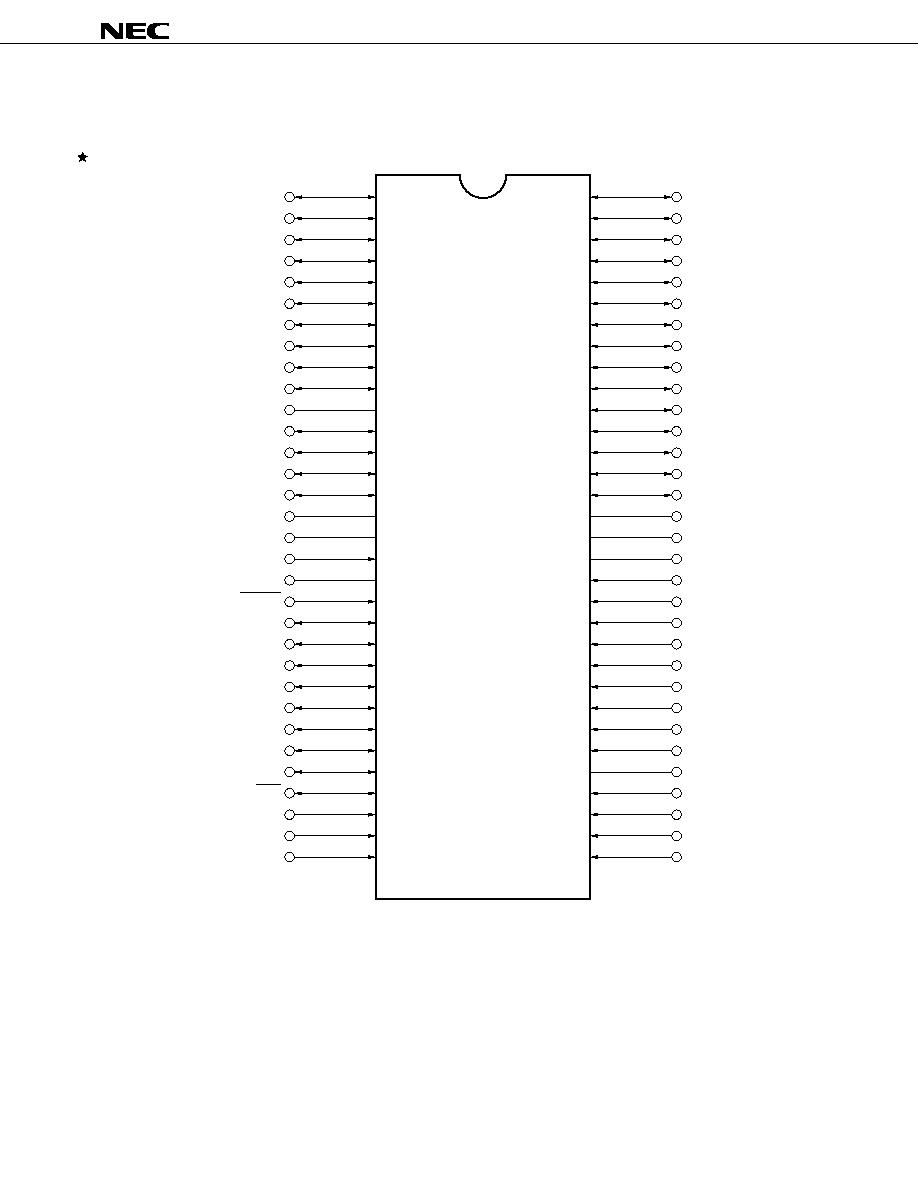

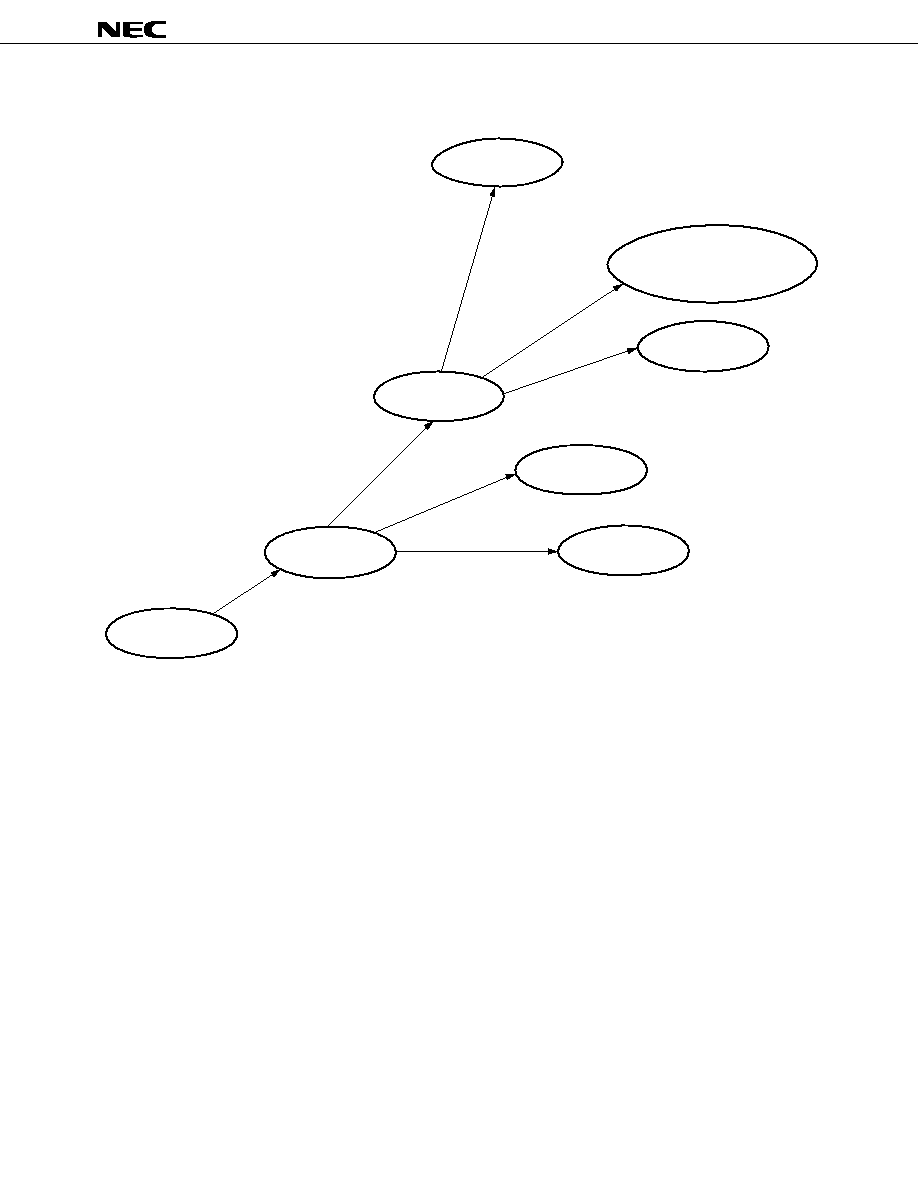

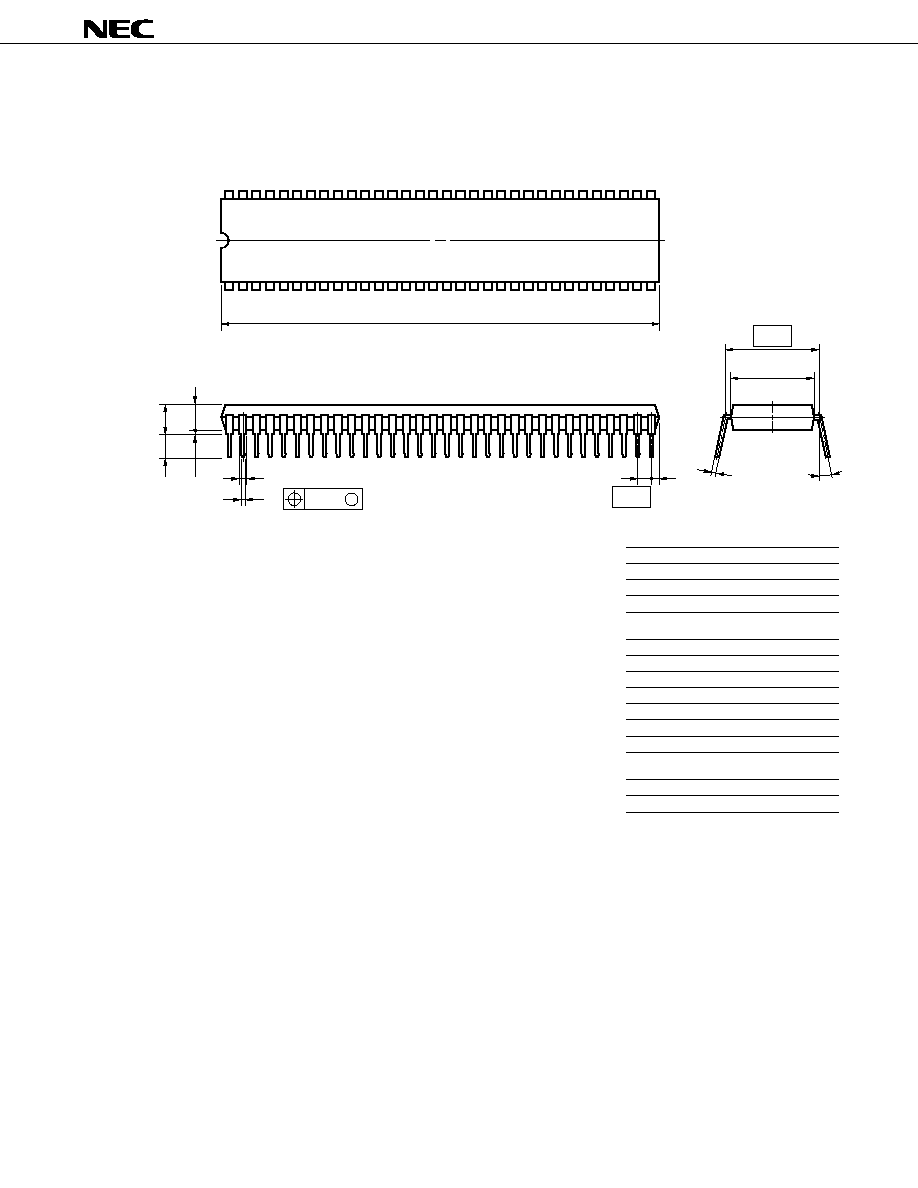

PIN CONFIGURATION (TOP VIEW)

∑

64-pin plastic shrink DIP (750 mil)

µ

PD78361ACW-

◊◊◊

, 78362ACW-

◊◊◊

Remark

◊◊◊

indicates a ROM code suffix.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

P57

P90

P91

P92

P80/TO00

P81/TO01

P82/TO02

P83/TO03

P84/TO04

P85/TO05

V

SS

P00/RTP0

P01/RTP1

P02/RTP2

P03/RTP3

V

DD

V

SS

X1

X2

RESET

P04/PWM0

P05/PWM1/TCUD

P06/TO40/TIUD

P07/TCLRUD

P30/TxD

P31/RxD

P32/SO/SB0

P33/SI/SB1

P34/SCK

MODE

P20/NMI

P21/INTP0

P56

P55

P54

P53

P52

P51

P50

P47

P46

P45

P44

P43

P42

P41

P40

V

SS

V

DD

AV

DD

AV

REF

P77/ANI7

P76/ANI6

P75/ANI5

P74/ANI4

P73/ANI3

P72/ANI2

P71/ANI1

P70/ANI0

AV

SS

P25/INTP4

P24/INTP3/TI

P23/INTP2

P22/INTP1

4

µ

PD78361A, 78362A

P00-P07

: Port0

P20-P25

: Port2

P30-P34

: Port3

P40-P47

: Port4

P50-P57

: Port5

P70-P77

: Port7

P80-P85

: Port8

P90-P92

: Port9

RTP0-RTP3

: Real-time Port

NMI

: Nonmaskable Interrupt

INTP0-INTP4

: Interrupt From Peripherals

TO00-TO05, TO40 : Timer Output

TI

: Timer Input

TIUD

: Timer Input Up Down Counter

TCUD

: Timer Control Up Down Counter

TCLRUD

: Timer Clear Up Down Counter

ANI0-ANI7

: Analog Input

T

X

D

: Transmit Data

R

X

D

: Receive Data

SI

: Serial Input

SO

: Serial Output

SB0, SB1

: Serial Bus

SCK

: Serial Clock

PWM0, PWM1

: Pulse Width Modulation Output

MODE

: Mode

RESET

: Reset

X1, X2

: Crystal

AV

DD

: Analog V

DD

AV

SS

: Analog V

SS

AV

REF

: Analog Reference Voltage

V

DD

: Power Supply

V

SS

: Ground

5

µ

PD78361A, 78362A

125 ns (internal clock: 16 MHz, external clock: 8 MHz)

32K bytes

24K bytes

2K bytes

768 bytes

64K bytes

8 bits

◊

16

◊

8 banks

115

∑ 16-bit transfer/operation

∑ Multiplication/division (16 bits

◊

16 bits, 32 bits

˜

16 bits)

∑ Bit manipulation

∑ String

∑ Sum-of-products operation (16 bits

◊

16 bits + 32 bits)

∑ Relative operation

14 (of which 8 are shared with analog input)

38

∑ 16-bit timer

◊

1

10-bit dead time timer

◊

3

16-bit compare register

◊

4

2 kinds of output mode can be selected

Mode 0, set-reset output: 6 channels

Mode 1, buffer output: 6 channels

∑ 16-bit timer

◊

1

16-bit compare register

◊

1

∑ 16-bit timer

◊

1

16-bit capture register

◊

1

16-bit capture/compare register

◊

1

∑ 16-bit timer

◊

1

16-bit capture register

◊

2

16-bit capture/compare register

◊

1

∑ 16-bit timer

◊

1

16-bit compare register

◊

2

16-bit resolution PWM output: 1 channel

Pulse outputs associated with real-time pulse unit: 4 lines

8-/9-/10-/12-bit resolution variable PWM output: 2 channels

10-bit resolution, 8 channels

Dedicated baud rate generator

UART:

1 channel

Clocked serial interface/SBI: 1 channel

∑ External: 6, internal: 14 (of which 2 are multiplexed with external)

∑ 4 priority levels can be specified through software

∑ 3 types of interrupt service modes selectable

(vectored interrupt, macro service, and context switching)

64-pin plastic shrink DIP (750 mil)

∑ Watchdog timer

∑ Standby function (HALT and STOP modes)

∑ PLL control circuit

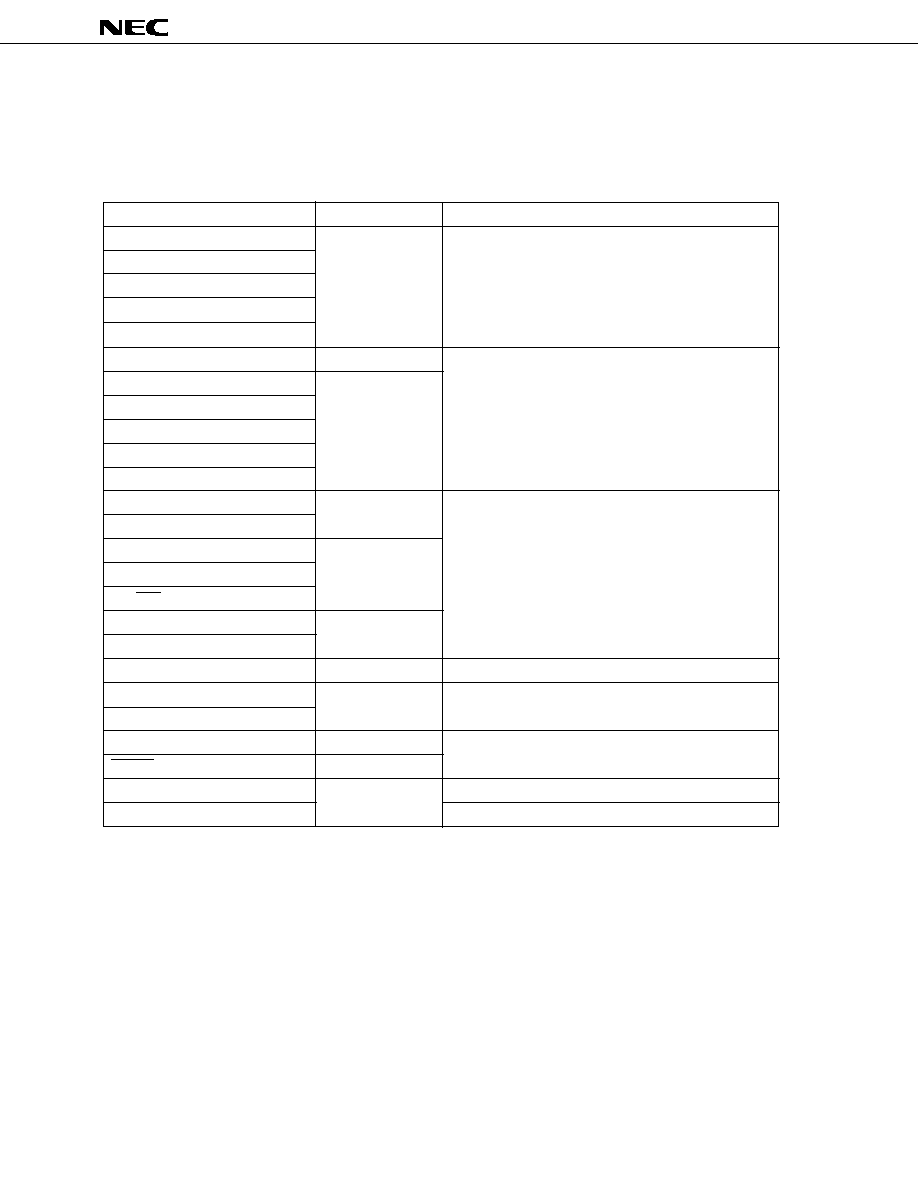

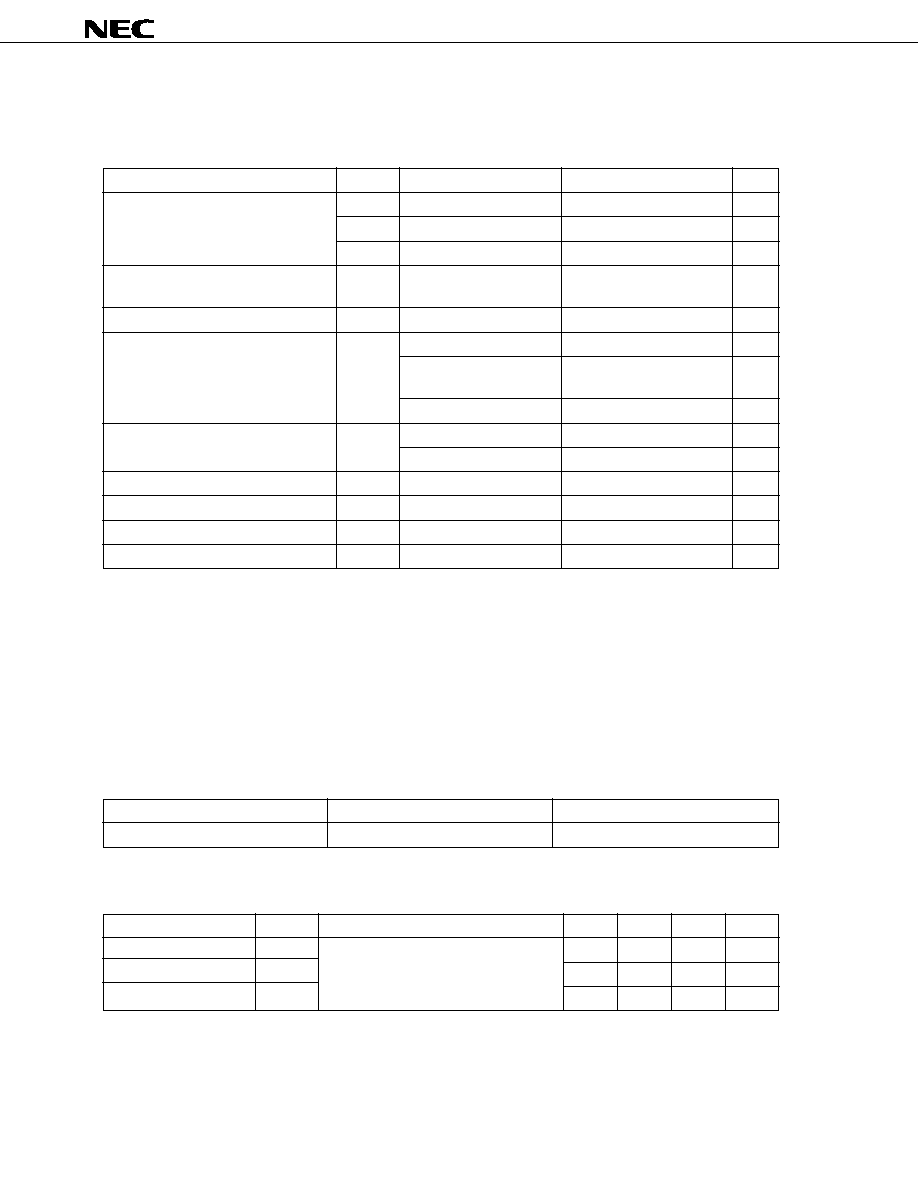

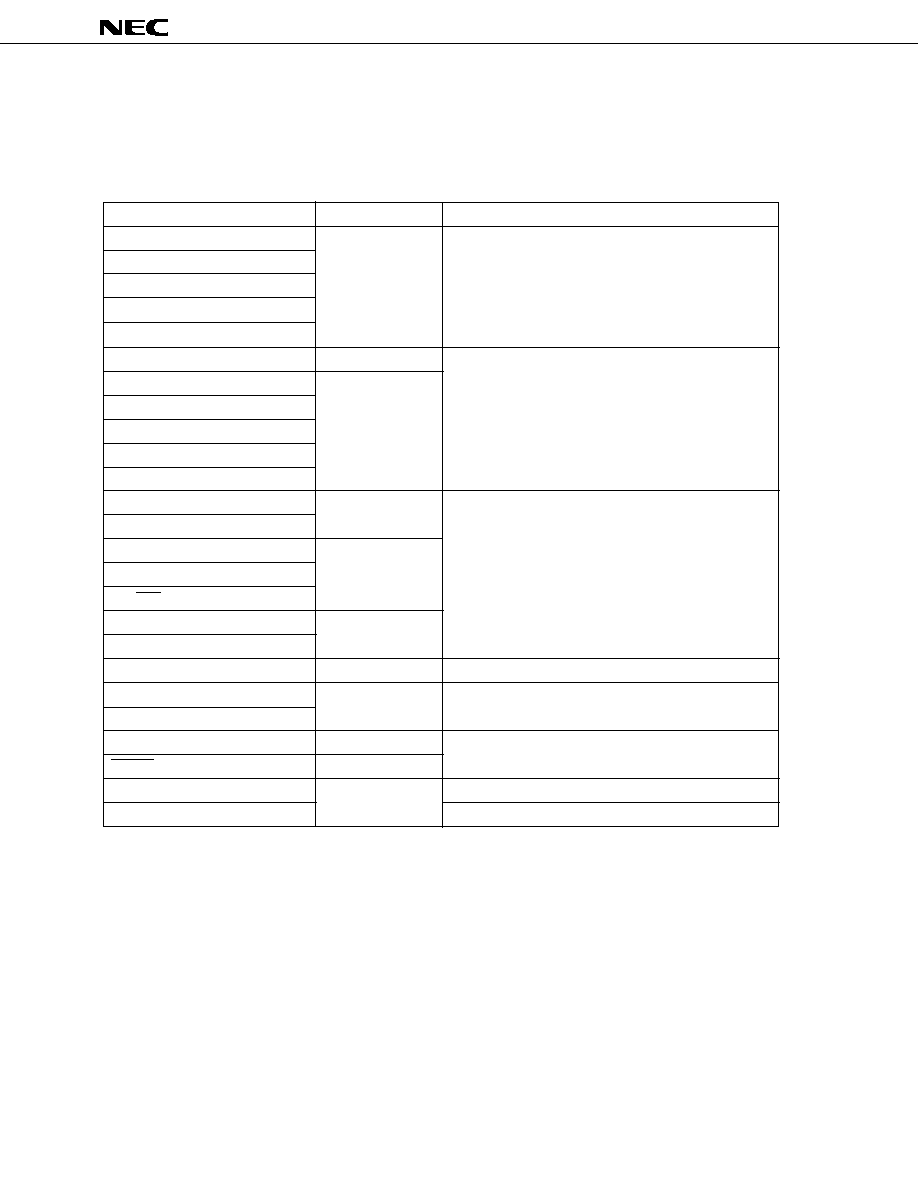

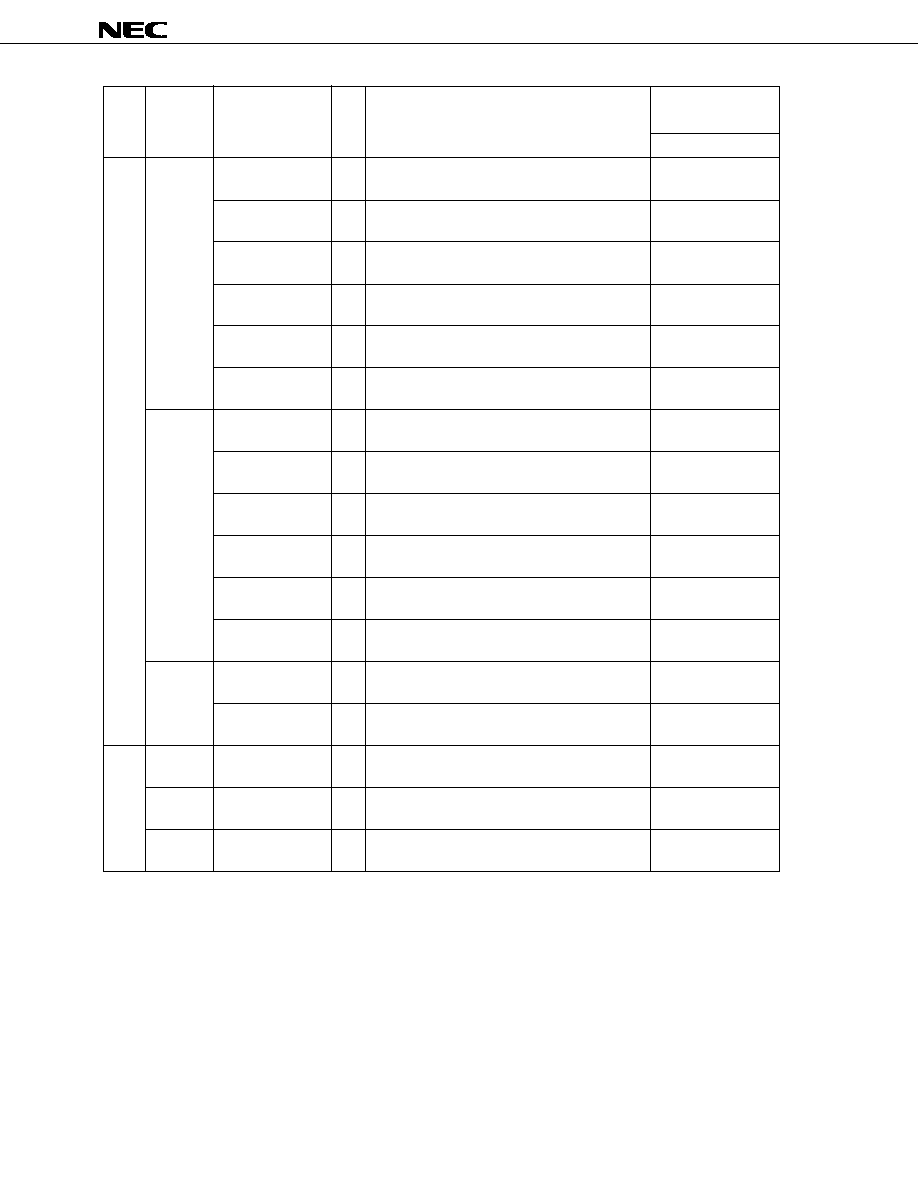

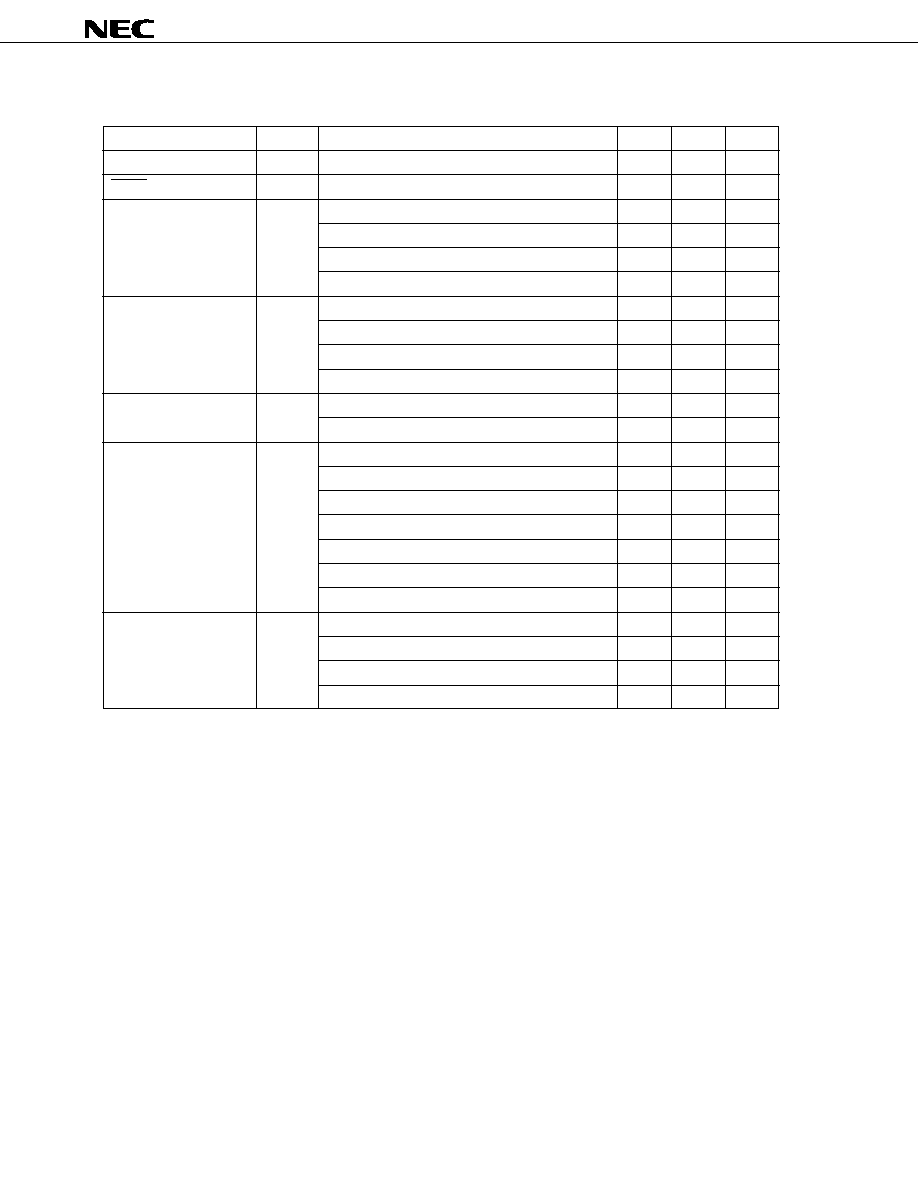

FUNCTIONAL OUTLINE

Minimum instruction execution

time

Internal memory

ROM

RAM

Memory space

General-purpose registers

Number of basic instructions

Instruction set

I/O lines

Input

I/O

Real-time pulse unit

Real-time output port

PWM unit

A/D converter

Serial interface

Interrupt function

Package

Others

µ

PD78361A

Item

µ

PD78362A

6

µ

PD78361A, 78362A

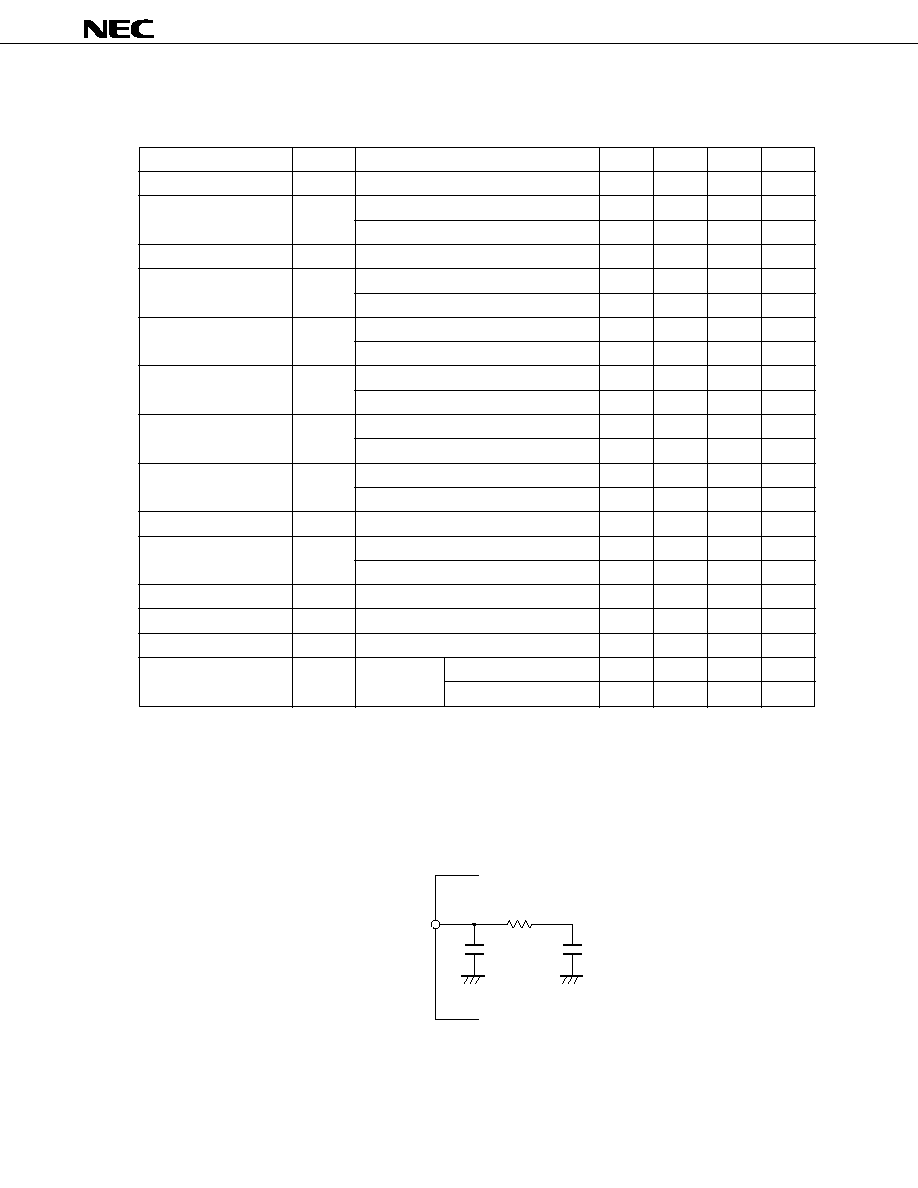

DIFFERENCES BETWEEN

µ

PD78362A AND

µ

PD78366A

ROM

Internal ROM

RAM

Input

I/O lines

I/O

Serial Interface

External expansion function

ROM-less mode

MODE setting

Package

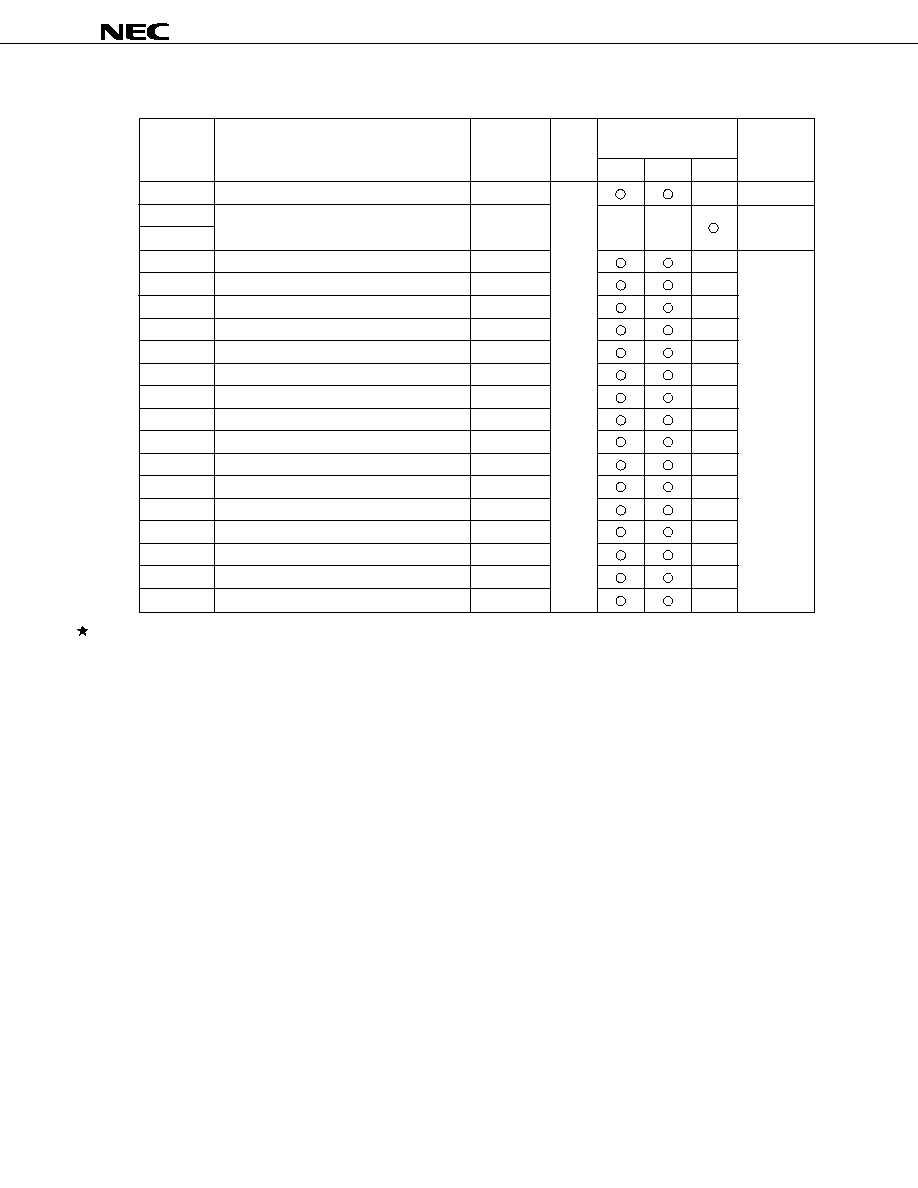

Product name

Item

24K bytes

32K bytes

786 bytes

2K bytes

14 (of which 8 are multiplexed with analog input)

38

Dedicated baud rate generator

UART: 1 channel

Clocked serial interface/SBI: 1 channel

None

None

Always set as follows:

MODE = L

64-pin plastic shrink DIP (750 mil)

49

Dedicated baud rate generator

UART (with pin selection function):

1 channel

Clocked serial interface/SBI:

1 channel

Provided

Provided

∑

In ordinary operation mode:

MODE0, 1 = LL

∑

In ROM-less mode:

MODE0, 1 = HH

80-pin plastic QFP (14

◊

20 mm)

µ

PD78362A

µ

PD78366A

7

µ

PD78361A, 78362A

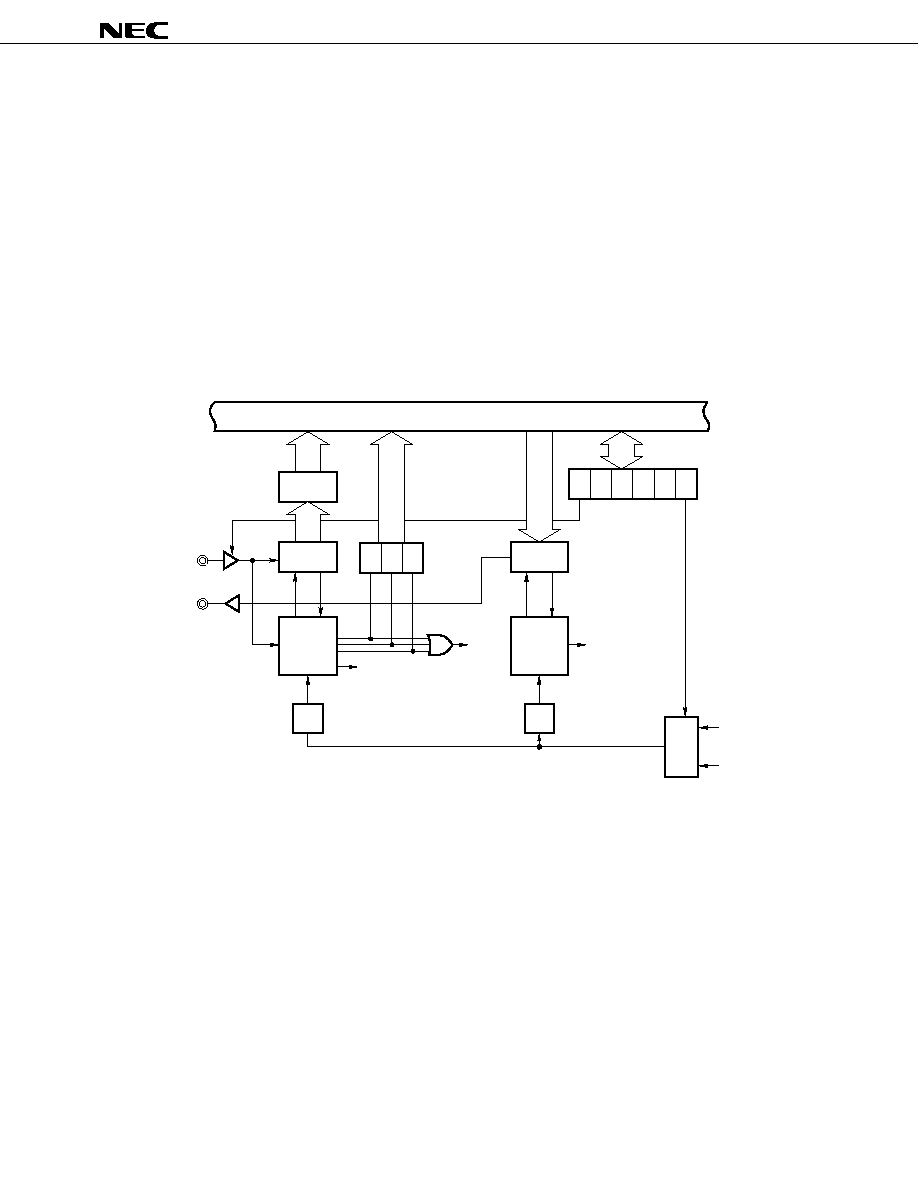

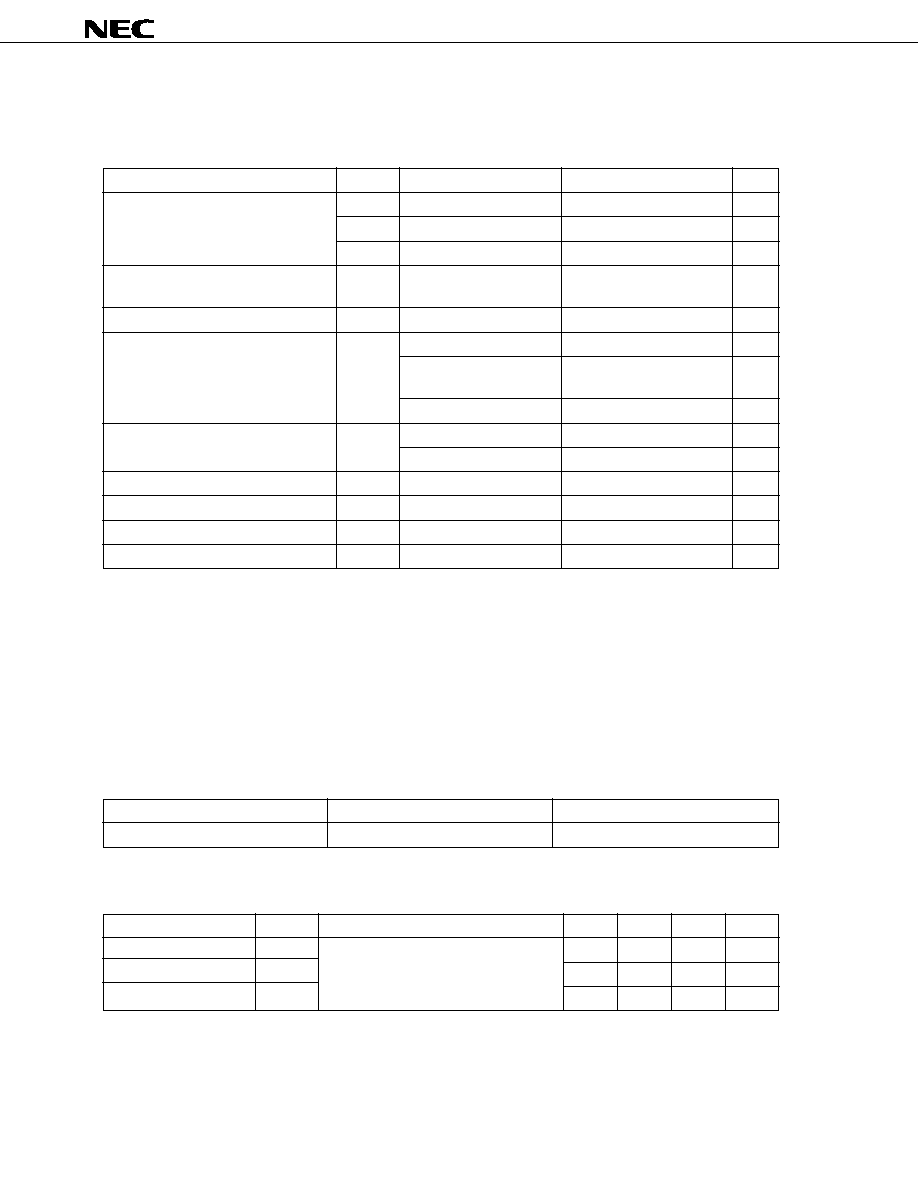

BLOCK DIAGRAM

P0

P2

P3

P4

P5

P6

P7

P8

8

6

5

8

8

8

6

3

V

DD

V

SS

PWM

AV

DD

AV

SS

AV

REF

INTP2

ANI

TO

TI

TIUD

TCLRUD

TCUD

SCK

SO/SB0

SI/B1

RxD

TxD

RTP

NMI

INTP

5

5

4

4

2

3

2

EXU

ROM/RAM

BCU

X1

X2

RESET

MODE

PROGRAMMABLE

INTERRUPT

CONTROLLER

TIMER/COUNTER

UNIT

(REAL-TIME

PULSE UNIT)

SERIAL

INTERFACE

(SBI)

(UART)

REAL-TIME

OUTPUT PORT

GENERAL

REGISTERS

128

◊

8

&

DATA

MEMORY

128

◊

8

Main RAM

MICRO

SEQUENCE

CONTROL

MICRO ROM

A/D

CONVERTER

RWM

WATCHDOG

TIMER

PORT

ALU

ROM

24K

◊

8

32K

◊

8

&

Peripheral

RAM

512

◊

8

1792

◊

8

SYSTEM

CONTROL

&

BUS

CONTROL

&

PREFETCH

CONTROL

8

7

Remark

Internal ROM and RAM capacities differ depending on the product.

8

µ

PD78361A, 78362A

TABLE OF CONTENTS

1.

PIN FUNCTIONS ......................................................................................................................

10

1.1

PORT PINS ..................................................................................................................................... 10

1.2

PINS OTHER THAN PORT PINS .................................................................................................. 11

1.3

PIN I/O CIRCUITS AND PROCESSING OF UNUSED PINS ....................................................... 12

2.

CPU ARCHITECTURE .............................................................................................................

14

2.1

MEMORY SPACE ........................................................................................................................... 14

2.2

DATA MEMORY ADDRESSING .................................................................................................... 16

2.3

PROCESSOR REGISTERS ........................................................................................................... 18

2.3.1

Control Registers ................................................................................................................. 18

2.3.2

General-Purpose Registers .................................................................................................. 19

2.3.3

Special Function Registers (SFR) ........................................................................................ 20

3.

FUNCTIONAL BLOCKS ...........................................................................................................

26

3.1

EXECUTION UNIT (EXU) ............................................................................................................... 26

3.2

BUS CONTROL UNIT (BCU) ......................................................................................................... 26

3.3

ROM/RAM ....................................................................................................................................... 26

3.4

PORT FUNCTIONS ........................................................................................................................ 26

3.5

CLOCK GENERATOR CIRCUIT ................................................................................................... 28

3.6

REAL-TIME PULSE UNIT (RPU) .................................................................................................. 30

3.7

REAL-TIME OUTPUT PORT (RTP) .............................................................................................. 37

3.8

A/D CONVERTER .......................................................................................................................... 38

3.9

SERIAL INTERFACE ..................................................................................................................... 39

3.10 PWM UNIT ...................................................................................................................................... 41

3.11 WATCHDOG TIMER (WDT) .......................................................................................................... 42

4.

INTERRUPT FUNCTIONS .......................................................................................................

43

4.1

OUTLINE ......................................................................................................................................... 43

4.2

MACRO SERVICE .......................................................................................................................... 44

4.3

CONTEXT SWITCHING ................................................................................................................. 47

4.3.1

Context Switching Function by Interrupt Request ................................................................ 47

4.3.2

Context Switching Function by BRKCS Instruction .............................................................. 48

4.3.3

Restoration from Context Switching ..................................................................................... 48

5.

STANDBY FUNCTIONS

...................................................................................................................... 49

6.

RESET FUNCTION ...................................................................................................................

50

7.

INSTRUCTION SET ..................................................................................................................

51

8.

EXAMPLE OF SYSTEM CONFIGURATION ...........................................................................

65

9.

ELECTRICAL SPECIFICATIONS ............................................................................................

66

10. PACKAGE DRAWING ..............................................................................................................

75

9

µ

PD78361A, 78362A

11. RECOMMENDED SOLDERING CONDITIONS ......................................................................

76

APPENDIX A. DIFFERENCES BETWEEN

µ

PD78362A AND

µ

PD78328 ..................................

77

APPENDIX B. TOOLS ....................................................................................................................

78

B.1

DEVELOPMENT TOOLS ............................................................................................................... 78

B.2

EMBEDDED SOFTWARE .............................................................................................................. 83

10

µ

PD78361A, 78362A

Port 0.

8-bit I/O port.

Can be set in input or output mode in 1-bit units.

Port 2.

6-bit input port.

Port 3.

5-bit I/O port.

Can be set in input or output mode in 1-bit units.

Port 4.

8-bit I/O Port.

Can be set in input or output mode in 8-bit units.

Port 5.

8-bit I/O port.

Can be set in input or output mode in 1-bit units.

Port 7.

8-bit input port

Port 8.

6-bit I/O port.

Can be set in input or output mode in 1-bit units.

Port 9.

3-bit I/O port.

Can be set in input or output mode in 1-bit units.

P00-P03

P04

P05

P06

P07

P20

P21

P22

P23

P24

P25

P30

P31

P32

P33

P34

P40-P47

P50-P57

P70-P77

P80-P85

P90-P92

RTP0-RTP3

PWM0

TCUD/PWM1

TIUD/TO40

TCLRUD

NMI

INTP0

INTP1

INTP2

INTP3/TI

INTP4

T

X

D

R

X

D

SO/SB0

SI/SB1

SCK

≠

≠

ANI0-ANI7

TO00-TO05

≠

1.

PIN FUNCTIONS

1.1

PORT PINS

I/O

Input

I/O

I/O

I/O

Input

I/O

I/O

Pin name

I/O

Function

Shared by:

11

µ

PD78361A, 78362A

P00-P03

P20

P21

P22

P23

P24/TI

P25

P24/INTP3

P05/PWM1

P06/TO40

P07

P80-P85

P06/TIUD

P70-P77

P30

P31

P34

P33/SB1

P32/SB0

P32/SO

P33/SI

P04

P05/TCUD

Real-time output port that outputs pulses in synchronization with trigger

signal from real-time pulse unit.

Non-maskable interrupt request input.

External interrupt request input.

External count clock input to timer 1.

Count operation selection control signal input to up/down counter (timer

4).

External count clock input to up/down counter (timer 4).

Clear signal input to up/down counter (timer 4).

Pulse output from real-time pulse unit.

Analog input to A/D converter.

Serial data output of asynchronous serial interface.

Serial data input of asynchronous serial interface.

Serial clock input/output of clocked serial interface.

Serial data input of clocked serial interface in 3-line mode.

Serial data output of clocked serial interface in 3-line mode.

Serial data input/output of clocked serial interface in SBI mode.

PWM signal output.

Output

Input

Input

Output

Input

Output

Input

I/O

Input

Ouput

I/O

Output

RTP0-RTP3

NMI

INTP0

INTP1

INTP2

INTP3

INTP4

TI

TCUD

TIUD

TCLRUD

TO00-TO05

TO40

ANI0-ANI7

T

X

D

R

X

D

SCK

SI

SO

SB0

SB1

PWM0

PWM1

1.2

PINS OTHER THAN PORT PINS

Pin name

I/O

Function

Shared by:

MODE

RESET

X1

X2

AV

REF

AV

DD

AV

SS

V

DD

V

SS

Input

Input

Input

≠

Input

≠

≠

≠

≠

Control signal input to set operation mode. Connected to V

SS

.

System reset input

Crystal oscillator connecting pins for system clock. If a clock is externally

supplied, input it to pin X1. Leave pin X2 open.

A/D converter reference voltage input.

A/D converter analog power supply.

A/D converter GND.

Positive power supply

GND

≠

≠

≠

≠

≠

≠

≠

≠

12

µ

PD78361A, 78362A

Input

: Independently connect to V

DD

or V

SS

through resistor

Output : Open

Connect to V

SS

Input

: Independently connect to V

DD

or V

SS

through resistor

Output : Open

Connect to V

SS

Input

: Independently connect to V

DD

or V

SS

through resistor

Output : Open

≠

Connect to V

SS

Connect to V

DD

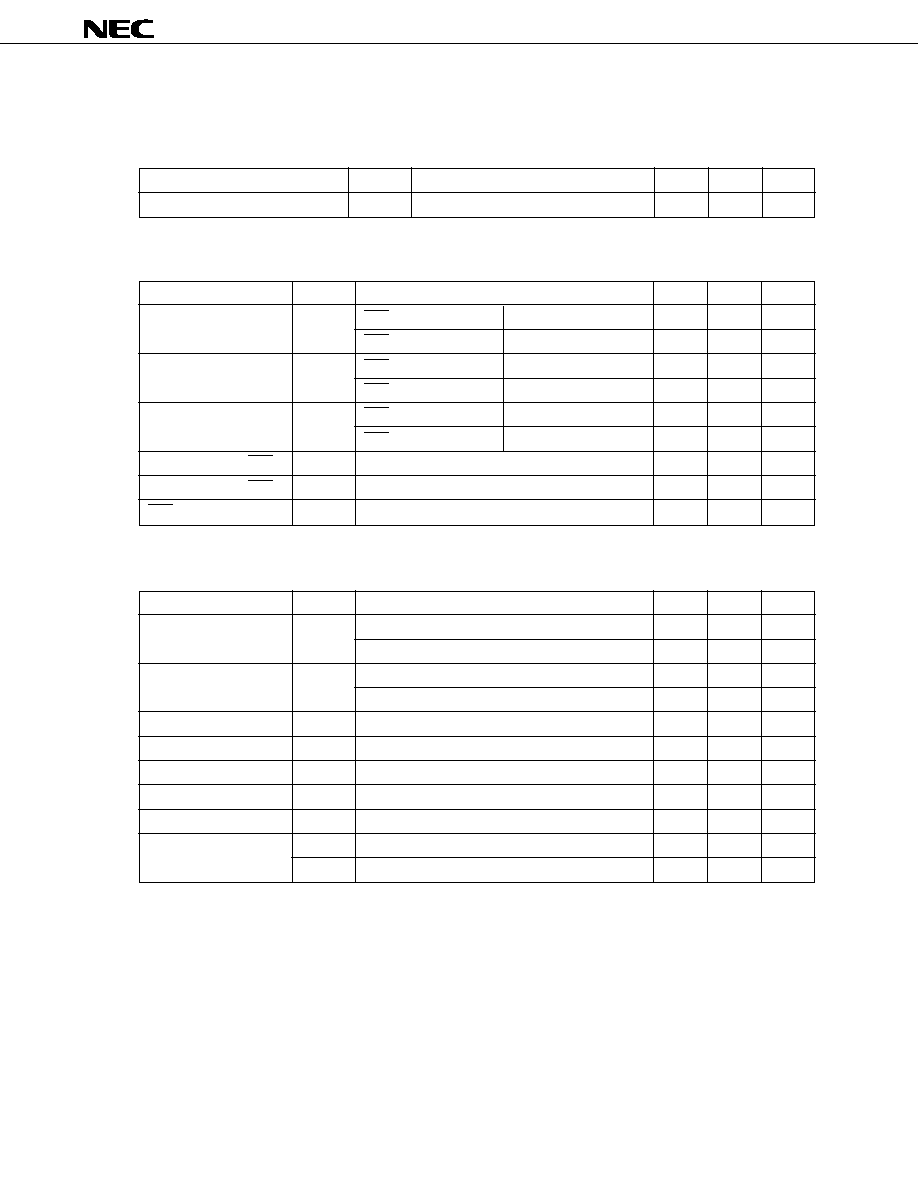

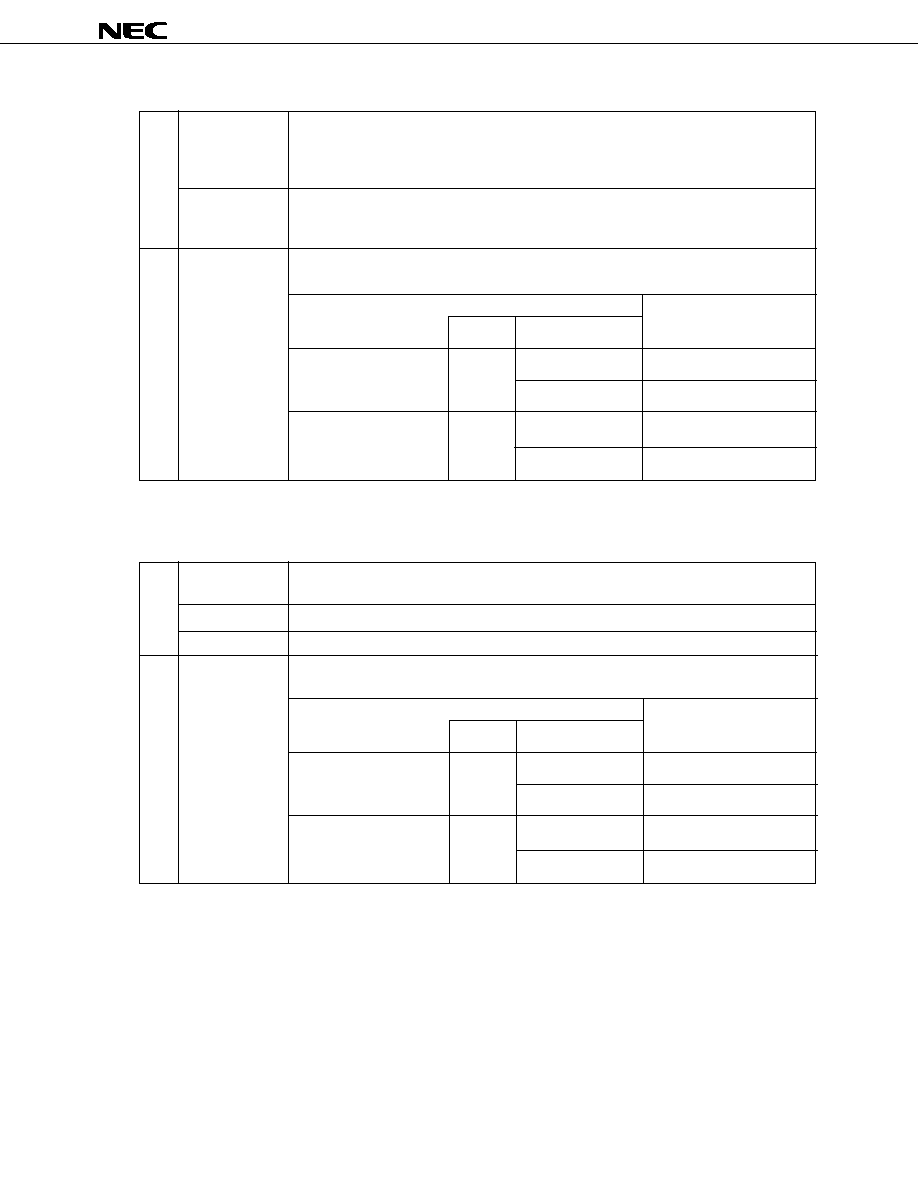

1.3

PIN I/O CIRCUITS AND PROCESSING OF UNUSED PINS

Table 1-1 shows the I/O circuit types of the respective pins, and recommended connections of the unused

pins. Figure 1-1 shows the circuits of the respective pins.

Table 1-1. Pin I/O Circuit Type and Recommended Connections of Unused Pins

Pin

I/O circuit type

Recommended connections

P00/RTP0-P03/RTP3

P04/PWM0

P05/TCUD/PWM1

P06/TIUD/TO40

P07/TCLRUD

P20/NMI

P21/INTP0

P22/INTP1

P23/INTP2

P24/INTP3/TI

P25/INTP4

P30/T

X

D

P31/R

X

D

P32/SO/SB0

P33/SI/SB1

P34/SCK

P40-P47

P50-P57

P70/ANI0-P77/ANI7

P80/TO00-P85/TO05

P90-P92

MODE

RESET

AV

REF

, AV

SS

AV

DD

5-A

2

2-A

5-A

8-A

5-A

9

5-A

1

2

≠

13

µ

PD78361A, 78362A

Figure 1-1. Pin I/O Circuits

Type 1

Type 5-A

Type 2

Type 8-A

Type 2-A

Schmitt trigger input with hysteresis characteristics

Type 9

Schmitt trigger input with hysteresis characteristics

V

DD

P-ch

N-ch

IN

IN

V

DD

P-ch

IN

pull-up

enable

pull-up

enable

data

output

disable

input

enable

V

DD

P-ch

IN/OUT

V

DD

P-ch

N-ch

V

DD

P-ch

IN/OUT

V

DD

P-ch

N-ch

pull-up

enable

data

output

disable

P-ch

N-ch

IN

+

≠

V

ref

input

enable

Comparator

(Threshold voltage)

14

µ

PD78361A, 78362A

2.

CPU ARCHITECTURE

2.1

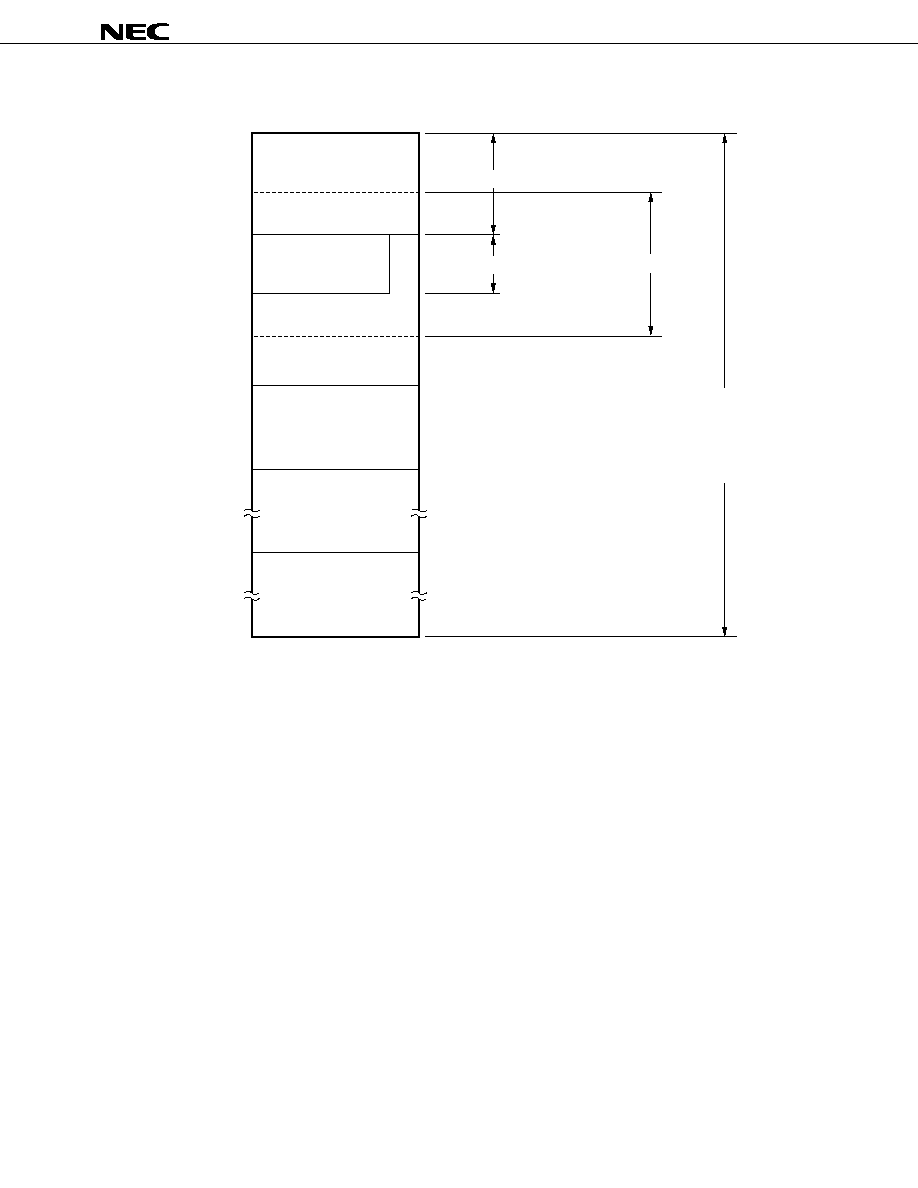

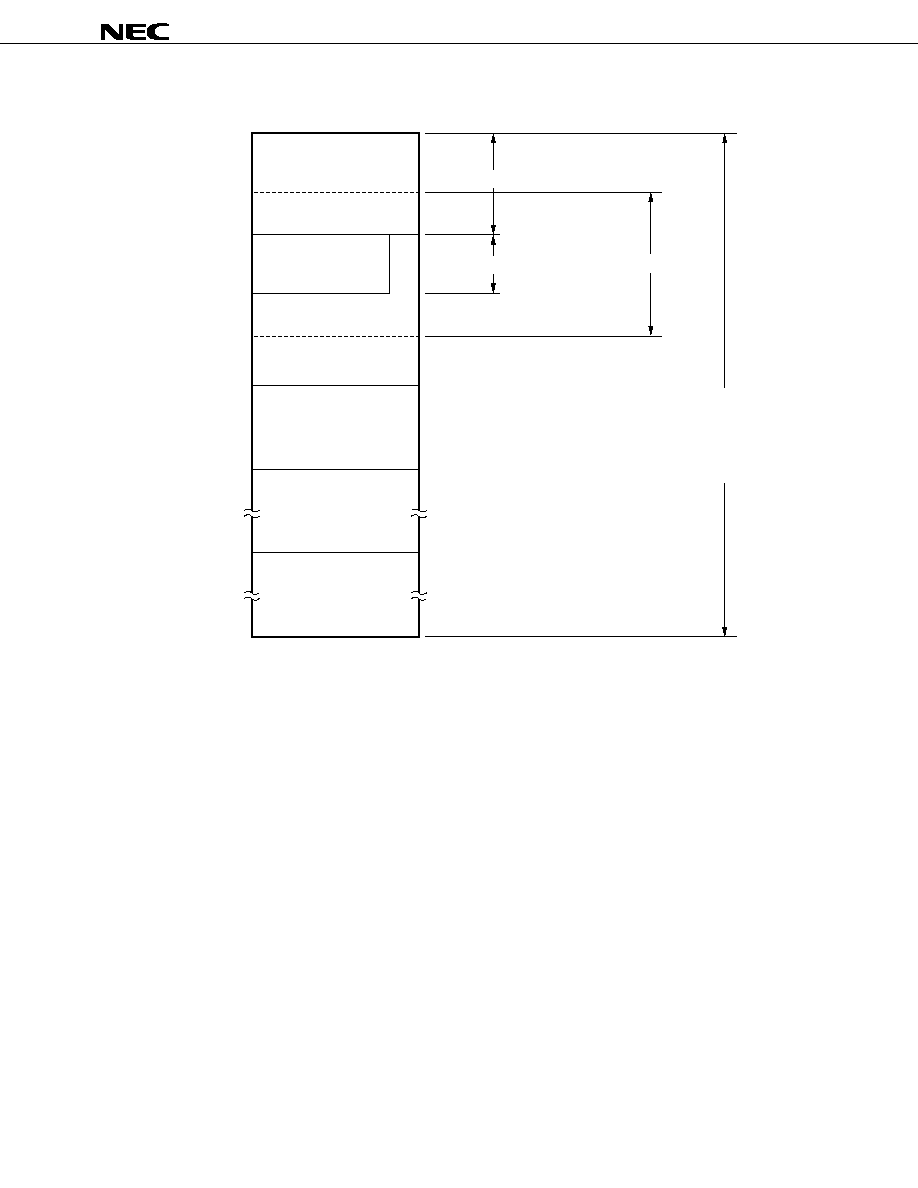

MEMORY SPACE

The

µ

PD78362A can access a memory space of 64K bytes. Figure 2-1 and 2-2 show the memory map.

Figure 2-1. Memory Map (

µ

PD78361A)

Caution

For word access (including stack operations) to the main RAM area (FE00H-FEFFH), the

address that specifies the operand must be an even value.

Memory space

(64 K

◊

8)

Data memory

Program memory

Data memory

FEFFH

FFFFH

FF00H

FDFFH

FF00H

F6FFH

F700H

0000H

Special function register

(SFR)

(256

◊

8)

Main RAM

(256

◊

8)

Cannot be used

Internal ROM

(32768

◊

8)

FEFFH

FE80H

FE25H

FE06H

F700H

7FFFH

1000H

0FFFH

0800H

07FFH

0080H

007FH

0040H

003FH

0000H

Program area

Program area

CALLT instruction table area

(64

◊

8)

Vector table area

(64

◊

8)

General-purpose

register (128

◊

8)

MODE = L

Macro service

control (32

◊

8)

Data area

(768

◊

8)

7FFFH

8000H

CALLF instruction entry area

(2048

◊

8)

Peripheral RAM

(1792

◊

8)

15

µ

PD78361A, 78362A

Figure 2-2. Memory Map (

µ

PD78362A)

Caution

For word access (including stack operations) to the main RAM area (FE00H-FEFFH), the

address that specifies the operand must be an even value.

Memory space

(64 K

◊

8)

Data memory

FEFFH

FFFFH

FF00H

FDFFH

FF00H

FBFFH

FC00H

0000H

Special function register

(SFR)

(256

◊

8)

Main RAM

(256

◊

8)

Cannot be used

Internal ROM

(24576

◊

8)

FEFFH

FE80H

FE25H

FE06H

FC00H

5FFFH

1000H

0FFFH

0800H

07FFH

0080H

007FH

0040H

003FH

0000H

Program area

Program area

CALLT instruction table area

(64

◊

8)

Vector table area

(64

◊

8)

General-purpose

register (128

◊

8)

MODE = L

Macro service

control (32

◊

8)

Data area

(768

◊

8)

5FFFH

6000H

CALLF instruction entry area

(2048

◊

8)

Peripheral RAM

(512

◊

8)

Program memory

Data memory

16

µ

PD78361A, 78362A

2.2

DATA MEMORY ADDRESSING

The

µ

PD78362A is provided with many addressing modes that improve the operability of the memory and

can be used with high-level languages. Especially, an area of addresses FC00H-FFFFH (F700H-FFFFH

in the

µ

PD78361A) to which the data memory is mapped can be addressed in a mode peculiar to the functions

provided in this area, including special function registers (SFR) and general-purpose registers.

Figure 2-3. Data Memory Addressing (

µ

PD78361A)

Caution

For word access (including stack oprations) to the main RAM area (FE00H-FEFFH), the

address that specifies the operand must be an even value.

FF20H

FF1FH

FE20H

FE1FH

F700H

F6FFH

FF00H

FEFFH

FE80H

FE7FH

FE00H

FDFFH

8000H

7FFFH

0000H

Special function

register

(SFR)

General-purpose

register

Main RAM

Peripheral RAM

Internal ROM

Cannot be used

SFR addressing

Register addressing

Short direct addressing

Direct addressing

Register indirect addressing

Based addressing

Based indexed addressing

Based indexed addressing

(with displacement)

FFFFH

17

µ

PD78361A, 78362A

Figure 2-4. Data Memory Addressing (

µ

PD78362A)

Caution

For word access (including stack oprations) to the main RAM area (FE00H-FEFFH), the

address that specifies the operand must be an even value.

FF20H

FF1FH

FE20H

FE1FH

FC00H

FBFFH

FF00H

FEFFH

FE80H

FE7FH

FE00H

FDFFH

6000H

5FFFH

0000H

Special function

register

(SFR)

General-purpose

register

Main RAM

Peripheral RAM

Internal ROM

Cannot be used

SFR addressing

Register addressing

Short direct addressing

Direct addressing

Register indirect addressing

Based addressing

Based indexed addressing

Based indexed addressing

(with displacement)

FFFFH

18

µ

PD78361A, 78362A

2.3

PROCESSOR REGISTERS

The

µ

PD78362A is provided with the following three types of processor registers:

∑ Control registers

∑ General-purpose registers

∑ Special function registers (SFRs)

2.3.1

Control Registers

(1) Program counter (PC)

This is a 16-bit register that holds an address of the instruction to be executed next.

(2) Program status word (PSW)

This 16-bit register indicates the status of the CPU as a result of instruction execution.

(3) Stack pointer (SP)

This 16-bit register indicates the first address of the stack area (LIFO) of the memory.

Figure 2-5. Configuration of Control Registers

PC

PSW

SP

15

0

Figure 2-6. Configuration of PSW

PSW

UF

RBS2

RBS1

RBS0

0

0

0

0

15

8

S

Z

RSS

AC

IE

P/V

0

CY

7

0

UF

: User flag

RBS0-RBS2: Register bank select flag

S

: Sign flag (MSB of execution result)

Z

: Zero flag

RSS

: Register set select flag

AC

: Auxiliary carry flag

IE

: Interrupt request enable flag

P/V

: Parity/overflow flag

CY

: Carry flag

19

µ

PD78361A, 78362A

2.3.2

General-Purpose Registers

The

µ

PD78362A is provided with eight banks of general-purpose registers with one bank consisting of 8

words

◊

16 bits. Figure 2-7 shows the configuration of the general-purpose register banks. The general-purpose

registers are mapped to an area of addresses FE80H-FEFFH. Each of these registers can be used as an 8-

bit register. In addition, two registers can be used as one 16-bit register pair (refer to Figure 2-8 ). These

general-purpose registers facilitate complicated multitask processing.

Figure 2-8. Processing Bits of General-Purpose Registers

Figure 2-7. Configuration of General-Purpose Register Banks

15

0

RP0

RP1

RP2

RP3

RP4

RP5

RP6

RP7

Bank 7

Bank 1

Bank 0

RBNK0

RBNK1

RBNK2

RBNK3

RBNK4

RBNK5

RBNK7

RBNK6

R15

R13

R11

R9

R7

R5

R3

R1

R14

R12

R10

R8

R6

R4

R2

R0

RP7

RP6

RP5

RP4

RP3

RP2

RP1

RP0

(FH)

(DH)

(BH)

(9H)

(7H)

(5H)

(3H)

(1H)

(EH)

(CH)

(AH)

(8H)

(6H)

(4H)

(2H)

(0H)

FEFFH

FE80H

8-bit processing

16-bit processing

7

07

0

15

0

20

µ

PD78361A, 78362A

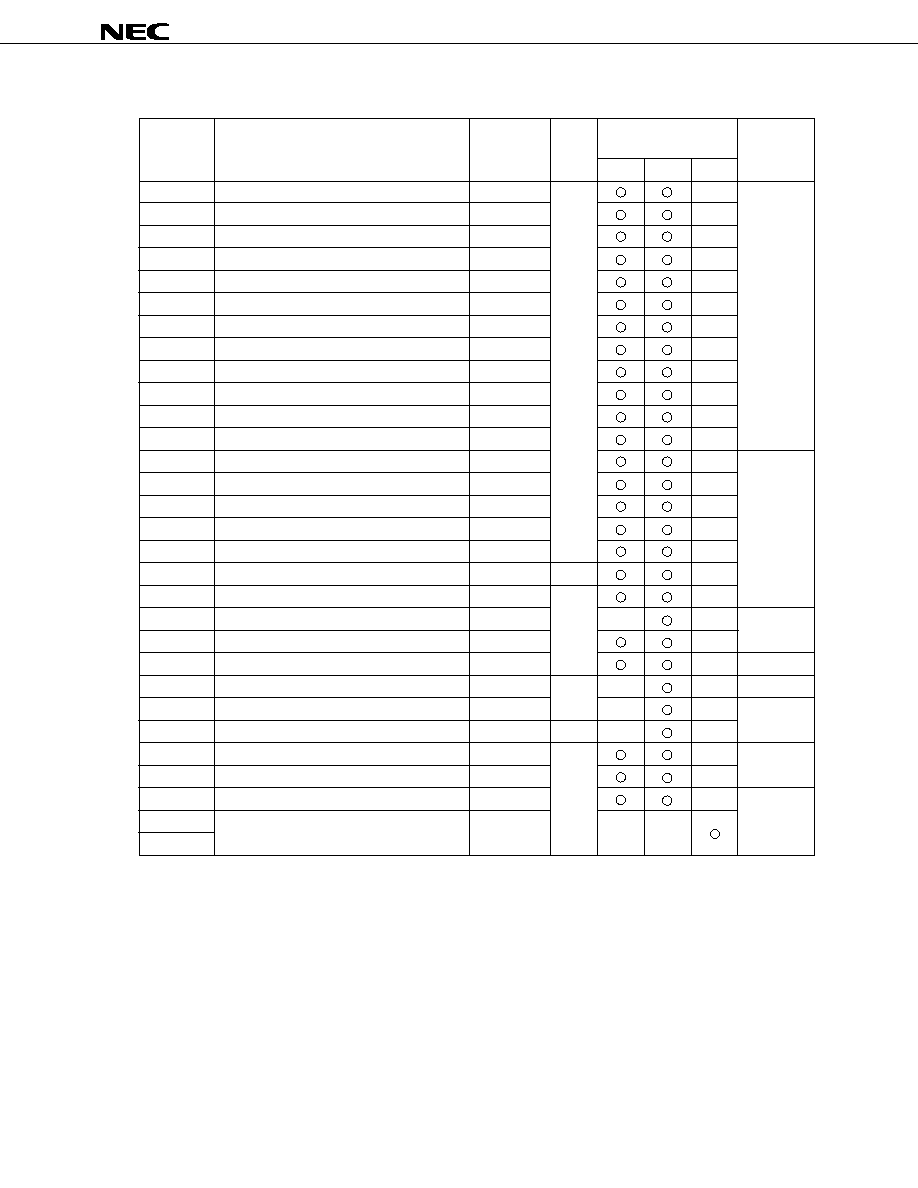

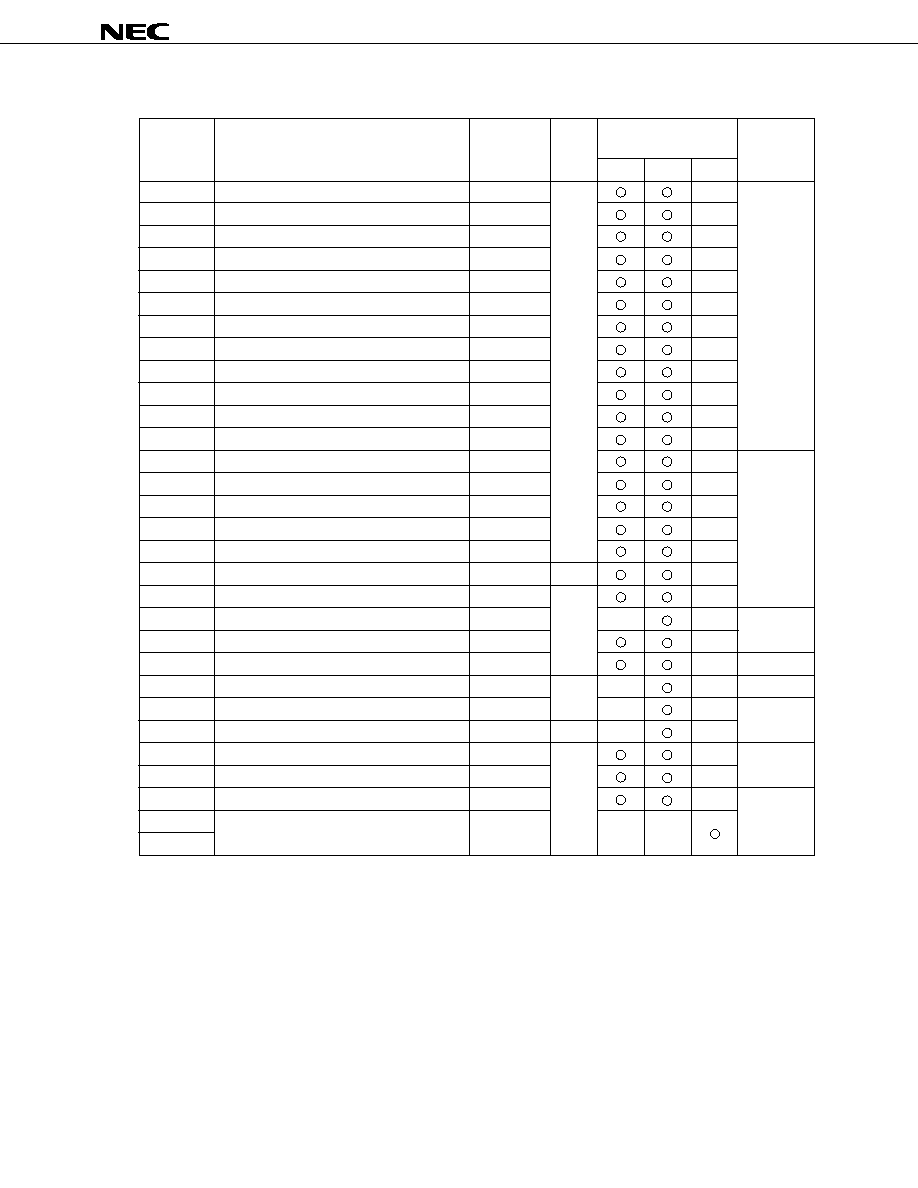

2.3.3

Special Function Registers (SFR)

Special function registers (SFRs) are registers assigned special functions such as mode registers and control

registers for internal peripheral hardware, and are mapped to a 256-byte address space at FF00H through

FFFFH.

Table 2-1 lists the SFRs. The meanings of the symbols in this table are as follows:

∑

Symbol ................................... Indicates the mnemonic symbol for an SFR.

This mnemonic can be coded in the operand field of an instruction.

∑

R/W ........................................ Indicates whether the SFR can be read or written.

R/W : Read/write

R

: Read only

W

: Write only

∑

Bit units for manipulation ...... Indicates bit units in which the SFR can be manipulated. The SFRs that

can be manipulated in 16-bit units can be coded as an sfrp operand.

Specify an even address for these SFRs.

The SFRs that can be manipulated in 1-bit units can be coded as the

operand of bit manipulation instructions.

∑

On reset ................................. Indicates the status of the register at RESET input.

Cautions 1. Do not access the addresses in the range FF00H-FFFFH to which no special function

register is allocated. If these addresses are accessed, malfunctio ning may occur.

2. Do not write data to the read-only registers. Otherwise, the internal circuit may not

operate normally.

3. When using read data as byte data, process undefined bit(s) first.

4. TOUT and TXS are write-only registers. Do no read these registers.

5. Bits 0, 1, and 4 of SBIC are write-only bits. When these bits are read, they are always

"0".

21

µ

PD78361A, 78362A

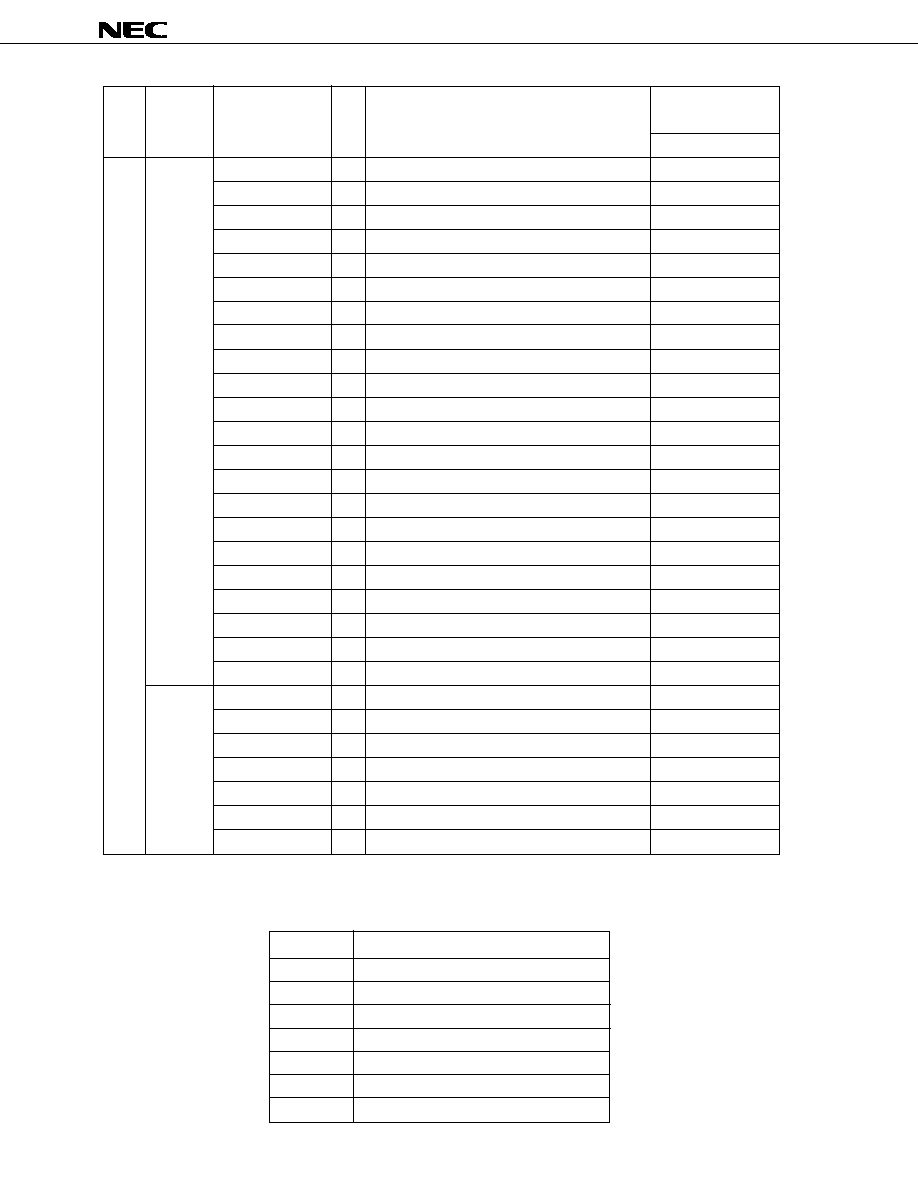

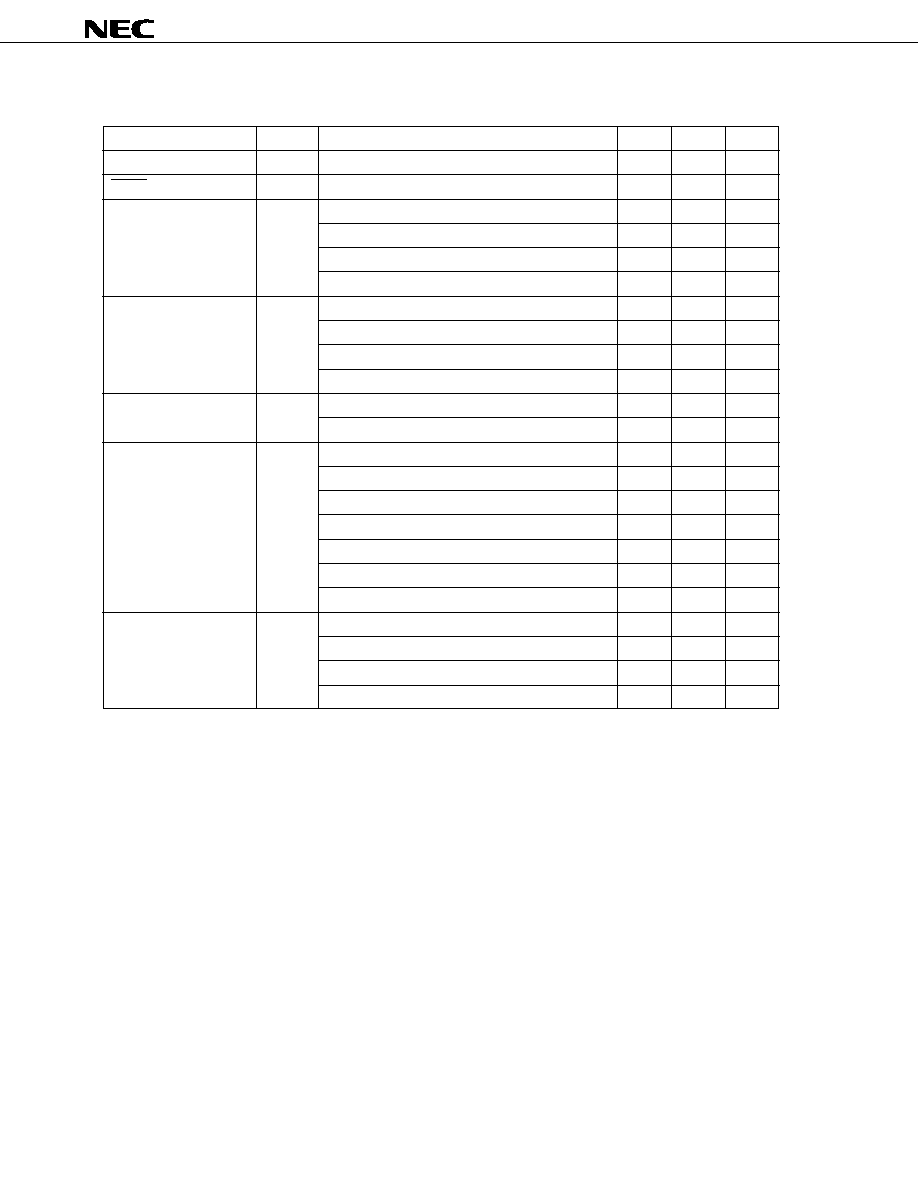

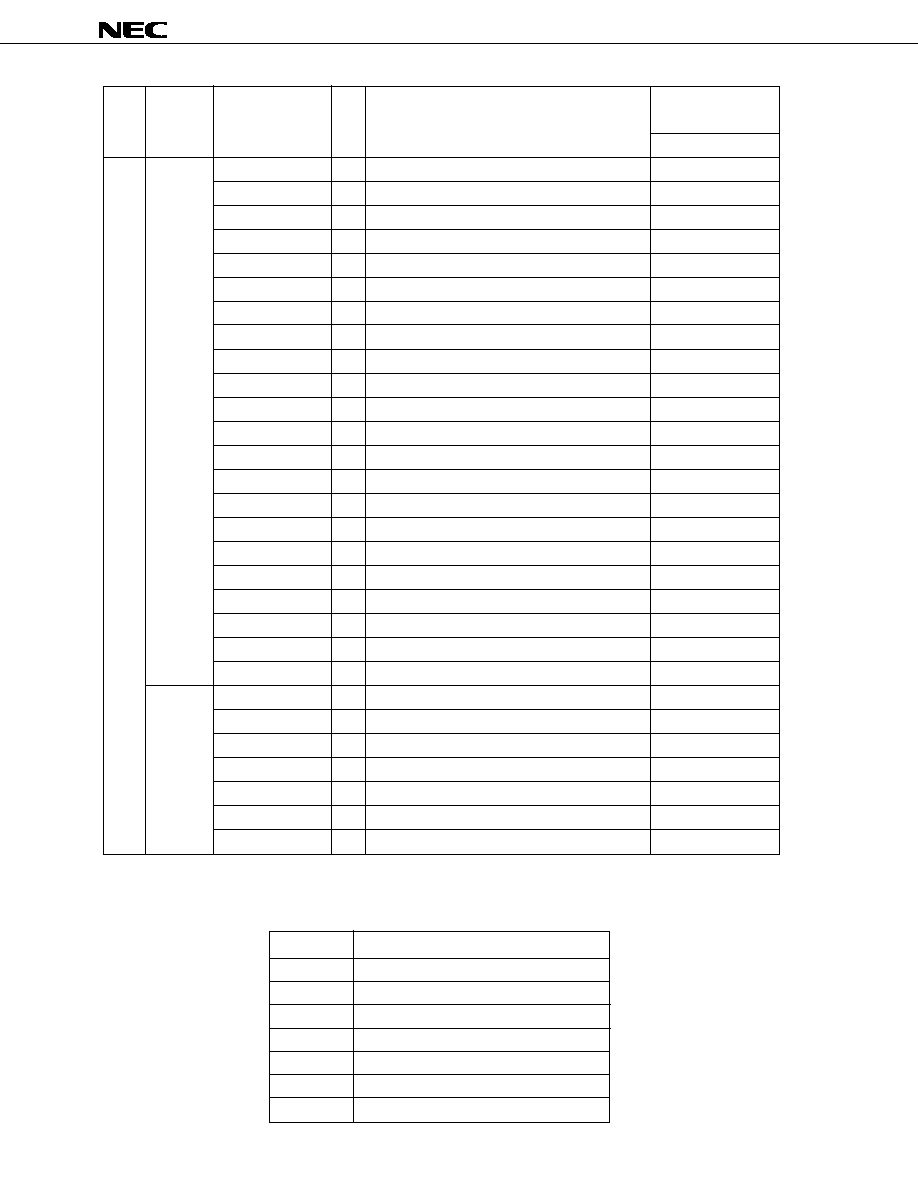

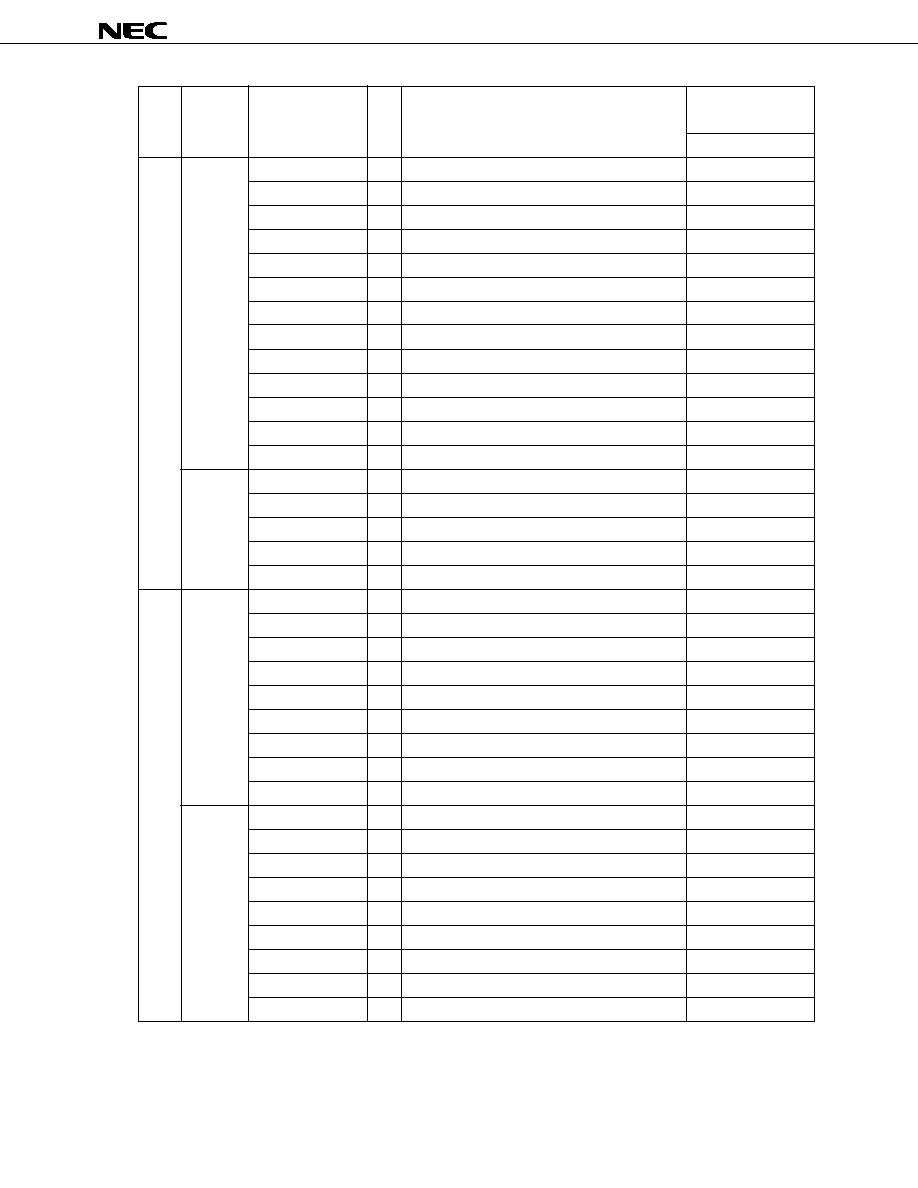

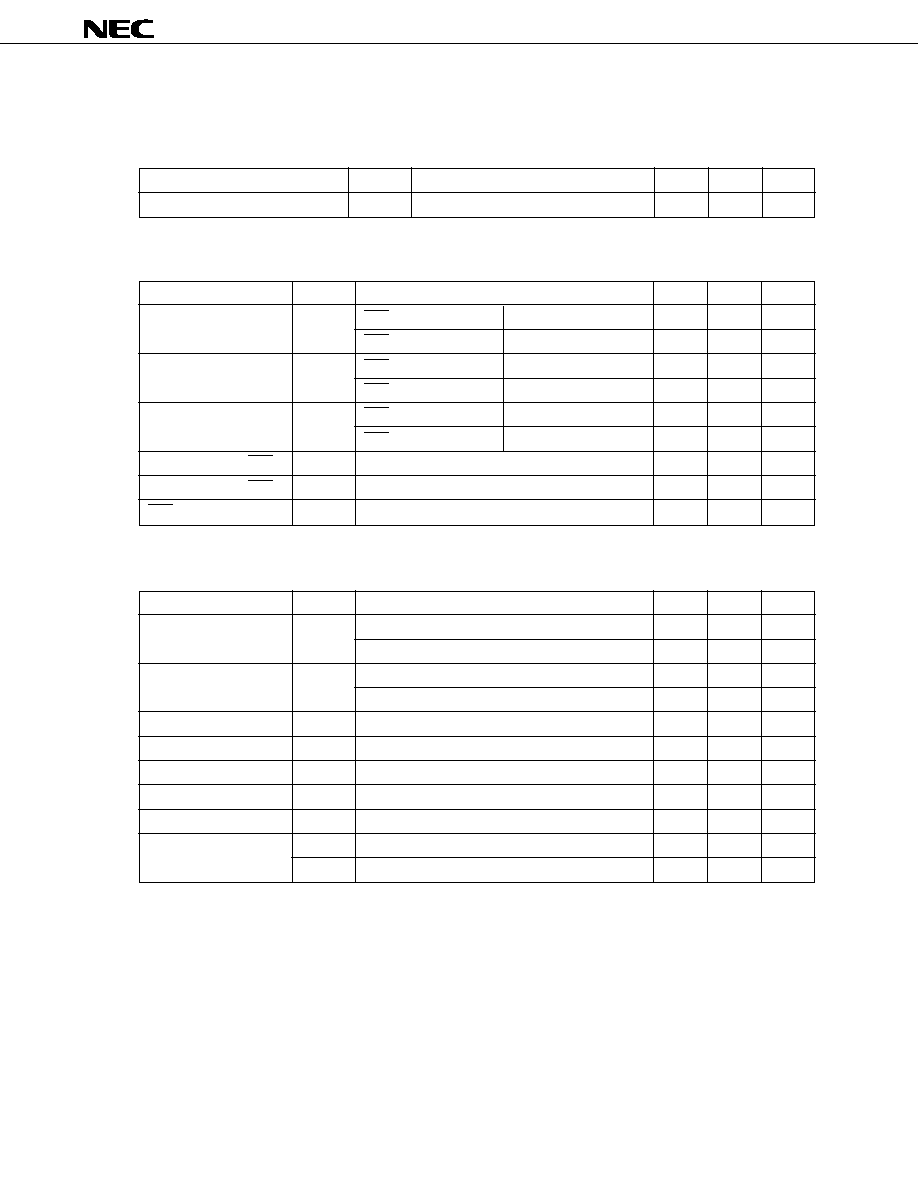

Table 2-1. List of Special Function Registers (1/5)

Bit units for

manipulation

1 bit

8 bits

16 bits

On reset

Address

Special function register (SFR)

Symbol

R/W

FF00H

FF02H

FF03H

FF04H

FF05H

FF07H

FF08H

FF09H

FF10H

FF11H

FF12H

FF13H

FF14H

FF15H

FF16H

FF17H

FF18H

FF19H

FF1AH

FF1BH

FF1CH

FF1DH

FF1EH

FF1FH

FF20H

FF23H

FF25H

FF28H

FF29H

FF2CH

FF2DH

FF2EH

FF2FH

FF30H

FF31H

FF32H

FF33H

Port 0

Port 2

Port 3

Port 4

Port 5

Port 7

Port 8

Port 9

Compare register 00

Compare register 01

Compare register 02

Compare register 03

Buffer register CM00

Buffer register CM01

Buffer register CM02

Timer register 0

Port 0 mode register

Port 3 mode register

Port 5 mode register

Port 8 mode register

Port 9 mode register

Reload register

Timer unit mode register 0

Timer unit mode register 1

Compare register 10

Timer register 1

R/W

R

R/W

R

R/W

R

R/W

R/W

R

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

0000H

FFH

◊◊◊

1 1111B

FFH

◊◊

11 1111B

◊◊◊◊ ◊

111B

Undefined

00H

Undefined

0000H

P0

P2

P3

P4

P5

P7

P8

P9

CM00

CM01

CM02

CM03

BFCM00

BFCM01

BFCM02

TM0

PM0

PM3

PM5

PM8

PM9

DTIME

TUM0

TUM1

CM10

TM1

Undefined

22

µ

PD78361A, 78362A

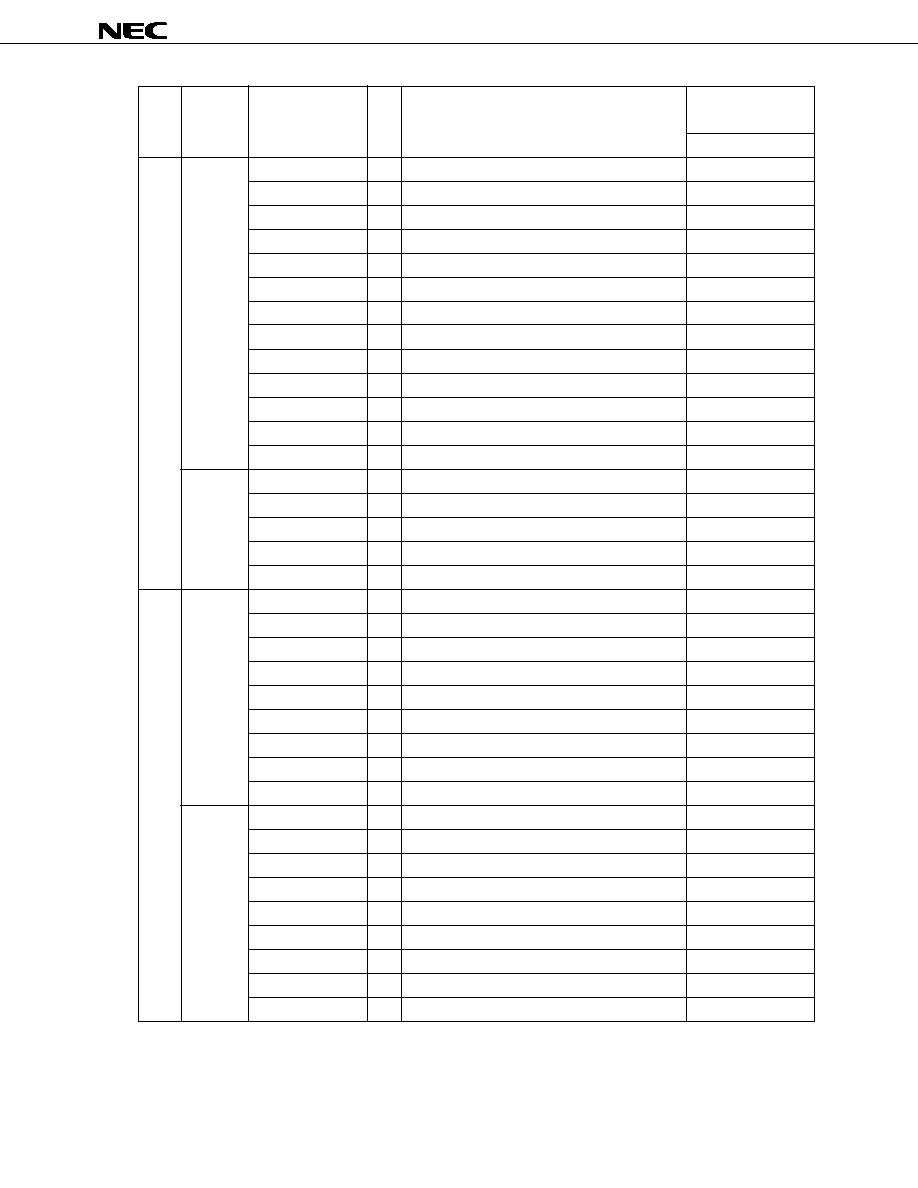

Table 2-1. List of Special Function Registers (2/5)

Bit units for

manipulation

1 bit

8 bits

16 bits

On reset

Address

Special function register (SFR)

Symbol

R/W

FF34H

FF35H

FF36H

FF37H

FF38H

FF39H

FF3AH

FF3BH

FF3CH

FF3DH

FF40H

FF43H

FF44H

FF45H

FF48H

FF4EH

FF4FH

FF50H

FF51H

FF52H

FF53H

FF54H

FF55H

FF56H

FF57H

FF58H

FF59H

FF5AH

FF5BH

FF5CH

FF5DH

FF5EH

FF5FH

FF60H

FF61H

FF62H

FF68H

Capture/compare register 20

Capture register 20

Timer register 2

Buffer register CM03

External interrupt mode register 0

External interrupt mode register 1

Port 0 mode control register

Port 3 mode control register

Pull-up resistor option register L

Pull-up resistor option register H

Port 8 mode control register

Sampling control register 0

Sampling control register 1

Capture/compare register 30

Capture register 30

Capture register 31

Timer register 3

Compare register 40

Compare register 41

Timer register 4

Timer control register 4

Timer out register

Real-time output port register

Real-time output port mode register

Port read control register

A/D converter mode register

CC20

CT20

TM2

BFCM03

INTM0

INTM1

PMC0

PMC3

PUOL

PUOH

PMC8

SMPC0

SMPC1

CC30

CT30

CT31

TM3

CM40

CM41

TM4

TMC4

TOUT

RTP

RTPM

PRDC

ADM

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

R/W

R

R/W

R

R/W

R

R/W

W

R/W

Undefined

0000H

Underfined

00H

◊◊◊

0 0000B

00H

◊◊

00 0000B

00H

Undefined

0000H

Undefined

0000H

00H

◊◊

01 0101B

Undefined

00H

23

µ

PD78361A, 78362A

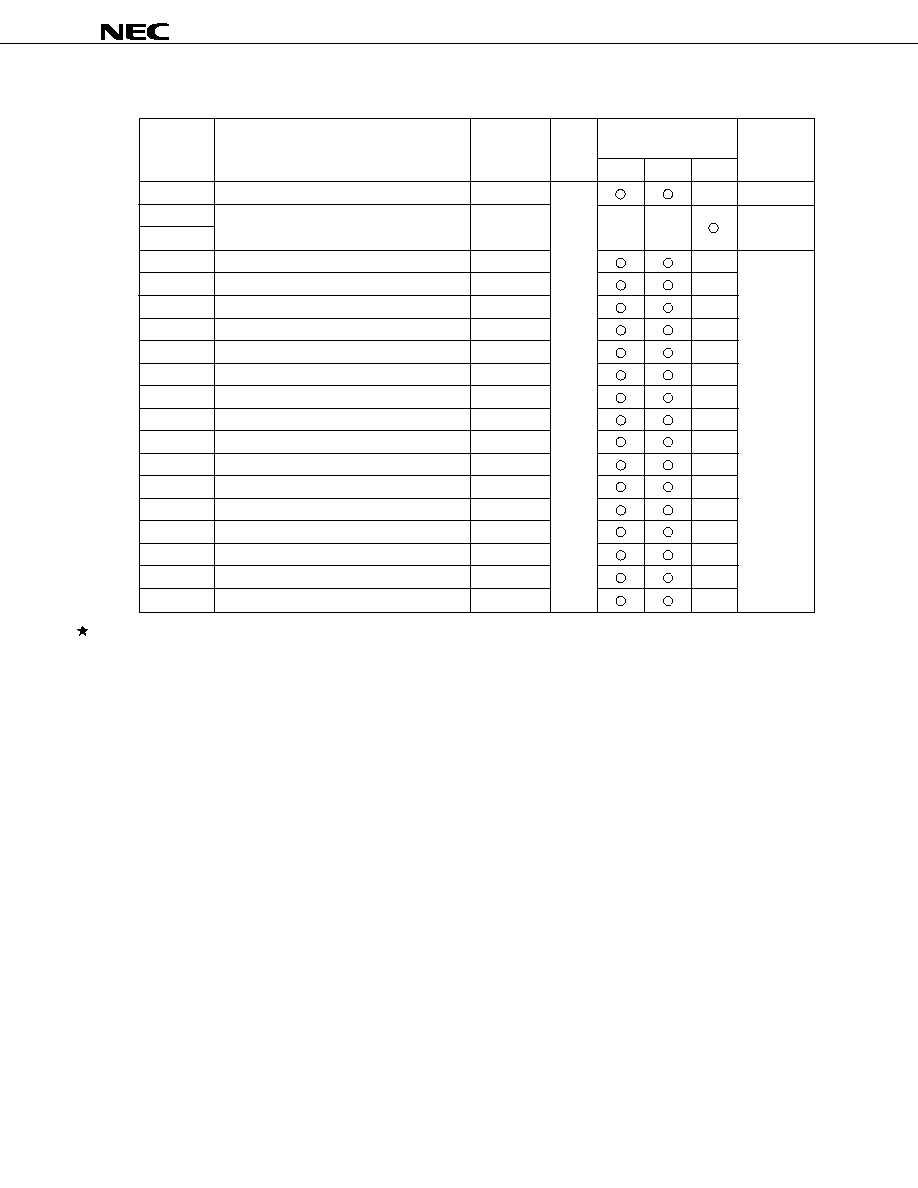

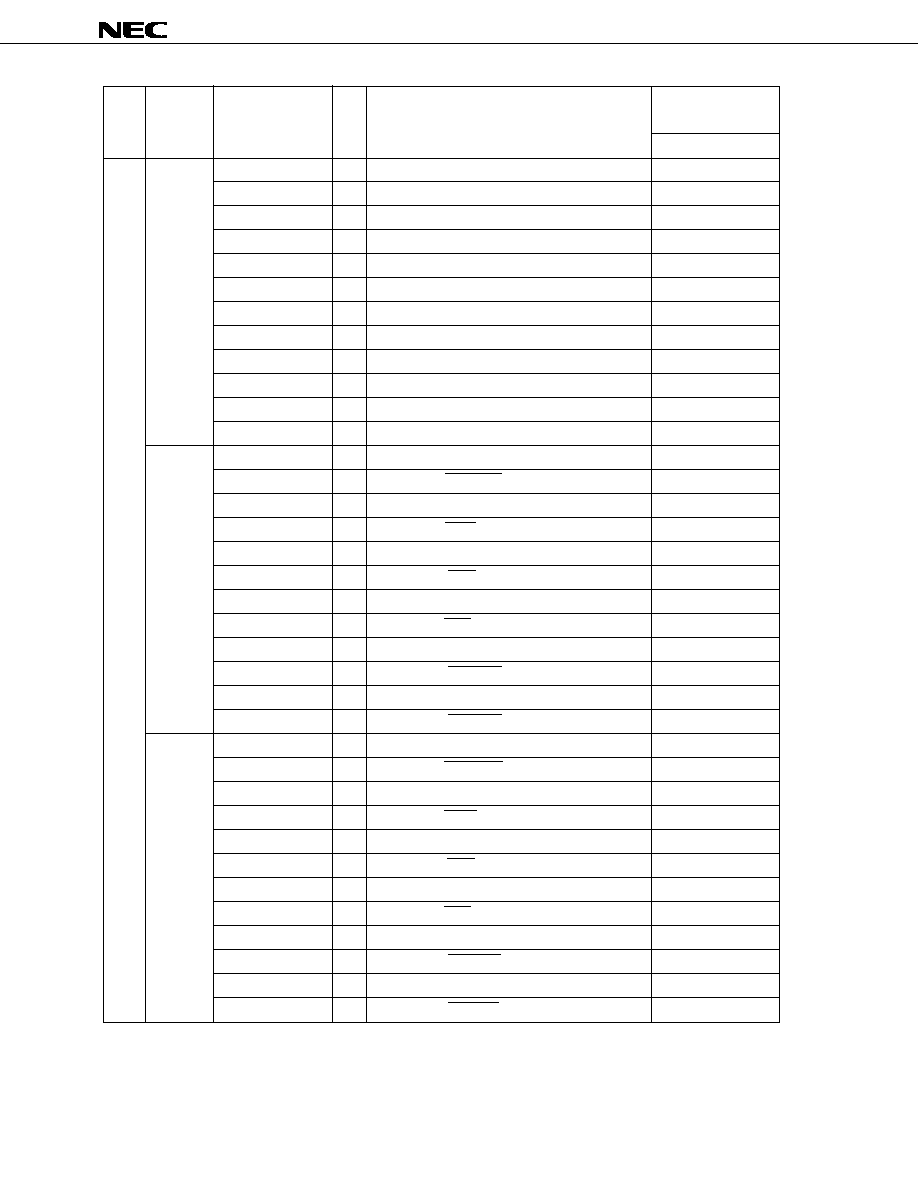

Table 2-1. List of Special Function Registers (3/5)

Bit units for

manipulation

1 bit

8 bits

16 bits

On reset

Address

Special function register (SFR)

Symbol

R/W

FF70H

FF71H

FF72H

FF73H

FF74H

FF75H

FF76H

FF77H

FF78H

FF79H

FF7AH

FF7BH

FF7CH

FF7DH

FF7EH

FF7FH

FF80H

FF82H

FF84H

FF85H

FF86H

FF88H

FF8AH

FF8CH

FF8EH

FFA0H

FFA1H

FFA2H

FFA2H

FFA3H

Slave buffer register 0

Slave buffer register 1

Slave buffer register 2

Slave buffer register 3

Slave buffer register 4

Slave buffer register 5

Master buffer register 0

Master buffer register 1

Master buffer register 2

Master buffer register 3

Master buffer register 4

Master buffer register 5

Timer control register 0

Timer control register 1

Timer control register 2

Timer control register 3

Clocked serial interface mode register

Serial bus interface control register

Baud rate generator control register

Baud rate generator compare register

Serial I/O shift register

Asynchronous serial interface mode register

Asynchronous serial interface status register

Serial receive buffer: UART

Serial transfer shift register: UART

PWM control register 0

PWM control register 1

PWM register 0L

PWM register 0

SBUF0

SBUF1

SBUF2

SBUF3

SBUF4

SBUF5

MBUF0

MBUF1

MBUF2

MBUF3

MBUF4

MBUF5

TMC0

TMC1

TMC2

TMC3

CSIM

SBIC

BRGC

BRG

SIO

ASIM

ASIS

RXB

TXS

PWMC0

PWMC1

PWM0L

PWM0

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

Undefined

00H

Undefined

80H

00H

Undefined

00H

Undefined

Note

Bits 7 and 5

: read/write

Bits 6, 3, and 2 : read-only

Bits 4, 1, and 0 : write-only

R/W

R/W

Note

R/W

R

W

R/W

24

µ

PD78361A, 78362A

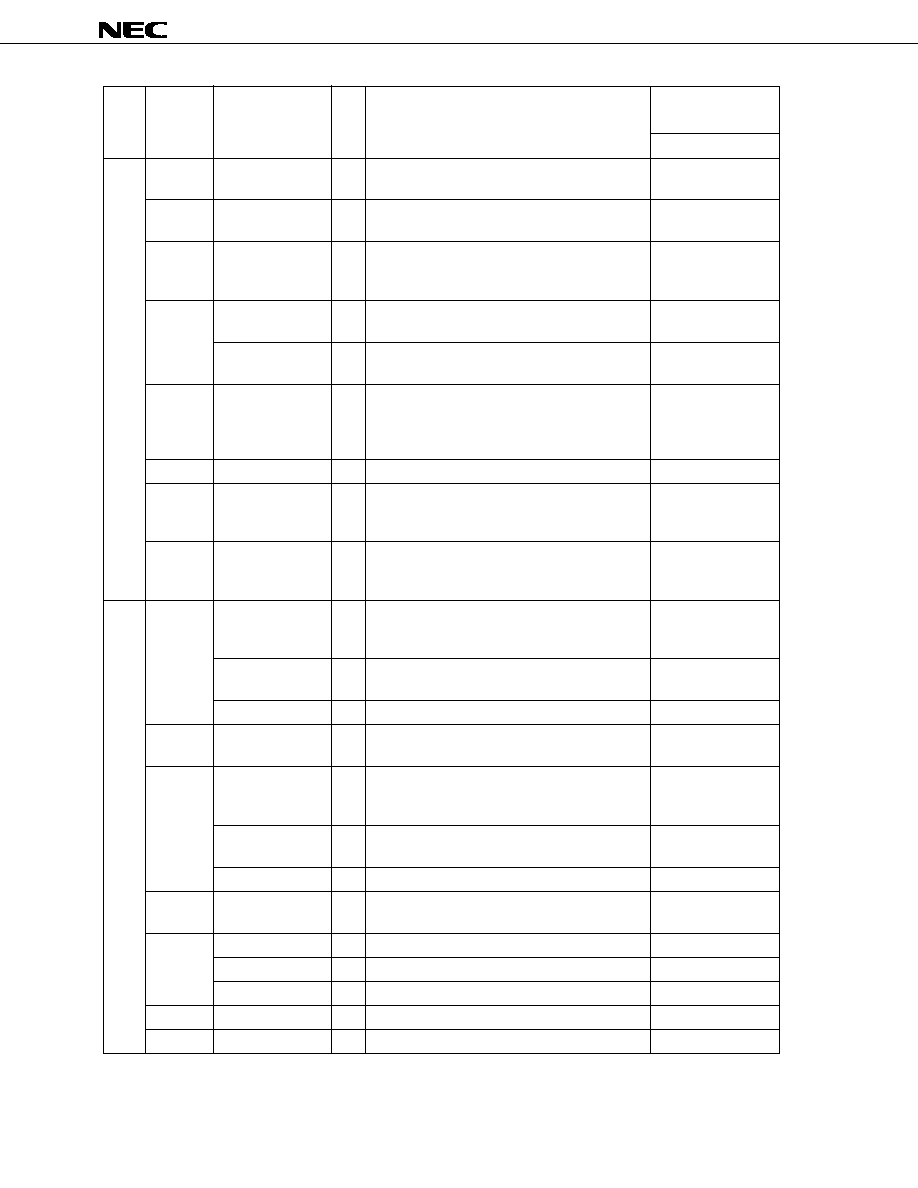

Table 2-1. List of Special Function Registers (4/5)

Bit units for

manipulation

1 bit

8 bits

16 bits

On reset

Address

Special function register (SFR)

Symbol

R/W

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

PWM1L

PWM1

ISPR

IMC

MK0L

MK0

MK0H

ADCR0

ADCR0H

ADCR1

ADCR1H

ADCR2

ADCR2H

ADCR3

ADCR3H

ADCR4

ADCR4H

ADCR5

ADCR5H

ADCR6

ADCR6H

ADCR7

ADCR7H

STBC

Note

WDM

Note

R/W

R

R/W

R

R/W

Undefined

00H

80H

FFH

FFFFH

FFH

Undefined

0000

◊

000B

00H

FFA4H

FFA4H

FFA5H

FFA8H

FFAAH

FFACH

FFACH

FFADH

FFADH

FFB0H

FFB1H

FFB1H

FFB2H

FFB3H

FFB3H

FFB4H

FFB5H

FFB5H

FFB6H

FFB7H

FFB7H

FFB8H

FFB9H

FFB9H

FFBAH

FFBBH

FFBBH

FFBCH

FFBDH

FFBDH

FFBEH

FFBFH

FFBFH

FFC0H

FFC2H

PWM register 1L

PWM register 1

In-service priority register

Interrupt mode control register

Interrupt mask register 0L

Interrupt mask register 0

Interrupt mask register 0H

A/D conversion result register 0

A/D conversion result register 0H

A/D conversion result register 1

A/D conversion result register 1H

A/D conversion result register 2

A/D conversion result register 2H

A/D conversion result register 3

A/D conversion result register 3H

A/D conversion result register 4

A/D conversion result register 4H

A/D conversion result register 5

A/D conversion result register 5H

A/D conversion result register 6

A/D conversion result register 6H

A/D conversion result register 7

A/D conversion result register 7H

Standby control register

Watchdog timer mode register

Note

Can be written when a special instruction is executed.

25

µ

PD78361A, 78362A

Table 2-1. List of Special Function Registers (5/5)

Bit units for

manipulation

1 bit

8 bits

16 bits

On reset

Address

Special function register (SFR)

Symbol

R/W

Note

C0AAH

43H

Memory expansion mode register

Programmable wait control register

Interrupt control register (INTOV3)

Interrupt control register (INTP0/INTCC30)

Interrupt control register (INTP1)

Interrupt control register (INTP2)

Interrupt control register (INTP3/INTCC20)

Interrupt control register (INTP4)

Interrupt control register (INTTM0)

Interrupt control register (INTCM03)

Interrupt control register (INTCM10)

Interrupt control register (INTCM40)

Interrupt control register (INTCM41)

Interrupt control register (INTSER)

Interrupt control register (INTSR)

Interrupt control register (INTST)

Interrupt control register (INTCSI)

Interrupt control register (INTAD)

FFC4H

FFC6H

FFC7H

FFE0H

FFE1H

FFE2H

FFE3H

FFE4H

FFE5H

FFE6H

FFE7H

FFE8H

FFE9H

FFEAH

FFEBH

FFECH

FFEDH

FFEEH

FFEFH

MM

PWC

OVIC3

PIC0

PIC1

PIC2

PIC3

PIC4

TMIC0

CMIC03

CMIC10

CMIC40

CMIC41

SERIC

SRIC

STIC

CSIIC

ADIC

R/W

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

≠

Note

The value of the MM register on reset differs depending on the product.

µ

PD78361A ∑∑∑∑ 20H

µ

PD78362A ∑∑∑∑ 60H

26

µ

PD78361A, 78362A

3.

FUNCTIONAL BLOCKS

3.1

EXECUTION UNIT (EXU)

EXU controls address computation, arithmetic and logical operations, and data transfer through microprogram.

EXU has an internal main RAM. This RAM can be accessed by instructions faster than the peripheral RAM.

3.2

BUS CONTROL UNIT (BCU)

BCU starts necessary bus cycles according to the physical address obtained by the execution unit (EXU).If

EXU does not request start of the bus cycle, an address is generated to prefetch an instruction. The prefetched

op code is stored in an instruction queue.

3.3

ROM/RAM

Internal ROM and RAM capacities differ depending on the product.

The

µ

PD78361A has a 32K-byte ROM and a 1792-byte peripheral RAM.

The

µ

PD78362A has a 24K-byte ROM and a 512-byte peripheral RAM.

3.4

PORT FUNCTIONS

The

µ

PD78362A is provided with the ports shown in Figure 3-1 for various control operations.

The functions of each port are listed in Table 3-1. These ports function not only as digital ports but also as

input/output lines of the internal hardware.

Figure 3-1. Port Configuration

P00

P07

P20

P25

P30

P34

8

8

P50

P57

P70-P77

P80

P85

P90

P92

P40-P47

Port 0

Port 2

Port 3

Port 4

Port 5

Port 8

Port 7

Port 9

27

µ

PD78361A, 78362A

Table 3-1. Functions of Each Port

8-bit I/O port. Can be set in input or

output mode in 1-bit units.

6-bit input port.

5-bit I/O port. Can be set in input or

output in 1-bit units.

8-bit I/O port. Can be set in input or

output mode in 8-bit units.

8-bit I/O port. Can be set in input or

output mode in 1-bit units.

8-bit input port.

6-bit I/O port. Can be set in input or

output mode in 1-bit units.

3-bit I/O port. Can be set in input or

output mode in 1-bit units.

In control mode, serves as real-time output port (RTP), or

input operation control signal of real-time pulse unit (RPU)

and output PWM signal.

Inputs external interrupt and count pulse of real-time pulse

unit (RPU) (fixed to the control mode).

In control mode, inputs/outputs signals of serial interfaces

(UART, CSI).

--

--

Input analog signals to A/D converter (fixed to the control

mode).

In control mode, outputs timer of real-time pulse unit (RPU).

--

Port

Port function

Multiplexed function

Port 0

Port 2

Port 3

Port 4

Port 5

Port 7

Port 8

Port 9

28

µ

PD78361A, 78362A

3.5

CLOCK GENERATOR CIRCUIT

The clock generator circuit generates and controls the internal system clock (CLK) that is supplied to the CPU.

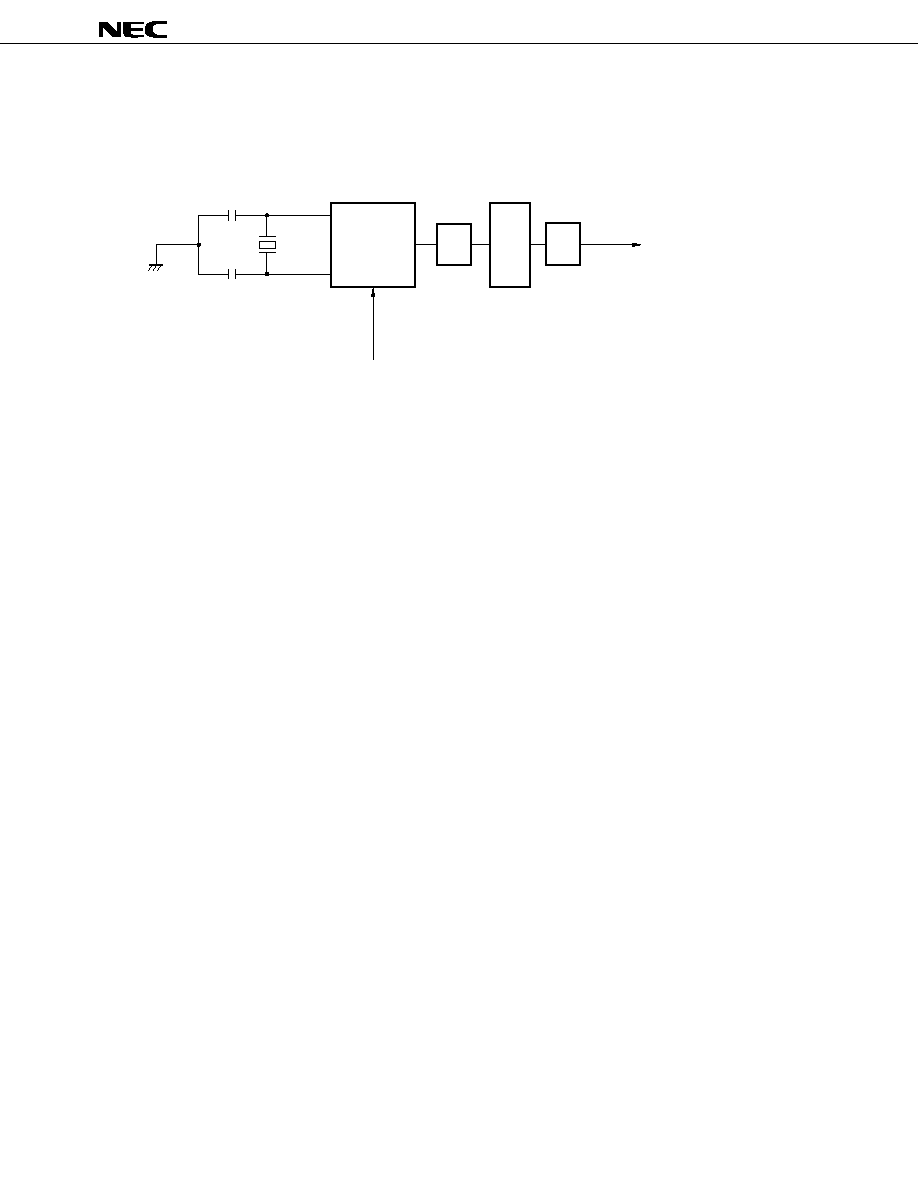

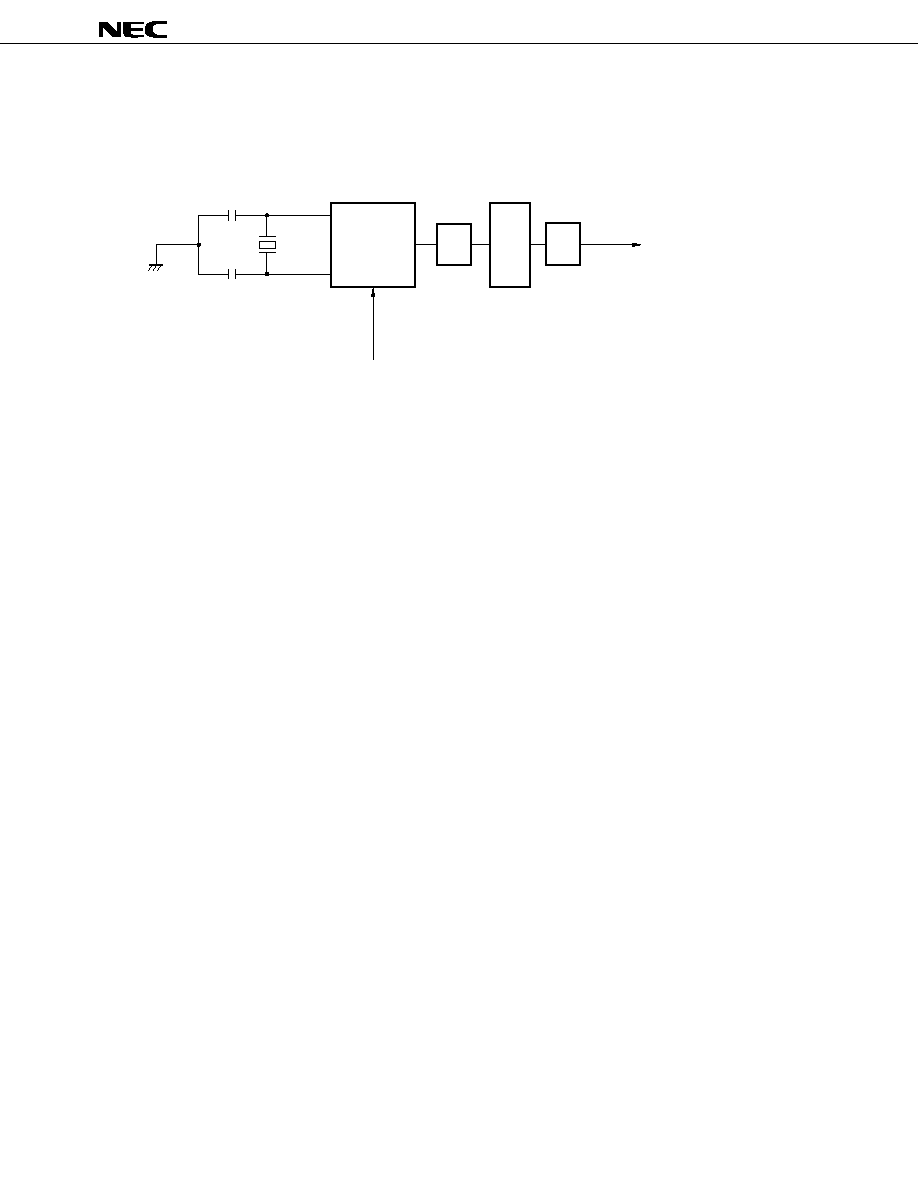

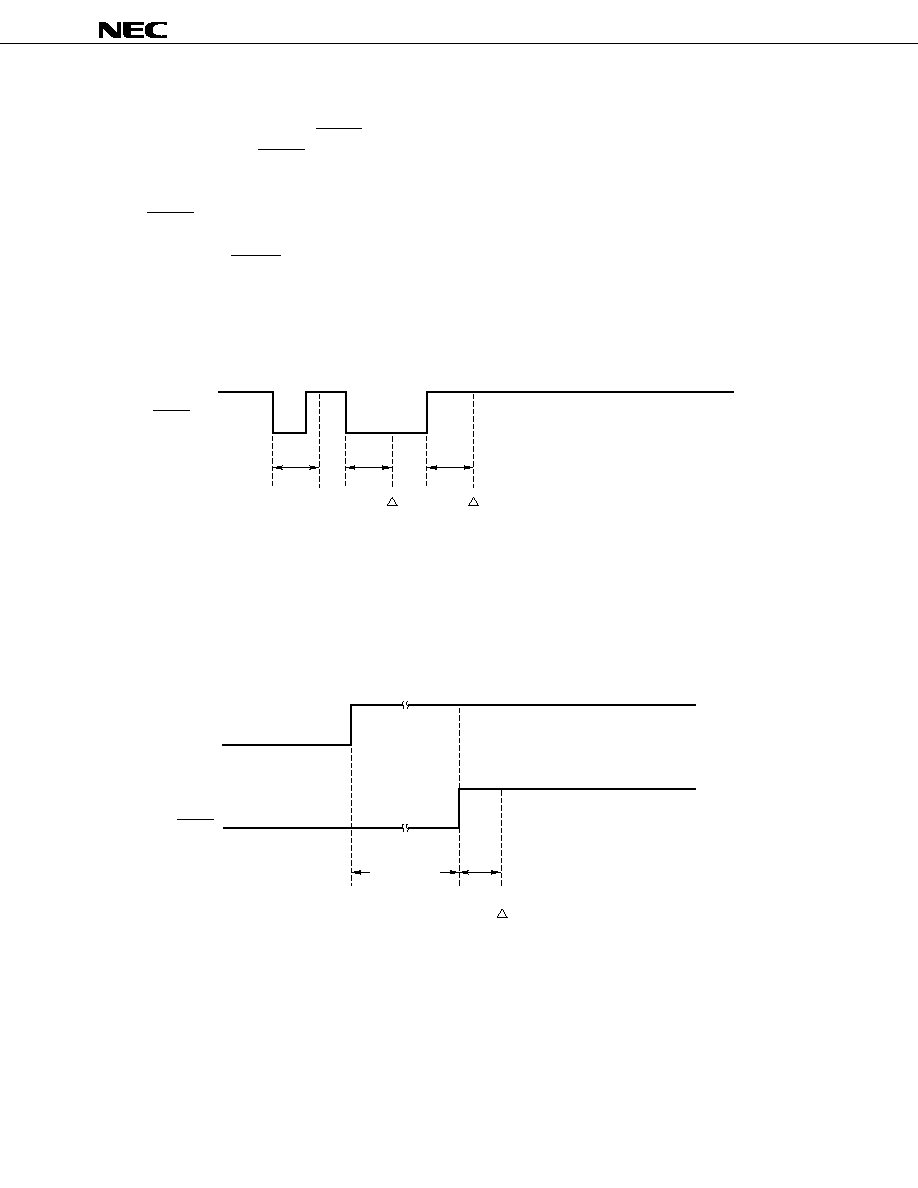

Figure 3-2. Block Diagram of Clock Generator Circuit

Remarks 1.

f

XX

: crystal oscillation frequency

2.

f

X

: external clock frequency

3.

f

CLK

: internal system clock frequency

By connecting an 8-MHz crystal resonator across the X1 and X2 pins, an internal system clock of up to 16

MHz (f

CLK

) can be generated.

The system clock oscillation circuit oscillates by using the crystal resonator connected across the X1 and

X2 pins. It stops oscillation in standby mode.

An external clock can also be input. To do so, input the clock signal to the X1 pin and leave the X2 pin open.

Caution

Do not set STOP mode when the external clock is used.

X1

X2

f

XX

or

f

X

f

CLK

1/2

System

cloock

oscillator

circuit

Internal system

clock (CLK)

STOP mode

Frequency

divider

1/2

PLL

control

circuit

Frequency

divider

29

µ

PD78361A, 78362A

Cautions 1. Wire the portion enclosed by dotted line in Figure 3-3 as follows to avoid adverse

influences due to wiring capacity when using the system clock oscillation circuit.

∑ Keep the wiring length as short as possible.

∑ Do not cross the wiring with the other signal line. Make sure that the wiring is not close

to lines through which a high alternating current flows.

∑ Always keep the ground point of the capacitor of the oscillation circuit at the same

potential as V

SS

. Do not ground the circuit to a ground pattern through which a high

current flows.

∑ Do not extract signals from the oscillator circuit.

2. To input an external clock, do not connect a load such as wiring capacitance to the X2

pin.

Figure 3-3. External Circuit of System Clock Oscillator Circuit

(a) crystal oscillator

(b) external clock

PD78362A

µ

V

SS

X1

X2

PD78362A

µ

X1

X2

Open

30

µ

PD78361A, 78362A

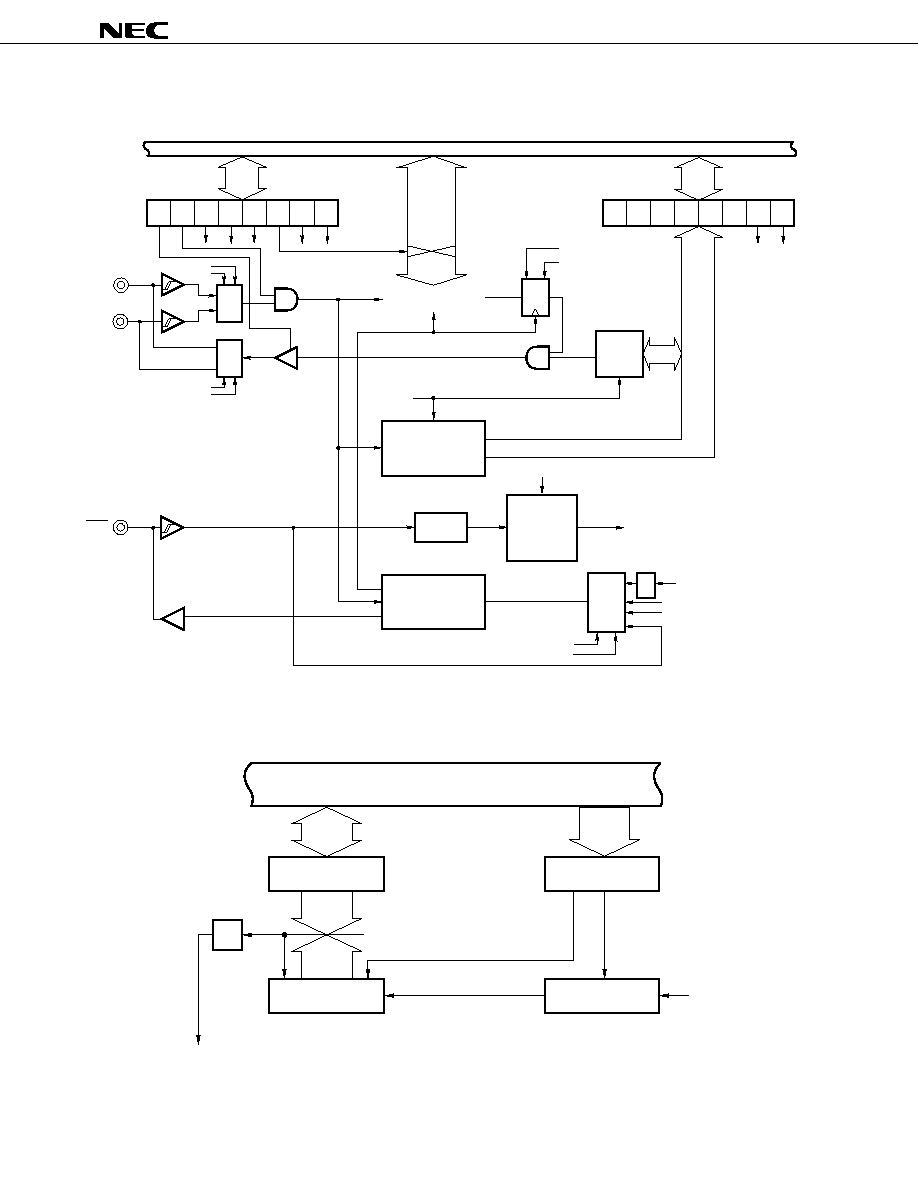

3.6

REAL-TIME PULSE UNIT (RPU)

The real-time pulse unit (RPU) can measure pulse intervals and frequencies, and output programmable

pulses (six channels of PWM control signals).

The RPU consists of five 16-bit timers (timers 0 through 4), of which one is provided with a 10-bit dead time

timer, which is ideal for inverter control. In addition, a function to turn off the output by the software or an external

interrupt is also provided.

Each timer has the following features:

∑

Timer 0 : Controls the PWM period of the TO00 through TO05 pins. In addition, operates as a

general-purpose interval timer. Timer 0 has the following five operation modes:

General-purpose interval timer mode

PWM mode 0 (symmetrical triangular wave)

PWM mode 0 (asymmetrical triangular wave)

PWM mode 0 (saw-tooth wave)

PWM mode 1

∑

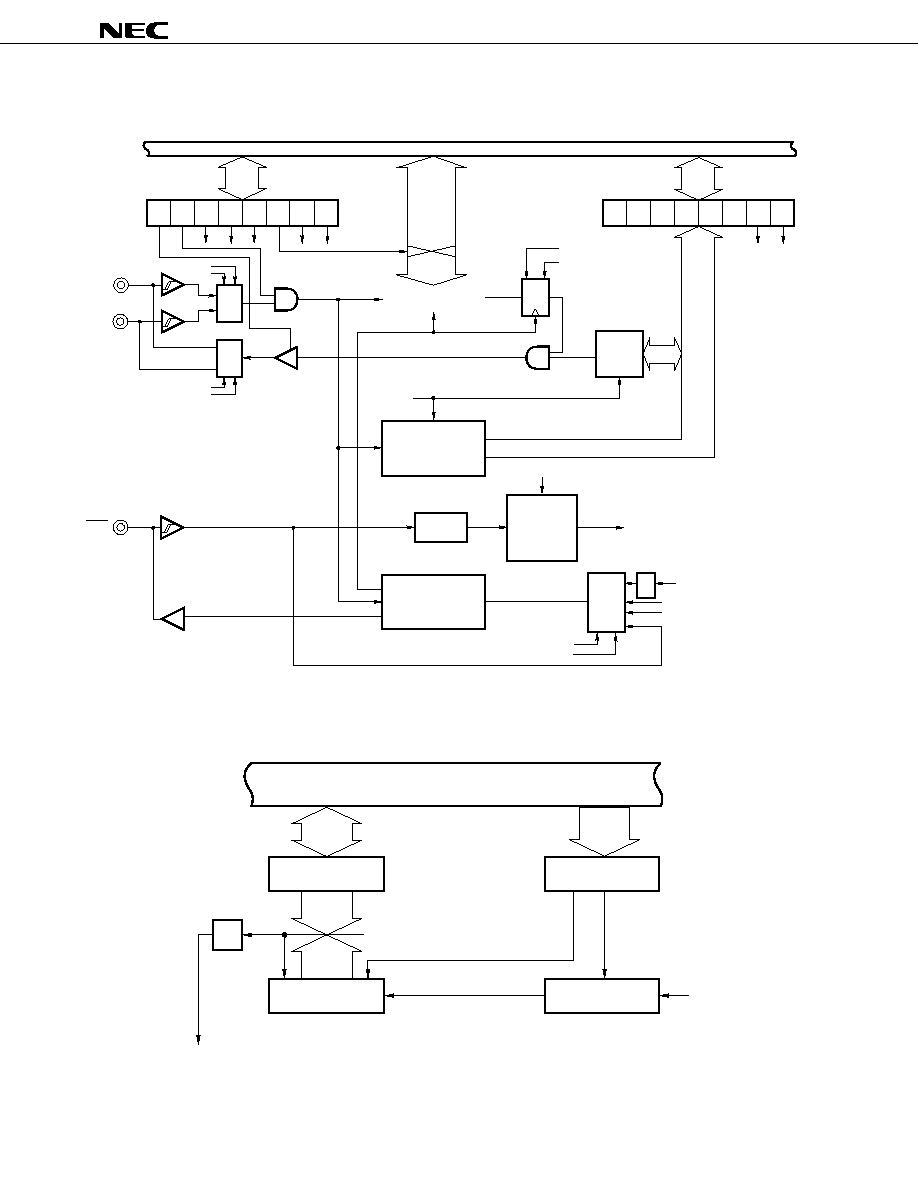

Timer 1 : Operates as a general-purpose interval timer.

∑

Timers 2 & 3 : Has a programmable input sampling circuit that rejects the noise of an input signal,

and a capture function.

∑

Timer 4 : Operates as a general-purpose timer or an up-down counter. When operating as a general-

purpose timer, controls the PWM cycle of the TO40 output pin. Timer 4 has the following

two operation modes:

General-purpose timer mode

Up/down counter mode (UDC mode)

The RPU consists of the hardware shown in Table 3-2. Figures 3-4 through 3-12 show the block diagrams

of the respective timers.

Table 3-2. Configuration of Real-Time Pulse Unit (RPU)

16-bit compare register (CM00)

≠

16-bit compare register (CM01)

≠

16-bit compare register (CM02)

≠

16-bit compare register (CM03)

INTCM03

16-bit compare register (CM10)

INTCM10

16-bit capture/compare register (CC20)

INTCC20

16-bit capture register (CT20)

≠

16-bit capture/compare register (CC30)

INTCC30

16-bit capture register (CT30)

≠

16-bit capture register (CT31)

≠

16-bit compare register (CM40)

INTCM40

16-bit compare register (CM41)

INTCM41

Timer 0 16-bit timer (TM0)

Timer 1 16-bit timer (TM1)

Timer 2 16-bit timer (TM2)

Timer 3 16-bit timer (TM3)

Timer 4 16-bit timer (TM4)

Compare

register

coincidence

interrupt

Capture

trigger

Timer

output

Timer

clear

≠

6

INTCM03

≠

≠

INTCM10

INTP3

≠

INTCC20

INTP0

INTP1

≠

INTCC30

INTP4

TCLRUD

INTCM40

≠

1

Timer register

Register

31

µ

PD78361A, 78362A

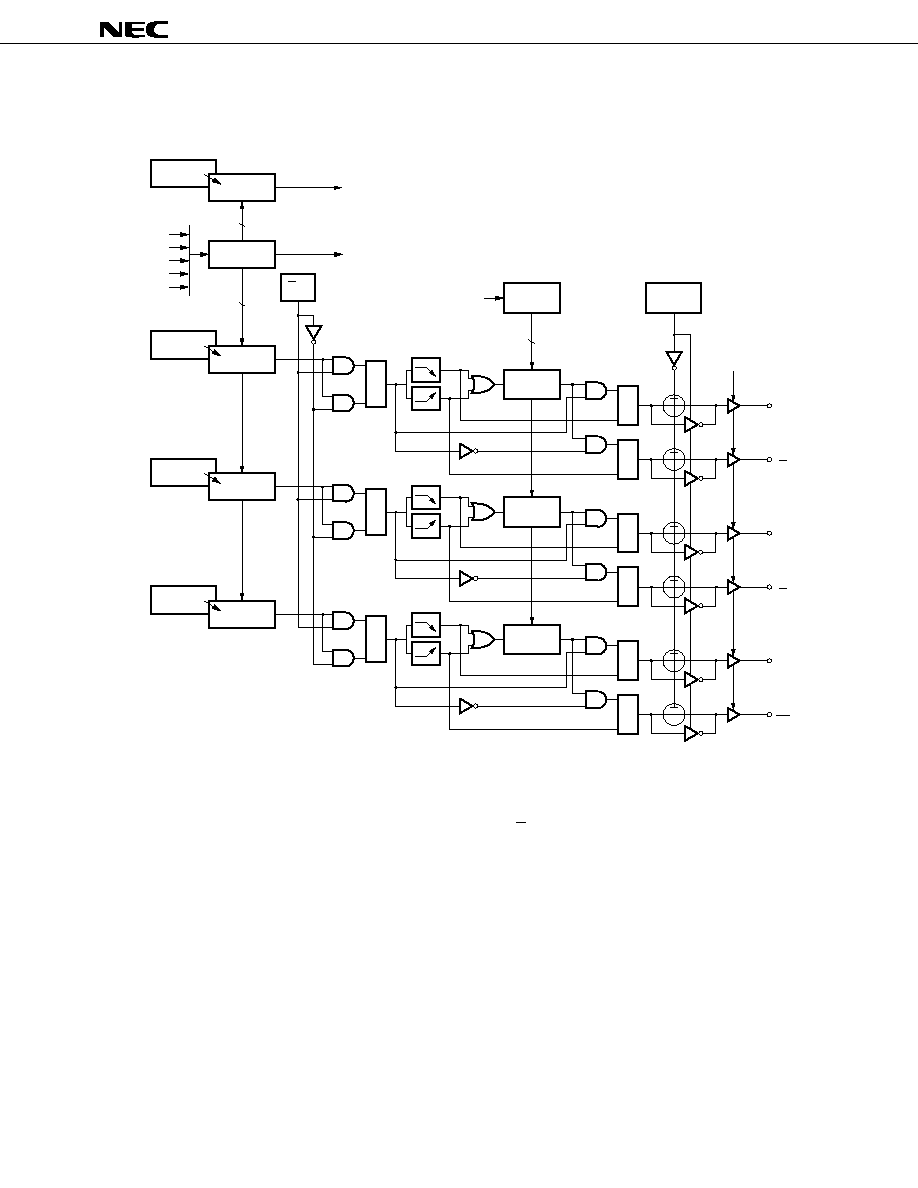

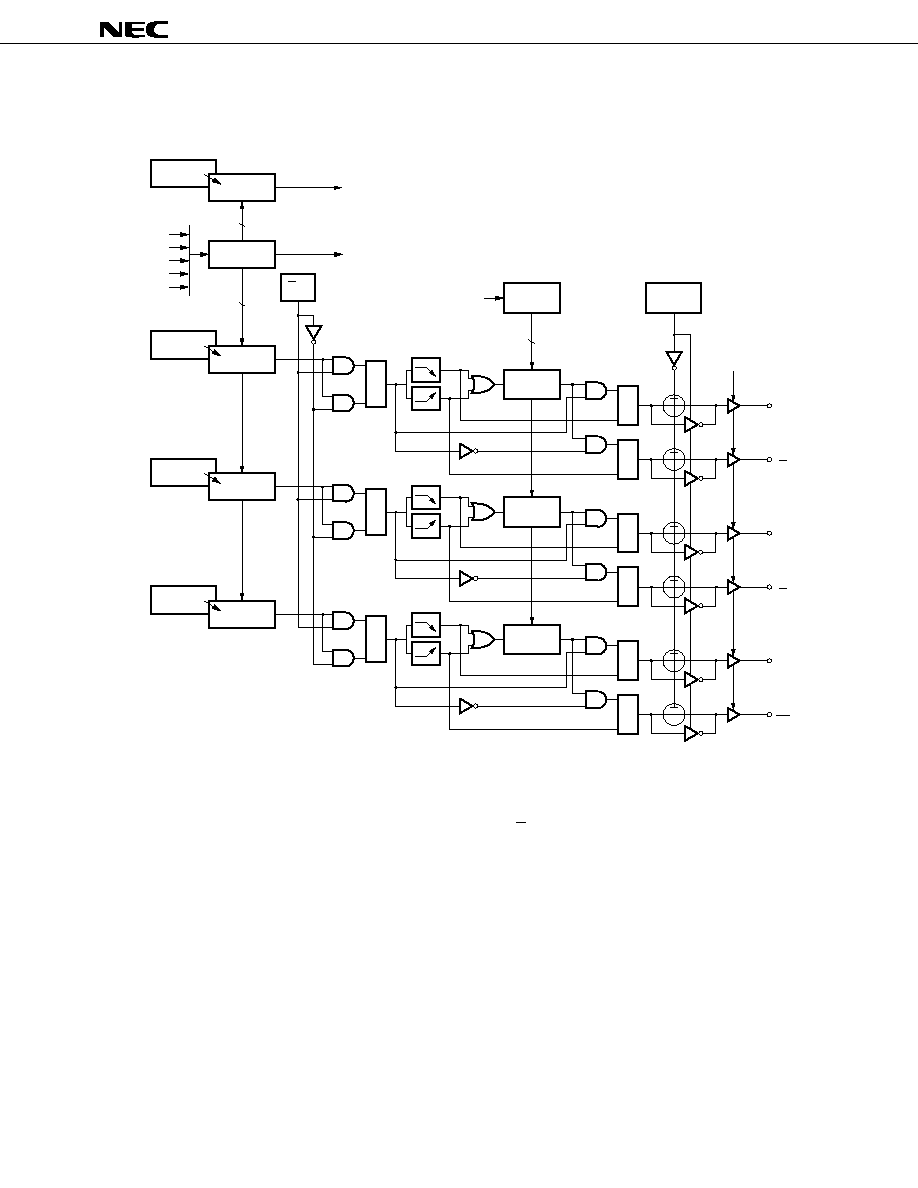

Figure 3-4. Block Diagram of Timer 0 (PWM mode 0 ... symmetrical triangular wave, asymmetrical

triangular wave)

TM0

: Timer register

ALVT0 : Bit 2 of TUM0 register

CM00-CM03

: Compare registers

U/D N : Bit 3 of TMC0 register

BFCM00-BFCM03 : Buffer registers

DTIME

: Reload register

DTM0-DTM2

: Dead time timers

Remark f

CLK

: internal system clock

BFCM03

CM03

TM0

BFCM00

CM00

R

S

DTM0

R

S

TO00

(U phase)

Underflow

R

S

TO01

(U phase)

BFCM01

CM01

R

S

DTM1

R

S

TO02

(V phase)

Underflow

R

S

TO03

(V phase)

BFCM02

CM02

R

S

DTM2

R

S

TO04

(W phase)

Underflow

R

S

TO05

(W phase)

INTCM03

INTTM0

16

16

f

CLK

f

CLK

/2

f

CLK

/4

f

CLK

/8

f

CLK

/16

U/D

UP = 0

DOWN = 1

DTIME

f

CLK

10

ALVTO

Output off function

by external interrupt

and software

32

µ

PD78361A, 78362A

Figure 3-5. Block Diagram of Timer 0 (PWM mode 0 ... saw-tooth wave)

TM0

: Timer register

CM00-CM03

: Compare registers

BFCM00-BFCM03 : Buffer registers

DTIME

: Reload register

DTM0-DTM2

: Dead time timers

ALVT0

: Bit 2 of TUM0 register

Remark f

CLK

: internal system clock

BFCM03

CM03

TM0

BFCM00

CM00

R

S

DTM0

R

S

TO00

(U phase)

Underflow

R

S

TO01

(U phase)

BFCM01

CM01

R

S

DTM1

R

S

TO02

(V phase)

Underflow

R

S

TO03

(V phase)

BFCM02

CM02

R

S

DTM2

R

S

TO04

(W phase)

Underflow

R

S

TO05

(W phase)

INTCM03

16

16

f

CLK

f

CLK

/2

f

CLK

/4

f

CLK

/8

f

CLK

/16

DTIME

f

CLK

10

ALVTO

Output off function

by external interrupt

and software

Clear

33

µ

PD78361A, 78362A

Figure 3-6. Block Diagram of Timer 0 (PWM mode 1)

TM0

: Timer register

MBUF0-MBUF5 : Master buffer registers

CM00-CM03

: Compare registers

SBUF0-SBUF5 : Slave buffer registers

BFCM00-BFCM03 : Buffer registers

TOUT

: Timer out register

DTIME

: Reload register

DTM0-DTM2

: Dead time timers

Remark f

CLK

: internal system clock

MBUF1

MBUF0

MBUF3

MBUF2

MBUF5

MBUF4

BFCM03

CM03

TM0

BFCM00

CM00

BFCM01

CM01

BFCM02

CM02

INTCM03

16

16

f

CLK

f

CLK

/2

f

CLK

/4

f

CLK

/8

f

CLK

/16

Clear

DTM0

DTIME

T

DTM1

T

DTM2

T

10

f

CLK

Underflow

Underflow

Underflow

SBUF1

SBUF0

SBUF3

SBUF2

SBUF5

SBUF4

6-bit buffer

register

6-bit buffer

register

6-bit write-only

register

TOUT

Output off function

by external interrupt

and software

TO00

(U phase)

TO02

(V phase)

TO04

(W phase)

TO01

(U phase)

TO03

(V phase)

TO05

(W phase)

34

µ

PD78361A, 78362A

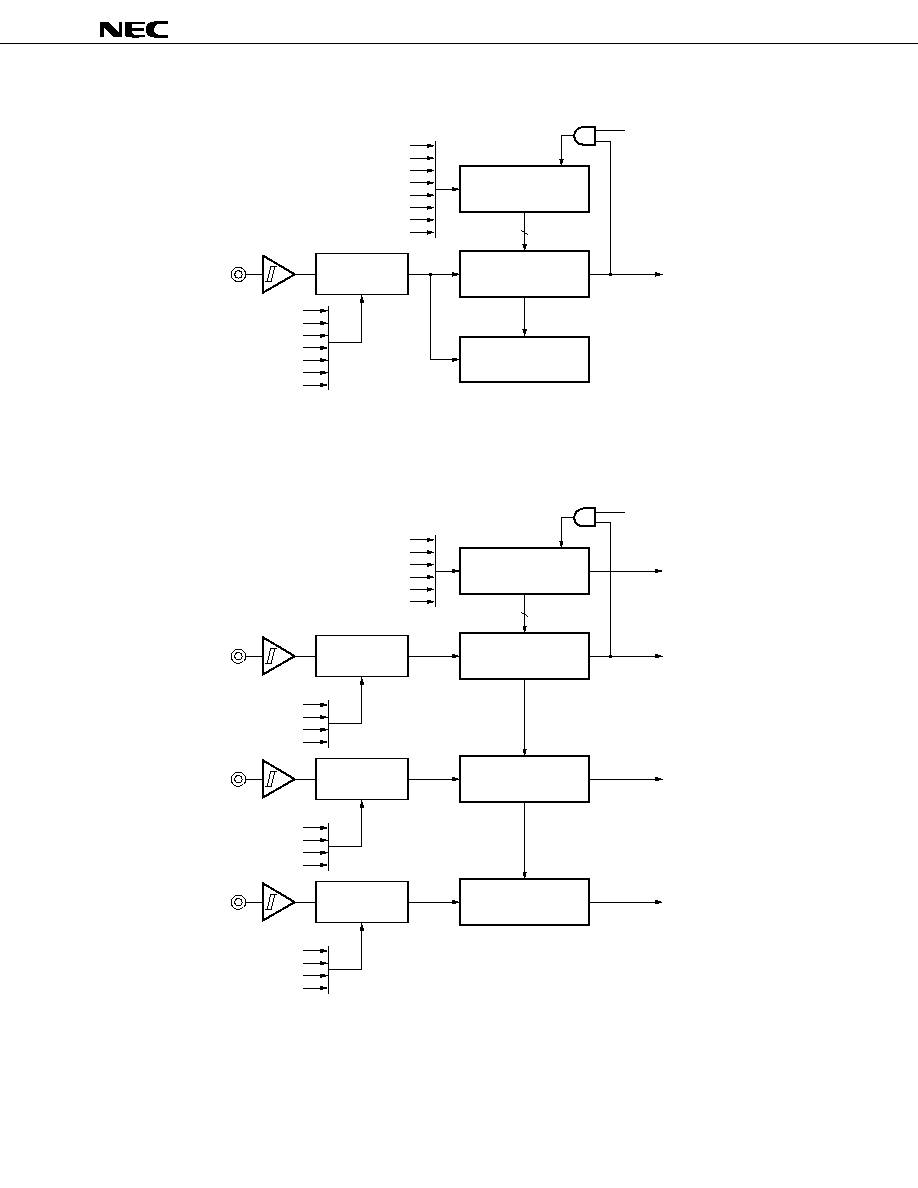

Figure 3-7. Block Diagram of Timer 0 (general-purpose interval timer mode)

Figure 3-8. Block Diagram of Timer 1

Remark f

CLK

: internal system clock

Compare register

CM03

Timer register

TM0

16

Master buffer register

(MBUF0)

Slave buffer register

(SBUF0)

Timer out register

(TOUT)

6

6

INTCM03

Clear

Output off function by external

interrupt and software

TO00

TO02

TO04

TO01

TO03

TO05

f

CLK

/4

f

CLK

/8

f

CLK

/16

TI

INTCM10

Clear

16

Timer register

TM1

Compare register

CM10

35

µ

PD78361A, 78362A

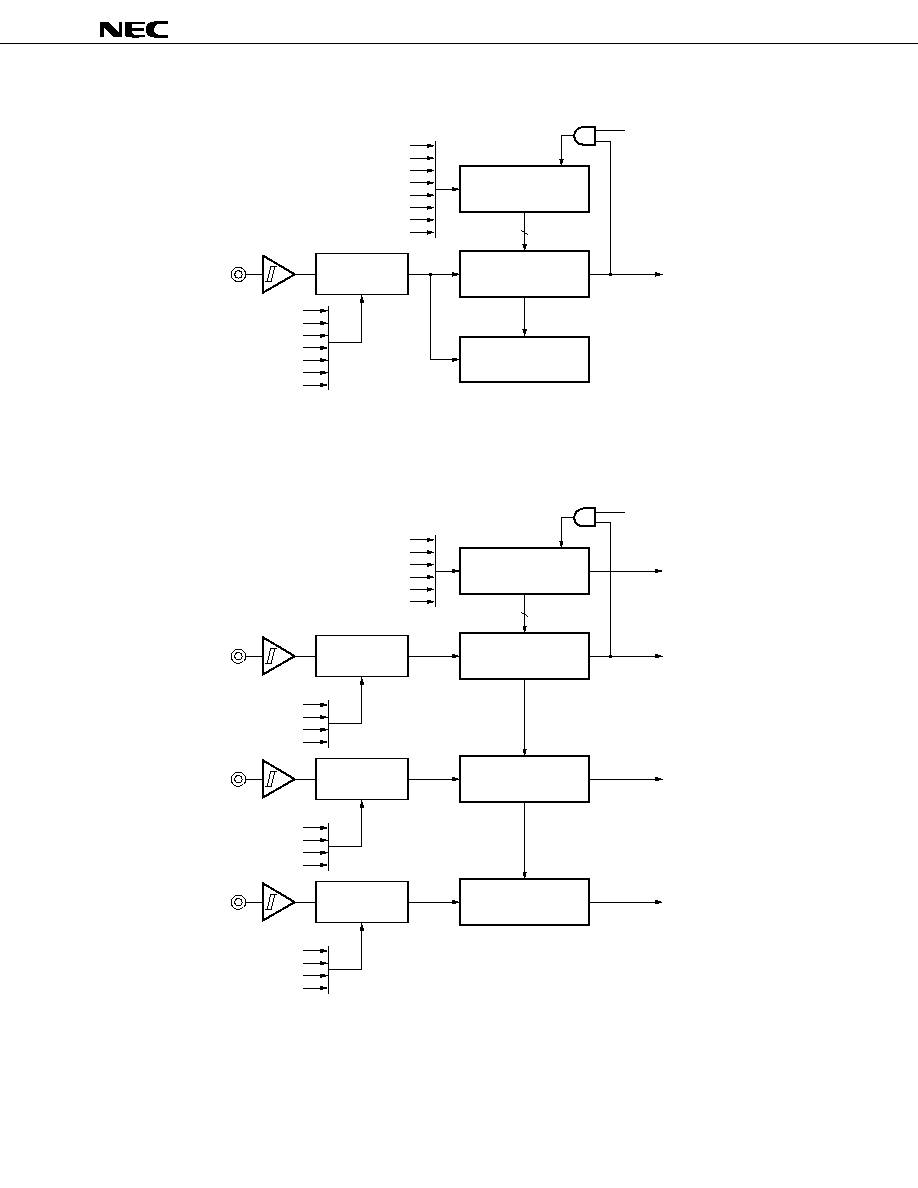

Figure 3-9. Block Diagram of Timer 2

Remark f

CLK

: internal system clock

Figure 3-10. Block Diagram of Timer 3

Remark f

CLK

: internal system clock

4-point sampling

noise rejection

circuit

Timer register TM2

Capture/compare

register CC20

Capture register CT20

16

f

CLK

/2

2

f

CLK

/2

3

f

CLK

/2

4

f

CLK

/2

5

f

CLK

/2

6

f

CLK

/2

8

f

CLK

/2

9

f

CLK

/2

10

f

CLK

f

CLK

/2

2

f

CLK

/2

3

f

CLK

/2

4

f

CLK

/2

6

f

CLK

/2

7

f

CLK

/2

8

CLR2

INTP3/INTCC20

INTP3

Clear

4-point sampling

noise rejection

circuit

Timer register TM3

Capture/compare

register CC30

16

f

CLK

/2

2

f

CLK

/2

3

f

CLK

/2

4

f

CLK

/2

5

f

CLK

/2

6

f

CLK

/2

8

f

CLK

f

CLK

/2

2

f

CLK

/2

3

f

CLK

/2

4

CLR3

INTP0/INTCC30

INTP0

4-point sampling

noise rejection

circuit

Capture register CT30

f

CLK

f

CLK

/2

2

f

CLK

/2

3

f

CLK

/2

4

INTP1

INTP1

4-point sampling

noise rejection

circuit

f

CLK

f

CLK

/2

2

f

CLK

/2

3

f

CLK

/2

4

INTP4

INTP4

INTOV3

Clear

Capture register CT31

36

µ

PD78361A, 78362A

Figure 3-11. Block Diagram of Timer 4 (General-Purpose Timer Mode)

Remark f

CLK

: internal system clock

Figure 3-12. Block Diagram of Timer 4 (UDC Mode)

Remark f

CLK

: internal system clock

f

CLK

f

CLK

/2

f

CLK

/4

f

CLK

/8

f

CLK

/16

f

CLK

/32

Timer register

TM4

Compare register

CM40

Compare register

CM41

Clear

INTCM40

Q

S

16

R

INTCM41

ALV40

TO40

f

CLK

/4

f

CLK

/8

f

CLK

/16

Timer register

TM4

INTCM40

TCLRUD

Compare register

CM40

Compare register

CM41

Up/down

detector

TIUD

Clear

16

INTCM41

TCUD

OVF

UDF

37

µ

PD78361A, 78362A

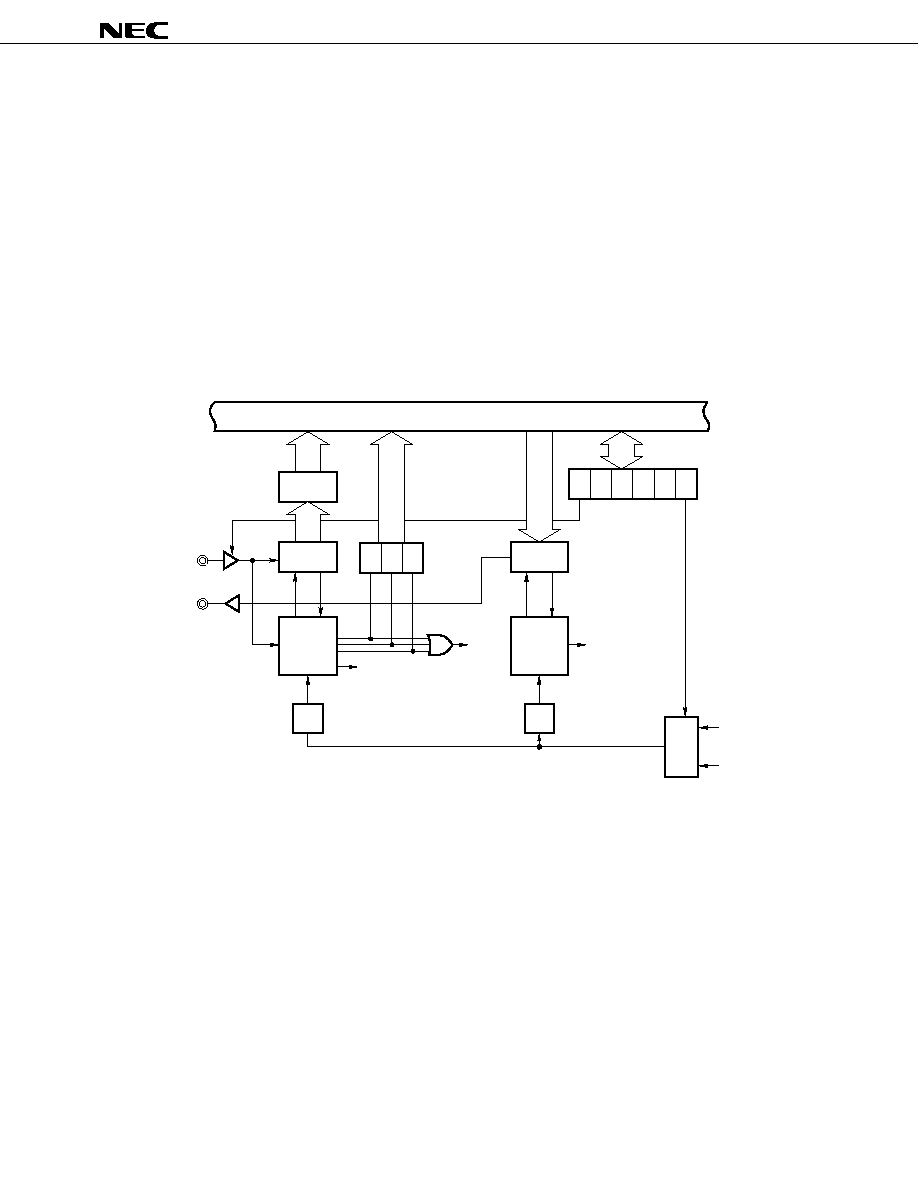

3.7

REAL-TIME OUTPUT PORT (RTP)

The real-time output port is a 4-bit port that can output the contents of the real-time output port register (RTP)

in synchronization with the trigger signal from the real-time pulse unit (RPU). It can output synchronization

pulses of multiple channels.

Also, PWM modulation can be applied to P00-P03.

Figure 3-13. Block Diagram of Real-Time Output Port

4

4

RTP

P03P02 P01P00

PWM0

PWM1

Internal bus

INTCM03 (from RPU)

INTCM10 (from RPU)

INTP0/INTCC30 (from RPU)

Software trigger

Output trigger

control circuit

RTPM

PWM signal

control circuit

Output latch

(P03-P00)

38

µ

PD78361A, 78362A

3.8

A/D CONVERTER

The

µ

PD78362A contains a high-speed, high-resolution 10-bit analog-to-digital (A/D) converter (conversion

time 12.6

µ

s at an internal clock frequency of 16 MHz). Successive approximation type is adopted. This

converter is provided with eight analog input lines (ANI0-ANI7) and can perform various operations as the

application requires, in select, scan, and mixed modes.

When A/D conversion ends, an internal interrupt (INTAD) occurs. This interrupt can start a macro service

that executes automatic data transfer through hardware.

Figure 3-14. Block Diagram of A/D Converter

ADCR0

ADCR1

ADCR2

ADCR3

ADCR4

ADCR5

ADCR6

ADCR7

ADM (8)

10

8

9

9

0

0

10

10

ANI0

ANI1

ANI2

ANI3

ANI4

ANI5

ANI6

ANI7

INTCM03

INTP2

AV

DD

AV

REF

AV

SS

SAR (10)

Input curcuit

Sample & hold

Resistor

string

Comparator

Controller

(Start trigger)

Internal bus

39

µ

PD78361A, 78362A

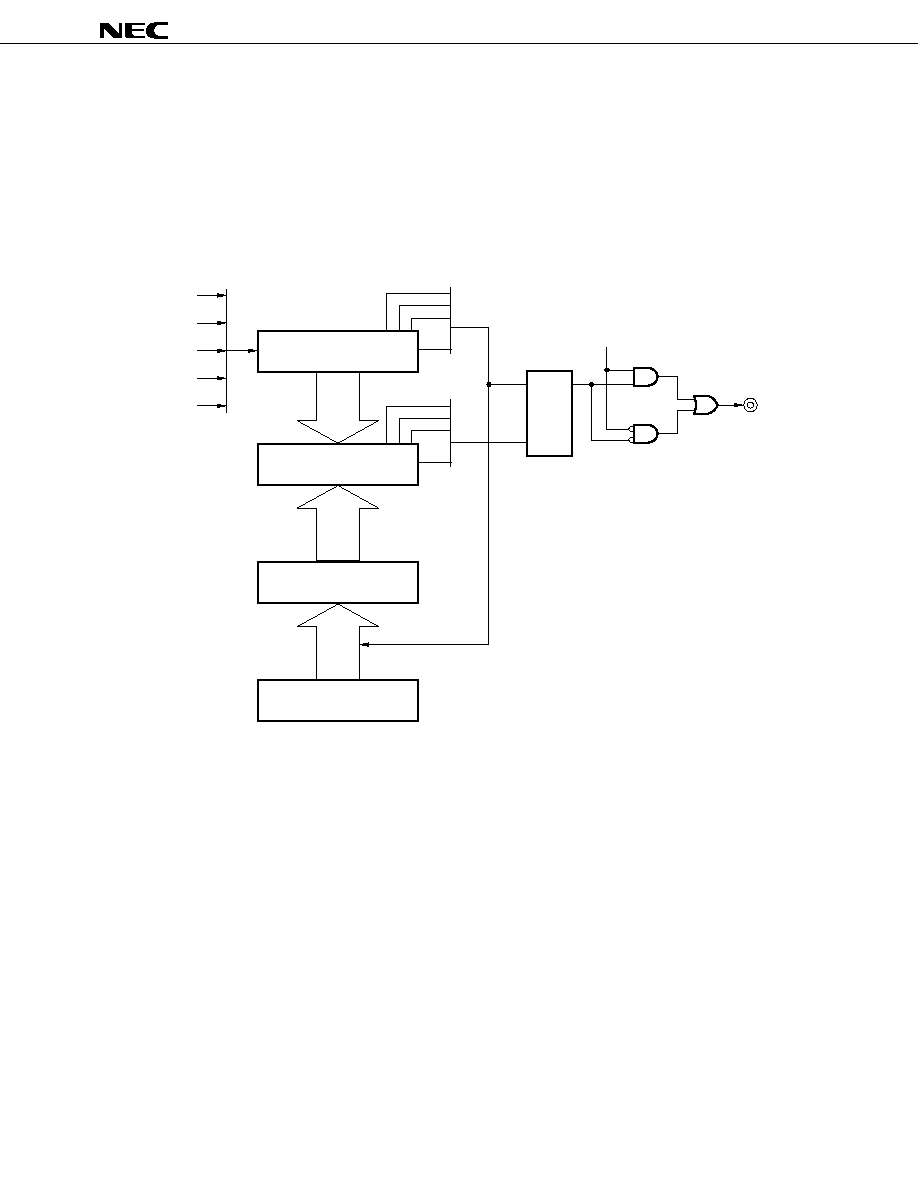

3.9

SERIAL INTERFACE

The

µ

PD78362A is provided with the following two independent serial interfaces:

∑

Asynchronous serial interface (UART)

∑

Clocked serial interface

∑ 3-line serial I/O mode

∑ Serial bus interface mode (SBI mode)

Since the

µ

PD78362A contains a baud rate generator (BRG), any serial transfer rate can be set regardless

of the operating clock frequency. The baud rate generator is a block to generate the shift clock for the transmit/

receive serial interface, and is used commonly with the two channels of the serial interfaces.

The serial transfer rate can be selected in a range of 110 bps to 38.4 Kbps by the mode register.

Figure 3-15. Block Diagram of Asynchronous Serial Interface

R

X

D

T

X

D

RXB

PE FE OVE

RXE PS1 PS0 CL SL SCK

ASIM

TXS

ASIS

INTSR

INTSER

INTST

1

--

16

1

--

16

f

CLK

/8

Internal bus

Receive

buffer

Receive

shift

register

Receive

control

parity

check

Transfer

shift

register

Transfer

control

parity

append

Transfer/

receive

baud rate

generator

output

Selector

40

µ

PD78361A, 78362A

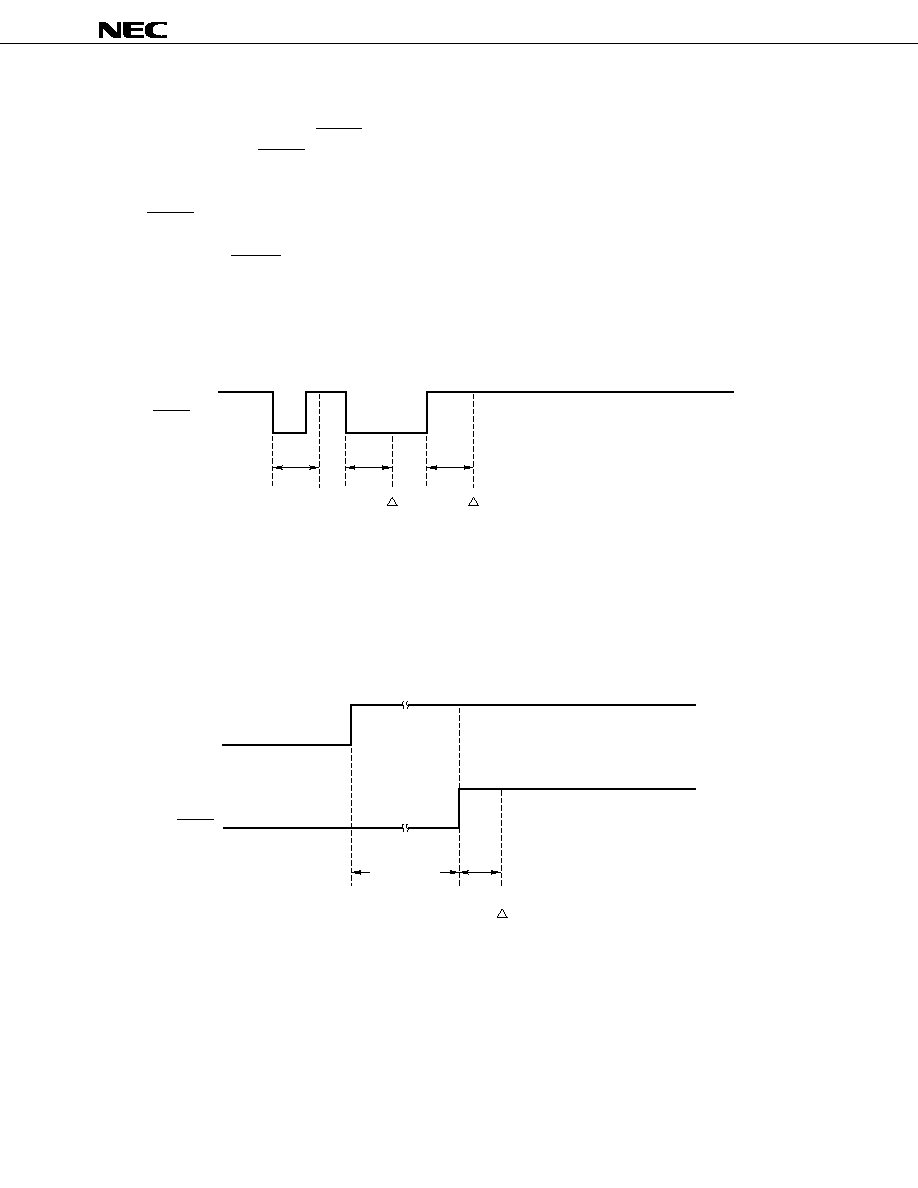

Figure 3-16. Block Diagram of Clocked Serial Interface

Figure 3-17. Block Diagram of Baud Rate Generator

CTXE

SI/SB1

SO/SB0

MOD1

MOD2

MOD1

SCK

MOD1

MOD2

WUP

INTCSI

1/2

CLS0

CLS1

CMDT

RELT

SBIC

MOD1

MOD2

WUP

CRXE

MOD0 CLS1 CLS0

BSYE

CMDD

ACKT

ACKE

ACKD

RELD CMDT RELT

8

8

8

0

7

D Q

Internal bus

Shift register (SIO)

SO latch

Busy/

acknow-

ledge

detector

circuit

Bus release/

command/

acknowledge

detector

circuit

Serial

clock

counter

Interrupt

signal

generation

control

circuit

Serial clock

control circuit

Baud rate

generator (BRG)

Selector

Selector

Selector

CSIM

f

CLK

/32

f

CLK

/8

7

0

7

0

BRG

BRGC

f

CLK

/2

TMBRG

1

--

2

Clear

Serial interface

Internal bus

Coincidence

Prescaler

41

µ

PD78361A, 78362A

3.10

PWM UNIT

The

µ

PD78362A is provided with two lines that output 8-/9-/10-/12-bit resolution variable PWM signals. The

PWM output can be used as a digital-to-analog conversion output by connecting an external lowpass filter, and

ideal for controlling actuators such as motors.

An output of between 244 Hz and 62.5 kHz can be obtaind, depending on the combination of the count clock

(62.5 ns to 1

µ

s) and counter bit length (8, 9, 10, or 12) (at an internal clock frequency of 16 MHz).

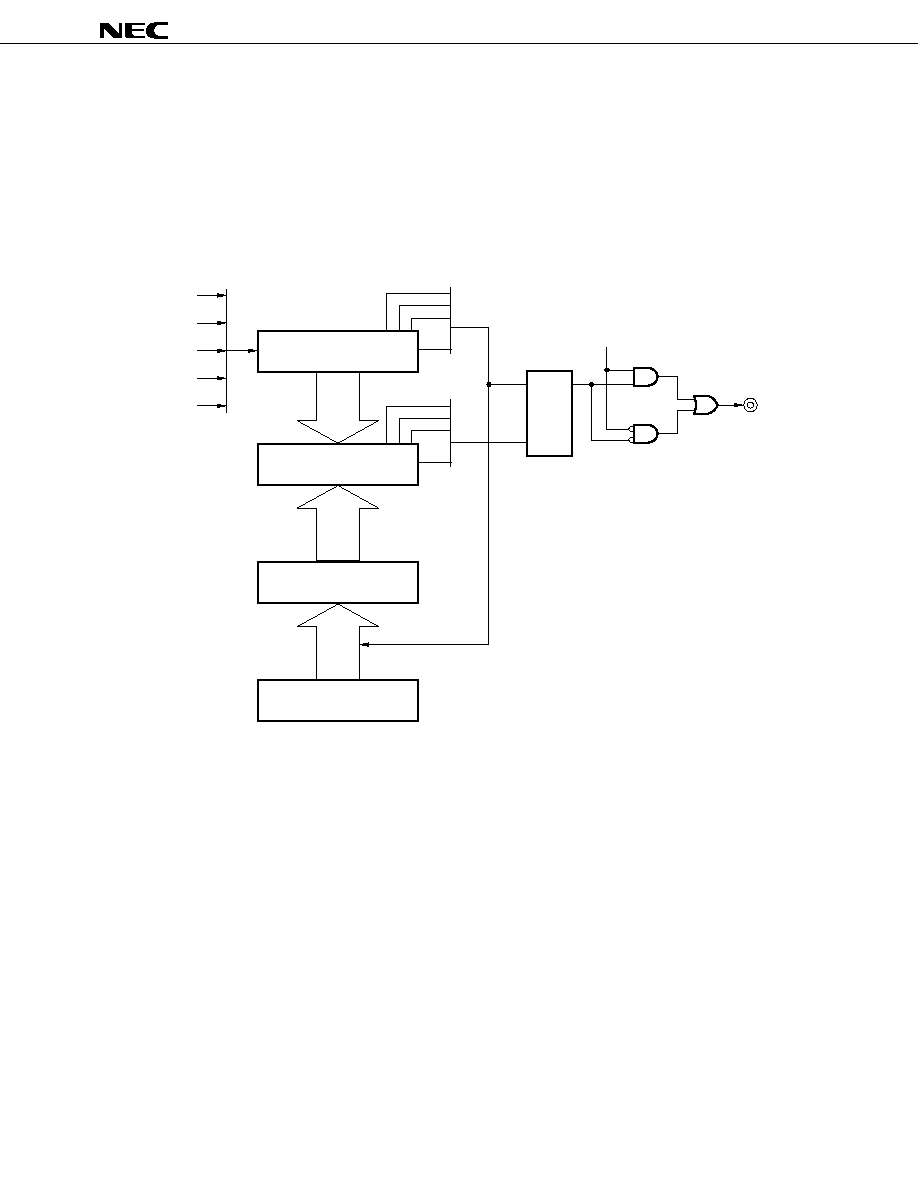

Figure 3-18. Block Diagram of PWM Unit

Remark

n = 0, 1

7

8

9

11

0-7

0-8

0-9

0-11

Counter (12)

f

CLK

/16

f

CLK

/8

f

CLK

/4

f

CLK

/2

f

CLK

Overflow

S

R

Q

ALVn

PWMn

Comparator (12)

Compare register CMPn (12)

PWM buffer register n (12)

Coinci-

dence

42

µ

PD78361A, 78362A

3.11

WATCHDOG TIMER (WDT)

The watchdog timer is a free running timer equipped with a non-maskable interrupt function to prevent

program hang-up or deadlock. An error of the program can be seen by the occurrence of the overflow interrupt

(INTWDT) of the watchdog timer.

Figure 3-19. Block Diagram of Watchdog Timer

f

CLK

/2

13

f

CLK

/2

11

f

CLK

/2

9

WDT CLR

WDT STOP

Clear

Overflow

INTWDT

Watchdog timer

(8 bits)

Oscillation

stabilization

time control circuit

43

µ

PD78361A, 78362A

4.

INTERRUPT FUNCTIONS

4.1

OUTLINE

The

µ

PD78362A is provided with powerful interrupt functions that can service interrupt requests from the

internal hardware peripherals and external sources. In addition, the following three interrupt service modes are

available. In addition, four levels of interrupt priority can be specified.

∑ Vectored interrupt service

∑ Macro service

∑ Context switching

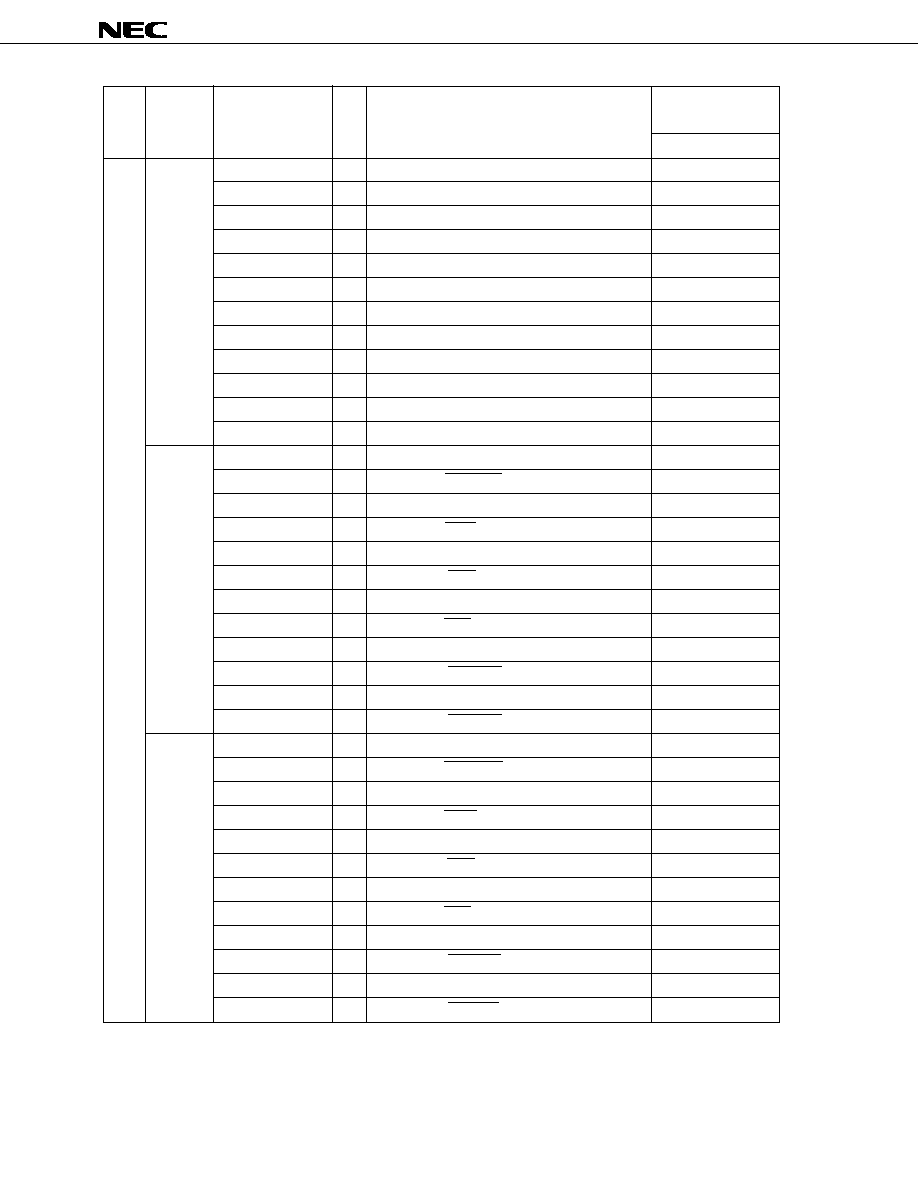

Table 4-1. Interrupt Sources

Note

≠

≠

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

≠

≠

≠

≠

Interrupt source

Name

Trigger

NMI

NMI pin input

INTWDT

Watchdog timer

INTOV3

Overflow of timer 3

INTP0/INTCC30 INTP0 pin input/CC30 coincidence signal

INTP1

INTP1 pin input

INTP2

INTP2 pin input

INTP3/INTCC20 INTP3 pin input/CC20 coincidence signal

INTP4

INTP4 pin input

INTTM0

Underflow of timer 0

INTCM03

CM03 coincidence signal

INTCM10

CM10 coincidence signal

INTCM40

CM40 coincidence signal

INTCM41

CM41 coincidence signal

INTSER

Receive error of UART

INTSR

End of UART reception

INTST

End of UART transfer

INTCSI

End of CSI transfer/reception

INTAD

End of A/D conversion

BRK

BRK instruction

BRKCS

BRKCS instruction

TRAP

Illegal op code trap

RESET

Reset input

Source unit

External

WDT

RPU

External/RPU

External

External/RPU

External

RPU

UART

CSI

A/D

≠

≠

≠

≠

Vector

table

address

0002H

0004H

0006H

0008H

000AH

000CH

000EH

0010H

0012H

0014H

0016H

0018H

001AH

001CH

001EH

0020H

0022H

0024H

003EH

≠

003CH

0000H

Macro

service

None

Provided

None

Context

switching

None

Provided

None

Provided

None

Type

Non-

maskable

Maskable

Software

Exception

Reset

Note Default priority : Priority that takes precedence when two or more maskable interrupts occur at the

same time. 0 is the highest priority, and 15 is the lowest.

44

µ

PD78361A, 78362A

4.2

MACRO SERVICE

The

µ

PD78362A has a total of five macro services. Each macro service is described below.

(1) Counter mode: EVTCNT

∑ Operation

(a) Increments or decrements an 8-bit macro service counter (MSC).

(b) A vectored interrupt request is generated when MSC reaches 0.

∑ Application example: As event counter, or to measure number of times a value is captured

(2) Block transfer mode: BLKTRS

∑ Operation

(a) Transfers data block between a buffer and a SFR specified by SFR pointer (SFRP).

(b) The transfer source and destination can be in SFR or buffer area. The length of the transfer data

can be specified to be byte or word.

(c) The number of times the data is to be transferred (block size) is specified by MSC.

(d) MSC is auto decremented by one each time the macro service has been executed.

(e) When MSC reaches 0, a vectored interrupt request is generated.

∑ Application example: To transfer/receive data through serial interface

MSC

+1/≠1

≠1

SFRP

MSC

SFR

Buffer N

Buffer 1

Internal bus

45

µ

PD78361A, 78362A

(3) Block transfer mode (with memory pointer): BLKTRS-P

∑ Operation

This is the block transfer mode in (2) above with a memory pointer (MEMP). The appended buffer

area of MEMP can be freely set on the memory space.

Remark

Each time the macro service is executed, MEMP is auto incremented (by one for byte

data transfer and by two for word data transfer).

∑ Application example: Same as (2)

(4) Data differential mode: DTADIF

∑ Operation

(a) Calculates the difference between the contents of SFR (current value) specified by SFRP and the

contents of SFR saved to the last data buffer (LDB).

(b) Stores the result of the calculation in a predetermined buffer area.

(c) Stores the contents of the current value of the SFR in LDB.

(d) The number of times the data is to be transferred (block size) is specified by MSC. Each time the

macro service is executed, MSC is auto decremented by one.

(e) When MSC reaches 0, a vector interrupt request is generated.

Remark

The differential calculation can be carried out only with 16-bit SFRs.

∑ Application example : To measure cycle and pulse width by the capture register of the real-time

pulse unit (RPU)

≠1

SFR

LDB

Buffer N

Buffer 1

Differential calculation

Internal bus

SFRP

MSC

≠1

SFRP

MSC

SFR

MEMP

+1/+2

Buffer N

Buffer 1

Internal bus

46

µ

PD78361A, 78362A

(5) Data differential mode (with memory pointer): DTADIF-P

∑ Operation

This is the data differential mode in (4) above with memory pointer (MEMP). By appending MEMP,

the buffer area in which the differential data is to be stored can be set freely on the memory space.

Remarks 1.

The differential calculation can be carried out only with 16-bit SFRs.

2.

The buffer is specified by the result of operation by MEMP and MSC

Note

. MEMP is

not updated after the data has been transferred.

Note MEMP ≠ (MSC

◊

2) + 2

∑ Application example: Same as (4)

≠1

SFR

MEMP

LDB

SFRP

MSC

Buffer N

Buffer 1

Differential calculation

Internal bus

47

µ

PD78361A, 78362A

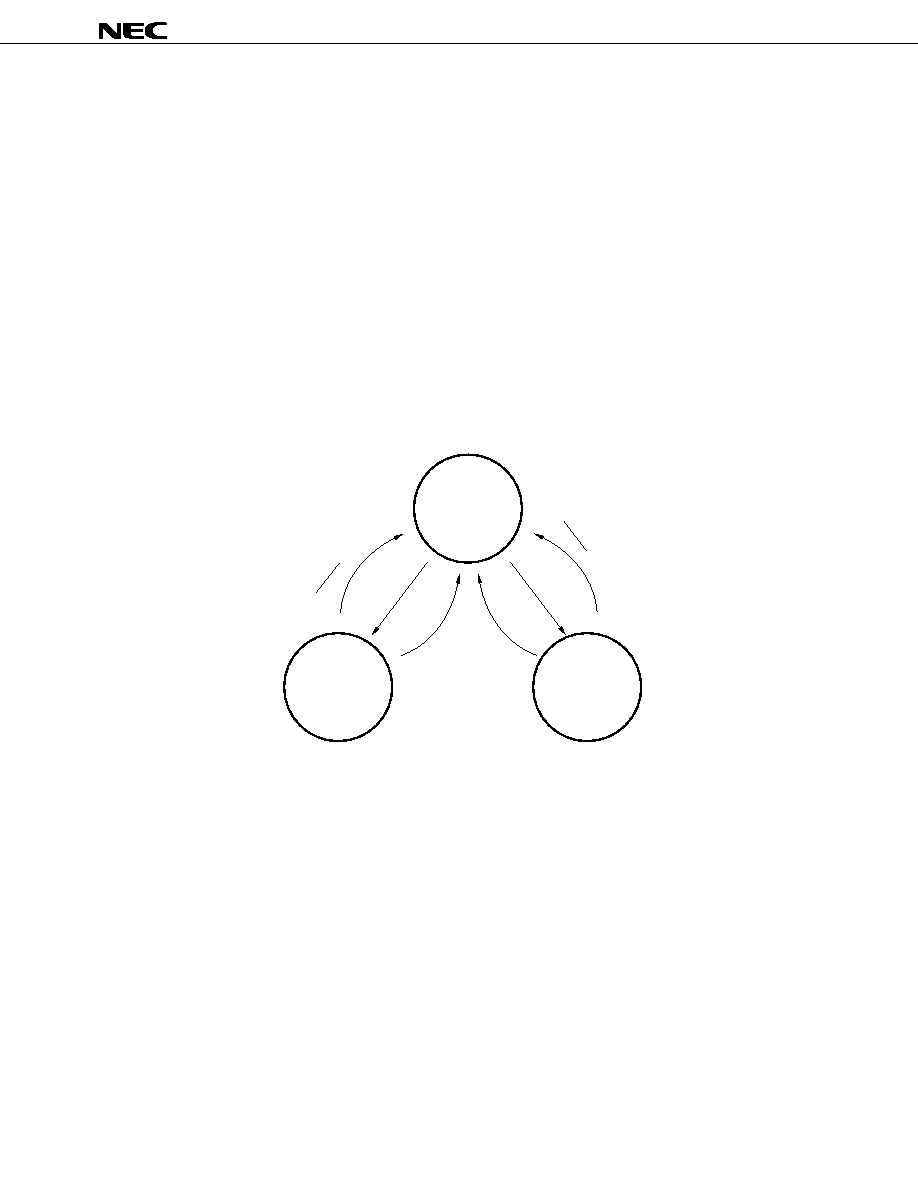

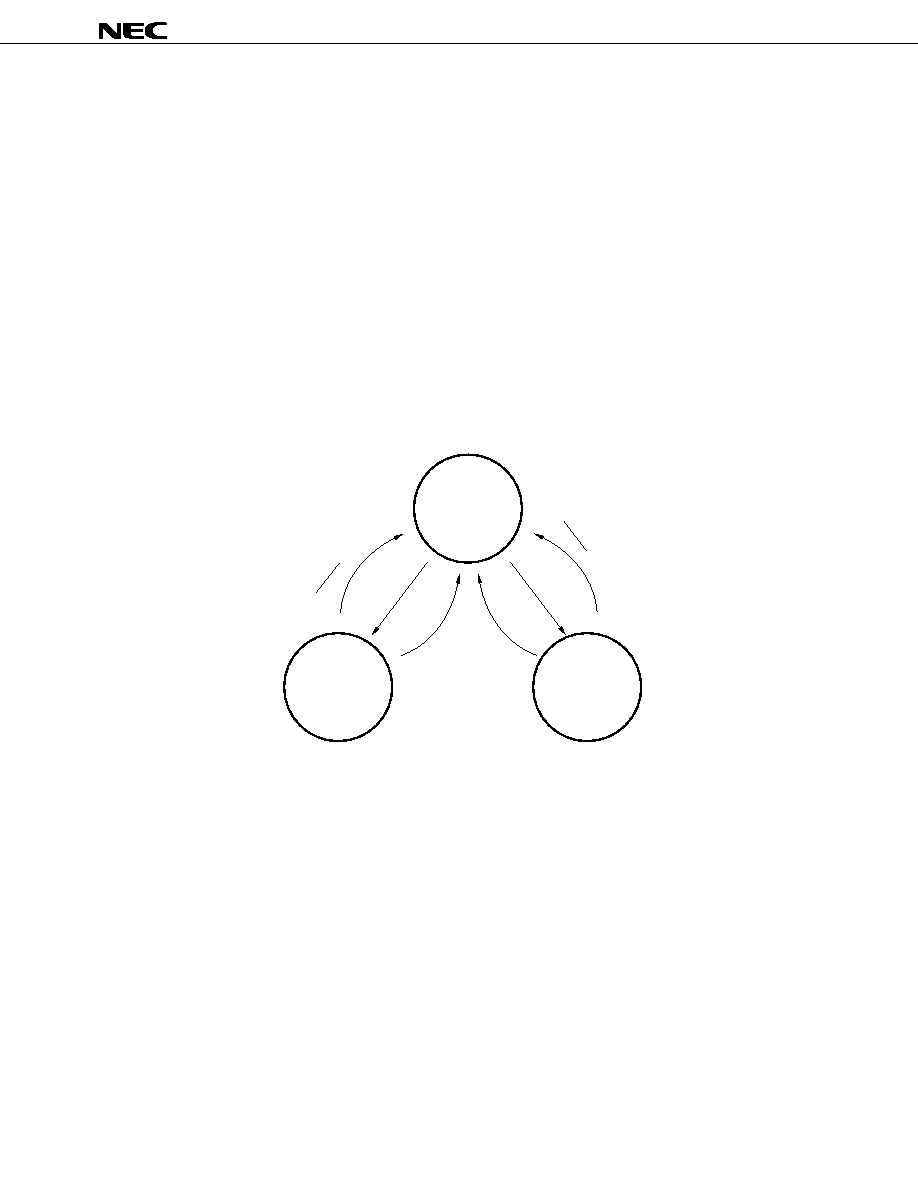

4.3

CONTEXT SWITCHING

This function is to select a specific register bank through the hardware, and to branch execution to a vector

address predetermined in the register bank. At the same time, it saves the present contents of the PC and PSW

to the register bank when an interrupt occurs, or when the BRKCS instruction is executed.

4.3.1

Context Switching Function by Interrupt Request

When a context switching enable flag corresponding to each maskable interrupt request is set to 1 in the EI

(interrupt enable) status, the context switching function can be started.

The context switching operation by an interrupt request is performed as follows:

(1) When an interrupt request is generated, a register bank to which the context is to be switched is specified

by the contents of the lower 3 bits of the row address (even address) of the corresponding vector table.

(2) A predetermined vector address is transferred to the PC in the register bank to which the context is to

be switched, and the contents of the PC and PSW immediately before the switching takes place are saved

to the register bank.

(3) Execution branches to an address indicated by the contents of the PC newly set.

Figure 4-1. Operation of Context Switching

PC

PSW

RP0

RP1

RP2

RP3

RP4

RP5

RP6

RP7

Registor Bank

Registor Bank

(0-7)

Exchange

Save

48

µ

PD78361A, 78362A

4.3.2

Context Switching Function by BRKCS Instruction

The context switching function can be started by the BRKCS instruction.

The operation of context switching by an interrupt request is as follows:

(1) An 8-bit register is specified by the operand of the BRKCS instruction, and the register bank to which

the context is to be switched is specified by the contents of this register (only the lower 3 bits of 8 bits are

valid).

(2) The vector address predetermined in the register bank to which the context is to be switched is transferred

to the PC, and at the same time, the contents of the PC and PSW immediately before the switching takes

place are saved to the register bank.

(3) Execution branches to the contents of the PC newly set.

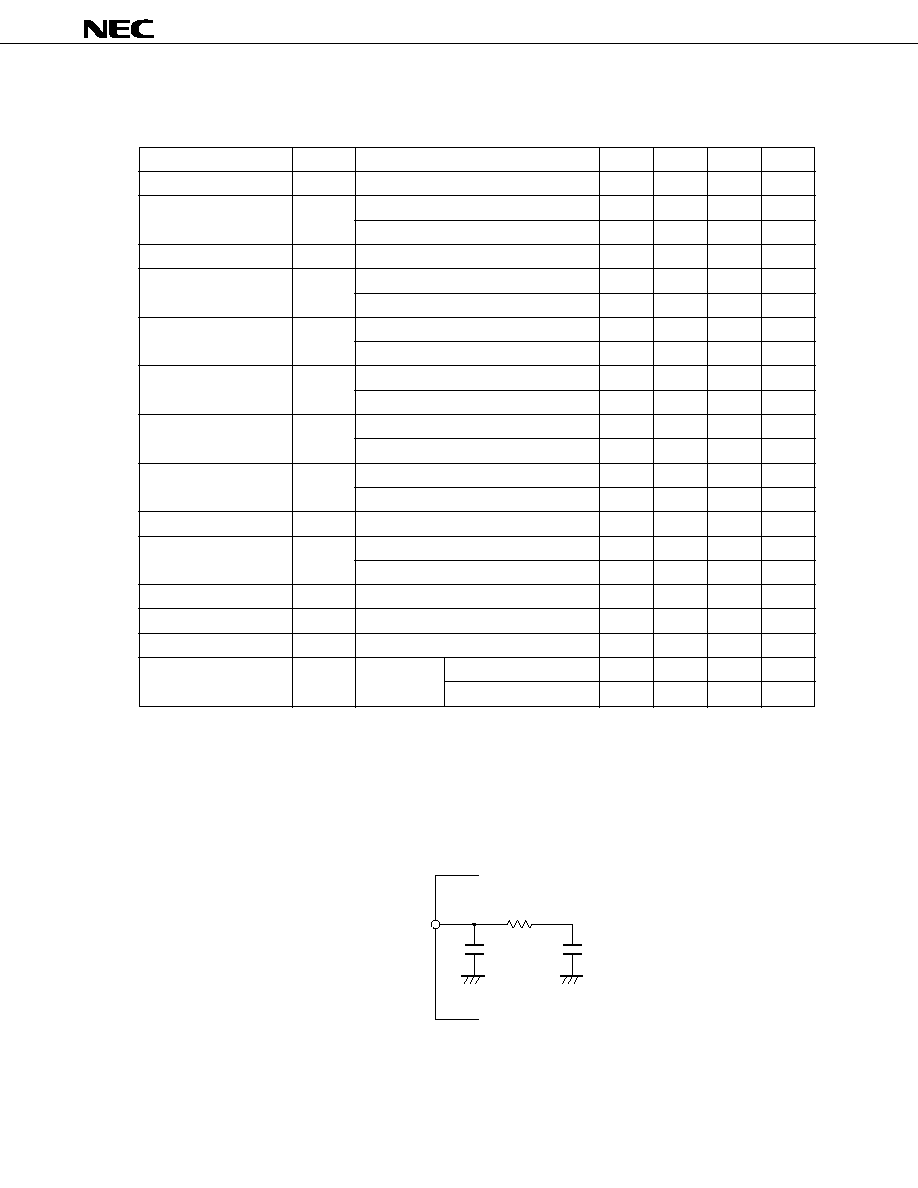

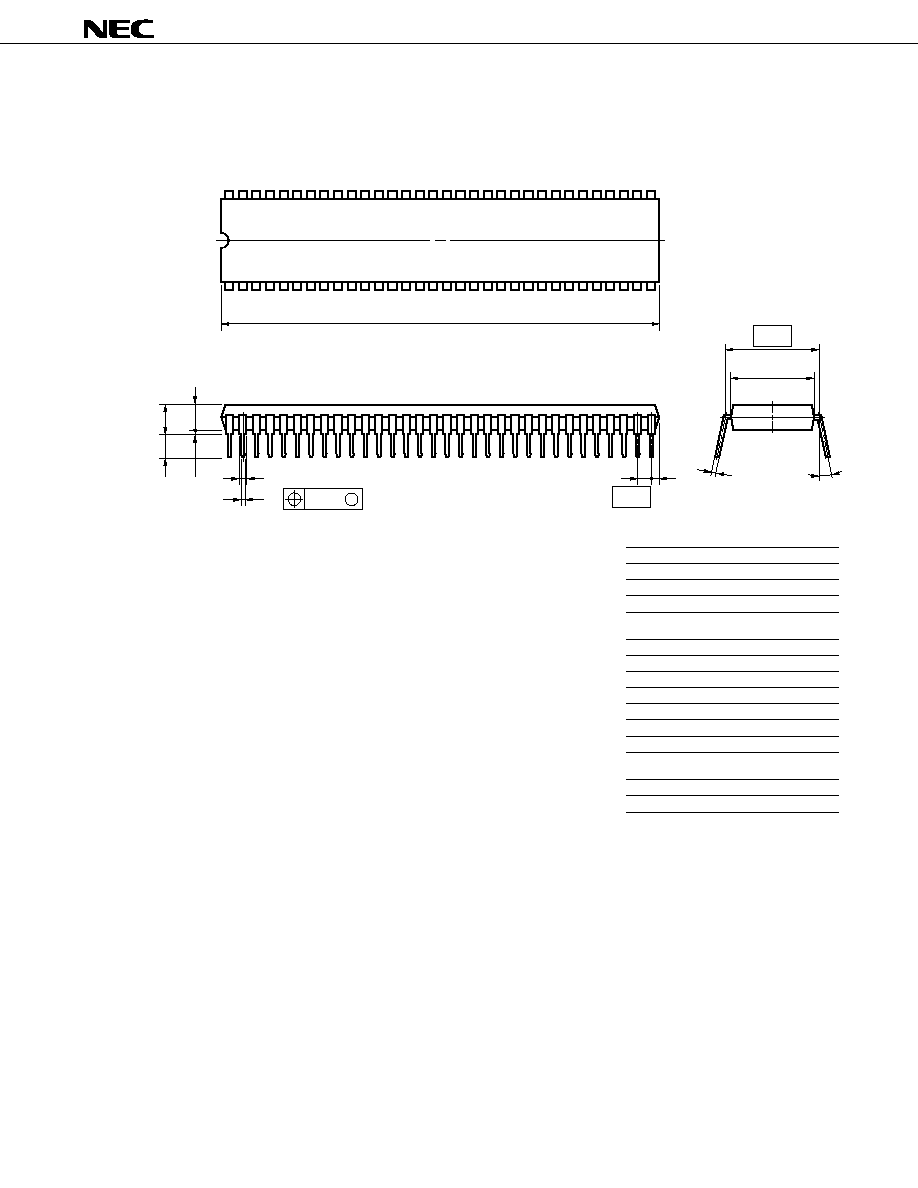

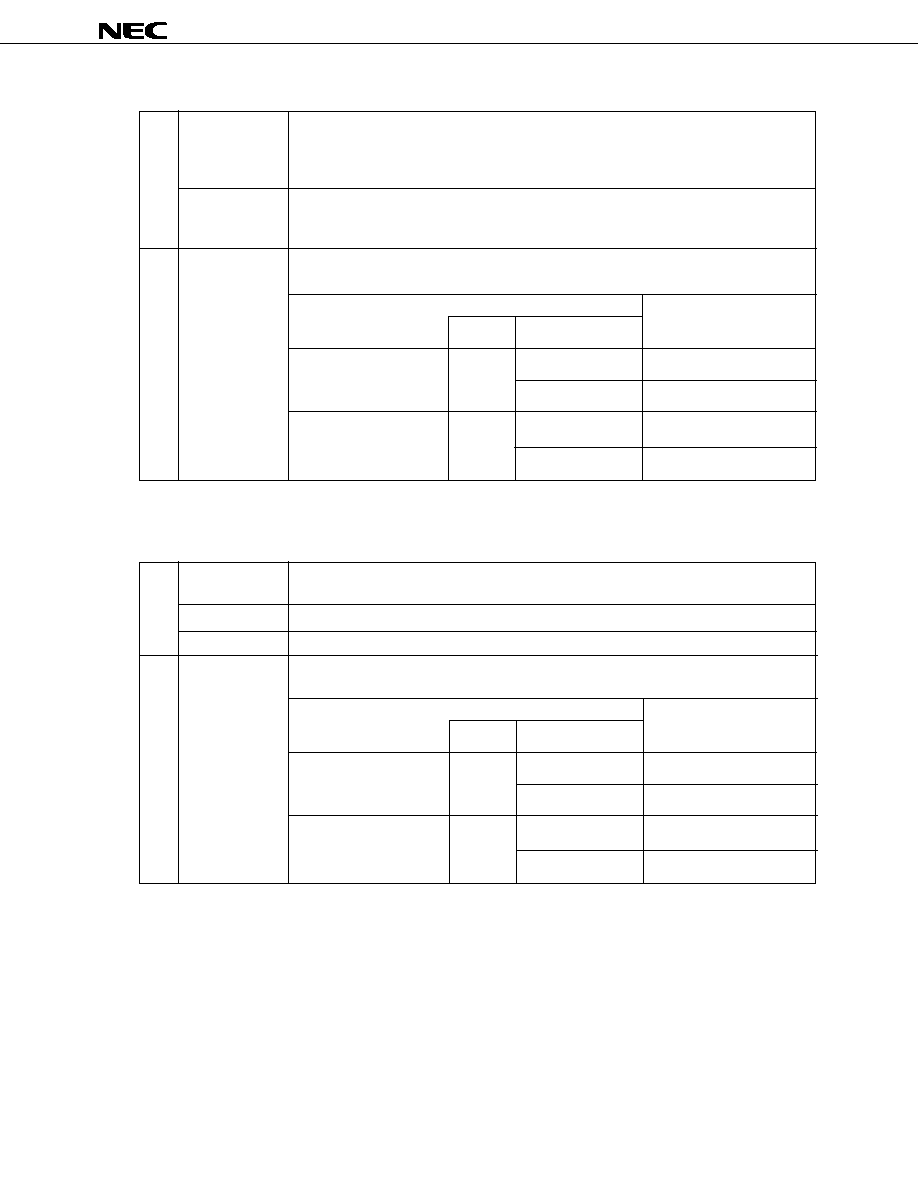

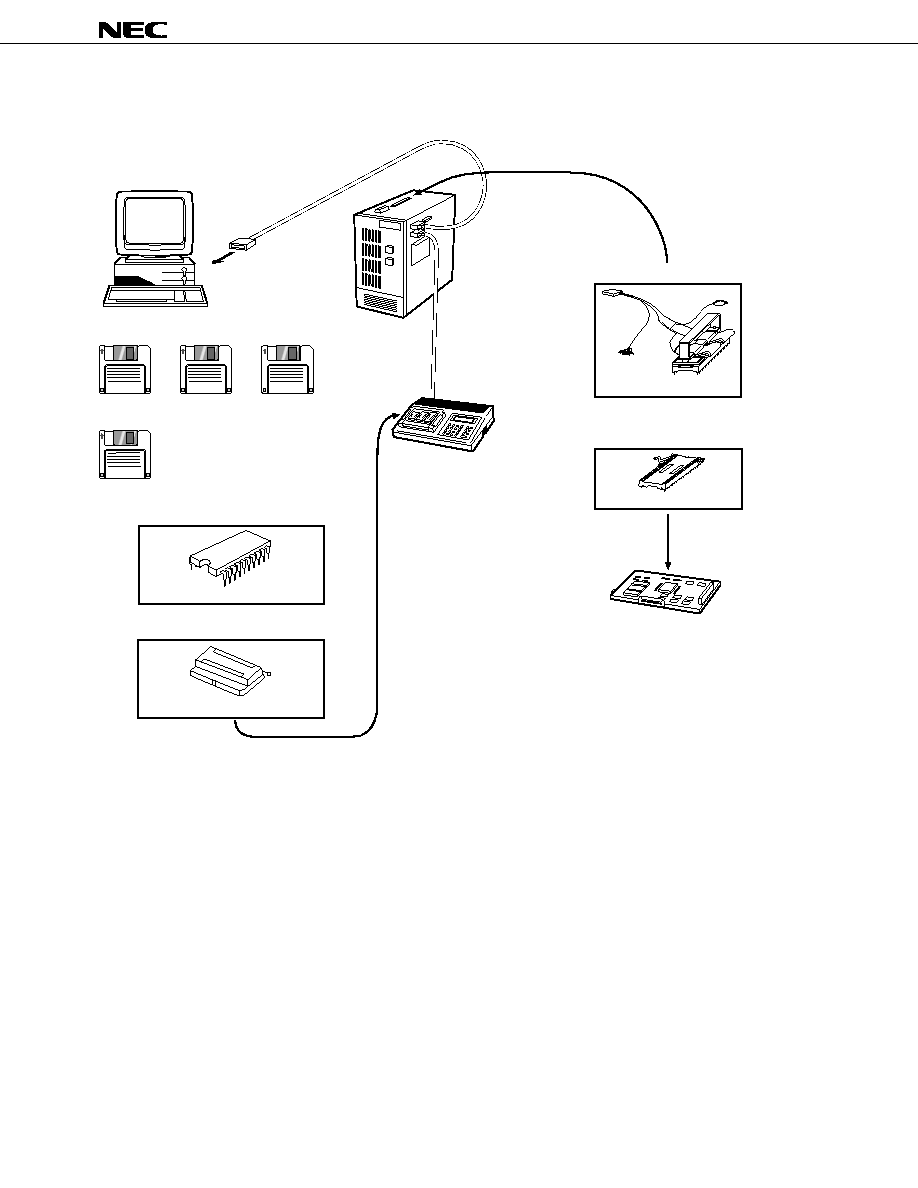

4.3.3