NJM2275

- 1 -

Ver.2004-08-25

Under Development

RF AMPLIFIER FOR VHF/UHF(LOW) BAND

GENERAL DESCRIPTION PACKAGE OUTLINE

The NJM2275 is a low current, low voltage RF amplifier,

especially designed for VHF/UHF(low) band.

The center frequency of this narrow band amplifier is

changed by external components.

NJM2275F

FEATURES

Wide Operating Voltage 1.8V to 6V

Low Operating Current 0.8mA type. at V

+

=1.9V, 400MHz input

High Gain

Power Gain 15dB (1.9V, 400MHz input)

Voltage Gain 30dB (1.9V, 400MHz input, 1k load)

Operating Frequency band VHF to UHF(Low)

High Isolation 26dB(OUT to IN, 400MHz)

Bipolar Technology

Package Outline MTP6

PIN CONFIGULATION

Pin Function

1. RF

IN

2. GND

3. BIAS

CAP

4. RF

OUT

5. IREF

6. V+

BLOCK DIAGRAM

1

2

3

6

5

4

Top View

4

V+

I REF

BIAS CAP

GND

RF OUT

5

6

1

3

2

RF IN

Orientation Mark

NJM2275

Ver.2004-08-25

- 2 -

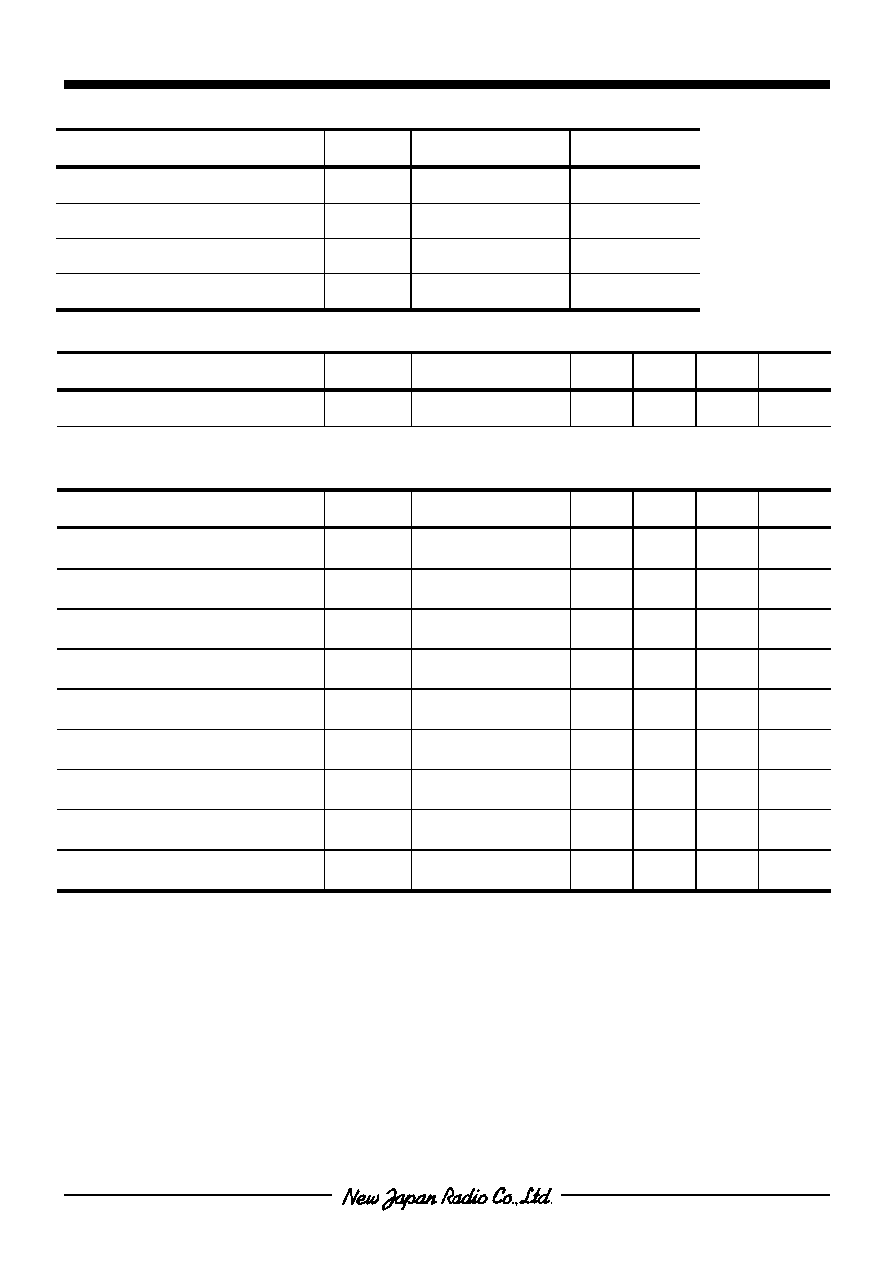

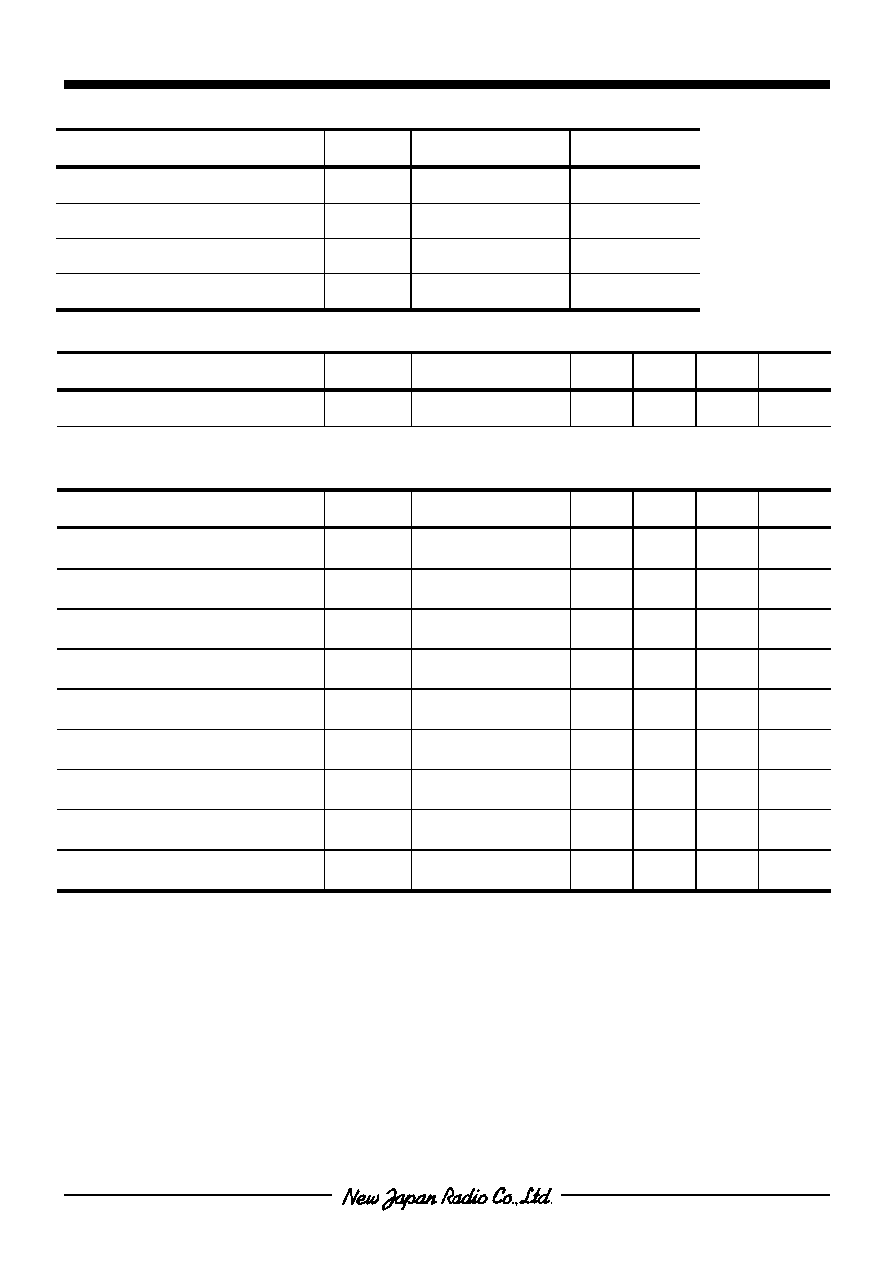

ABSOLUTE MAXIMUM RATINGS

(Ta=25�C)

PARAMETER SYMBOL

RATINGS UNIT

Supply Voltage

V

+

10.0

V

Power Dissipation

P d

200

mW

Operating Temperature

T o p r

- 40 to +85

�C

Storage Temperature

T s t g

- 40 to +125

�C

RECOMMENDED OPERATING CONDITION

(Ta=25�C)

PARAMETER SYMBOL

TEST

CONDITIONS

MIN.

TYP.

MAX.

UNIT

Supply Voltage

V

+

1.8 1.9 6.0 V

ELECTRICAL CHARACTERISTICS

(

Ta=25�C, V

+

=1.9V, fin=400MHz, unless otherwise noted)

PARAMETER SYMBOL

TEST

CONDITIONS

MIN.

TYP.

MAX.

UNIT

Current Consumption

I c c

No signal

-

0.8

1.0

mA

Power Gain

PG

Pin= - 40dBm

Test circuit1

- 15 - dB

Voltage Gain

VG

Pin= - 40dBm

Test circuit2

- 30 - dB

Noise Figure

NF

Test Circuit1

-

2.2

-

dB

Input Return Loss

l S 1 1 l

2

Pin= - 40dBm

Test Circuit1

- -

7 - dB

Output Return Loss

l S 2 2 l

2

Pin= - 40dBm

Test Circuit1

- -

7 - dB

RF OUT - RF IN Isolation

I S L

Pin= - 40dBm

Test Circuit1

- 26 - dB

Power Input at 1dB compression Point

P �1 dB

Test Circuit1

-

- 28

-

dBm

NJM2275

Ver.2004-08-25

- 3 -

TEST CIRCUIT

This test circuit allows the measurement of all parameters described in "ELECTRICAL CHARACTERISTICS".

Test Circuit 1 : PG , l S 1 1 l

2

, l S 2 2 l

2

, P �1 d B , Output Level versus Input Level

Test Circuit 2 : VG , Output Level versus Input Level

Test Circuit 3 : Power Gain versus Input signal Frequency

PG and PG shown in "Output level versus Input Level" are given by ,

PG = Pout � Pin

VG = (Pout + Prl ) � Pin

Prl is caused by the voltage drop of RL. RL is 1000 . The input impedance of spectrum analyzer Zin is 50.

Prl is calculated from

Prl = 20log ( ( RL + Zin) / RL)

Prl = 20 log (1050 / 50 )

4

5

6

1

3

2

Lout

27n

1000p

1000p

V+

SG

(50)

Cout

1000p

8p

15n

2p

L in

C in

Cb

Cv

CL

Spectrum

Analyzer

(Zin=50)

4

5

6

1

3

2

Lout

27n

1000p

1000p

V+

SG

(50)

Cout

1000p

4p

27n

2p

L in

C in

Cb

Cv

CL

Spectrum

Analyzer

(Zin=50)

RL

1k

4

5

6

1

3

2

Lout

27n

1000p

1000p

V+

Cout

1000p

8p

15n

2p

L in

C in

Cb

Cv

CL

NF

meter

NJM2275

Ver.2004-08-25

- 4 -

EVALUATION PC BOARD

The evaluation board is useful for your design and to have more understanding of the usage and performance of

this device. This circuit is the same as TEST CIRCUIT. Note that this board is not prepared to show the

recommendation of pattern and parts layout.

Circuit Diagram

Evaluation PC Board

This evaluation board is designed to have the maximum value of VG at 400MHz.

By using the value of Test Circuit1, this board can be changed to have the maximum value of PG at 400MHz.

If NF is not so good, Pin 5 may have a noisy signal. In such cases, it may be effective to connect a capacitor

between Pin 5 and ground. However, if the ground has a large noisy signal, NF may become worse.

4

5

6

1

3

2

Lout

27n

1000p

1000p

V+

Cout

1000p

4p

27n

2p

L in

C in

Cb

Cv

CL

RL

1k

RFOUT

RFIN

1608

1608

1608

1608

1608

1608

1608

1608

Cin Lin

Cb

CV

Lout

RL

CL

Cout

RFOUT

RFIN

V

+

Pin1

NJM2275

Ver.2004-08-25

- 5 -

TYPICAL CHARACTERISTICS

(

Ta=25�C, V

+

=2.0V, unless otherwise noted

)

[CAUTION]

The specifications on this databook are only

given for information , without any guarantee

as regards either mistakes or omissions. The

application circuits in this databook are

described only to show representative usages

of the product and not intended for the

guarantee or permission of any right including

the industrial rights.

Pout/Icc versus Pin

-60

-50

-40

-30

-20

-10

0

10

-60

-50

-40

-30

-20

-10

0

10

20

Power Input Level Pin(dBm)

P

o

w

e

r

O

u

t

put

Le

v

e

l

P

out

(

d

B

m

)

0

1

2

3

4

5

6

7

C

u

r

r

e

nt

C

o

nsum

pt

i

o

n

I

cc(

m

A

)

Test Circuit1(Power Gain)

Pout

Icc

Pout / Icc versus Pin

-60

-50

-40

-30

-20

-10

0

10

-60

-50

-40

-30

-20

-10

0

10

20

Power Input Level Pin(dBm)

P

o

w

e

r

O

u

t

p

ut

L

e

v

e

l

P

out

(

d

B

m

)

0

1

2

3

4

5

6

7

C

u

r

r

e

n

t

C

onsum

pt

i

o

n I

cc(

m

A

)

Test Circuit2(Voltage Gain)

Pout

Icc

Power Gain/NF versus Input Signal Frequency

0

2

4

6

8

10

12

14

16

300

350

400

450

500

Input Signal Frequency fin(MHz)

Pow

e

r

G

a

i

n

PG

(

d

B)

0

1

2

3

4

5

6

7

8

NF

(

d

B

)

Test Circuit3

PG

NF