NJW1109

≠ 1 ≠

Headphone Amplifier with Electronic Volume

s

s

s

s

GENERAL DESCRIPTION

The

NJW1109

is a headphone amplifier with electronic volume. It

includes widely gain adjustable volume, +20 to ≠80 dB, and mute

function. These are controlled by I

2

C bus. The

NJW1109

is

suitable for headphone output on TV set.

s

s

s

s

FEATURES

q

Operating Voltage

7.5 to 10 V

q

Electronic Volume

+20dB to -80dB / 0.5dB step, Mute

q

I

2

C Bus Interface

q

Bi-CMOS Technology

q

Package Outline

DIP14, DMP14, SSOP14

s

s

s

s

BLOCK DIAGRAM

s

s

s

s

PIN FUNCTION

s

s

s

s

PACKAGE OUTLINE

1

7 8

14

No.

SYMBOL

FUNCTION No.

SYMBOL

FUNCTION

1 V+ Power

Supply

8

SCL

I

2

C Bus Clock Input

2 OUTb

Bch

Output

9

Vref

Reference voltage stabilized

capacitor connect terminal

3

N.C.

No Connect

10

INa

Ach Input

4

CAPb

Balance control click noise

absorbing capacitor connect

terminal

11

CAPa Volume control click noise

absorbing capacitor connect

terminal

5 INb Bch

Input

12

N.C. No

Connect

6 ADR I

2

C Bus Slave Address

Select

13

OUTa Ach

Output

7 SDA I

2

C Bus Data Input

14

GND

Ground

NJW1109D NJW1109M

NJW1109V

VOL

IN b

IN a

VOL

Vref

V+

GND

OUTa

OUTb

ADR

Bias

I

2

C

CAPa

CAPb

Interface

SDA SCL

NJW1109

≠ 2 ≠

s

s

s

s

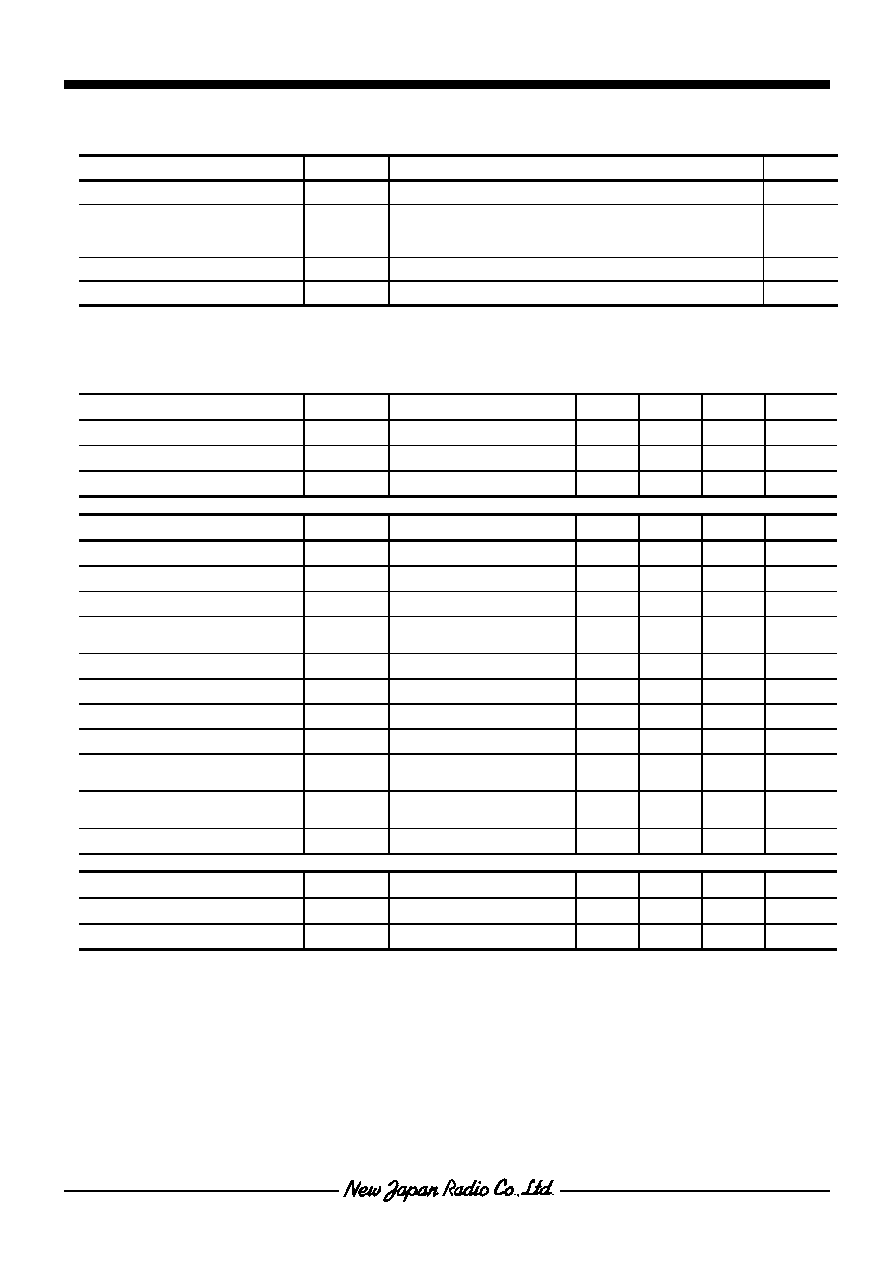

ABSOLUTE MAXIMUM RATING

(Ta=25

∞

∞

∞

∞

C)

PARAMETER SYMBOL

RATING

UNIT

Supply Voltage

V

+

12 V

Power Dissipation

P

D

500 (DIP14)

500* (DMP14)

440* (SSOP14)

mW

Operating Temperature Range

Topr

-20 to +75

∞

C

Storage Temperature Range

Tstg

-40 to +125

∞

C

*(Note) EIA/JEDEC STANDARD Test board(76.2 x 114.3 x 1.6mm, 2layers, FR-4)mounting

s

s

s

s

ELECTRICAL CHARACTERISTICS

(V

+

=9V, V

IN

=-20dBV, f=1kHz, R

L

=100

,

VOL = 0dB

, Ta=25

∞

C

)

q

q

q

q

POWER SUPPLY

PARAMETER SYMBOL

TEST

CONDITION

MIN.

TYP.

MAX.

UNIT

Operating Voltage

V

+

7.5 9 10 V

Operating Current

I

CC

No

Signal

- 5 8 mA

Reference Voltage

V

REF

4.0 4.5 5.0 V

q

q

q

q

AMPLIFIER

PARAMETER SYMBOL

TEST

CONDITION

MIN.

TYP.

MAX.

UNIT

Volume Maximum Gain

G

VMAX

VOL = +20dB setting

18 20 22 dB

Volume Minimum Gain

G

VMIN

VOL = -80dB setting

-80

Voltage Gain Channel Balance

Gv

VOL = 0dB setting

-1.5 0 1.5 dB

Maximum Input Voltage

V

IM

VOL = -10dB setting

THD=3%

8.9

(2.8)

9.5

(3.0)

-

dBV

(Vrms)

Output Power

P

O

VOL = 10dB,

THD=10%

70 100 - mW

Total Harmonic Distortion

THD

VOL = 0dB setting

- 0.1 1 %

Channel Separation

CS

Rg=600, Vin = 0dBV

70 80 - dB

Mute Level

Mute

VOL =

Mute, Vin = 0dBV

- -100 -90 dB

Output Noise Voltage 1

V

NO1

Rg=0, A-Weighted

-

-95

(18)

-85

(56)

dBV

(µVrms)

Output Noise Voltage 2

V

NO2

VOL =

Mute

Rg=0, A-Weighted

-

-105

(5.6)

-95

(18)

dBV

(µVrms)

Power Supply Ripple Rejection

PSRR

Vripple=-20dBV, Rg=0

- 70 - dB

q

q

q

q

CONTROL

PARAMETER SYMBOL

TEST

CONDITION

MIN.

TYP.

MAX.

UNIT

High Level Input Voltage

V

ADRH

High : Slave Address 84H

V

+

/2 - - V

Low Level Input Voltage

V

ADRL

Low : Slave Address 80H

- - 1.0 V

NJW1109

≠ 3 ≠

s

s

s

s

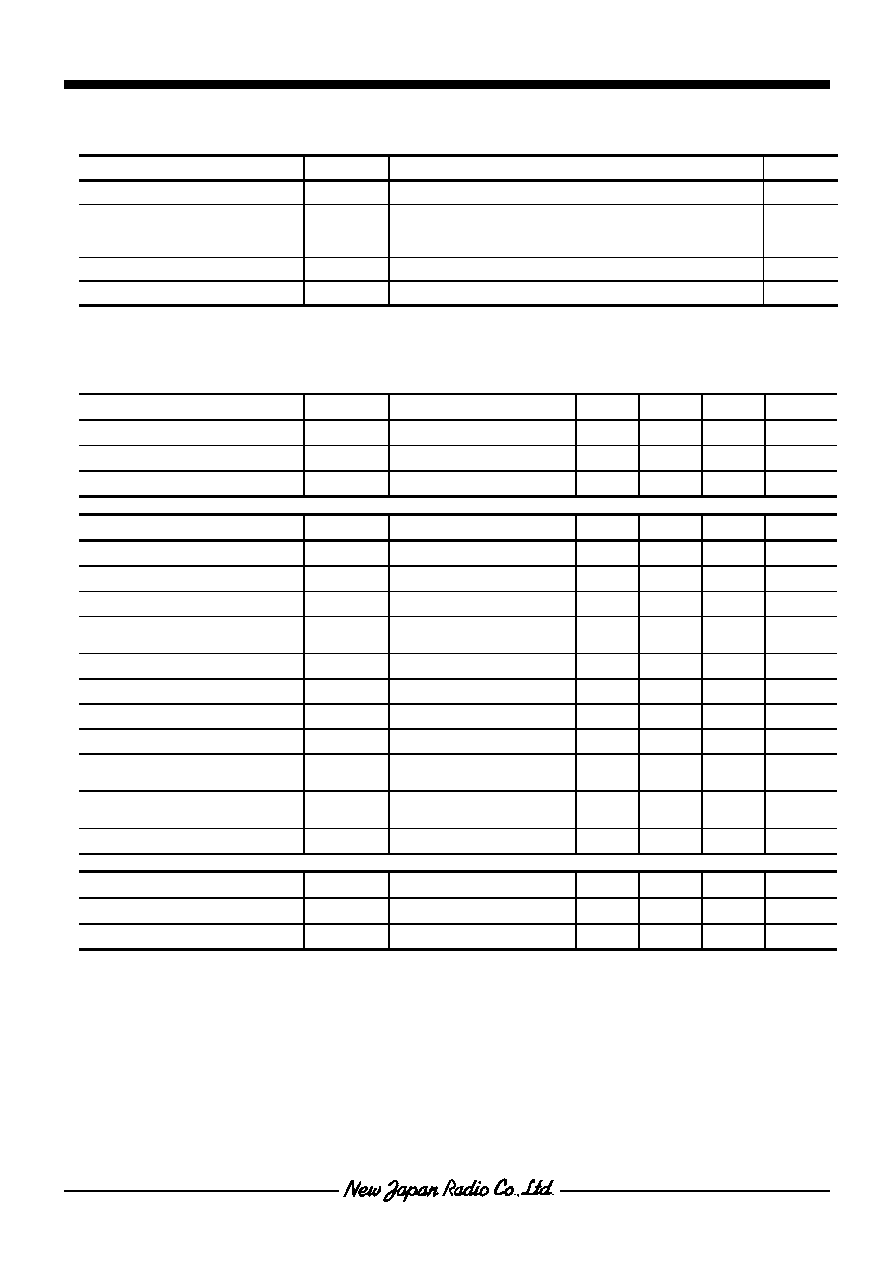

I

2

C BUS CHARACTERISTICS (SDA, SCL)

I

2

C BUS Load Conditions: Pull up resistance 4k

(Connected to +5V), Load capacitance 200pF (Connected to GND)

PARAMETER SYMBOL

MIN.

TYP.

MAX.

UNIT

Low Level Input Voltage

V

IL

0.0 -

1.5 V

High Level Input Voltage

V

IH

2.5 -

5.0 V

Hysteresis of Schmitt trigger inputs

V

hys

0.25 - - V

LOW level output voltage (3mA at SDA pin)

V

OL

0 -

0.4

V

Output fall time from V

IHmin

to V

ILmax

with

a bus capacitance from 10pF to 400pF

t

of

20+0.1C

b

- 250 ns

Pulse width of spikes which must be suppressed by the input filter

t

SP

0

-

50

ns

Input current each I/O pin with an input voltage between 0.1V

DD

and 0.9V

DDmax

I

i

-10

-

10

µA

Capacitance for each I/O pin

C

i

-

-

10

pF

SCL clock frequency

f

SCL

- -

400

kHz

Hold time (repeated) START condition.

t

HD:STA

0.6 - - µs

LOW period of the SCL clock

t

LOW

1.3 - - µs

HIGH period of the SCL clock

t

HIGH

0.6 - - µs

Set-up time for a repeated START condition

t

SU:STA

0.6 - - µs

Data hold time

t

HD:DAT

0 - 0.9 µs

Data set-up time

t

SU:DAT

100 - - ns

Rise time of both SDA and SCL signals

t

r

-

-

300

ns

Fall time of both SDA and SCL signals

t

f

-

-

300

ns

Set-up time for STOP condition

t

SU:STO

0.6 - - µs

Bus free time between a STOP and START condition

t

BUF

1.3 - - µs

Capacitive load for each bus line

C

b

-

-

400

pF

Noise margin at the LOW level

V

nL

0.5 - - V

Noise margin at the HIGH level

V

nH

1 - - V

C

b

; total capacitance of one bus line in pF.

SDA

SCL

t

f

t

HD:STA

t

LOW

t

r

t

HD:DAT

t

HIGH

t

f

t

SU:DAT

S

t

SU:STA

t

HD:STA

t

SP

t

SU:STO

Sr

t

r

t

BUF

P

S

NJW1109

≠ 4 ≠

s

s

s

s

TERMINAL DESCRIPTION

No. SYMBOL

FUNCTION

EQUIVALENT

CIRCUIT

VOLTAGE

5

10

INb

INa

Bch Input

Ach Input

V+/2

2

13

OUTb

OUTa

Bch Output

Ach Output

V+/2

4 CAPb

Balance control click noise

absorbing capacitor connect

terminal

3.8V

11 CAPa

Volume control click noise

absorbing capacitor connect

terminal

3.1V

17k

12k

8k

8k