| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: NJW1156 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

NJW1156

≠ 1 ≠

PRELIMINARY

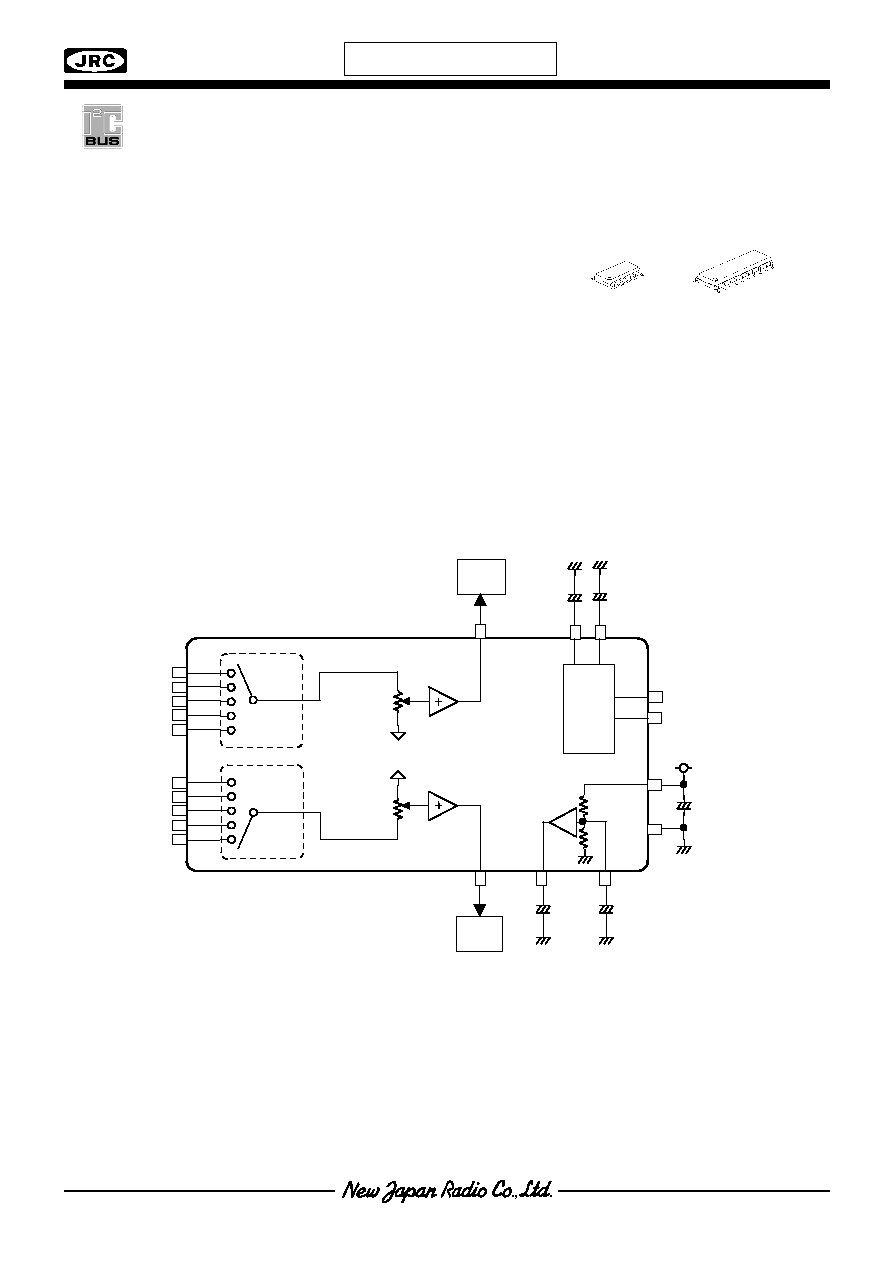

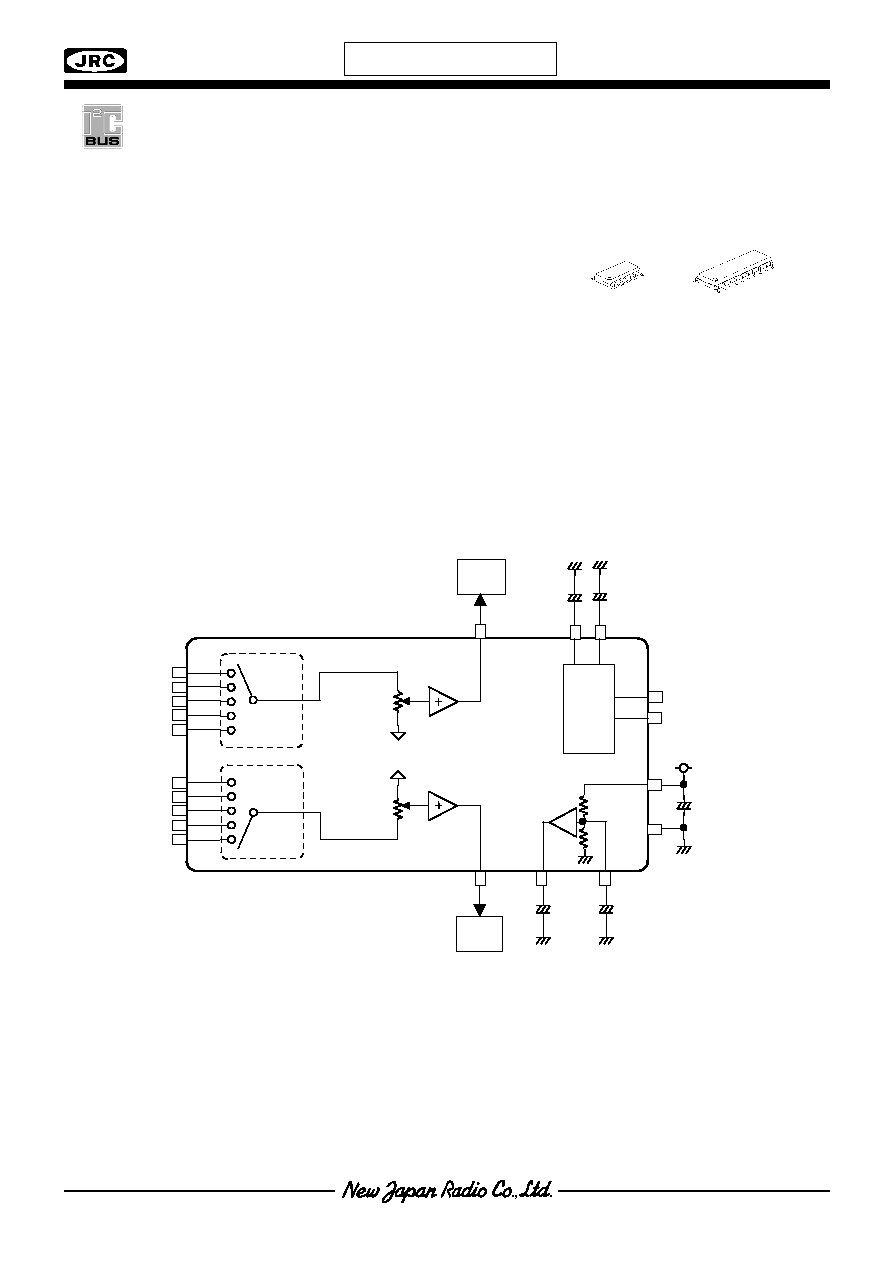

2-CHANNEL ELECTRONIC VOLUME WITH INPUT SELECTOR

I

I

I

I GENERAL DESCRIPTION I

I

I

I PACKAGE OUTLINE

NJW1156 is a two channel electronic volume with

5 input selector. It's suitable for Input signal trimmer

of audio equipments such as DVD / HDD recorder

and VCR. These functions are controlled by I

2

C Bus.

I

I

I

I FEATURES

G Operating Voltage

8 to 13V

G I

2

C Bus control

G 5 Input Selector

G

Volume

0

to

≠39.5dB/0.5dBstep,

MUTE

G Bi-CMOS Technology

G Package Outline

SSOP20, DMP20

I

I

I

I BLOCK DIAGRAM

I

2

C

In

te

r

f

a

c

e

A/D

A/D

INPUTS

INPUTS

I

2

C Control

V+

GND

V+

GND

NJW1156V

NJW1156M

NJW1156

≠ 2 ≠

PRELIMINARY

I

I

I

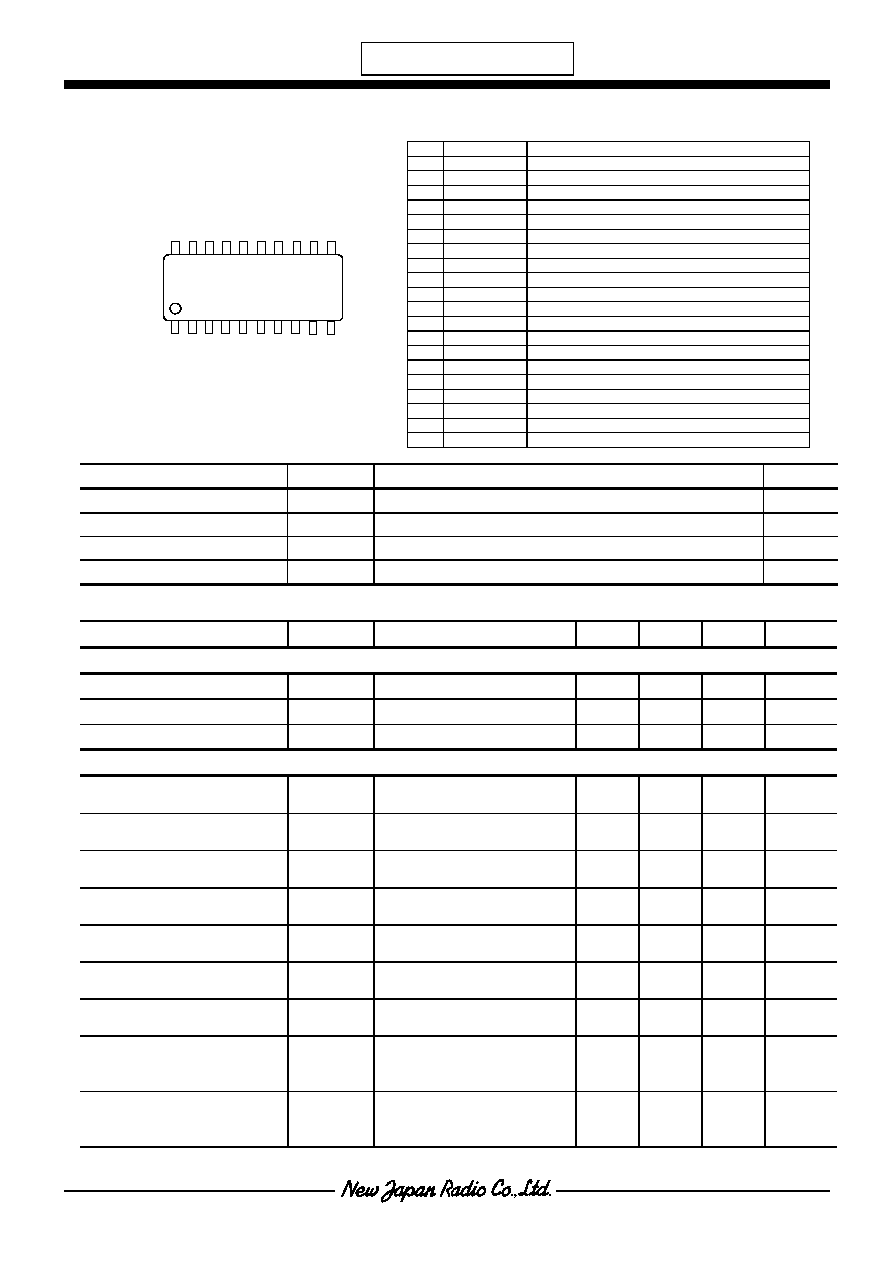

I PIN FUNCTION

I

I

I

I ABSOLUTE MAXIMUM RATING (Ta=25∞∞∞∞C)

PARAMETER SYMBOL

RATING

UNIT

Power Supply Voltage

V+

15

V

Power Dissipation

P

D

375

mW

Operating Temperature Range

Topr

-20 to +75

∞C

Storage Temperature Range

Tstg

-40 to +125

∞C

I

I

I

I ELECTRICAL CHARACTERISTICS

(Ta=25

∞

∞

∞

∞C,V

+

=+12V)

PARAMETER SYMBOL

TEST

CONDITION

MIN.

TYP.

MAX.

UNIT

N

N

N

N Power Supply

Operating Voltage

V+ - 8

12

13

V

Reference Voltage

V

ref

-

5.5

6

6.5

V

Supply Current

I

CC

No

signal

- 4.5 6.8 mA

N

N

N

N Input/Output Characteristics

Maximum Output Voltage

V

OM

f=1kHz,THD=1%

Volume=0dB

3.0 4.0 - Vrms

Voltage Gain 1

G

V1

V

IN

=1Vrms, f=1kHz

Volume=0dB

-0.5 0 0.5 dB

Voltage Gain 2

G

V2

V

IN

=1Vrms, f=1kHz

Volume=-20dB

-21 -20 -19 dB

Voltage Gain 3

G

V3

V

IN

=1Vrms, f=1kHz

Volume=-39.5dB

-42.0 -39.5 -37.0 dB

Voltage Gain Error

G

V

V

IN

=1Vrms, f=1kHz

Volume=-20dB , Ach - Bch

-0.5 0 0.5 dB

Mute Level

Mute

f=1kHz, V

IN

=1Vrms

Volume=Mute, A-weight

- -100 - dB

Output Noise

V

NO

Volume=0dB,

Rg=0,A-weight

-

-110

(3.2

µ)

-100

(10

µ)

dBV

(Vrms)

Total Harmonic Distortion

THD

f=1kHz,Vo=1Vrms,

Volume=0dB

BW : 400Hz - 30kHz

- 0.0015

0.05 %

Channel Separation

CS

f=1kHz,Vo=1Vrms,

Volume=0dB

Rg=0, A-weight

- -100 -90 dB

No.

SYMBOL FUNCTION

1 GND

Ground

2 R1IN

R channel Input 1

3 R2

IN

R channel Input 2

4 R3IN

R channel Input 3

5 R4IN

R channel Input 4

6 R5IN

R channel Input 5

7 ROUT

R channel Output

8 VSSOUT

Internal VSS Noise Rejection Capacitor Terminal

9 SCL

I

2

C Clock Input

10

SDA

I

2

C Data Input

11

VDDOUT

Internal VDD Noise Rejection Capacitor Terminal

12

VREFOUT

Reference Voltage Output

13

V+

Power Supply

14

VREFIN

Reference Voltage Noise Rejection Capacitor Terminal

15

LOUT

L channel Output

16

L5IN

L channel Input 5

17

L4IN

L channel Input 4

18

L3IN

L channel Input 3

19

L2IN

L channel Input 2

20

L1IN

L channel Input 1

1

10

11

20

NJW1156

≠ 3 ≠

PRELIMINARY

I

I

I

I I

2

C BUS BLOCK CHARACTERISTICS (SDA,SCL)

PARAMETER SYMBOL

MIN.

TYP.

MAX.

UNIT

High Level Input Voltage

V

IH

2.5 - 5.0 V

Low Level Input Voltage

V

IL

0 - 1.5 V

High Level Input Current

I

IH

- - 10

µA

Low Level Input Current

I

IL

- - 10

µA

Low Level Output Voltage (3mA at SDA pin)

V

OL

0 - 0.4 V

Maximum Output Current

I

OL

-3.0 -

- mA

Maximum Clock Frequency

f

SCL

- - 100

kHz

Data Change Minimum Waiting Time

t

BUF

4.7 -

-

µs

Data Transfer Start Minimum Waiting Time

t

HD:STA

4.0

-

-

µs

Low Level Clock Pulse Width

t

LOW

4.7 -

-

µs

High Level Clock Pulse Width

t

HIGH

4.0 -

-

µs

Minimum Start Preparation Waiting Time

t

SU:STA

4.7

-

-

µs

Minimum Data Hold Time

t

HD:DAT

5.0

-

-

µs

Minimum Data Preparation Time

t

SU:DAT

250

-

-

ns

Rise Time

t

R

- - 1.0

µs

Fall Time

t

F

- - 300

ns

Minimum Stop Preparation Waiting Time

t

SU:STO

4.0

-

-

µs

I

2

C BUS Load Condition:

Pull up resistance 4k

(Connected to +5V)

Load capacitance 200pF (Connected to GND)

SDA

SCL

t

BUF

t

HD:STA

Sr

P

t

LOW

t

R

t

HD:DAT

t

HIGH

t

F

t

SU:DAT

S

P

t

SU:STA

t

SU:STO

t

HD:STA

NJW1156

≠ 4 ≠

PRELIMINARY

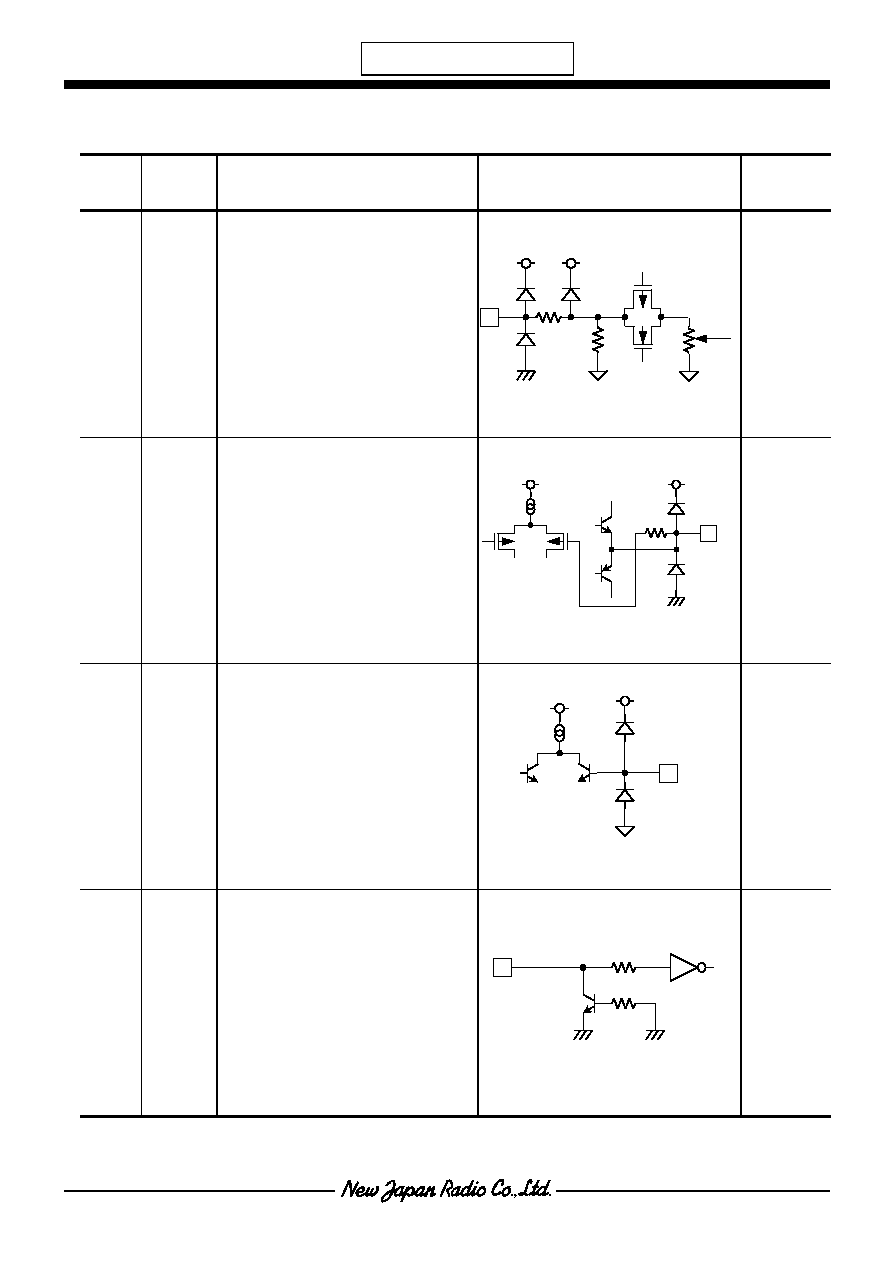

TERMINAL DESCRIPTION

PIN

NO.

SYMBOL FUNCTION

EQUIVALENT

CIRCUIT

TERMINAL

DC

VOLTAGE

2

3

4

5

6

16

17

18

19

20

R1IN

R2IN

R3IN

R4IN

R5IN

L5IN

L4IN

L3IN

L2IN

L1IN

R channel Input 1

R channel Input 2

R channel Input 3

R channel Input 4

R channel Input 5

L channel Input 5

L channel Input 4

L channel Input 3

L channel Input 2

L channel Input 1

V

+

/2

7

15

ROUT

LOUT

Rch Output

Lch Output

V

+

/2

8

11

VSS_OUT

VDD_OUT

Internal VSS Noise Rejection Capacitor Terminal

Internal VDD Noise Rejection Capacitor Terminal

VSS_OUT

=Vref ≠ 2.5V

VDD_OUT

=Vref + 2.5V

9 SCL

I

2

C Clock Input

-

GND

V+

400

V- (SUB)

V+

GND

4K

8K

VREF

GND

300

V+

50K

VREF

50K

NJW1156

≠ 5 ≠

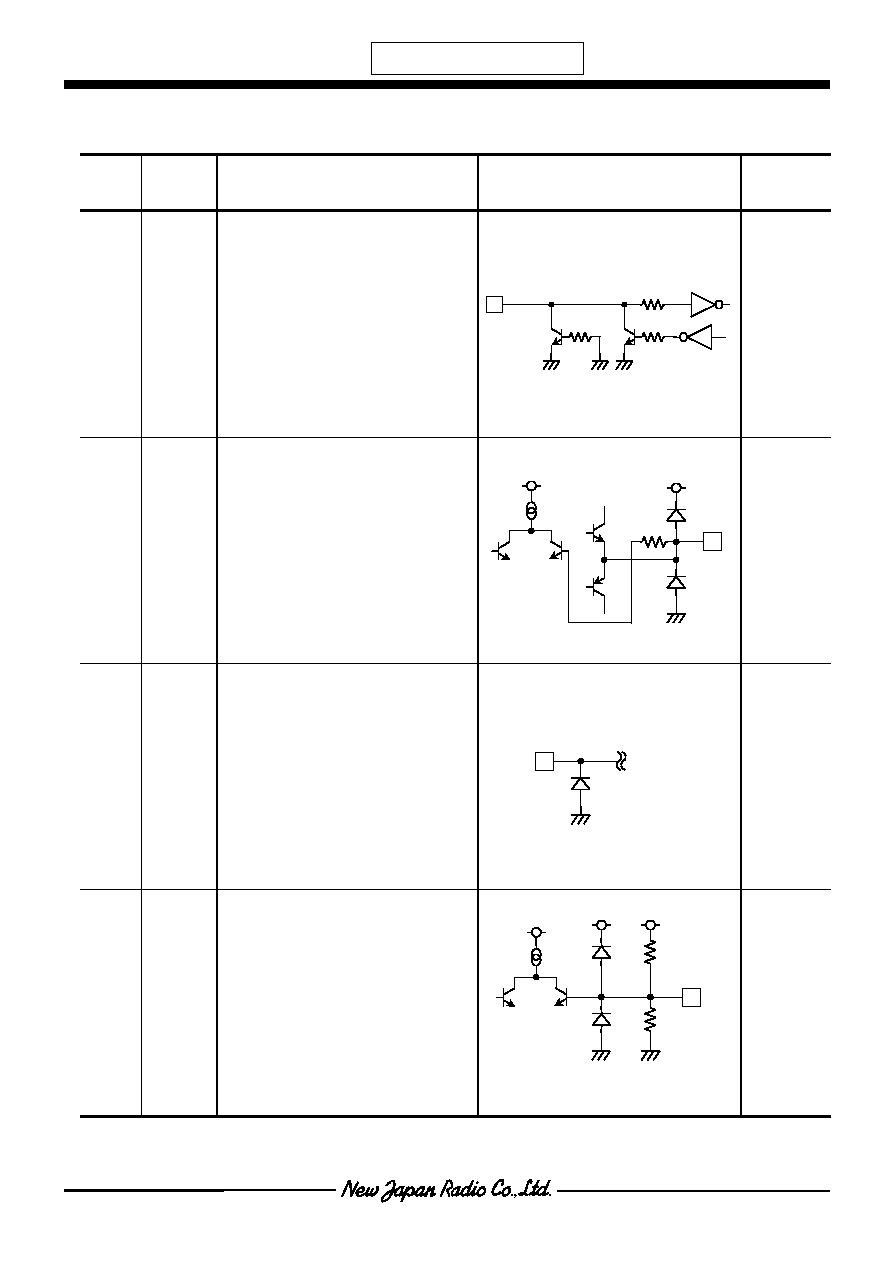

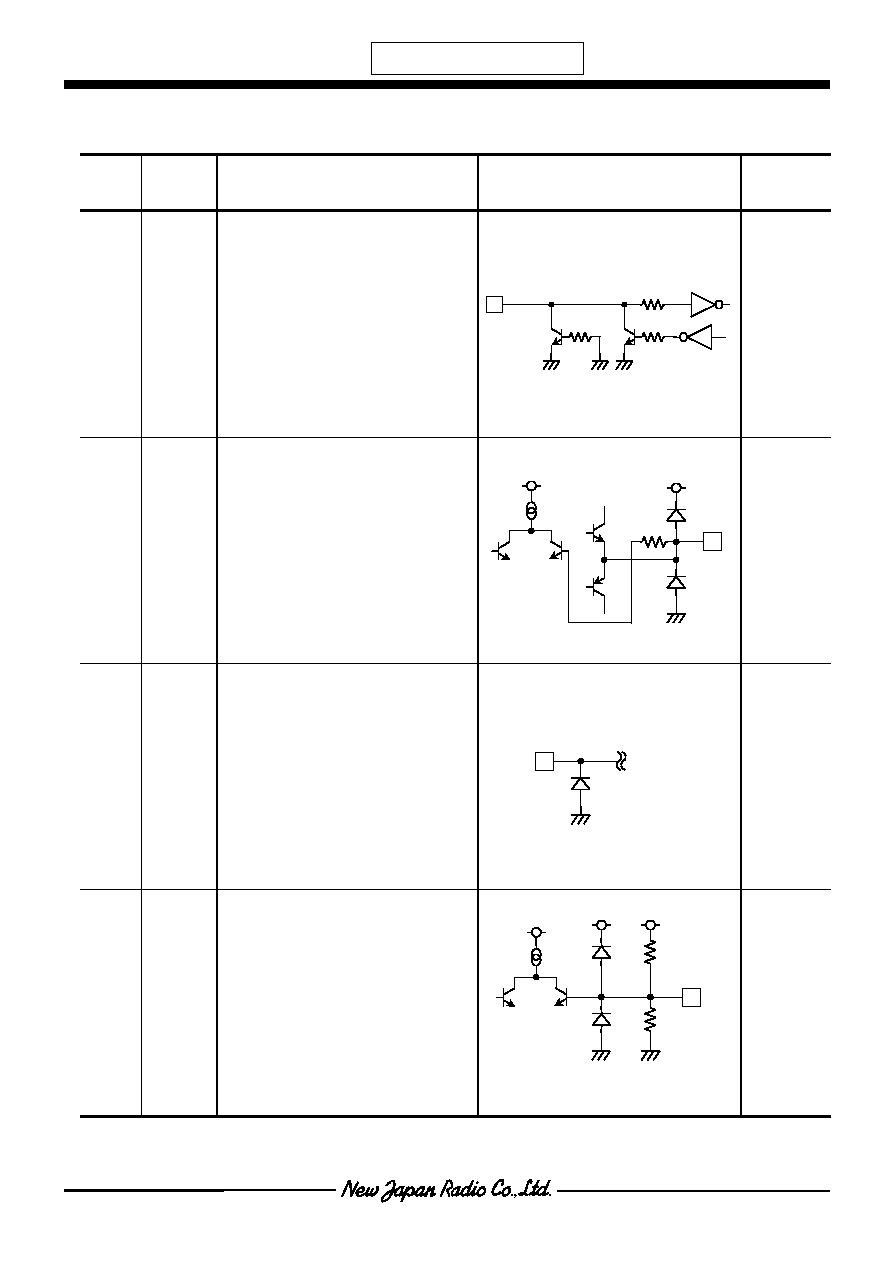

PRELIMINARY

TERMINAL DESCRIPTION

PIN

NO.

SYMBOL FUNCTION

EQUIVALENT

CIRCUIT

TERMINAL

DC

VOLTAGE

10 SDA I

2

C Data Input

-

12

VREFOUT Reference Voltage Output

V

+

/2

13 V+

Power

Supply

V+

14

VREFIN

Reference Voltage Noise Rejection Capacitor

Terminal

V

+

/2

4K

GND

8K

GND

V+

400

GND

50K

50K

GND

V+