NT7501

33 X 100 RAM-Map LCD Controller/Driver

1

V2.0

Features

!

Direct RAM data display using the display RAM. When

RAM data bit is 0, it is not displayed. When RAM data bit

is 1, it is displayed. (In normal display mode)

!

RAM capacity: 65 X 132 = 8580 bits

!

Many command functions: Read/Write Display Data,

Display ON/OFF, Normal/Reverse Display, Page

Address Set, Set Display Start Line, Set LCD Bias,

Electronic contrast Controls, Read Modify Write, Select

Segment Driver Direction and Power Save

!

High-speed 8-bit microprocessor interface allowing direct

connection to both the 8080 and 6800

!

Serial interface

!

Single supply operation, 2.4 - 3.5V

!

Maximum 9V LCD driving output voltage

!

2X / 3X / 4X on chip DC-DC converter

!

Voltage regulator

!

Voltage follower (LCD bias: 1/5 or 1/6)

!

On chip oscillator

General Description

The NT7501 is a single-chip LCD driver for dot-matrix liquid

crystal displays, which is directly connectable to a

microcomputer bus. It accepts 8-bit serial or parallel display

data directly sent from a microcomputer and stores it in an

on-chip display RAM. It generates a LCD drive signal

independent of the microprocessor clock.

The set of the on-chip display RAM of 65 X 132 bits, and a

one-to-one correspondence between the LCD panel pixel

dots and the on-chip RAM bits, permits implementation of

displays with a high degree of freedom.

As a total of 133 circuits of common and segment outputs

are incorporated, a single chip of NT7501 can make 33 X

100 dots displays.

No external operation clock is required for RAM read/write

operations. Accordingly, this driver can be operated with

minimum current consumption and its on-board low-current-

consumption liquid crystal power supply can implement a

high-performance handy display system with minimal current

consumption and a minute LSI configuration.

NT7501

2

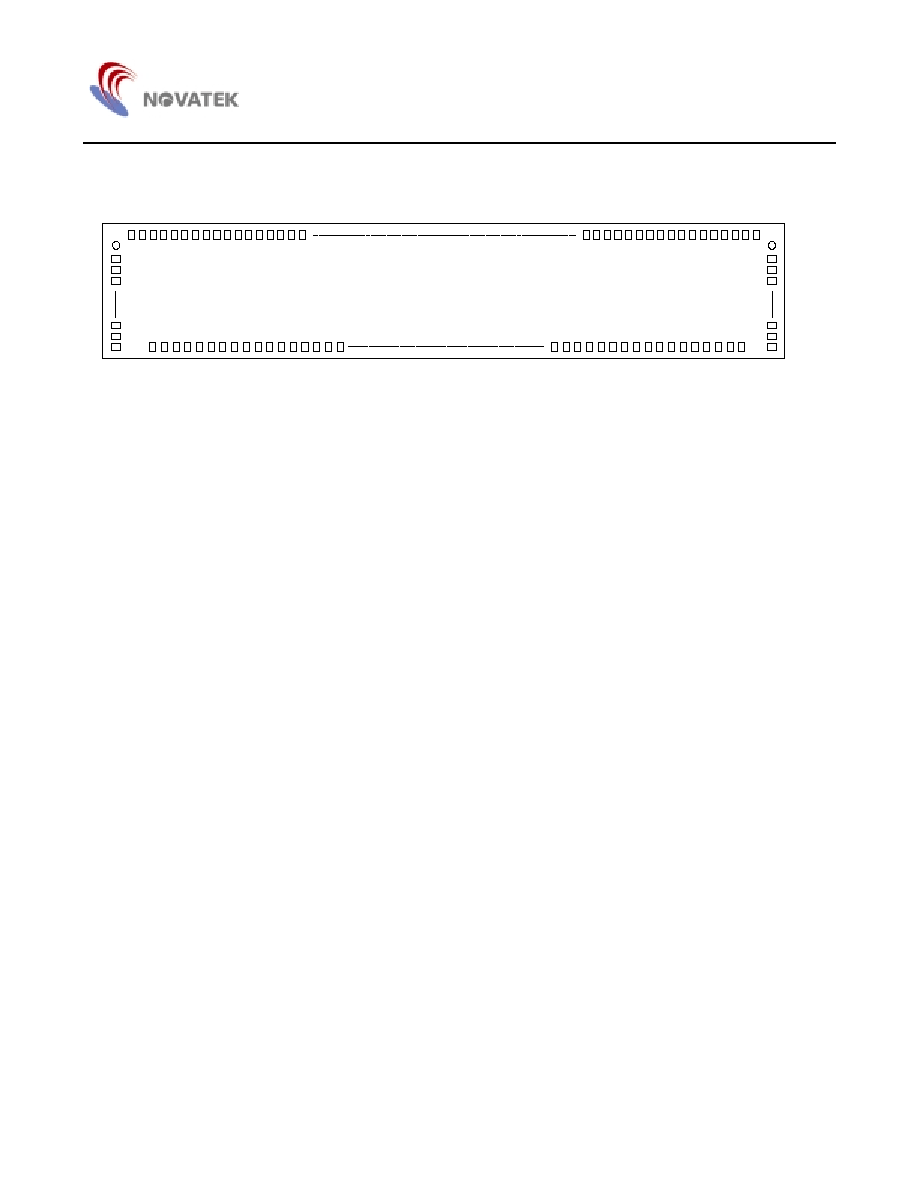

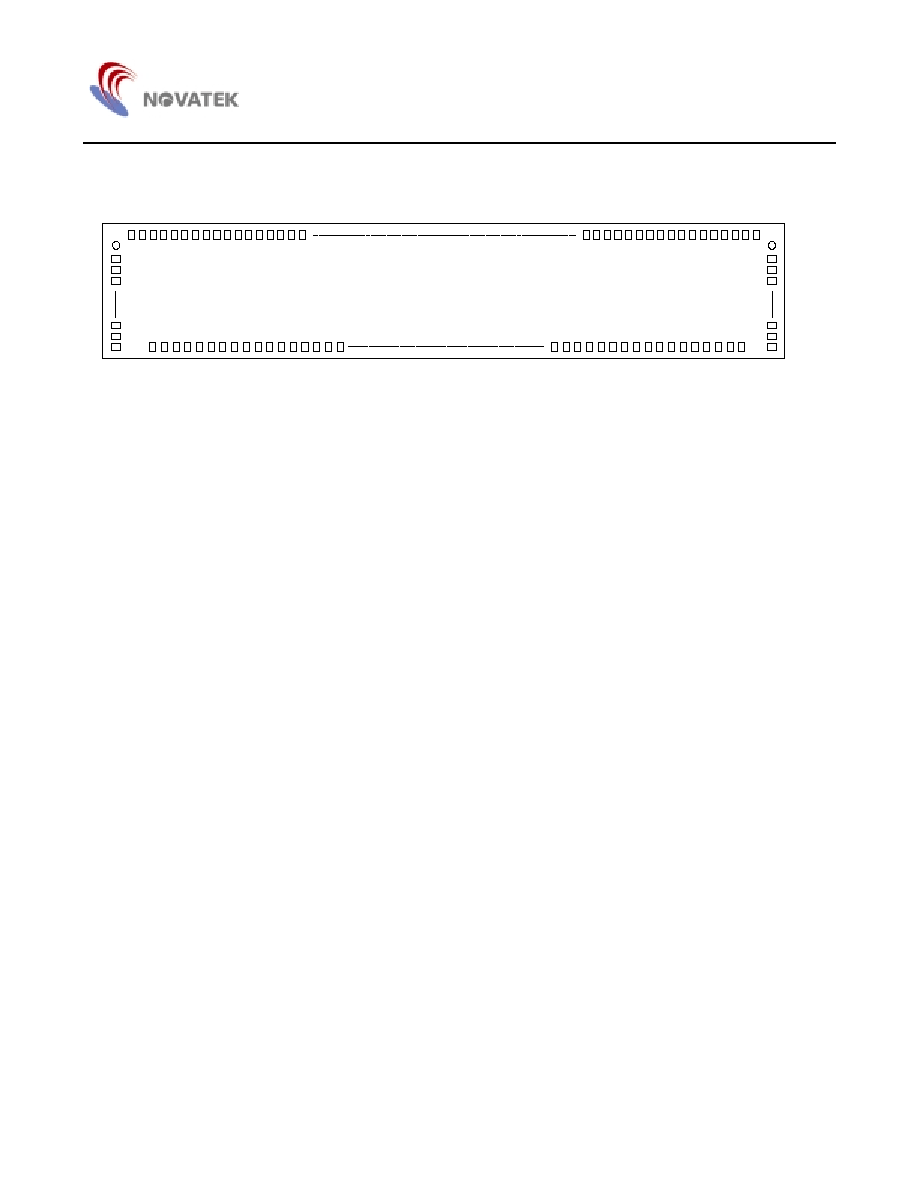

Pad Configuration

198

200

212

214

98

114

197

181

64

80

1

17

180~113

94~82

18~63

211~199

81

83

97

95

NT7501

NT7501

3

Block Diagram

Segment driver

Common

driver

Shift register

COM S

Power Supply

Circuit

Display data latch

132*65-dot

display data RAM

line address decoder

I/O buffer circuit

Line counter

Initial display line register

Output

status

selector

circuit

Column address decoder

8-bit column address counter

8-bit column address counter

Page address

register

Display timing

generator

circuit

Bus holder

Command decoder

Bus holder

Oscillator

Microprocessor interface

I/O buffer

SEG0

SEG99 COM0 COM31 COMS

V

0

V2

V4

V1

V3

Vss

CAP1+

CAP1-

CAP2+

CAP2-

CAP3+

V

OUT

V

R

FRS

FR

CL

DYO

DOF

M/S

VS1

CS2

A0

RD

(E)

WR

)

W

/

R

(

C86

P/S RES

1

CS

V

DD

D7

(SI)

D5

D4

D3

D2

D1

D0

D6

(SCL)

TPS0

TPS1

NT7501

4

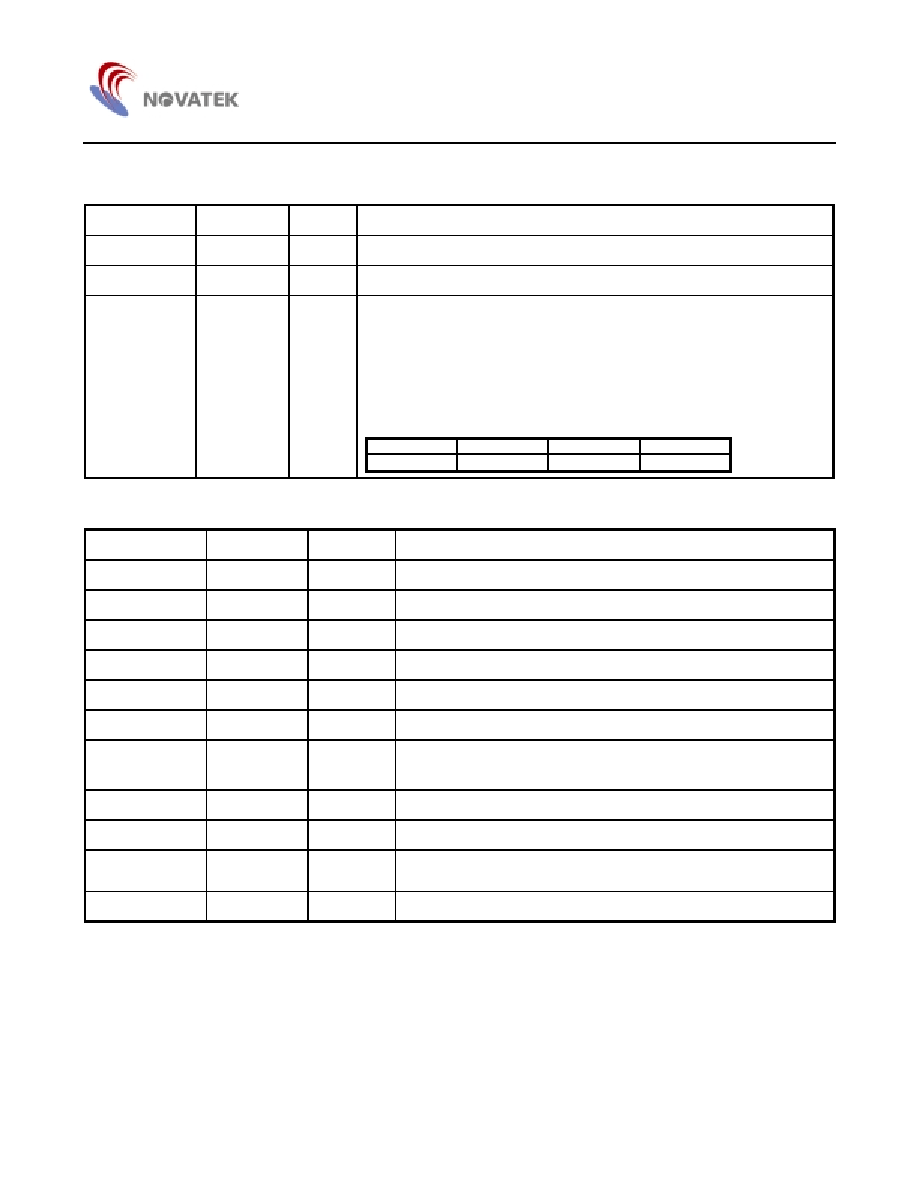

Pad Description

Power Supply

Pad No.

Symbol

I/O

Description

20 - 26

V

DD

Supply

2.4 - 3.5V power supply input. These pads must be connected to each other

35 - 42

V

SS

Supply

Ground input. These pads must be connected to each other

63 - 64

65 - 66

67 - 68

69 - 70

71 - 72

V

0

V

1

V

2

V

3

V

4

Supply

LCD driver supply voltages. The voltage determined by the LCD cell is

impedance-converted by a resistive driver or an operation amplifier for

application. Voltages should have the following relationship:

V

0

V

1

V

2

V

3

V

4

V

SS

When the on-chip operating power circuit is on, the following voltages are

given to V

1

to V

4

by the on-chip power circuit. Voltage selection is performed

by the Set LCD Bias command

V1

V2

V3

V4

4/5V0, 5/6V0 3/5V0, 4/6V0 2/5V0, 2/6V0 1/5V0, 1/6V0

LCD Driver Supplies

Pad No.

Symbol

I/O

Description

47 - 48

CAP1-

O

Capacitor 1- pad for internal DC/DC voltage converter

49 - 50

CAP1+

O

Capacitor 1+ pad for internal DC/DC voltage converter

51 - 52

CAP2-

O

Capacitor 2- pad for internal DC/DC voltage converter

53 - 54

CAP2+

O

Capacitor 2+ pad for internal DC/DC voltage converter

45 - 46

CAP3+

O

Capacitor 3+ pad for internal DC/DC voltage converter

12, 61 - 62, 77

V

DD

Supply

Used for pad option or to connect to power filter capacitor

9, 15, 59 - 60,

73 - 74

V

SS

Supply

Used for pad option or to connect to power filter capacitor

43 - 44

V

OUT

O

DC/DC voltage converter output

55 - 56

V

0

O

Connect to Rb

57 - 58

V

R

I

Voltage adjustment pad. Applies voltage between V

0

and V

SS

using a

resistive divider

75 - 76

TPS0, TPS1

I

Selects the temperature coefficient of the reference voltage

NT7501

5

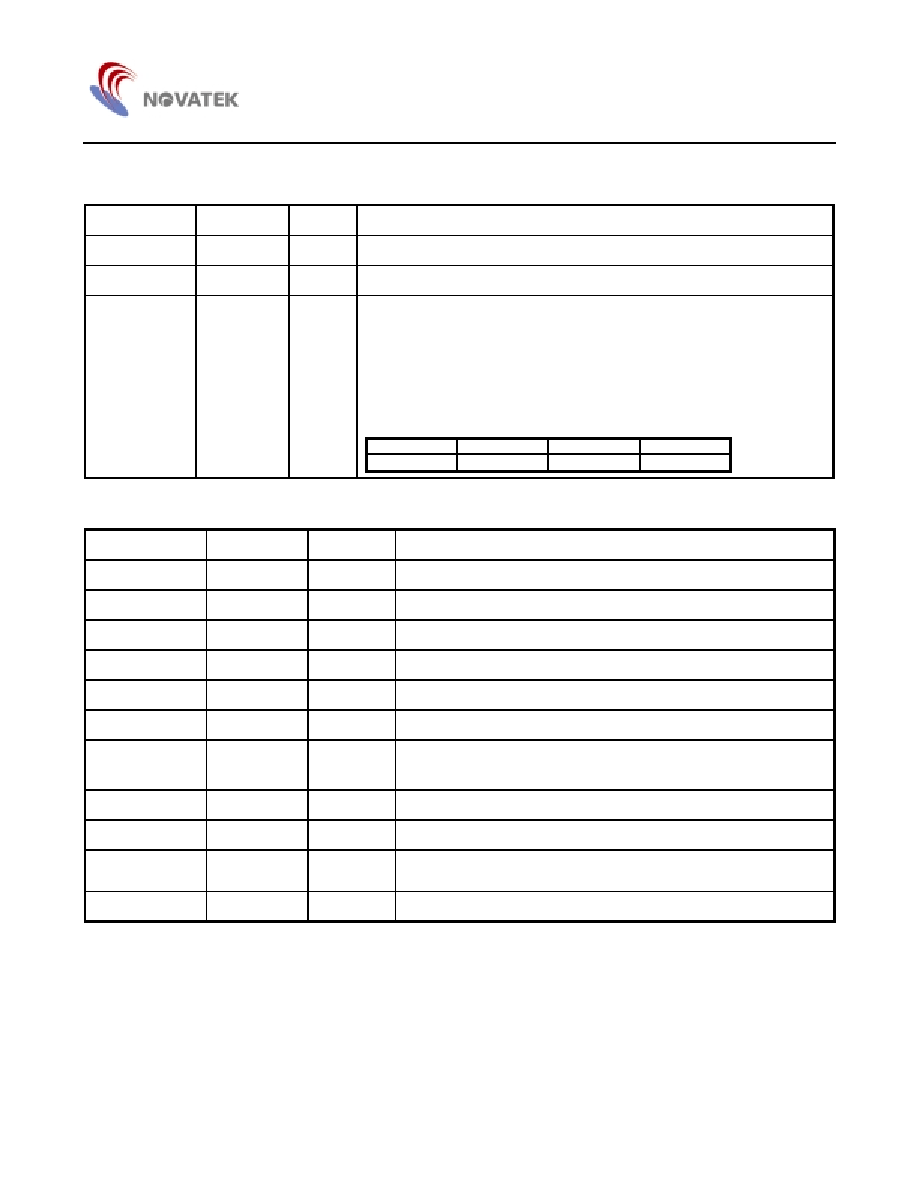

System Bus Connection Terminals

Pad No.

Symbol

I/O

Description

27 - 34

D0 - D7

(SI)

(SCL)

I/O

This is an 8-bit bi-directional data bus that connects to an 8-bit or 16-bit

standard MPU data bus.

When the serial interface is selected (P/S = "L"), then D7 serves as the

serial data input terminal (SI) and D6 serves as the serial clock input

terminal (SCL). At this time, D0 to D5 are set to high impedance.

When the chip select is inactive, D0 to D7 are set to high impedance.

16

A0

I

This is connected to the least significant bit of the normal MPU address

bus, and it determines whether the data bits are data or a command.

A0 = "H": Indicate that D0 to D7 are display data.

A0 = "L": Indicates that D0 to D7 are control data.

8

RES

I

When RES is set to "L", the settings are initialized.

The reset operation is performed by the RES signal level.

11 - 13

1

CS CS2

I

This is the chip select signal. When

1

CS = "L" and CS2 = "H", then the

chip select becomes active and data/command I/O are enabled

18

RD

(E)

I

When connected to an 8080 MPU, it is active LOW. This pad is

connected to the RD signal of the 8080MPU, and the NT7501 data bus

is in an output statue when this signal is "L".

When connected to a 6800 Series MPU, this is active HIGH. This is

used as an enable clock input of the 6800 series MPU.

17

WR

(

W

R

)

I

When connected to an 8080 MPU, this is active LOW. This terminal

connects to the 8080 MPU WR signal . The signals on the data bus are

latched at the rising edge of the WR signal.

When connected to a 6800 Series MPU: This is the read/write control

signal input terminal.

When

W

R

= "H": Read.

When

W

R

= "L": Write.

14

C86

I

This is the MPU interface switch terminal.

C86 = "H": 6800 Series MPU interface.

C86 = "L": 8080 Series MPU interface.

10

P/S

I

This is the parallel data input/serial data input switch terminal.

P/S = "H": Parallel data input.

P/S = "L": Serial data input.

The following applies depending on the P/S status:

P/S Data/Command

Data

Read/Write Serial

Clock

"H"

A0

D0 to D7

"L"

A0

SI (D7)

Write only

SCL (D6)

RD WR

When P/S = "L", D0 to D5 are HZ. D0 to D5 may be "H", "L" or Open.

RD (E) and WR (

W

/

R

) are fixed to either "H" or "L". With serial data

input, RAM display data reading is not supported.

7

M/S

I

This terminal selects the master/slave operation for the NT7501 chips.

Master operation outputs the timing signals that are required for the

LCD display, while slave operation inputs the timing signals required for

the liquid crystal display, synchronizing the liquid crystal display system.

4

CL

I/O

This is the display clock input terminal. When the NT7501 chips are

used in master/slave mode, the various CL terminals must be

connected.