| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: NT7703 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

NT7703

160 Output LCD Segment/Common Driver

1

V1.0

Features

(Segment mode)

!

Shift Clock frequency:

14 MHz (Max.) (V

DD

= 5V

±

10%)

8 MHz (Max.) (V

DD

= 2.5V - 4.5V)

!

Adopts a data bus system

!

4-bit / 8-bit parallel input modes are selectable with a

mode (MD) pin

!

Automatic transfer function with an enable signal

!

Automatic counting function when in "chip select" mode,

which causes the internal clock to be stopped by

automatically counting 160 bits of input data

(Common mode)

!

Shift clock frequency:

4.0MHz (Max.)

!

Built-in 160-bits bidirectional shift register (divisible into

80-bits x 2)

!

Available in a single mode (160-bits shift register) or in a

dual mode (80-bits shift register x 2)

1. Y1

Y160

Single mode

2. Y160

Y1

Single mode

3. Y1

Y80, Y81

Y160

Dual mode

4. Y160

Y81, Y80

Y1

Dual mode

The above 4 shift directions are pin-selectable

(Both segment mode and common mode)

!

Supply voltage for LCD drive: 15.0 to 30.0V

!

Number of LCD driver outputs: 160

!

Low output impedance

!

Low power consumption

!

Supply voltage for the logic system: +2.5 to +5.5V

!

COMS process

!

Package: Gold bump die / 186 Pin TCP (Tape Carrier

Package)

!

Not designed or rated as radiation hardened

General Description

The NT7703 is a 160-bit output segment/common driver LSI

suitable for driving the large scale dot matrix LCD panels

used by PDA's, personal computers and work stations for

example. Through the use of COG technology, it is ideal for

substantially decreasing the size of the frame section of the

LCD module. The NT7703 is good as both a segment driver

and a common driver, and a low power consuming, high-

precision LCD panel display can be assembled using the

NT7703. In the segment mode, the data input is selected as

4bit parallel input mode or as 8bit parallel input mode by a

mode (MD) pin. In common mode, the data input/output pins

are bi-directional and the four data shift directions are pin-

selectable.

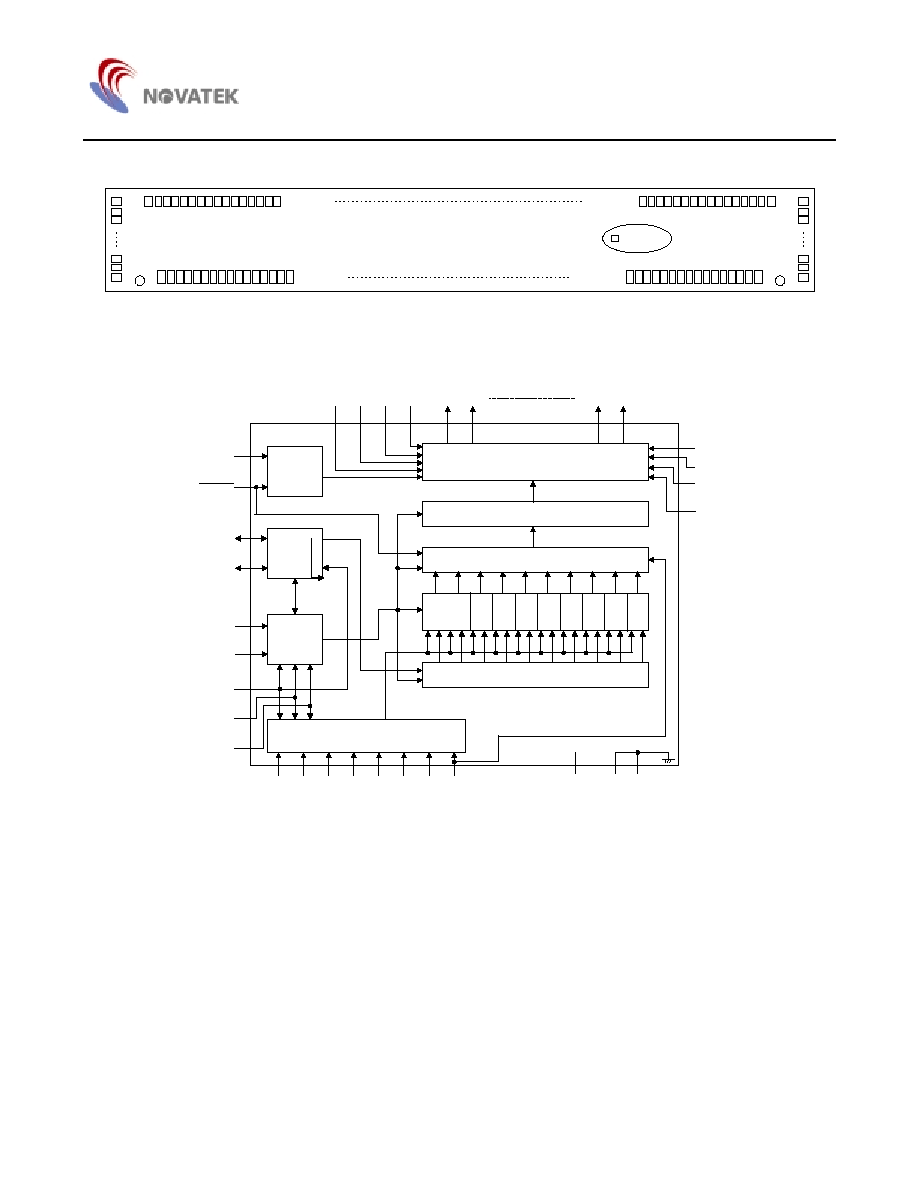

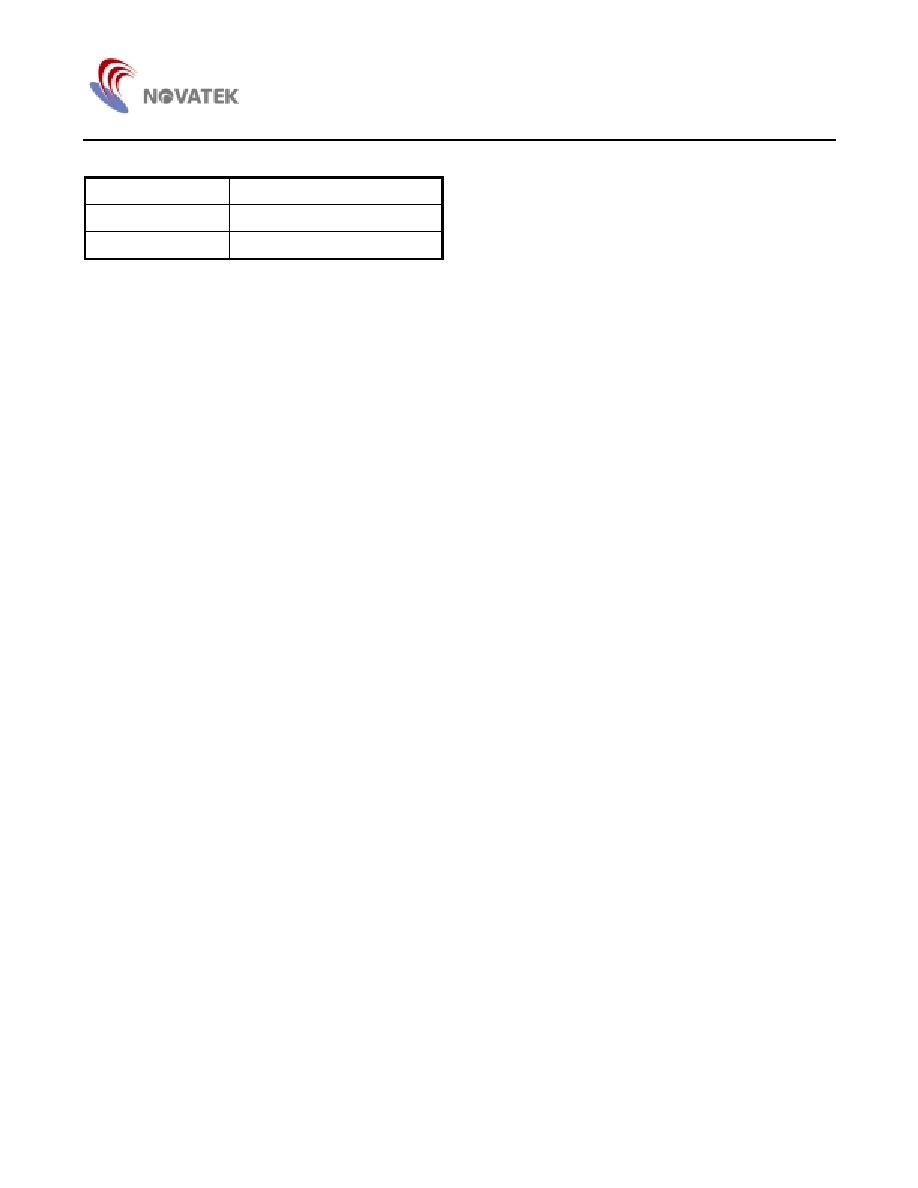

Pin Configuration

NT7703

1

V

0

L

2

3

4

5

6

7

8

9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26

V

1

2

L

V

4

3

L

V

S

S

/

V

5

L

L

/

R

V

D

D

S

/

C

E

I

O

2

D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

X

C

K

L

P

E

I

O

1

F

R

M

D

V

4

3

R

V

1

2

R

V

0

R

D

I

S

P

O

F

F

27

D

U

M

M

Y

D

U

M

M

Y

D

U

M

M

Y

D

U

M

M

Y

105

Y

8

3

Y

8

2

Y

8

1

Y

8

0

Y

7

9

Y

7

8

106

107

108

109

104

28

Y

6

Y

5

Y

4

Y

3

Y

2

Y

1

29

30

31

32

185

Y

1

5

5

Y

1

5

6

Y

1

5

7

Y

1

5

8

Y

1

5

9

Y

1

6

0

184 183 182 181

186

D

U

M

M

Y

D

U

M

M

Y

D

U

M

M

Y

D

U

M

M

Y

V

S

S

/

V

5

R

NT7703

2

Pad Configuration

NT7703

1

x

ALK_L

x

x

ALK_R

x

x

Dummy Pad

x

128

129

144

145

272

273

288

x

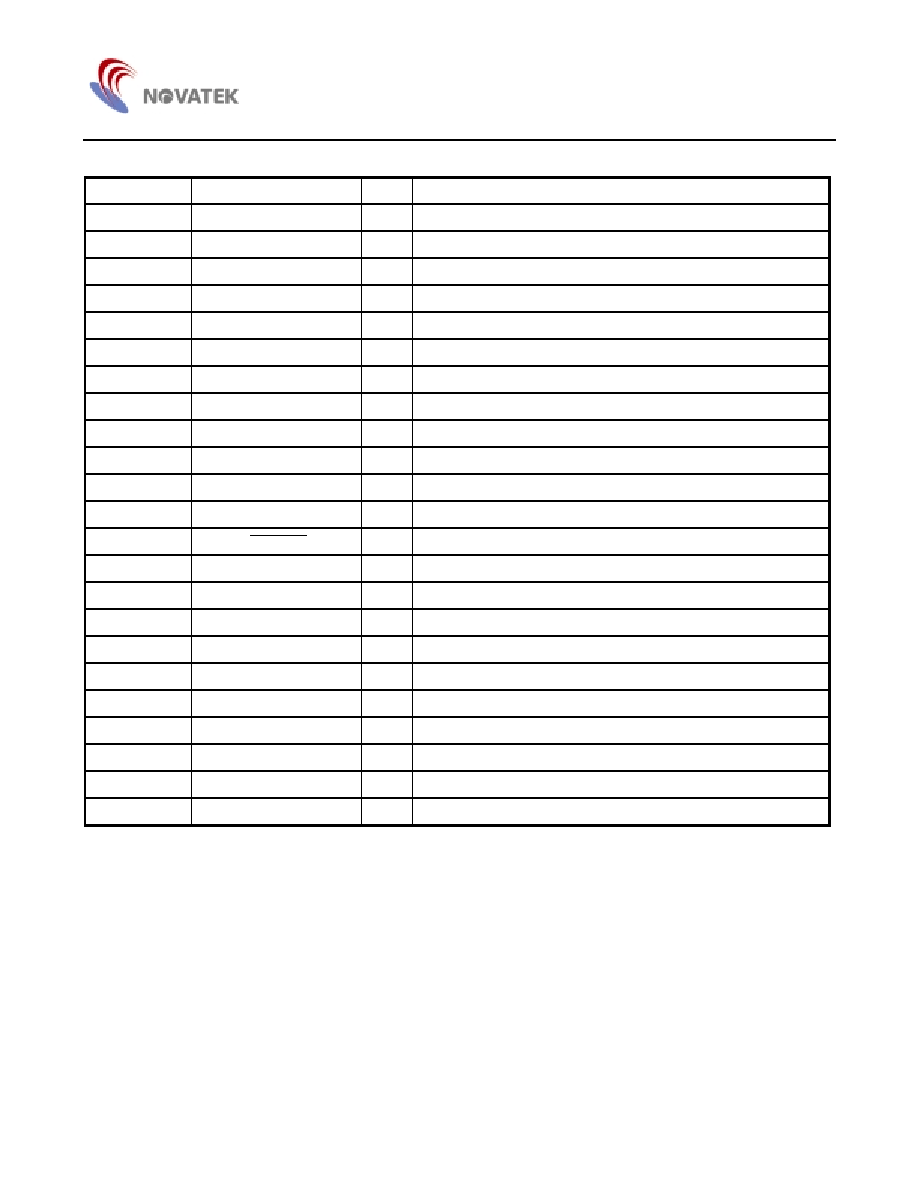

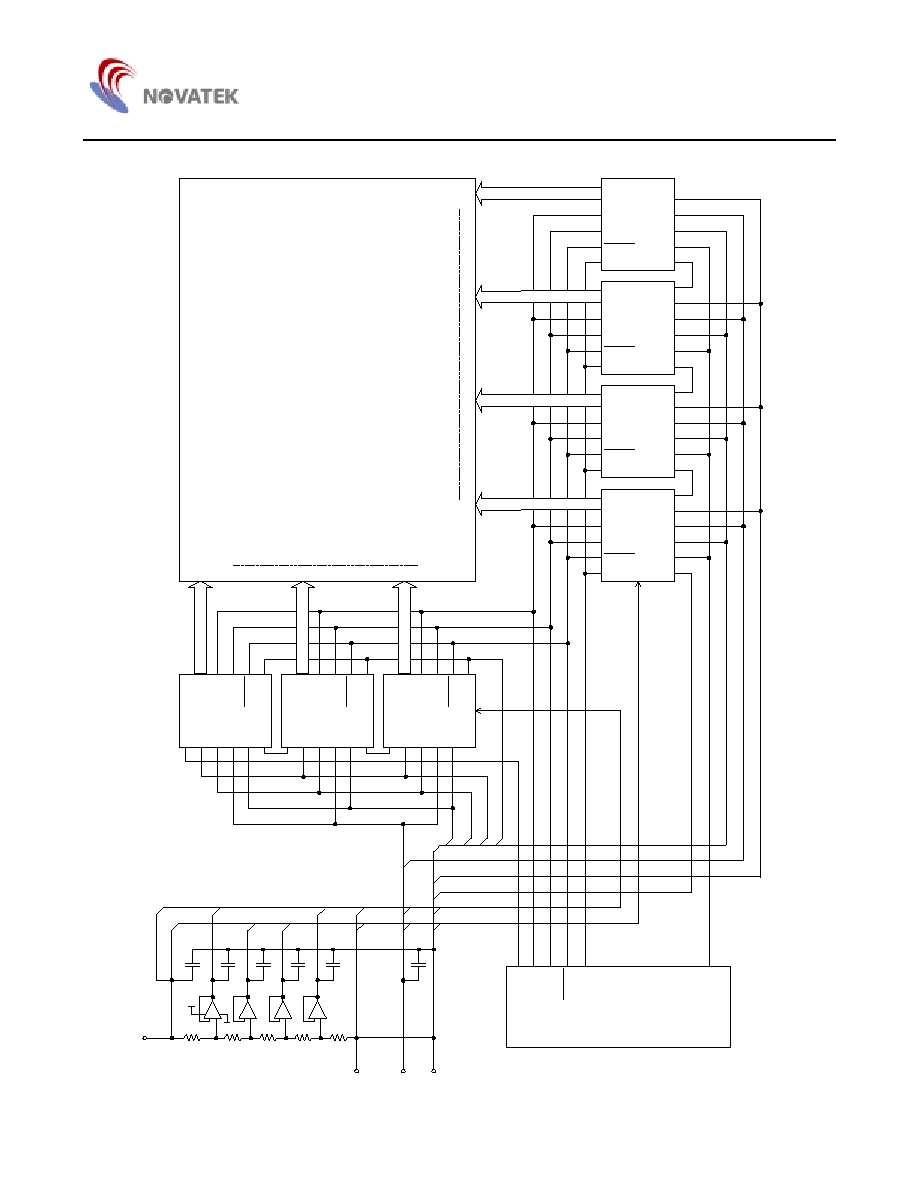

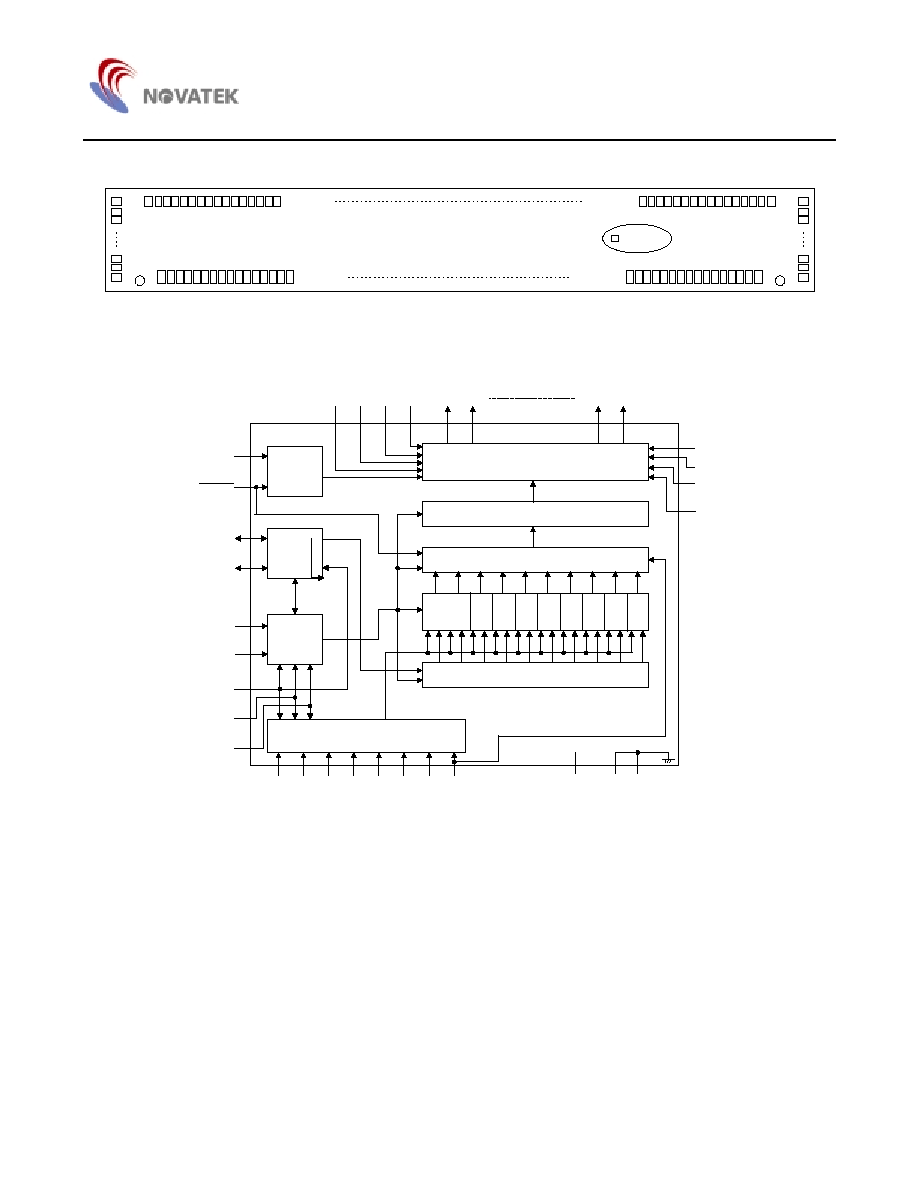

Block Diagram

160 Bits 4 Level Driver

160 Bits Level Shifter

160 Bits Line Latch/Shift Register

Y1

Y2

Y159 Y160

Level

Shifter

FR

DISPOFF

Active

Control

EIO

1

EIO

2

Control

Logic

SP Conversion & Data Control

(4 to 8 or 8 to 8)

DI

0

DI

1

DI

2

DI

3

DI

4

DI

5

DI

6

DI

7

L/R

MD

S/C

8Bits x 2

Data

Latch

Data Latch Control

/8

/160

/160

VDD

VSS VSS

/16

/16

/16

/16

/16

/16

/16

/16

/16

/16

LP

XCK

V

5R

V

5L

V

12L

V

0L

V

43L

V

43R

V

12R

V

0R

V

5R

NT7703

3

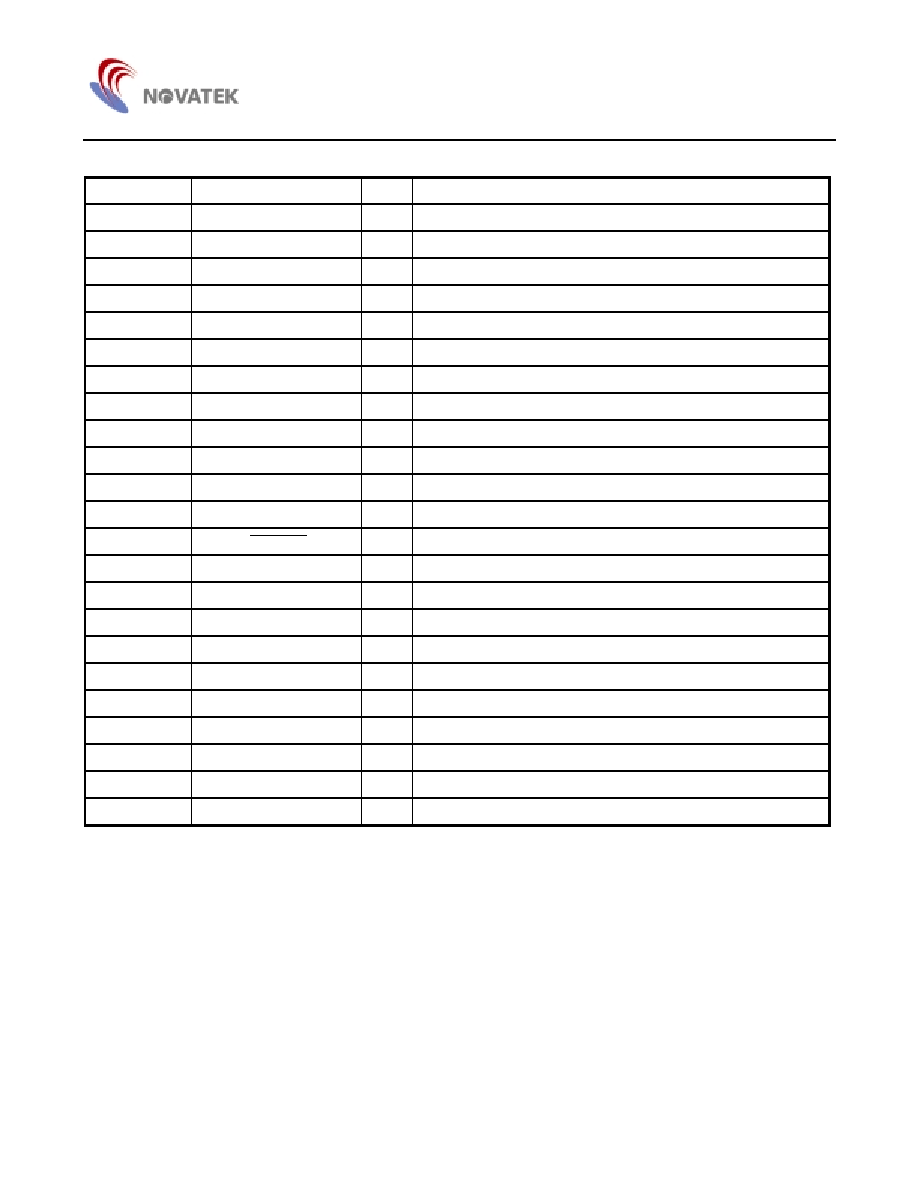

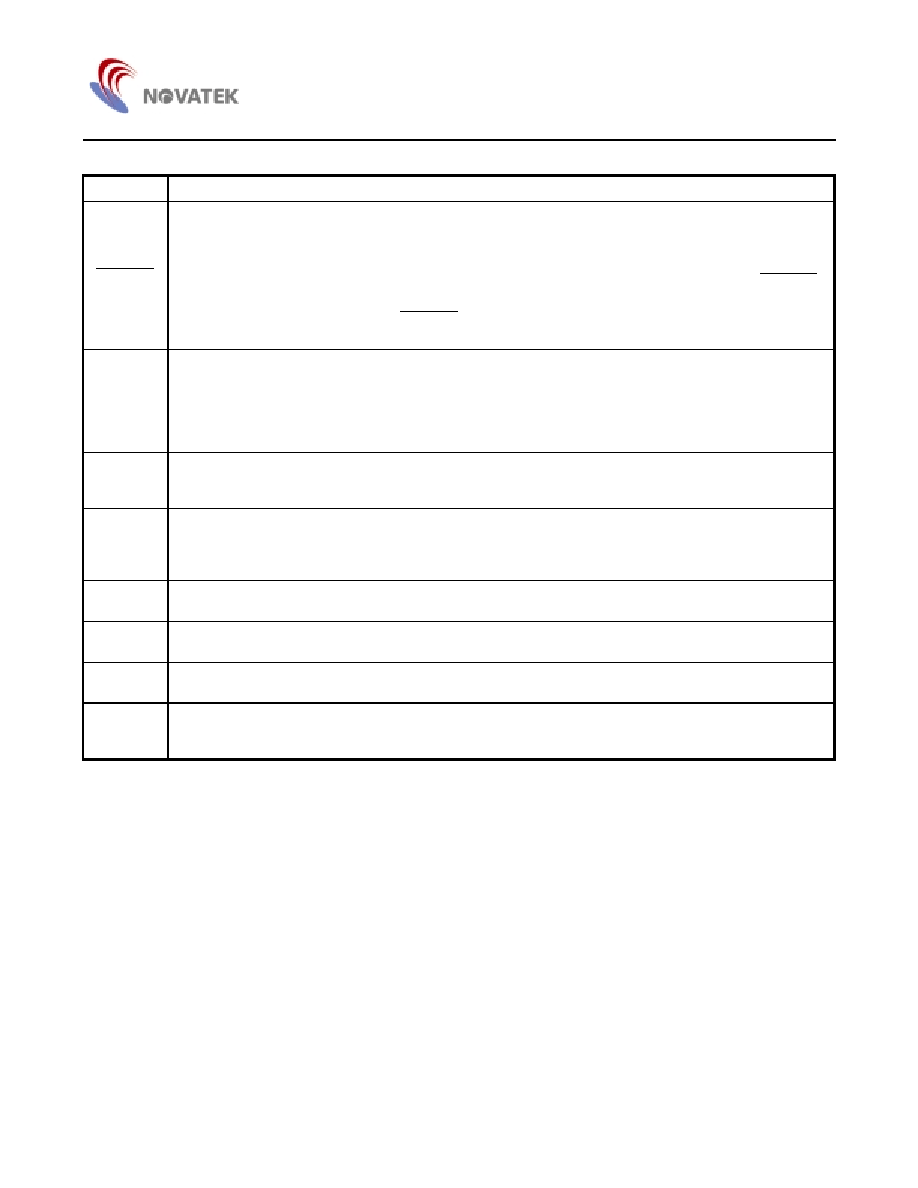

Pad Description

Pad No.

Designation

I/O

Description

1 - 7

V

0L

P

Power supply for LCD driver

8 - 12

V

12L

P

Power supply for LCD driver

13 - 17

V

43L

P

Power supply for LCD driver

18 - 22

V

5L

P

Power supply for LCD driver

23 - 39

V

SS

P

Ground (0V), these two pads must be connected to each other

40 - 41

L/R

I

Display data shift direction selection

42 - 57

V

DD

P

Power supply for the logic system (+2.5 to + 5.5V)

58 - 59

S/C

I

Segment mode / common mode selection

60 - 61

EIO

2

I/O

Input / output for chip select or data of shift register

62, 63 - 74, 75

D0 - D6

I

Display data input for segment mode

76 - 77

D7

I

Display data input for Segment mode / Dual mode data input

78 - 79

XCK

I

Display data shift clock input for segment mode

80 - 81

DISPOFF

I

Control input for deselect output level

82 - 83

LP

I

Latch pulse input / shift clock input for the shift register

84 - 85

EIO

1

I/O

Input / output for chip select or data of the shift register

86 - 87

FR

I

AC-converting signal input for LCD driver waveform

88 - 89

MD

I

Mode selection input

90 - 106

V

SS

P

Ground (0V), these two pads must be connected to each other

107 - 111

V

5R

P

Power supply for LCD driver

112 - 116

V

43R

P

Power supply for LCD driver

117 - 121

V

12R

P

Power supply for LCD driver

122 - 128

V

0R

P

Power supply for LCD driver

129 - 288

Y1 - Y160

O

LCD driver output

NT7703

4

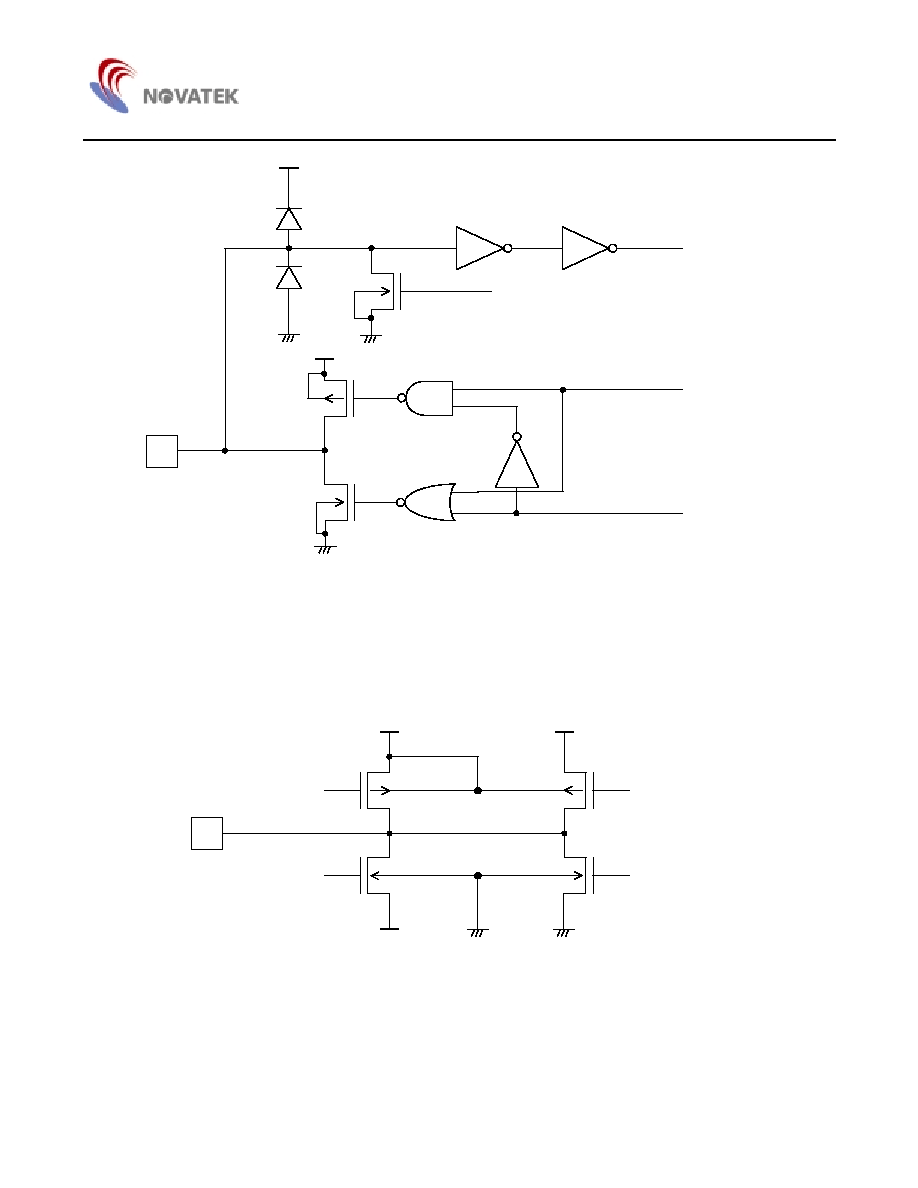

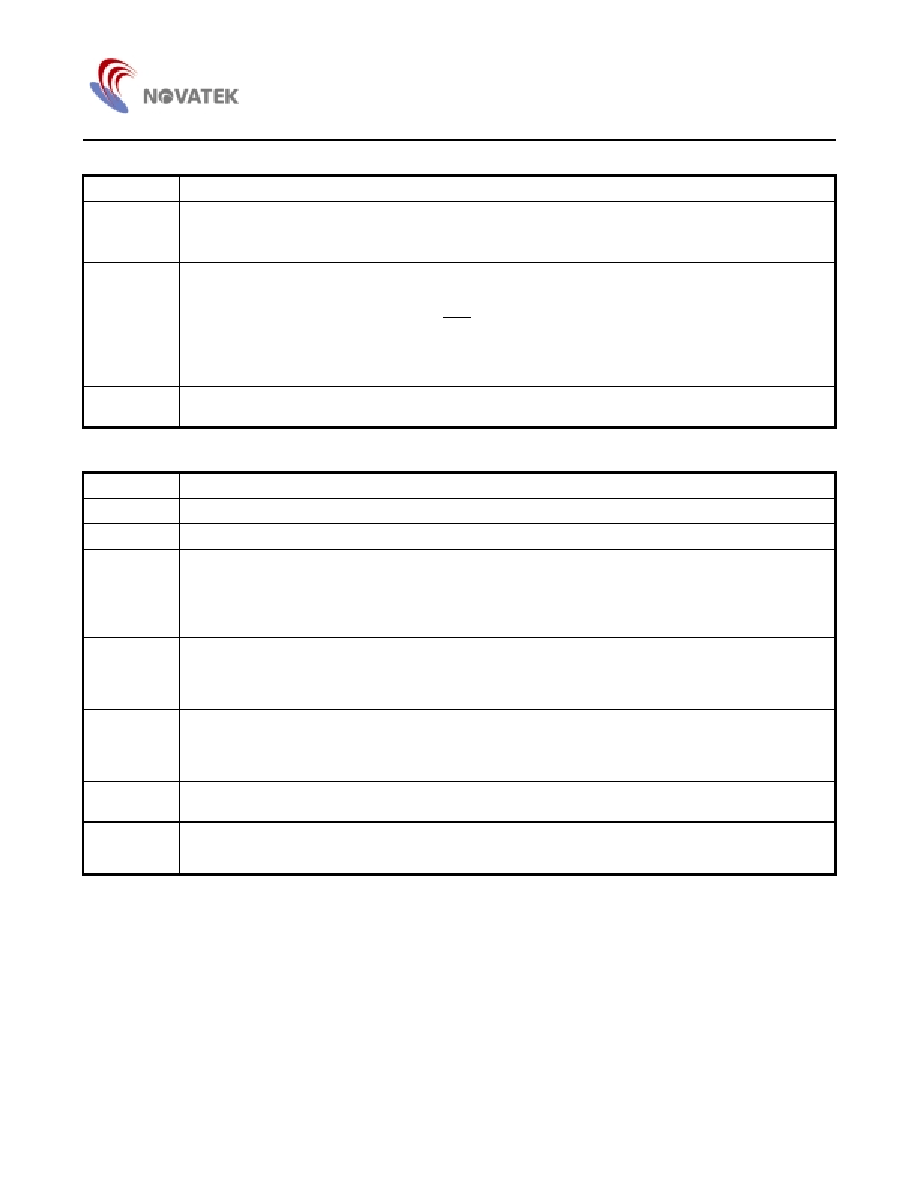

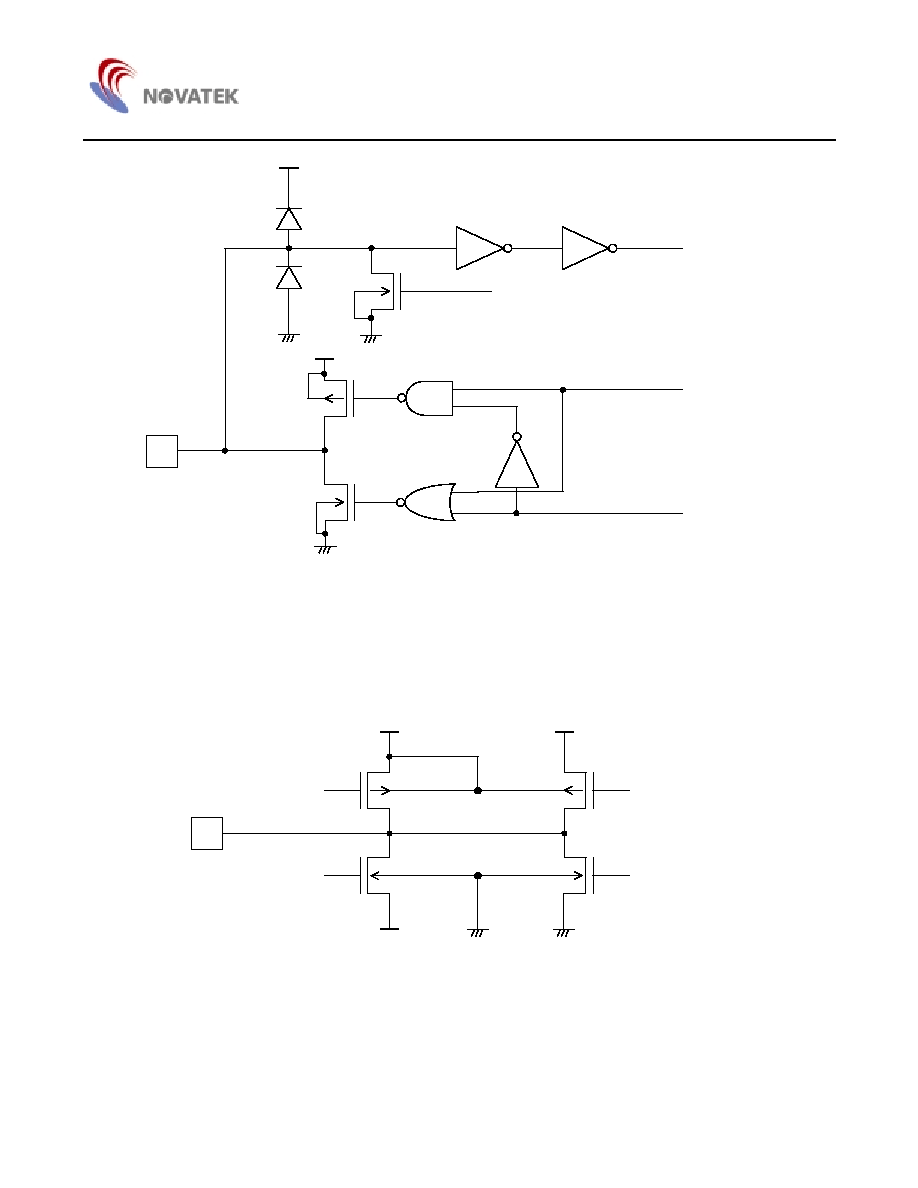

Input / Output Circuits

V

DD

V

SS

I

Input Signal

Applicable Pins

L/R, S/C, D0 - D6,

, LP, FR, MD

DISPOFF

Input Circuit (1)

V

DD

I

V

SS

V

SS

Input Signal

Control Signal

Applicable Pins

D7, XCK

Input Circuit (2)

NT7703

5

V

DD

I/O

V

SS

V

SS

Input Signal

Control Signal

Applicable Pins

EIO1, EIO2

Output Signal

Control Signal

V

SS

V

DD

Input / Output Circuit

Control Signal 1

Control Signal 3

Control Signal 2

Control Signal 4

V0

V12

O

V43

Applicable Pins

Y1 to Y160

V5

V

SS

LCD Driver Output circuit

NT7703

6

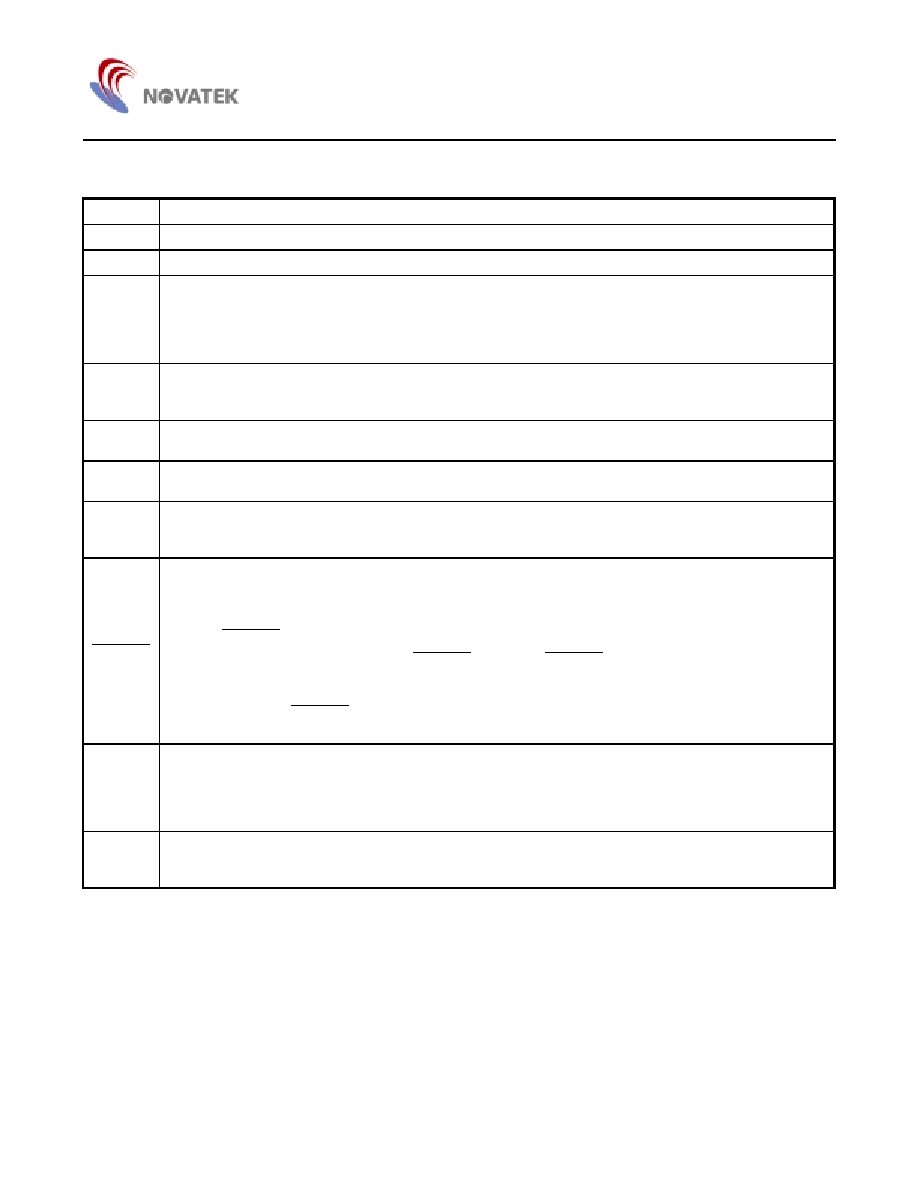

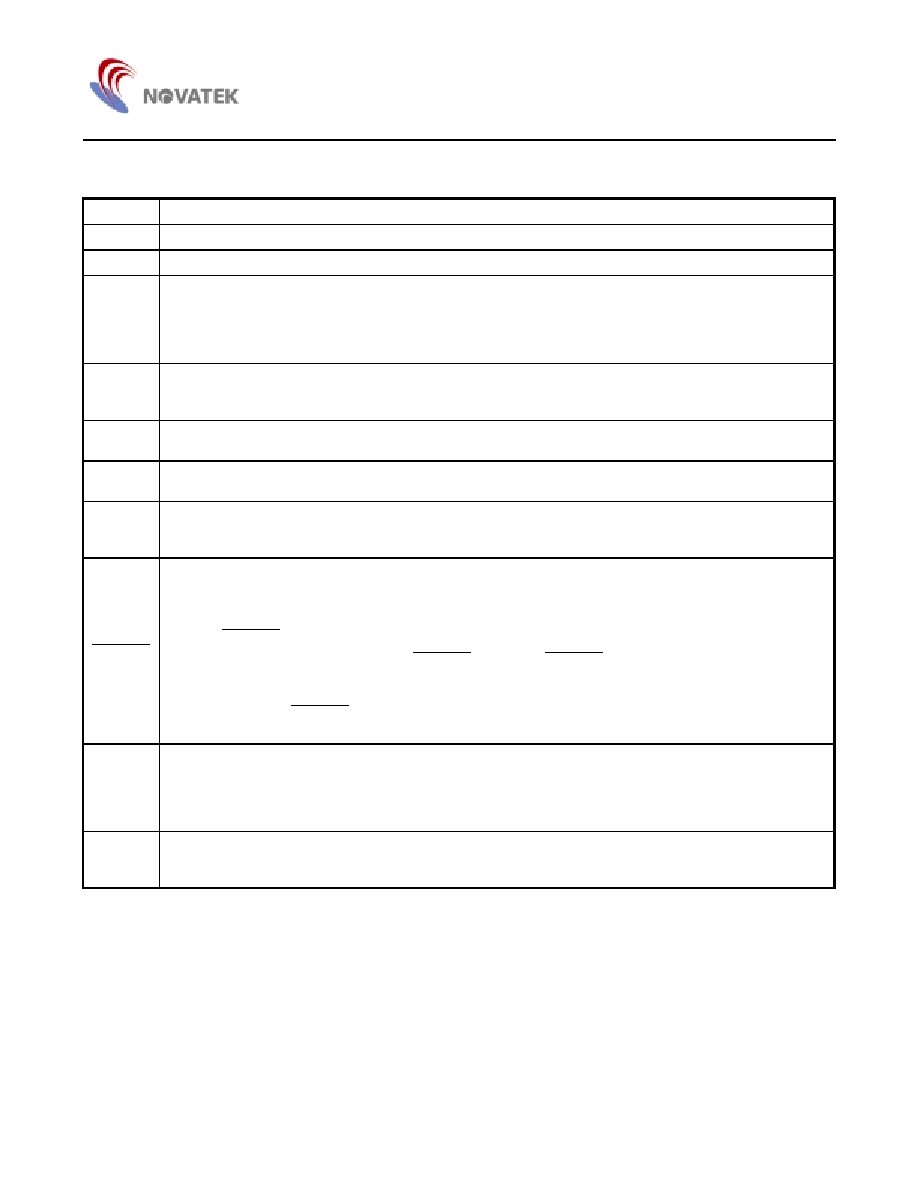

Pad Description

Segment mode

Symbol

Function

V

DD

Logic system power supply pin connects from +2.5 to +5.5V

V

SS

Ground pin connects to 0V

V

OR

, V

OL

V

12R

, V

12L

V

43R

, V

43L

V

5R

, V

5L

Power supply pin for LCD driver voltage bias

"

Normally, the bias voltage used is set by a resistor divider

"

Ensure that the voltages are set such that V

SS

V

5

< V

43

< V

12

< V

0

"

To further reduce the differences between the output waveforms of the LCD driver output pins Y

1

and Y

160,

externally connect V

iR

and V

iL

(I = 0, 12, 43)

D

0

-

D

7

Input pin for display data

"

In 4-bit parallel input mode, input data into the 4 pins D

0

-

D

3

. Connect D

4

-

D

7

to V

SS

or V

DD

"

In 8-bit parallel input mode, input data into the 8 pins D

0

-

D

7

XCK

Clock input pin for taking display data

"

Data is read on the falling edge of the clock pulse

LP

Latch pulse input pin for display data

"

Data is latched on the falling edge of the clock pulse

L/R

Direction selection pin for reading display data

"

When set to V

SS

level "L", data is read sequentially from Y160 to Y1

"

When set to V

DD

level "H", data is read sequentially from Y1 to Y160

DISPOFF

Control input pin for output deselect level

"

The input signal is level-shifted from the logic voltage level to the LCD driver voltage level, and controls the

LCD driver circuit

"

When set to V

SS

level "L", the LCD driver output pins (Y1 - Yl60) are set to level V

5

"

When DISPOFF is set to "L", the contents of the line latch are reset, but the display data in the data latch

are read regardless of the condition of DISPOFF . When the DISPOFF function is canceled, the driver

outputs the deselect level (V

12

or V

43

), then outputs the contents of the date latch onto the next falling edge

of the LP

At that time, if the DISPOFF removal time can not keep in regulation with what is shown on the AC

characteristics, then it can not output the reading data correctly

FR

AC signal input for LCD driving waveform

"

The input signal is level-shifted from the logic voltage level to the driver voltage level, and controls LCD

driver circuit

"

It normally inputs a frame inversion signal

The LCD driver output pin's output voltage level can be set to the line latch output signal and the FR signal

MD

Mode selection pin

"

When set to V

SS

level "L", 4-bit parallel input mode is set

"

When set to V

DD

level "H", 8-bit parallel input mode is set

NT7703

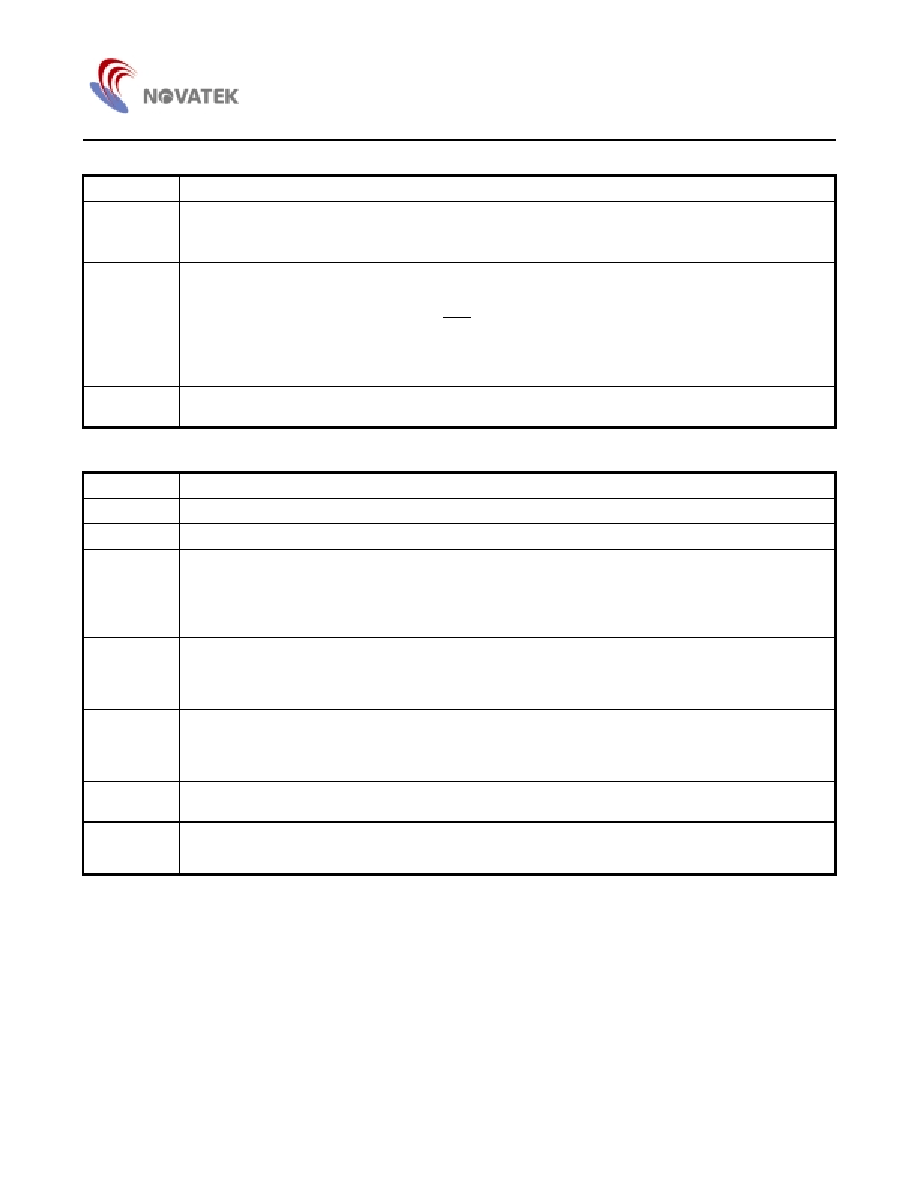

7

Segment mode continued

Symbol

Function

S/C

Segment mode/common mode selection pin

"

When set to V

DD

level "H", segment mode is set

"

When set to V

SS

level "L", common mode is set

EIO

1

, EIO

2

Input/output pin for chip selection

"

When L/R input is at V

SS

level "L", EIO

1

is set for output, and EIO

2

is set for input

"

When L/R input is at V

DD

level "H", EIO

1

is set for input, and EIO

2

is set for output

"

During output, it is set to "H" when LP* XCK is "H" and then after 160-bits of data have been read, it is

set to "L" for one cycle (from falling edge to falling edge of XCK), after which it returns to "H"

"

During input, after the LP signal is input, the chip is selected while EI is set to "L". After 160-bits of

data have been read, the chip is deselected

Y

1

-

Y

160

LCD driver output pins

These correspond directly to each bit of the data latch, one level (V

0

, V

12

, V

43

, or V

5

) is selected and output

Common mode

Symbol

Function

V

DD

Logic system power supply pin connects from +2.5 to +5.5V

V

SS

Ground pin connects to 0V

V

0R

, V

0L

V

12R

, V

12L

V

43R

, V

43L

V

5R

, V

5L

Power supply pin for LCD driver voltage bias.

"

Normally, the bias voltage used is set by a resistor divider

"

Ensure that the voltages are set such that V

SS

V

5

<V

43

< V

12

< V

0

"

To further reduce the differences between the output waveforms of the LCD driver output pins Y

1

and

Y

160,

externally connect V

iR

and V

iL

(I = 0, 12, 43)

EIO

1

Bi-directional shift register shift data input/output pin

"

Is an Output pin when L/R is at V

SS

level "L" and is an input pin when L/R is at V

DD

level "H"

"

When EIO

1

is used as an input pin, it will be pulled-down

"

When EIO

1

is used as an output pin, it won't be pulled-down

EIO

2

Bi-directional shift register shift data input/output pin

"

Is an Input pin when L/R is at V

SS

level "L" and is an output pin when L/R is at V

DD

level "H"

"

When EIO

2

is used as an input pin, it will be pulled-down

"

When EIO

2

is used as an output pin, it won't be pulled-down

LP

Bi-directional shift register shift clock pulse input pin

"

Data is shifted on the falling edge of the clock pulse

L/R

Bi-directional shift register shift direction selection pin

"

Data is shifted from Y

160

to Y

1

when it is set to V

SS

level "L", and data is shifted from Y

1

to Y

160

when set

it is to V

DD

level "H"

NT7703

8

Common mode continued

Symbol

Function

DISPOFF

Control input pin for output deselect level

"

The input signal is level-shifted from the logic voltage level to the LCD driver voltage level and it controls

the LCD driver circuit

"

When set to V

SS

level "L", the LCD driver output pins (Y

1

- Y

160

) are set to level V

5

"

While set to "L", the contents of the shift resister are reset and are not reading data. When the DISPOFF

function is canceled, the driver outputs deselect level (V

12

or V

34

), and the shift data is read on the falling

edge of the LP. At that time, if the DISPOFF removal time can not keep regulation with what is shown on

the AC characteristics, then the shift data is not read correctly

FR

AC signal input for LCD driving waveform

"

The input signal is level-shifted from the logic voltage level to the LCD driver voltage level, and controls the

LCD driver circuit

"

Normally, it inputs a frame inversion signal

The LCD driver output pin's output voltage level can be set using the shift register output signal and the FR

signal

MD

Mode selection pin

"

When set to V

SS

level "L", Single Mode operation is selected. When set to V

DD

level "H", Dual Mode

operation is selected

D

7

Dual Mode data input pin

"

According to the data shift direction of the data shift register, data can be input starting from the 81st bit

When the chip is used in Dual Mode, D

7

will be pulled-down

When the chip is used in Single Mode, D

7

won't be pulled-down

S/C

Segment mode/common mode selection pin

"

When set to V

SS

level "L", common mode is set

D

0

-

D6

Not used

"

Connect D

0

-D

6

to V

SS

or V

DD

. Avoid floating

XCK

Not used

"

XCK is pulled-down in common mode, so connect to V

SS

or leave open

Y

1

-

Y

160

LCD driver output pins

"

These correspond directly to each bit of the shift register, one level (V

0

, V

12,

V

43

, or V

5

) is selected and

output

NT7703

9

Functional Description

1. Block description

1.1. Active Control

In segment mode, it controls the selection or deselection of

the chip. Following a LP signal input and after the select

signal is input, a select signal is generated internally until 160

bits of data have been read in. Once data input has been

completed, a select signal for the cascade connection is

output, and the ship is deselected.

In common mode, it controls the input/output data of the

bidirectional pins.

1.2. SP Conversion & Data Control

In segment mode, it keeps input data, which are 2 clocks of

XCK at 4-bit parallel mode in the latch circuit, or keeps input

data which are 1 clock of XCK at 8-bit parallel mode in the

latch circuit, after which they are put on the internal data bus

8 bits at a time.

1.3. Data Latch Control

In segment mode, it selects the state of the data latch, which

reads in the data bus signals. The shift direction is controlled

by the control logic and for every 16 bits of data read in, the

selection signal shifts one bit, based on the state of the

control circuit.

1.4. Data Latch

In segment mode, it latches the data onto the data bus. The

latched state of each LCD driver output pin is controlled by

the control logic and the data latch control. 160 bits of data

are read in 20 sets of 8 bits.

1.5. Line Latch / Shift Register

In segment mode, it ensures that all 160 bits which have

been read into the data latch are simultaneously latched on

to the falling edge of the LP signal, and output to the level

shift block.

In common mode, shifts data from the data input pin on to

the falling edge of the LP signal.

1.6. Level Shifter

It ensures the logic voltage signal is level-shifted to the LCD

driver voltage level, and output to the driver block.

1.7. 4-Level Driver

It drives the LCD driver output pins from the line latch/shift

register data, selecting one of 4 levels (V

0

, V

12

, V

43

, V

5

)

based on the S/C, FR and DISPOFF signals.

1.8. Control Logic

It controls the operation of each block. In segment mode,

when an LP signal has been input, all blocks are reset and

the control logic waits for the selection signal output from the

active control block. Once the selection signal has been

output, operation of the data latch and data transmission are

controlled, 160 bits of data are read in, and the chip is

deselected.

In common mode, it controls the direction of the data shift.

NT7703

10

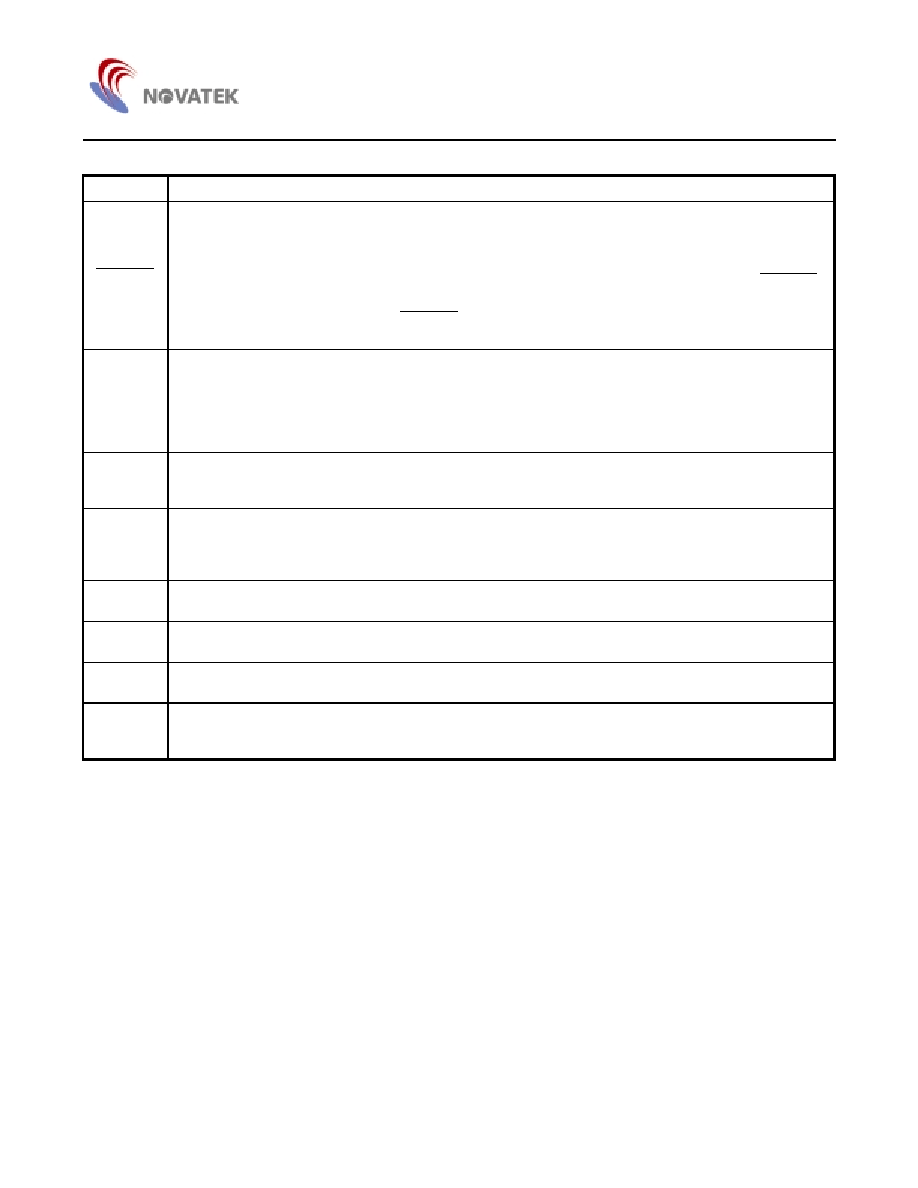

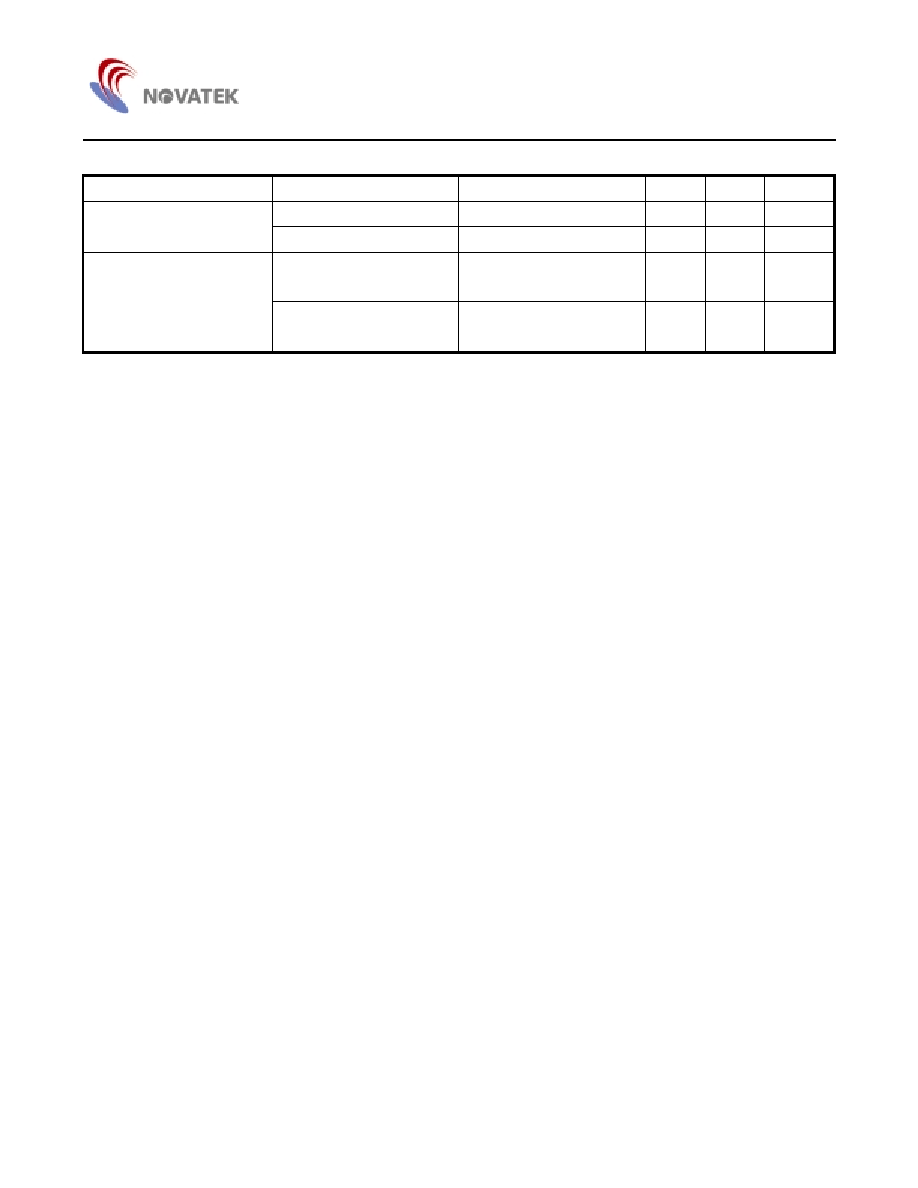

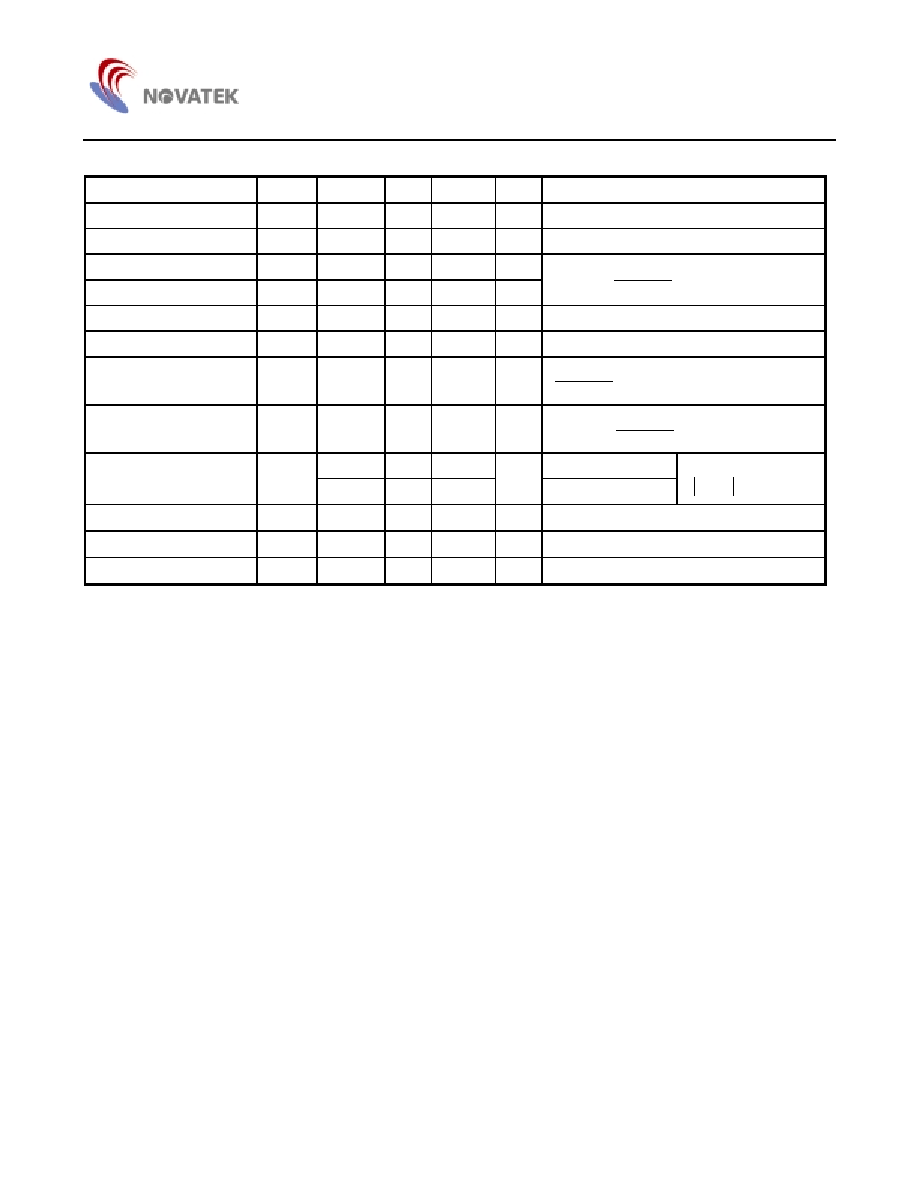

2. LCD Driver Output Voltage Level

The relationship between the data bus signal, AC converted signal FR and LCD driver output voltage is as shown in the table

below:

2.1. Segment Mode

FR

Latch Data

DISPOFF

Driver Output Voltage Level (Y

1

-

Y

160

)

L

L

H

V

43

L

H

H

V

5

H

L

H

V

12

H

H

H

V

0

X

X

L

V

5

Here, V

SS

V

5

< V

43

< V

12

<V

0

, H: V

DD

(+2.5 to +5.5V), L: V

SS

(0V), X: Don't care

2.2. Common Mode

FR

Latch Data

DISPOFF

Driver Output Voltage Level (Y

1

-

Y

160

)

L

L

H

V

43

L

H

H

V

0

H

L

H

V

12

H

H

H

V

5

X

X

L

V

5

Here, V

SS

V

5

< V

43

< V

12

< V

0

, H: V

DD

(+2.5 to +5.5V), L: V

SS

(0V), X: Don't care

Note: There are two kinds of power supply (logic level voltage, LCD driver voltage) for the LCD driver. Please supply regular

voltage, which is assigned by specification for each power pin.

That time "Don't care" should be fixed to "H" or "L", avoiding floating.

NT7703

11

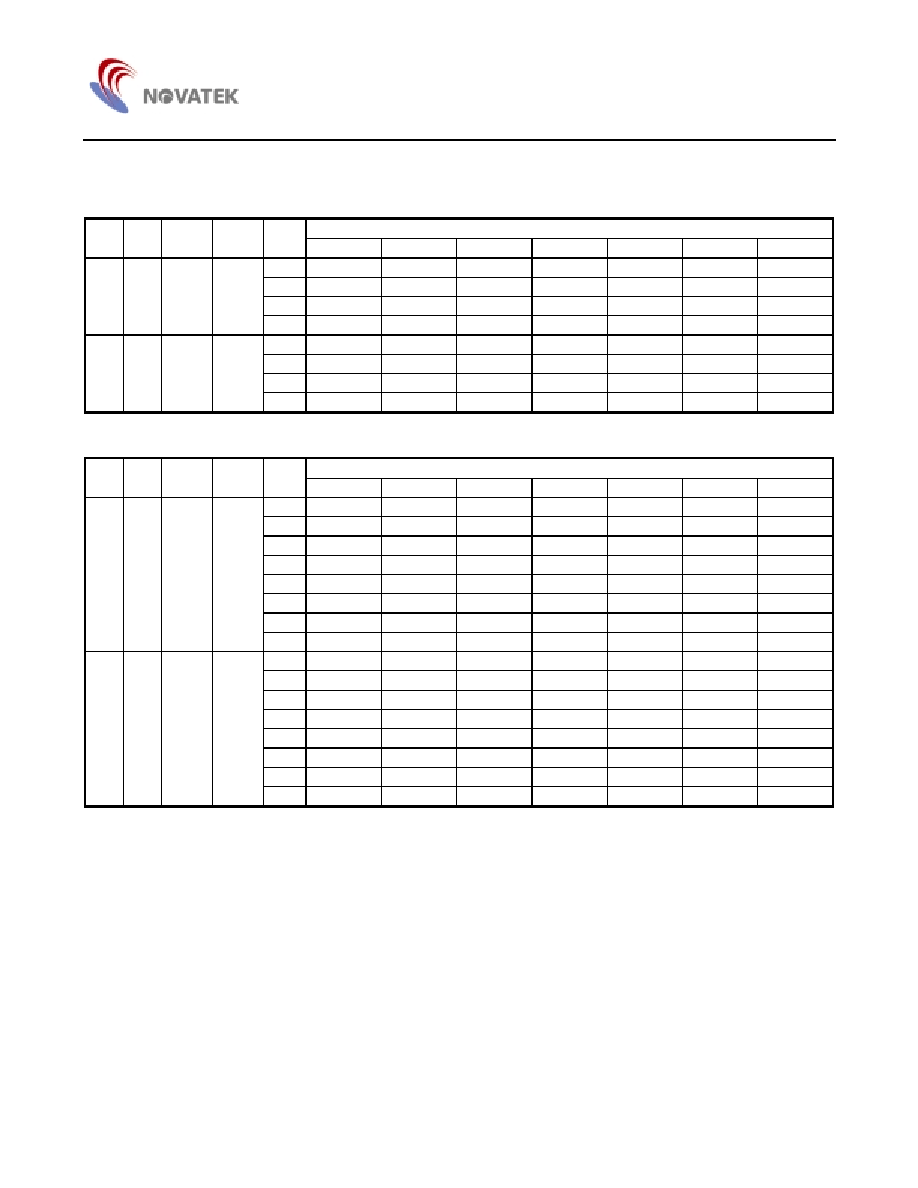

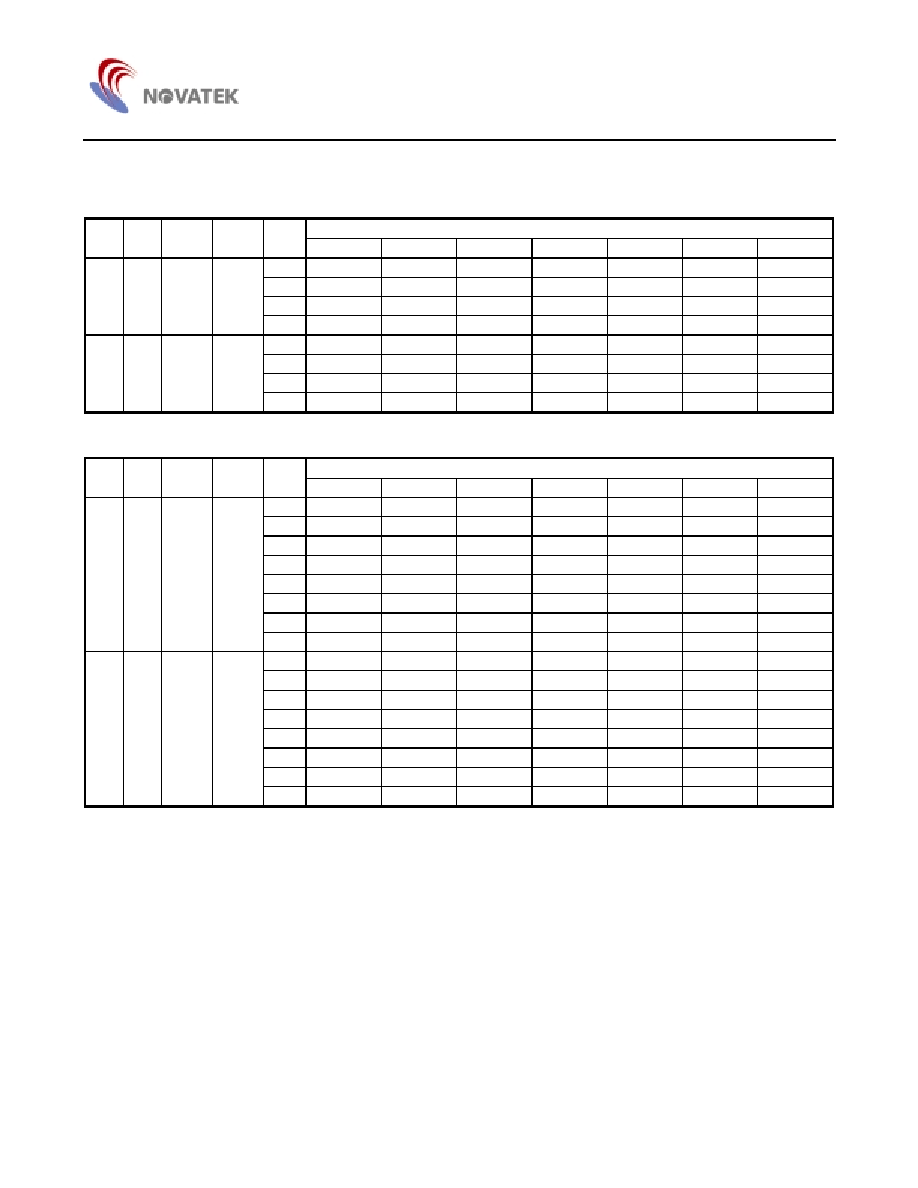

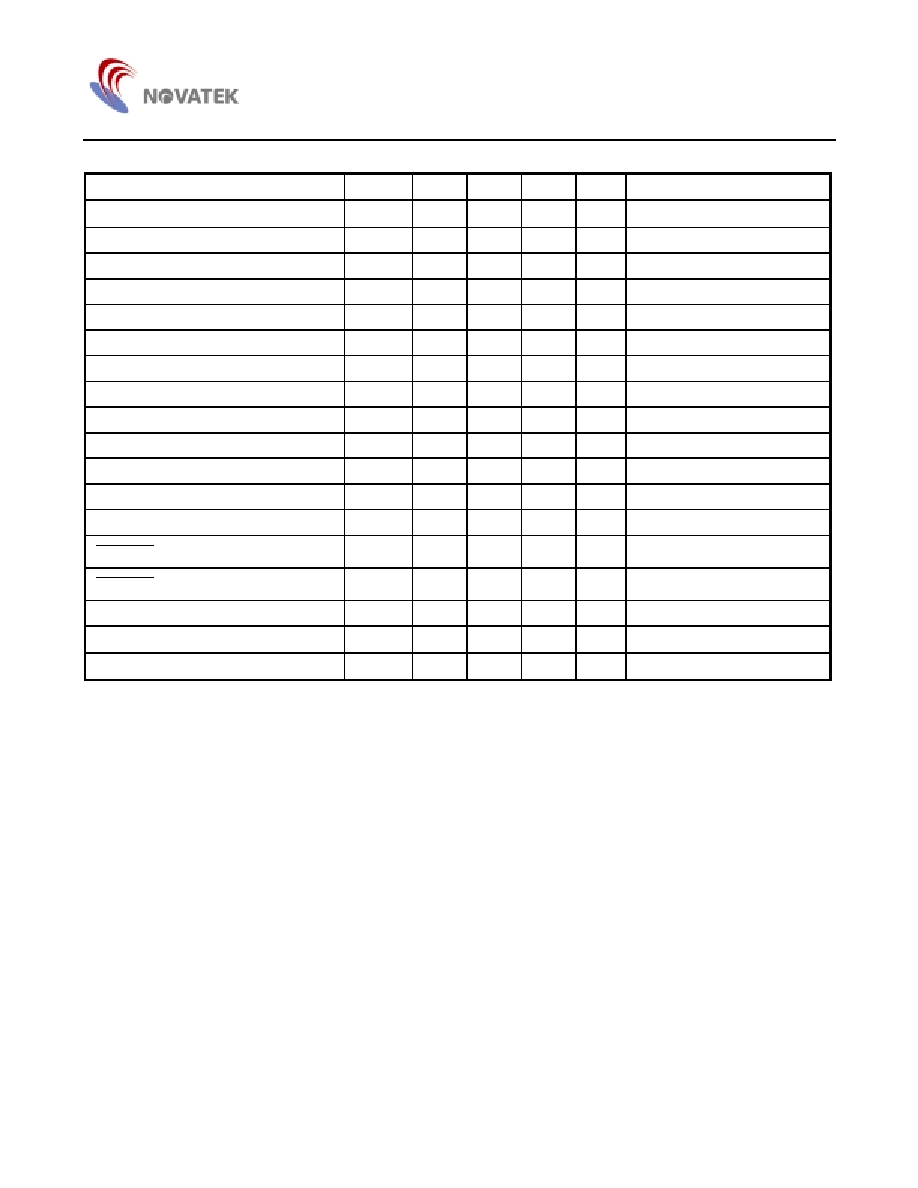

3. Relationship between the Display Data and Driver Output Pins

3.1. Segment Mode:

(a) 4-bit Parallel Mode

Number of Clock

MD

L/R

EIO

1

EIO

2

Data

Input

40clock

39clock

38clcok

~

3clock

2clock

1clock

D

0

Y1

Y5

Y9

~

Y149

Y153

Y157

D

1

Y2

Y6

Y10

~

Y150

Y154

Y158

D

2

Y3

Y7

Y11

~

Y151

Y155

Y159

L

L

Output

Input

D

3

Y4

Y8

Y12

~

Y152

Y156

Y160

D

0

Y160

Y156

Y152

~

Y12

Y8

Y4

D

1

Y159

Y155

Y151

~

Y11

Y7

Y3

D

2

Y158

Y154

Y150

~

Y10

Y6

Y2

L

H

Input

Output

D

3

Y157

Y153

Y149

~

Y9

Y5

Y1

(b) 8-bit Parallel Mode

Number of Clock

MD

L/R

EIO

1

EIO

2

Data

Input

20clock

19clock

18clcok

~

3clock

2clock

1clock

D

0

Y1

Y9

Y17

~

Y137

Y145

Y153

D

1

Y2

Y10

Y18

~

Y138

Y146

Y154

D

2

Y3

Y11

Y19

~

Y139

Y147

Y155

D

3

Y4

Y12

Y20

~

Y140

Y148

Y156

D

4

Y5

Y13

Y21

~

Y141

Y149

Y157

D

5

Y6

Y14

Y22

~

Y142

Y150

Y158

D

6

Y7

Y15

Y23

~

Y143

Y151

Y159

H

L

Output

Input

D

7

Y8

Y16

Y24

~

Y144

Y152

Y160

D

0

Y160

Y152

Y144

~

Y24

Y16

Y8

D

1

Y159

Y151

Y143

~

Y23

Y15

Y7

D

2

Y158

Y150

Y142

~

Y22

Y14

Y6

D

3

Y157

Y149

Y141

~

Y21

Y13

Y5

D

4

Y156

Y148

Y140

~

Y20

Y12

Y4

D

5

Y155

Y147

Y139

~

Y19

Y11

Y3

D

6

Y154

Y146

Y138

~

Y18

Y10

Y2

H

H

Input

Output

D

7

Y153

Y145

Y137

~

Y17

Y9

Y1

NT7703

12

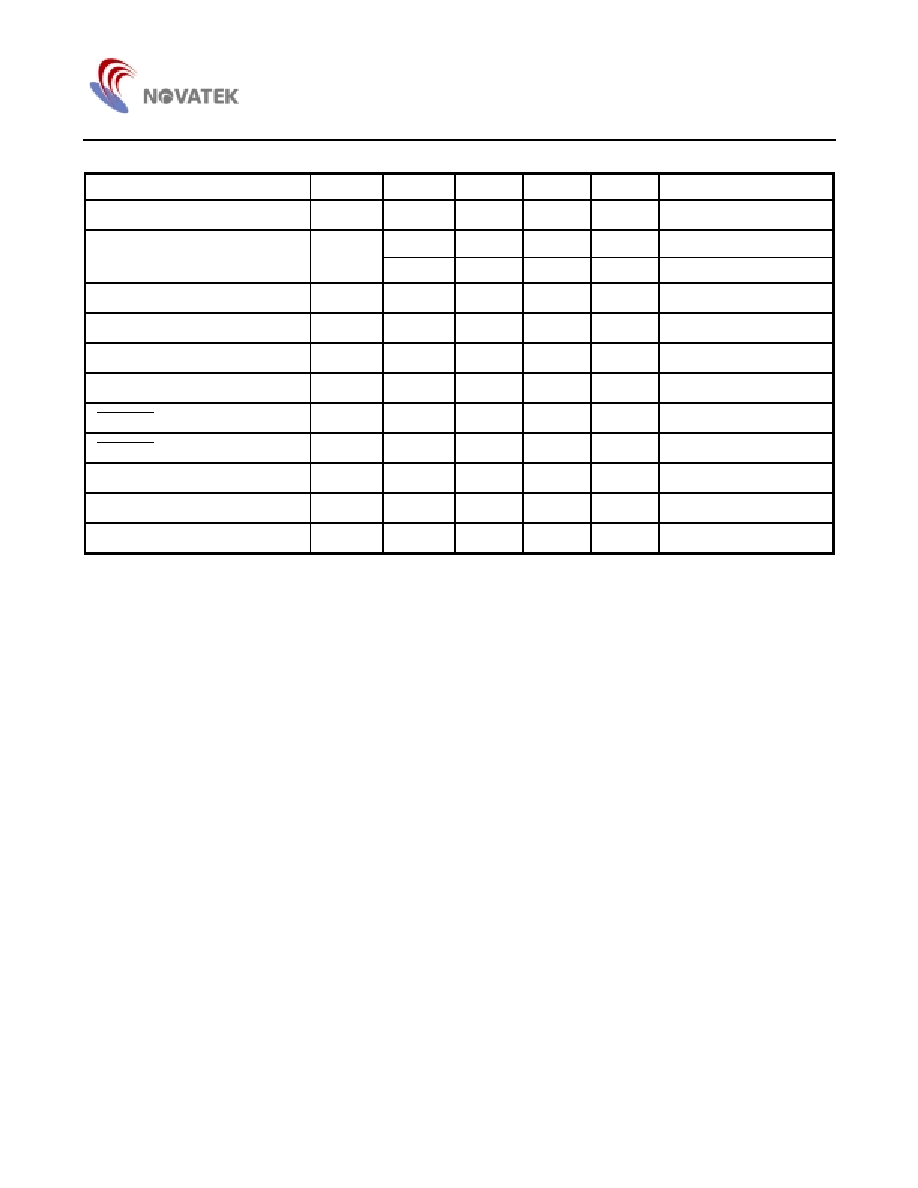

3.2. Common Mode

MD

L/R

Data Transfer Direction

EIO

1

EIO

2

D

7

L (shift to left)

Y160 to Y1

Output

Input

X

L

(Single)

H (shift to right)

Y1 to Y160

Input

Output

X

L (shift to left)

Y160 to Y81

Y80 to Y1

Output

Input

Input

H

(Dual)

H (shift to right)

Y1 to Y80

Y81 to Y160

Input

Output

Input

Here, L: V

SS

(0V), H: V

DD

(+2.5V to +5.5V), X: Don't care

Note: "Don't care" should be fixed to "H" or "L", avoiding floating.

NT7703

13

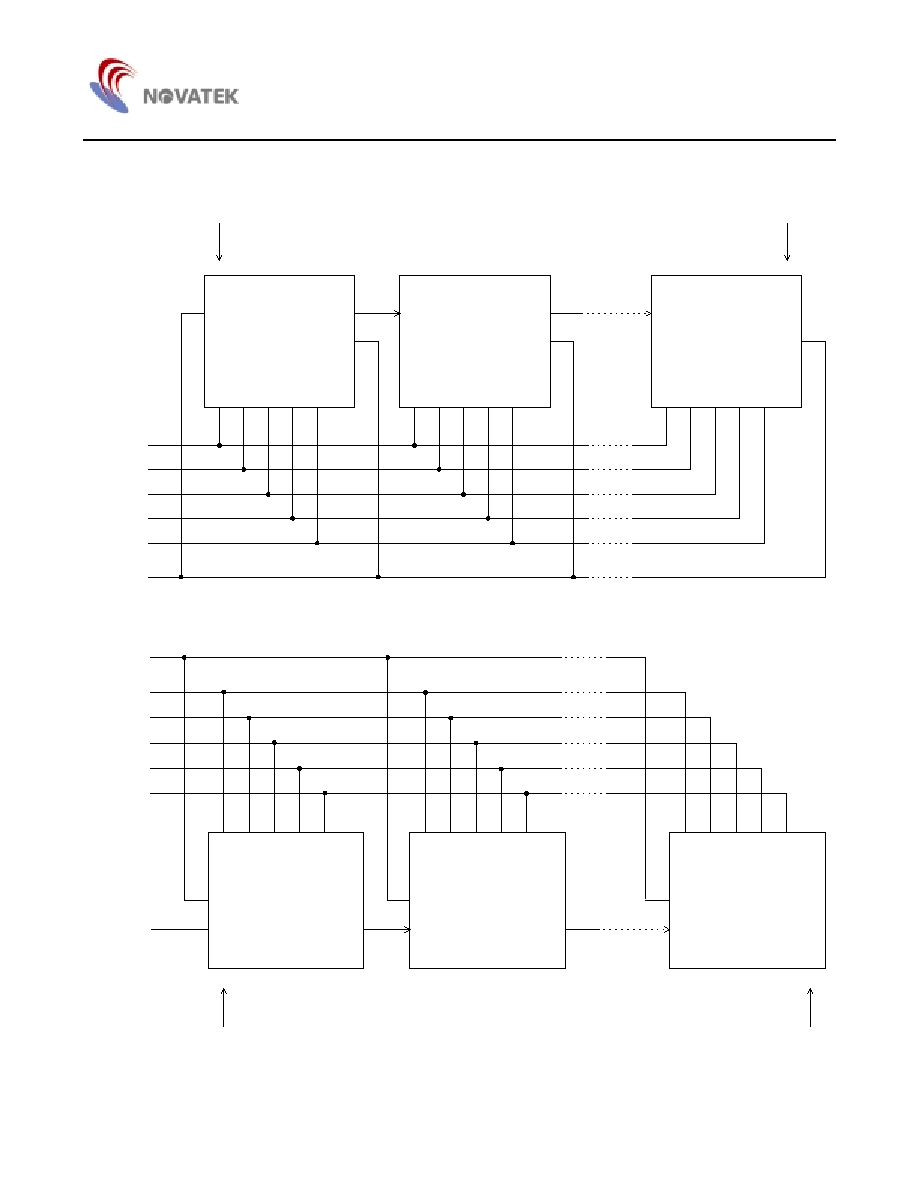

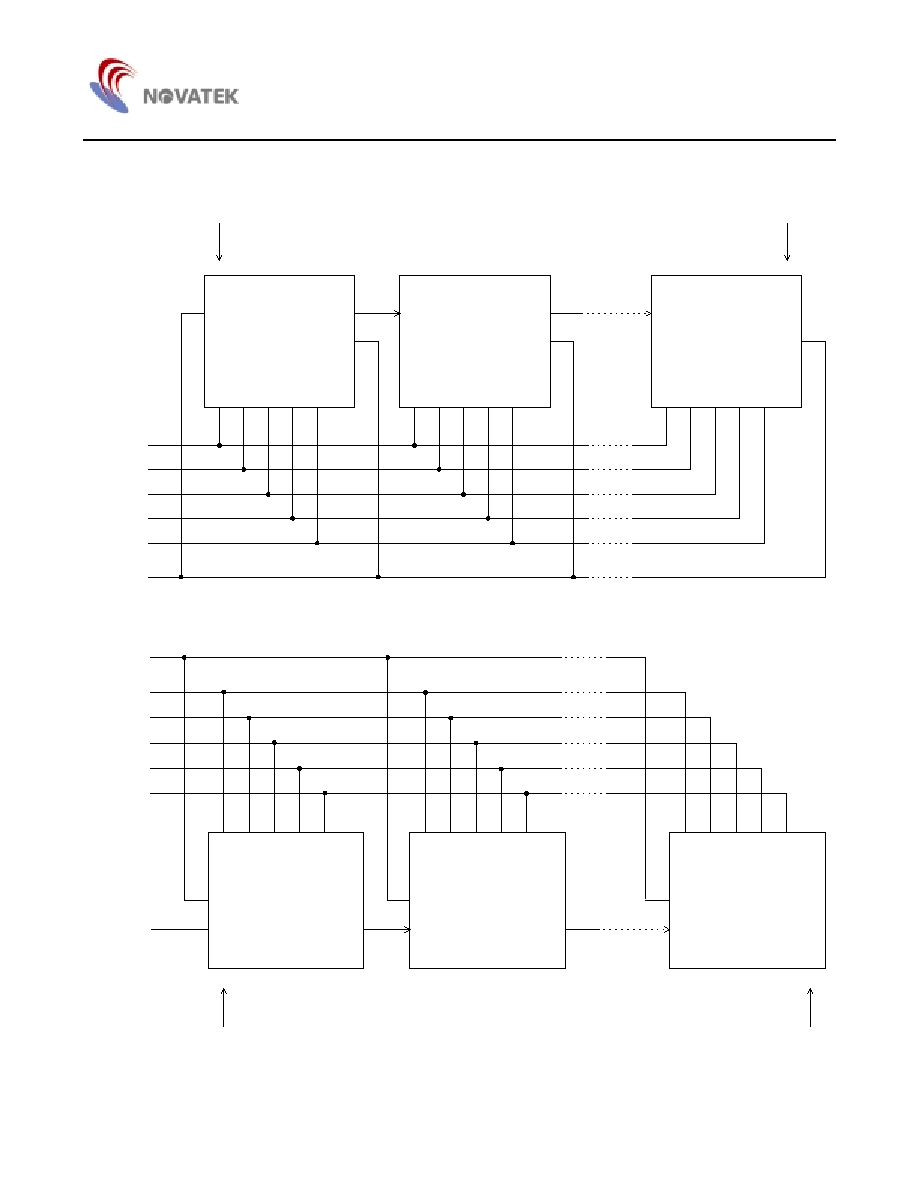

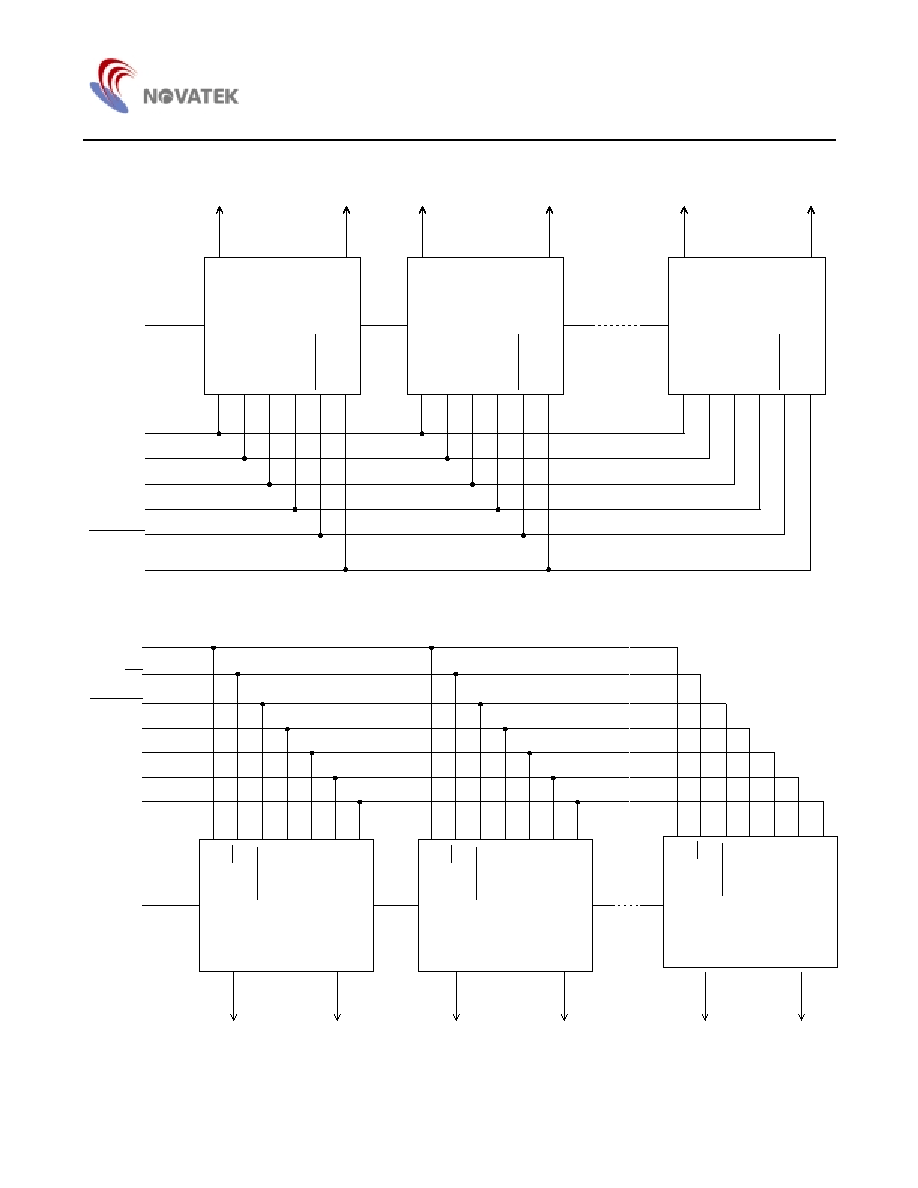

4. Connection Examples of Segment Drivers

4.1. Case of L/R = "L"

XCK

LP

MD

FR

DI0 - DI7

L/R

EIO1

EIO2

XCK

LP

MD

FR

DI0 - DI7

L/R

EIO1

EIO2

XCK

LP

MD

FR

DI0 - DI7

L/R

EIO1

EIO2

XCK

LP

MD

D0 - D7

FR

V

SS

Y160 ---------------------->Y1

Y160 ---------------------->Y1

Y160 ---------------------->Y1

(data taking flow)

first data

last data

/8

4.2 Case of L/R = "H"

XCK

LP

MD

D0 - D7

FR

V

DD

Y1 ---------------------->Y160

(data taking flow)

first data

Y1 ---------------------->Y160

Y1 ---------------------->Y160

last data

XCK

LP

MD

FR

DI0 - DI7

L/R

EIO1

EIO2

XCK

LP

MD

FR

DI0 - DI7

L/R

EIO1

EIO2

XCK

LP

MD

FR

DI0 - DI7

L/R

EIO1

EIO2

V

SS

/8

NT7703

14

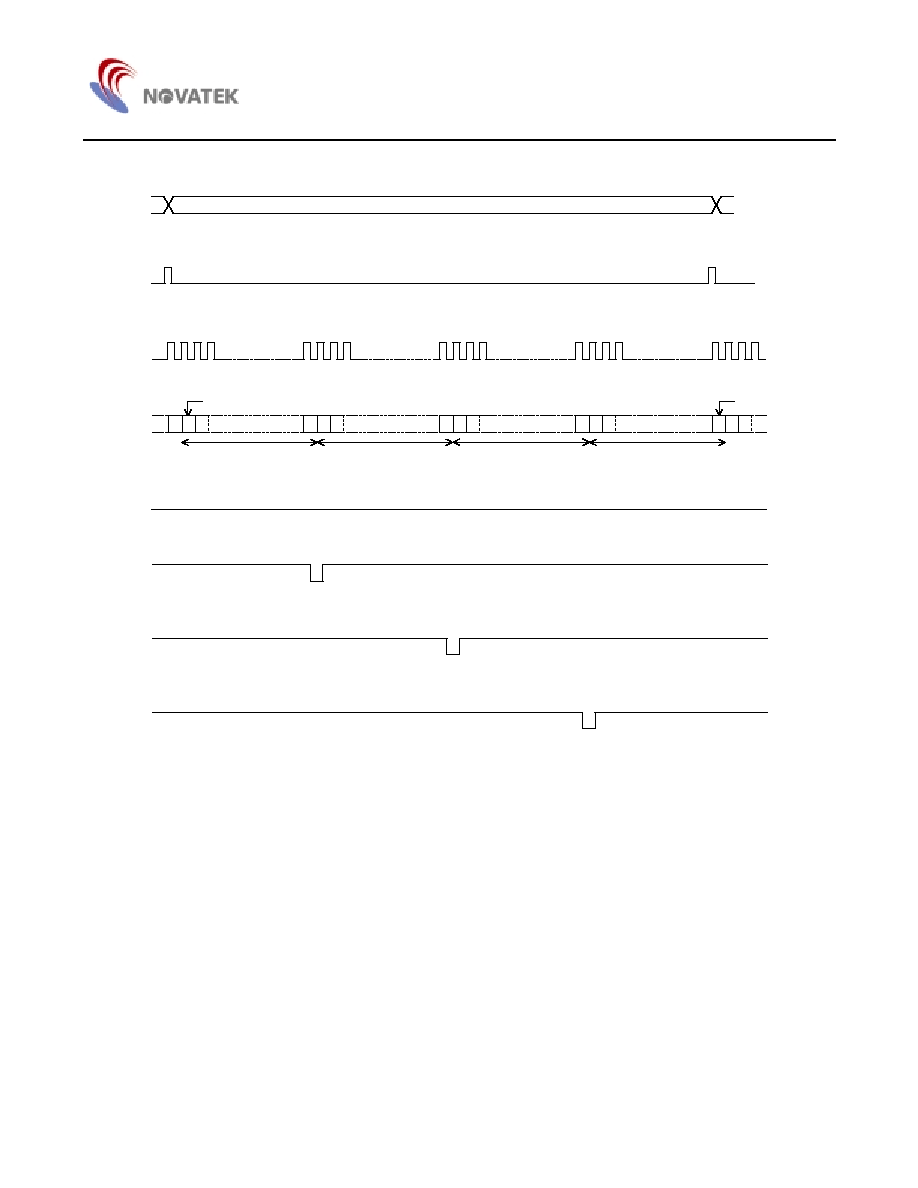

5. Timing Waveform of 4-Device Cascade Connection of Segment Drivers.

n 1 2

n 1 2

n 1 2

n 1 2

n 1 2

device A

device B

device C

device D

First data

Last data

FR

LP

XCK

D0 - D7

EI

(device A)

EO

(device A)

EO

(device B)

EO

(device C)

n: 4-bit parallel mode 40

8-bit parallel mode 20

H

L

NT7703

15

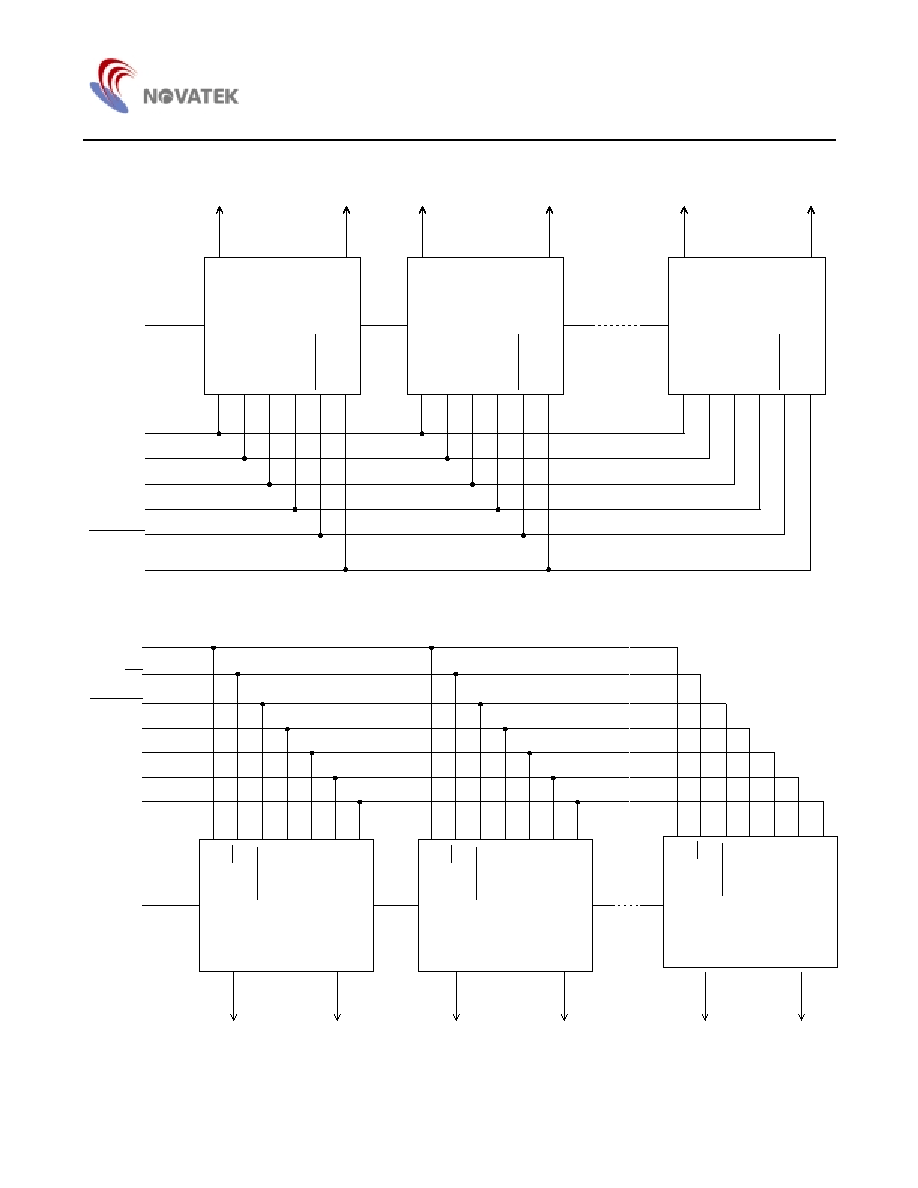

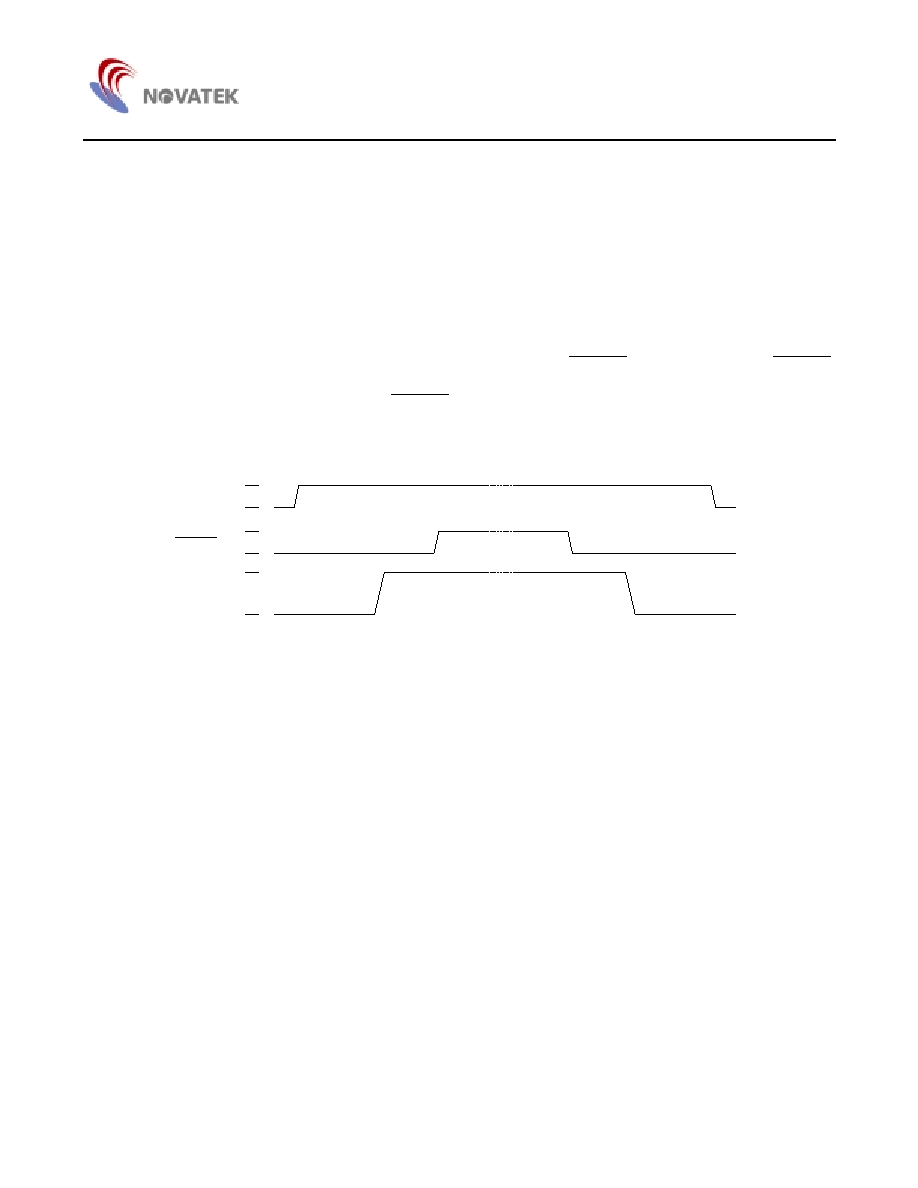

6. Connection Examples for Common Drivers

D

V

SS

(V

DD

)

V

SS

V

SS

FR

First

LP

DISPOFF

EIO1

EIO2

LP

D7

MD

L/R

FR

DISPOFF

Y160

Y1

EIO1

EIO2

LP

D7

MD

L/R

FR

DISPOFF

Y160

Y1

Last

EIO1

EIO2

LP

D7

MD

L/R

FR

DISPOFF

Y160

Y1

Single Mode (Shifting towards the left)

FR

DI

V

SS

(V

DD

)

V

SS

V

DD

First

LP

DISPOFF

Last

CS

EIO1

EIO2

LP

DI7

MD

L/R

FR

Y160

Y1

CS

DISPOFF

EIO1

EIO2

LP

DI7

MD

L/R

FR

Y160

Y1

CS

DISPOFF

EIO1

EIO2

LP

DI7

MD

L/R

FR

Y160

Y1

CS

DISPOFF

Single Mode (Sifting towards the right)

NT7703

16

D1

EIO1

EIO2

LP

D7

MD

L/R

FR

DISPOFF

Y160

Y1

EIO1

EIO2

LP

D7

MD

L/R

FR

DISPOFF

Y160

Y1

EIO1

EIO2

LP

D7

MD

L/R

FR

DISPOFF

Y160

Y1

V

SS

(V

DD

)

V

DD

V

SS

FR

LP

DISPOFF

D2

Last2

First1

Last1 First2

Y81

Y80

Dual mode (Shifting towards the left)

D1

Y160

Y1

EIO1

EIO2

LP

D7

MD

L/R

FR

DISPOFF

EIO1

EIO2

LP

D7

MD

L/R

FR

DISPOFF

EIO1

EIO2

LP

D7

MD

L/R

FR

DISPOFF

Y160

Y1

V

SS

(V

DD

)

V

DD

FR

LP

DISPOFF

D2

Last2

First1

Last1 First2

Y160

Y1

Y81

Y80

V

DD

Dual mode (Shifting towards the right)

NT7703

17

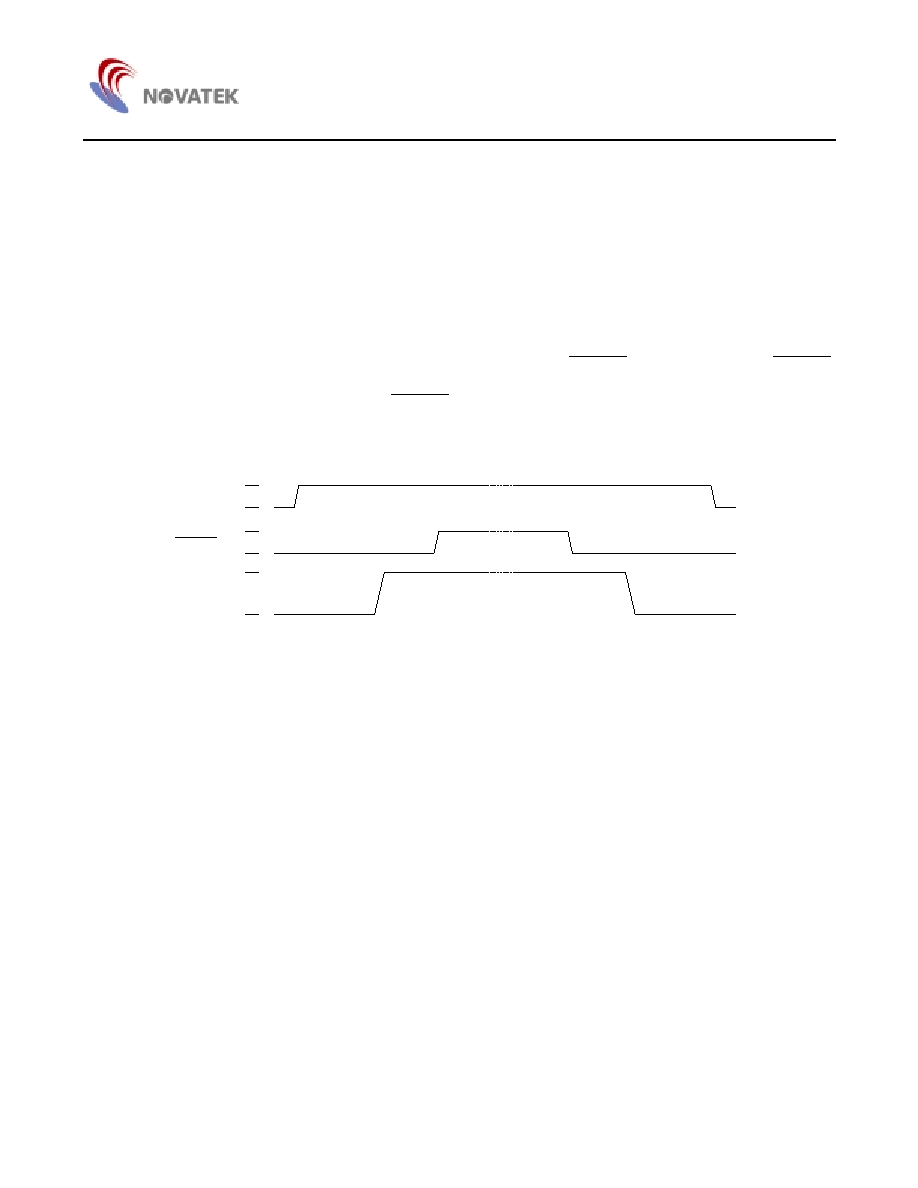

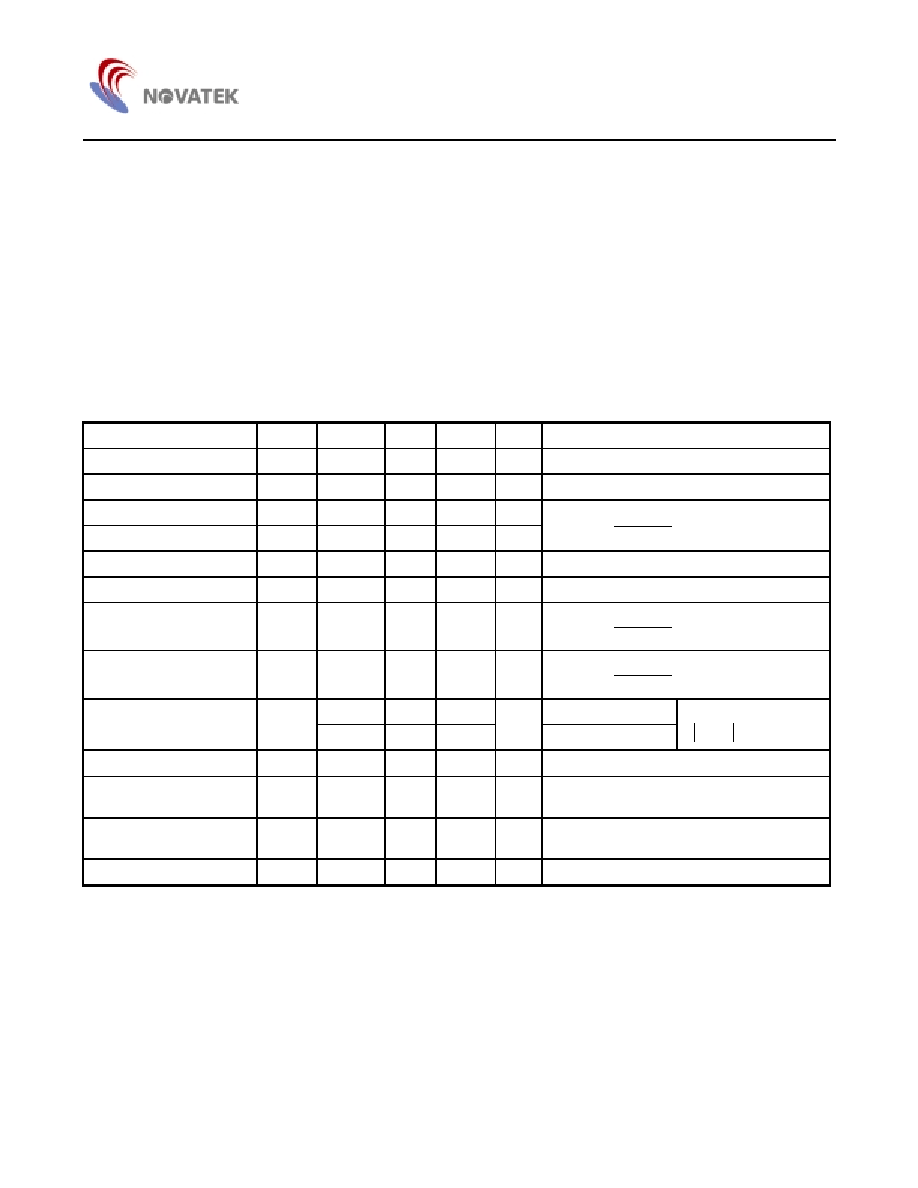

7. Precaution

Be careful when connecting or disconnecting the power

This LSI has a high-voltage LCD driver, so it may be permanently damaged by a high current, which may occur if voltage is

supplied to the LCD driver power supply while the logic system power supply is floating.

The details are as follows:

!

When connecting the power supply, connect the LCD driver power after connecting the logic system power. Furthermore,

when disconnecting the power, disconnect the logic system power after disconnecting the LCD driver power.

!

We recommend that you connect a serial resistor (50-100

) or fuse to the LCD driver power V

0

of the system as a current

limiting device. Also, set a suitable value for the resistor in consideration of the LCD display grade.

In addition, when connecting the logic power supply, the logic condition of the LSI inside is insecure. Therefore connect the LCD

driver power supply only after resetting the logic condition of this LSI inside to the DISPOFF function. After that, the DISPOFF

will cancel the function after the LCD driver power supply has become stable. Furthermore, when disconnecting the power, set

the LCD driver output pins to level V

SS

on the DISPOFF function. After that, disconnect the logic system power after

disconnecting the LCD driver power.

When connecting the power supply, follow the recommended sequence shown.

V

DD

DISPOFF

V

0

V

DD

V

SS

V

DD

V

SS

V

SS

V

0

NT7703

18

Absolute Maximum Rating*

DC Supply Voltage V

DD

. . . . . . . . . . . . -0.3V to +7.0V

DC Supply Voltage V

0

. . . . . . . . . . . . . . -0.3V to +30V

Input Voltage . . . . . . . . . . . . . . . . . -0.3V to V

DD

+0.3V

Operating Ambient Temperature . . . . -30

∞

C to +85

∞

C

Storage Temperature . . . . . . . . . . . . . -45

∞

C to +125

∞

C

*Comments

Stresses above those listed under "Absolute Maximum

Ratings" may cause permanent damage to this device.

These are stress ratings only. Functional operation of this

device under these or any other conditions above those

indicated in the operational sections of this specification is

not implied or intended. Exposure to the absolute maximum

rating conditions for extended periods may affect device

reliability.

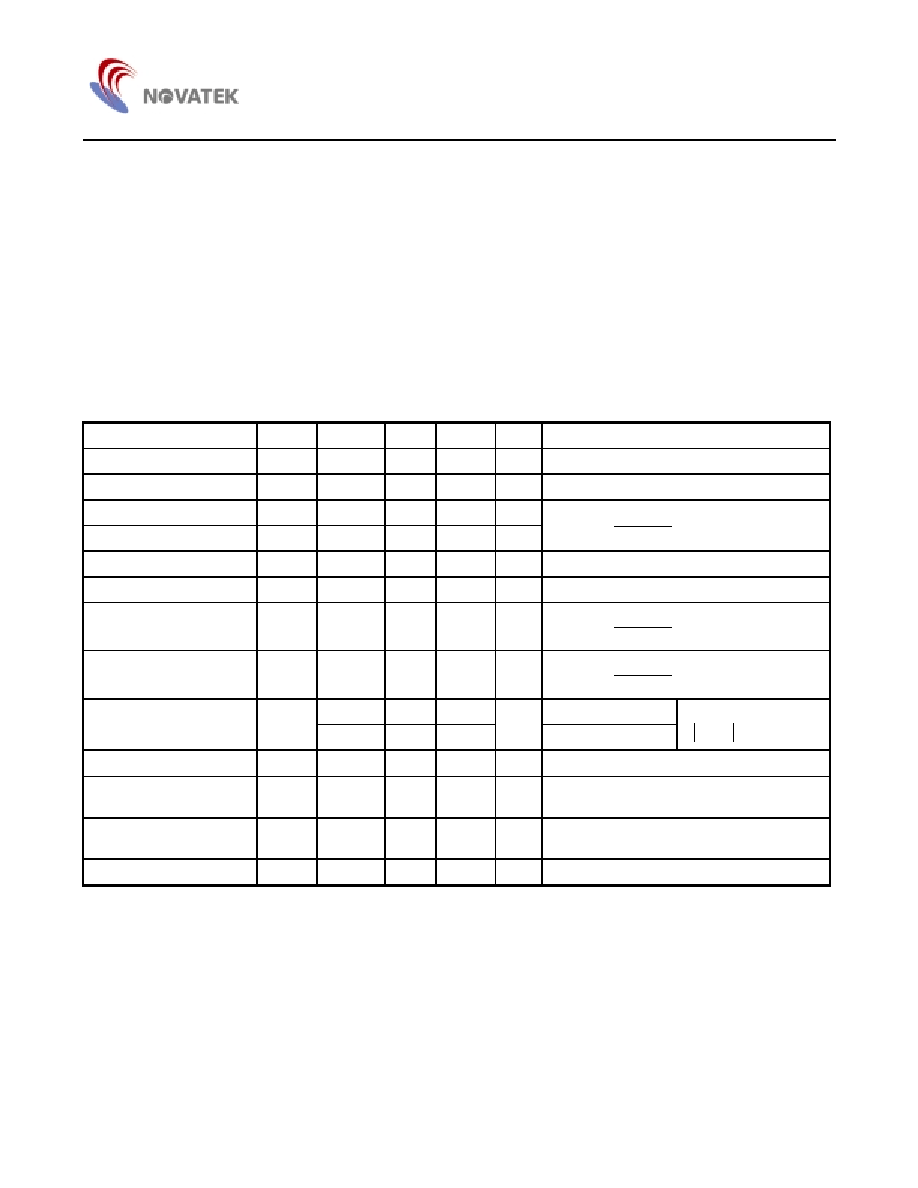

Electrical Characteristics

DC Characteristics

Segment Mode (V

SS

= V

5

= 0V, V

DD

= 2.5 - 5.5V, V

0

= 15 to 30 V, and T

A

= -30 to +85

∞

C, unless otherwise noted)

Parameter

Symbol

Min.

Typ.

Max.

Unit

Condition

Operating Voltage

V

DD

2.5

-

5.5

V

Operating Voltage

V

0

15

-

30

V

Input high voltage

V

IH

0.8 V

DD

-

-

V

Input low voltage

V

IL

-

-

0.2 V

DD

V

D0 - 7, XCK, LP, L/R, FR, MD, S/C, EIO

1

,

EIO

2

and DISPOFF pins

Output high voltage

V

OH

V

DD

- 0.4

-

-

V

EIO

1

, EIO

2

pins, I

OH

= -0.4mA

Output low voltage

V

OL

-

-

+0.4

V

EIO

1

, EIO

2

pins, I

OL

= +0.4mA

Input leakage current 1

I

IH

-

-

+1.0

µ

A

D0 - 7, XCK, LP, L/R, FR, MD, S/C, EIO

1

,

EIO

2

and DISPOFF pins, V

I

= V

DD

Input leakage current 2

I

IL

-

-

-1.0

µ

A

D0 - 7, XCK, LP, L/R, FR, MD, S/C, EIO

1

,

EIO

2

and DISPOFF pins, V

I

= V

SS

-

1.0

1.5

V

0

= +30.0V

Output resistance

R

ON

-

1.5

2.0

k

V

0

= +20.0V

Y

1 -

Y

160

pins,

N

O

V

= 0.5V

Stand-by current

I

SB

-

-

5.0

µ

A

V

SS

pin, Note 1

Consumed current (1)

(Deselection)

I

DD1

-

-

2.0

mA

V

DD

pin, Note 2

Consumed current (2)

(Selection)

I

DD2

-

-

8.0

mA

V

DD

pin, Note 3

Consumed current

I

0

-

-

1.0

mA

V

0

pin, Note 4

Note:

1. V

DD

= +5.0V, V

0

= +30V, V

I

= V

SS

2. V

DD

= +5.0V, V

0

= +30V, f

XCK

= 14MHz, No-load, EI = V

DD

The input data is turned over by the data taking clock (4-bit parallel input mode)

3. V

DD

= +5.0V, V

0

= +30V, f

XCK

= 14MHz, No-load. EI = V

SS

The input data is turned over by the data taking clock (4-bit parallel input mode)

4. V

DD

= +5.0V, V

0

= +30V, f

XCK

= 14MHz, f

LP

= 41.6kHz. f

FR

= 80 Hz, No-load

The input data is turned over by the data taking clock (4-bit parallel-input mode)

NT7703

19

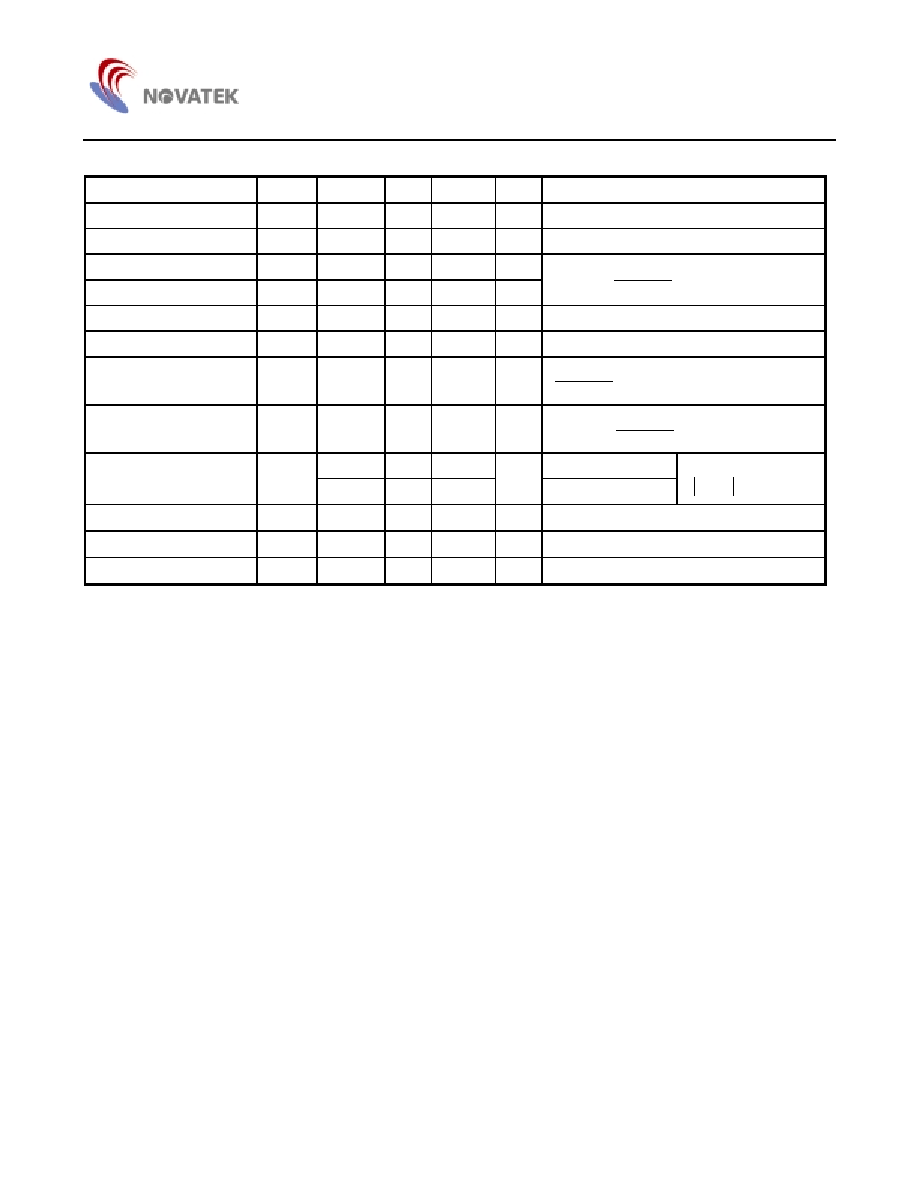

Common Mode (V

SS

= V

5

= 0V, V

DD

= 2.5 - 5.5V, V

0

= 15 to 30V, and T

A

= -30 to +85

∞

C, unless otherwise noted)

Parameter

Symbol

Min.

Typ.

Max.

Unit

Condition

Operating Voltage

V

DD

2.5

-

5.5

V

Operating Voltage

V

0

15

-

30

V

Input high voltage

V

IH

0.8 V

DD

-

-

V

Input low voltage

V

IL

-

-

0.2 V

DD

V

D0 - 7, XCK, LP, L/R, FR, MD, S/C, EIO

1

,

EIO

2

and DISPOFF pins

Output high voltage

V

OH

V

DD

- 0.4

-

-

V

EIO

1

, EIO

2

pins, I

OH

= -0.4mA

Output low voltage

V

OL

-

-

+0.4

V

EIO

1

, EIO

2

pins, I

OL

= +0.4mA

Input leakage current 1

I

IH

-

-

+1.0

µ

A

D0 - 6, LP, L/R, FR, MD, S/C and

DISPOFF pins, V

I

= V

DD

Input leakage current 2

I

IL

-

-

-1.0

µ

A

D0 - 7, XCK, LP, L/R, FR, MD, S/C, EIO1,

EIO2 and DISPOFF pins, V

I

= V

SS

-

1.0

1.5

V

0

= +30.0V

Output resistance

R

ON

-

1.5

2.0

k

V

0

= +20.0V

Y

1 -

Y

160

pins,

N

O

V

= 0.5V

Stand-by current

I

SB

-

-

5

µ

A

V

SS

pin, Note 1

Consumed current (1)

I

DD

-

-

80

µ

A

V

DD

pin, Note 2

Consumed current (2)

I

0

-

-

160

µ

A

V

0

pin, Note 2

Note:

1. V

DD

= +5.0V, V

0

= +30V, V

I

= V

SS

2. V

DD

= +5.0V, V

0

= +30V, f

LP

= 41.6KHz, f

FR

= 80Hz, case of 1/480 duty operation, No-load

NT7703

20

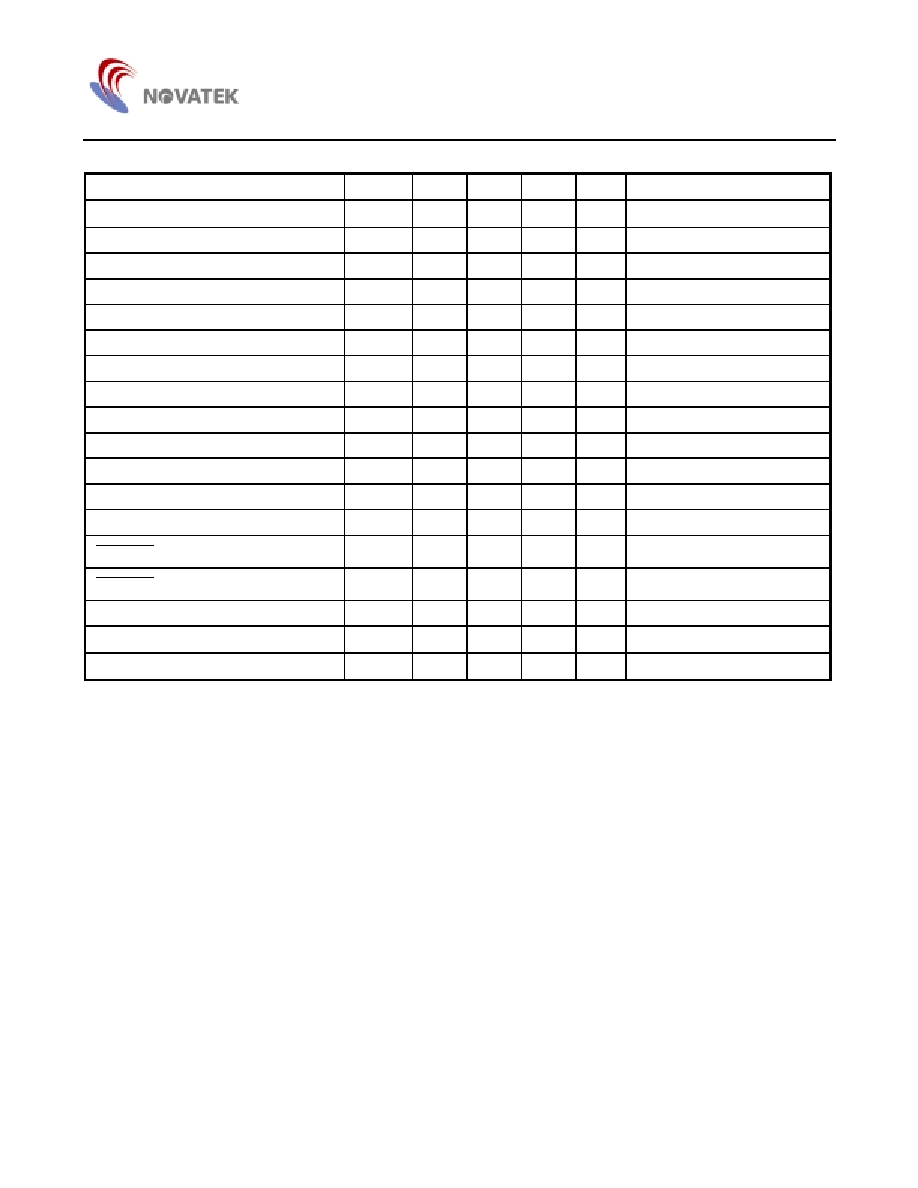

AC Characteristics

Segment Mode 1 (V

SS

= V

5

= 0V, V

DD

= 4.5 - 5.5V, V

0

= 15 to 30, and T

A

= -30 to +85

∞

C, unless otherwise noted)

Parameter

Symbol

Min.

Typ.

Max.

Unit

Condition

Shift clock period

t

WCK

71

-

ns

tr, tf

10ns, Note 1

Shift clock "H" pulse width

t

WCKH

23

-

ns

Shift clock "L" pulse width

t

WCKL

23

-

ns

Data setup time

t

DS

10

-

ns

Data hole time

t

DH

20

-

ns

Latch pulse "H" pulse width

t

WLPH

23

-

ns

Shift clock rise to Latch pulse rise time

t

LD

0

-

ns

Shift clock fall to Latch pulse fall time

t

SL

25

-

ns

Latch pulse rise to Shift clock rise time

t

LS

25

-

ns

Latch pulse fall to Shift clock rise time

t

LH

25

-

ns

Input signal rise time

t

r

-

50

ns

Note 2

Input signal fall time

t

f

-

50

ns

Note 2

Enable setup time

t

S

21

-

ns

DISPOFF Removal time

t

SD

100

-

ns

DISPOFF enable pulse width

t

WDL

1.2

-

µ

s

Output delay time (1)

t

D

-

40

ns

CL = 15pF

Output delay time (2)

t

pd1

, t

pd2

-

1.2

µ

s

CL = 15pF

Output delay time (3)

t

pd3

-

1.2

µ

s

CL = 15pF

Note:

1. Take the cascade connection into consideration.

2. (T

ck

- t

WCKII

- t

wckl

)/2 is the maximum in the case of high speed operation.

NT7703

21

Segment Mode 2 (V

SS

= V

5

= 0V, V

DD

= 2.5 - 4.5V, V

0

= 15 to 30, and T

A

= -30 to +85

∞

C, unless otherwise noted)

Parameter

Symbol

Min.

Typ.

Max.

Unit

Condition

Shift clock period

t

WCK

125

-

ns

tr, tf

11ns, Note 1

Shift clock "H" pulse width

t

WCKH

51

-

ns

Shift clock "L" pulse width

t

WCKL

51

-

ns

Data setup time

t

DS

30

-

ns

Data hole time

t

DH

40

-

ns

Latch pulse "H" pulse width

t

WLPH

51

-

ns

Shift clock rise to Latch pulse rise time

t

LD

0

-

ns

Shift clock fall to Latch pulse fall time

t

SL

51

-

ns

Latch pulse rise to Shift clock rise time

t

LS

51

-

ns

Latch pulse fall to Shift clock fall time

t

LH

51

-

ns

Input signal rise time

t

r

-

50

ns

Note 2

Input signal fall time

t

f

-

50

ns

Note 2

Enable setup time

t

S

36

-

ns

DISPOFF Removal time

t

SD

100

-

ns

DISPOFF enable pulse width

t

WDL

1.2

-

µ

s

Output delay time (1)

t

D

-

78

ns

CL = 15pF

Output delay time (2)

t

pd1

, t

pd2

-

1.2

µ

s

CL = 15pF

Output delay time (3)

t

pd3

-

1.2

µ

s

CL = 15pF

Note:

1. Take the cascade connection into consideration.

2. (t

CK

- t

WCKII

- t

WCKL

)/2 is the maximum in the case of high speed operation.

NT7703

22

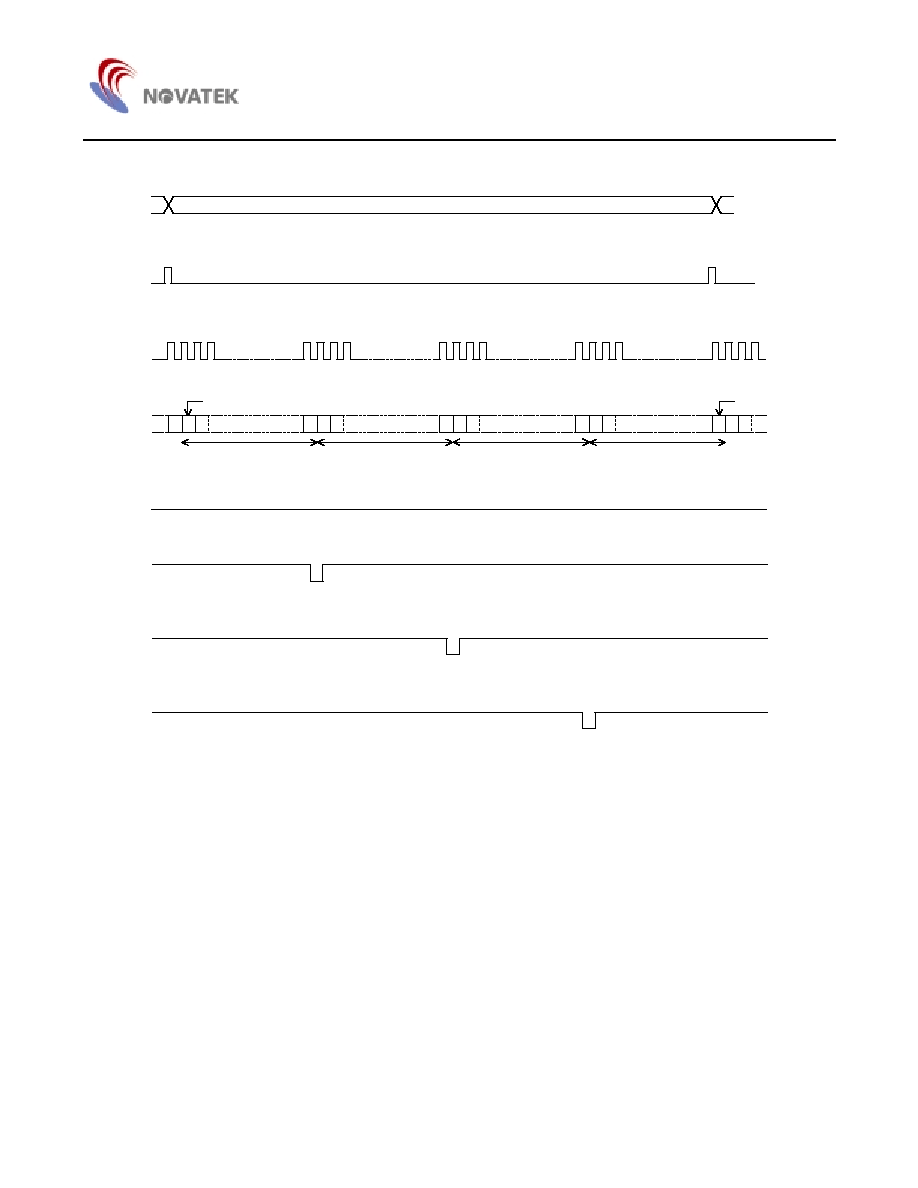

Timing waveform of the Segment Mode

t

SL

LP

LAST DATA

TOP DATA

t

LD

t

LS

t

WCKL

t

r

t

r

t

WCK

t

DS

t

DH

XCK

D0 - D7

DISPOFF

t

LH

t

WDL

t

SD

t

WLPH

t

WCKH

t

pd1

t

pd2

t

pd3

FR

LP

Y1 - Y160

DISPOFF

XCK

EO

t

S

1

2

t

D

n: 4-bit parallel mode 40

8-bit parallel mode 20

LP

EI

n

NT7703

23

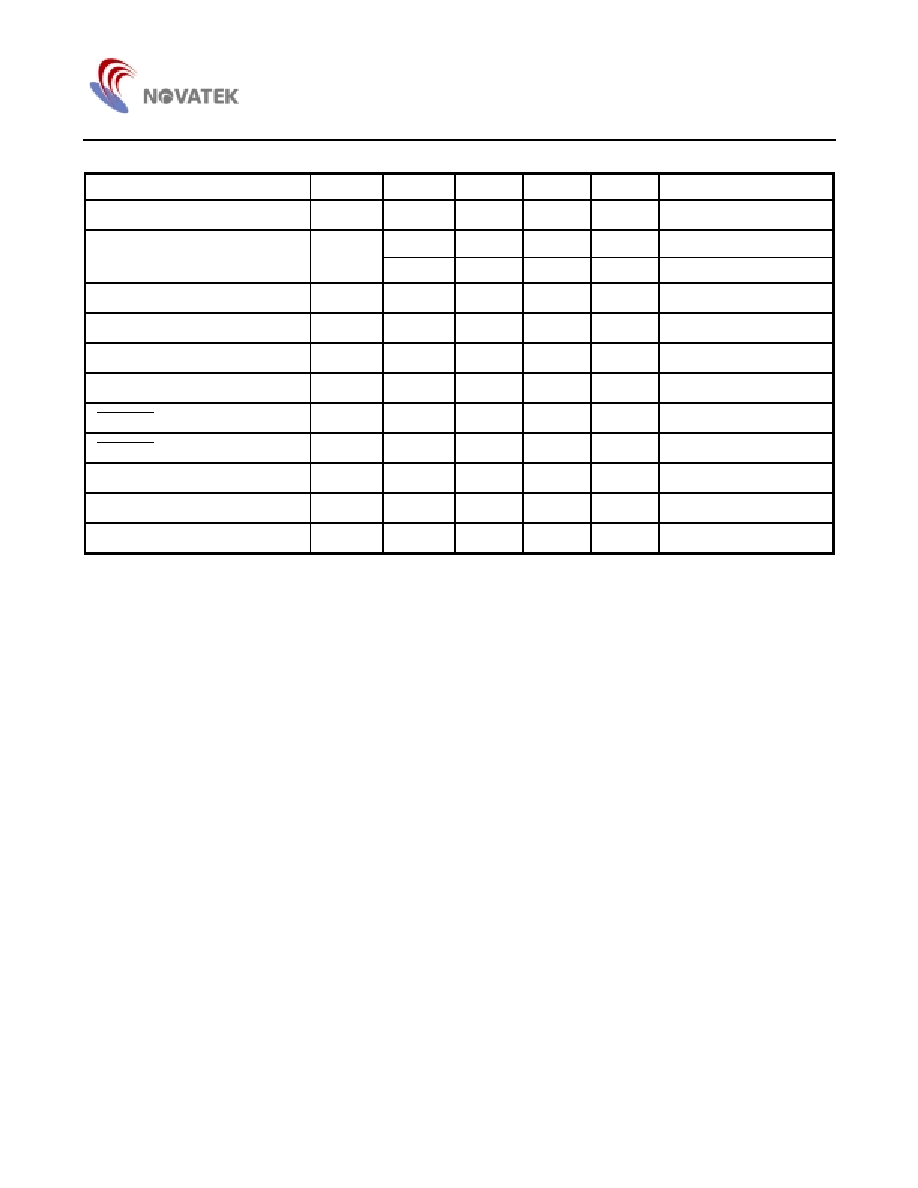

Common Mode (V

SS

= V

5

= 0V, V

DD

= 2.5 - 5.5V, V

0

= 15 to 30V and T

A

= -30 to +85

∞

C, unless otherwise noted)

Parameter

Symbol

Min.

Typ.

Max.

Unit

Condition

Shift clock period

t

WLP

250

-

-

ns

t

r

, t

f

20ns

15

-

-

ns

V

DD

= +5.0V

10%

Shift clock "H" pulse width

t

WLPH

30

-

-

ns

V

DD

= +2.5 - +4.5V

Data setup time

t

SU

30

-

-

ns

Data hole time

t

H

50

-

-

ns

Input signal rise time

t

r

-

50

ns

Input signal fall time

t

f

-

50

ns

DISPOFF Removal time

t

SD

100

-

-

ns

DISPOFF enable pulse width

t

WDL

1.2

-

-

µ

s

Output delay time (1)

t

DL

-

-

200

ns

C

L

= 15pF

Output delay time (2)

t

pd1

, t

pd2

-

-

1.2

µ

s

C

L

= 15pF

Output delay time (3)

t

pd3

-

-

1.2

µ

s

C

L

= 15pF

NT7703

24

Timing Characteristics of Common Mode

tr

tf

LP

DISPOFF

tWDL

tSD

tWLP

tWLPH

tSU

tH

tDL

EIO2

(D7)

EIO1

tpd1

tpd2

tpd3

FR

LP

Y1 - Y160

DISPOFF

L/R = "L"

NT7703

25

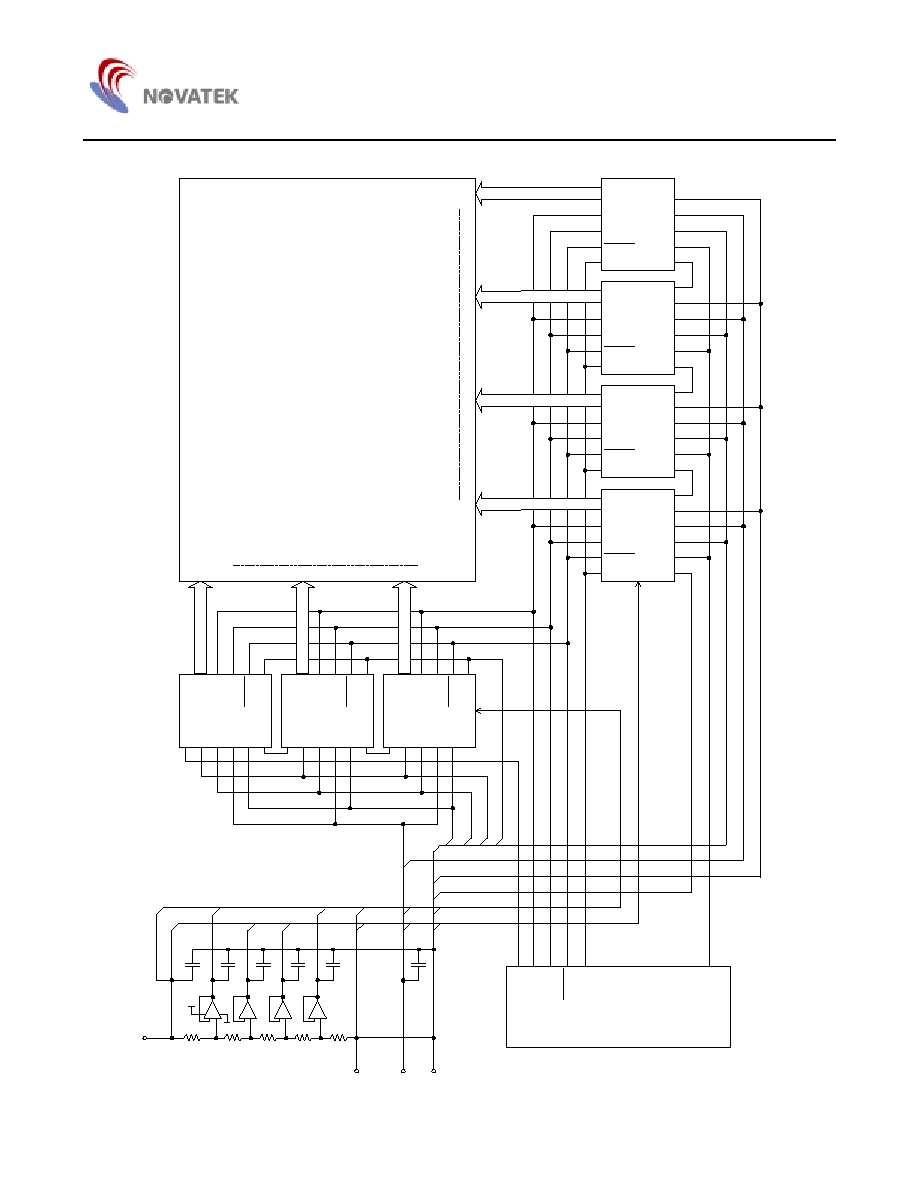

Application Circuit (for reference only)

FR

LP

XCK

EIO1

MD

S/C

L/R

D0 - D7

EIO2

DISPOFF

FR

LP

XCK

EIO1

MD

S/C

L/R

YD

EIO2

DISPOFF

FR

LP

XCK

EIO1

MD

S/C

L/R

D0 - D7

EIO2

DISPOFF

C

O

M

1

C

O

M

2

C

O

M

3

C

O

M

4

7

9

C

O

M

4

8

0

SEG1

SEG2

SEG3

SEG640

SEG639

Y1 - Y160

Y1 - Y160

Y1 - Y160

LCD controller

/8

FR

LP

XCK

EIO1

MD

S/C

L/R

D0 - D7

EIO2

FR

LP

XCK

EIO1

MD

S/C

L/R

D0 - D7

EIO2

FR

LP

XCK

EIO1

MD

S/C

L/R

D0 - D7

EIO2

FR

LP

XCK

EIO1

MD

S/C

L/R

D0 - D7

EIO2

/8

Y1 - Y160

Y1 - Y160

Y1 - Y160

Y1 - Y160

/5

/5

FR

LP

XCK

XD

0 -

XD

7

D0 - D7

DISPOFF

V

DD

V

SS

(case of 1/n bias)

NT7703*4

NT7703*3

640*480 DOT MATRIX

LCD PANEL

DISPOFF

DISPOFF

DISPOFF

DISPOFF

V

5

V

1

V

2

V

3

4

V

(n-4)R

R

R

R

Note: V

0

-V

1

>1.5V

R

V

0

V

0

V

SS

NT7703

26

Bonding Diagram

NT7703

8168um

1168um

1

x

ALK_L

x

x

ALK_R

x

x

Dummy Pad

x

128

129

144

145

272

273

288

( 0 , 0 )

X

Y

x

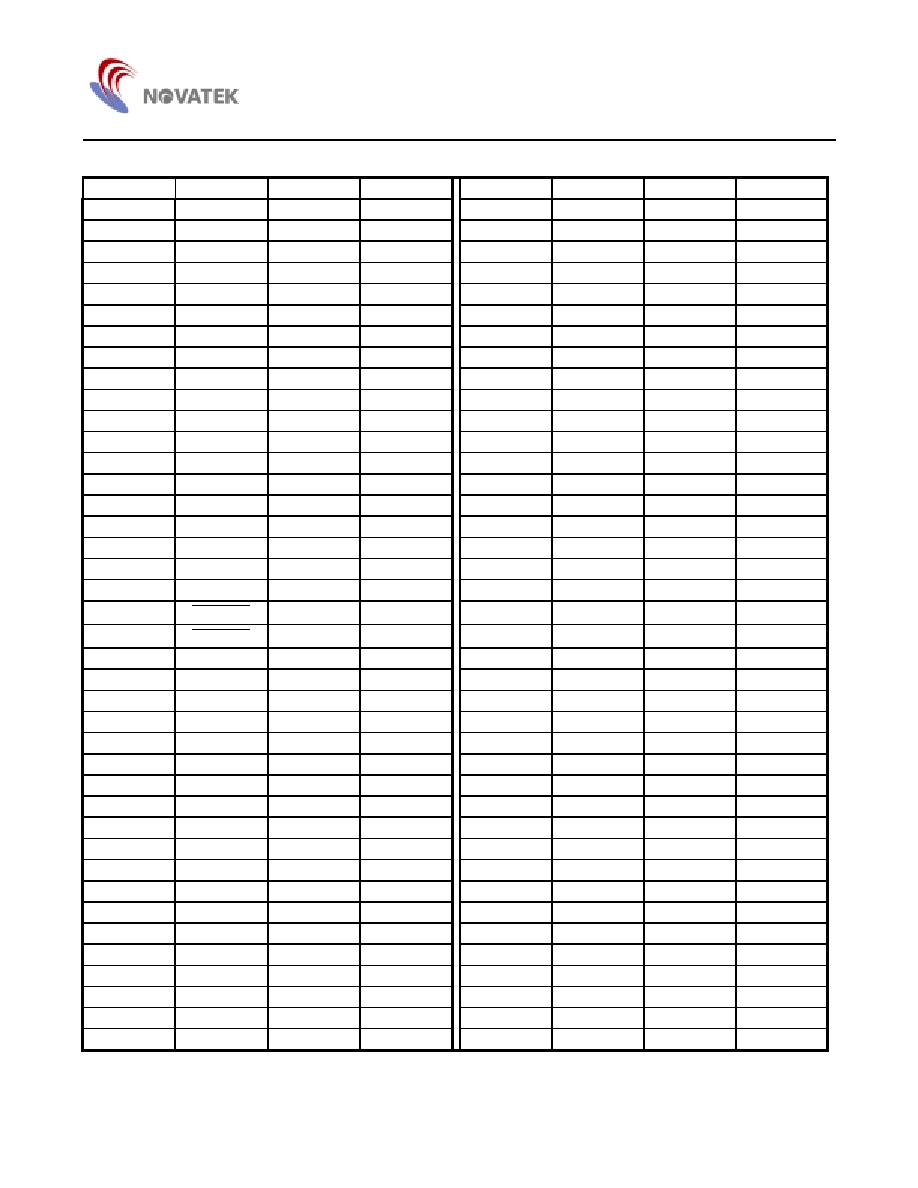

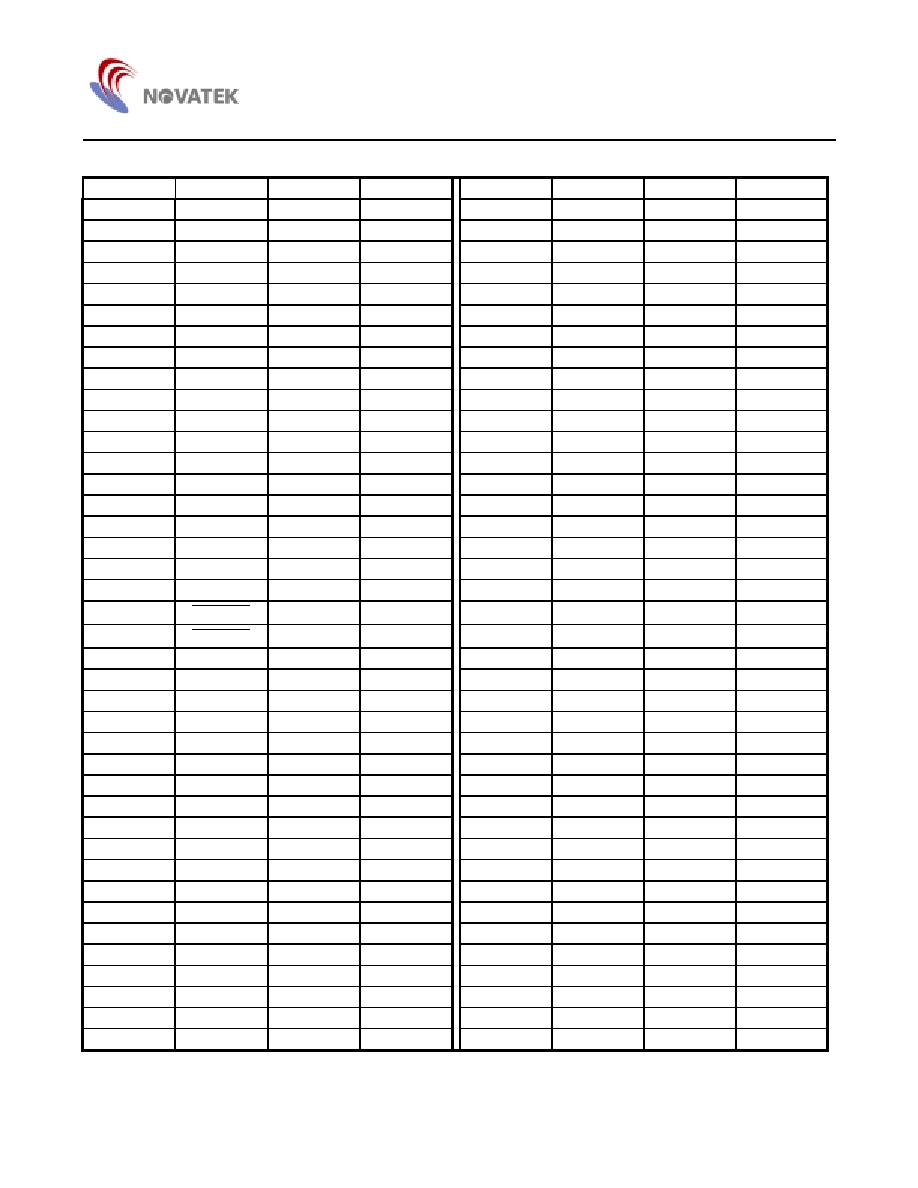

Pad Location

Pad No.

Designation

X

Y

Pad No.

Designation

X

Y

1

V

0L

-3820

-521

31

V

SS

-2010

-521

2

V

0L

-3750

-521

32

V

SS

-1950

-521

3

V

0L

-3690

-521

33

V

SS

-1890

-521

4

V

0L

-3630

-521

34

V

SS

-1830

-521

5

V

0L

-3570

-521

35

V

SS

-1770

-521

6

V

0L

-3510

-521

36

V

SS

-1710

-521

7

V

0L

-3450

-521

37

V

SS

-1650

-521

8

V

12L

-3390

-521

38

V

SS

-1590

-521

9

V

12L

-3330

-521

39

V

SS

-1530

-521

10

V

12L

-3270

-521

40

L/R

-1470

-521

11

V

12L

-3210

-521

41

L/R

-1410

-521

12

V

12L

-3150

-521

42

V

DD

-1350

-521

13

V

43L

-3090

-521

43

V

DD

-1290

-521

14

V

43L

-3030

-521

44

V

DD

-1230

-521

15

V

43L

-2970

-521

45

V

DD

-1170

-521

16

V

43L

-2910

-521

46

V

DD

-1110

-521

17

V

43L

-2850

-521

47

V

DD

-1050

-521

18

V

5L

-2790

-521

48

V

DD

-990

-521

19

V

5L

-2730

-521

49

V

DD

-930

-521

20

V

5L

-2670

-521

50

V

DD

-870

-521

21

V

5L

-2610

-521

51

V

DD

-810

-521

22

V

5L

-2550

-521

52

V

DD

-750

-521

23

V

SS

-2490

-521

53

V

DD

-690

-521

24

V

SS

-2430

-521

54

V

DD

-630

-521

25

V

SS

-2370

-521

55

V

DD

-570

-521

26

V

SS

-2310

-521

56

V

DD

-510

-521

27

V

SS

-2250

-521

57

V

DD

-450

-521

28

V

SS

-2190

-521

58

S/C

-390

-521

29

V

SS

-2130

-521

59

S/C

-330

-521

30

V

SS

-2070

-521

60

EIO

2

-270

-521

NT7703

27

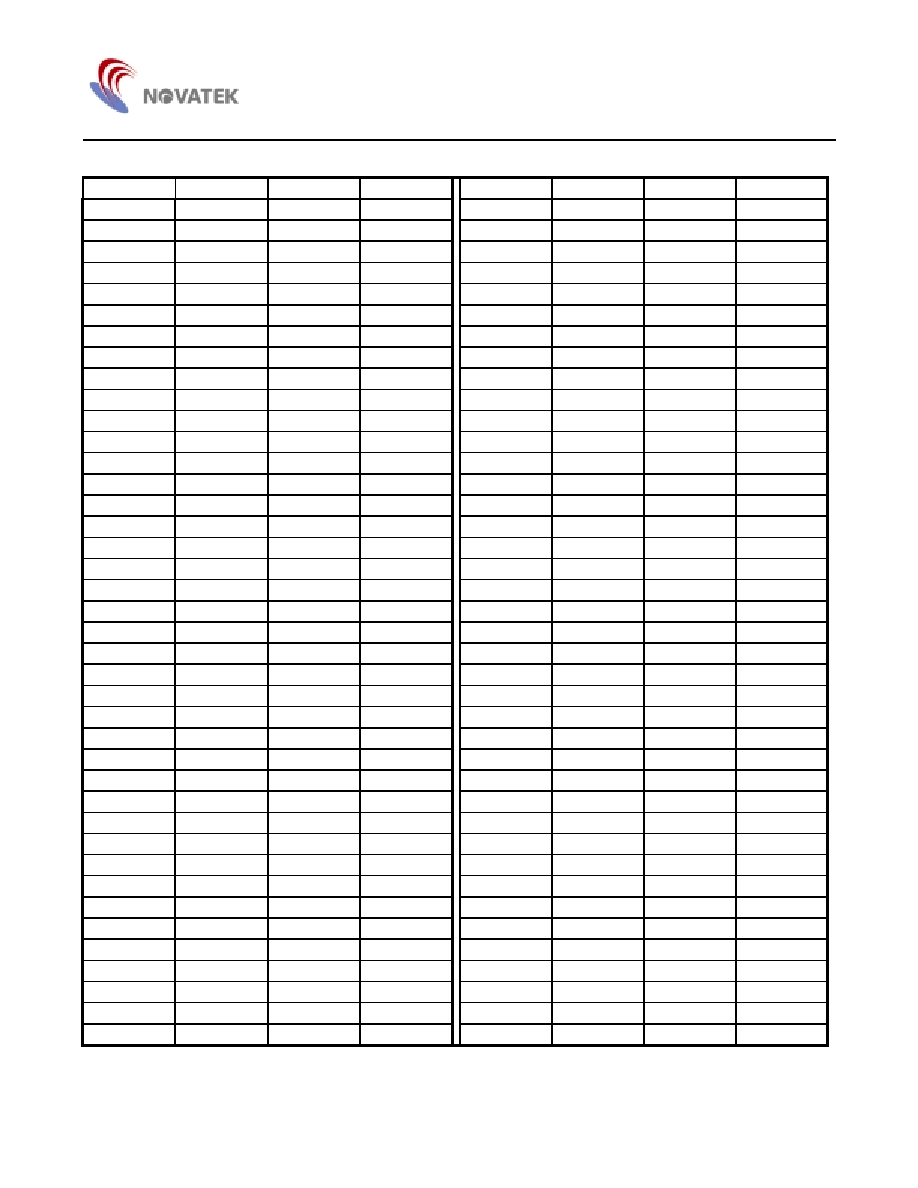

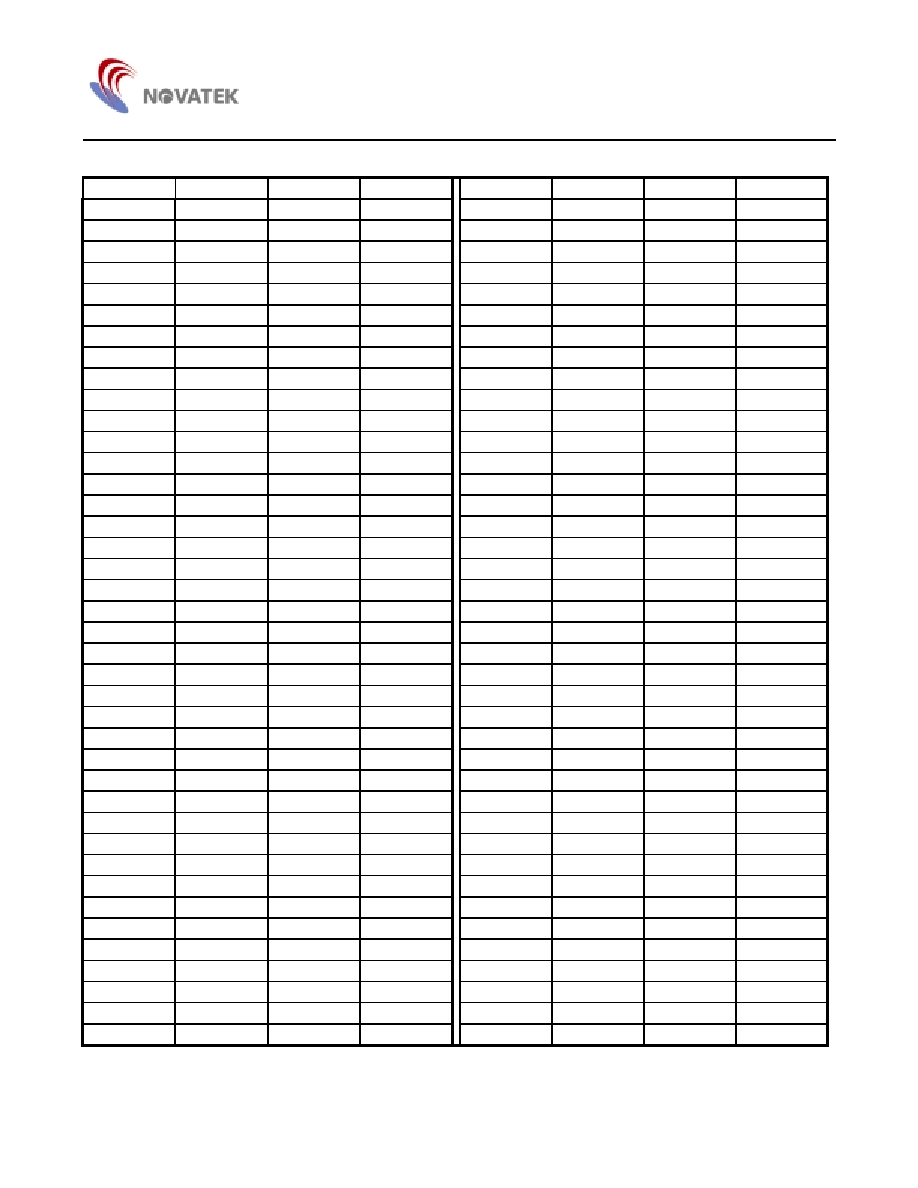

Pad Location

(continued)

Pad No.

Designation

X

Y

Pad No.

Designation

X

Y

61

EIO

2

-210

-521

101

V

SS

2190

-521

62

D0

-150

-521

102

V

SS

2250

-521

63

D0

-90

-521

103

V

SS

2310

-521

64

D1

-30

-521

104

V

SS

2370

-521

65

D1

30

-521

105

V

SS

2430

-521

66

D2

90

-521

106

V

SS

2490

-521

67

D2

150

-521

107

V

5R

2550

-521

68

D3

210

-521

108

V

5R

2610

-521

69

D3

270

-521

109

V

5R

2670

-521

70

D4

330

-521

110

V

5R

2730

-521

71

D4

390

-521

111

V

5R

2790

-521

72

D5

450

-521

112

V

43R

2850

-521

73

D5

510

-521

113

V

43R

2910

-521

74

D6

570

-521

114

V

43R

2970

-521

75

D6

630

-521

115

V

43R

3030

-521

76

D7

690

-521

116

V

43R

3090

-521

77

D7

750

-521

117

V

12R

3150

-521

78

XCK

810

-521

118

V

12R

3210

-521

79

XCK

870

-521

119

V

12R

3270

-521

80

DISPOFF

930

-521

120

V

12R

3330

-521

81

DISPOFF

990

-521

121

V

12R

3390

-521

82

LP

1050

-521

122

V

0R

3450

-521

83

LP

1110

-521

123

V

0R

3510

-521

84

EIO

1

1170

-521

124

V

0R

3570

-521

85

EIO

1

1230

-521

125

V

0R

3630

-521

86

FR

1290

-521

126

V

0R

3690

-521

87

FR

1350

-521

127

V

0R

3750

-521

88

MD

1410

-521

128

V

0R

3820

-521

89

MD

1470

-521

129

Y1

4030

-450

90

V

SS

1530

-521

130

Y2

4030

-390

91

V

SS

1590

-521

131

Y3

4030

-330

92

V

SS

1650

-521

132

Y4

4030

-270

93

V

SS

1710

-521

133

Y5

4030

-210

94

V

SS

1770

-521

134

Y6

4030

-150

95

V

SS

1830

-521

135

Y7

4030

-90

96

V

SS

1890

-521

136

Y8

4030

-30

97

V

SS

1950

-521

137

Y9

4030

30

98

V

SS

2010

-521

139

Y10

4030

90

99

V

SS

2070

-521

139

Y11

4030

150

100

V

SS

2130

-521

140

Y12

4030

210

NT7703

28

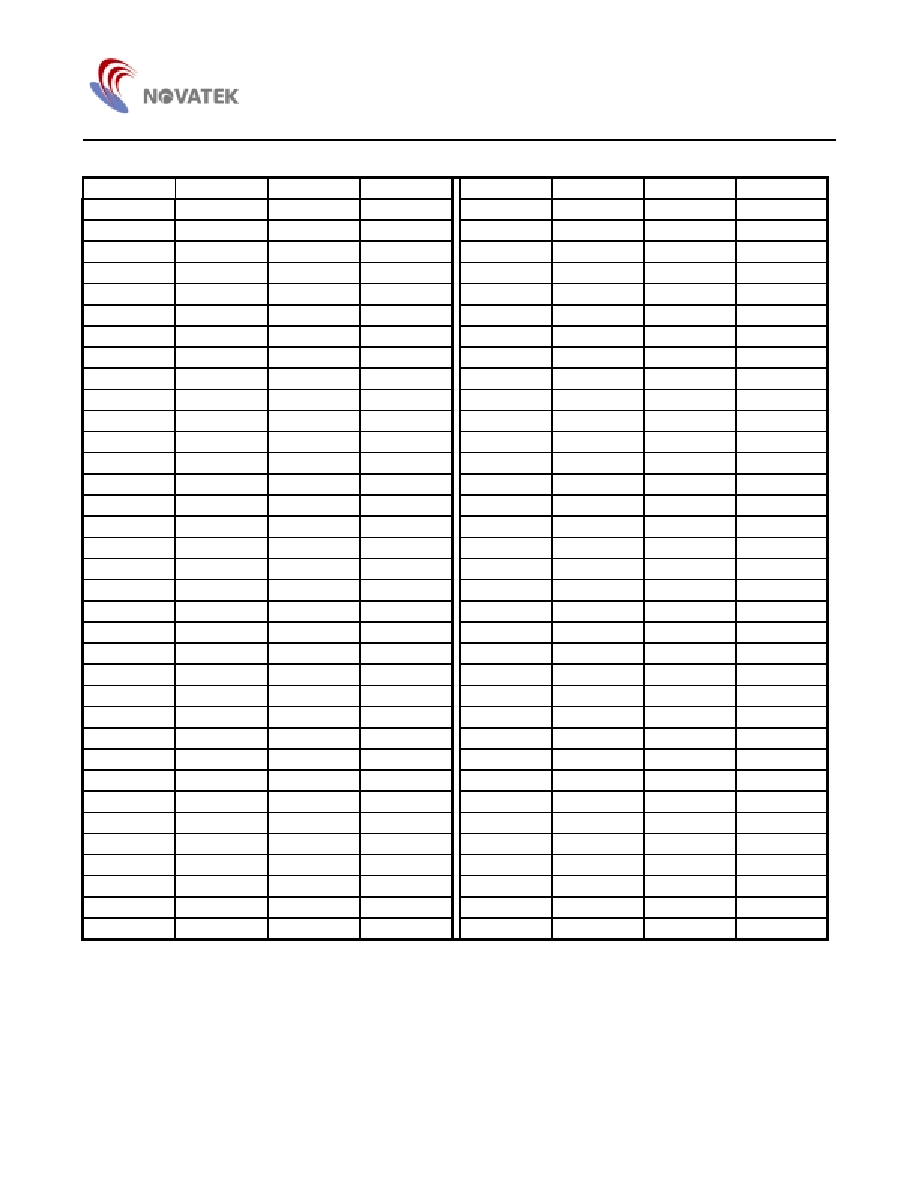

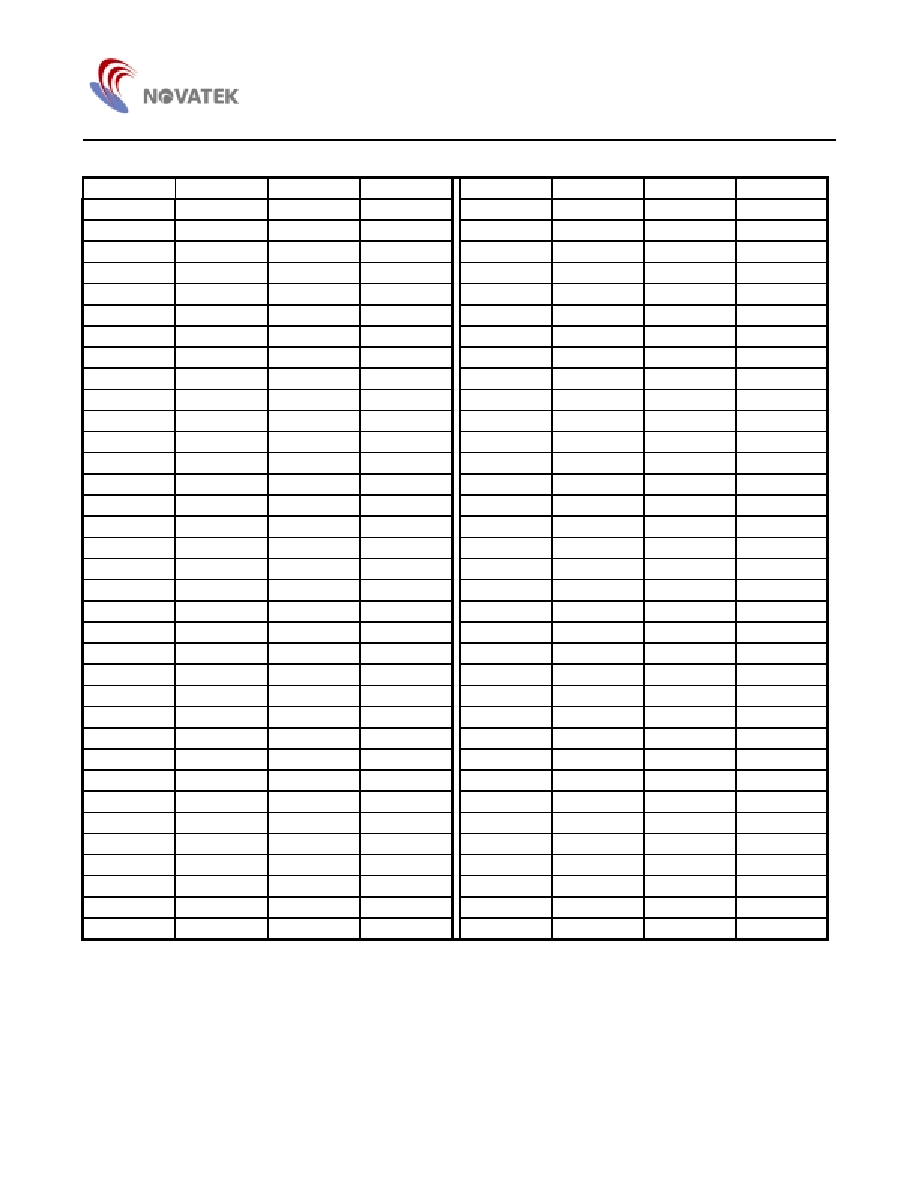

Pad Location

(continued)

Pad No.

Designation

X

Y

Pad No.

Designation

X

Y

141

Y13

4030

270

181

Y53

1650

529

142

Y14

4030

330

182

Y54

1590

529

143

Y15

4030

390

183

Y55

1530

529

144

Y16

4030

450

184

Y56

1470

529

145

Y17

3810

529

185

Y57

1410

529

146

Y18

3750

529

186

Y58

1350

529

147

Y19

3690

529

187

Y59

1290

529

148

Y20

3630

529

188

Y60

1230

529

149

Y21

3570

529

189

Y61

1170

529

150

Y22

3510

529

190

Y62

1110

529

151

Y23

3450

529

191

Y63

1050

529

152

Y24

3390

529

192

Y64

990

529

153

Y25

3330

529

193

Y65

930

529

154

Y26

3270

529

194

Y66

870

529

155

Y27

3210

529

195

Y67

810

529

156

Y28

3150

529

196

Y68

750

529

157

Y29

3090

529

197

Y69

690

529

158

Y30

3030

529

198

Y70

630

529

159

Y31

2970

529

199

Y71

570

529

160

Y32

2910

529

200

Y72

510

529

161

Y33

2850

529

201

Y73

450

529

162

Y34

2790

529

202

Y74

390

529

163

Y35

2730

529

203

Y75

330

529

164

Y36

2670

529

204

Y76

270

529

165

Y37

2610

529

205

Y77

210

529

166

Y38

2550

529

206

Y78

150

529

167

Y39

2490

529

207

Y79

90

529

168

Y40

2430

529

208

Y80

30

529

169

Y41

2370

529

209

Y81

-30

529

170

Y42

2310

529

210

Y82

-90

529

171

Y43

2250

529

211

Y83

-150

529

172

Y44

2190

529

212

Y84

-210

529

173

Y45

2130

529

213

Y85

-270

529

174

Y46

2070

529

214

Y86

-330

529

175

Y47

2010

529

215

Y87

-390

529

176

Y48

1950

529

216

Y88

-450

529

177

Y49

1890

529

217

Y89

-510

529

178

Y50

1830

529

218

Y90

-570

529

179

Y51

1770

529

219

Y91

-630

529

180

Y52

1710

529

220

Y92

-690

529

NT7703

29

Pad Location

(continued)

Pad No.

Designation

X

Y

Pad No.

Designation

X

Y

221

Y93

-750

529

256

Y128

-2850

529

222

Y94

-810

529

257

Y129

-2910

529

223

Y95

-870

529

258

Y130

-2970

529

224

Y96

-930

529

259

Y131

-3030

529

225

Y97

-990

529

260

Y132

-3090

529

226

Y98

-1050

529

261

Y133

-3150

529

227

Y99

-1110

529

262

Y134

-3210

529

228

Y100

-1170

529

263

Y135

-3270

529

229

Y101

-1230

529

264

Y136

-3330

529

230

Y102

-1290

529

265

Y137

-3390

529

231

Y103

-1350

529

266

Y138

-3450

529

232

Y104

-1410

529

267

Y139

-3510

529

233

Y105

-1470

529

268

Y140

-3570

529

234

Y106

-1530

529

269

Y141

-3630

529

235

Y107

-1590

529

270

Y142

-3690

529

236

Y108

-1650

529

271

Y143

-3750

529

237

Y109

-1710

529

272

Y144

-3810

529

238

Y110

-1770

529

273

Y145

-4030

450

239

Y111

-1830

529

274

Y146

-4030

390

240

Y112

-1890

529

275

Y147

-4030

330

241

Y113

-1950

529

276

Y148

-4030

270

242

Y114

-2010

529

277

Y149

-4030

210

243

Y115

-2070

529

278

Y150

-4030

150

244

Y116

-2130

529

279

Y151

-4030

90

245

Y117

-2190

529

280

Y152

-4030

30

246

Y118

-2250

529

281

Y153

-4030

-30

247

Y119

-2310

529

282

Y154

-4030

-90

248

Y120

-2370

529

283

Y155

-4030

-150

249

Y121

-2430

529

284

Y156

-4030

-210

250

Y122

-2490

529

285

Y157

-4030

-270

251

Y123

-2550

529

286

Y158

-4030

-330

252

Y124

-2610

529

287

Y159

-4030

-390

253

Y125

-2670

529

288

Y160

-4030

-450

254

Y126

-2730

529

ALK_L

-3921

-534

255

Y127

-2790

529

ALK_R

3921

-534

NT7703

30

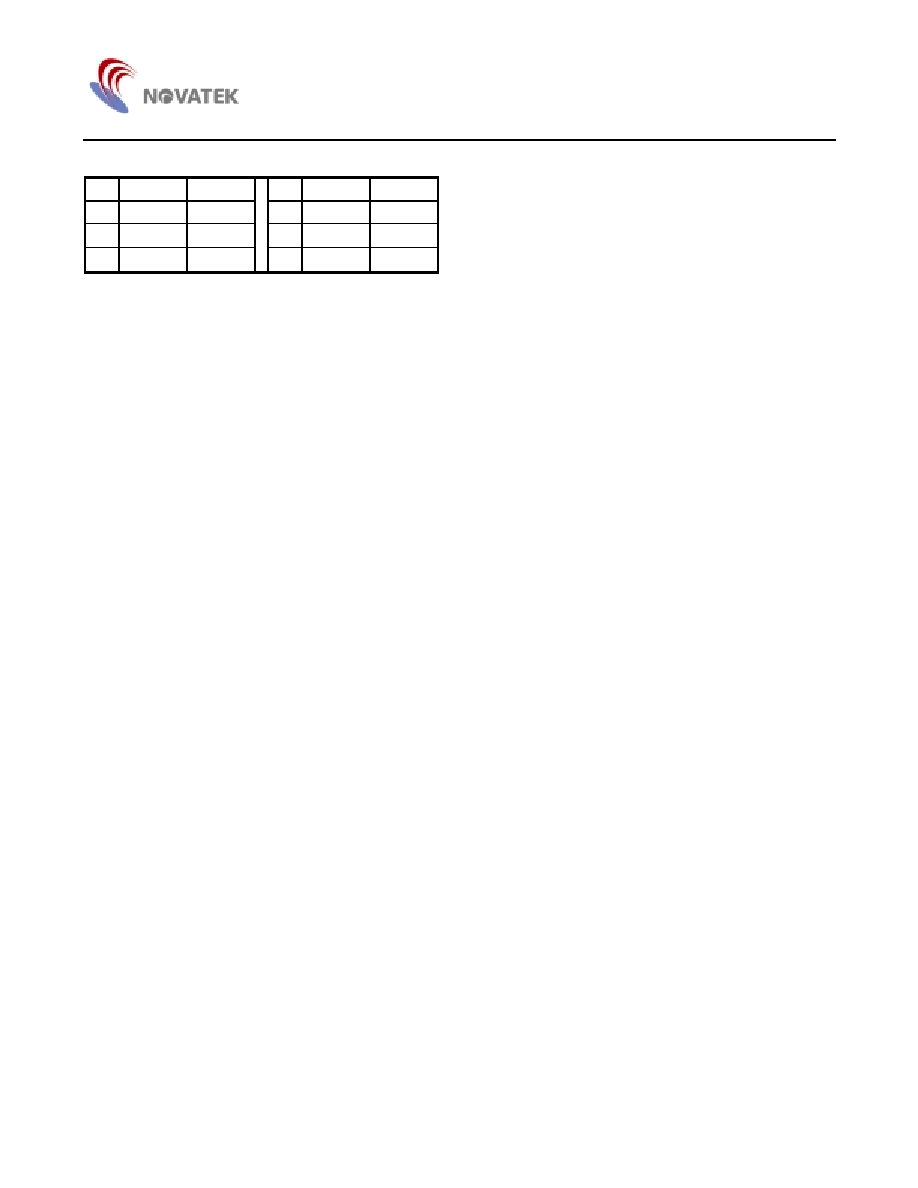

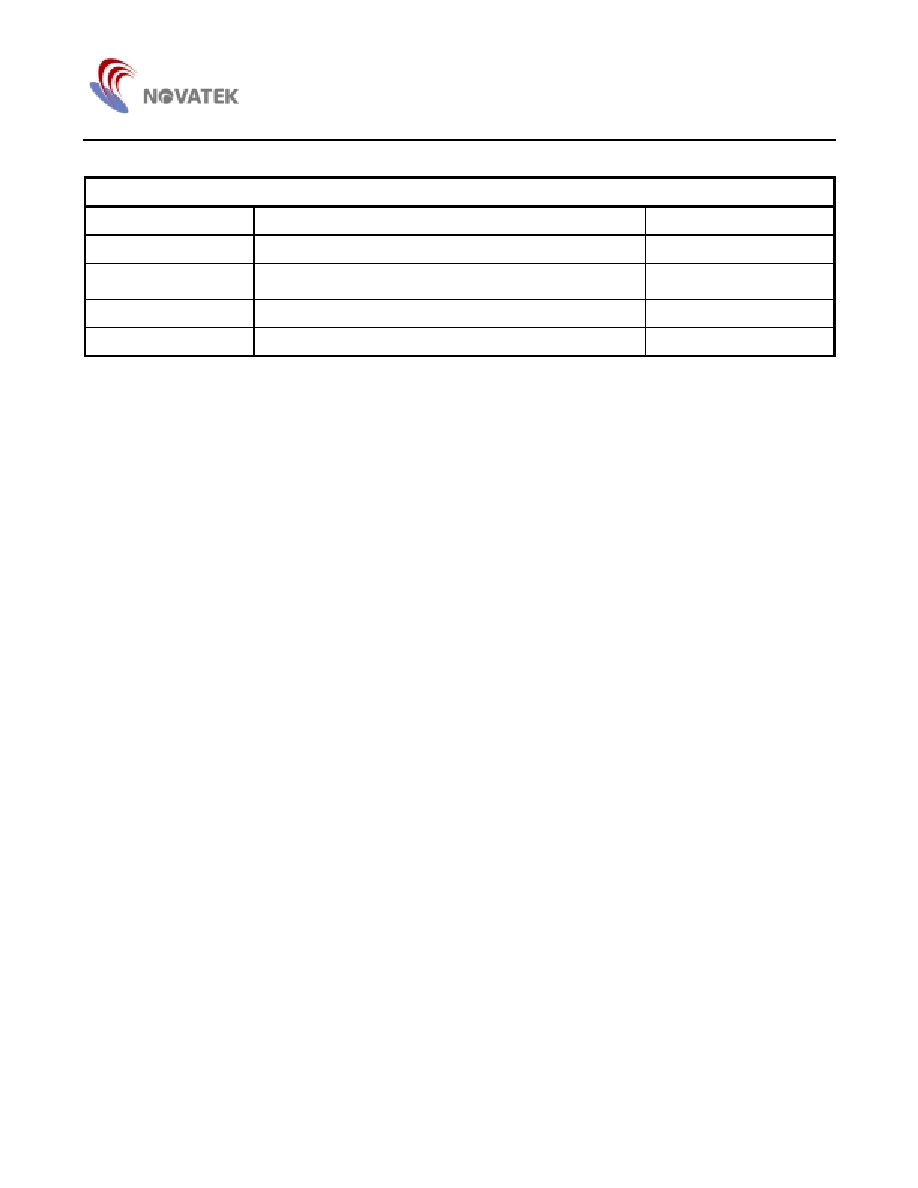

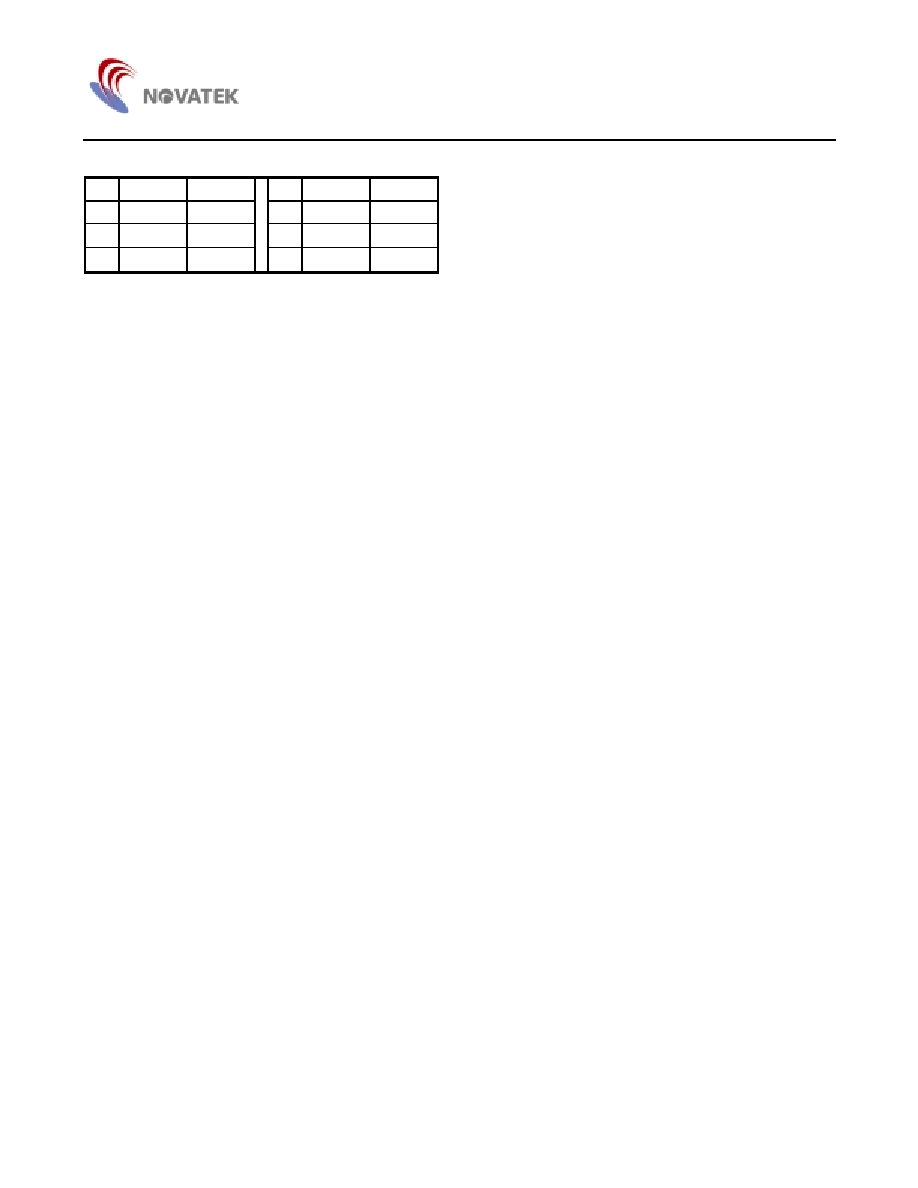

Dummy Pad Location (Total: 6 pin)

NO.

X

Y

NO.

X

Y

1

4030

-520

4

-3880

529

2

4030

520

5

-4030

520

3

3880

529

6

-4030

-520

NT7703

31

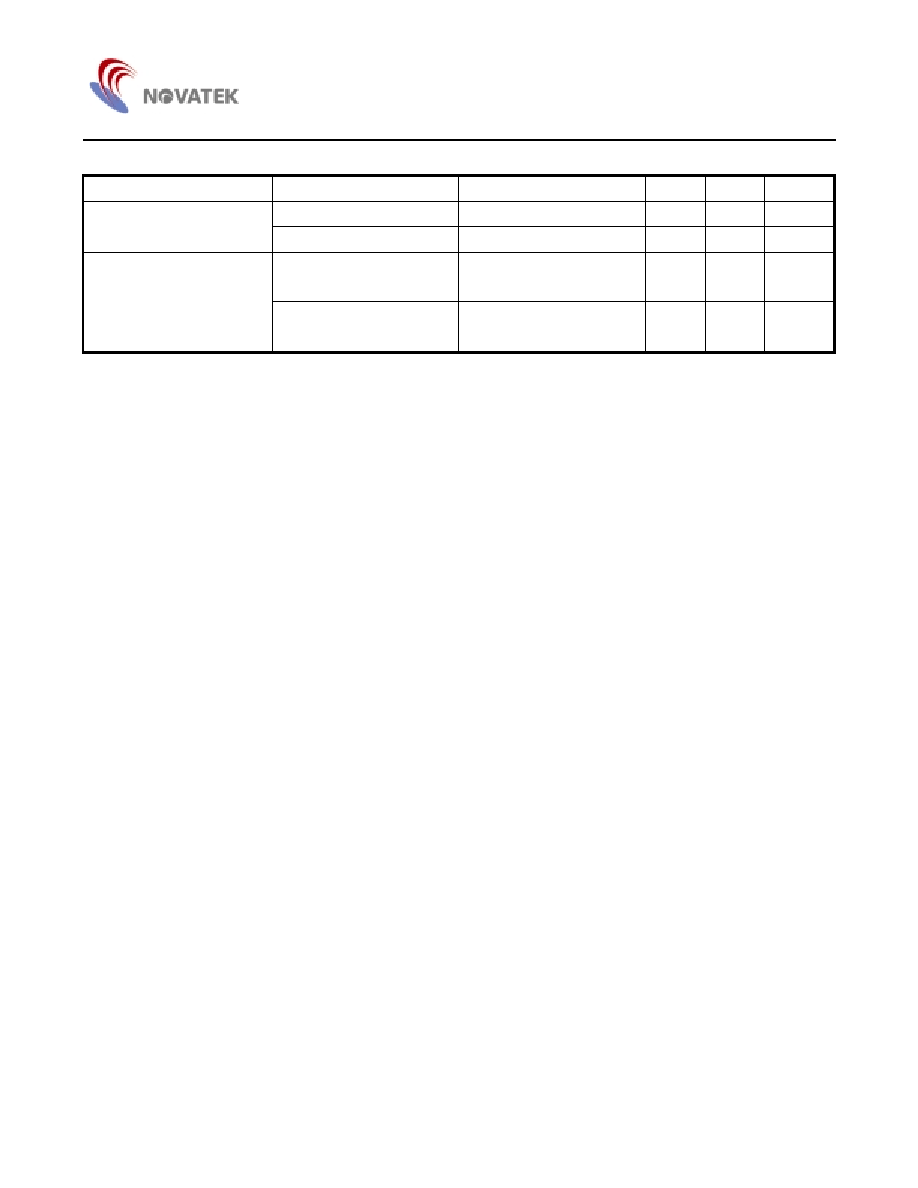

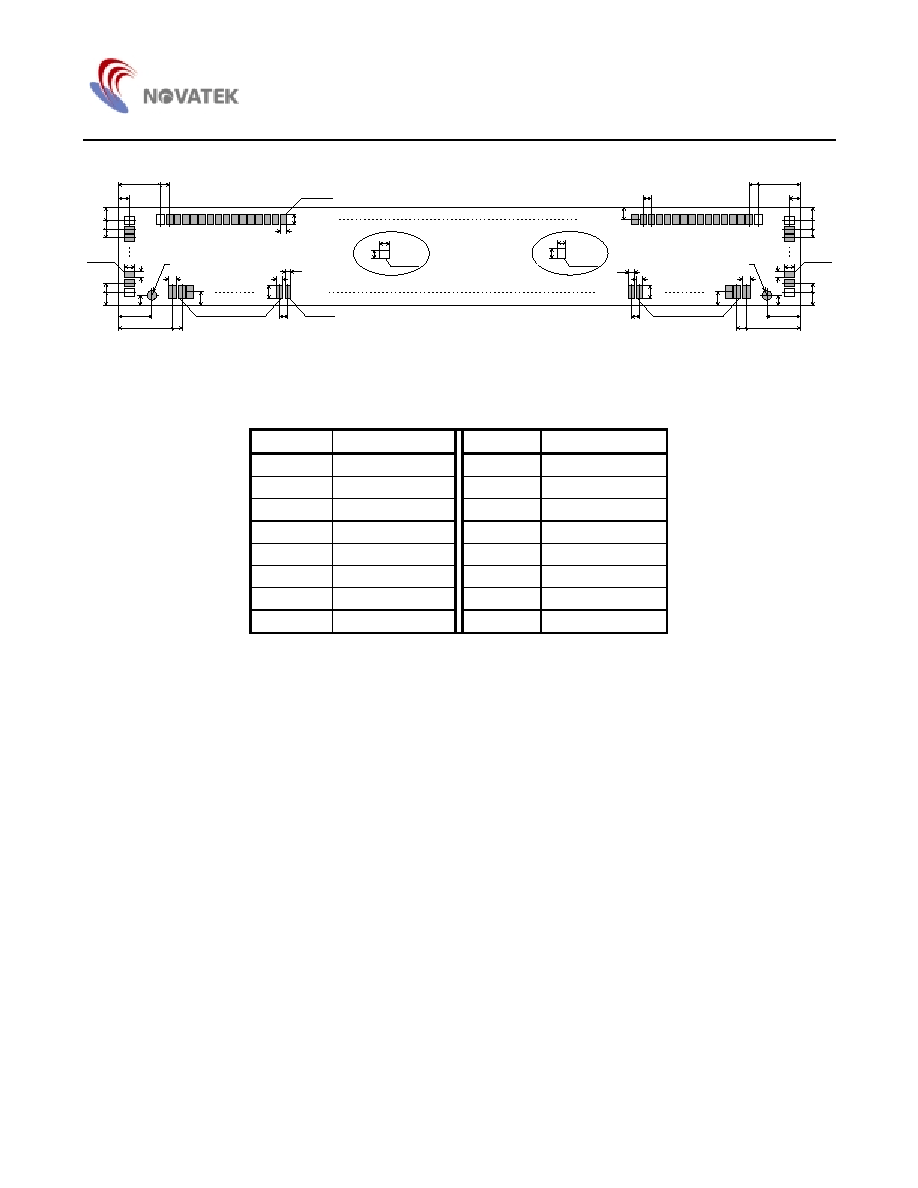

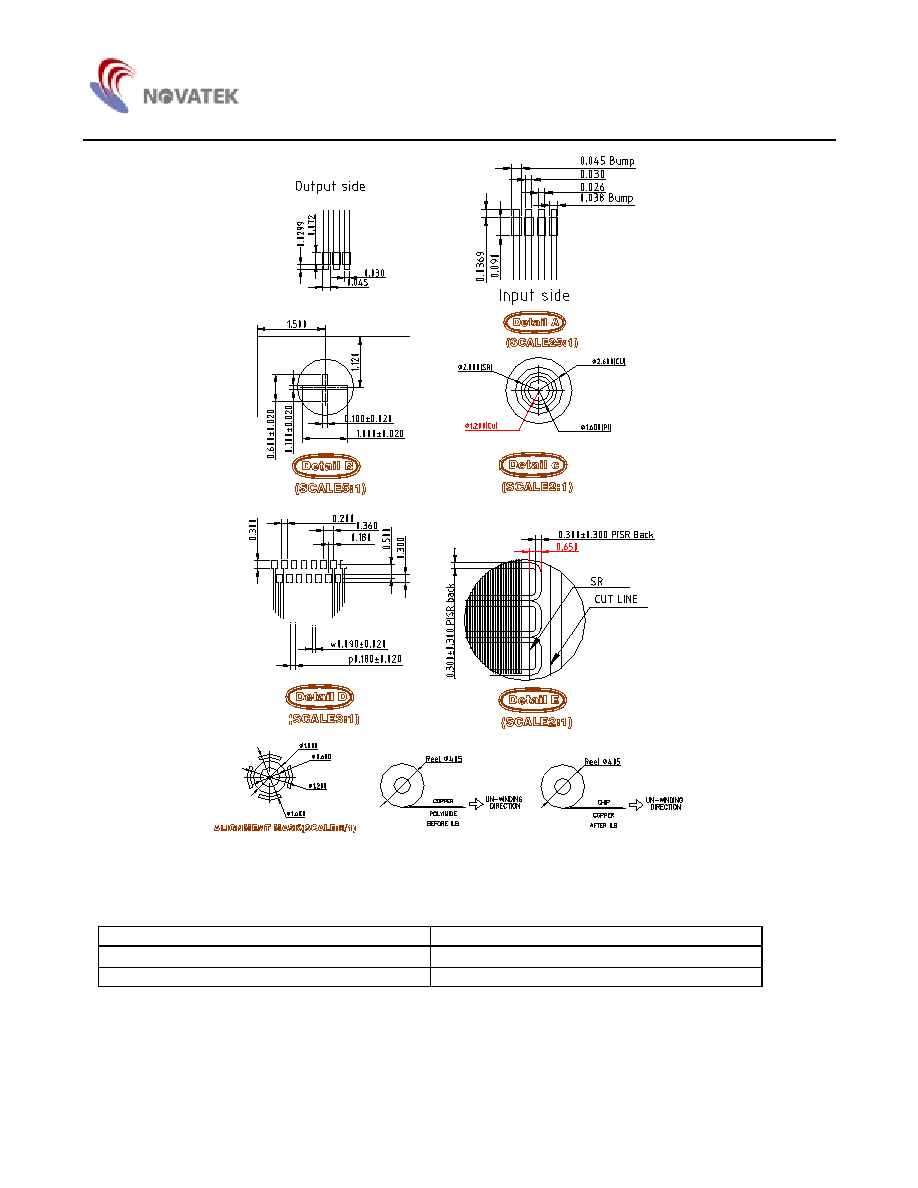

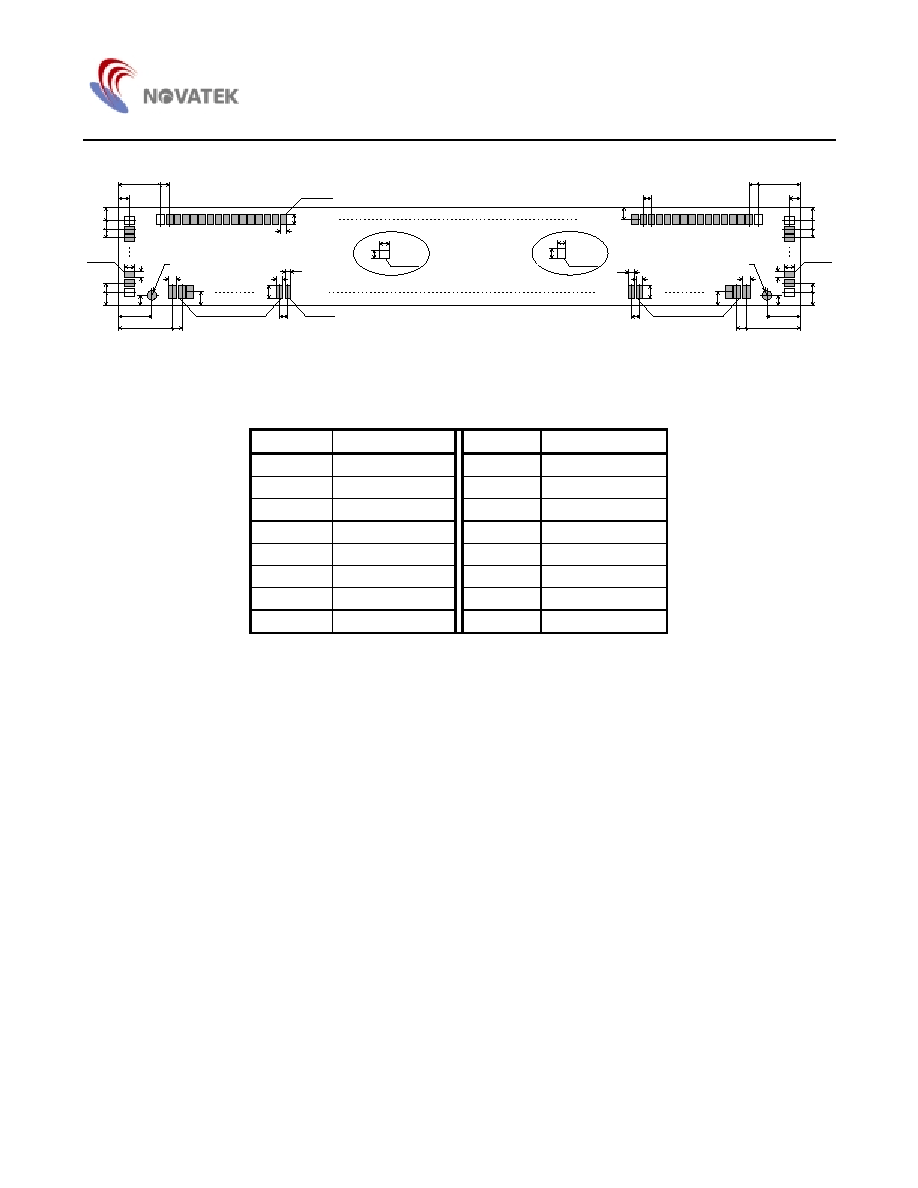

Package Information

A1

A2

D1

D2

n1

m1

A1

A2

D1

C2

128

m1

n1

D2

C1

D1

C1

D1

n1

m1

16

n1

m1

H

D2

C1

D1

C1

D1

n1

m1

16

n1

m1

H

NT7703

B

J

D1

r

r

m2

n1

m2

4

n1

m2

m2

n1

2

m2

n1

m2

C3

m1

n2

50

m3

n2

m2

C3

D2

m1

n2

B

J

D1

D2

m3

m3

38

m1

n2 (L)

38

m1

n2 (R)

Chip Outline Dimensions

unit: um

Symbol

Dimensions in um

Symbol

Dimensions in um

A1

204

H

50

A2

54

J

163

B

264

m1

39

C1

64

m2

55

C2

55

m3

38

C3

63

n1

72

D1

70

n2

90

D2

60

r

35

NT7703

32

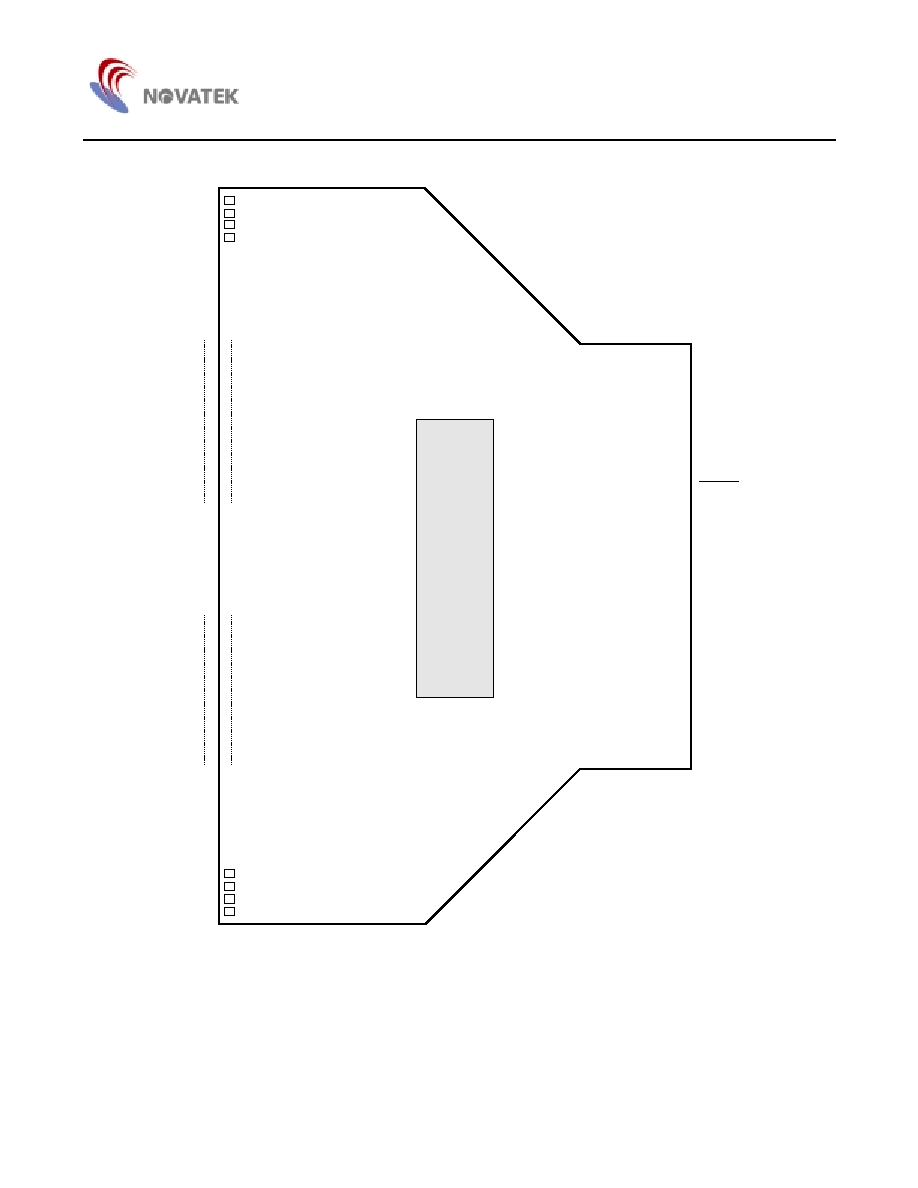

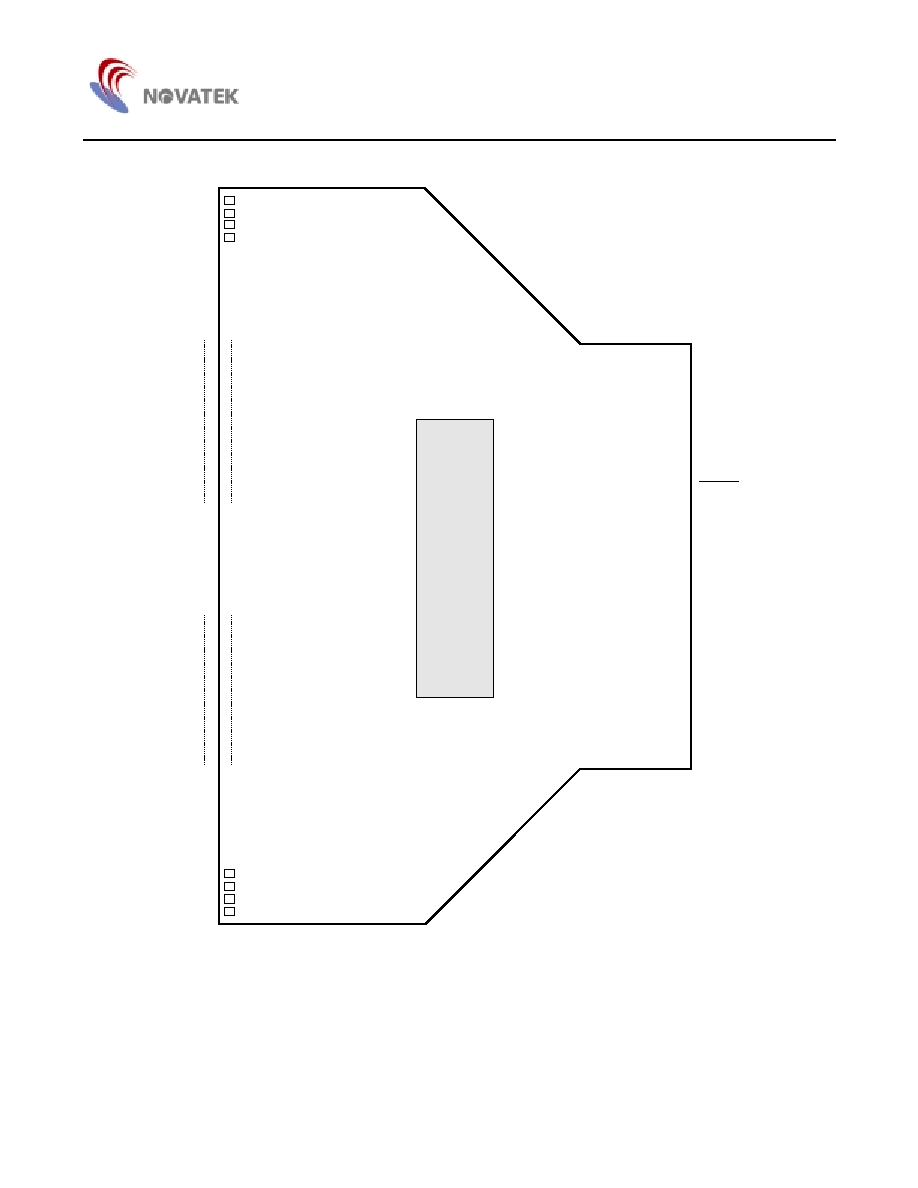

TCP Pin Layout

NT7703

VSS(V5R)

V43R

V12R

V0R

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

V0L

V12L

V43L

VSS(V5L)

28

29

30

31

27

32

104

105

106

107

108

109

181

182

183

184

185

186

Y1

Y2

Y3

Y4

Y5

Y6

Y78

Y79

Y80

Y81

Y82

Y83

Y155

Y156

Y157

Y158

Y159

Y160

DUMMY

DUMMY

DUMMY

DUMMY

DUMMY

DUMMY

DUMMY

DUMMY

L/R

VDD

S/C

EIO2

D0

D1

D2

D3

D4

D5

D6

D7

XCK

LP

EIO1

FR

MD

DISPOFF

(COPPER SIDE VIEW)

NT7703

33

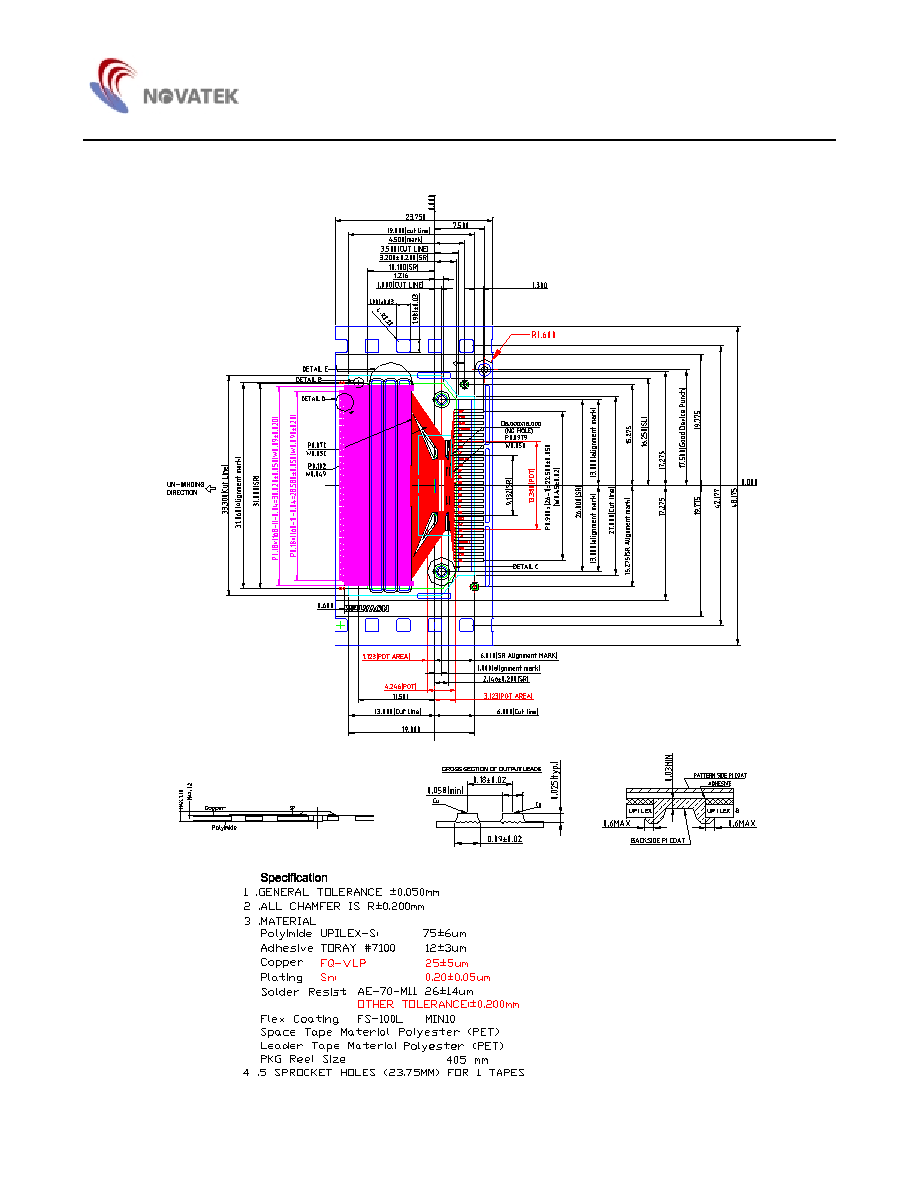

External View of TCP Pins

N T7703H -TA B 18

N

T

7703H

- TA

B

1

8

NT7703

34

Cautions concerning storage:

1. When storing the product, it is recommended that it be left in its shipping package.

After the seal of the packing bag has been broke, store the products in a nitrogen atmosphere.

2. Storage conditions :

Storage state

Storage conditions

unopened (less than 90 days)

Temperature: 5 to 30

; humidity: 80%RH or less

After seal of broken (less than 30 days)

Room temperature, dry nitrogen atmosphere

3. Don't store in a location exposed to corrosive gas or excessive dust.

4. Don't store in a location exposed to direct sunlight of subject to sharp changes in temperature.

5. Don't store the product such that it is subjected to an excessive load weight, such as by stacking.

6. Deterioration of the plating may occur after long-term storage, so special care is required.

It is recommended that the products be inspected before use.

NT7703

35

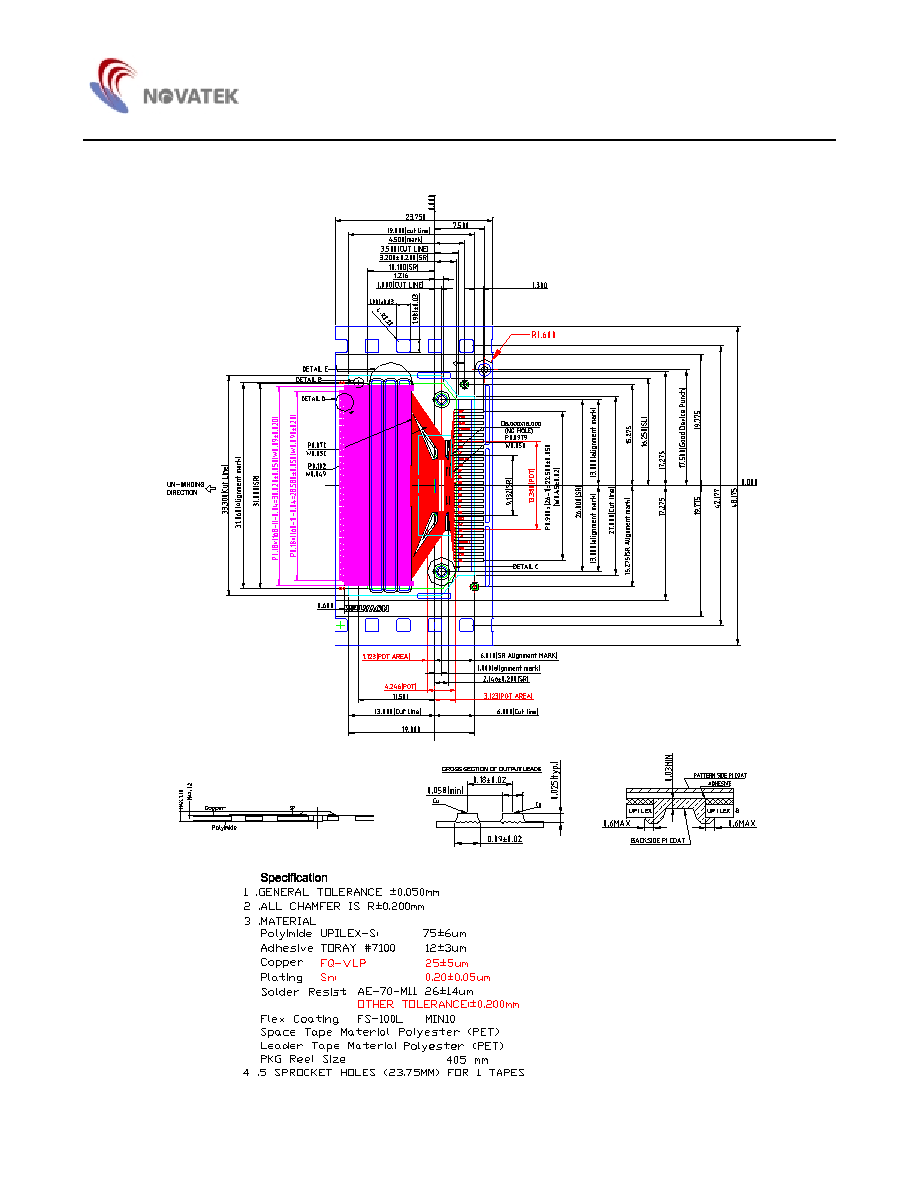

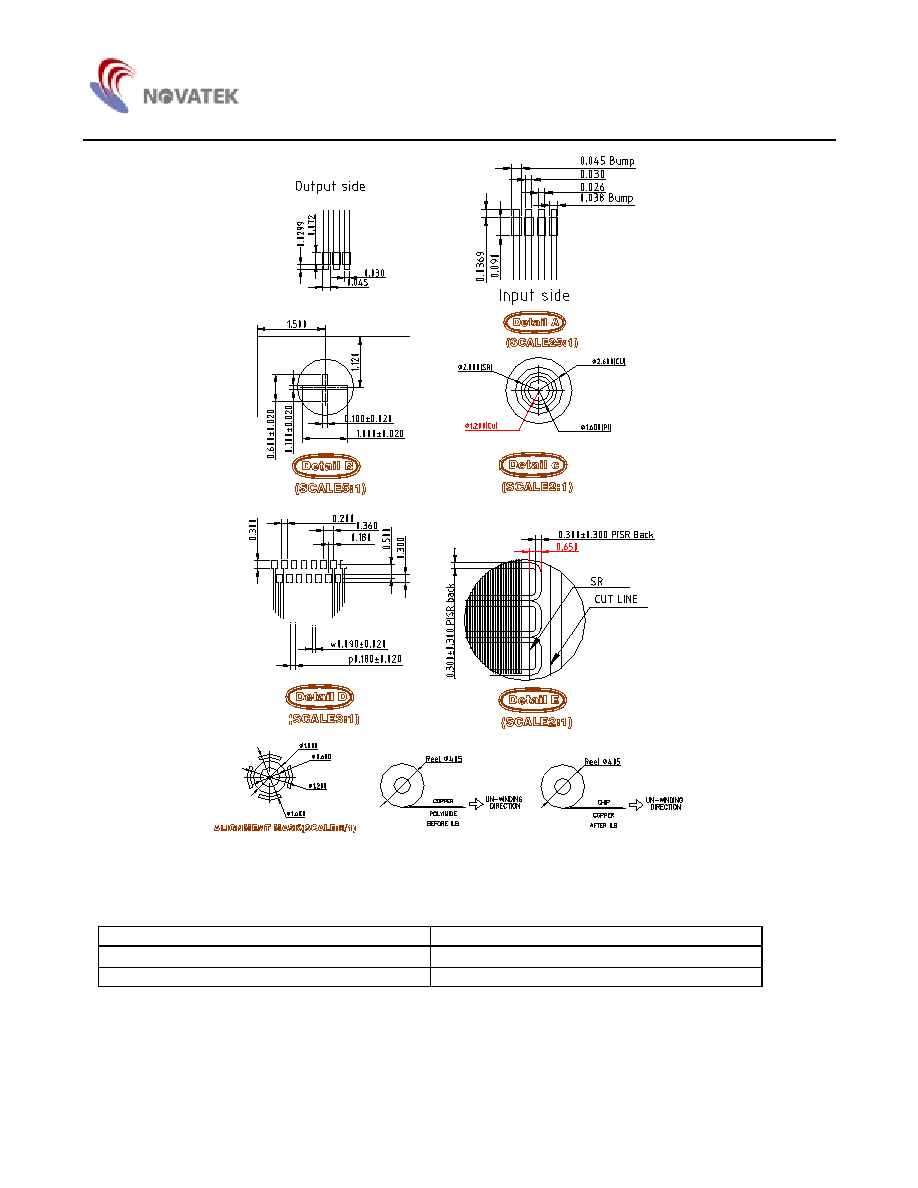

Tray Information

6

25=150

d

c

SECTION Y-Y

e

f

W2

h

g

W1

T1

T2

W2

a

b

W1

h

g

e

f

T1

T2

SECTION X-X

X

X

H30-334

59-25

Tray Outline Dimensions

unit: mm

Symbol

Dimensions in mm

Symbol

Dimensions in mm

a

1.50

g

0.64

b

2.67

h

4.20

c

8.50

W1

76.0

d

10.90

W2

68.0

e

1.60

T1

71.0

f

1.40

T2

68.3

NT7703

36

Ordering Information

Part No.

Package

NT7703H-BDT

Au bump on chip tray

NT7703H-TAB18

TCP Form

NT7703

37

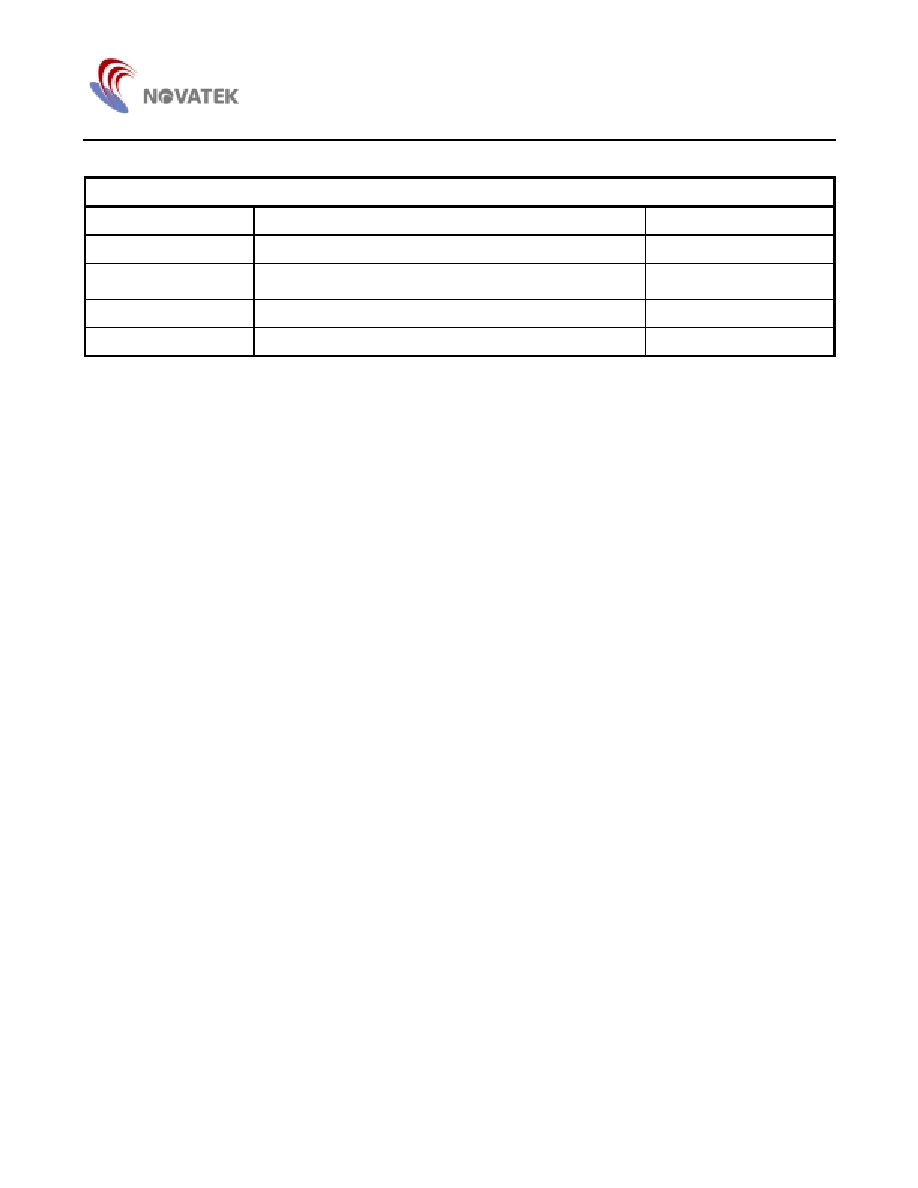

Product Spec. Change Notice

NT7703 Specification Revision History

Version

Content

Date

1.0

TCP and tray information addition (Page 33 - 36)

Dec. 2001

0.2

Gold Bump Size revision (Page 31)

m1: 45

39, m2: 58

55

Sep. 2001

0.1

Pad Location Addition

Nov. 2000

0.0

Original

Nov. 2000