| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 100353QCX | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

100353

Low Power 8-Bit Register

General Description

The 100353 contains eight D-type edge triggered, master/

slave flip-flops with individual inputs (D

n

), true outputs (Q

n

),

a clock input (CP), and a common clock enable pin (CEN).

Data enters the master when CP is LOW and transfers to the

slave when CP goes HIGH. When the CEN input goes HIGH

it overrides all other inputs, disables the clock, and the Q out-

puts maintain the last state.

The 100353 output drivers are designed to drive 50

termi-

nation to -2.0V. All inputs have 50 k

pull-down resistors.

Features

n

Low power operation

n

2000V ESD protection

n

Voltage compensated operating range = -4.2V to -5.7V

n

Available to MIL-STD-883

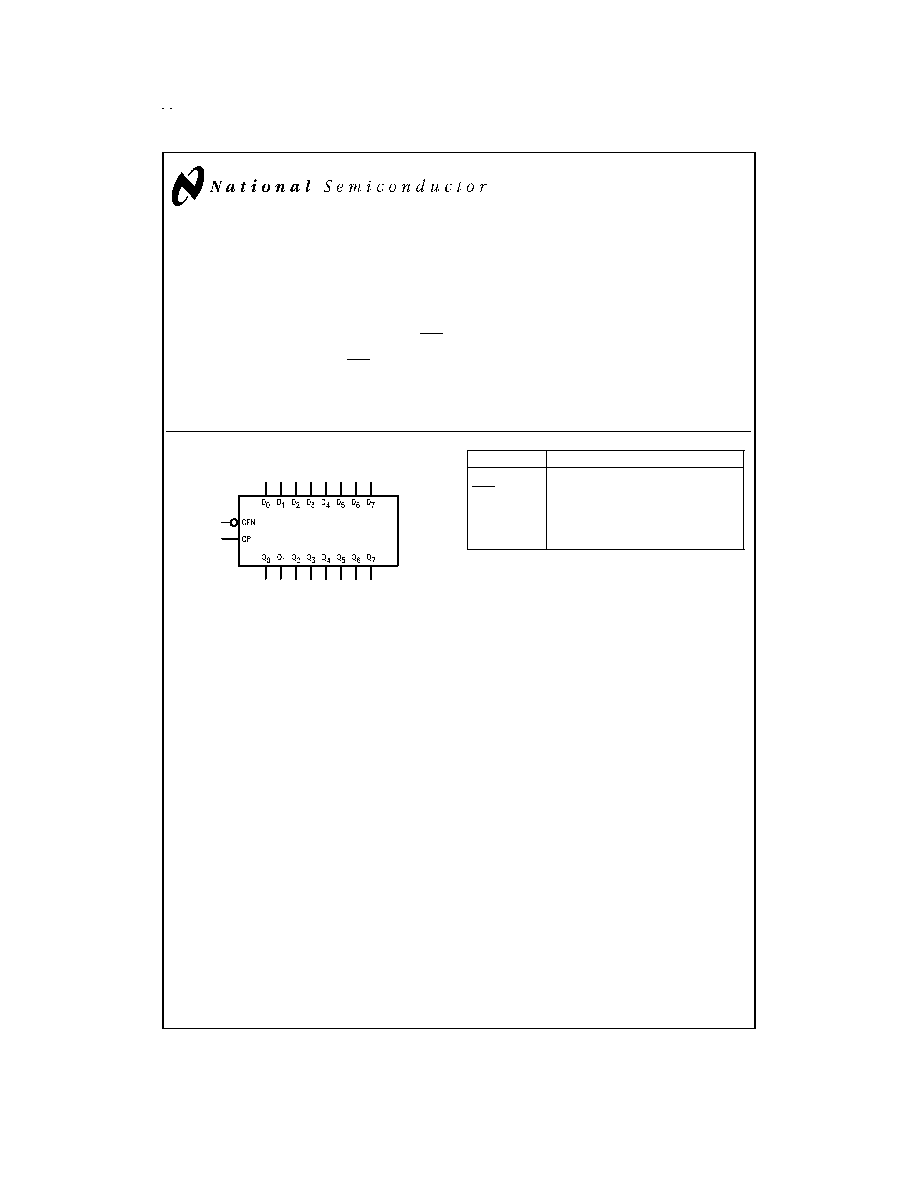

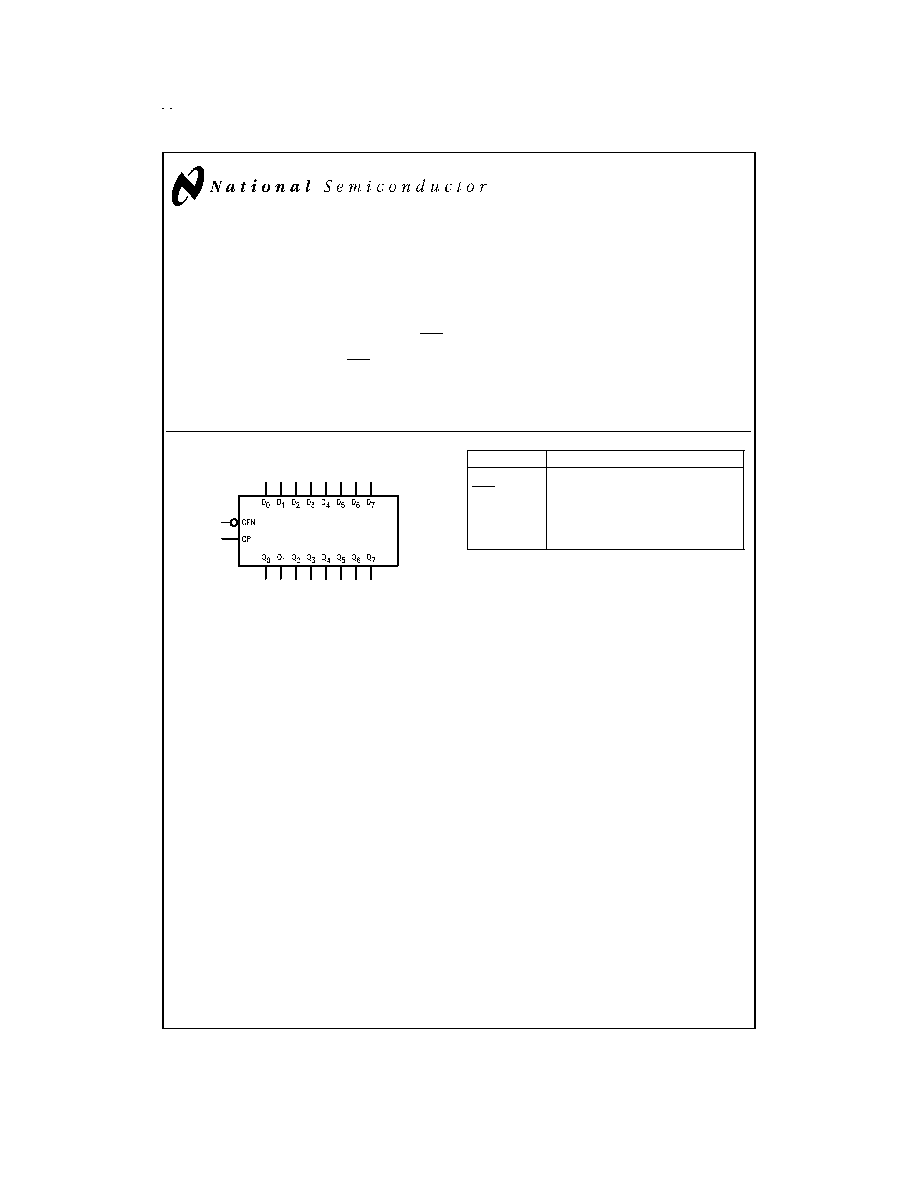

Logic Symbol

Pin Names

Description

D

0

≠D

7

Data Inputs

CEN

Clock Enable Input

CP

Clock Input (Active Rising Edge)

Q

0

≠Q

7

Data Outputs

NC

No Connect

DS100316-4

August 1998

100353

Low

Power

8-Bit

Register

© 1998 National Semiconductor Corporation

DS100316

www.national.com

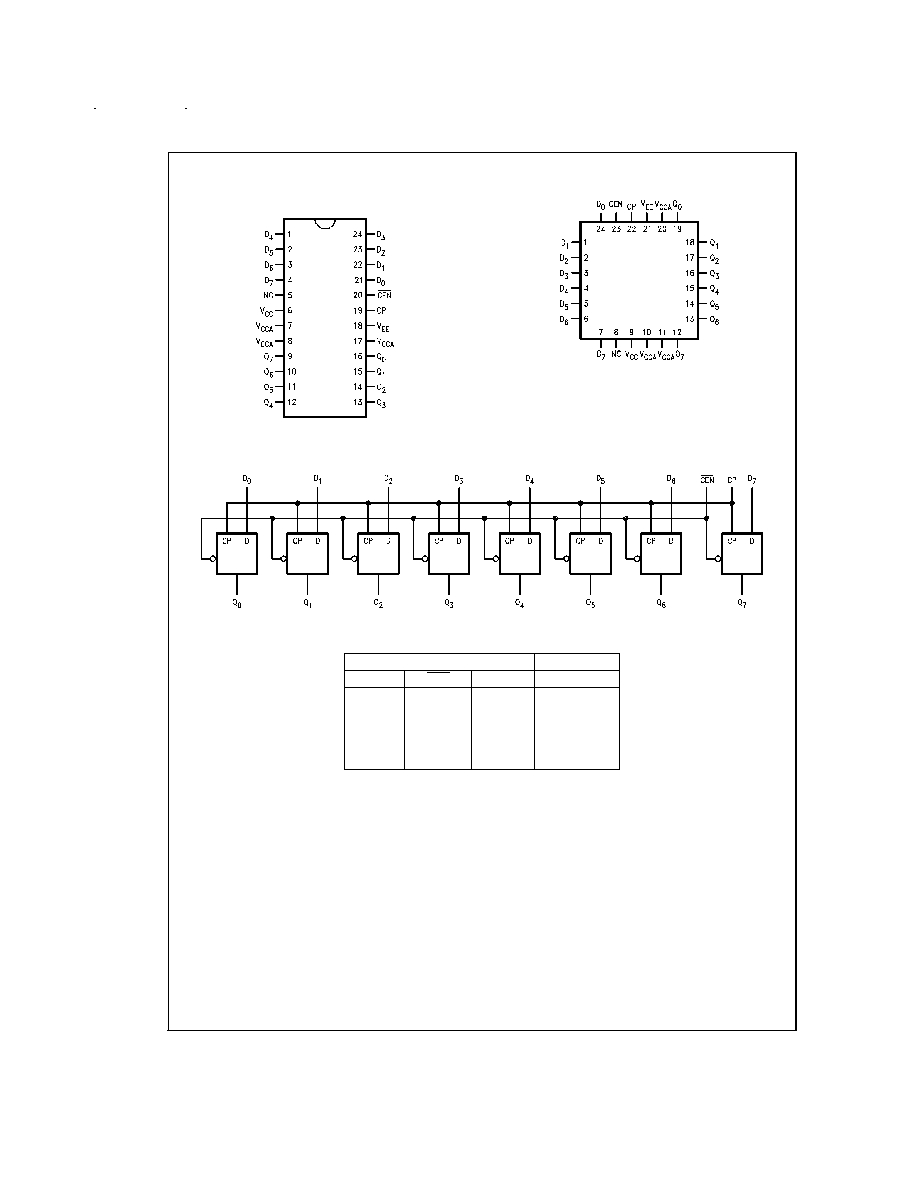

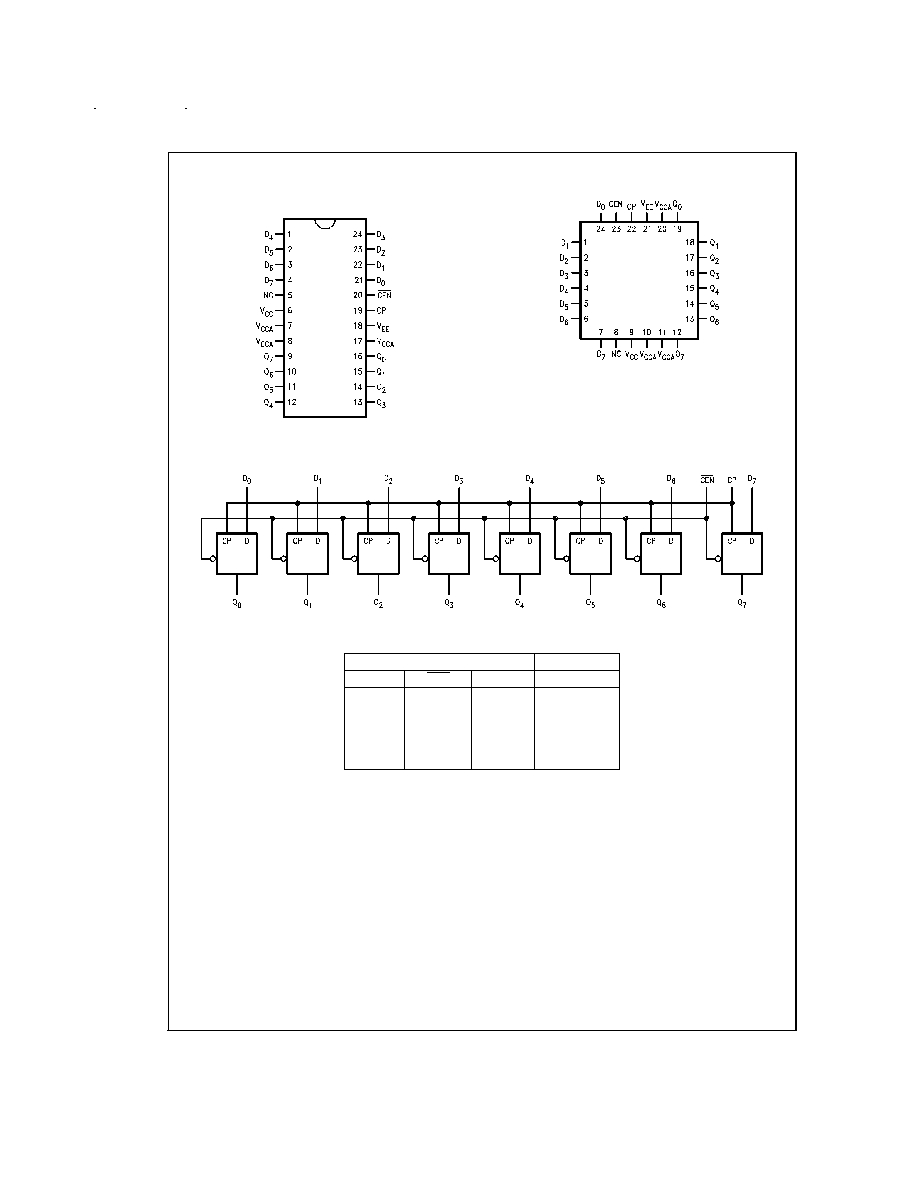

Connection Diagrams

Logic Diagram

Truth Table

Inputs

Outputs

D

n

CEN

CP

Q

n

L

L

N

L

H

L

N

H

X

X

L

NC

X

X

H

NC

X

H

X

NC

H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

NC = No Change

N

= LOW to HIGH Transition

24-Pin DIP

DS100316-1

24-Pin Quad Cerpak

DS100316-2

DS100316-5

www.national.com

2

Absolute Maximum Ratings

(Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Above which the useful life may be impared

Storage Temperature (T

STG

)

-65∞C to +150∞C

Maximum Junction Temperature (T

J

)

Ceramic

+175∞C

V

EE

Pin Potential to Ground Pin

-7.0V to +0.5V

Input Voltage (DC)

V

EE

to + 0.5V

Output Current (DC Output HIGH)

-50 mA

ESD (Note 2)

2000V

Recommended Operating

Conditions

Case Temperature (T

C

)

Military

-55∞C to +125∞C

Supply Voltage (V

EE

)

-5.7V to -4.2V

Note 1: Absolute maximum ratings are those values beyond which the de-

vice may be damaged or have its useful life impaired. Functional operation

under these conditions is not implied.

Note 2: ESD testing conforms to MIL-STD-883, Method 3015.

Military Version

DC Electrical Characteristics

V

EE

= -4.2V to -5.7V, V

CC

= V

CCA

= GND, T

C

= -55∞C to +125∞C

Symbol

Parameter

Min

Max

Units

T

C

Conditions

Notes

V

OH

Output HIGH Voltage

-1025

-870

mV

0∞C to

+125∞C

-1085

-870

mV

-55∞C

V

IN

= V

IH

(Max)

Loading with

(Notes 3, 4, 5)

V

OL

Output LOW Voltage

-1830 -1620

mV

0∞C to

or V

IL

(Min)

50

to -2.0V

+125∞C

-1830 -1555

mV

-55∞C

V

OHC

Output HIGH Voltage

-1035

mV

0∞C to

+125∞C

-1085

mV

-55∞C

V

IN

= V

IH

(Min)

Loading with

(Notes 3, 4, 5)

V

OLC

Output LOW Voltage

-1610

mV

0∞C to

or V

IL

(Max)

50

to -2.0V

+125∞C

-1555

mV

-55∞C

V

IH

Input HIGH Voltage

-1165

-870

mV

-55∞C to

Guaranteed HIGH Signal for all Inputs

(Notes 3, 4, 5, 6)

+125∞C

V

IL

Input LOW Voltage

-1830 -1475

mV

-55∞C to

Guaranteed LOW Signal for all Inputs

(Notes 3, 4, 5, 6)

+125∞C

I

IL

Input LOW Current

0.50

µA

-55∞C to

V

EE

= -4.2V

(Notes 3, 4, 5)

+125∞C

V

IN

= V

IL

(Min)

I

IH

Input HIGH Current

240

µA

0∞C to

V

EE

= -5.7V

V

IN

= V

IH

(Max)

(Notes 3, 4, 5)

+125∞C

340

µA

-55∞C

I

EE

Power Supply Current

-55∞C to

Inputs Open

-132

-42

mA

+125∞C

V

EE

= -4.2V to -5.7V

(Notes 3, 4, 5)

Note 3: F100K 300 Series cold temperature testing is performed by temperature soaking (to guarantee junction temperature equals -55∞C), then testing immediately

without allowing for the junction temperature to stabilize due to heat dissipation after power-up. This provides "cold start" specs which can be considered a worst case

condition at cold temperatures.

Note 4: Screen tested 100% on each device at -55∞C, +25∞C, and +125∞C, Subgroups 1, 2, 3, 7, and 8.

Note 5: Sample tested (Method 5005, Table I) on each manufactured lot at -55∞C, +25∞C, and +125∞C, Subgroups A1, 2, 3, 7, and 8.

Note 6: Guaranteed by applying specified input condition and testing V

OH

/V

OL

.

AC Electrical Characteristics

V

EE

= -4.2V to -5.7V, V

CC

= V

CCA

= GND

Symbol

Parameter

T

C

= -55∞C

T

C

= +25∞C

T

C

= +125∞C

Units

Conditions

Notes

Min

Max

Min

Max

Min

Max

f

max

Toggle Frequency

400

400

400

MHz

Figures 1, 2

(Note 10)

www.national.com

3

AC Electrical Characteristics

(Continued)

V

EE

= -4.2V to -5.7V, V

CC

= V

CCA

= GND

Symbol

Parameter

T

C

= -55∞C

T

C

= +25∞C

T

C

= +125∞C

Units

Conditions

Notes

Min

Max

Min

Max

Min

Max

t

PLH

Propagation Delay

0.70

3.30

0.80

3.10

0.80

3.50

ns

(Notes 7, 8,

9, 11)

t

PHL

CP to Output

Figures 1, 2

t

TLH

Transition Time

0.40

2.20

0.40

2.20

0.40

2.20

ns

(Note 10)

t

THL

20% to 80%, 80% to 20%

t

s

Setup Time

D

n

0.30

0.30

0.30

CEN (Disable Time)

0.60

0.60

0.60

ns

Figures 1, 3

(Note 10)

CEN (Release Time)

1.40

1.40

1.40

t

h

Hold Time

D

n

1.50

1.50

1.50

ns

Figures 1, 4

(Note 10)

t

pw

(H)

Pulse Width HIGH

CP

2.00

2.00

2.00

ns

Figures 1, 2

(Note 10)

Note 7: F100K 300 Series cold temperature testing is performed by temperature soaking (to guarantee junction temperature equals -55∞C), then testing immediately

after power-up. This provides "cold start" specs which can be considered a worst case condition at cold temperatures.

Note 8: Screen tested 100% on each device at +25∞C temperature only, Subgroup A9.

Note 9: Sample tested (Method 5005, Table I) on each manufactured lot at +25∞C, Subgroup A9, and at +125∞C and -55∞C, temperatures, Subgroups A10 and A11.

Note 10: Not tested at +25∞C, +125∞C, and -55∞C temperature (design characterization data).

Note 11: The propagation delay specified is for single output switching. Delays may vary up to 300 ps with multiple outputs switching.

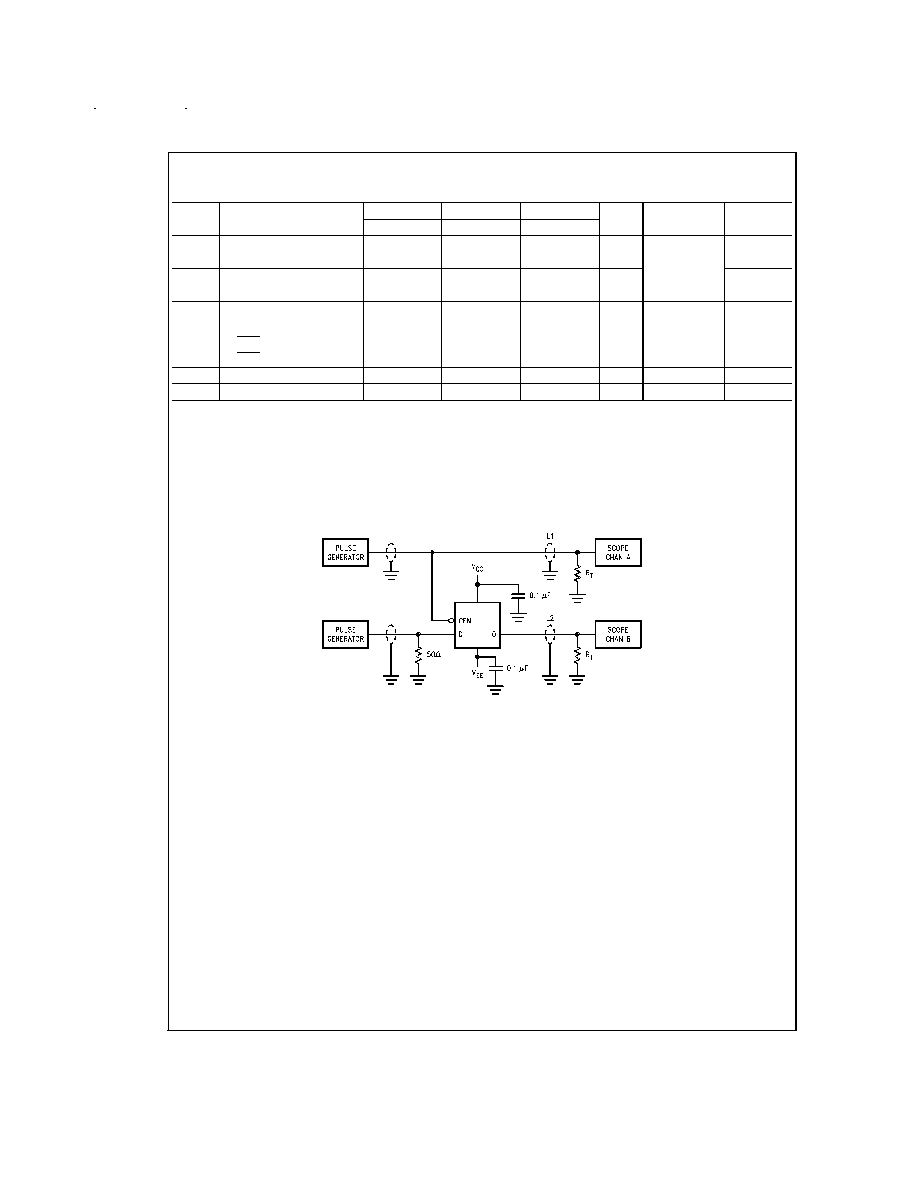

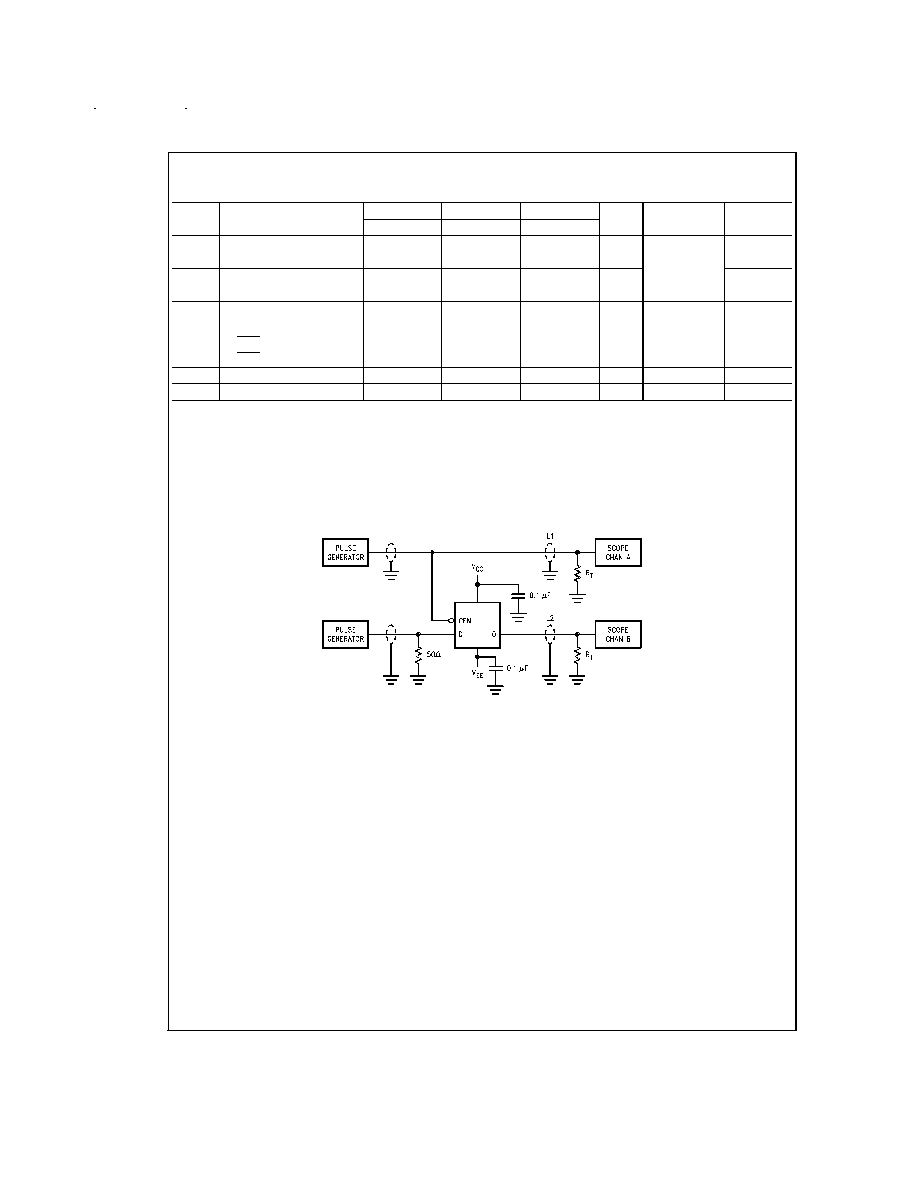

Test Circuitry

DS100316-6

Notes:

V

CC

, V

CCA

= +2V, V

EE

= -2.5V

L1 and L2 = equal length 50

impedance linesR

T

= 50

terminator internal to scopeDecoupling 0.1 µF from GND to V

CC

and V

EE

All unused outputs are

loaded with 50

to GNDC

L

= Fixture and stray capacitance

3 pF

FIGURE 1. AC, Toggle Frequency Test Circuit

www.national.com

4

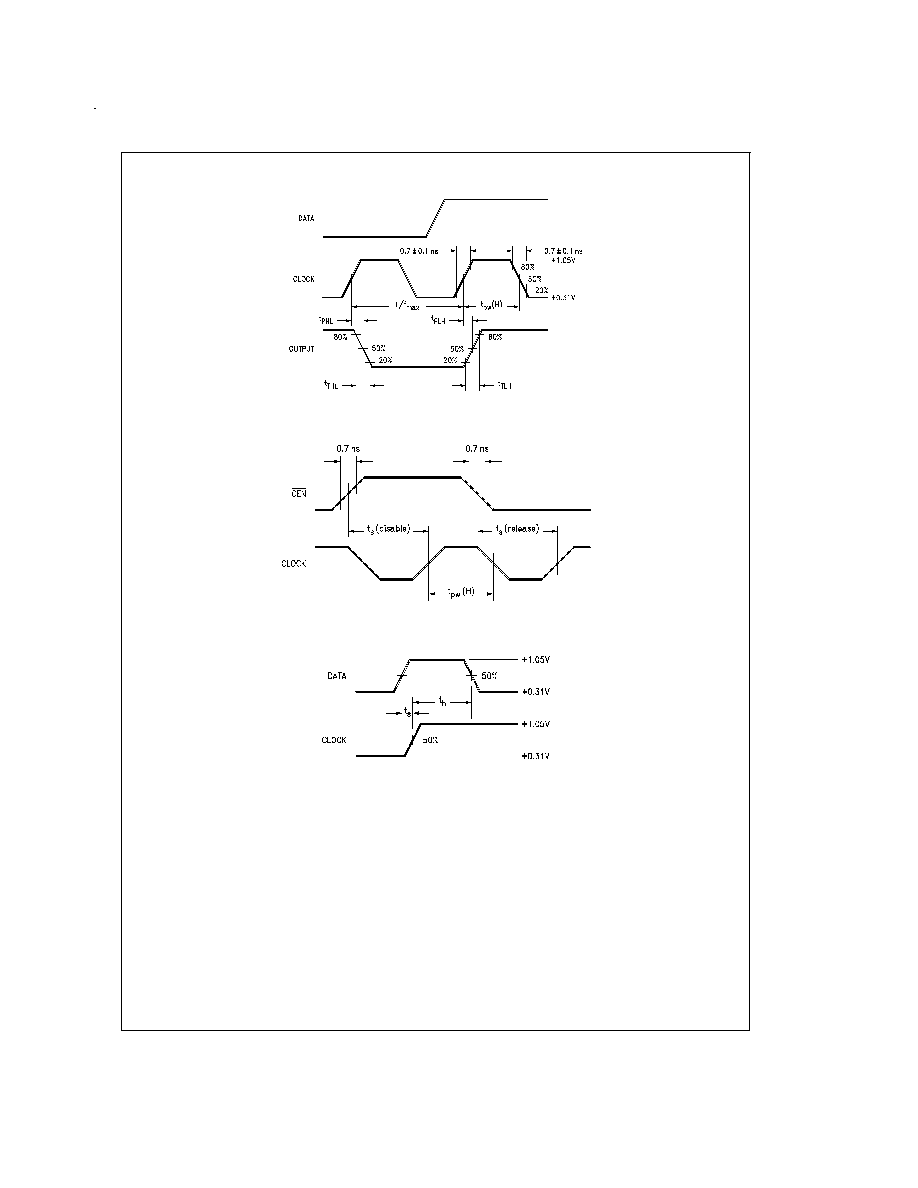

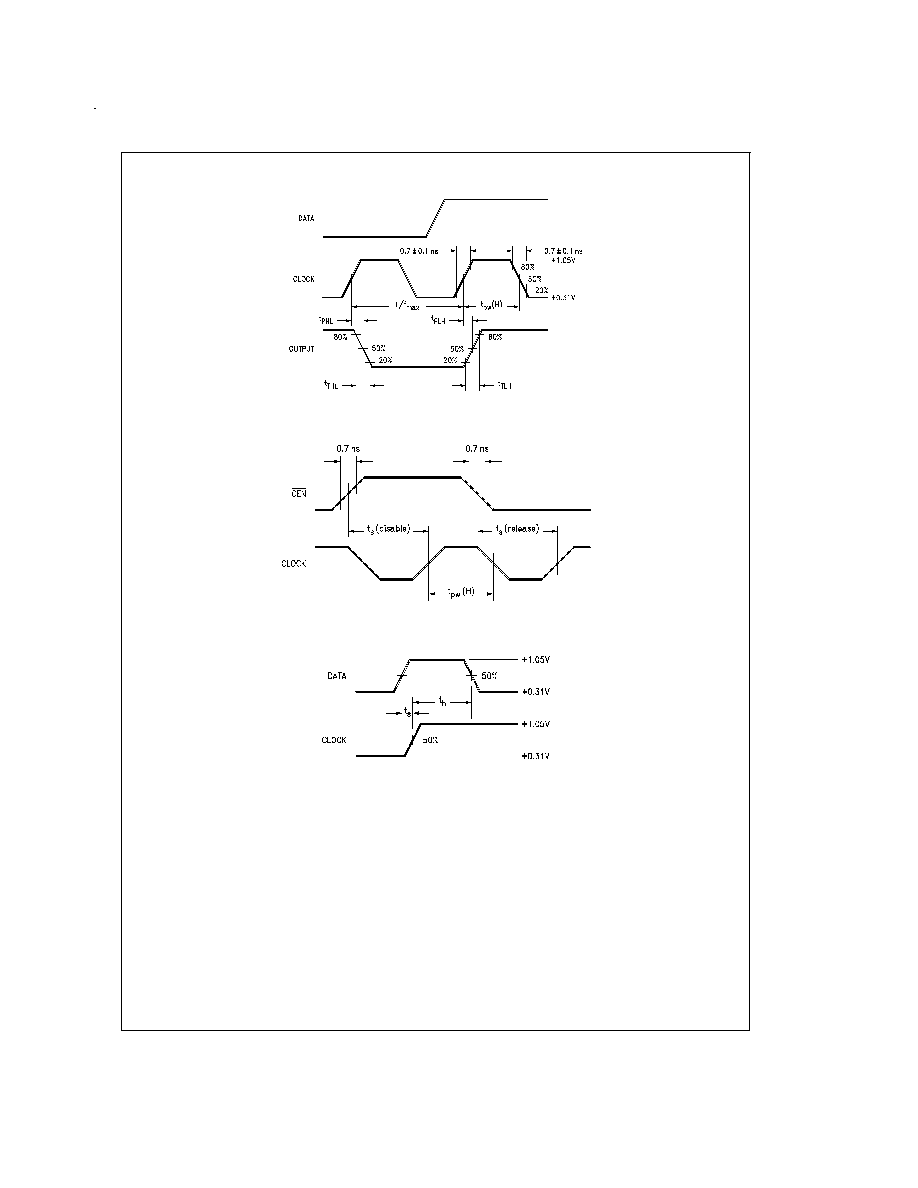

Switching Waveforms

DS100316-8

FIGURE 2. Propagation Delay (Clock) and Transition Times

DS100316-9

FIGURE 3. Setup and Pulse Width Times

DS100316-10

Note 12: t

s

is the minimum time before the transition of the clock that information must be present at the data input.

Note 13: t

h

is the minimum time after the transition of the clock that information must remain unchanged at the data input.

FIGURE 4. Data Setup and Hold Time

www.national.com

5