ADC1175-50

8-Bit, 50 MSPS, 125 mW A/D Converter

General Description

The ADC1175-50 is a low power, 50 MSPS analog-to-digital

converter that digitizes signals to 8 bits while consuming just

125 mW (typ). The ADC1175-50 uses a unique architecture

that achieves 6.8 Effective Bits at 25 MHz input and 50 MHz

clock frequency. Output formatting is straight binary coding.

The excellent DC and AC characteristics of this device,

together with its low power consumption and +5V single

supply operation, make it ideally suited for many video and

imaging applications, including use in portable equipment.

Furthermore, the ADC1175-50 is resistant to latch-up and

the outputs are short-circuit proof. The top and bottom of the

ADC1175-50's reference ladder is available for connections,

enabling a wide range of input possibilities. The low input

capacitance (7 pF, typical) makes this device easier to drive

than conventional flash converters and the power down

mode reduces power consumption to less than 5 mW.

The ADC1175-50 is offered in SOIC (EIAJ), TSSOP and LLP

(a molded lead frame-based chip-scale package.) It is de-

signed to operate over the commercial temperature range of

-20∞C to +75∞C.

Features

n

Internal Track-and-Hold function

n

Single +5V operation

n

Internal reference bias resistors

n

Industry standard pinout

n

Power-down mode (

<

5 mW)

Key Specifications

n

Resolution

8 Bits

n

Maximum Sampling Frequency

50 MSPS (min)

n

THD

54 dB (typ)

n

DNL

0.7 LSB (typ)

n

ENOB

@

f

IN

= 25 MHz

6.8 Bits (typ)

n

Guaranteed No Missing Codes

n

Differential Phase

0.5∞ (typ)

n

Differential Gain

1.0% (typ)

n

Power Consumption

125 mW (typ), 190 mW (max)

(Excluding Reference Current)

Applications

n

Digital Still Cameras

n

CCD Imaging

n

Electro-Optics

n

Medical Imaging

n

Communications

n

Video Digitization

n

Digital Television

n

Multimedia

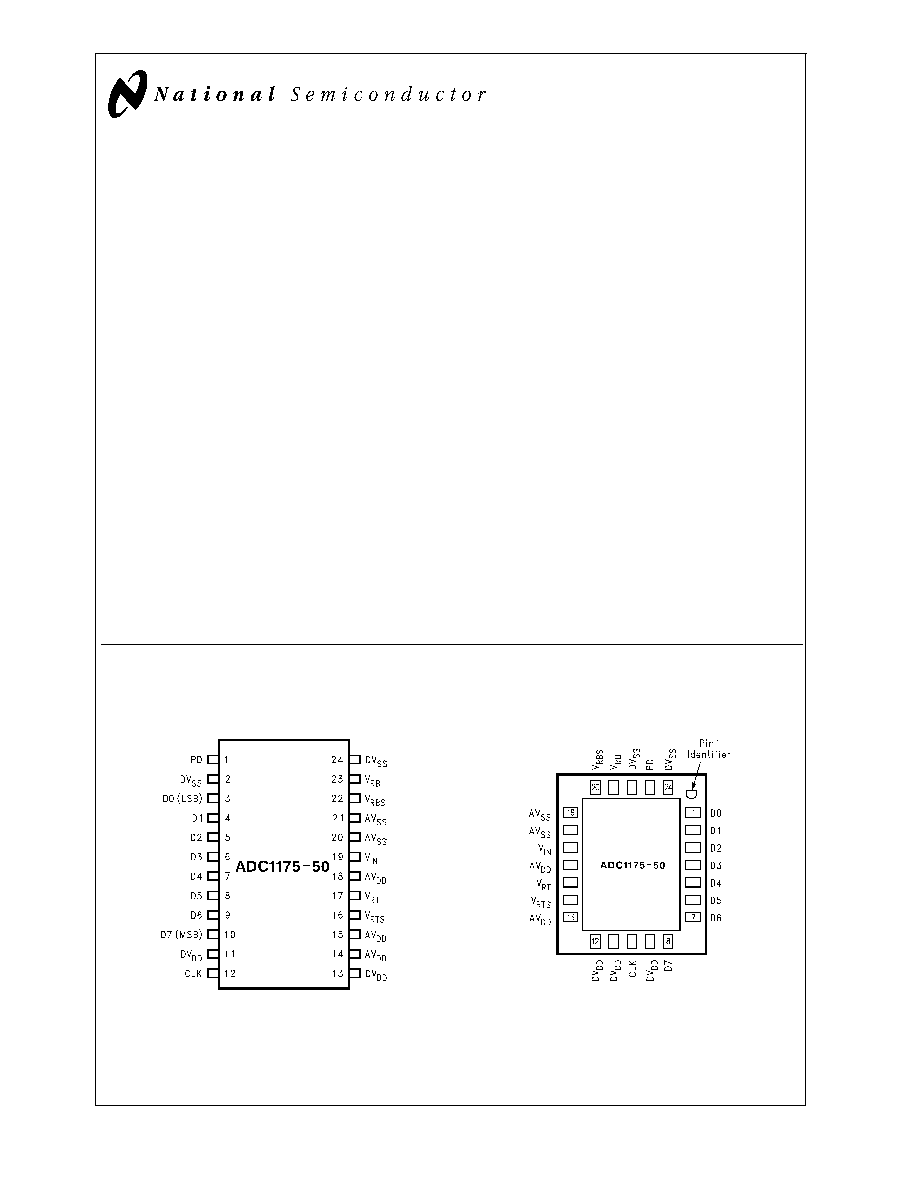

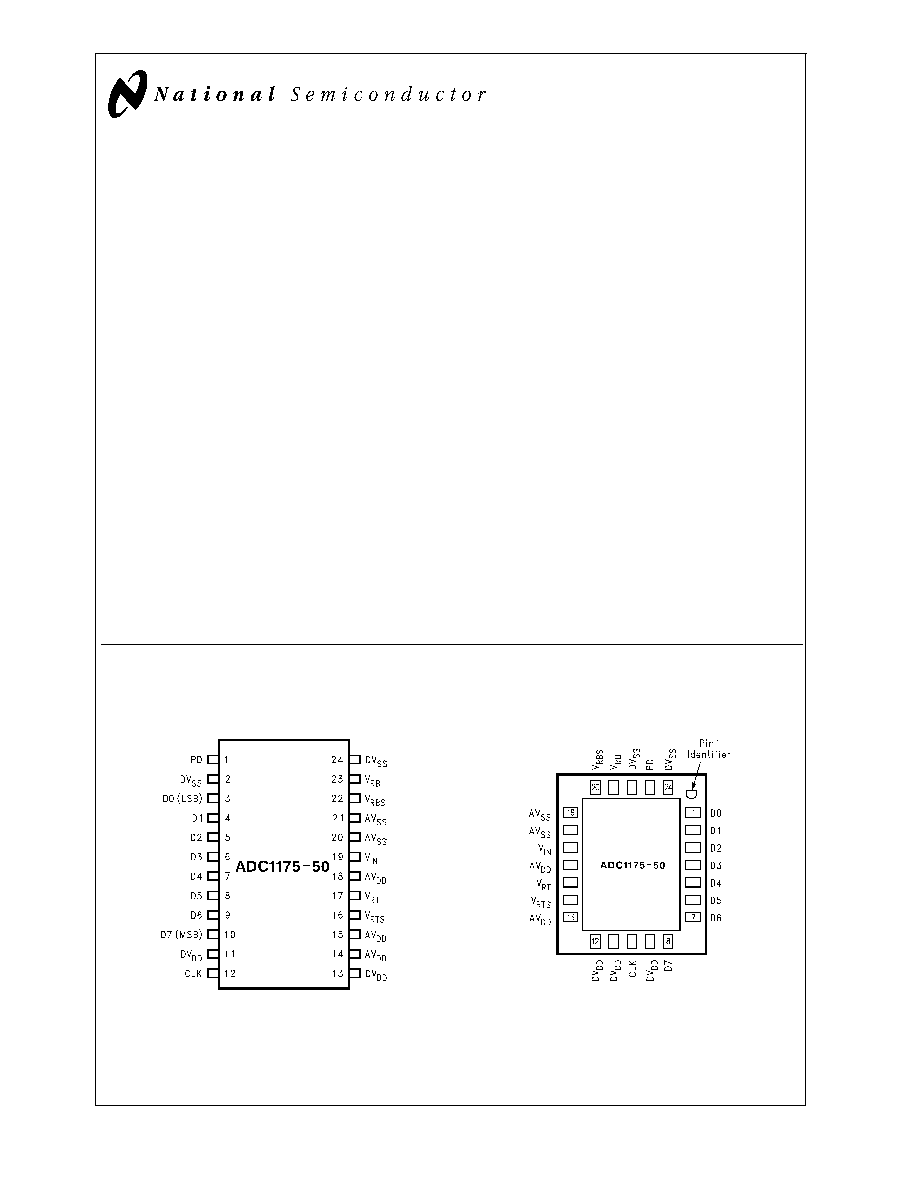

Connection Diagram

24-pin SOLC and TSSOP

DS100896-1

Top View

24-pin LLP (CSP)

DS100896-34

Bottom View

December 2000

ADC1

175-50

8-Bit,

50

MSPS,

125

mW

A/D

Converter

© 2001 National Semiconductor Corporation

DS100896

www.national.com

Ordering Information

ADC1175-50CIJM

SOIC (EIAJ)

ADC1175-50CIJMX

SOIC (EIAJ) (tape and reel)

ADC1175-50CIMT

TSSOP

ADC1175-50CIMTX

TSSOP (tape and reel)

ADC1175-50CILQ

LLP (tape and reel - 1, 000 units)

ADC1175-50CILQX

LLP (tape and reel - 4, 500 units)

Block Diagram

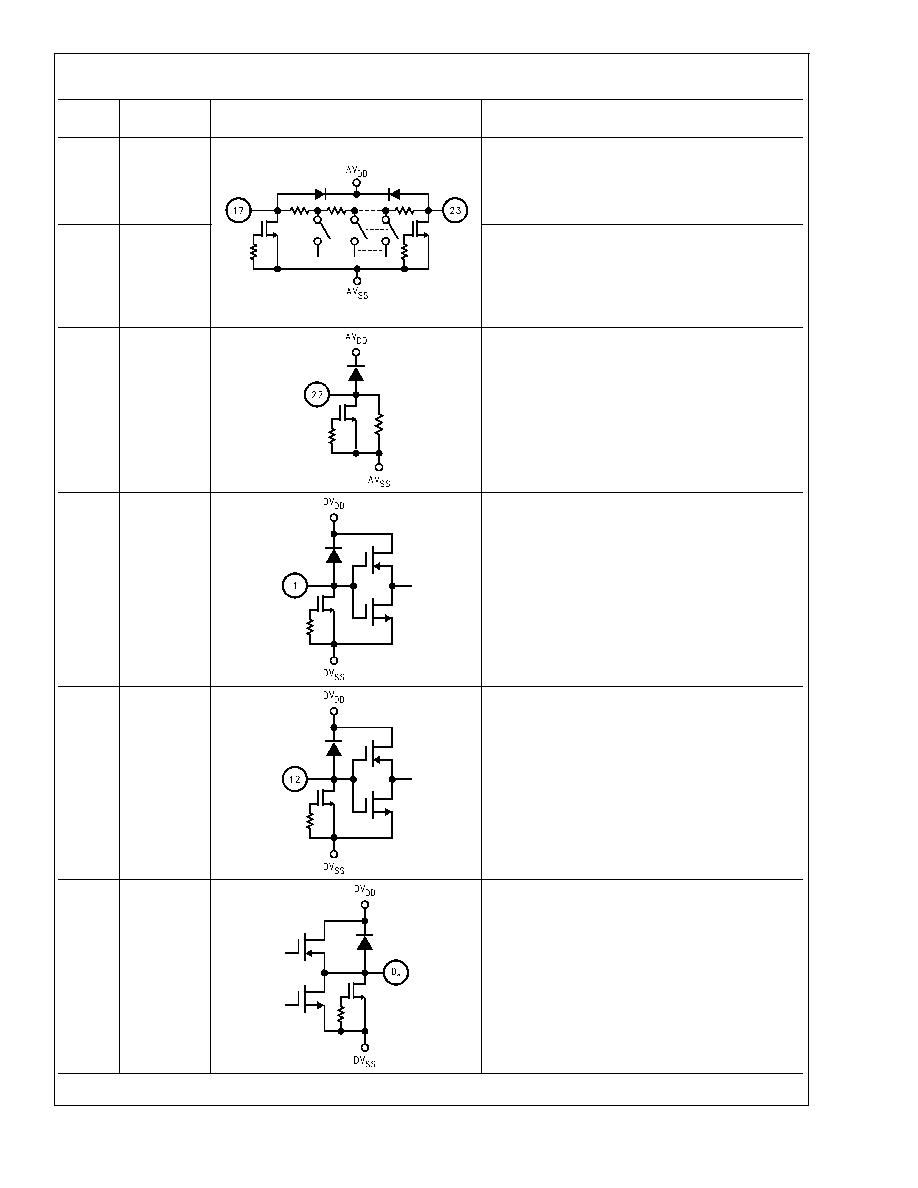

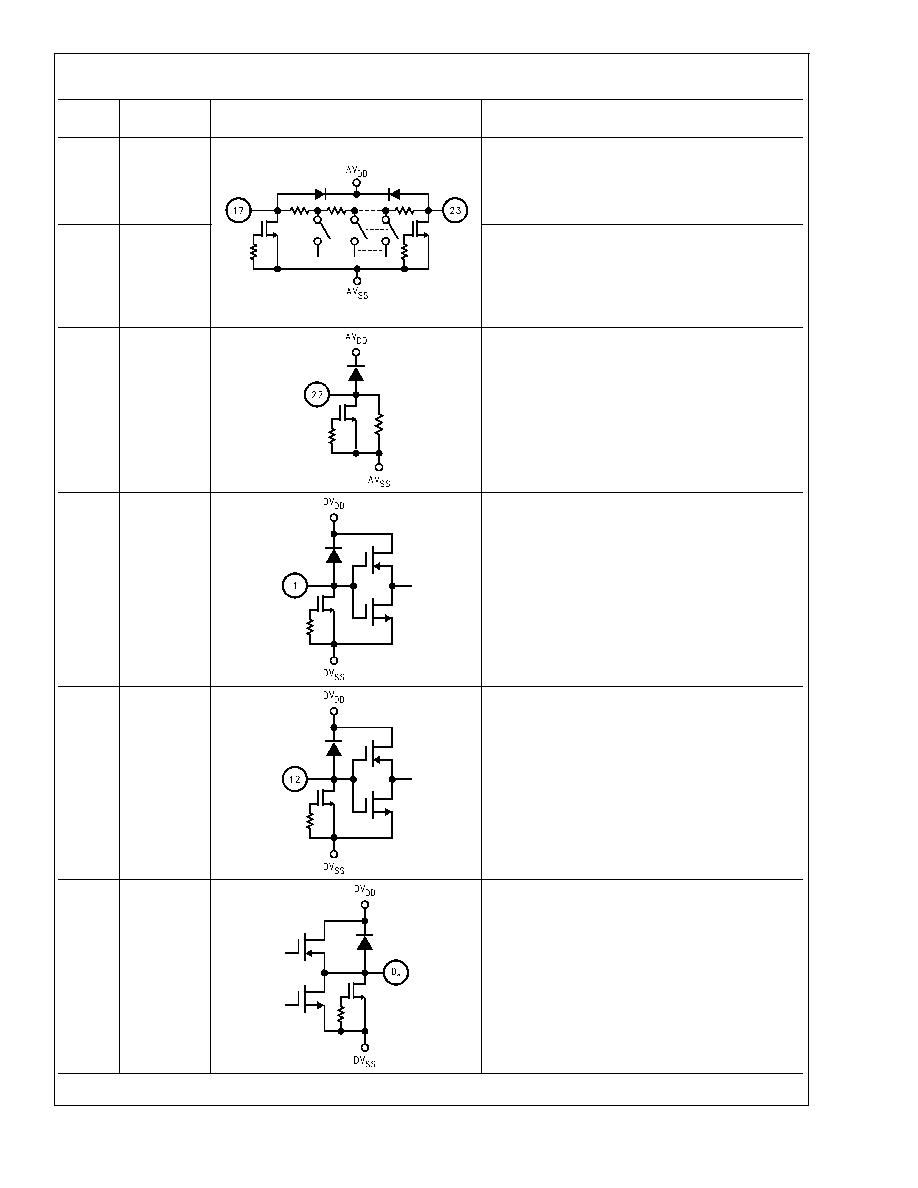

Pin Descriptions and Equivalent Circuits

(LLP pins in parentheses)

Pin

No.

Symbol

Equivalent Circuit

Description

19

(17)

V

IN

Analog signal input. Conversion range is V

RT

to

V

RB

.

16

(14)

V

RTS

Reference Top Bias with internal pull up resistor.

Short this pin to V

RT

to self-bias the reference

ladder.

DS100896-2

ADC1

175-50

www.national.com

2

Pin Descriptions and Equivalent Circuits

(LLP pins in parentheses) (Continued)

Pin

No.

Symbol

Equivalent Circuit

Description

17

(15)

V

RT

Analog input that is the high (top) side of the

reference ladder of the ADC. Nominal range is 1.0V

to AV

DD

, optimized value of 2.6V. Voltages on V

RT

and V

RB

inputs define the V

IN

conversion range.

Bypass well. See Section 2.0 for more information.

23

(21)

V

RB

Analog input that is the low (bottom) side of the

reference ladder of the ADC. Nominal range is 0.0V

to 4.0V, with optimized value of 0.6V. Voltage on

V

RT

and V

RB

inputs define the V

IN

conversion

range. Bypass well. See Section 2.0 for more

information.

22

(20)

V

RBS

Reference Bottom Bias with internal pull down

resistor. Short to V

RB

to self-bias the reference

ladder. Bypass well if not grounded. See Section

2.0 for more information.

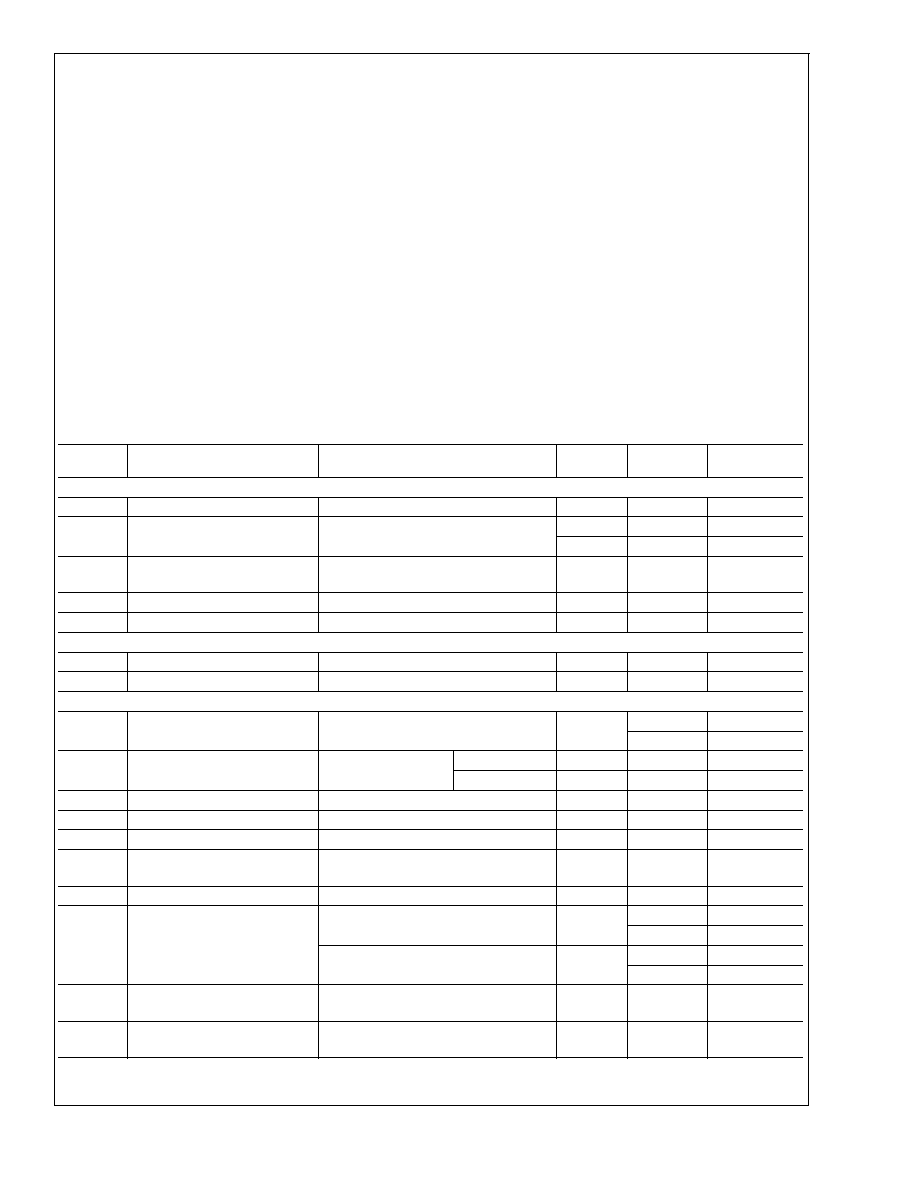

1

(23)

PD

CMOS/TTL compatible Digital input that, when high,

puts the ADC1175-50 into a power-down mode

where total power consumption is typically less than

5 mW. With this pin low, the device is in the normal

operating mode.

12

(10)

CLK

CMOS/TTL compatible digital clock input. V

IN

is

sampled on the falling edge of CLK input.

3 thru

10

(1 thru

8)

D0≠D7

Conversion data digital Output pins. D0 is the LSB,

D7 is the MSB. Valid data is output just after the

rising edge of the CLK input. These pins are in a

high impedance mode when the PD pin is low.

ADC1

175-50

www.national.com

3

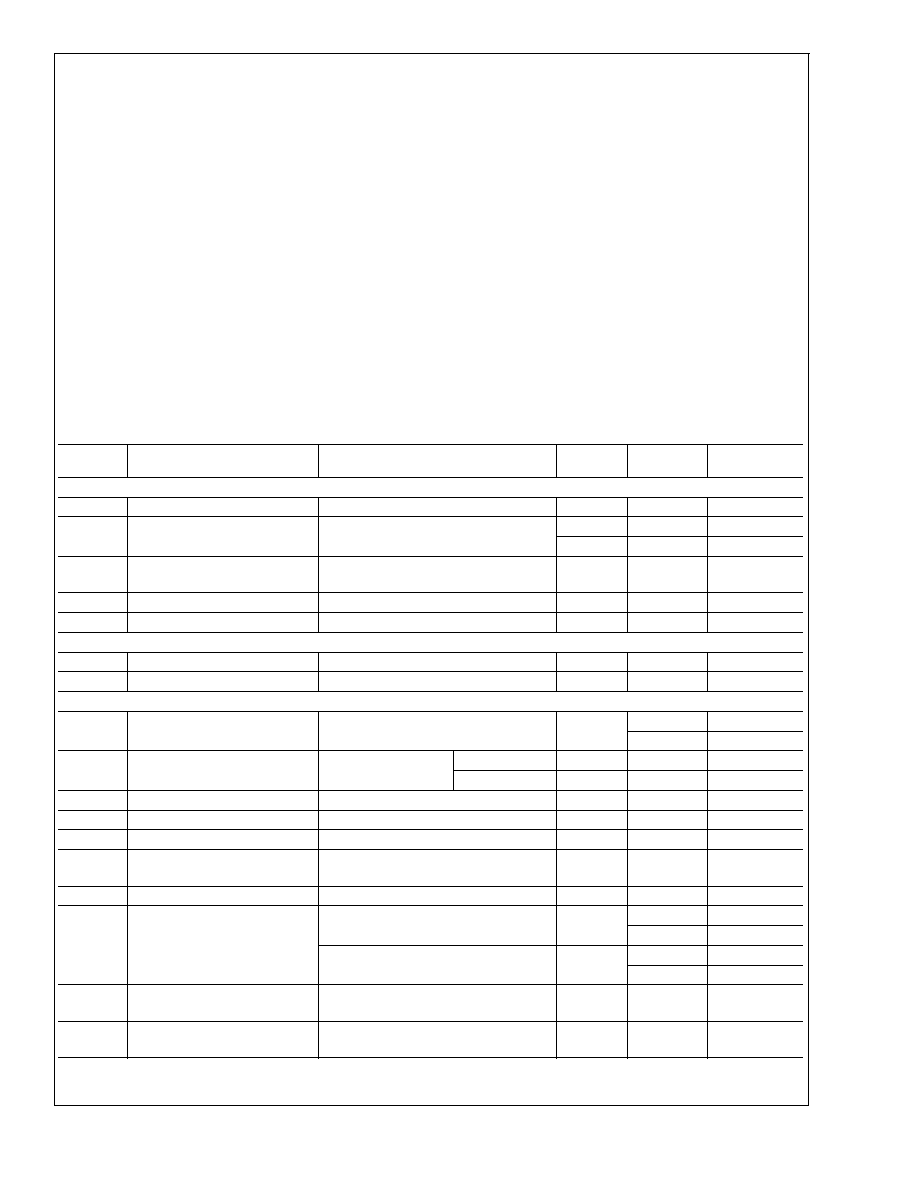

Pin Descriptions and Equivalent Circuits

(LLP pins in parentheses) (Continued)

Pin

No.

Symbol

Equivalent Circuit

Description

11,

13, 14

(9, 11,

12)

DV

DD

Positive digital supply pin. Connect to a clean, quiet

voltage source of +5V. AV

DD

and DV

DD

should have

a common source and be separately bypassed with

a 10 µF capacitor and a 0.1 µF ceramic chip

capacitor. See Section 4.0 for more information.

2, 24

(22,

24)

DV

SS

The ground return for the digital supply. AV

SS

and

DV

SS

should be connected together close to the

ADC1175-50.

15, 18

(13,

16)

AV

DD

Positive analog supply pin. Connect to a clean,

quiet voltage source of +5V. AV

DD

and DV

DD

should

have a common source and be separately bypassed

with a 10 µF capacitor and a 0.1 µF ceramic chip

capacitor. See Section 4.0 for more information.

20, 21

(18,

19)

AV

SS

The ground return for the analog supply. AV

SS

and

DV

SS

should be connected together close to the

ADC1175-50 package.

ADC1

175-50

www.national.com

4

Absolute Maximum Ratings

(Notes 1, 2)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage (AV

DD

, DV

DD

)

6.5V

Voltage on Any Input or Output Pin

-0.3V to +6.5V

Reference Voltage (V

RT

, V

RB

)

AV

DD

to V

SS

CLK, PD Voltage Range

-0.5 to (AV

DD

+0.5V)

Digital Output Voltage (V

OH

, V

OL

)

V

DD

to V

SS

Input Current at Any Pin (Note 3)

±

25 mA

Package Input Current (Note 3)

±

50 mA

Power Dissipation at T

A

= 25∞C

See (Note 4)

ESD Susceptibility (Note 5)

Human Body Model

2000V

Machine Model

250V

Soldering Temperature, Infrared,

(10 sec.) (Note 6)

235∞C

Storage Temperature

-65∞C to +150∞C

Short Circuit Duration

(Single High Output to Ground)

1 Second

Operating Ratings

(Notes 1, 2)

Operating Temperature Range

-20∞C

T

A

+75∞C

Supply Voltage (AV

DD

, DV

DD

)

+4.75V to +5.25V

AV

DD

- DV

DD

<

0.5V

Ground Difference |DV

SS

≠AV

SS

|

0V to 100 mV

Upper Reference Voltage (V

RT

)

1.0V to V

DD

Lower Reference Voltage (V

RB

)

0V to 4.0V

V

IN

Voltage Range

V

RB

to V

RT

Converter Electrical Characteristics

The following specifications apply for AV

DD

= DV

DD

= +5.0 V

DC

, PD = 0V, V

RT

= +2.6V, V

RB

= 0.6V, C

L

= 20 pF, f

CLK

=

50 MHz at 50% duty cycle. Boldface limits apply for T

A

= T

MIN

to T

MAX

; all other limits T

A

= 25∞C (Notes 7, 8).

Symbol

Parameter

Conditions

Typical

(Note 9)

Limits

(Note 9)

Units

(Limits)

DC ACCURACY

INL

Integral Non Linearity Error

V

IN

= 0.6V to 2.6V

±

0.8

±

1.95

LSB (max)

DNL

Differential Non-Linearity

V

IN

= 0.6V to 2.6V

+0.7

+1.75

LSB (max)

-0.7

-1.0

LSB (min)

Resolution for No Missing

Codes

8

Bits

E

OT

Top Offset Voltage

-12

mV

E

OB

Bottom Offset Voltage

+10

mV

VIDEO ACCURACY

DP

Differential Phase Error

f

IN

= 4.43 MHz Modulated Ramp

0.5

deg

DG

Differential Gain Error

f

IN

= 4.43 MHz Modulated Ramp

1.0

%

ANALOG INPUT AND REFERENCE CHARACTERISTICS

V

IN

Input Range

2.0

V

RB

V (min)

V

RT

V (max)

C

IN

V

IN

Input Capacitance

V

IN

= 1.5V

+0.7 Vrms

(CLK LOW)

4

pF

(CLK HIGH)

7

pF

R

IN

R

IN

Input Resistance

>

1

M

BW

Full Power Bandwidth

120

MHz

R

RT

Top Reference Resistor

320

R

REF

Reference Ladder Resistance

V

RT

to V

RB

270

200

350

(min)

(max)

R

RB

Bottom Reference Resistor

80

I

REF

Reference Ladder Current

V

RT

= V

RTS

, V

RB

= V

RBS

7

5.4

mA (min)

10.8

mA (max)

V

RT

= V

RTS

, V

RB

= AV

SS

8

6.1

mA (min)

12.3

mA (max)

V

RT

Reference Top Self Bias

Voltage

V

RT

Connected to V

RTS

, V

RB

Connected to V

RBS

2.6

V (min)

V (max)

V

RB

Reference Bottom Self Bias

Voltage

V

RT

Connected to V

RTS

, V

RB

Connected to V

RBS

0.6

0.55

0.70

V (min)

V (max)

ADC1

175-50

www.national.com

5