| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: ADC78H89 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

2003

4

1

© National Semiconductor Corporation

DS200616-01-JP

ADC78

H

89

7

5

00kSPS

12

A/

D

A

D

C

78H

89

20

030

40

1

M

o

d

i

f

i

ed

t

o

78

H

8

9 s

p

e

c

s

N

e

w

D

a

t

a

sh

ee

t

for

W

a

r

r

en

C

r

a

ddo

ck,

co

py a

nd re

na

m

e

from

ds20

057

7.

C

N

d

s

20

06

16

2

0

0

2

11

11

2

002

09

19

A

D

C

78H

89

7

500

kS

PS

12

A/D

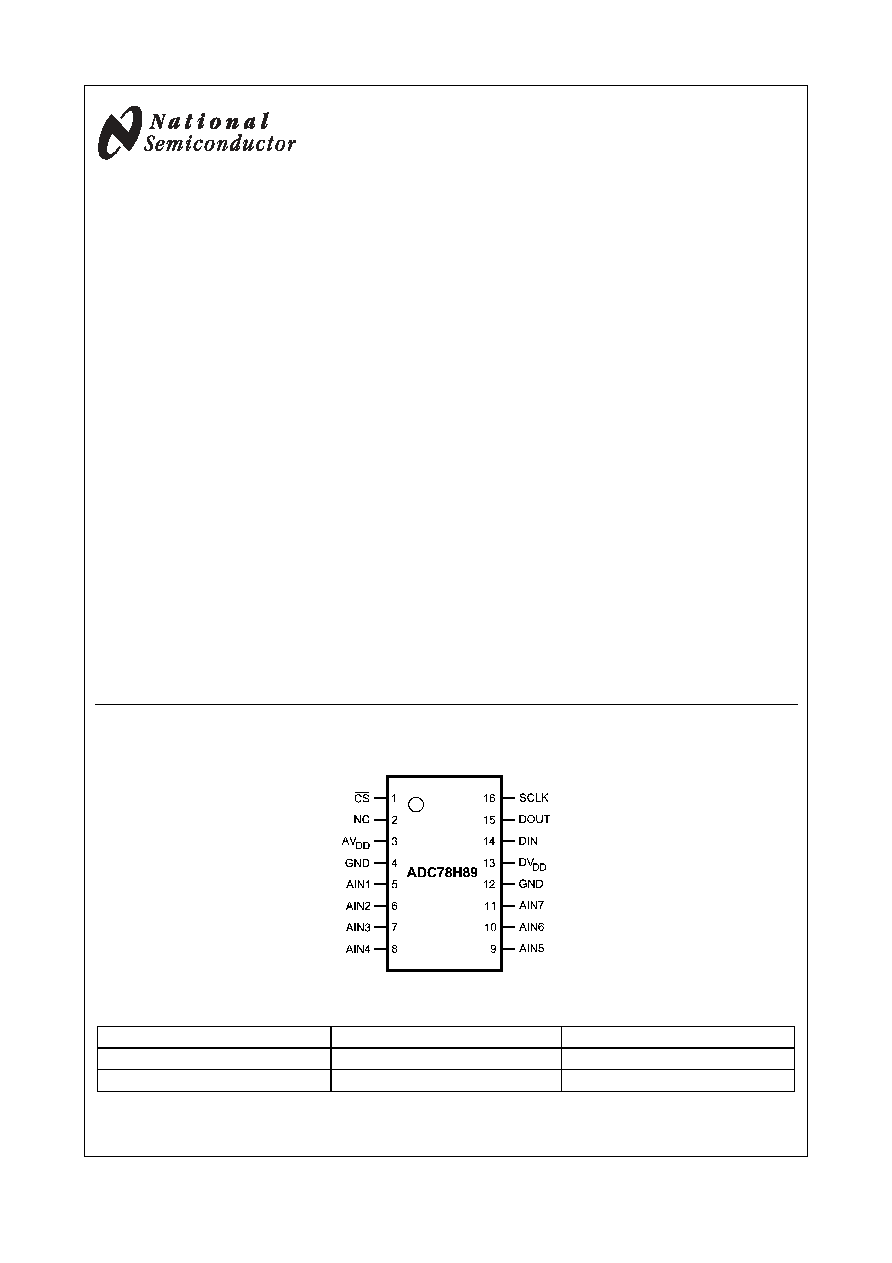

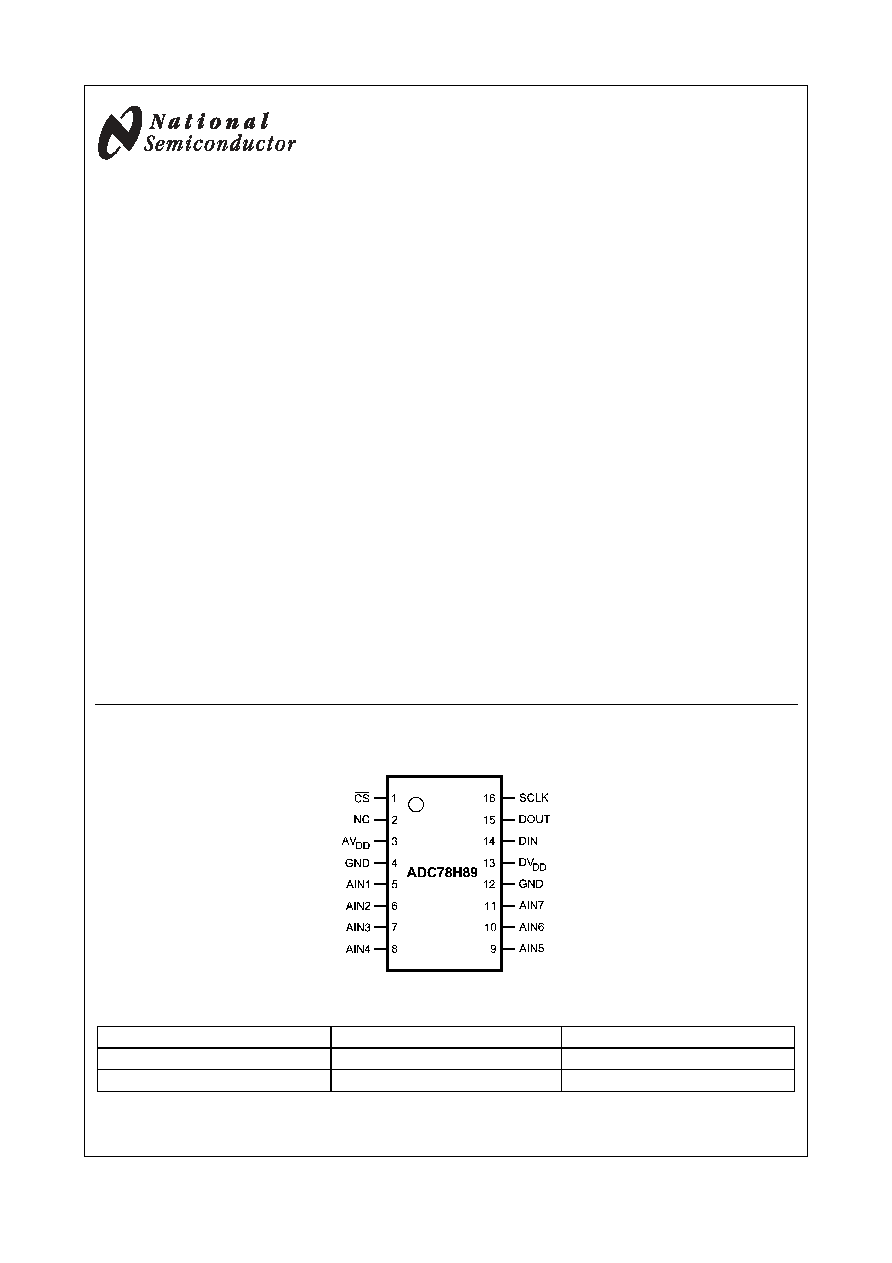

ADC78H89

7

500kSPS

12

A/D

TRI-STATE

Æ

MICROWIRETM

QSPITM SPITM ( )

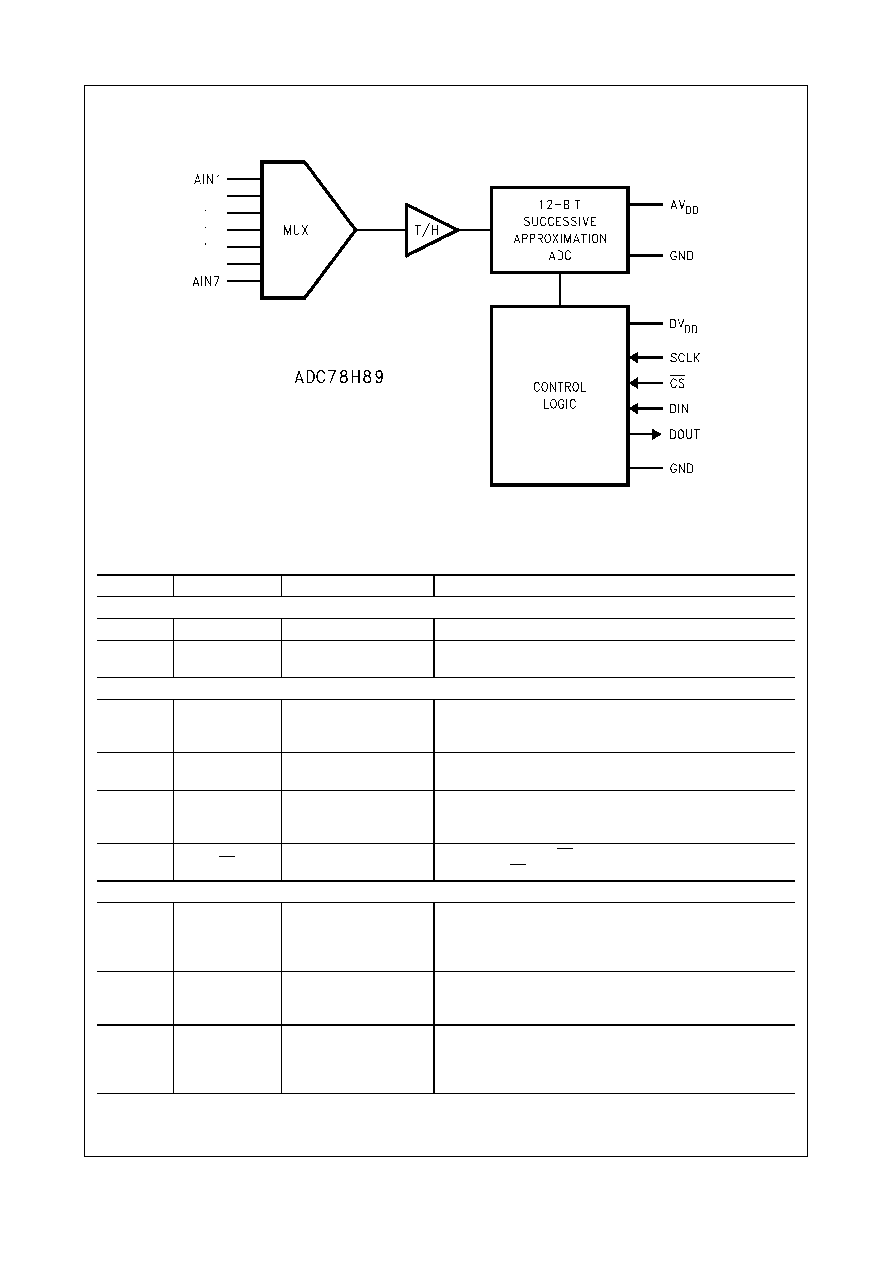

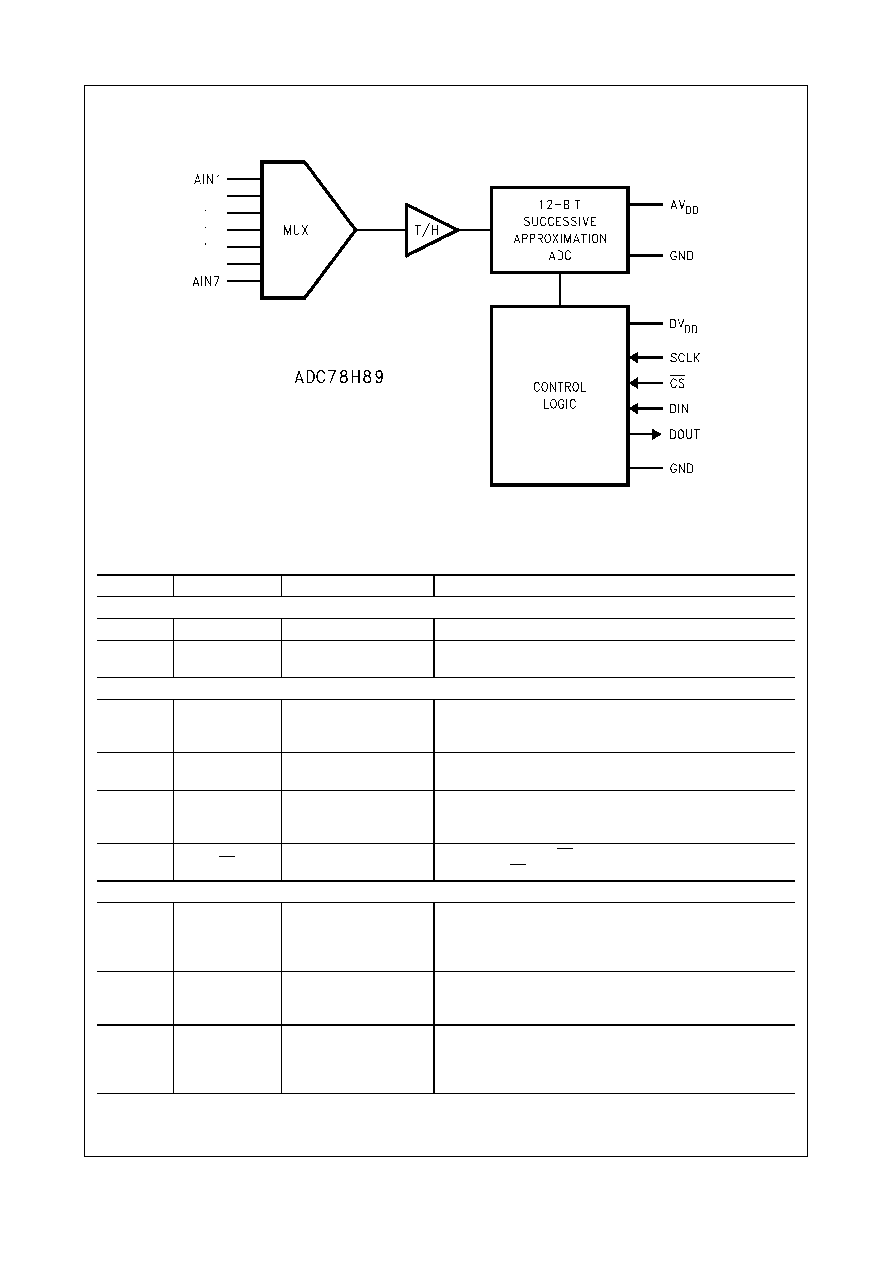

ADC78H89 7 12 CMOS A/D

500kSPS

ADC78H89 /

AIN1 AIN7 7

SPITMQSPITM

MICROWIRETM DSP

ADC78H89

(AV

DD

) 2.7V

5.25V (DV

DD

) 2.7V

AV

DD

3V

1.5mW 5V 8.3mW

3V 0.3W 5V

0.5W ADC78H89 16 TSSOP

- 40

85

7

SPITM/QSPITM/MICROWIRETM/DSP

16 TSSOP

500 kSPS

DNL

± 1 LSB (max)

INL

± 1 LSB (max)

3V

1.5 mW ( )

5V

8.3 mW ( )

Order Code

Temperature Range

Description

ADC78H89CIMT

- 40 to 85

16-Lead TSSOP Package

ADC78H89CIMTX

- 40 to 85

16-Lead TSSOP Package, Tape & Reel

2

www.national.com/JPN/

ADC

78H89

I/O

5 - 11

AIN1 to AIN7

0V AV

DD

2

NC

I/O

16

SCLK

10kHz

8MHz 8MHz

15

DOUT

SCLK

14

DIN

SCLK

ADC78H89

1

CS

CS

CS LOW

3

AV

DD

2.7V 5.25V

1cm 0.1F

1F

13

DV

DD

2.7V AV

DD

1cm 0.1F

4, 12

GND

3

www.national.com/JPN/

ADC78

H

89

(Note 1)

ADC78H89

(Note 2)

AV

DD

DV

DD

2.7V 5.25Vf

SCLK

8MHzf

SAMPLE

500kSPS

T

A

T

MIN

T

MAX

T

A

25

AV

DD

- 0.3V 6.5V

DV

DD

- 0.3V AV

DD

0.3V

6.5V ( )

GND

- 0.3V AV

DD

0.3V

(Note 3)

± 10 mA

ESD

2500V

250V

( )

10

260

150

- 65 150

- 40 T

A

85

AV

DD

2.7V 5.25V

DV

DD

2.7V AV

DD

- 0.3V AV

DD

JA

16-lead TSSOP on 4-layer, 2 oz. PCB

96 / W

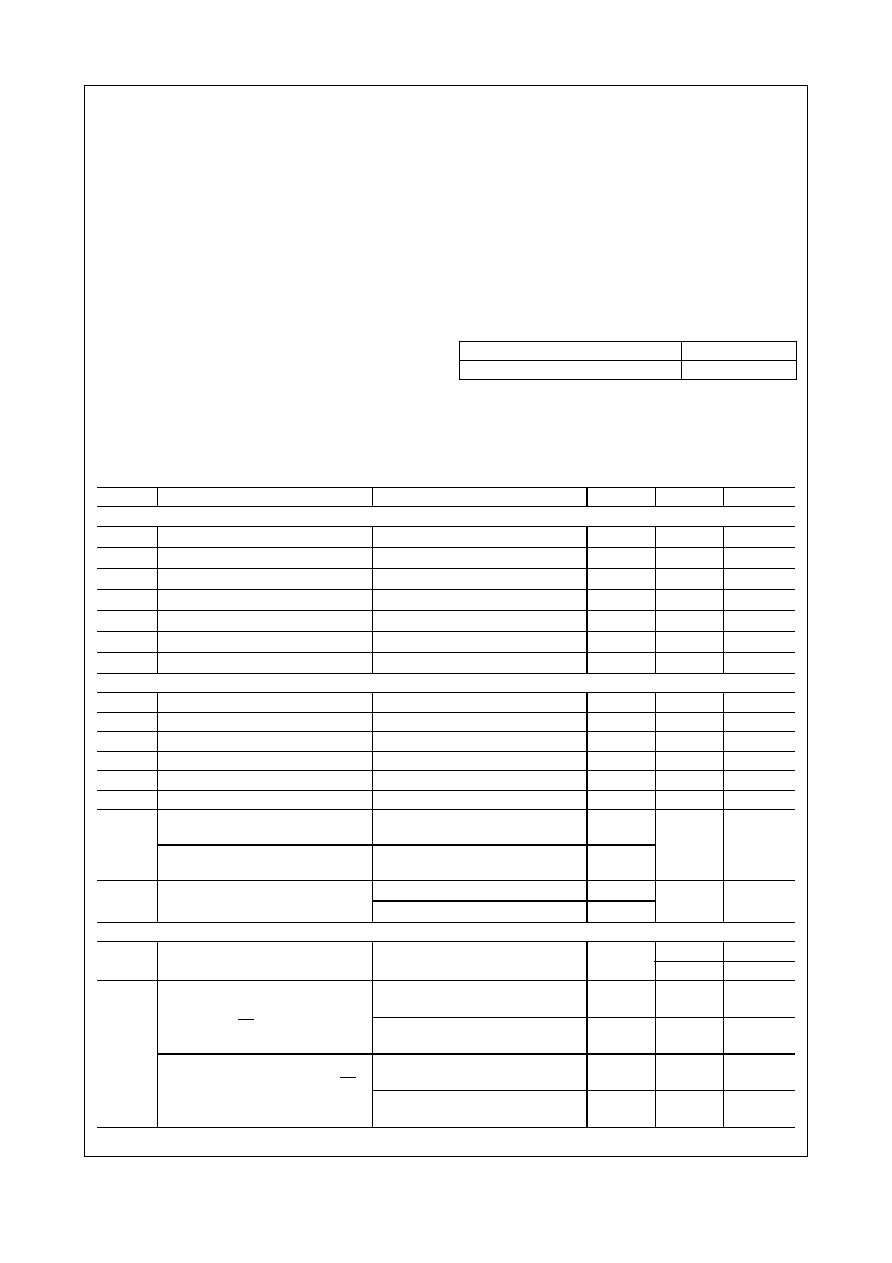

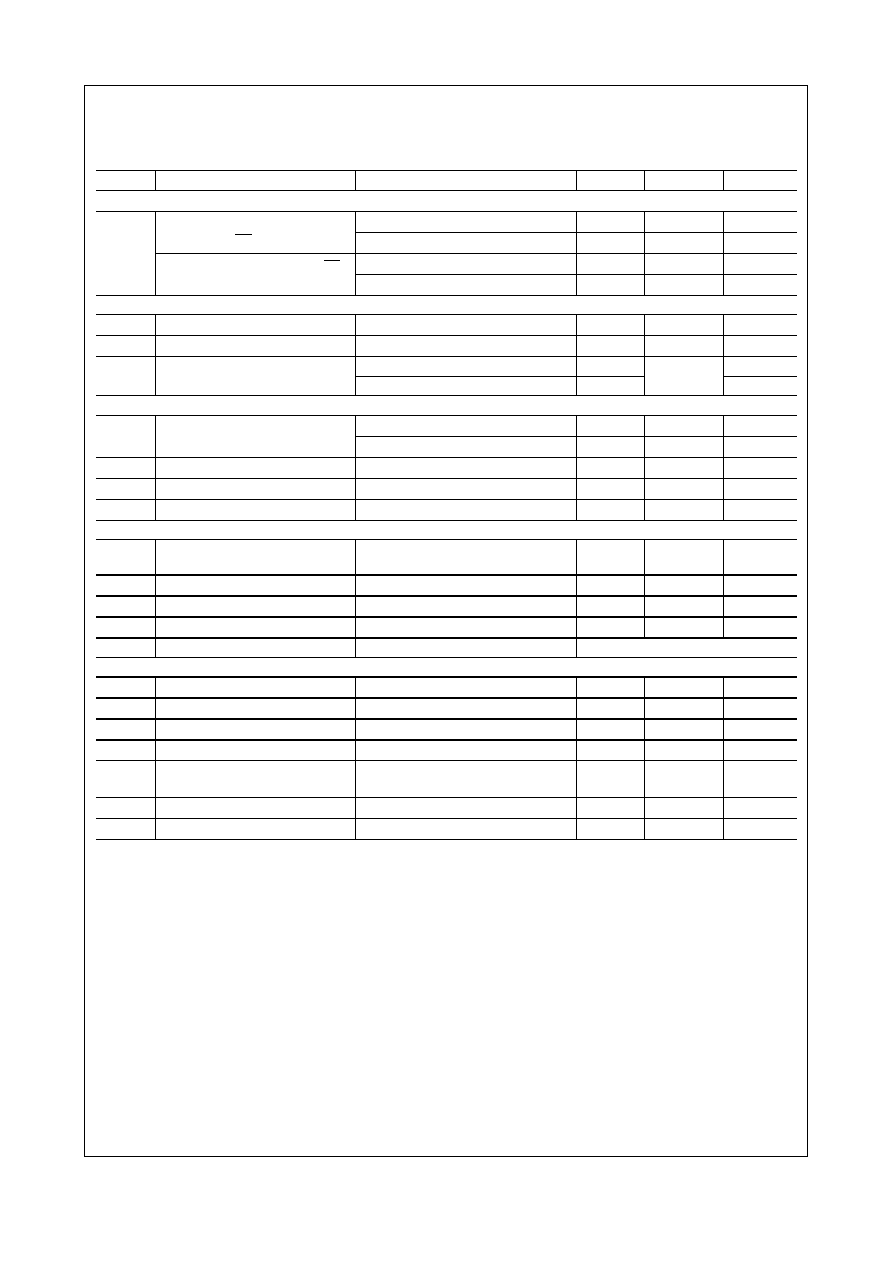

Symbol

Parameter

Conditions

Typical

Limits

Units

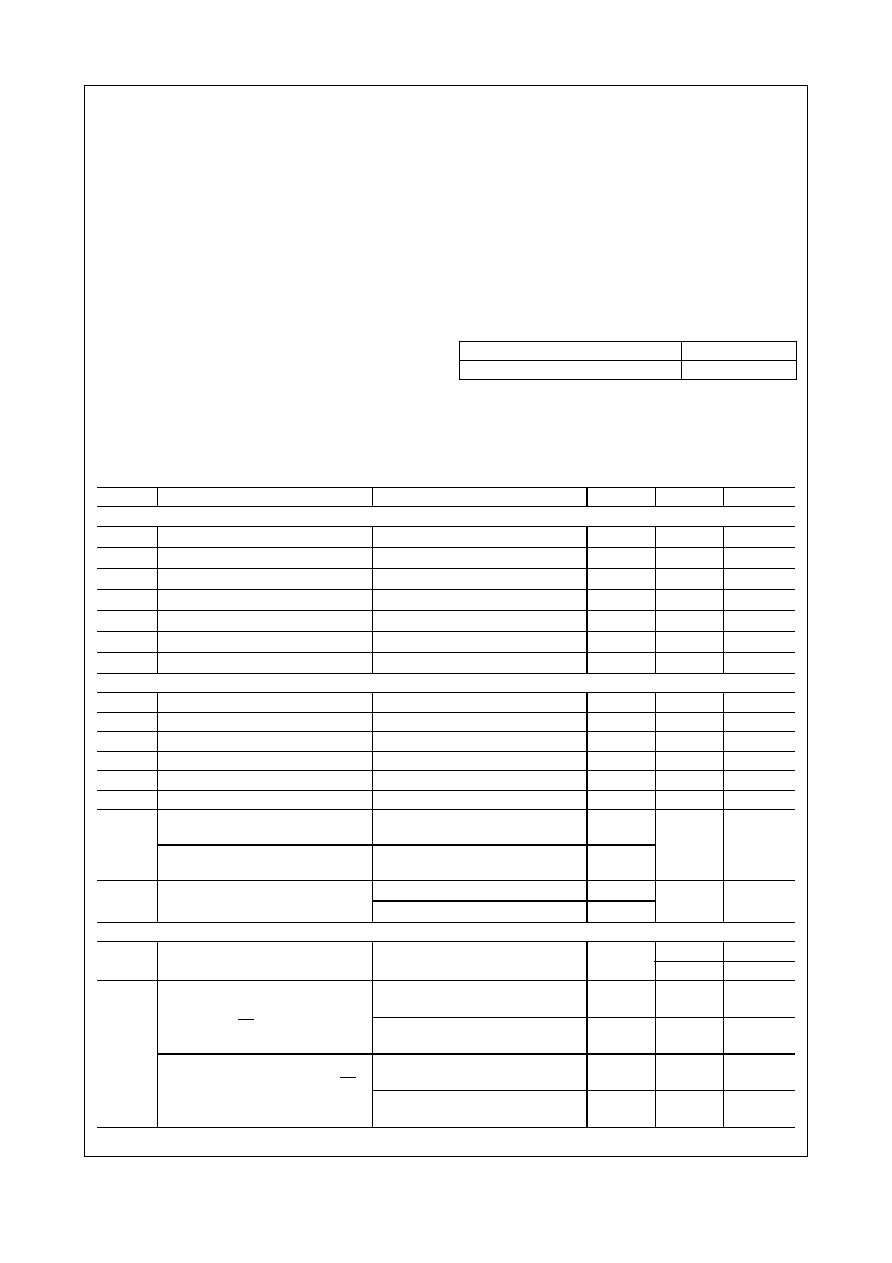

STATIC CONVERTER CHARACTERISTICS

Resolution with No Missing Codes

AV

DD

5.0V, DV

DD

3.3V

12

Bits

INL

Integral Non-Linearity

AV

DD

5.0V, DV

DD

3.3V

±

1

LSB(max)

DNL

Differential Non-Linearity

AV

DD

5.0V, DV

DD

3.3V

±

1

LSB(max)

OE

Offset Error

AV

DD

5.0V, DV

DD

3.3V

±

2

LSB(max)

OEM

Offset Error Match

AV

DD

5.0V, DV

DD

3.3V

±

2

LSB(max)

GE

Gain Error

AV

DD

5.0V, DV

DD

3.3V

±

3

LSB(max)

GEM

Gain Error Match

AV

DD

5.0V, DV

DD

3.3V

±

3

LSB(max)

DYNAMIC CONVERTER CHARACTERISTICS

(f

IN

40 kHz, -0.02 dBFS sine wave, unless otherwise noted)

SINAD

Signal-to-Noise Plus Distortion Ratio

72.6

dB

SNR

Signal-to-Noise Ratio

72.8

dB

THD

Total Harmonic Distortion

- 86

dB

SFDR

Spurious-Free Dynamic Range

88

dB

ENOB

Effective Number of Bits

11.8

bits

Channel-to-Channel Crosstalk

- 82

dB

IMD

Intermodulation Distortion, Second

Order Terms

f

a

40.161 kHz, f

b

41.015 kHz

- 93

dB

Intermodulation Distortion, Third Order

Terms

f

a

40.161 kHz, f

b

41.015 kHz

- 90

FPBW

- 3 dB Full Power Bandwidth

AV

DD

5V

11

MHz

AV

DD

3V

8

POWER SUPPLY CHARACTERISTICS

(C

L

10 pF)

AV

DD

,

DV

DD

Analog and Digital Supply Voltages

AV

DD

DV

DD

2.7

V(min)

5.25

V(max)

I

DD

Total Supply Current, Normal Mode

(Operational, CS low)

AV

DD

DV

DD

4.75V to 5.25V,

f

SAMPLE

500 kSPS

1.65

2.3

mA(max)

AV

DD

DV

DD

2.7V to 3.6V,

f

SAMPLE

500 kSPS

0.5

2.3

mA(max)

Total Supply Current, Shutdown (CS

high)

AV

DD

DV

DD

4.75V to 5.25V,

f

SAMPLE

0 kSPS

0.1

A

AV

DD

DV

DD

2.7V to 3.6V,

f

SAMPLE

0 kSPS

0.1

A

4

www.national.com/JPN/

ADC

78H89

ADC78H89

(Note 2)( )

AV

DD

DV

DD

2.7V 5.25Vf

SCLK

8MHzf

SAMPLE

500kSPS

T

A

T

MIN

T

MAX

T

A

25

Note 1:

Note 2:

min/max

Note 3:

Symbol

Parameter

Conditions

Typical

Limits

Units

POWER SUPPLY CHARACTERISTICS

(C

L

10 pF)

P

D

Power Dissipation, Normal Mode

(Operational, CS low)

AV

DD

DV

DD

4.75V to 5.25V

8.3

12

mW(max)

AV

DD

DV

DD

2.7V to 3.6V

1.5

8.3

mW(max)

Power Dissipation, Shutdown (CS

high)

AV

DD

DV

DD

4.75V to 5.25V

0.5

W

AV

DD

DV

DD

2.7V to 3.6V

0.3

W

ANALOG INPUT CHARACTERISTICS

V

IN

Input Range

0 to AV

DD

V

I

DCL

DC Leakage Current

1

A(max)

C

INA

Input Capacitance

In Track Mode

33

pF

In Hold Mode

3

pF

DIGITAL INPUT CHARACTERISTICS

V

IH

Input High Voltage

DV

DD

4.75Vto 5.25V

2.4

V(min)

DV

DD

2.7V to 3.6V

2.1

V(min)

V

IL

Input Low Voltage

DV

DD

2.7V to 5.25V

0.8

V(max)

I

IN

Input Current

V

IN

0V or DV

DD

10 nA

1

A(max)

C

IND

Input Capacitance

2

4

pF(max)

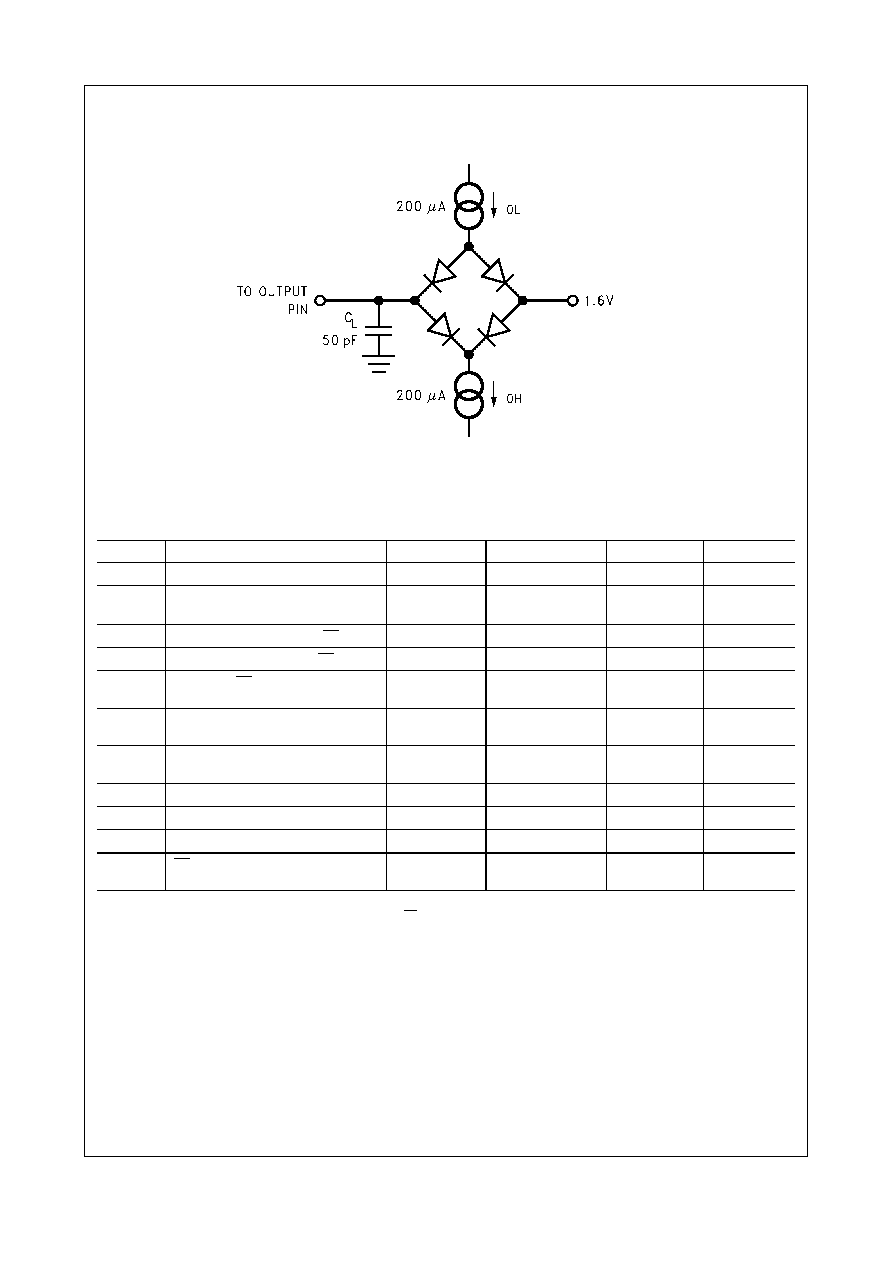

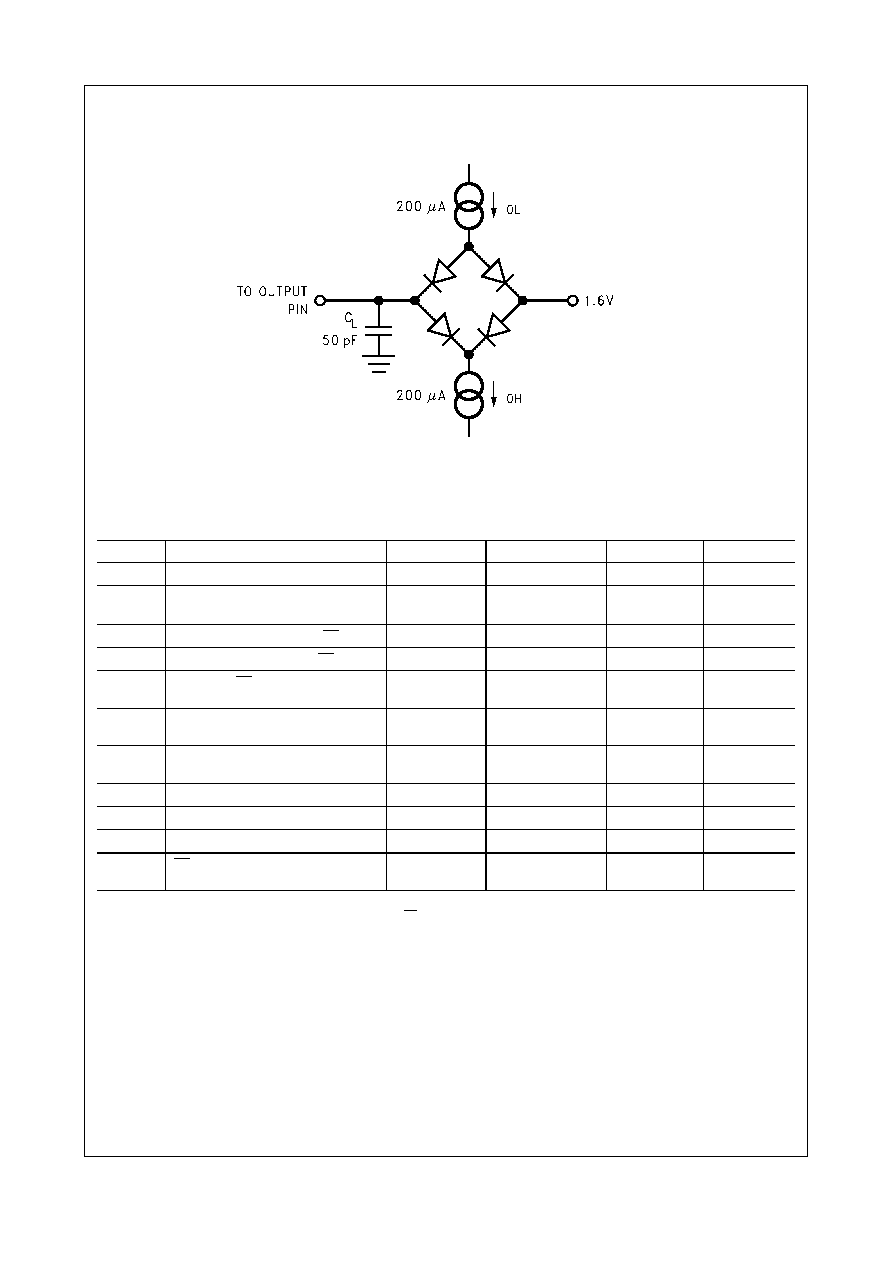

DIGITAL OUTPUT CHARACTERISTICS

V

OH

Output High Voltage

I

SOURCE

200 A, DV

DD

2.7V to

5.25V

DV

DD

-

0.5

V(min)

V

OL

Output Low Voltage

I

SINK

200 A

0.4

V(max)

I

OZL

TRI-STATE Leakage Current

1

A(max)

C

OUT

TRI-STATE Output Capacitance

2

4

pF(max)

Output Coding

Straight (Natural) Binary

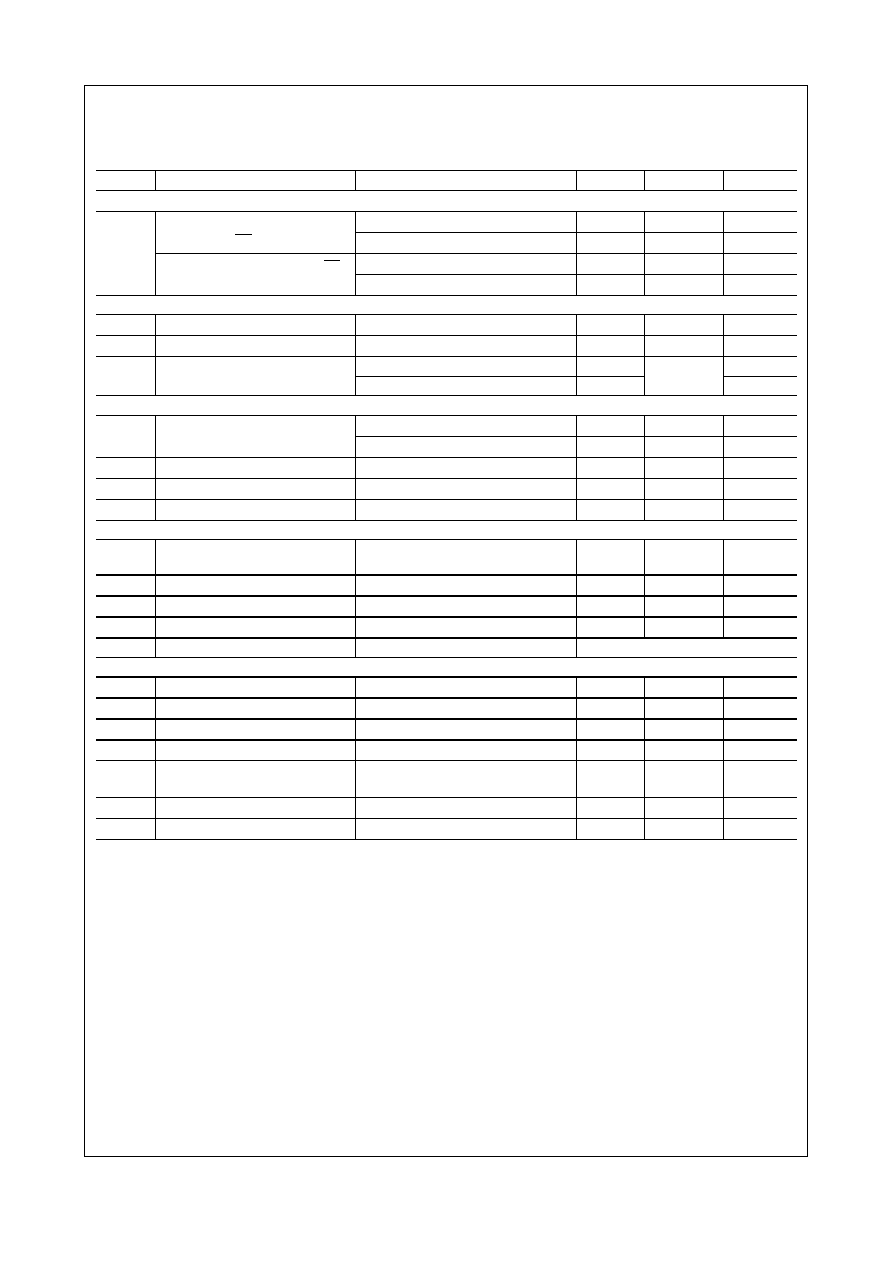

AC ELECTRICAL CHARACTERISTICS

f

SCLK

Clock Frequency

8

MHz(max)

t

CON

Conversion Time

1.625 s with f

SCLK

8 MHz

13

SCLK cycles

DC

Duty Cycle

40-60

t

TH

Track/Hold Acquisition Time

Full-Scale Step Input

3

SCLK cycles

Throughput Time

Conversion Time Acquisition Time,

500 kSPS with f

SCLK

8 MHz

16

SCLK cycles

f

RATE

Throughput Rate

500

kSPS(min)

t

AD

Aperture Delay

4

ns

5

www.national.com/JPN/

ADC78

H

89

ADC78H89

AV

DD

DV

DD

2.7V 5.25Vf

SCLK

8MHzC

L

50pF

T

A

T

MIN

T

MAX

T

A

25

Note 4:

t

1a

t

1b

CS (HIGH LOW)

Symbol

Parameter

Conditions

Typical

Limits

Units

t

CONVERT

13

SCLK Cycles

t

ACQ

Acquisition Time; Throughput Time

t

CONVERT

t

ACQ

16 x t

SCLK

3

SCLK Cycles

t

1a

High SCLK Setup to Falling CS

(Note 4)

10

ns(min)

t

1b

Low SCLK Hold to Falling CS

(Note 4)

10

ns(min)

t

2

Delay from CS Until DOUT

TRI-STATE

Æ

Disabled

30

ns(max)

t

3

Data Access Time after SCLK

Falling Edge

30

ns(max)

t

4

Data Setup Time Prior to SCLK

Rising Edge

10

ns(max)

t

5

Data Valid SCLK Hold Time

10

ns(max)

t

6

SCLK High Pulse Width

0.4 x t

SCLK

ns(min)

t

7

SCLK Low Pulse Width

0.4 x t

SCLK

ns(min)

t

8

CS Rising Edge to DOUT

High-Impedance

20

ns(max)