| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CS5530A | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

ƒÓÍÛÏÂÌÚýˆËˇ Ë ÓÔËÒýÌˡ www.docs.chipfind.ru

© 2001 National Semiconductor Corporation

www.national.com

GeodeTM

C

S

5530A

I/

O

C

ompani

on

M

u

l

t

i-Function

S

out

h

B

ri

dg

e

General Description

The CS5530A I/O companion is designed to work in con-

junction with a GX-series processor (i.e., GX1, GXLV,

GXm); all members of the National Semiconductor

Æ

GeodeTM family of products. Together, the Geode proces-

sor and CS5530A provide a system-level solution well

suited for the high performance needs of a host of devices

which include digital set-top boxes and thin client devices.

Due to the low power consumption of the GX-series pro-

cessors, this solution satisfies the needs of battery pow-

ered devices such as National's WebPADTM system, and

thermal design is eased allowing for fanless system

design.

The CS5530A I/O companion is a PCI-to-ISA bridge (South

Bridge), ACPI-compliant chipset that provides AT/ISA style

functionality. The device contains state-of-the-art power

management that enables systems, especially battery

powered systems, to significantly reduce power consump-

tion.

Audio is supported through PCI bus master engines which

connect to an AC97 compatible codec such as the National

Semiconductor LM4548. If industry standard audio is

required, a combination of hardware and software called

Virtual System Architecture

Æ

(VSATM) technology is pro-

vided.

The Geode GX-series processors' graphics/video output is

connected to the CS5530A. The CS5530A graphics/video

support includes a PLL that generates the DOT clock for

the GX-series processors (where the graphics controller is

located), video acceleration hardware, gamma RAM plus

three DACs for RGB output to CRT, and digital RGB that

can be directly connected to TFT panels or NTSC/PAL

encoders. The digital RGB output can also be connected to

the National Semiconductor Geode CS9211 graphics com-

panion (a flat panel display controller) for DSTN panel sup-

port.

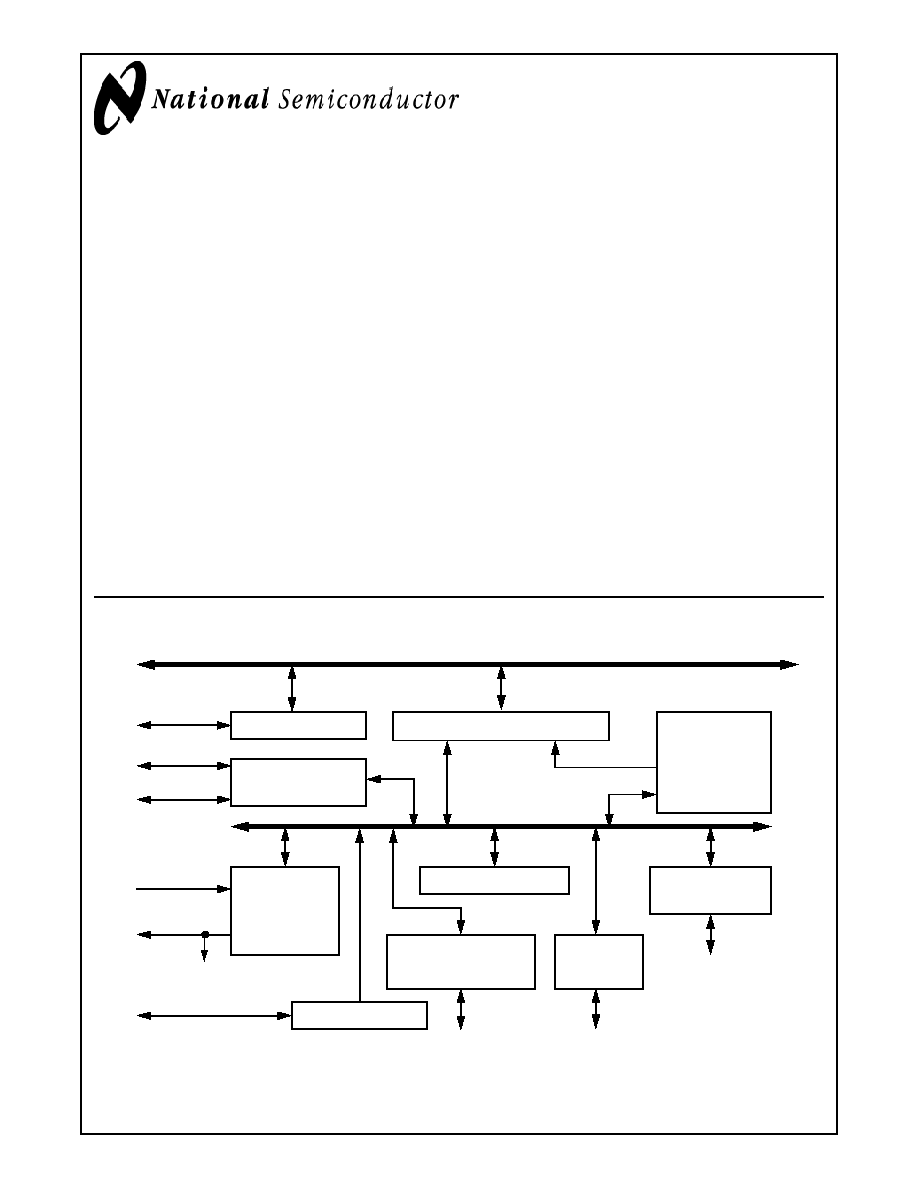

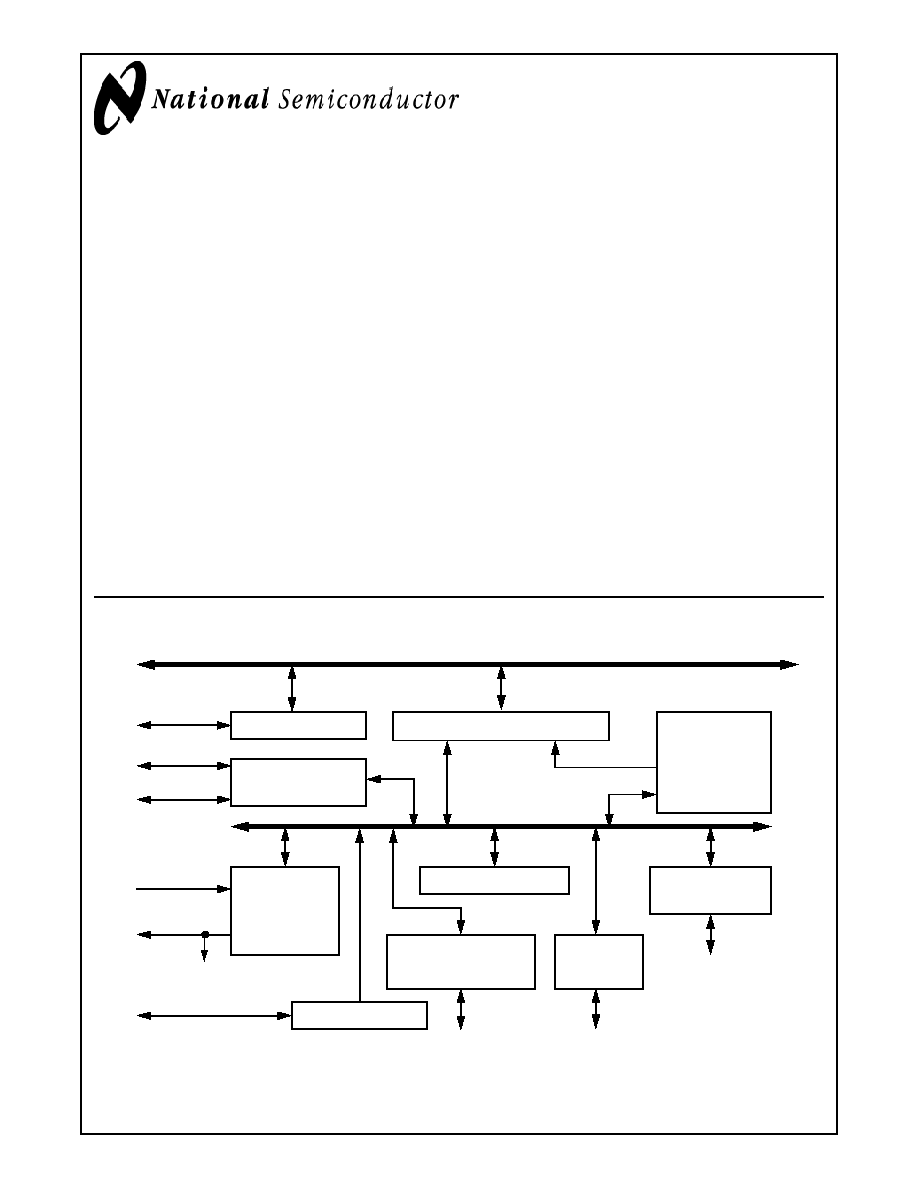

GeodeTM CS5530A Internal Block Diagram

X-Bus

ISA Bus

PCI Bus

USB

PCI to X-Bus / X-Bus to PCI Bridge

PCI to USB Macro

Active Decode

Address Mapper

Audio/Codec/MPU

Interface

Pwr Mgmt, Traps,

Events, and Timers

IDE

Interface

Display Interface

MPEG, DOT Clock

CSC and SCL

RGB/FP Interface

AT Compatibility Logic

ISA Bus Interface

AT Ports, ISA Megacells

Display

PCI Configuration

Registers

Graphics

and Video

from CPU

X-Bus Arbiter

CS5530A Support

GPIOs

IDE

AC97 Codec

Ultra DMA/33

(e.g., LM4548)

Joystick / Game Port

Joystick

PC97317 SIO

GPCS

GeodeTM CS9211

Graphics Companion

May 2001

Revision 1.1

GeodeTM CS5530A I/O Companion

Multi-Function South Bridge

National Semiconductor and Virtual System Architecture are registered trademarks of National Semiconductor Corporation.

Geode, VSA and WebPAD are trademarks of National Semiconductor Corporation.

For a complete listing of National Semiconductor trademarks, please visit www.national.com/trademarks.

www.national.com

2

Revision 1.1

G

e

od

eTM

CS

55

30

A

Two bus mastering IDE controllers are included for support

of up to four ATA-compliant devices. A two-port Universal

Serial Bus (USB) provides high speed, Plug & Play expan-

sion for a variety of consumer peripheral devices such as a

keyboard, mouse, printer, and digital camera. If additional

functions are required like real-time clock, floppy disk, PS2

keyboard, and PS2 mouse, a SuperI/O such as the

National PC97317 can be easily connected to the

CS5530A.

Features

General Features

Designed for use with National's Geode GX-series

processors

352 PBGA (Plastic Ball Grid Array) package

3.3V or 5.0V PCI bus compatible

5.0V tolerant on all inputs

3.3V core

PCI-to-ISA Bridge

PCI 2.1 compliant

Supports PCI initiator-to-ISA and ISA master-to-PCI

cycle translations

PCI master for audio I/O and IDE controllers

Subtractive agent for unclaimed transactions

PCI-to-ISA interrupt mapper/translator

AT Compatibility

Two 8259A-equivalent interrupt controllers

8254-equivalent timer

Two 8237-equivalent DMA controllers

Boot ROM and keyboard chip select

Extended ROM to 16 MB

Bus Mastering IDE Controllers

Two controllers with support for up to four IDE devices

Independent timing for master and slave devices for

both channels

PCI bus master burst reads and writes

Ultra DMA/33 (ATA-4) support

Multiword DMA support

Programmed I/O (PIO) Modes 0-4 support

Power Management

Intelligent system controller supports multiple power

management standards:

-- Full ACPI and Legacy (APM) support

-- Directly manages all GX-series processors' power

states (including automatic Suspend modulation for

optimal performance/thermal balancing)

I/O traps and idle timers for peripheral power

management

Up to eight GPIOs for system control:

-- All eight are configurable as external wakeup events

Dedicated inputs for keyboard and mouse wakeup

events

XpressAUDIO

Provides "back-end" hardware support via six buffered

PCI bus masters

AC97 codec interface:

-- Specification Revision 1.3, 2.0, and 2.1 compliant

interface. Note that the codec (e.g., LM4548) must

have SRC (sample rate conversion) support

Display Subsystem Extensions

Complements the GX-series processors' graphics and

video capabilities:

-- Three independent line buffers for accelerating video

data streams

-- Handles asynchronous video and graphics data

streams concurrently from the processor

-- YUV to RGB conversion hardware

-- Arbitrary X & Y interpolative scaling

-- Color keying for graphics/video overlay

VDACs / Display interface:

-- Three integrated DACs

-- Gamma RAM:

≠ Provides gamma correction for graphics data

streams

≠ Provides brightness/contrast correction for video

data streams

-- Integrated DOT clock generator

-- Digital RGB interface drives TFT panels or standard

NTSC/PAL encoders

-- Up to 1280x1024 @ 85 Hz

Universal Serial Bus

Two independent USB interfaces:

-- Open Host Controller Interface (OpenHCI)

specification compliant

-- Second generation proven core design

Ge

odeTM

C

S

553

0A

Table of Contents

Revision 1.1

3

www.national.com

1.0

Architecture Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.1

PCI BUS INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.2

ISA BUS INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.3

AT COMPATIBILITY LOGIC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.3.1

DMA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.3.2

Programmable Interval Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.3.3

Programmable Interrupt Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.4

IDE CONTROLLERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.5

POWER MANAGEMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.5.1

GPIO Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.6

XPRESSAUDIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.6.1

AC97 Codec Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.6.2

VSA Technology Support Hardware . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.7

DISPLAY SUBSYSTEM EXTENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1.8

CLOCK GENERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.9

UNIVERSAL SERIAL BUS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.10

PROCESSOR SUPPORT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.0

Signal Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.1

PIN ASSIGNMENTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.2

SIGNAL DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.2.1

Reset Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.2.2

Clock Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.2.3

CPU Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

2.2.4

PCI Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2.2.5

ISA Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

2.2.6

ROM Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2.2.7

IDE Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.2.8

USB Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.2.9

Game Port and General Purpose I/O Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.2.10

Audio Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

2.2.11

Display Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

2.2.12

DCLK PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

2.2.13

Power, Ground, and No Connects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

2.2.14

Internal Test and Measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.0

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

3.1

PROCESSOR INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3.1.1

Display Subsystem Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.1.2

PSERIAL Pin Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3.1.2.1

Video Retrace Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3.2

PCI BUS INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

3.2.1

PCI Initiator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

3.2.2

PCI Target . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

3.2.3

Special Bus Cycles≠Shutdown/Halt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

3.2.4

PCI Bus Parity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

3.2.5

PCI Interrupt Routing Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

3.2.6

Delayed Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

www.national.com

4

Revision 1.1

G

e

od

eTM

CS

55

30

A

Table of Contents

(Continued)

3.3

RESETS AND CLOCKS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

3.3.1

Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

3.3.2

ISA Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

3.3.3

DOT Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

3.3.3.1

DCLK Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

3.4

POWER MANAGEMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

3.4.1

CPU Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

3.4.1.1

On . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

3.4.1.2

Active Idle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

3.4.1.3

Suspend . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

3.4.1.4

3 Volt Suspend . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

3.4.1.5

Off . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

3.4.1.6

Suspend Modulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

3.4.1.7

Save-to-Disk/Save-to-RAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

3.4.2

APM Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

3.4.3

Peripheral Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

3.4.3.1

Device Idle Timers and Traps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

3.4.3.2

General Purpose Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3.4.3.3

ACPI Timer Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

3.4.3.4

General Purpose I/O Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

3.4.3.5

Power Management SMI Status Reporting Registers . . . . . . . . . . . . . . . . . . . . . . . . 78

3.4.3.6

Device Power Management Register Programming Summary . . . . . . . . . . . . . . . . . 86

3.5

PC/AT COMPATIBILITY LOGIC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

3.5.1

ISA Subtractive Decode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

3.5.2

ISA Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

3.5.2.1

Delayed PCI Transactions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

3.5.2.2

Limited ISA and ISA Master Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

3.5.2.3

ISA Bus Data Steering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

3.5.2.4

I/O Recovery Delays. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

3.5.2.5

ISA DMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

3.5.3

ROM Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

3.5.4

Megacells . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

3.5.4.1

Direct Memory Access (DMA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

3.5.4.2

Programmable Interval Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

3.5.4.3

Programmable Interrupt Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

3.5.4.4

PCI Compatible Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

3.5.5

I/O Ports 092h and 061h System Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

3.5.5.1

I/O Port 092h System Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

3.5.5.2

I/O Port 061h System Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

3.5.5.3

SMI Generation for NMI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

3.5.6

Keyboard Interface Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

3.5.6.1

Fast Keyboard Gate Address 20 and CPU Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . 106

3.5.7

External Real-Time Clock Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

3.6

IDE CONTROLLER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

3.6.1

IDE Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

3.6.2

IDE Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

3.6.2.1

PIO Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

3.6.2.2

Bus Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

3.6.2.3

Ultra DMA/33 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Revision 1.1

5

www.national.com

Ge

odeTM

C

S

553

0A

Table of Contents

(Continued)

3.7

XPRESSAUDIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

3.7.1

Subsystem Data Transport Hardware . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

3.7.1.1

Audio Bus Masters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

3.7.1.2

Physical Region Descriptor Table Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

3.7.1.3

Physical Region Descriptor Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

3.7.1.4

Programming Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

3.7.1.5

AC97 Codec Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

3.7.2

VSA Technology Support Hardware . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

3.7.2.1

VSA Technology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

3.7.2.2

Audio SMI Related Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

3.7.2.3

IRQ Configuration Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

3.8

DISPLAY SUBSYSTEM EXTENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

3.8.1

Video Interface Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

3.8.2

Video Accelerator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

3.8.2.1

Line Buffers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

3.8.2.2

Video Port Protocol. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

3.8.2.3

Video Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

3.8.2.4

X and Y Scaler / Filter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

3.8.2.5

Color-Space-Converter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

3.8.3

Video Overlay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

3.8.4

Gamma RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

3.8.5

Display Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

3.8.5.1

Video DACs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

3.8.5.2

VESA DDC2B / DPMS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

3.8.5.3

Flat Panel Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

3.9

UNIVERSAL SERIAL BUS SUPPORT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

3.9.1

USB PCI Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

3.9.2

USB Host Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

3.9.3

USB Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

4.0

Register Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

4.1

PCI CONFIGURATION SPACE AND ACCESS METHODS . . . . . . . . . . . . . . . . . . . . . . . . . 141

4.2

REGISTER SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

4.3

CHIPSET REGISTER SPACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

4.3.1

Bridge Configuration Registers - Function 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

4.3.2

SMI Status and ACPI Timer Registers - Function 1 . . . . . . . . . . . . . . . . . . . . . . . . . 182

4.3.3

IDE Controller Registers - Function 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

4.3.4

XpressAUDIO Registers - Function 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

4.3.5

Video Controller Registers - Function 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

4.4

USB REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

4.5

CS5530A ISA LEGACY I/O REGISTER SPACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

4.6

V-ACPI I/O REGISTER SPACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

Document Outline