| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: DM9316W | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

TL F 6606

9316DM9316

Synchronous

4-Bit

Counters

June 1989

9316 DM9316 Synchronous 4-Bit Counters

General Description

These synchronous presettable counters feature an inter-

nal carry look-ahead for application in high-speed counting

designs The 9316 is a 4-bit binary counter The carry output

is decoded by means of a NOR gate thus preventing spikes

during the normal counting mode of operation Synchronous

operation is provided by having all flip-flops clocked simulta-

neously so that the outputs change coincident with each

other when so instructed by the count-enables inputs and

internal gating This mode of operating eliminates the output

counting spikes which are normally associated with asyn-

chronous (ripple clock) counters A buffered clock input trig-

gers the four flip-flops on the rising (positive-going) edge of

the clock input waveform

These counters are fully programmable that is the outputs

may be preset to either level As presetting is synchronous

setting up a low level at the load input disables the counter

and causes the outputs to agree with the setup data after

the next clock pulse regardless of the levels of the enable

input Low-to-high transitions at the load input are perfectly

acceptable regardless of the logic levels on the clock or

enable inputs The clear function is asynchronous and a low

level at the clear input sets of the flip-flop outputs low re-

gardless of the levels of clock load or enable inputs

The carry look-ahead circuitry provides for cascading coun-

ters for n-bit synchronous applications without additional

gating Instrumental in accomplishing this function are two

count-enable inputs and a ripple carry output Both count-

enable inputs (P and T) must be high to count and input T is

fed-forward to enable the ripple carry output The ripple car-

ry output thus enabled will produce a high-level output pulse

with a duration approximately equal to the high-level portion

of the Q

A

output This high-level overflow ripple carry pulse

can be used to enable successive cascaded stages High-

to-low level transitions at the enable P or T inputs may occur

regardless of the logic level in the clock

Features

Y

Internal look-ahead for fast counting

Y

Carry output for n-bit cascading

Y

Synchronous counting

Y

Load control line

Y

Diode-clamped inputs

Y

Typical clock frequency 35 MHz

Y

Pin-for-pin replacements popular 54 74 counters

5416A 7416A (binary)

Y

Alternate Military Aerospace device (9316) is available

Contact a National Semiconductor Sales Office Distrib-

utor for specifications

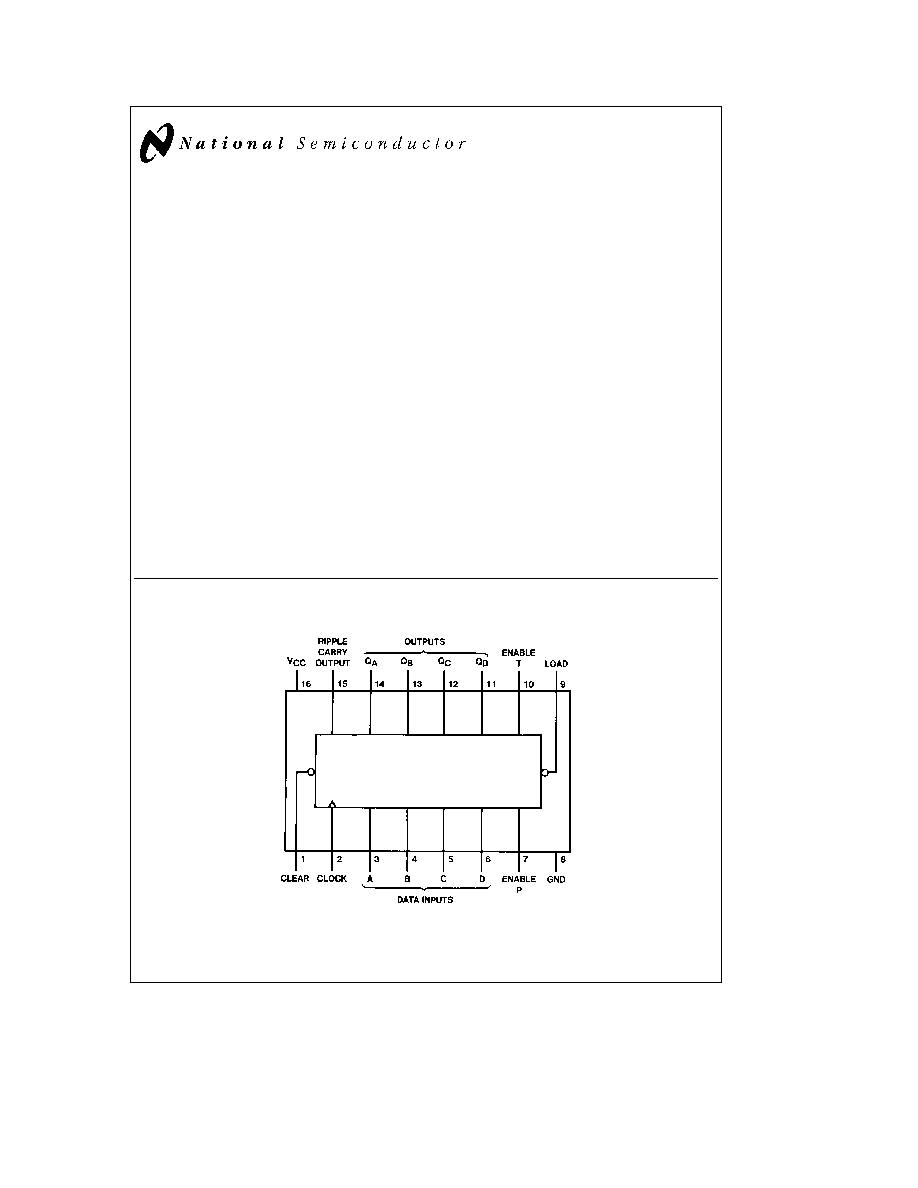

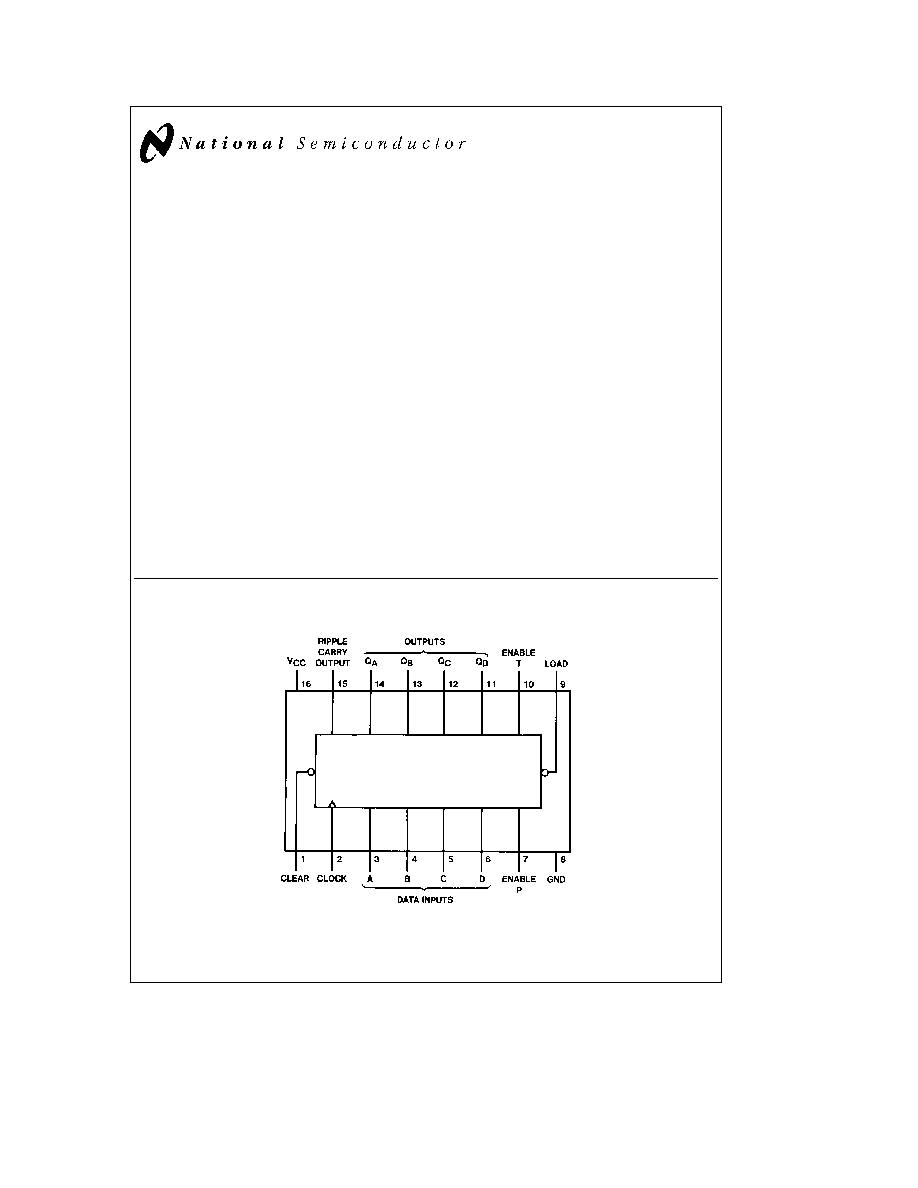

Connection Diagram

Dual-In-Line Package

TL F 6606 ≠ 1

Order Number 9316DMQB 9316FMQB DM9316J

DM9316W or DM9316N

See NS Package Number J16A N16E or W16A

C1995 National Semiconductor Corporation

RRD-B30M105 Printed in U S A

Absolute Maximum Ratings

(Note)

If Military Aerospace specified devices are required

please contact the National Semiconductor Sales

Office Distributors for availability and specifications

Supply Voltage

7V

Input Voltage

5 5V

Operating Free Air Temperature Range

Military

b

55 C to

a

125 C

Commercial

0 C to

a

70 C

Storage Temperature Range

b

65 C to

a

150 C

Note

The ``Absolute Maximum Ratings'' are those values

beyond which the safety of the device cannot be guaran-

teed The device should not be operated at these limits The

parametric values defined in the ``Electrical Characteristics''

table are not guaranteed at the absolute maximum ratings

The ``Recommended Operating Conditions'' table will define

the conditions for actual device operation

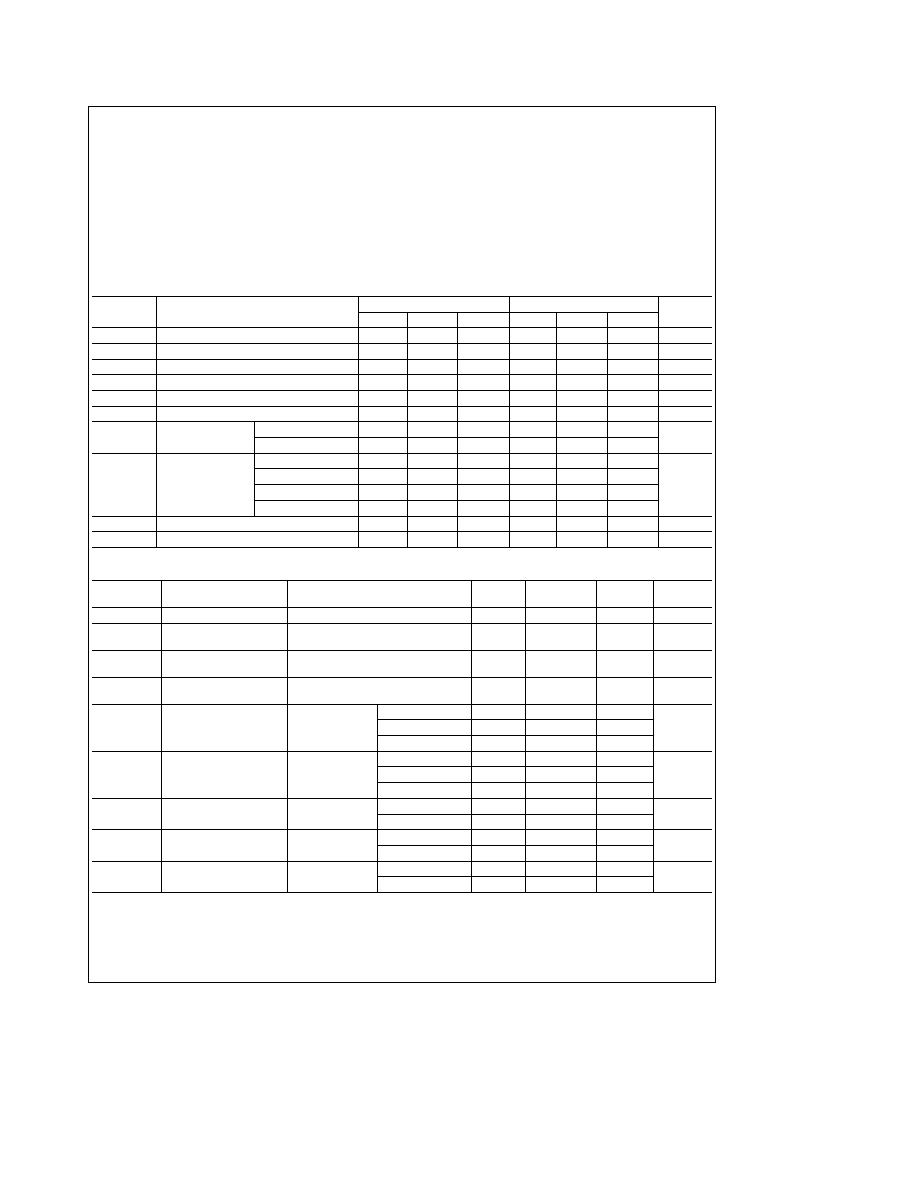

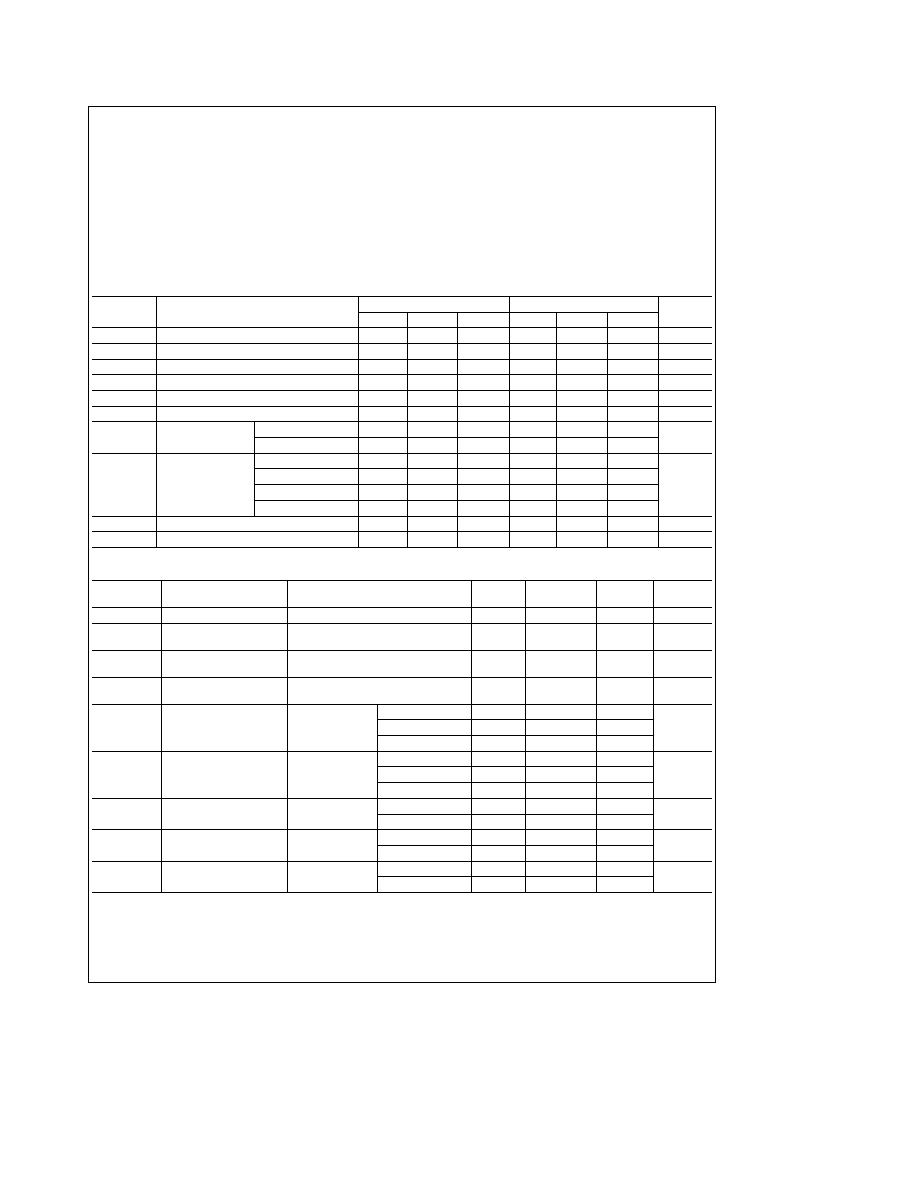

Recommended Operating Conditions

Symbol

Parameter

Military

Commercial

Units

Min

Nom

Max

Min

Nom

Max

V

CC

Supply Voltage

4 5

5

5 5

4 75

5

5 25

V

V

IH

High Level Input Voltage

2

2

V

V

IL

Low Level Input Voltage

0 8

0 8

V

I

OH

High Level Output Current

b

0 8

b

0 8

mA

I

OL

Low Level Output Current

16

16

mA

f

CLK

Clock Frequency (Note 6)

0

25

0

25

MHz

t

W

Pulse Width

Clock

25

25

ns

(Note 6)

Clear

20

20

t

SU

Setup Time

Data

20

20

(Note 6)

Enable P

20

20

ns

Load

25

25

Clear

20

20

t

H

Any Hold Time (Notes 1

6)

0

0

ns

T

A

Free Air Operating Temperature

b

55

125

0

70

C

Electrical Characteristics

over recommended operating free air temperature range (unless otherwise noted)

Symbol

Parameter

Conditions

Min

Typ

Max

Units

(Note 2)

V

I

Input Clamp Voltage

V

CC

e

Min I

I

e b

12 mA

b

1 5

V

V

OH

High Level Output

V

CC

e

Min I

OH

e

Max

2 4

3 4

V

Voltage

V

IL

e

Max V

IH

e

Min

V

OL

Low Level Output

V

CC

e

Min I

OL

e

Max

0 2

0 4

V

Voltage

V

IH

e

Min V

IL

e

Max

I

I

Input Current

Max

V

CC

e

Max V

I

e

5 5V

1

mA

Input Voltage

I

IH

High Level Input

V

CC

e

Max

Clock

80

Current

V

I

e

2 4 V

Enable T

80

m

A

Other

40

I

IL

Low Level Input

V

CC

e

Max

Clock

b

3 2

Current

V

I

e

0 4V

Enable T

b

3 2

m

A

Other

b

1 6

I

OS

Short Circuit

V

CC

e

Max

MIL

b

20

b

57

mA

Output Current

(Note 3)

COM

b

18

b

57

I

CCH

Supply Current with

V

CC

e

Max

MIL

59

85

mA

Outputs High

(Note 4)

COM

59

94

I

CCL

Supply Current with

V

CC

e

Max

MIL

63

91

mA

Outputs Low

(Note 5)

COM

63

101

Note 1

The minimum HOLD time is as specified or as long as the CLOCK input takes to rise from 0 8V to 2V whichever is longer

Note 2

All typicals are at V

CC

e

5V T

A

e

25 C

Note 3

Not more than one output should be shorted at a time

Note 4

I

CCH

is measured with the LOAD input high then again with the LOAD input low with all other inputs high and all outputs open

Note 5

I

CCL

is measured with the CLOCK input high then again with the CLOCK input low with all other inputs low and all outputs open

Note 6

T

A

e

25 C and V

CC

e

5V

2

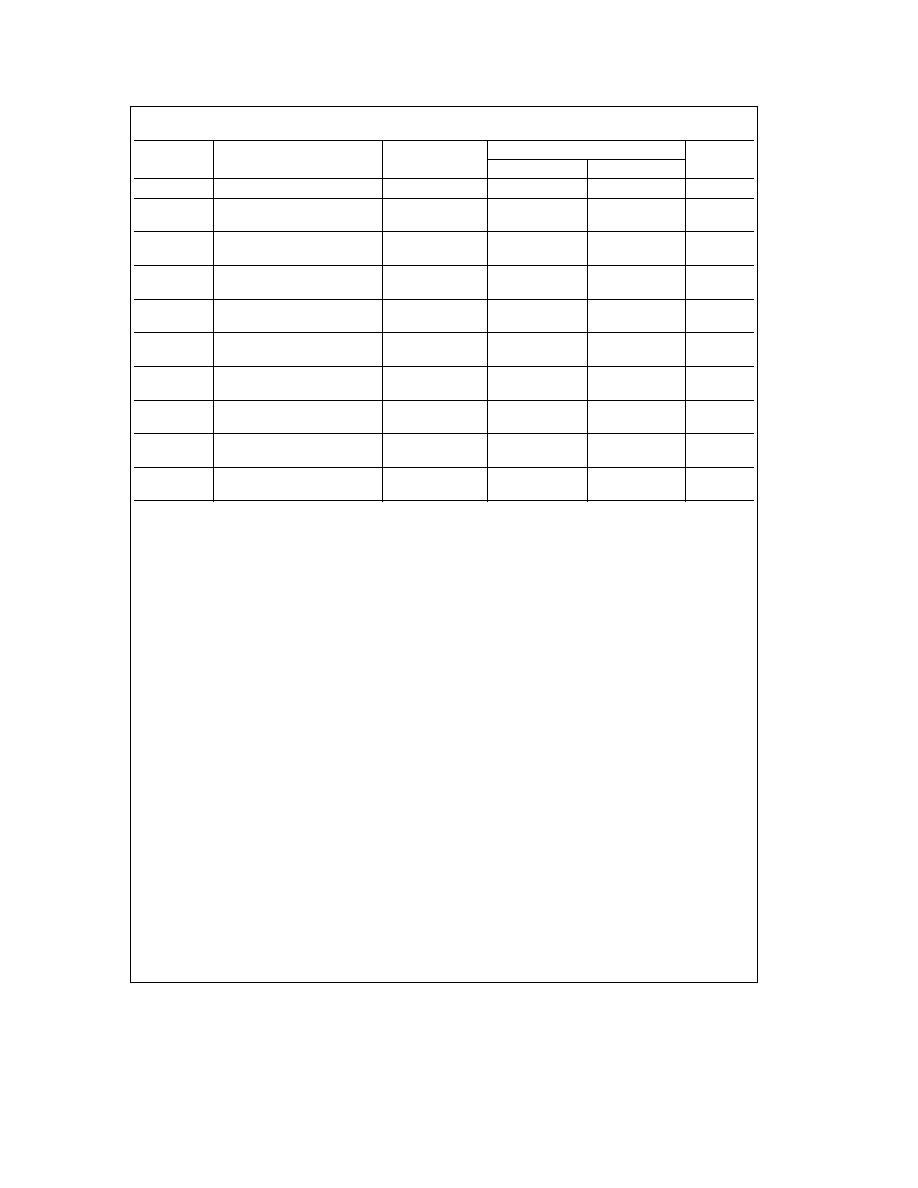

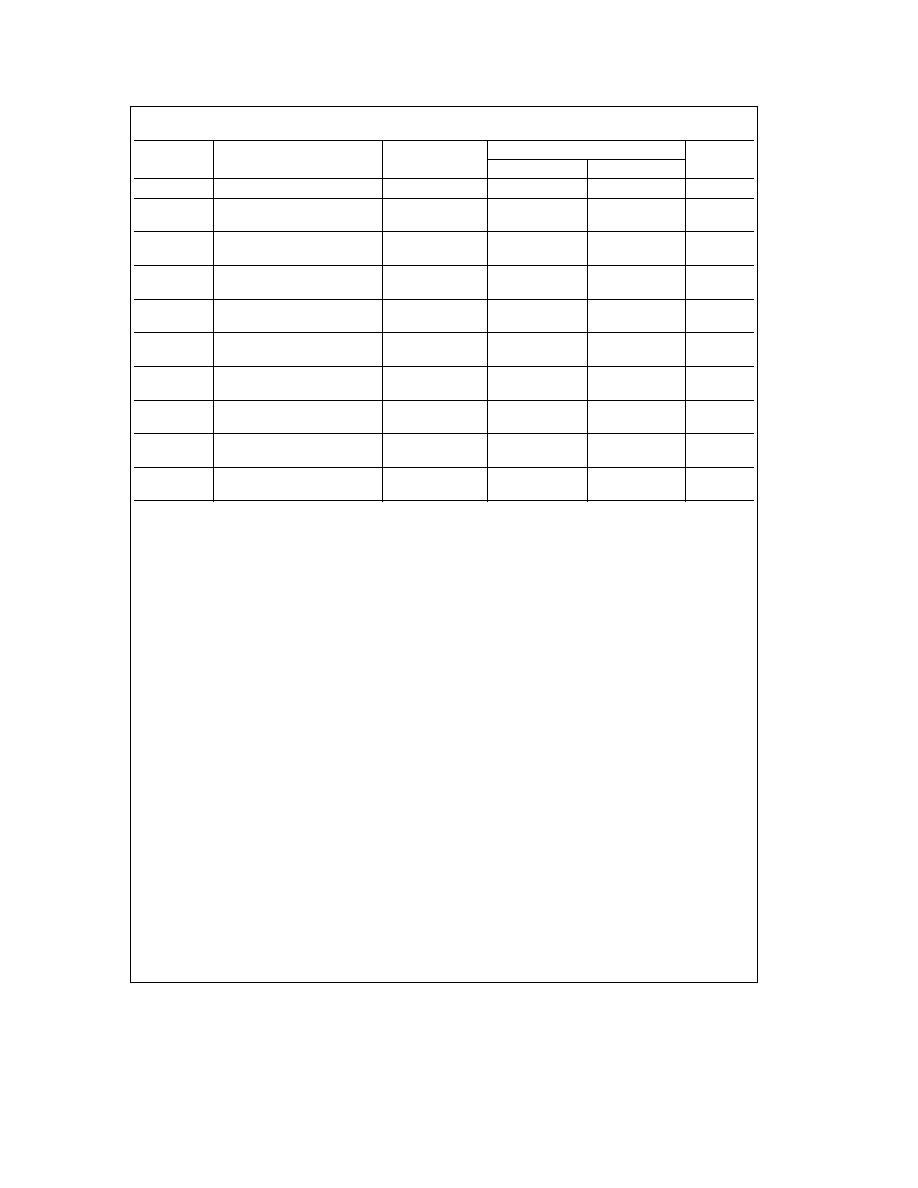

Switching Characteristics

at V

CC

e

5V and T

A

e

25 C (See Section 1 for Test Waveforms and Output Load)

Symbol

Parameter

From (Input)

R

L

e

400X C

L

e

15 pF

Units

To (Output)

Min

Max

f

MAX

Maximum Clock Frequency

25

MHz

t

PLH

Propagation Delay Time

Clock

27

ns

Low to High Level Output

to RC

t

PHL

Propagation Delay Time

Clock

24

ns

High to Low Level Output

to RC

t

PLH

Propagation Delay Time

Clock

20

ns

Low to High Level Output

to Q

t

PHL

Propagation Delay Time

Clock

23

ns

High to Low Level Output

to Q

t

PLH

Propagation Delay Time

Clock

21

ns

Low to High Level Output

to Q

t

PHL

Propagation Delay Time

Clock

25

ns

High to Low Level Output

to Q

t

PLH

Propagation Delay Time

ENT

15

ns

Low to High Level Output

to RC

t

PHL

Propagation Delay Time

ENT

16

ns

High to Low Level Output

to RC

t

PHL

Propagation Delay Time

Clear

36

ns

High to Low Level Output

to Q

3

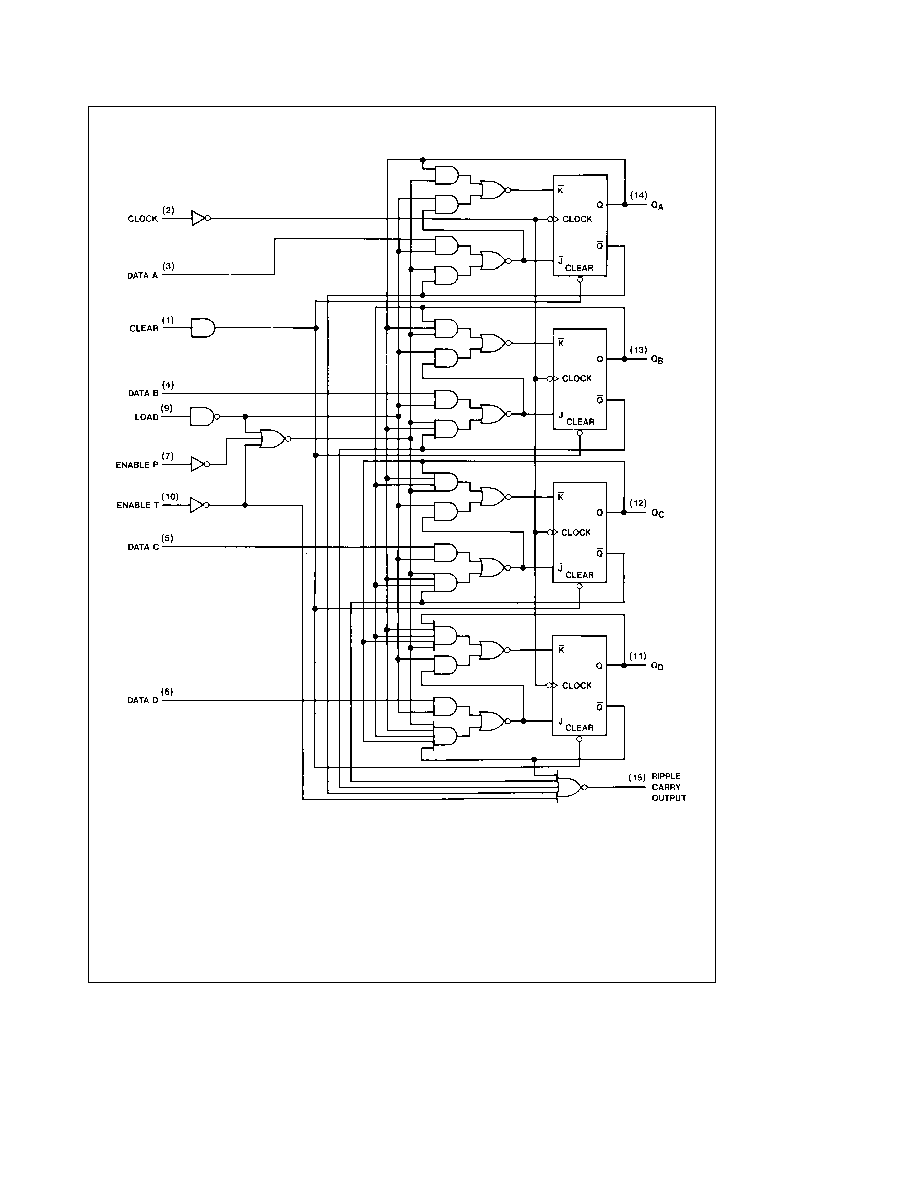

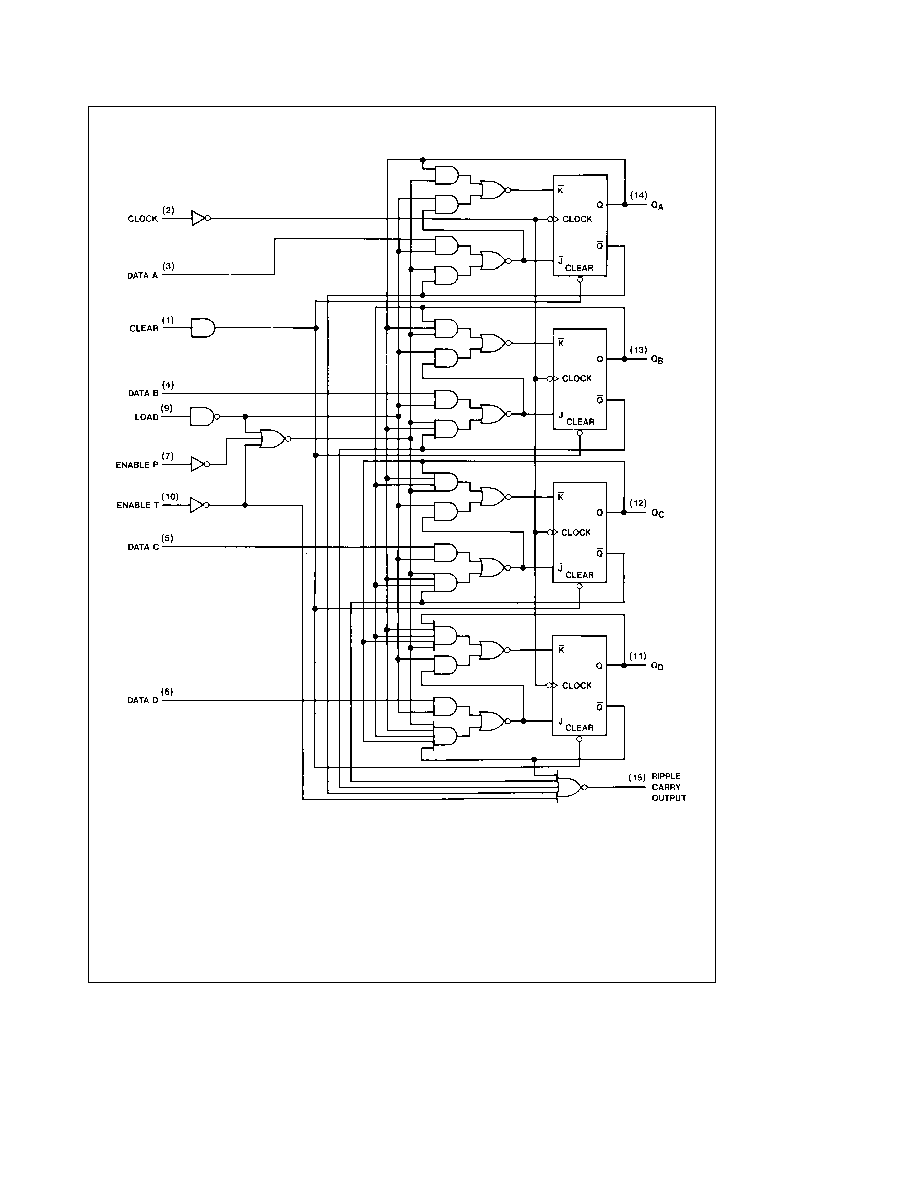

Logic Diagram

9316

TL F 6606 ≠ 2

4

Timing Diagram

9316 Synchronous Binary Counters

Typical Clear Preset Count and Inhibit Sequences

TL F 6606 ≠ 3

Sequence

(1) Clear outputs to zero

(2) Preset to binary twelve

(3) Count to thirteen fourteen fifteen zero one and two

(4) Inhibit

5