FPD85308

Panel Timing Controller

General Description

The FPD85308 Panel Timing Controller is an integrated

FPD-Link based TFT-LCD timing controller. It resides on the

flat panel display and provides the interface signal routing

and timing control between graphics or video controllers and

a TFT-LCD system. FPD-Link is a low power, low electro-

magnetic interference interface used between this controller

and the host system.

The FPD85308 chip links the panel's system interface to the

LCD display via a ten wire LVDS data bus. The data is then

routed to the source and gate display drivers. Both XGA and

SVGA resolutions are supported.

The FPD85308 is programmable via an optional external

serial EEPROM. Reserved space in the EEPROM is avail-

able for display identification information. The system can

access the EEPROM to read the display identification data

or program initialization values used by the FPD85308.

Features

n

FPD-Link System Interface utilizes Low Voltage

Differential Signaling (LVDS).

n

Supports Graphics Controllers with Spread Spectrum

interfaces for lower EMI

n

System programmable via EEPROM

n

Suitable for notebook and monitor applications

n

8-bit or 6-bit system interface

n

XGA or SVGA capable

n

Supports single or dual port column drivers

n

Programmable outputs provide customized control for

standard or in-house column drivers and row drivers

n

Programmable slew rate controlled outputs on CD

interface for reduced EMI

n

Polarity pin reduces CD data bus switching

n

CMOS circuitry operates from a 3.3V supply

System Diagram

TRI-STATE

Æ

is a registered trademark of National Semiconductor Corporation.

DS101356-1

PRELIMINARY

May 2001

FPD85308

Panel

T

iming

Controller

© 2001 National Semiconductor Corporation

DS101356

www.national.com

Absolute Maximum Ratings

(Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage (V

DD

)

4.0V

DC Input Voltage (V

IN

)

-0.3V to V

DD

+0.3V

DC Output Voltage (V

OUT

)

-0.3V to V

DD

+0.3V

Storage Temperature Range

(T

STG

)

-65∞C to +150∞C

Lead Temperature (T

L

)

(Soldering 10 sec.)

260∞C

ESD Rating:

(C

ZAP

= 120 pF, R

ZAP

= 1500

)

MM = 200V, HBM = 2000V

Operating Conditions

Min

Max

Units

Supply Voltage (V

DD

)

3.0

3.6

V

Operating Temp. Range (T

A

)

0

70

∞C

Supply Noise Voltage (V

CC

)

100

mV

PP

Note 1: "Absolute Maximum Ratings" are those values beyond which the

safety of the device cannot be guaranteed. They are not meant to imply that

the devices should be operated at these limits. The table of "Electrical

Characteristics" specifies conditions of device operation.

DC Electrical Characteristics

T

A

= 0∞C to 70∞C, V

DD

= 3.3V

±

0.3V (unless otherwise specified)

Symbol

Parameter

Conditions

Min

Max

Units

V

OH

Minimum High Level

Output Voltage

V

DD

= 3.0V, I

OH

= -8 mA

2.4

V

V

OL

Maximum Low Level

Output Voltage

V

DD

= 3.0V, I

OL

= 8 mA

0.4

V

V

IH

Minimum High Level

Input Voltage

2.0

V

V

IL

Maximum Low Level

Input Voltage

0.8

V

I

IN

Input Current

V

IN

= V

DD

10

µA

I

OZ

Maximum TRI-STATE

Output Leakage Current

V

IN

= V

DD

, V

IN

= V

SS

10

µA

I

DD

Average Supply Current

f = 65 MHz, C

LOAD

= 50 pF

312

mA

V

THH

Differential Input High

Threshold

Common Mode Voltage = +1.2V

+100

mV

V

THL

Differential Input Low

Threshold

Common Mode Voltage = +1.2V

-100

mV

Device Specifications

T

A

= 0∞C to 70∞C, V

DD

= 3.3V (unless otherwise specified)

Symbol

Parameter

Conditions

Min

Max

Units

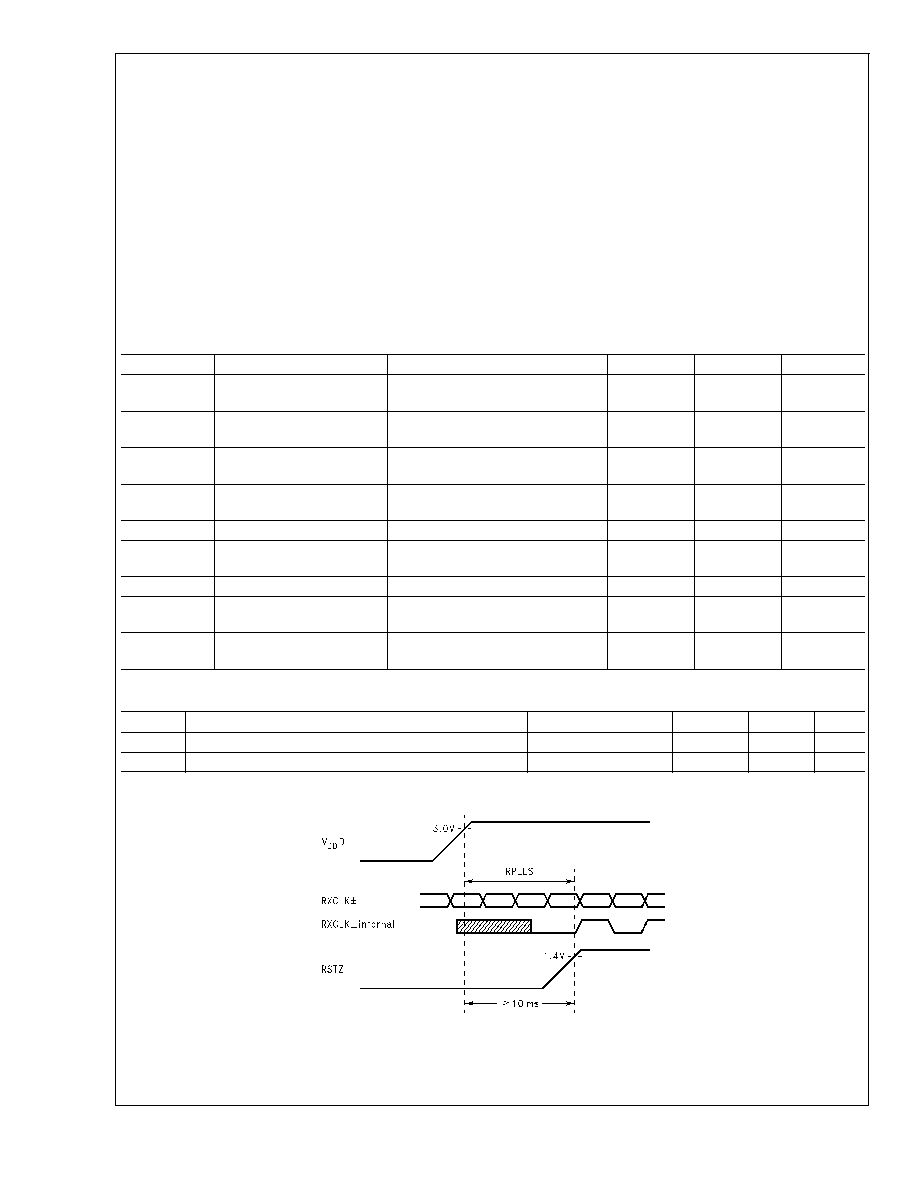

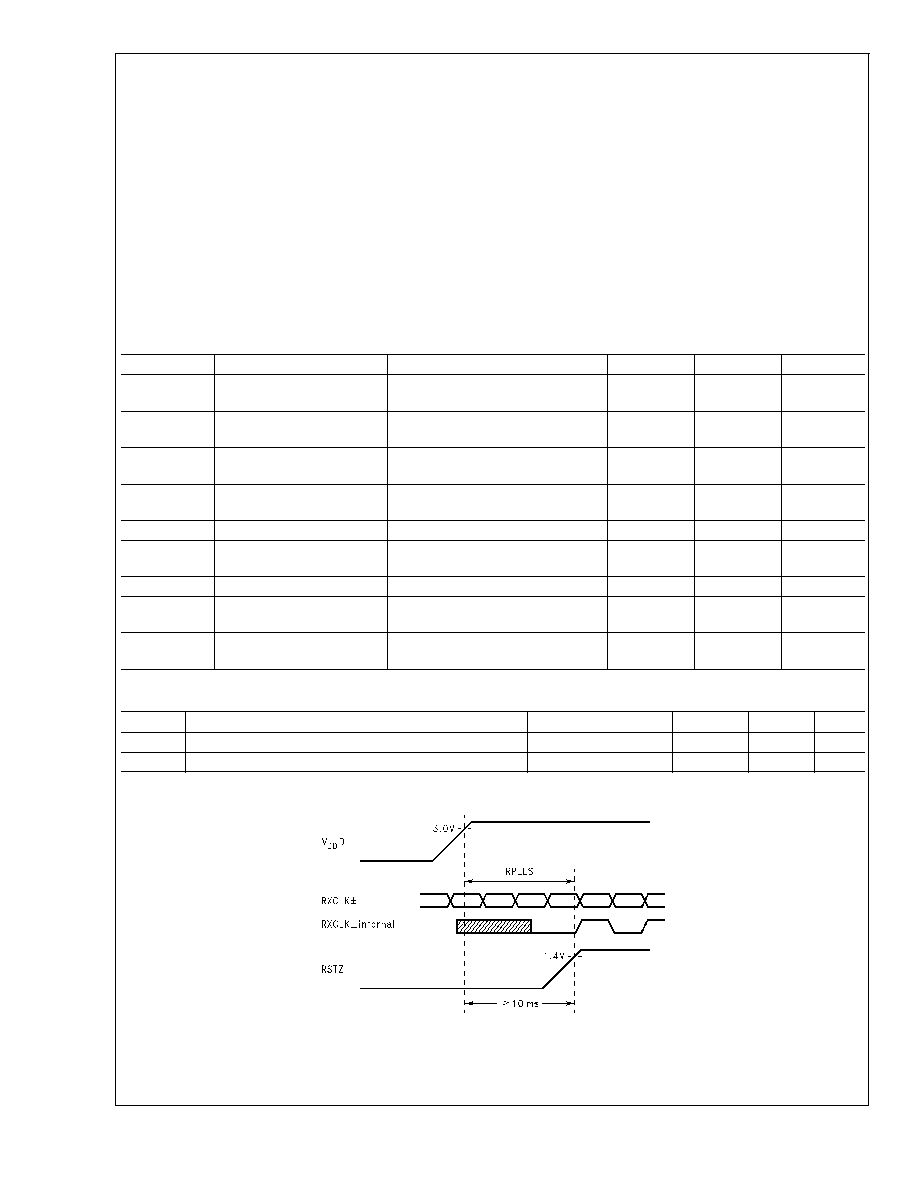

RPLLS

Receiver Phase Lock Loop Set Time

10

ms

RCCS

RxIN Channel-to-Channel Skew (Note 2)

700

ps

Note 2: This limit assumes a maximum cable skew of 350 ps. Actual automated test equipment limit is 400 ps due to tester accuracy.

DS101356-12

FIGURE 1. FPD85308 (Receiver) Phase Lock Loop Set Time

FPD85308

www.national.com

2

Device Specifications

T

A

= 0∞C to 70∞C, V

DD

= 3.3V (unless otherwise specified) (Continued)

DS101356-26

FIGURE 2. FPD85308 Power-up Sequencing

DS101356-13

Note 3: Measurements at V

DIFF

= 0V

Note 4: RCCS measured between earliest and latest LVDS edges

Note 5:

*

RxIN3 pair (RxIN_3

±

) is option for 24-bit color depth

FIGURE 3. FPD85308 (Receiver) Channel-to-Channel Skew and Pulse Width

FPD85308

www.national.com

3

Device Specifications

T

A

= 0∞C to 70∞C, V

DD

= 3.3V (unless otherwise specified) (Continued)

Symbol

Parameter

Conditions

Min

Max

Units

SPsetup

E/OSP from E/OCLK

65 MHz Video (Note 6)

8

ns

SPhold

E/OSP from E/OCLK

65 MHz Video (Note 6)

8

ns

RGBsetup

ER/EG/EB/OR/OG/OB from E/OCLK

65 MHz Video (Note 6)

8

ns

RGBhold

ER/EG/EB/OR/OG/OB from E/OCLK

65 MHz Video (Note 6)

8

ns

CLKpw

E/OCLK pulsewidth

65 MHz Video (Note 6)

11

ns

CLKperiod

E/OCLK period

65 MHz Video (Note 6)

30

ns

Note 6: Timing applies to Dual Bus output modes.

DS101356-27

Note:

R/G/B[5] are MSBs and R/G/B[0] are LSBs

FIGURE 4. FPD85308-6 bit Input Mapping

DS101356-28

Note:

R/G/B[7] are MSBs and R/G/B[0] are LSBs

FIGURE 5. FPD85308-8 bit Input Mapping

FPD85308

www.national.com

4

Device Specifications

T

A

= 0∞C to 70∞C, V

DD

= 3.3V (unless otherwise specified) (Continued)

DS101356-15

FIGURE 6. Column Driver Bus AC Timing

DS101356-16

FIGURE 7. Vertical Backporch Definition

(Video Data from Host)

DS101356-17

FIGURE 8. Horizontal Backporch Definition

(Video Data from Host)

FPD85308

www.national.com

5