© 2000 National Semiconductor Corporation

www.national.com

GeodeTM

G

X1

Pr

ocessor

S

eries

L

o

w

P

o

wer

I

ntegrated

x

86

S

o

l

u

t

i

on

General Description

The National Semiconductor

Æ

GeodeTM GX1 processor

series is a line of integrated processors specifically

designed to power information appliances for entertain-

ment, education, and business. Serving the needs of con-

sumers and business professionals alike, it's the perfect

solution for IA (information appliance) applications such as

thin clients, interactive set-top boxes, and personal internet

access devices.

The Geode GX1 processor series is divided into three main

categories as defined by the core operating voltage. Avail-

able with core voltages of 2.0V, 1.8V, and 1.6V, it offers

extremely low typical power consumption (1.2W, 1.0W, and

0.8W, respectively) leading to longer battery life and

enabling small form-factor, fanless designs. Typical power

consumption is defined as an average, measured running

Microsoft Windows at 80% Active Idle (Suspend-on-Halt)

with a display resolution of 800x600x8 bpp at 75 Hz.

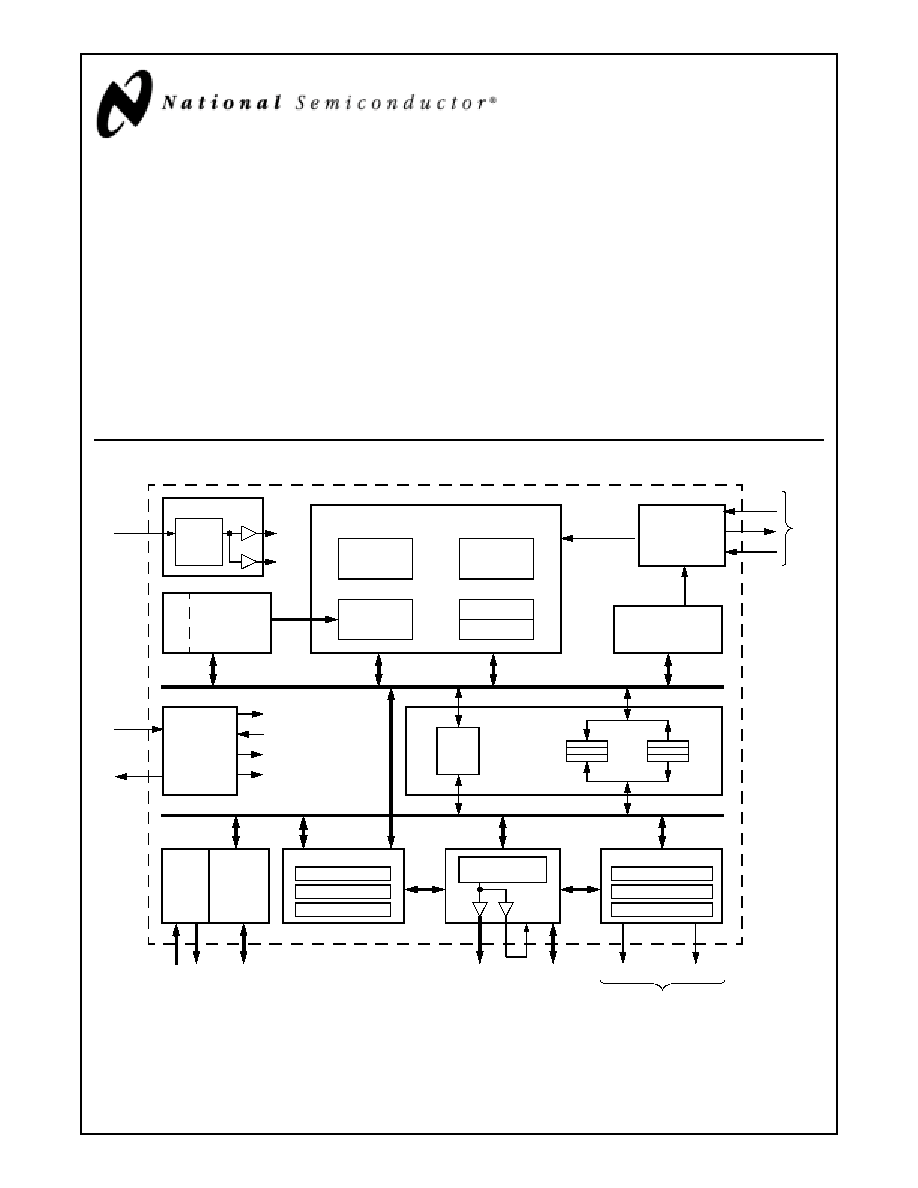

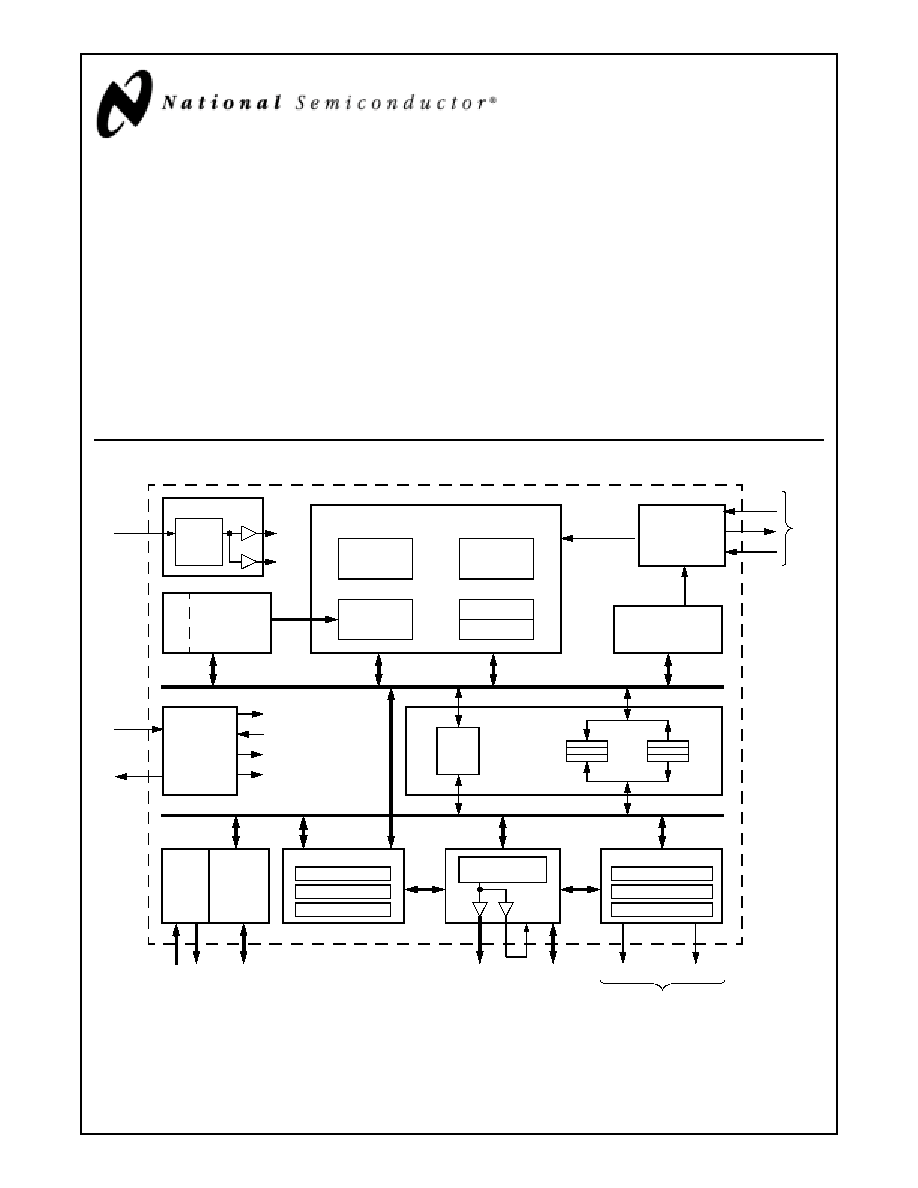

GeodeTM GX1 Processor Internal Block Diagram

Interrupt

Floating Point

Clock Module

SYSCLK

Core

X-Bus

x86 Compatible Core

TLB

Instruction

16 KB

Unified L1

Cache

SYSCLK

X-Bus CLK

(128)

FP_Error

INT/NMI

X-Bus

Power

Management

Control

SUSP#

SUSPA#

Core Suspend

Core Acknowledge

X-Bus Suspend

X-Bus Acknowledge

X-Bus (32)

C-Bus (64)

Write

Read

Display Controller

Timing Generator

INTR

IRQ13

3

REQ/GNT

Pairs

PCI

4

SDRAM

Clocks

64-bit

RGB

YUV

GeodeTM Graphics

S

c

ra

tchp

ad

Arbiter

SMI#

G

eod

eTM

I/O

C

o

mp

ani

o

Clocks

Clocks

Fetch

MMU

Load/Store

Integer

Unit

Unit

Control

Controller

Palette RAM

Compression Buffer

2D Accelerator

ROP Unit

BLT Engine

VGA

Buffers

Buffers

SDRAM

Bus

Arbiter

PCI Host

Controller

multiplied

by "A"

divide by "B"

Companion Interface

April 2000

GeodeTM GX1 Processor Series

Low Power Integrated x86 Solution

National Semiconductor and Virtual System Architecture are registered trademarks of National Semiconductor Corporation.

Geode, WebPAD, and VSA, are trademarks of National Semiconductor Corporation.

For a complete listing of National Semiconductor trademarks, please visit www.national.com/trademarks.

www.national.com

2

Revision 1.0

G

e

ode

TM

G

X

1

P

r

oc

es

sor

S

er

i

e

s

While the x86 core provides maximum compatibility with

the vast amount of Internet content available, the intelligent

integration of several other functions, such as audio and

graphics, offers a true system-level multimedia solution.

The Geode GX1 processor core is a proven x86 design

that offers competitive performance. It contains integer and

floating point execution units based on sixth-generation

technology. The integer core contains a single, five-stage

execution pipeline and offers advanced features such as

operand forwarding, branch target buffers, and extensive

write buffering. Accesses to the 16 KB write-back L1 cache

are dynamically reordered to eliminate pipeline stalls when

fetching operands.

In addition to the advanced CPU features, the GX1 proces-

sor integrates a host of functions typically implemented

with external components. A full function graphics acceler-

ator contains a VGA (video graphics array) controller, bit-

BLT engine, and a ROP (raster operations) unit for

complete GUI (Graphical User Interface) acceleration

under most operating systems. A display controller con-

tains additional video buffering to enable >30 fps MPEG1

playback and video overlay when used with a National

Semiconductor Geode I/O or graphics companion chip

(e.g., CS5530 or CS9211). Graphics and system memory

accesses are supported by a tightly coupled SDRAM con-

troller which eliminates the need for an external L2 cache.

A PCI host controller supports up to three bus masters for

additional connectivity and multimedia capabilities.

The GX1 processor also incorporates Virtual System

Architecture

Æ

(VSATM)

technology.

VSA

technology

enables the XpressGRAPHICS and XpressAUDIO sub-

systems. Software handlers are available that provide full

compatibility for industry standard VGA and 16-bit audio

functions that are transparent at the operating system level.

Together the National Semiconductor I/O companion and

GX1 processor Geode devices provide a scalable, flexible,

low-power, system-level solution well suited for a wide

array of information appliances ranging from hand-held

personal information access devices to digital set-top

boxes and thin clients.

Features

General Features

Packaging:

-- 352-Terminal Ball Grid Array (BGA) or

-- 320-Pin Staggered Pin Grid Array (SPGA)

0.18-micron four layer metal CMOS process

Split rail design:

-- Available 1.6V, 1.8V, or 2.0V core

-- 3.3V I/O interface

Fully static design

Low Typical Power Consumption:

-- 0.8W @ 1.6V/200 MHz

-- 1.2W @ 2.0V/300 MHz

Note:

Typical power consumption is defined as an aver-

age, measured running Windows at 80% Active

Idle (Suspend-on-Halt) with a display resolution of

800x600x8 bpp @ 75 Hz.

Speeds offered up to 300 MHz

Unified Memory Architecture

-- Frame buffer and video memory reside in main

memory

-- Minimizes PCB (Printed Circuit Board) area require-

ments

-- Reduces system cost

Compatible with multiple Geode I/O companion devices

provided by National Semiconductor

32-Bit x86 Processor

Supports Intel's MMX instruction set extension for the

acceleration of multimedia applications

16 KB unified L1 cache

Six-stage pipelined integer unit

Integrated Floating Point Unit (FPU)

Memory Management Unit (MMU) adheres to standard

paging mechanisms and optimizes code fetch perfor-

mance:

-- Load-store reordering gives priority to memory reads

-- Memory-read bypassing eliminates unnecessary or

redundant memory reads

Re-entrant System Management Mode (SMM)

enhanced for VSA technology

Revision 1.0

3

www.national.com

G

e

ode

TM

G

X

1

P

r

oc

es

sor

S

er

i

e

s

Flexible Power Management

Supports a wide variety of standards:

-- APM (Advanced Power Management) for Legacy

power management

-- ACPI (Advanced Configuration and Power Interface)

for Windows power management

≠ Direct support for all standard processor (C0-C4)

states

-- OnNOW design initiative compliant

Supports a wide variety of hardware and software

controlled modes:

-- Active Idle (core-only stopped, display active)

-- Standby (core and all integrated functions halted)

-- Sleep (core and integrated functions halted and all

external clocks stopped)

-- Suspend Modulation (automatic throttling of CPU

core via Geode I/O or graphics companion chip)

≠ Programmable duty cycle for optimal performance/

thermal balancing

-- Several dedicated and programmable wake-up

events (via Geode I/O or graphics companion chip)

PCI Host Controller

Several arbitration schemes supported

Directly supports up to three PCI bus masters, more with

external logic

Synchronous to CPU core

Allows external PCI master accesses to main memory

concurrent with CPU accesses to L1 cache

Virtual Systems Architecture Technology

Innovative architecture allowing OS independent (soft-

ware) virtualization of hardware functions

Provides XpressGRAPHICS subsystem:

-- High performance legacy VGA core compatibility

Note:

The GUI acceleration is pure hardware.

Provides 16-bit XpressAUDIO subsystem:

-- 16-bit stereo FM synthesis

-- OPL3 emulation

-- Supports MPU-401 MIDI interface

-- Hardware assist provided via Geode I/O companion

chip

Additional hardware functions can be supported as

needed

2D Graphics Accelerator

Accelerates BitBLTs, line draw, text:

-- Bresenham vector engine

Supports all 256 Raster Operations (ROPs)

Supports transparent BLTs and page flipping for

Microsoft's DirectDraw

Runs at core clock frequency

Full VGA and VESA mode support

Special "driver level" instructions utilize internal

scratchpad for enhanced performance

Display Controller

Display Compression Technology (DCT) architecture

greatly reduces memory bandwidth consumption of

display refresh

Supports a separate video buffer and data path to

enable video acceleration in Geode I/O and graphics

companion chips

Internal palette RAM for gamma correction

Direct interface to Geode I/O and graphics companion

chips for CRT and TFT flat panel support eliminates the

need for an external RAMDAC

Hardware cursor

Supports up to 1280x1024x8 bpp and 1024x768x16 bpp

XpressRAM

SDRAM interface tightly coupled to CPU core and

graphics subsystem for maximum efficiency

64-Bit wide memory bus

Support for:

-- Two 168-pin unbuffered DIMMs

-- Up to 16 simultaneously open banks

-- 16-byte reads (burst length of two)

-- Up to 512 MB total memory supported

Diverse Operating System Support

Microsoft's Windows 2000, Windows 95, Windows 98,

and Windows NT in non PC applications; along with

Windows CE and Windows NTE

WindRiver System's VxWorks

QNX Software Systems' QNX

Linux

www.national.com

4

Revision 1.0

G

e

ode

TM

G

X

1

P

r

oc

es

sor

S

er

i

e

s

Table of Contents

1.0

Architecture Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1.1

INTEGER UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.2

FLOATING POINT UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.3

WRITE-BACK CACHE UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.4

MEMORY MANAGEMENT UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.5

INTERNAL BUS INTERFACE UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.6

INTEGRATED FUNCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

1.6.1

Graphics Accelerator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

1.6.2

Display Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

1.6.3

XpressRAM Memory Subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

1.6.4

PCI Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

1.7

GEODE GX1/CS5530 SYSTEM DESIGNS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1.7.1

Reference Designs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.0

Signal Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.1

PIN ASSIGNMENTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.2

SIGNAL DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2.2.1

System Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2.2.2

PCI Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.2.3

Memory Controller Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

2.2.4

Video Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

2.2.5

Power, Ground, and No Connect Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

2.2.6

Internal Test and Measurement Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.0

Processor Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

3.1

CORE PROCESSOR INITIALIZATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

3.2

INSTRUCTION SET OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3.2.1

Lock Prefix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3.3

REGISTER SETS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.3.1

Application Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.3.1.1

General Purpose Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.3.1.2

Segment Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3.3.1.3

Instruction Pointer Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3.3.1.4

EFLAGS Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

3.3.2

System Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

3.3.2.1

Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

3.3.2.2

Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

3.3.2.3

Debug Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

3.3.2.4

TLB Test Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

3.3.2.5

Cache Test Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

3.3.3

Model Specific Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

3.3.4

Time Stamp Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

3.4

ADDRESS SPACES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

3.4.1

I/O Address Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

3.4.2

Memory Address Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Revision 1.0

5

www.national.com

G

e

ode

TM

G

X

1

P

r

oc

es

sor

S

er

i

e

s

Table of Contents

(Continued)

3.5

OFFSET, SEGMENT, AND PAGING MECHANISMS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

3.5.1

Offset Mechanism . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

3.5.2

Segment Mechanisms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

3.5.2.1

Real Mode Segment Mechanism . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

3.5.2.2

Virtual 8086 Mode Segment Mechanism . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

3.5.2.3

Segment Mechanism in Protected Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

3.5.2.4

Segment Selectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

3.5.3

Descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

3.5.3.1

Global and Local Descriptor Table Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

3.5.3.2

Segment Descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

3.5.3.3

Task, Gate, Interrupt, and Application and System Descriptors . . . . . . . . . . . . . . . . . 71

3.5.4

Paging Mechanism . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

3.6

INTERRUPTS AND EXCEPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

3.6.1

Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

3.6.2

Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

3.6.3

Interrupt Vectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

3.6.3.1

Interrupt Vector Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

3.6.3.2

Interrupt Descriptor Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

3.6.4

Interrupt and Exception Priorities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

3.6.5

Exceptions in Real Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

3.6.6

Error Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

3.7

SYSTEM MANAGEMENT MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

3.7.1

SMM Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

3.7.2

SMI# Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

3.7.3

SMM Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

3.7.4

SMM Memory Space Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

3.7.5

SMM Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

3.7.6

SMM Memory Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

3.7.7

SMI Generation for Virtual VGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

3.7.8

SMM Service Routine Execution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

3.7.9

SMI Nesting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

3.7.9.1

CPU States Related to SMM and Suspend Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

3.8

HALT AND SHUTDOWN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

3.9

PROTECTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

3.9.1

Privilege Levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

3.9.2

I/O Privilege Levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

3.9.3

Privilege Level Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

3.9.3.1

Gates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

3.9.4

Initialization and Transition to Protected Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

3.10

VIRTUAL 8086 MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

3.10.1

Memory Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

3.10.2

Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

3.10.3

Interrupt Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

3.10.4

Entering and Leaving Virtual 8086 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

3.11

FLOATING POINT UNIT OPERATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

3.11.1

FPU Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

3.11.2

FPU Tag Word Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

3.11.3

FPU Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

3.11.4

FPU Mode Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94