LM4560

Advanced PCI Audio Accelerator

General Description

LM4560 is an advanced PCI audio accelerator providing full

legacy compatibility, wavetable synthesis, DirectMusic, Di-

rectSound, and DirectSound3D on a single chip for the high-

performance, cost-sensitive consumer market. It supports

Sound Blaster functionality and is fully PC98 compliant.

The LM4560 integrates a 64-voice wave table engine with

per voice effect processing capability. It supports the upcom-

ing Microsoft

TM

DirectMusic API and is fully compatible with

DLS Level 1 (downloadable samples) specification. The

LM4560 is optimized for Microsoft Windows

TM

98 and Win-

dows NT5.0 WDM streaming architecture with re-routable

end-point support. The LM4560 includes DirectSound3D ac-

celeration hardware for ITD (Interaural Time Difference), IID

(Interaural Intensity Difference), Pan, Delay, and Doppler

hardware.

The LM4560 supports Sound Blaster Pro/16 DOS games

while improving gaming audio quality. The LM4560 supports

both the legacy analog gameport and a Digital Enhanced

Game Port. When coupled with DirectInput

TM

driver, the Digi-

tal Enhanced Game Port can save up to 12% of the CPU

overhead nominally required by a conventional analog game

port. The LM4560 employs a high precision 26-bit digital

mixer, providing an accurate 20-bit output and higher than 90

dB signal-to-noise ratio when used with high quality AC97

Rev 1.03 and Rev 2.0 codecs.

The LM4560 is designed with aggressive power manage-

ment. It is PCI Bus Power Management Interface (PPMI

1.0)-compliant. The LM4560 supports multiple Rev 2.0 AC97

codecs, which are useful for notebook docking systems.

With a low power, 3.3V process and a space conscious 100

TQFP package, the LM4560 is also well suited for Notebook

systems.

In summary, the LM4560 provides a balanced combination

of features and performance to the end-user. By combining

PCI bus mastering for DirectSound acceleration, Hardware

Wave table synthesizer, Digital Enhanced Game Port and

DirectSound 3D audio acceleration. It delivers high perfor-

mance, high quality audio, high-end features with efficient

power management in a space-efficient 100 TQFP package.

Features

n

PCI 2.1-compliant with Bus Mastering optimized for

multiple stream operation

n

On-chip per voice cache minimizes PCI bandwidth

n

Up to 20X improvement over ISA DMA on PCI bus

bandwidth utilization

Advanced Wavetable Synthesizer

n

Wavetable synthesis with 64-voices polyphony, which

supports all combinations of stereo/mono, 8-/16-bits,

and signed/unsigned samples

n

Per channel volume, pitch shift, left/right pan, tremolo,

vibrato and envelope control (32 channels in hardware)

n

Per channel effect process ing and effect volume control

for reverb, chorus, and echo

n

DLS1-compliant Downloadable Samples support

Legacy Compatibility

n

Legacy game audio support with SoundBlaster Pro/16

compatibility on the PCI bus

n

Legacy DMA support on PCI Bus with DDMA-enabled or

standard (non-DDMA) PCI chipsets

n

FM through realtime FM-to-wavetable conversion

n

MPU-401 compatible UART for external or internal

synthesis

n

General MIDI/GS command interpretation for wavetable

& effect synthesis

High Quality Audio and AC97 Support

n

CD quality audio with higher than 90 dB signal-to-noise

ratio using an external high quality AC97 codec

n

AC97 support with full duplex, independent sample rate

converter for audio recording and playback

n

On-chip sample rate converter ensures all internal

operation at 48 kHz

n

High precision internal 26-bit digital mixer with 16- and

20-bit digital audio output

Advanced Streaming Architecture

n

Microsoft WDM Streaming architecture compliant and

"Re-routable endpoint" support

n

Three stereo capture channels

n

AC97 stereo recording channel through AC-link

DirectSound 3D

n

64-voices DirectSound channels

n

32-voices DirectSound3D accelerator with IID, ITD, and

Doppler effects on 3D positional audio buffers

n

DirectSound accelerator for volume, pan, and pitch shift

control on streaming or static buffers

Telephony & Modem

n

Full duplex speaker phone with AC97 2.0 audio-modem

codec

n

Fax-modem with host based software

Extras

n

Fully Plug and Play PCI controller and software

n

Digital Enhanced Game port enables an analog joystick

to emulate digital joystick performance using the

National Semiconductor-provided DirectInput driver. This

eliminates up to 12% CPU overhead wasted on joystick

polling.

TRI-STATE

�

is a registered trademark of National Semiconductor Corporation.

Microsoft

TM

is a trademark of Microsoft Corporation.

Windows

�

is a registered trademark of Microsoft Corporation.

DirectInput

TM

is a trademark of Microsoft Corporation

December 1998

LM4560

Advanced

PCI

Audio

Accelerator

� 1998 National Semiconductor Corporation

DS100910

www.national.com

Features

(Continued)

n

DirectX timer for video/audio synchronization

n

Forward pin-compatible with future PCI audio

accelerators

n

100-pin TQFP package

n

3.3V operation

Software Support

n

Complete DirectX driver suite (DirectSound3D,

DirectSound, DirectMusic, and DirectInput) for Windows

95 and Windows 98/NT 5.0

n

Configuration installation, and diagnostics under real

mode DOS, WindowsWindows 95, and Windows 98

DOS box

n

Windows 3.1, 95, NT4.0, Windows 98/NT5.0

configuration, installation, and mixer program

n

1, 2, 4, or 8 Mbytes General MIDI (GM)/General Sound

(GS) compliant sample Library

Block Diagram

Table of Contents

1.0 Pin Description

1.1 Package Diagram

1.2 Pin Description

2.0 Functional Decription

2.1 Device Overview

3.0 Register Description

3.1 PCI Configuration Register Map

3.1.1 PCI Configuration Register Description

3.1.1.1 Device ID & Vendor ID

3.1.1.2 Status & Command

3.1.1.3 Class Code & Revision ID

3.1.1.5 Audio IO Base Register

3.1.1.6 Audio MEM Base Register

3.1.1.7 Subsystem ID & Subsystem vendor ID

3.1.1.8 PCIPM Capability List Pointer Register

3.1.1.9 Max_Lat, Min_Gnt, Interrupt Pin & Interrupt Line

3.1.1.10 DDMA Slave Configuration Register

3.1.1.11 Legacy audio/power management configuration

3.1.1.13 Power management capability register (PMC)

3.1.1.14

Power

management

control/status

register

(PMCSR) & PMCSR_BSE & Data

3.2 Audio Processor Register Map

3.3 Audio Processor Register Access Mode

3.3.1 I/O Access Mode

3.3.2 Memory Access Mode

3.4 Audio Processor Register Description

3.4.1 DMA Registers

3.4.1.1 DMAR0 (Legacy DMA Playback Buffer Base Regis-

ter Port1)

3.4.2 Legacy Sound Blaster/Adlib Registers

3.4.3 Legacy MPU-401 Registers

3.4.4 Legacy Gameport Register

3.4.5 Serial Interface Control Register

3.4.6 Misc and Status Register

3.4.7 OPL3 Channel Status Register

3.4.8 S/PDIF & GPIO Registers

3.4.9 Wave Engine Registers

3.4.9.31 F4h_A (EBUF1) ( Bank A Only)

4.0 Functional Description

4.1 Wave Engine

4.1.1 Scheduler

4.1.2 Address Engine

4.1.3 Envelope Engine

4.1.4 Interpolation & Volume Adjustment

4.1.5 Digital Mixer

4.1.6 LFO

4.1.7 Recording

DS100910-1

www.national.com

2

Table of Contents

(Continued)

4.1.8 PCI Buffer/Sample Cache

4.1.9 CODEC Buffer/Sample FIFO

4.1.10 Legacy Channel Playback/Recording

4.2 Legacy Audio

4.2.1 SB Engine:

4.3 Serial Interface

4.3.1 AC-97 Interface

4.3.2 I2S Interface

4.3.3 S/PDIF

4.4 Power Management

4.4.1 Power Management For D0�D3 States

4.4.2 D0�D3 State Transition Table

5.0 Signals and Timing

5.1.2 Timing

5.1.2.1 Slave read/write timing

6.0 Device Configuration

6.1 Overview

6.2 Configuration and GPIO Registers

7.0 Device Specifications

7.1 Absolute Maximum Ratings

7.2 Capacitance

7.3 Electrical Characteristics

7.4.1 Timing Table

7.4.2 PCI Signals

Physical Dimensions

List of Figures

Figure 1. 100-Pin TQFP Package

Figure 2. LM4560 Block diagram

Figure 3. Wave Engine Block Diagram

www.national.com

3

1.0 Pin Description

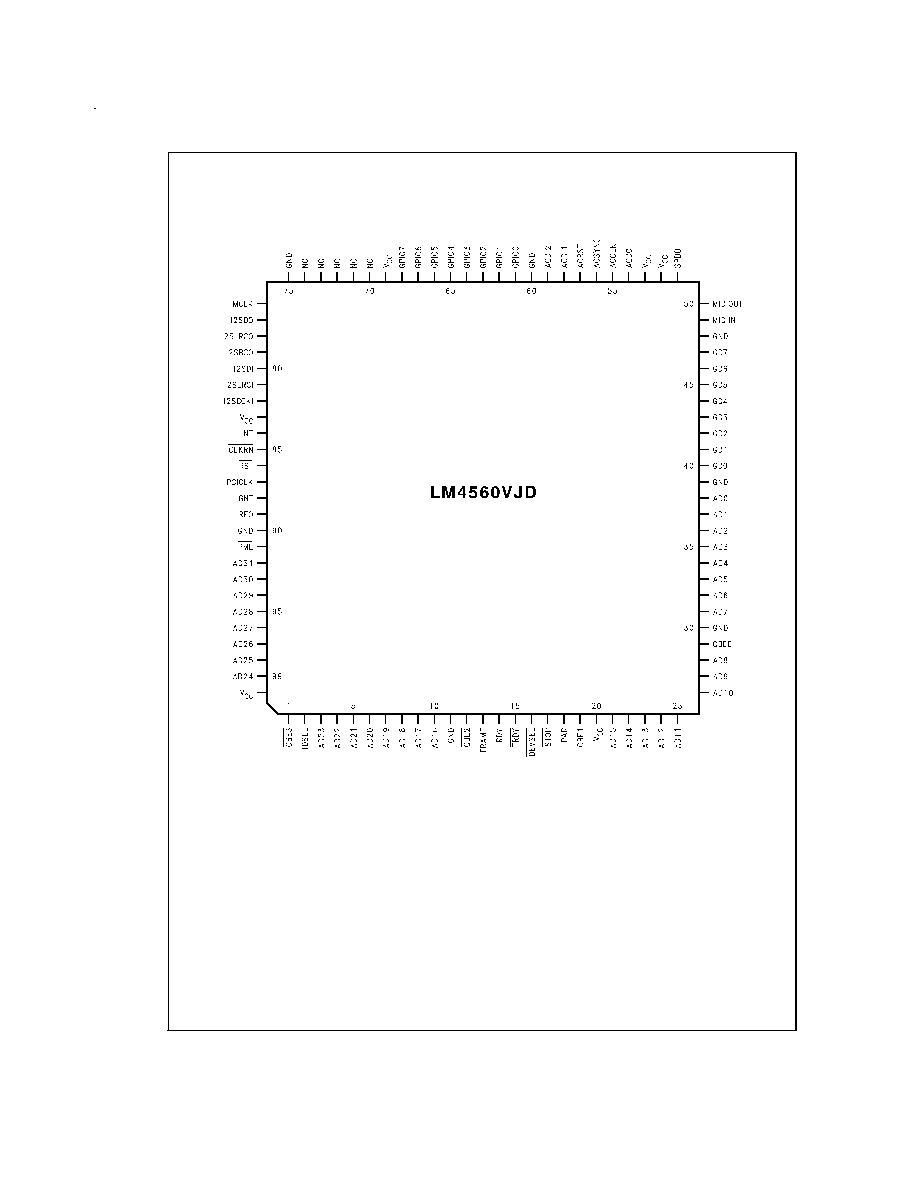

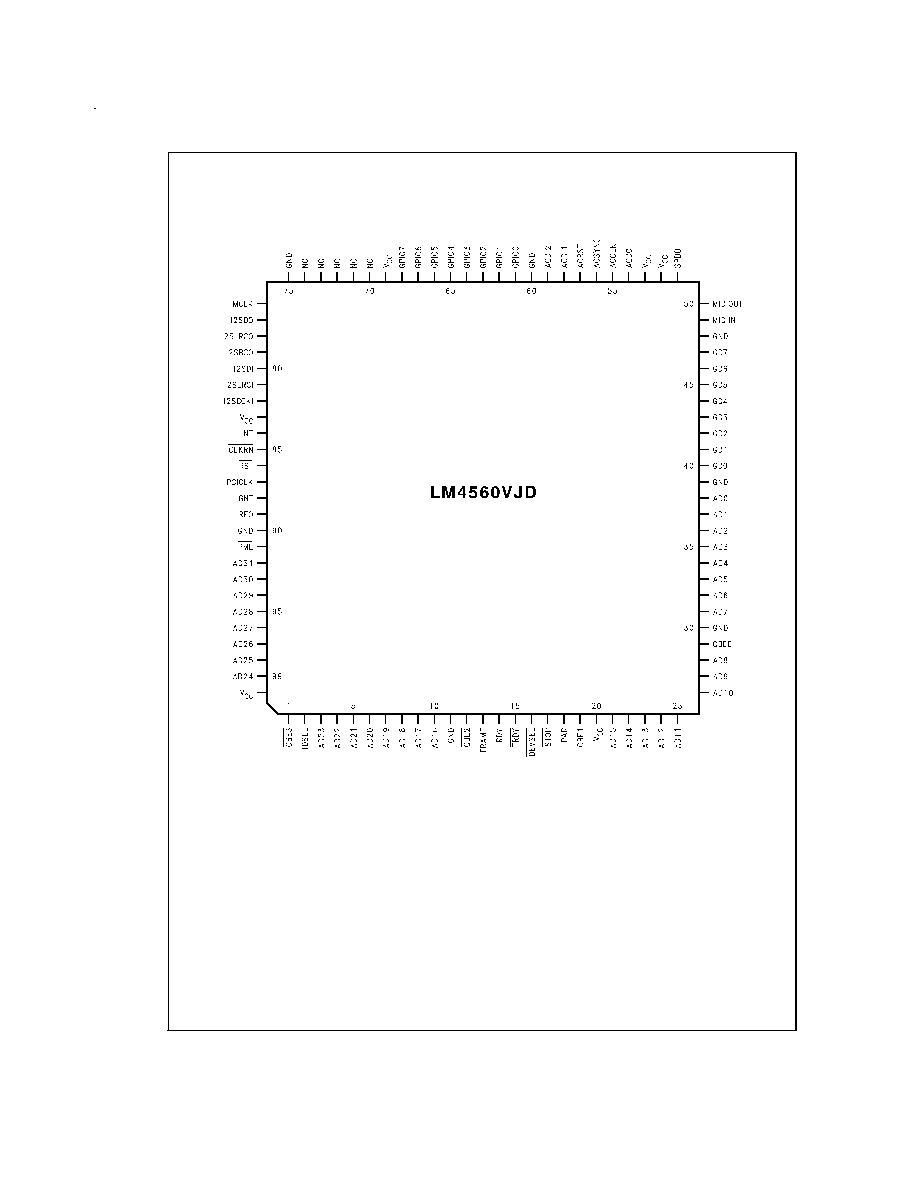

1.1 PACKAGE DIAGRAM

Top View

DS100910-2

FIGURE 1. 100-Pin TQFP Package

www.national.com

4

1.0 Pin Description

(Continued)

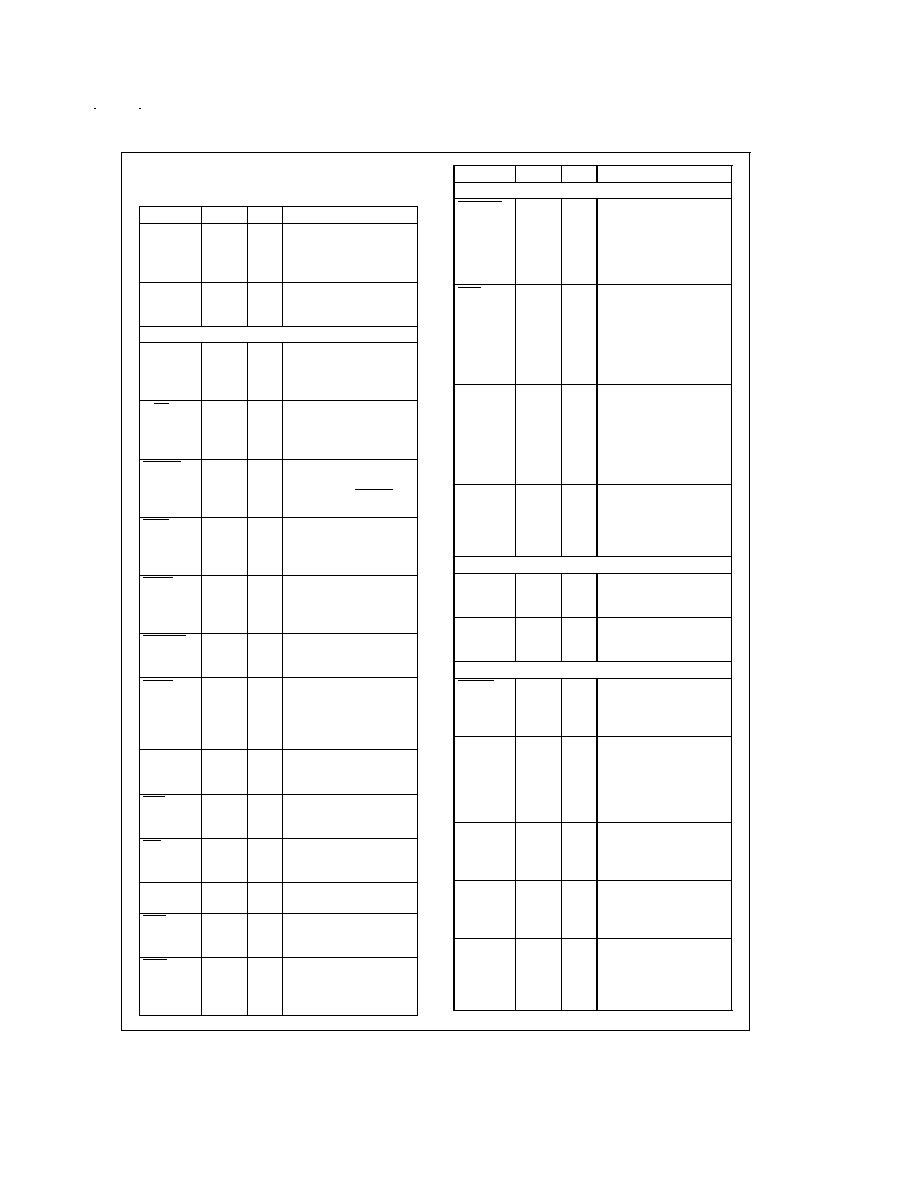

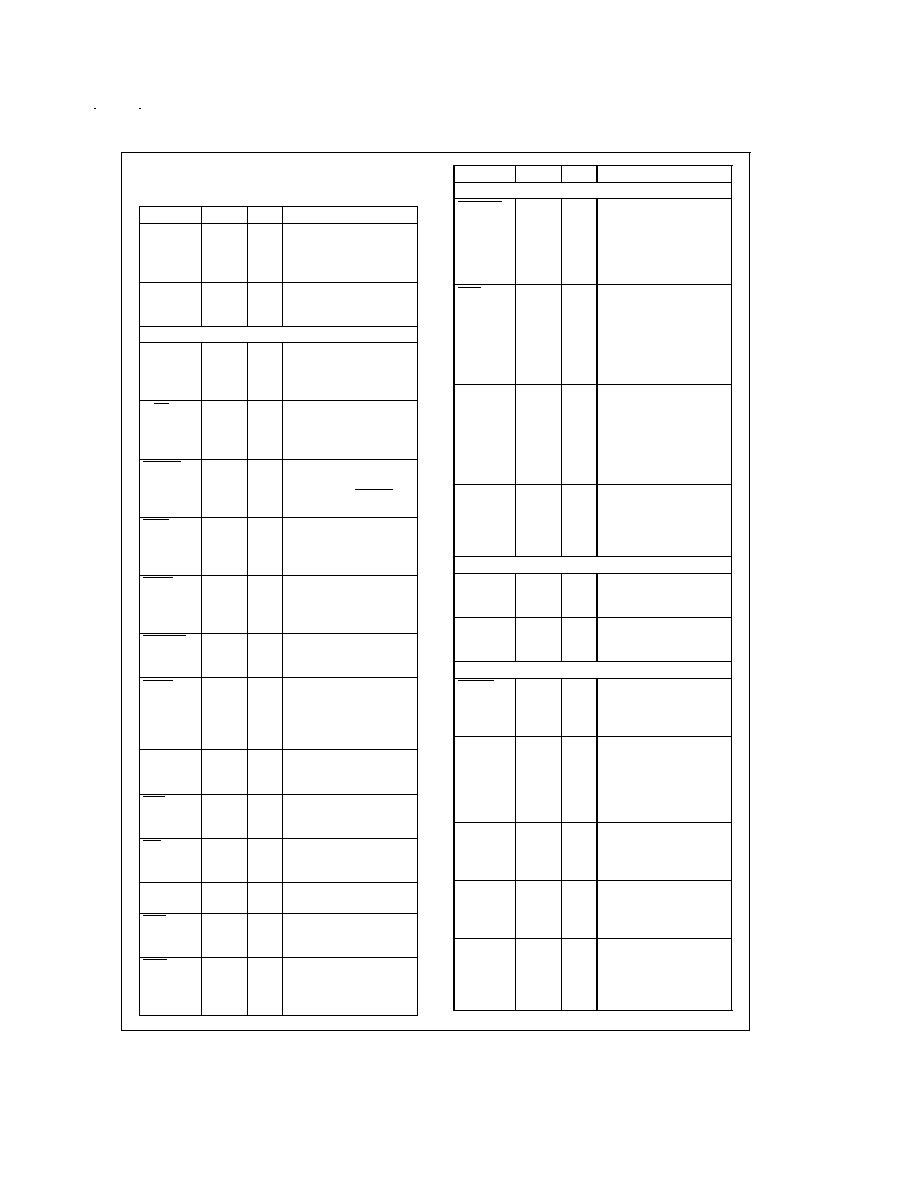

1.2 PIN DESCRIPTION

Symbol

Pin(s)

Type

Description

V

DD

20, 39,

52, 53,

69, 83,

100

IN

3.3V Power Supply

V

SS

11, 30,

48, 60,

75, 90

IN

Ground

PCI BUS INTERFACE SIGNALS (51)

AD[31:0]

92�99,

3�10,

21�28,

31�38

I/O

PCI Address/Data Bus.

A time-multiplexed

address data bus.

C/BE[3:0]

1, 12,

19, 29

I/O

PCI Command/Byte

Enable. Defines the type

of AD bus transaction

type.

FRAME

13

I/O

Cycle Frame. A PCI

transaction begins and

ends with the FRAME

signal.

IRDY

14

I/O

Initiator Ready. An active

low indicates the cycle

initiator is ready to send

or receive data.

TRDY

15

I/O

Target Ready. An active

low indicates that the

target is read to complete

the current transaction.

DEVSEL

16

I/O

Device Select. An active

low indicates the target

has decoded its address.

STOP

17

I/O

STOP. An active low

indicates the target wants

the initiator to stop data

during the current data

phase.

PAR

18

I/O

Parity. Generates an

even parity for the

AD[31.0].

RST

86

IN

Reset. A low active signal

which resets the PCI

device.

INT

84

OUT

Interrupt. An active low

signals in interrupt to the

CPU.

PCICLK

87

IN

Clock. The clock that

drives the PCI timing.

GNT

88

IN

Grant. An active low

signals the master has

access to the PCI bus.

REQ

89

OUT

Request. An active low

indicates the master

wants access to the PCI

bus.

Symbol

Pin(s)

Type

Description

PCI BUS INTERFACE SIGNALS (51)

CLKRUN

85

I/O

Clock Run. An active low

signal used for power

management on

motherboards only. It is

not assigned a pin on the

PCI connector.

PME

91

OUT

Power Management

Event. An active low

signal used for power

management for add in

cards or motherboards. It

is assigned a pin on the

PCI connector.

TC

78

IN

Terminal Count. This

input is asserted by the

DMA controller to indicate

the end of a DMA

transfer. The signal is

only effective during a

DMA access cycle.

IDSEL

2

IN

Initialization Device

Select. An active high

allows reads to the PCI

devices configuration

registers.

MPU-401 INTERFACE SIGNALS (2)

MIDIOUT

50

OUT

MIDI Data Out. Sends

midi data to the midi

connector.

MIDIIN

49

IN

MIDI Data In. Receives

midi data from an

optocoupler.

AC97 CODEC INTERFACE SIGNALS (6)

ACRST

57

OUT

AC97 Master Reset. An

active low which resets

the internal circuitry of

AC97 codecs.

ACCLK

55

IN

AC97 Bit Clock. A

12.288 MHz clock from

the codec. This is used to

synchronize the data

streams to and from the

codecs.

ACSYNC

56

I/O

AC97 Sync. Used to start

the data frame used to

format the serial data to

and from the codecs.

ACDI1

58

IN

Primary CODEC Serial

Data Input. This receives

serial data in from the

primary codec.

ACDI2

59

IN

Secondary CODEC

Serial Data Input. This

receives serial data in

from the secondary

codec.

www.national.com

5