| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: LM5112 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

LM5112

Tiny 7A MOSFET Gate Driver

General Description

The LM5112 MOSFET gate driver provides high peak gate

drive current in the tiny LLP-6 package (SOT23 equivalent

footprint) with improved package power dissipation required

for high frequency operation. The compound output driver

stage includes MOS and bipolar transistors operating in

parallel that together sink more than 7A peak from capacitive

loads. Combining the unique characteristics of MOS and

bipolar devices reduces drive current variation with voltage

and temperature. Under-voltage lockout protection is pro-

vided to prevent damage to the MOSFET due to insufficient

gate turn-on voltage. The LM5112 provides both inverting

and non-inverting inputs to satisfy requirements for inverting

and non-inverting gate drive with a single device type.

Features

n

Compound CMOS and bipolar outputs reduce output

current variation

n

7A sink/3A source current

n

Fast propagation times (25 ns typical)

n

Fast rise and fall times (14 ns/12 ns rise/fall with 2 nF

load)

n

Inverting and non-inverting inputs provide either

configuration with a single device

n

Supply rail under-voltage lockout protection

n

Dedicated input ground (IN_REF) for split supply or

single supply operation

n

Power Enhanced 6-pin LLP package (3.0mm x 3.0mm)

n

Output swings from V

CC

to V

EE

which can be negative

relative to input ground

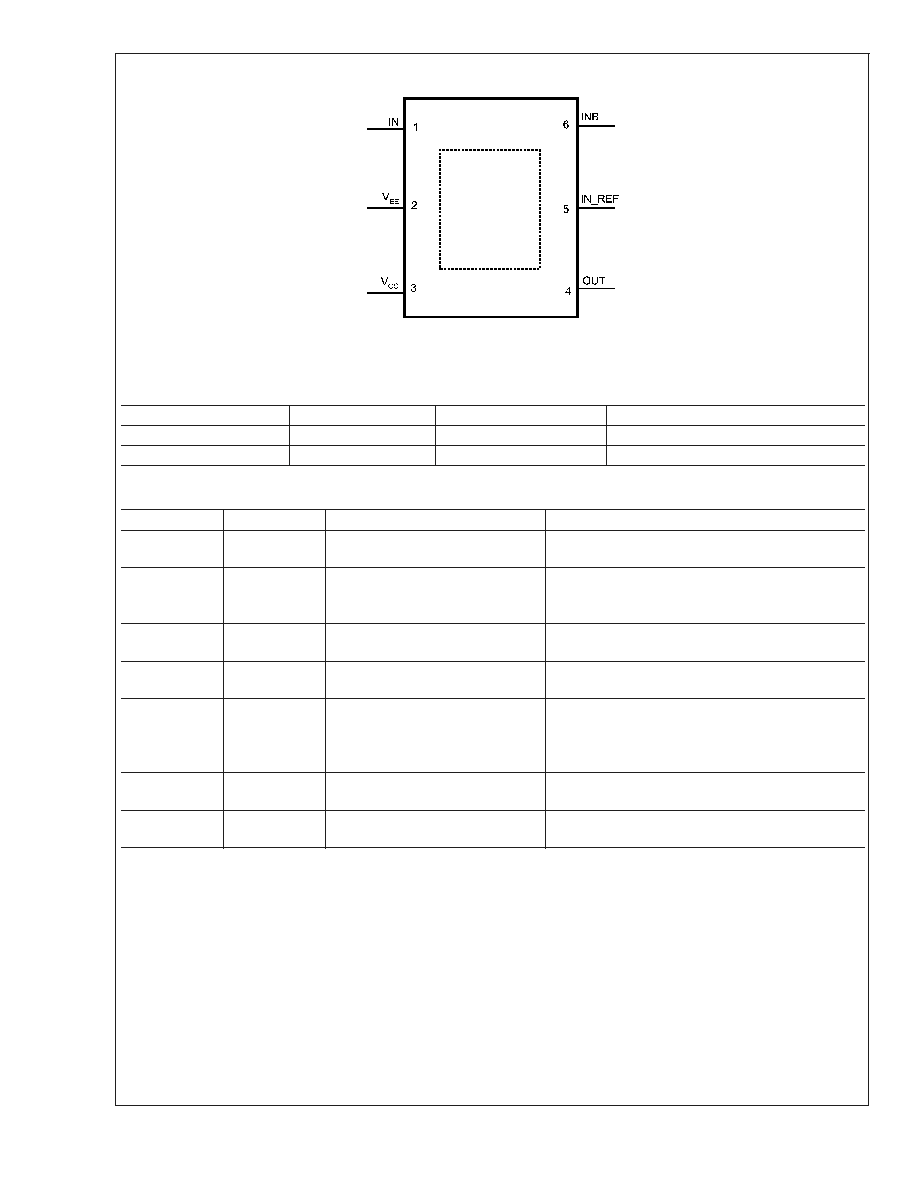

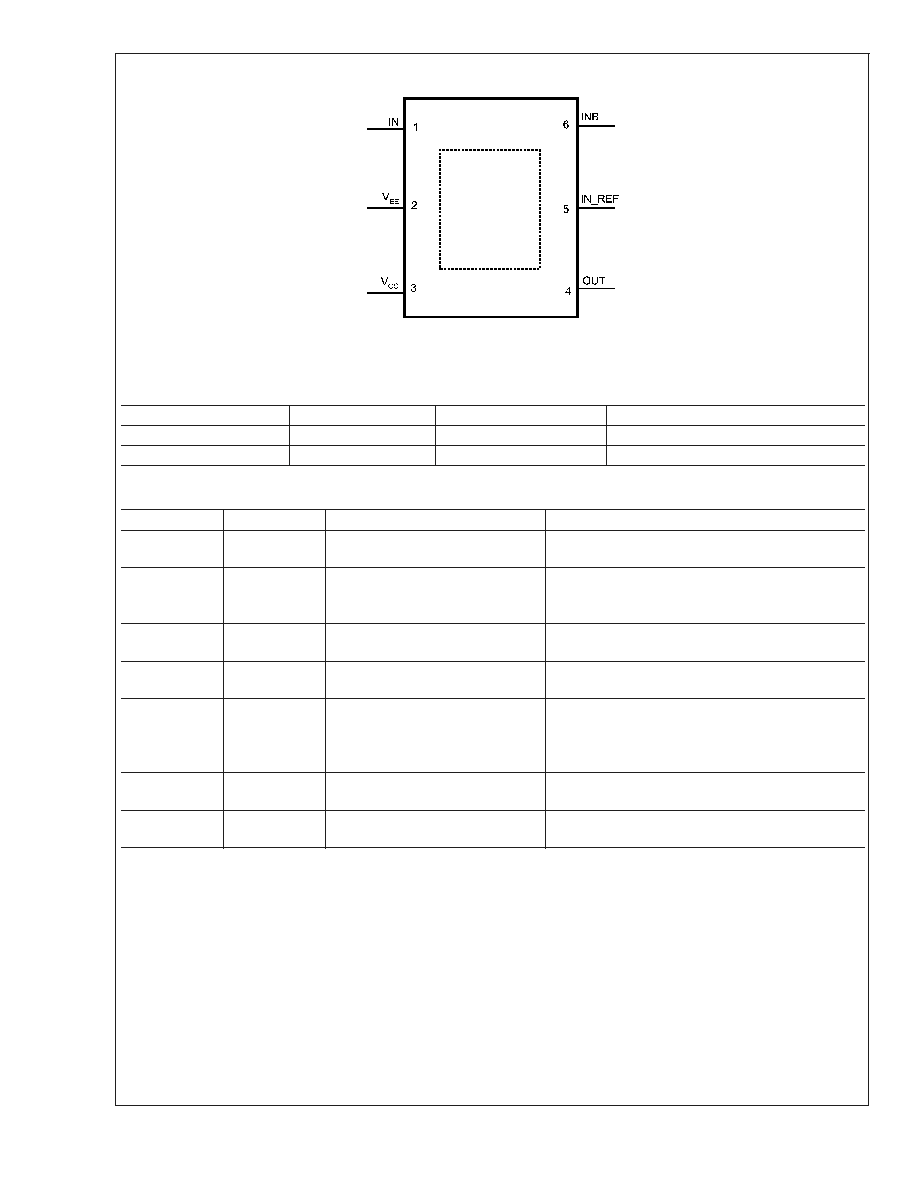

Block Diagram

20066801

Block Diagram of LM5112

October 2004

LM51

12

T

iny

7A

MOSFET

Gate

Driver

© 2004 National Semiconductor Corporation

DS200668

www.national.com

Pin Configurations

20066802

LLP-6

Ordering Information

Order Number

Package Type

NSC Package Drawing

Supplied As

LM5112-SD

LLP-6

SDE06A

1000 shipped in Tape & Reel

LM5112-SDX

LLP-6

SDE06A

4500 shipped in Tape & Reel

Pin Description

Pin

Name

Description

Application Information

1

IN

Non-inverting input pin

TTL compatible thresholds. Pull up to V

CC

when

not used

2

V

EE

Power ground for driver outputs

Connect to either power ground or a negative

gate drive supply for positive or negative voltage

swing

3

V

CC

Positive Supply voltage input

Locally decouple to V

EE

. The decoupling capacitor

should be located close to the chip

4

OUT

Gate drive output

Capable of sourcing 3A and sinking 7A. Voltage

swing of this output is from V

EE

to V

CC

5

IN_REF

Ground reference for control

inputs

Connect to power ground (V

EE

) for standard

positive only output voltage swing. Connect to

system logic ground when V

EE

is connected to a

negative gate drive supply

6

INB

Inverting input pin

TTL compatible thresholds. Connect to IN_REF

when not used

- - -

Exposed

Pad

Exposed Pad, underside of LLP

package

Internally bonded to the die substrate. Connect to

V

EE

ground pin for low thermal impedance

LM51

12

www.national.com

2

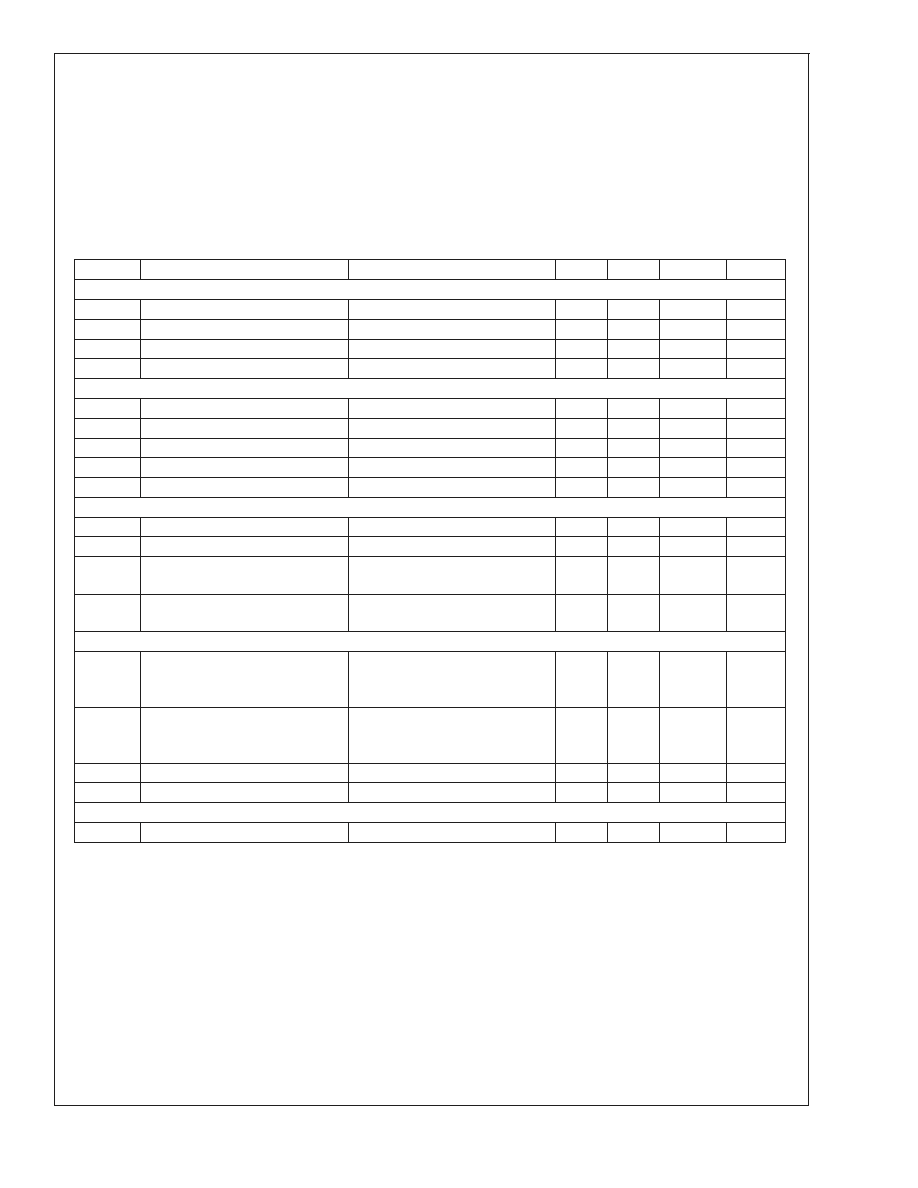

Absolute Maximum Ratings

(Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

V

CC

to V

EE

-0.3V to 15V

V

CC

to IN_REF

-0.3V to 15V

IN/INB to IN_REF

-0.3V to 15V

IN_REF to V

EE

-0.3V to 5V

Storage Temperature Range

-55∞C to +150∞C

Maximum Junction Temperature

+150∞C

Operating Junction Temperature

-40∞C+125∞C

ESD Rating

2kV

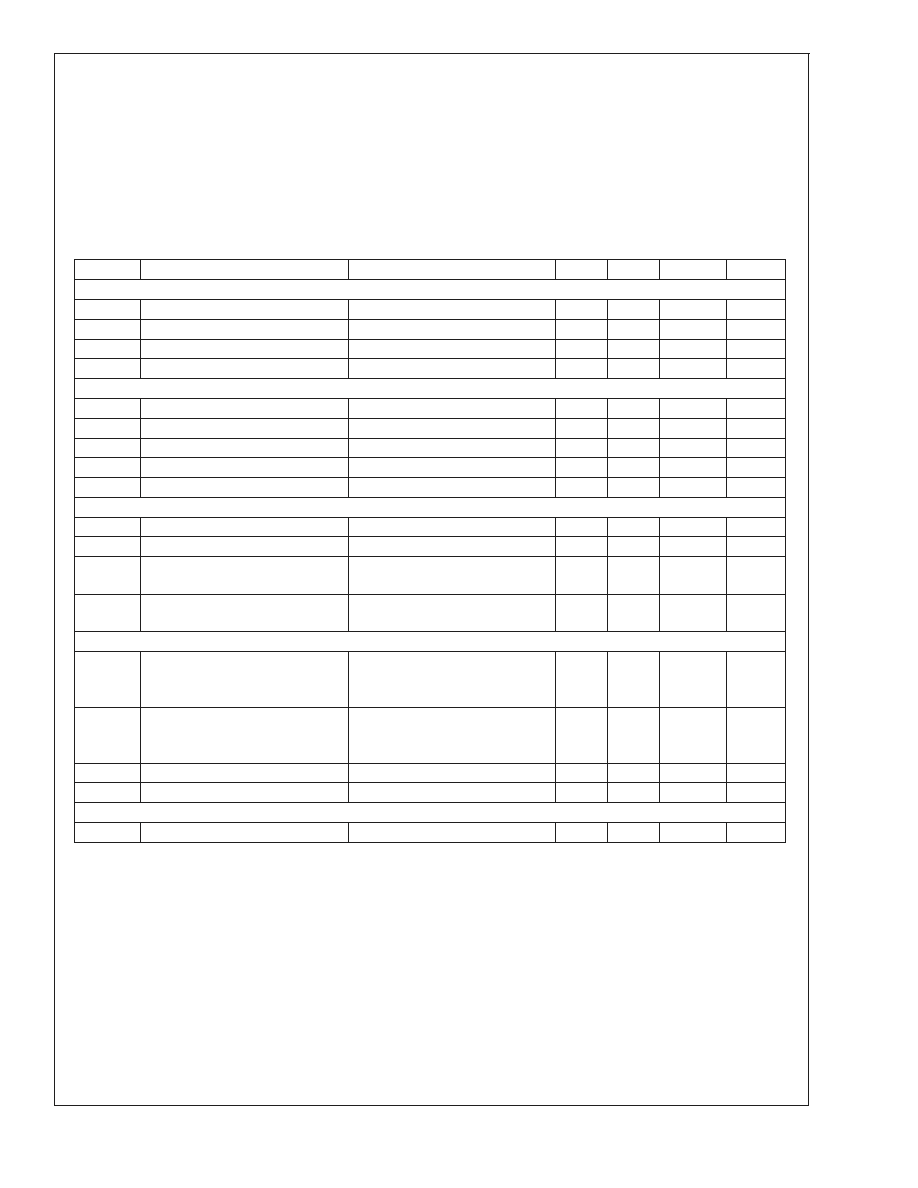

Electrical Characteristics

T

J

= -40∞C to +125∞C, V

CC

= 12V, INB = IN_REF = V

EE

= 0V, No Load on out-

put, unless otherwise specified.

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

SUPPLY

V

CC

V

CC

operating range

V

CC

≠ IN_REF and V

CC

- V

EE

3.5

14

V

UVLO

V

CC

Under-voltage lockout (rising)

V

CC

≠ IN_REF

2.4

3.0

3.5

V

V

CCH

V

CC

Under-voltage hysteresis

230

mV

I

CC

V

CC

supply current

1.0

2.0

mA

CONTROL INPUTS

V

IH

Logic High

1.75

2.3

V

V

IL

Logic low

0.8

1.35

V

HYS

Input Hysteresis

400

mV

I

IL

Input Current Low

IN = INB = 0V

-1

0.1

1

µA

I

IH

Input Current High

IN = INB = V

CC

-1

0.1

1

µA

OUTPUT DRIVER

R

OH

Output Resistance High

I

OUT

= -10mA

30

50

R

OL

Output Resistance Low

I

OUT

= 10mA

1.4

2.5

I

SOURCE

Peak Source Current

OUT = V

CC

/2, 200ns pulsed

current

3

A

I

SINK

Peak Sink Current

OUT = V

CC

/2, 200ns pulsed

current

7

A

SWITCHING CHARACTERISTICS

td1

Propagation Delay Time Low to

High,

IN/ INB rising ( IN to OUT)

C

LOAD

= 2 nF, see Figure 3

25

40

ns

td2

Propagation Delay Time High to

Low,

IN / INB falling (IN to OUT)

C

LOAD

= 2 nF, see Figure 3

25

40

ns

tr

Rise time

C

LOAD

= 2 nF , see Figure 3

14

ns

tf

Fall time

C

LOAD

= 2 nF , see Figure 3

12

ns

LATCHUP PROTECTION

AEC ≠Q100, METHOD 004

T

J

= 150∞C

500

mA

Note 1: Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device

is intended to be functional. For guaranteed specifications and test conditions, see the Electrical Characteristics.

LM51

12

www.national.com

3

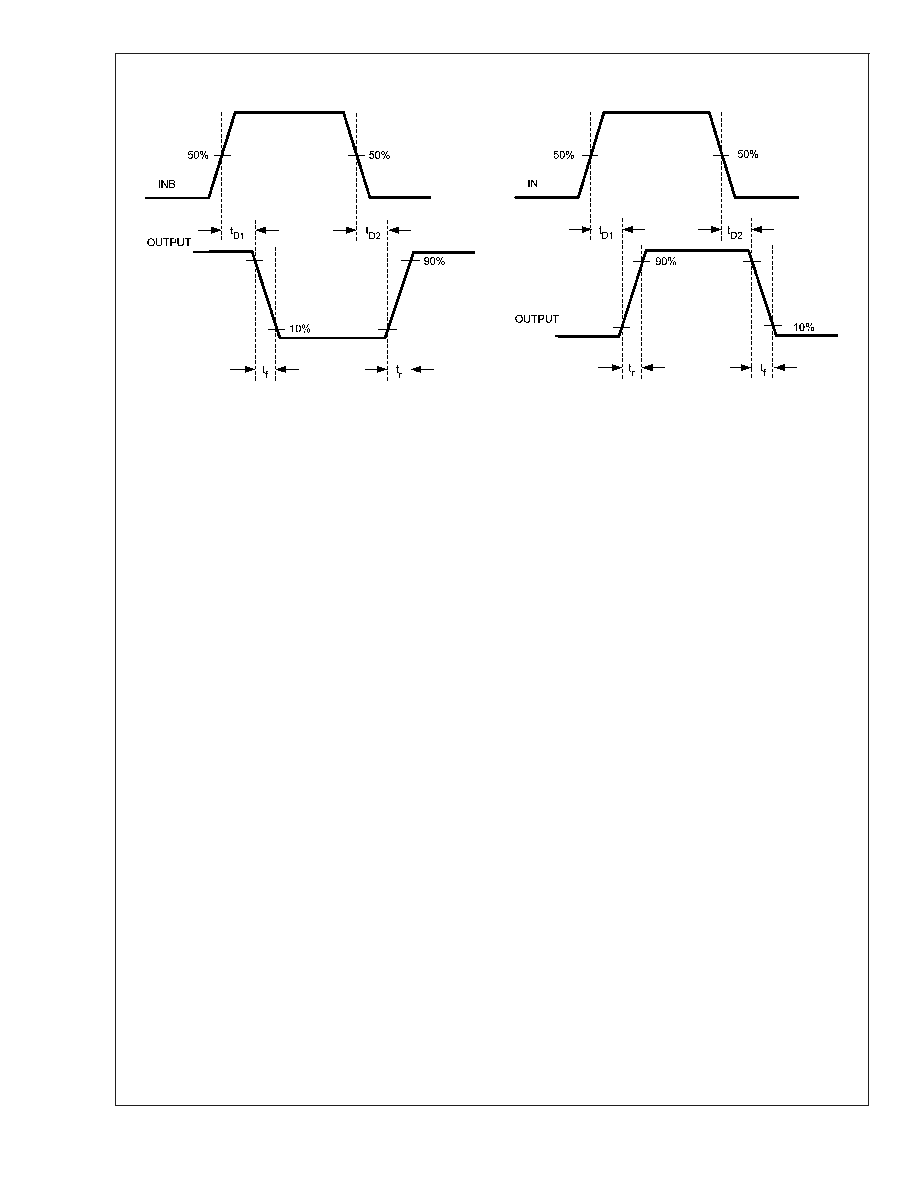

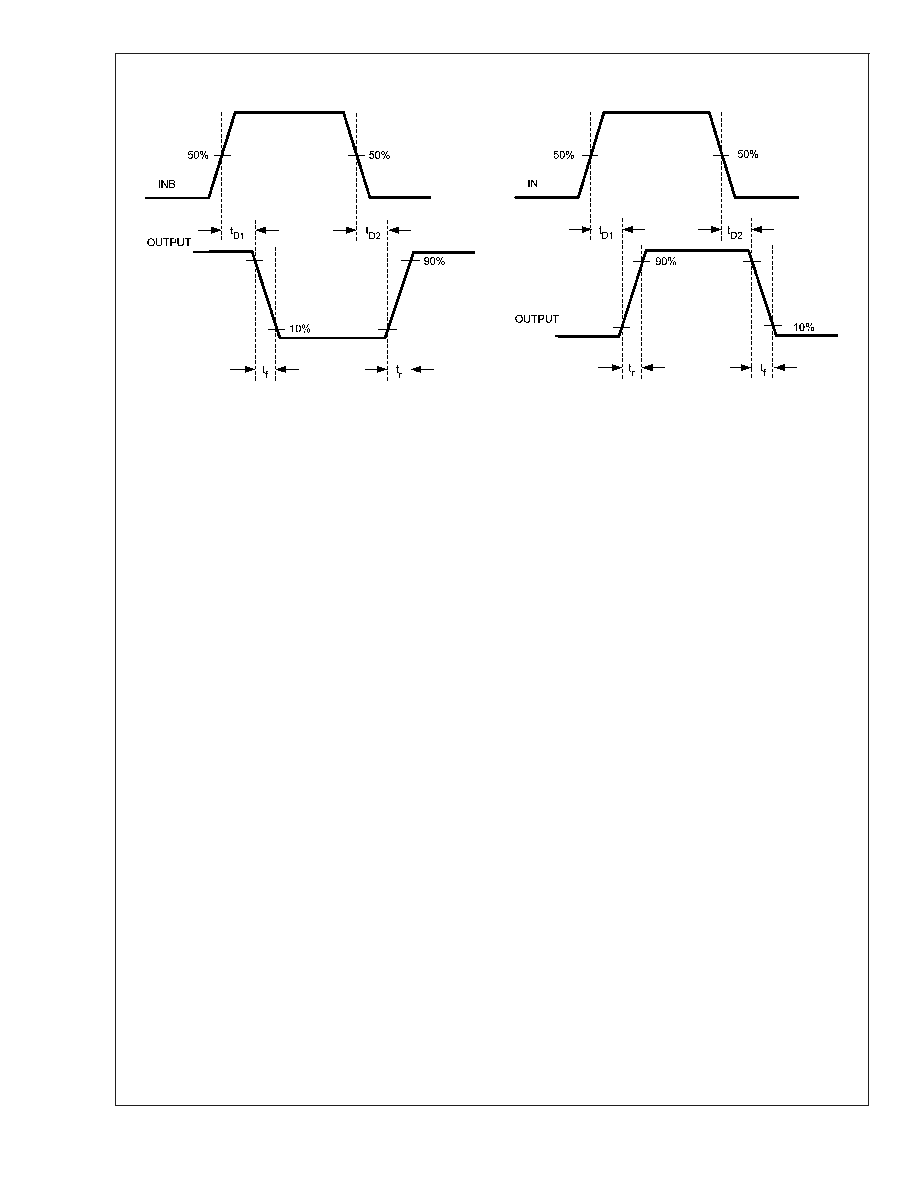

Timing Waveforms

20066804

(a)

20066805

(b)

FIGURE 1. (a) Inverting, (b) Non-Inverting

LM51

12

www.national.com

4

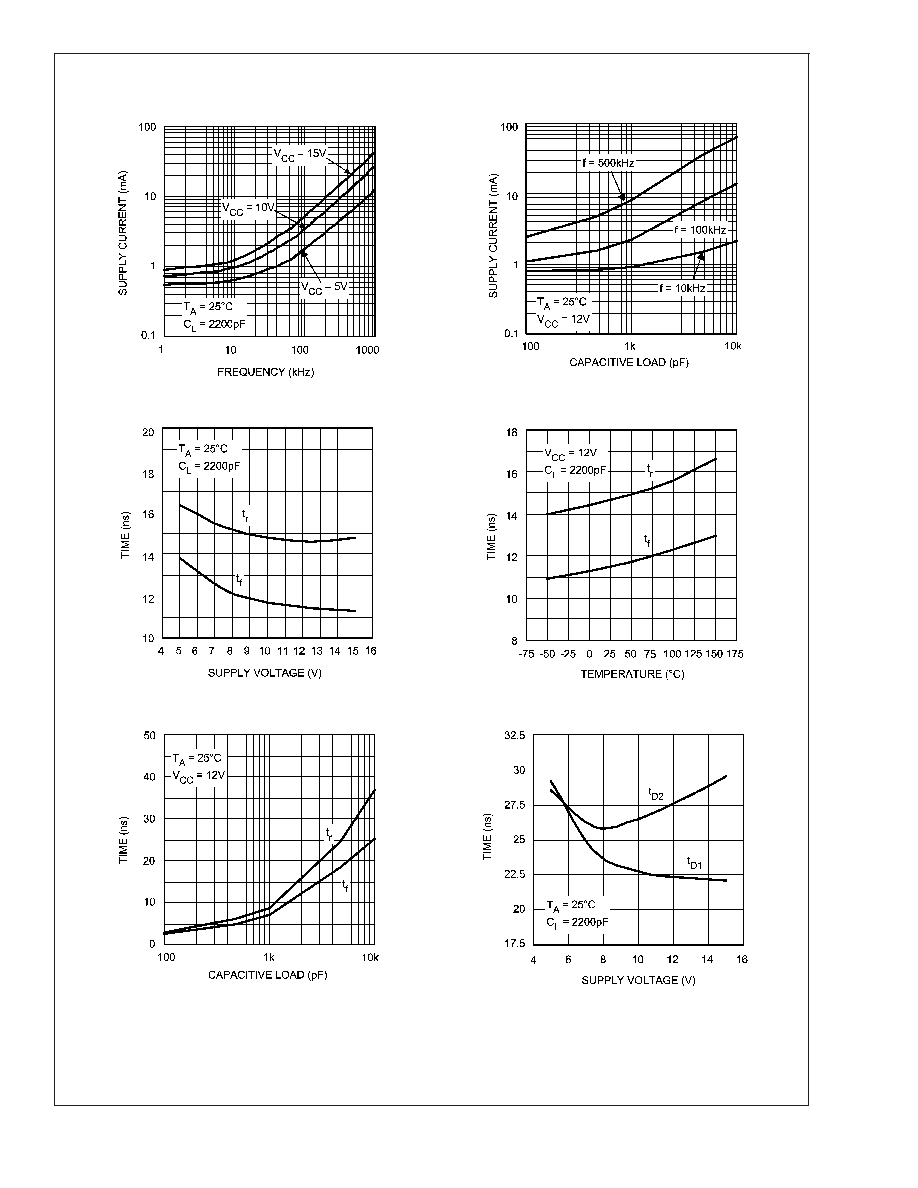

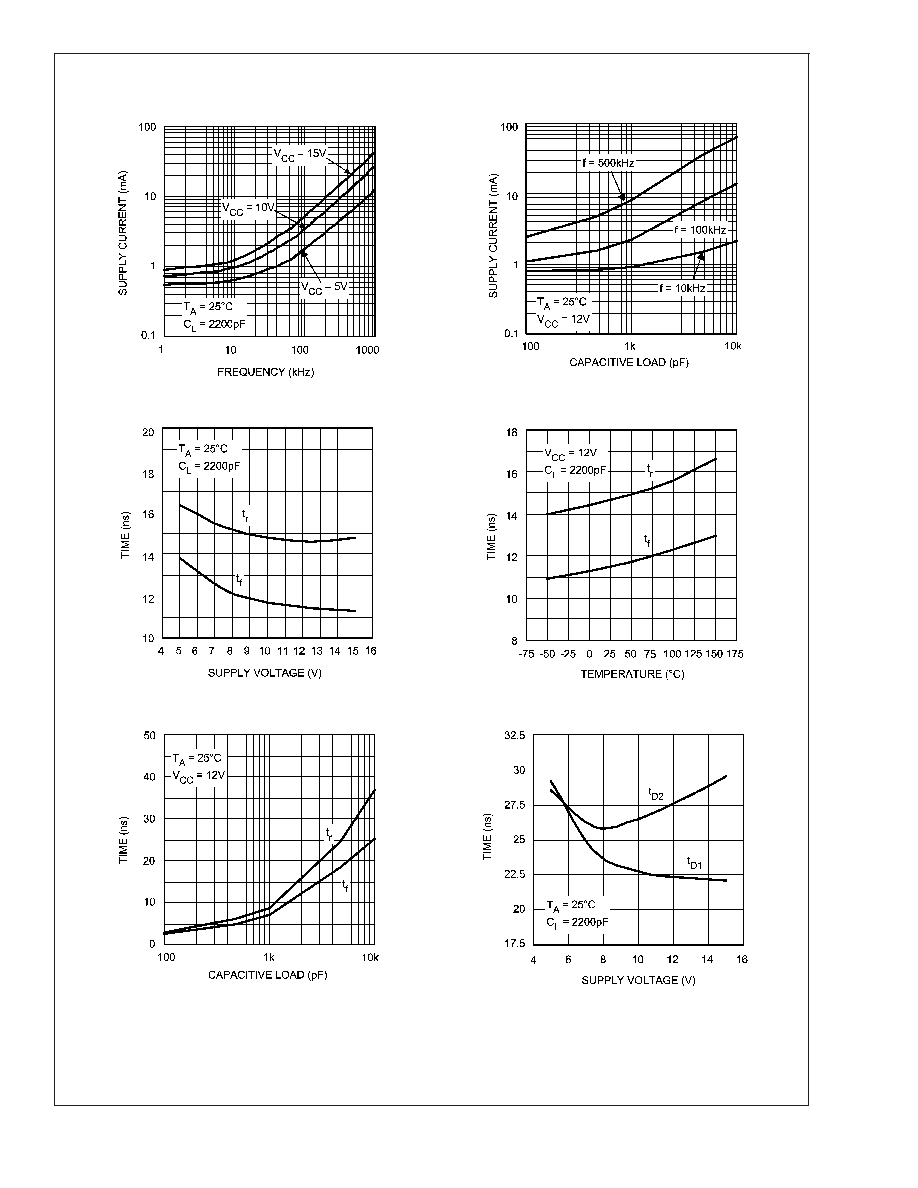

Typical Performance Characteristics

Supply Current vs Frequency

Supply Current vs Capacitive Load

20066807

20066808

Rise and Fall Time vs Supply Voltage

Rise and Fall Time vs Temperature

20066809

20066810

Rise and Fall Time vs Capacitive Load

Delay Time vs Supply Voltage

20066811

20066812

LM51

12

www.national.com

5